#

US 20040113153A1

## (19) United States (12) Patent Application Publication (10) Pub. No.: US 2004/0113153 A1 Wong et al.

## Jun. 17, 2004 (43) **Pub. Date:**

### (54) INTEGRATED ELECTRONIC MICROPHONE

(75)Inventors: Man Wong, New Territories (HK); Yitshak Zohar, Kowloon (HK)

> Correspondence Address: BURNS DOANE SWECKER & MATHIS L L P **POST OFFICE BOX 1404** ALEXANDRIA, VA 22313-1404 (US)

- (73) Assignee: THE HONG KONG UNIVERSITY OF SCIENCE AND TECHNOLOGY, Kowloon (HK)

- (21)Appl. No.: 10/725,388

- Dec. 3, 2003 (22) Filed:

#### **Related U.S. Application Data**

(62) Division of application No. 10/050,858, filed on Jan. 18, 2002, now Pat. No. 6,677,176.

### **Publication Classification**

(51) Int. Cl.<sup>7</sup> ..... H01L 29/04

#### ABSTRACT (57)

The present invention provides an integrated electronic microphone formed as part of a semiconductor device, and a manufacturing method therefor. The microphone is formed with a sensing electrode as part of a sensing membrane, and the sensing electrode is connected to the gate of a sensing transistor to provide an output. The microphone may be operated in constant bias or constant charge mode.

PRAZ5260E Al poly silicon gate oxide low stress nitride 1 10 boron doping arsenic doping normal mitride thermal oxide N-Si

FIG. 1

FIG. 3

US 2004/0113153 A1

PRAZS260E LA poly silicon gate o zide low area minde LTO baron doping arsenic doping normal nimite

Ti PRAZ5260E A poly silicon gate oxide low stress tuttide LTO boron doping arsenic doping normal netride thermal oxide N-Si

īì PRAZ5250E AI poly silicon gate oxide low stress mitride LTO boron doping ars enic doping normal mirrie thermal oxide N-Si

Б PRAZ5260E £A. poly silicon gate o zide low stress nitride LTO boron doping arsenic doping normal miride thermal oxide N-Si

FIG. 2d

Ti PRAZ5250E AI. poly silicon gate oxide low stress nitride LTO boron doping arsenic doping normal nirrite thermal exide N-Si

FIG. 4

FIG. 5

FIG. 7

#### FIELD OF THE INVENTION

**[0001]** This invention relates to a novel design for an integrated electronic microphone, and in particular to such a microphone that can be manufactured by microfabrication techniques, and to methods of manufacturing such a microphone.

#### BACKGROUND OF THE INVENTION

**[0002]** Miniaturized microphones are used in a wide range of applications, such as cell phones, hearing aids, smart toys and surveillance devices for example. It would be desirable to design such microphones and manufacturing methods therefor that allow batch production and allow the integration of the microphone with miniaturised devices having other functions. Microfabrication of various types of miniature microphones has been explored.

#### PRIOR ART

**[0003]** U.S. Pat. No. 5,573,679 discloses capacitive microphones that are fabricated using etch-release of sacrificial silicon by an isotropic dry etchant. The process allows the production of a microphone largely from chemical vapour deposition processes with flexibility in the materials selection. The dry etch chemistry does not require freeze-drying after release, and the etchant does not attack electrodes or metallized circuitry and so allows placement of the electrodes between the backplate and diaphragm dielectric layers. Diffusion barrier layers between the sacrificial and electrode layers protect both materials from interdiffusion during device fabrication. This process is especially suitable for forming a microphone comprising silicon nitride dielectric layers with aluminium electrodes.

**[0004]** U.S. Pat. No. 4,558,184 describes an electroacoustic transducer, such as a microphone, which may be integrated into a semiconductor chip, and a method of fabrication. The semiconductor is etched to produce a membrane having a sufficiently small thickness and an area sufficiently large that the membrane can vibrate at audio frequencies. Electrodes are provided in relation to the membrane so that an electrical output signal can de derived from the vibrations due to variable capacitance.

**[0005]** U.S. Pat. No. 4,533,795 describes an electroacoustic transducer, preferably in the form of a capacitive microphone, for incorporation into a semiconductor substrate. The vibrating element comprises a largely nontensioned diaphragm, such as an epitaxial layer formed on the semiconductor substrate, so as to greatly reduce its mechanical stiffness. The substrate is etched away in the desired area to define the diaphragm and form an acoustic cavity. A continuous array of microscopic holes is formed in the backplate to cut down the lateral flow of air in the gap between the capacitor electrodes. Narrow gaps made possible by the hole array allow low voltage diaphragm biasing.

**[0006]** Also known from the literature are Bergqvist et al "Capacitive microphone with a surface micromachined backplate using electroplating technology", Journal of Microelectromechanical Systems Vol.3 No.2 (June 1994) pp.69-75 which describes a technology for surface micromachining of free-standing metal microstructures using metal electrodeposition on a sacrificial photoresist layer as applied to a condenser microphone. Murphy, P et al "Subminiature silicon integrated electret condenser microphone"6<sup>th</sup> International Symposium on Elecrets (ISE 6) Proceedings describes a structure for a microphone which uses one silicon wafer to support a thin polyester diaphragm and a second to carry a Teflon electret. Subassemblies are diced from the wafer and bonded together to form complete microphones. Finally, Zou, O. B. et al, "Design and fabrication of a novel integrated floating-electrode "Electret" microphone (FEEM)"Proceedings of the 11th IEEE International Workshop on Micro Electro Mechanical Systems, January 1998. pp586-590. describes an electret microphone implemented by a single chip fabrication technique. The microphone uses a charged floating electrode surrounded by highly insulated materials as the "electret" to excite the electric field.

#### SUMMARY OF THE INVENTION

**[0007]** According to the present invention there is provided a semiconductor device comprising a microphone formed in an integrated manner and comprising a sensing electrode formed as part of an acoustic pressure sensing membrane, and a counter electrode in the form of a perforated rigid back-plate membrane, wherein said sensing electrode is connected to the gate of a sensing transistor.

**[0008]** In one embodiment the device may be operable in a constant bias mode. For example, the counter electrode may be set to a bias voltage and the potential of the sensing electrode and hence the gate potential of the sensing transistor may vary in accordance with the acoustic pressure, with the gate potential being biased in the conducting regime whereby variations in the gate voltage vary the output voltage of the sensing transistor.

**[0009]** Another possibility is that the potential of the sensing electrode may be fixed and an output current from the sensing electrode or the counter electrode and varying in response to acoustic pressure on the sensing membrane is taken as the output signal.

**[0010]** In another embodiment the device is operable in a constant charge mode by first charging the sensing electrode followed by setting the potential of the counter electrode to ground and biasing the sensing transistor to a conducting state. The charging of the sensing electrode may be by tunneling from a substrate, or may be by injection from the sensing transistor.

**[0011]** Preferably the sensing membrane is formed of a layer of an insulating material and a layer of a conducting material. The insulating material may comprise low stress silicon nitride, and the conducting material may comprise polysilicon.

**[0012]** Preferably the counter electrode is formed of a layer of a first conducting material and a layer of a second conducting material. In particular the second conducting material may be a relatively hard material and may be sandwiched between two layers of said first conducting material which is preferably a relatively soft material. For example the first material may be aluminium and the second material titanium.

**[0013]** Viewed from another broad aspect the present invention provides a method of forming an integrated semiconductor device including a microphone, comprising the steps of:

- **[0014]** (a) depositing a first layer of an insulating material on a substrate to form a part of an acoustic sensing membrane,

- [0015] (b) depositing a layer of conducting material on said layer of insulating material,

- **[0016]** (c) depositing a second layer of an insulating material on said conducting material,

- [0017] (d) depositing a sacrificial layer on said second layer of insulating material,

- [0018] (c) depositing at least one rigid conducting material on said sacrificial layer to define a rigid counter electrode,

- **[0019]** (f) forming a plurality of holes in said counter electrode,

- **[0020]** (g) etching said substrate from a back side thereof to expose said membrane, and

- [0021] (h) removing said sacrificial layer by etching through said holes to leave an airgap between said membrane and said counter electrode.

**[0022]** Preferably, before step (a), the substrate is subject to an isolation technique to separate on the substrate an area for the membrane, an area for a tunneling window, and areas for forming at least one sensing transistor and a substrate contact.

**[0023]** Preferably the conducting layer of the membrane also forms the gate electrode(s) of at least one sensing transistor.

**[0024]** Viewed from a still further broad aspect the present invention provides a method of forming a semiconductor device including a membrane, comprising the steps of:

- [0025] (a) depositing a membrane forming material on a substrate,

- [**0026**] (b) depositing a sacrificial layer of polysilicon on said membrane forming material,

- [0027] (c) constructing a further semiconductor device structure on said substrate and over said sacrificial layer,

- [0028] (d) removing said sacrificial layer, and

- **[0029]** (c) etching a back side of said substrate to expose said membrane.

**[0030]** Viewed from a yet further broad aspect the present invention provides a method of forming a semiconductor device including a membrane, comprising the steps of:

- [0031] (a) depositing a first membrane forming material on a substrate, said first membrane forming material being an insulating material,

- [0032] (b) depositing a second membrane forming material on said first membrane forming material, said second membrane forming material being a conducting material and said second membrane forming material extending beyond said first membrane forming material so as to contact said substrate, whereby charges may be injected into said conducting material.

**[0033]** (c) depositing a sacrificial layer on said second membrane forming material,

- [0034] (d) constructing a further semiconductor device structure on said substrate and over said sacrificial layer,

- [0035] (e) removing said sacrificial layer, and

- **[0036]** etching a back side of said substrate to expose said membrane.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0037] An embodiment of the invention will now be described by way of example and with reference to the accompanying drawings, in which:—

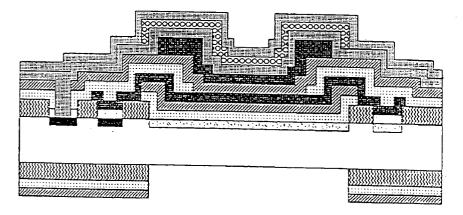

[0038] FIG. 1 is a circuit diagram showing an equivalent circuit model,

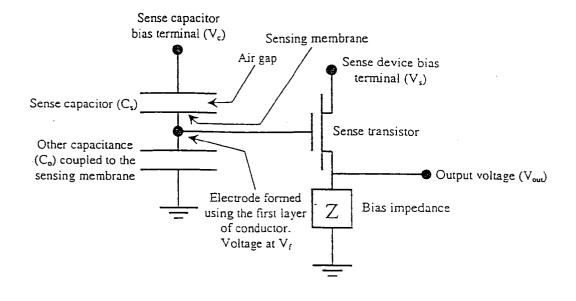

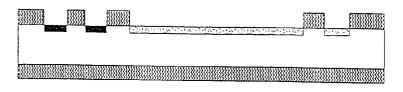

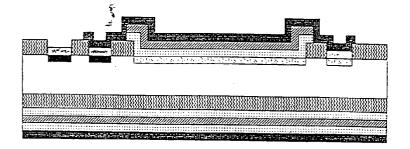

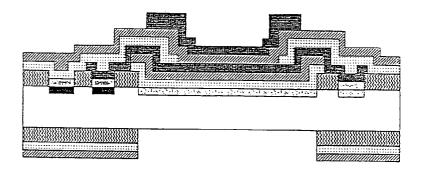

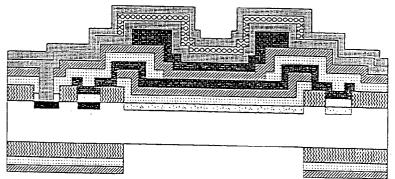

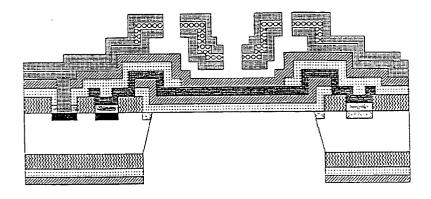

[0039] FIG. 2 shows the main steps of the fabrication process,

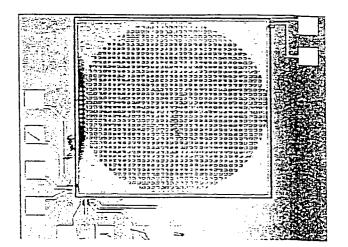

**[0040]** FIG. 3 is a photograph of a device manufactured in accordance with an embodiment of the invention,

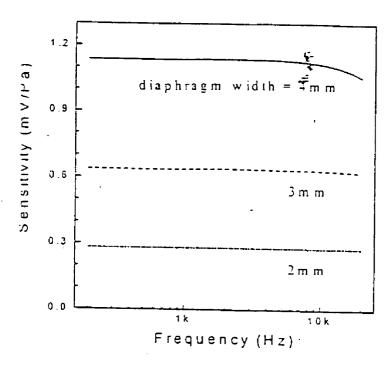

**[0041] FIG. 4** plots the simulated dependence of the frequency response on the membrane size,

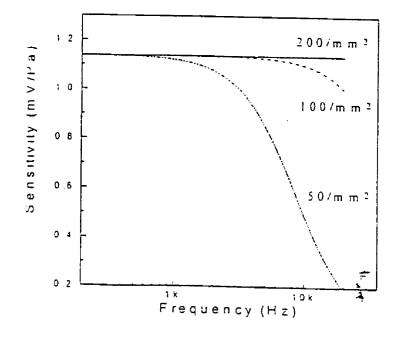

**[0042]** FIG. 5 plots the simulated dependence of the frequency response on ventilation hole density,

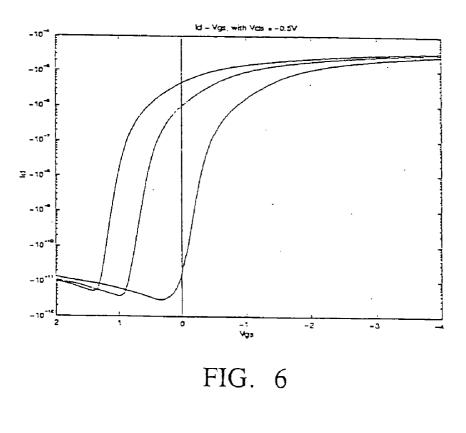

**[0043]** FIG. 6 shows the current-voltage (I-V) characteristics of the sense transistor with different levels of programming, and

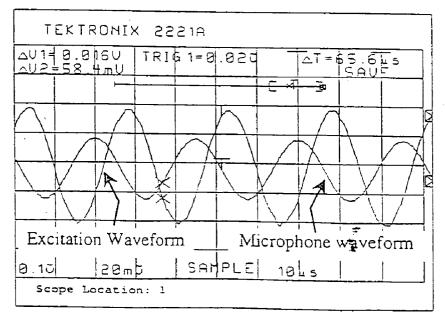

**[0044]** FIG. 7 is a trace showing the response of a microphone in accordance with an embodiment of the invention to an acoustic excitation.

#### DETAILED DESCRIPTION OF PREFERRED EMBODIMENT

[0045] Referring firstly to FIG. 1 there is shown an equivalent circuit model of a microphone in accordance with an embodiment of the invention. At the heart of the microphone is a sense capacitor formed of a sensing membrane which is responsive to acoustic excitation, and a rigid counter electrode, with an airgap between the membrane and the counter electrode. The sensing membrane is formed with an electrode which is connected to or formed integrally with the gate of a sense transistor. The counter electrode may be connected to a bias terminal, and a further capacitance may be connected to the sense capacitor.

**[0046]** This microphone design can be operated in a number of modes.

[0047] Firstly, in a constant bias mode,  $V_c$  is set and  $V_f$  is fixed accordingly via capacitive coupling, namely:

$$V_f = V_c \frac{C_o}{C_o + C_s}$$

**[0048]** The sense transistor, the gate potential of which is  $V_f$ , is biased in the conducting regime. When the sensing membrane is deflected in response to an acoustic pressure (p), the sense capacitance  $C_s$  and hence  $V_f$  is modulated.

Consequently the conductance of the sense transistor is changed and the output voltage  $V_{\rm out}$  is modulated accordingly.

**[0049]** An alternative way of operating in the constant bias mode is to set  $V_f$  to some fixed bias by providing an external electrical contact to the sensing electrode. The signal sensed would then be a varying current  $I_{out}$  which could be taken from either the  $V_c$  or the  $V_f$  terminal, namely:

$$I_{out} = (V_c - V_f) \frac{dC_s}{dp} \frac{dp}{dt}.$$

[0050] In a constant charge mode, the electrically isolated sensing electrode is first charged using a tunneling current established by applying a high  $V_c$  to the capacitor stack and electrons enter through a tunneling window from the substrate. Alternatively charging can be accomplished by injecting into the isolated electrode hot electrons generated at the drain of the sense transistor. Subsequent to the injection,  $V_c$  is set to electrical ground and the sense transistor is biased to a conducting state. The voltage on the sensing membrane is:

$$V_f = \frac{Q_f}{C_o + C_s},$$

**[0051]** Where  $Q_f$  is the total stored charge. When an acoustic excitation is applied to the sensing membrane,  $C_s$  and hence  $V_f$  is modulated. The output voltage is thus modulated accordingly as before. **FIG. 6** shows the simulated I-V characteristics of the sensing transistor with different levels of programming, that is to say with different storage of charge in the storage electrode. The right-most curve is the I-V before programming, the middle and left most curves are I-V characteristics with progressively more electrons being stored in the storage electrode.

[0052] FIGS. 2(a)-(e) show the fabrication process of a microphone in accordance with an embodiment of the present invention. Although in a practical device more than one sensing transistor will be provided, in this example for the sake of clarity only a p-type sensing metal-oxide-semiconductor (MOS) field-effect transistor is shown. Furthermore, extensions of the fabrication process to CMOS circuits containing additionally one or more transistors of n-type polarity can easily be achieved using conventional fabrication techniques as would be readily understood by a skilled reader.

**[0053]** Referring firstly to **FIG.** 2(*a*), the device isolation structures are formed, constructed using techniques including but not limited to the local oxidation of silicon (LOCOS), separating the transistors, the tunneling window, the substrate contact region and the membrane. Boron doping is carried out to adjust the characteristics of the transistors, while the tunneling window and the substrate contact region are heavily doped n-type, using dopants such as phosphorous or arsenic.

[0054] As shown in FIG. 2(b), a first layer of insulator, such as low stress nitride, is deposited and patterned to

eventually form a part of the acoustic sensing membrane. Next the gate dielectric, such as silicon oxide, is formed for the transistors. A first layer of conductor, such as polycrystalline silicon (poly-Si) is deposited and patterned to form one electrode of the sensing capacitor and the gate electrodes of the transistors. Self-aligned boron doping of the gate, source and drain regions of the transistors is done at this stage.

[0055] In FIG. 2(c) a second layer of insulator, such as low stress nitride, is deposited. This layer could, optionally, completely isolate the portion of the first layer of conductor that forms part of the membrane. Patterning of the access to the membrane from the back side of the wafer is next defined. This is followed by the deposition and patterning on the front side of the wafer a layer of sacrificial layer, such as poly-Si, the thickness of which determines the dimension of the air-gap to be formed.

**[0056]** In **FIG.** 2(d) contact holes are opened before a second layer of conducting thin film, such as aluminium, is deposited. Part of the second layer of conducting thin film forms the top, mechanically rigid, counter-electrode plate of the capacitor. A layer of hard conductor, such as titanium, is selectively deposited and patterned on the capacitor to reinforce the stiffness of this plate. A third layer of conducting thin film, again possibly aluminium, is next deposited to balance the mechanical stress distribution in the plate.

[0057] A gird of ventilation holes (FIG. 2(e)) together with interconnections is patterned. Access to the bottom of the membrane is achieved by etching through the silicon wafer from the underside. The top of the membrane is released by removing the poly-Si sacrificial layer through the ventilation holes.

**[0058]** FIG. 3 shows a plan-view photograph of a completed device. The square perforated top membrane occupies the center of the photograph. The tunneling window and the substrate contact are located at the top right-hand corner of the membrane. A set of sensing transistors is located at the lower left-hand corner of the membrane.

[0059] FIG. 4 is a plot showing the simulated dependence of the frequency response on the membrane size, while FIG. 5 is a plot showing the simulated dependence of the frequency response on the ventilation hole density. These plots show that the performance of a microphone in accordance with an embodiment of the invention improves with increasing membrane size and increasing ventilation hole density.

**[0060] FIG. 6** shows the measured response of an integrated microphone in accordance with an embodiment of this invention when excited by acoustic signals. When the sensing membrane is excited by acoustic signals, the change in capacitance of the sensing capacitor is converted to a voltage signal, since the floating gate provides a relatively constant electric field due to the injected charge. The change in the voltage is converted by the current-buffer to a measurable output signal.

**[0061]** It will thus be seen that, at least in preferred embodiments, the present invention provides for the simultaneous realisation of both the mechanical and electrical components of an integrated microphone using microfabrication processes. Microfabrication, being fundamentally a batch-fabrication technique greatly reduces the unit production cost.

1. A semiconductor device comprising a microphone formed in an integrated manner and comprising a sensing electrode formed as part of an acoustic pressure sensing membrane, and a counter electrode in the form of a perforated rigid back-plate membrane, wherein said sensing electrode is connected to the gate of a sensing transistor.

**2**. A semiconductor device as claimed in claim 1 wherein said device is operable in a constant bias mode.

**3**. A semiconductor device as claimed in claim 2 wherein the counter electrode is set to a bias voltage and wherein the potential of the sensing electrode and hence the gate potential of the sensing transistor vary in accordance with the acoustic pressure, and wherein the gate potential is biased in the conducting regime whereby variations in the gate voltage vary the output voltage of the sensing transistor.

**4**. A semiconductor device as claimed in claim 2 wherein the potential of the sensing electrode is fixed and an output current from the sensing electrode or the counter electrode and varying in response to acoustic pressure on the sensing membrane is taken as the output signal.

**5.** A semiconductor device as claimed in claim wherein said device is operable in a constant charge mode by first charging the sensing electrode followed by setting the potential of the counter electrode to ground and biasing the sensing transistor to a conducting state.

**6**. A semiconductor device as claimed in claim 5 wherein the charging of the sensing electrode is by tunneling from a substrate.

7. A semiconductor device as claimed in claim 5 wherein the charging of the sensing electrode is by injection from the sensing transistor.

**8**. A semiconductor device as claimed in claim 1 wherein the sensing membrane is formed of a layer of an insulating material and a layer of a conducting material.

**9**. A semiconductor device as claimed in claim 8 wherein said insulating material comprises low stress silicon nitride, and wherein said conducting material comprises polysilicon.

**10**. A semiconductor device as claimed in claim 1 wherein said counter electrode is formed of a layer of a first conducting material and a layer of a second conducting material.

11. A semiconductor device as claimed in claim 10 wherein said second conducting material is a relatively hard material and is sandwiched between two layers of said first conducting material which is a relatively soft material.

12. A semiconductor device as claimed in claim 11 wherein said first material is aluminium and said second material is titanium.

**13**. A method of forming an integrated semiconductor device including a microphone, comprising the steps of:

- (a) depositing a first layer of an insulating material on a substrate to form a part of an acoustic sensing membrane,

- (b) depositing a layer of conducting material on said layer of insulating material,

- (c) depositing a second layer of an insulating material on said conducting material,

- (d) depositing a sacrificial layer on said second layer of insulating material,

- (e) depositing at least one rigid conducting material on said sacrificial layer to define a rigid counter electrode,

- (f) forming a plurality of holes in said counter electrode,

- (g) etching said substrate from a back side thereof to expose said membrane, and

- (h) removing said sacrificial layer by etching through said holes to leave an airgap between said membrane and said counter electrode.

14. A method as claimed in claim 13 wherein before step (a) said substrate is subject to an isolation technique to separate on said substrate an area for said membrane, an area for a tunneling window, and areas for forming at least one sensing transistor and a substrate contact.

**15**. A method as claimed in claim 13 wherein the conducting layer of said membrane also forms the gate electrode(s) of at least one sensing transistor.

16. A method as claimed in claim 13 wherein said first insulating layer in step (a) is formed of low stress silicon nitride.

17. A method as claimed in claim 13 wherein the conducting layer of said membrane in step (b) is formed of polysilicon.

**18**. A method as claimed in claim 13 wherein the sacrificial layer of step (d) is formed of polysilicon.

**19**. A method as claimed in claim 13 wherein the counter electrode is formed of a hard conducting material sandwiched between two layers of a softer conducting material.

20. A method as claimed in claim 19 wherein said hard conducting material is titanium, and said softer conducting material is aluminium.

**21**. A method of forming a semiconductor device including a membrane, comprising the steps of:

- (a) depositing a membrane forming material on a substrate,

- (b) depositing a sacrificial layer of polysilicon on said membrane forming material,

- (c) constructing a further semiconductor device structure on said substrate and over said sacrificial layer,

- (d) removing said sacrificial layer, and

- (e) etching a back side of said substrate to expose said membrane.

**22**. A method of forming a semiconductor device including a membrane, comprising the steps of:

- (a) depositing a first membrane forming material on a substrate, said first membrane forming material being an insulating material,

- (b) depositing a second membrane forming material on said first membrane forming material, said second membrane forming material being a conducting material and said second membrane forming material extending beyond said first membrane forming material so as to contact said substrate, whereby charges may be injected into said conducting material.

- (c) depositing a sacrificial layer on said second membrane forming material,

- (d) constructing a further semiconductor device structure on said substrate and over said sacrificial layer,

- (e) removing said sacrificial layer, and

- etching a back side of said substrate to expose said membrane.

\* \* \* \* \*