## SCHWEIZERISCHE EIDGENOSSENSCHAFT

BUNDESAMT FÜR GEISTIGES EIGENTUM

(f) CH 653 482

H 01 L

61) Int. Cl.4: H 01 L H 01 L

21/72 27/04 29/78

Erfindungspatent für die Schweiz und Liechtenstein

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

## 12 PATENTSCHRIFT A5

(21) Gesuchsnummer:

3064/80

(73) Inhaber:

N.V. Philips' Gloeilampenfabrieken, Eindhoven

(22) Anmeldungsdatum:

21.04.1980

30 Priorität(en):

23.04.1979 NL 7903158

72 Erfinder:

Jochems, Pieter Johannes Wilhelmus, Eindhoven (NL)

(24) Patent erteilt:

31.12.1985

(74) Vertreter:

Patentanwalts-Bureau Isler AG, Zürich

45 Patentschrift veröffentlicht:

31.12.1985

(54) Verfahren zur Herstellung einer integrierten Schaltung mit einem Feldeffekttransistor und durch ein derartiges Verfahren hergestellte Schaltung.

Beim Verfahren zur vollständig selbstregistrierenden Herstellung einer IGFET-Anordnung, wird auf dem Halbleiterkörper (1) ein schmaler Siliziumnitridstreifen (23) gebildet, der nur das aktive Gebiet des Körpers bedeckt und dessen Breite im wesentlichen gleich der der herzustellenden Transistoren und gegebenenfalls anderer Schaltungselemente ist. Dieser Siliziumnitridstreifen (23) wird als Maske für die Anbringung der kanalunterbrechenden Zone (21) und als Oxidationsmaske für die Anbringung einer ersten Oxidschicht (24) verwendet. Dann wird der Siliziumnitridstreifen (23) geätzt, wobei der Streifen örtlich über seine ganze Breite entfernt wird und nur Teile (26) über den Kanalgebieten (12) und Kontaktgebieten (3, 7, 9) zurückbleiben, die eine zweite Oxidationsmaske und in Zusammenarbeit mit der ersten Oxidschicht (24) eine Dotierungsmaske bilden. Über diese Dotierungsmaske werden die Source- und Drainzonen (4, 5, 6) der Transistoren und etwaige weitere Zonen, wie Unterführungen (8), angebracht, wonach durch Oxidation ein versenktes Oxidmuster (10) über die ganze Oberfläche, mit Ausnahme der Kanalgebiete (12) und der Kontaktgebiete (3, 7, 9), erzeugt wird. Nach der Oxidation kann das verbleibende Nitrid mit einer maskenlosen Ätzbehandlung entfernt werden, wonach auf einfache Weise über den Kanalgebieten das Gate-Dielektrikum mit den Gate-Elektroden und in den Kontaktgebieten die Kontakte - wobei diesem Ver-

fahrensschritt gegebenenfalls die Anbringung von Kontaktzonen vorangeht - angebracht werden können.

## PATENTANSPRÜCHE

1. Verfahren zur vollständig selbstregistrierenden Herstellung einer integrierten Schaltung mit einem Feldeffekttransistor mit isolierter Gate-Elektrode, bei dem ein Siliziumkörper, von dem wenigstens ein an eine Oberfläche grenzendes Teilgebiet vom einen Leitungstyp ist, unter Verwendung einer eine Siliziumnitrid Schicht enthaltenden Maskierungsschicht, die das darunterliegende Material des Halbleiterkörpers gegen Oxidation maskiert, mit einer Anzahl von Oberflächenzonen vom zweiten Leitungstyp versehen wird, aus denen die Source- und die Drainzone des Transistors gebildet werden, wonach dieser Körper mit Hilfe einer Oxidationsbehandlung mit einem wenigstens über einen Teil seiner Dicke in den Siliziumkörper versenkten Oxidmuster versehen wird, das sich über den Oberflächenzonen und über den angrenzenden Teilen des Siliziumkörpers erstreckt und eine Anzahl von Öffnungen aufweist, die mesaförmige Gebiete des Halbleiterkörpers definieren, die das Kanalgebiet des Transistors und Kontaktgebiete der Zonen, die in den mesaförmigen Gebieten neben dem versenkten Oxidmuster an die Oberfläche des Körpers grenzen, bilden, dadurch gekennzeichnet, dass, bevor die Oberflächenzonen gebildet werden, aus der genannten Maskierungsschicht eine erste Maske in Form eines Streifens gebildet wird, der die Oberflächenteile des Halbleiterkörpers, an denen die Oberflächenzonen, die Kontaktgebiete und das Ka- 25 nen Kontaktzonen vom zweiten Leitungstyp über die Öffnunnalgebiet erzeugt werden, bedeckt und die genannten angrenzenden Teile des Halbleiterkörpers freilässt, und dass unter Verwendung dieser ersten Maske als Dotierungsmaske in den angrenzenden Teilen des Halbleiterkörpers eine Dotierung vom einen Leitungstyp angebracht und unter Verwendung derselben Maske als Oxidationsmaske die angrenzenden Teile mit einer ersten Oxidschicht versehen werden, wonach die erste Maske einer selektiven Ätzbehandlung unterworfen wird, wobei sich quer über die ganze Breite des Streifens erstrekkende Teile der ersten Maske an den Stellen der anzubringen- 35 tung mit einem Feldeffekttransistor mit isolierter Gate-Elekden Oberflächenzonen entfernt werden und aus der ersten Maske eine zweite Maske erhalten wird, die das Kanalgebiet des Transistors und die Kontaktgebiete der Zonen bedeckt und die zusammen mit der ersten Siliziumoxidschicht eine dritte Maske bildet, die Fenster über Teilen des Halbleiterkörpers aufweist, an denen die Oberflächenzonen angebracht werden, wonach für diese Oberflächenzonen über die genannten Fenster in die freiliegende Teile des Halbleiterkörpers eine Verunreinigung vom zweiten Leitungstyp eingeführt wird, wonach das versenkte Oxidmuster mit Hilfe einer Oxidations- 45 behandlung erzeugt wird, wobei der Halbleiterkörper örtlich von der zweiten Maske gegen Oxidation maskiert wird, und wobei die in den Halbleiterkörper eingeführten Verunreinigungen vom zweiten und vom ersten Leitungstyp weiter in den Halbleiterkörper eindiffundieren und die genannten Oberflächenzonen vom zweiten Leitungstyp in den angrenzenden Teilen des Halbleiterkörpers kanalunterbrechende Zonen vom gleichen Leitungstyp wie der Halbleiterkörper und mit einer höheren Dotierungskonzentration bilden, wonach die verbleibenden Teile der gegen Oxidation maskieren- 55 den Maskierungsschicht, die die zweite Maske bilden, völlig entfernt werden und in den auf diese Weise freigelegten Offnungen im versenkten Oxidmuster eine isolierte Gate-Elektrode des Feldeffekttransistors und Kontakte für die Oberflächenzonen angebracht werden.

2. Verfahren nach Anspruch 1, dadurch gekennzeichnet, dass weitere Schaltungselemente in dem Halbleiterkörper angebracht werden, für die in dem Halbleiterkörper zugleich mit den Oberflächenzonen, die die Source- und die Drainzone des genannten Feldeffekttransistors bilden, weitere Oberflächen- 65 zonen vom zweiten Leitungstyp erzeugt werden, die leitende Verbindungen zwischen unterschiedlichen Schaltungselementen bilden.

- 3. Verfahren nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass ein Halbleiterkörper aus p-leitendem Silizium verwendet wird, und dass die Oberflächenzonen mit einer n-Typ Verunreinigung dotiert werden, die aus der durch As und 5 Sb gebildeten Gruppe gewählt wird.

- 4. Verfahren nach Anspruch 3, dadurch gekennzeichnet, dass als Verunreinigung As in einer Dosis von mindestens 5.10<sup>14</sup> Atomen/cm<sup>2</sup> verwendet wird.

- 5. Verfahren nach einem der vorstehenden Ansprüche, dadurch gekennzeichnet, dass als erste Siliziumoxidschicht, die auf den genannten angrenzenden Oberflächenteilen des Halbleiterkörpers neben der zweiten Maske liegt und zusammen mit der zweiten Maske die dritte Maske bildet, eine Schicht mit einer Dicke von höchstens 0,5 μm verwendet wird.

- 6. Verfahren nach Anspruch 5, dadurch gekennzeichnet, dass die erste Siliziumoxidschicht nach dem Einführen der Verunreinigungen in den Halbleiterkörper zum Erhalten der Oberflächenzonen vom zweiten Leitungstyp und vor der Anbringung des versenkten Oxidmusters entfernt wird, wodurch 20 das versenkte Oxidmuster eine praktisch gleichmässige Dicke aufweist.

- 7. Verfahren nach einem der Ansprüche 1 bis 6, dadurch gekennzeichnet, dass nach der Anbringung des versenkten Oxidmusters in den Mesas an den Stellen der Oberflächenzogen im versenkten Oxidmuster angebracht werden.

- 8. Integrierte Schaltung mit einem Feldeffekttransistor, die durch ein Verfahren nach einem der Ansprüche 1 bis 7 hergestellt ist.

Die Erfindung bezieht sich auf ein Verfahren zur vollständig selbstregistrierenden Herstellung einer integrierten Schaltrode, bei dem ein Siliziumkörper, von dem wenigstens ein an eine Oberfläche grenzendes Teilgebiet vom einen Leitungstyp ist, unter Verwendung einer eine Siliziumnitridschicht enthaltenden Maskierungsschicht, die das darunterliegende Material des Halbleiterkörpers gegen Oxidation maskiert, mit einer Anzahl von Oberflächenzonen vom zweiten Leitungstyp versehen wird, aus denen die Source- und die Drainzone des Transistors gebildet werden, wonach dieser Körper mittels einer Oxidationsbehandlung mit einem wenigstens über einen Teil seiner Dicke in den Siliziumkörper versenkten Oxidmuster versehen wird, das sich über den Oberflächenzonen und über den angrenzenden Teilen des Siliziumkörpers erstreckt und eine Anzahl von Öffnungen aufweist, die mesaförmige Gebiete des Halbleiterkörpers definieren, die das Kanalgebiet 50 des Transistors und Kontaktgebietes der Zonen, die in den mesaförmigen Gebieten neben dem versenkten Oxidmuster an die Oberfläche des Körpers grenzen, bilden. Die Erfindung bezieht sich weiterhin auf eine durch ein derartiges Verfahren hergestellte Schaltung.

Es ist bei der Herstellung von Feldeffekttransistoren allgemein üblich, die Source- und Drainzonen und die isolierte Gate-Elektrode selbstregistrierend in bezug aufeinander anzubringen. Ein derartiger Vorgang bietet nämlich sehr wichtige Vorteile: Die auf diese Weise erhaltenen Transistoren 60 können klein sein, weil nur geringe Ausrichttoleranzen berücksichtigt zu werden brauchen, während die Hochfrequenzeigenschaften im allgemeinen infolge der geringen parasitären Überlappungskapazitäten zwischen der Gate-Elektrode und den Source- und Drainzonen günstig sind.

Bei einem sehr häufig angewandten MOST-Verfahren werden die Source- und Drainzonen in den Halbleiterkörper unter Verwendung der Gate-Elektrode als Maske eindiffun-

diert. Die Gate-Elektrode besteht dabei gewöhnlich aus polykristallinem Silizium.

Dieses Verfahren weist jedoch den Nachteil auf, dass die Kanallänge des Transistors - d.h. der Abstand zwischen der Source- und Drainzone - völlig durch die Präzision, mit der mit Hilfe der üblichen Photoätztechniken ein Maskenmuster in einer Photolackschicht kopiert werden kann, und durch die Genauigkeit bestimmt wird, mit der anschliessend das Muster in der Photolackschicht in das polykristalline Material geätzt werden kann. Diese Genauigkeit ist oft geringer als erwünscht 10 und Draingebiete verbleiben, wonach, mit diesen Nitridflekwäre. Ausserdem finden diese kritischen Schritte gewöhnlich in einer Stufe statt, in der die Oberfläche des Halbleiterkörpers nicht mehr flach, sondern infolge des bereits angebrachten die aktiven Gebiete umgebenden Feldoxids stark profiliert ist, was ebenfalls eine grosse Beschränkung in bezug auf die in reproduzierbarer Weise erzielbare Kleinstabmessung mit sich bringt. In der US-PS 4 023 195 ist ein Feldeffekttransistor mit isolierter Gate-Elektrode beschrieben, in dem die Oberfläche des Halbleiterkörpers mit einem über einen Teil seiner Dicke in den Halbleiterkörper versenkten Oxidmuster überzogen ist, das Öffnungen aufweist, die in dem Halbleiterkörper eine Anzahl von Mesas definieren, die das Kanalgebiet und Kontaktgebiete der Source- und der Drainzone des Transistors bilden, wobei die Source- und Drainzonen ausgenommen an den Stellen der Mesas völlig unter dem versenkten Oxidmuster liegen. Die Gate-Elektrode darf sich ausserhalb des Kanalgebietes bis oberhalb des Oxidmusters und bis oberhalb der Source- und Drainzonen erstrecken, weil durch die Dicke des versenkten Oxidmusters die parasitären Überlappungskapazitäten zwischen den Source- und Drainzonen einerseits und den auf dem Oxidmuster liegenden Teilen der Gate-Elektrode andererseits verhältnismässig gering sind. Während der Herstellung dieses bekannten Transistors wird das Anbringen der Gate-Elektrode daher keine kritischen Ausrichtschritte erfordern. Dagegen wird die Anbringung des 35 versenkten Oxidmusters nach dem in der genannten Patentschrift beschriebenen Verfahren wohl einen kritischen Ausrichtschritt in bezug auf die bereits im Halbleiterkörper angebrachten Source- und Drainzonen erfordern, weil die Oxidationsmaske und die Diffusionsmaske, für die verschiedene Maskierungsschichten verwendet werden, nicht selbstregistrierend sind. Dadurch müssen bei diesen bekannten Transistoren Ausrichttoleranzen berücksichtigt werden, die eine Beschränkung in bezug auf die in reproduzierbarer Weise erzielbaren Kleinstabmessungen mit sich bringen.

Insbesondere wenn der Transistor vom n-Leitungstyp ist, wobei die Source- und Drainzonen vom n-Typ sind und der Halbleiterkörper vom p-Typ ist, ist es erwünscht, unter dem versenkten Oxidmuster neben dem Transistor eine kanalunschreitenden Dotierungskonzentration anzubringen, um parasitäte Kanalbildung unter dem versenkten Oxid, die z.B. falls der Transistor einen Teil einer integrierten Schaltung bildet, unerwünschte Verbindungen zwischen verschiedenen Schaltungselementen herstellen kann, zu vermeiden. Bei dem in der obengenannten USA-Patentschrift beschriebenen Verfahren wird eine derartige kanalunterbrechende Zone durch Implantation einer geeigneten Verunreinigung unter Verwendung einer gesonderten Photolackschicht als Implantationsder Einfachheit des Verfahrens als auch im Zusammenhang mit der Gedrängtheit der herzustellenden Halbleiteranordnung wünschenswert, die kanalunterbrechende Zone ebenfalls auf selbstregistrierende Weise in bezug auf die anderen zu bildenden Zonen anzubringen.

Ein Verfahren, bei dem das versenkte Oxidmuster und die Source- und Drainzonen teilweise, und zwar von der Sourcezu der Drainzone hin, selbstregistrierend angebracht werden,

dadurch, dass die gegen Oxidation maskierende Nitridschicht auch als Dotierungsmaske verwendet wird, ist in der US-PS 4 043 848 beschrieben. Dabei werden in der Nitritschicht zunächst Fenster angebracht, über die in dem Halbleiterkörper 5 dotierte Zonen angebracht werden, um die Source- und Drainzonen des Transistors zu erhalten. Nach diesem Dotierungsschritt wird die Nitridschicht durch Ätzen derart weit entfernt, dass nur noch Nitridflecke über dem Kanalgebiet des Transistors und über den Kontaktgebieten der Sourceken als Oxidationsmaske, mit Hilfe thermischer Oxidation das versenkte Oxidmuster angebracht wird.

Die Nitridmaske über dem Kanalgebiet ist daher nicht völlig selbstregistrierend in bezug auf die bereits definierten 15 Source- und Drainzonen des Transistors, und zwar nicht selbstregistrierend in der Richtung quer zu der Stromrichtung. Oft und insbesondere bei sehr kleinen Abmessungen und grossen Packungsdichten wäre eine vollständige Selbstregistrierung erwünscht. Ausserdem wird bei diesem bekannten 20 Verfahren keine kanalunterbrechende Zone verwendet. Eine derartige kanalunterbrechende Zone ist oft erwünscht und wird dann vorzugsweise auch selbstregistrierend in bezug auf die anderen anzubringenden Teile der herzustellenden Anordnungen angebracht.

Ein ähnliches Verfahren, bei dem jedoch wohl eine kanalunterbrechende Zone unter dem versenkten Oxidmuster angebracht wird, ist in der offengelegten niederländischen Patentanmeldung 7 704 636 beschrieben. In der Nitridschicht werden bei diesem bekannten Verfahren zunächst Diffusions-30 fenster für die Source- und Drainzonen gebildet; dann wird nach der Diffusionsbehandlung eine Maske mit einer die Diffusionsfenster umgebenden Öffnung für die kanalunterbrechende Zone angebracht. Dieses Verfahren ist ebenfalls nicht selbstregistrierend.

Die Aufgabe der Erfindung bestand daher u.a. darin, ein Verfahren der eingangs beschriebenen Art anzugeben, das praktisch völlig selbstregistrierend ist und mit dem deshalb auf reproduzierbare Weise Halbleiterstrukturen sehr kleiner Abmessungen und grosser Dichte erhalten werden können.

Nach der Erfindung wird diese Aufgabe bei einem derartigen Verfahren dadurch gelöst, dass bevor die Oberflächenzonen gebildet werden, aus der genannten Maskierungsschicht eine erste Maske in Form eines Streifens gebildet wird, der die Oberflächenteile des Halbleiterkörpers, an denen die Oberflä-45 chenzonen, die Kontaktgebiete und das Kanalgebiet erzeugt werden, bedeckt und die genannten angrenzenden Teile des Halbleiterkörpers frei lässt, und dass unter Verwendung dieser ersten Maske als Dotierungsmaske in den angrenzenden Teilen des Halbleiterkörpers eine Dotierung vom einen Leiterbrechende p-Zone mit einer die des Halbleiterkörpers über- 50 tungstyp angebracht und unter Verwendung derselben Maske als Oxidationsmaske auf den angrenzenden Teilen eine erste Oxidschicht erzeugt wird, wonach die erste Maske einer selektiven Ätzbehandlung unterworfen wird, wobei sich quer über die ganze Breite des Streifens erstreckende Teile der ersten Maske an den Stellen der anzubringenden Oberflächenzonen entfernt werden und aus der ersten Maske eine zweite Maske erhalten wird, die das Kanalgebiet des Transistors und die

Kontaktgebiete der Zonen bedeckt und die zusammen mit der ersten Siliziumoxidschicht eine dritte Maske bildet, die Fenmaske erhalten. Oft ist es aber sowohl im Zusammenhang mit 60 ster über Teilen des Halbleiterkörpers aufweist, an denen die Oberflächenzonen angebracht werden, wonach für diese Oberflächenzonen über die genannten Fenster in die freiliegenden Teile des Halbleiterkörpers eine Verunreinigung vom zweiten Leitungstyp eingeführt wird, wonach das versenkte

65 Oxidmuster mittels einer Oxidationsbehandlung erzeugt wird, wobei der Halbleiterkörper örtlich gegen Oxidation durch die zweite Maske maskiert wird, und wobei Oxidation durch die zweite Maske maskiert wird, und wobei die in den

Halbleiterkörper eingeführten Verunreinigungen vom zweiten und vom ersten Leitungstyp weiter in den Halbleiterkörper eindiffundieren und die genannten Oberflächenzonen vom zweiten Leitungstyp in den angrenzenden Teilen des Halbleiterkörpers kanalunterbrechende Zonen vom gleichen Leitungstyp wie der Halbleiterkörper und mit einer höheren Dotierungskonzentration bilden, wonach die verbleibenden Teile der gegen Oxidation maskierenden Maskierungsschicht, die die zweite Maske bilden, völlig entfernt werden und in den so gebildeten Öffnungen im versenkten Oxidmuster eine isolierte Gate-Elektrode des Feldeffekttransistors und Kontakte für die Oberflächenzonen angebracht werden.

Bei diesem Verfahren wird daher die Siliziumnitridschicht zunächst als Maske für die kanalunterbrechende Zone, dann als Maske für die Source- und Drainzonen des Transistors und schliesslich als Oxidationsmaske verwendet. Dabei wird die Maske für die kanalunterbrechende Zone in Form eines Streifens angebracht, dessen Breite zugleich die Breite des Transistors definiert. Diese Maske wird als Dotierungsmaske für die kanalunterbrechende Zone und als Oxidationsmaske für die Bildung der Oxidschicht neben oder rings um die Maske verwendet.

Diese Oxidschicht kann mittels einer leichten thermischen Oxidationsbehandlung erhalten werden. In einer nächsten Stufe werden in dem Streifen der Siliziumnitridschicht Offnungen vorgesehen, die die Source- und Drainzonen mit zwischen ihnen dem noch von der Siliziumnitridschicht bedeckten Kanalgebiet definieren. Für die Bildung dieser Öffnungen (Diffusions- oder Implantationsfenster) ist kein kritischer Ausrichtschritt erforderlich, weil sich diese Öffnungen über die ganze Breite des Streifens erstrecken dürfen und seitlich von der genannten Oxidschicht begrenzt werden. Nach dem Dotierungsschritt wird das versenkte Oxidmuster unter Verwendung derselben Maske aus der Siliziumnitridschicht angeselbstregistrierend ohne kritische Ausrichtschritte. Der Vorgang ist dadurch besonders einfach und gestattet kleine Abmessungen für die unterschiedlichen Elemente und im Falle einer integrierten Schaltung eine hohe Packungsdichte.

Eine besondere Ausführungsform des Verfahrens nach der Erfindung ist dadurch gekennzeichnet, dass weitere Schaltungselemente im Halbleiterkörper angebracht werden, für die in dem Halbleiterkörper zugleich mit den Oberflächenzonen, die die Source- und Drainzone des genannten Feldeffekttransistors bilden, weitere Oberflächenzonen vom zweiten Leitungstyp im Halbleiterkörper angebracht werden, die leitende Verbindung zwischen verschiedenen Schaltungselemen-

Diese Ausführungsform ist von besonderer Bedeutung bei die Schaltungselemente miteinander durch Verbindungsmuster auf verschiedenen Pegeln verbunden werden. Bei dem vorliegenden Verfahren erfordert die Anbringung des unteren Pegels in Form eines Musters von Zonen vom zweiten Leitungstyp keine zusätzlichen Verfahrensschritte und erfolgt ausserdem auf selbstregistrierende Weise. Dadurch, dass weiter dieses Verbindungsmuster völlig unter dem - verhältnismässig dichten - versenkten Oxidmuster vergraben ist, können ohne Bedenken auf dem versenkten Oxidmuster weitere leitende Verbindungen, die die Zonen unter dem versenkten Oxidmuster kreuzen, angebracht werden, weil infolge der verhältnismässig grossen Dicke des Oxids die parasitären Kapazitäten verhältnismässig klein sind.

Zur Durchführung des Verfahrens nach der Erfindung kann von einem n-leitenden Körper ausgegangen werden, in dem die Source- und die Drainzone als p-leitende Zonen angebracht werden. Eine bevorzugte Ausführungsform ist dadurch gekennzeichnet, dass ein Halbleiterkörper aus p-leiten-

dem Silizium verwendet wird, und dass die Oberflächenzonen mit einer n-Typ Verunreinigung dotiert werden, die aus der durch As und Sb gebildeten Gruppe gewählt wird. Der Gebrauch dieser Verunreinigungen ergibt den Vorteil, dass in-5 folge der verhältnismässig niedrigen Diffusionsgeschwindigkeit im Vergleich zu z.B. Phosphor oder Bor untiefe Zonen und dadurch geringe parasitäre Überlappungskapazitäten zwischen diesen Zonen und der isolierten Gate-Elektrode er-

Nach dem Anbringen des versenkten Oxidmusters kann 10 die gegen Oxidation maskierende Siliziumnitridschicht mittels einer maskenlosen Ätzbehandlung entfernt werden, wonach über dem Kanalgebiet eine dünne Oxidschicht als Gate-Dielektrikum gebildet werden kann. Die Kontakt-Mesas wer-15 den, wie aus der Figurbeschreibung hervorgehen wird, mittels einer einfachen Ätzbehandlung mit Hilfe einer nichtkritischen Maske freigelegt. Die Öffnungen in dieser Maske dürfen grösser als die Kontakt-Mesas sein, weil durch den selbstregistrierenden Effekt doch Kontaktöffnungen erhalten werden, die 20 gleich gross wie die Kontakt-Mesas sind, was insbesondere bei sehr kleinen Abmessungen sehr vorteilhaft ist. Dann können Kontakte gebildet werden.

Eine Ausführungsform der Erfindung ist in der Zeichnung dargestellt und wird im folgenden näher beschrieben. Es

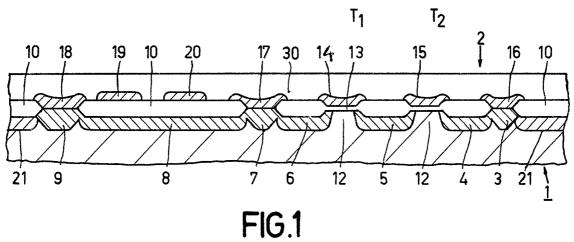

Fig. 1 einen Schnitt durch einen Teil einer Halbleiteranordnung mit einem durch das Verfahren nach der Erfindung hergestellten Transistor,

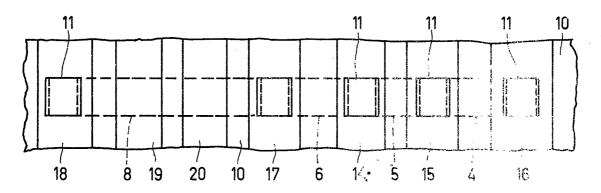

Fig. 2 eine Draufsicht auf die Anordnung nach Fig. 1, und Figuren 3 bis 11 die Anordnung nach den Figuren 1 und 2 in Draufsicht und im Querschnitt während einer Anzahl Stufen in deren Herstellung.

Obwohl die Erfindung auch mit Vorteil zur Herstellung diskreter Feldeffekttransistoren angewandt werden kann, bracht. Dieser ganze Vorgang ist daher praktisch vollständig 35 wird im nachstehenden Ausführungsbeispiel die Herstellung einer integrierten Schaltung mit mehreren derartigen Transistoren beschrieben. Da es insbesondere in komplexen integrierten Schaltungen erwünscht ist, eine möglichst grosse Anzahl von Schaltungselementen pro Volumeneinheit oder 40 Oberflächeneinheit des Halbleiterkörpers unterbringen zu können, bietet die Erfindung, mit deren Hilfe Schaltungselemente völlig oder wenigstens praktisch völlig selbstregistrierend hergestellt werden können, gerade für derartige komplexe integrierte Schaltungen besondere Vorteile. Nur zur Il-45 lustrierung der Erfindung ist eine Anordnung in den Figuren 1 und 2 dargestellt, die beispielsweise nur zwei Feldeffekttransistoren mit isolierten Gate-Elektroden, eine sogenannte diffundierte Unterführungs und eine Anzahl die Unterführung kreuzender Leiterbahnen enthält. In praktischen Ausführunder Herstellung komplexer integrierter Schaltungen, in denen 50 gen wird naturgemäss die Anzahl von Elementen viel grösser sein, aber zur Illustrierung der Prinzipien der Erfindung reicht das hier dargestellte Ausführungsbeispiel aus.

Die Anordnung enthält einen Halbleiterkörper 1 aus Silizium, der im hier zu beschreibenden Ausführungsbeispiel im 55 wesentlichen völlig von einem ersten Leitungstyp ist, aber der naturgemäss auch eine andere Konfiguration aufweisen kann, wobei nur ein einziges Oberflächengebiet, in dem die dargestellten Elemente angebracht werden, vom ersten Leitungstyp ist und innerhalb des Halbleiterkörpers von Teilen 60 vom zweiten entgegengesetzten Leitungstyp begrenzt wird. Für die anzubringenden Schaltungselemente wird der Körper 1 an der Oberfläche 2 mit einer Anzahl von Oberflächenzonen 3 bis 9 vom zweiten Leitungstyp, die Source- und Drainzonen der Feldeffekttransistoren T<sub>1</sub> und T<sub>2</sub>, eine diffundierte Unter-65 führung und Kontaktzonen bilden, und mit einem Muster 10 aus Siliziumoxid versehen, das über einen Teil seiner Dicke in den Körper 1 versenkt ist. Das Muster 10 – für dessen Anbringung dieselbe Maskierungsschicht wie für die Anbrin-

gung der Zonen 4, 5, 6 und 8 verweneet wird, wie aus Nachstehendem noch hervorgehen wird - erstreckt sich über den Oberflächenzonen 4, 5, 6 und 8 und über angrenzenden nichtwirksamen Gebieten des Halbleiterkörpers. Aus diesem Grunde sind diese Zonen in der Draufsicht nach Fig. 2 mit gestrichelten Linien angegeben.

Wie sich aus Fig. 2 erkennen lässt, erstreckt sich das versenkte Oxidmuster 10 über praktisch die ganze Oberfläche und weist nur eine Anzahl verhältnismässig kleiner Öffnungen 11 auf, die mesaförmige Gebiete (nachstehend auch als Mesas bezeichnet) definieren (siehe Fig. 1). An den Stellen dieser Mesas (die die Kanalgebiete der Transistoren T<sub>1</sub> und T<sub>2</sub> und Kontaktgebiete 3, 7 und 9 definieren) kommen die n-leitenden Zonen 4, 6 und 8 von unterhalb des versenkten Oxidche 2 des Halbleiterkörpers. Über den Mesas, die die Kanalgebiete der Transistoren T1, T2 bilden, ist eine dünne Siliziumoxidschicht 13 als Gate-Dielektrikum angebracht. Auf der Schicht 13 befinden sich die Gate-Elektroden 14, 15 der Transistoren. Die Zonen der Transistoren und diese Gate-Elektro- 20 Temperatur von etwa 1100 °C Wasserdampf geführt wird, den sind durch das Muster 10 voneinander getrennt. Infolge der verhältnismässig grossen Dicke des Musters 10 ist die Streukapazität zwischen den Gates 14, 15 und den darunterliegenden Zonen verhältnismässig gering, so dass die Anbringung der Gates keinen genauen Ausrichtschritt erfordert.

Beispielsweise enthalten die Transistoren als Hauptelektrodengebiet eine gemeinsame praktisch völlig unter dem Muster 10 liegende Zone 5. Die anderen Hauptelektrodengebiete der Transistoren, die durch die Zonen 4 und 6 gebildet werden, sind über die in den Kontakt-Mesas angebrachten n-leitenden Kontaktzonen 3 bzw. 7 mit den Kontakten oder Leiterstreifen 16 bzw. 17 verbunden. Der Kontakt 17 bildet zugleich einen Anschluss der diffundierten Unterführung 8. die auf der anderen Seite über die Zone 9 vom zweiten Leimuster 10 sind noch zwei Leiterbahnen 19 und 20 dargestellt, die die Unterführung 8 kreuzen und durch die verhältnismässig dicke Oxidschicht 10 von ihr getrennt sind. Die Kontakte und Leiterbahnen 14 bis 20 können mit weiteren in den Figu-

Wie sich weiter aus Fig. 1 erkennen lässt, befindet sich in dem Halbleiterkörper 1 unter dem versenkten Oxidmuster 10 und ausserhalb des aktiven Gebietes der Schaltung (d.h. das Gebiet, in dem Schaltungselemente und diffundierte Verbindungen liegen) eine Zone 21, die denselben Leitungstyp wie, aber eine höhere Dotierungskonzentration als der Halbleiterkörper 1 aufweist. Bekanntlich kann mittels einer derartigen höher dotierten Zone die Bildung parasitärer Kanäle unter dem versenkten Oxidmuster 10, die durch unerwünschte Verbindungen zwischen den Schaltungselementen hergestellt werden können, vermieden werden.

Im vorliegenden Ausführungsbeispiel wird die Herstellung einer Halbleiteranordnung mit Feldeffekttransistoren vom n-Kanaltyp beschrieben; naturgemäss sind jedoch die Prinzipien des Herstellungsverfahrens auch auf Anordnungen vom p-Kanaltyp anwendbar. Wegen mehrerer nachstehend noch zu erwähnender Vorteile sind jedoch Anordnungen vom n-Kanaltyp den Anordnungen vom p-Kanaltyp vorzuziehen.

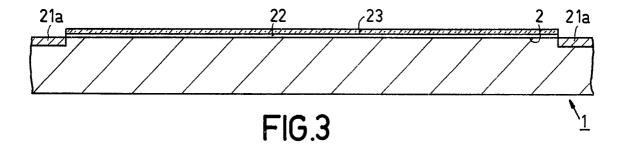

Für die Herstellung der in den Figuren 1 und 2 gezeigten Anordnung wird von einem Halbleiterkörper 1 aus p-leitendem Silizium mit einem üblichen spezifischen Widerstand von etwa 6 bis 8 Ω. cm und einer Dicke von etwa 300 bis 400 μm ausgegangen (Fig. 3).

Mittels thermischer Oxidation wird die Oberfläche 2 mit einer verhältnismässig dünnen Schicht 22 aus Siliziumoxid mit einer Dicke von etwa 50 nm überzogen. Dadurch, dass über den Halbleiterkörper 1 ein Gemisch von NH3 und SiCl3

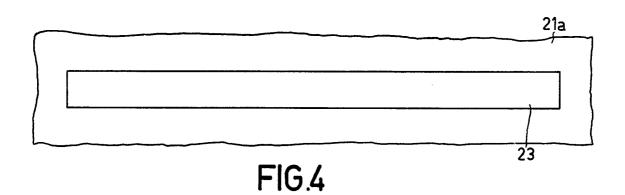

bei einer Temperatur von etwa 800 °C geführt wird, wird auf der Siliziumoxidschicht 21 eine Schicht aus Siliziumnitrid mit einer Dicke von etwa 150 nm abgelagert. Aus dieser Schicht wird durch photolithographisches Ätzen eine erste Maske in 5 Form eines Streifens 23 gebildet. Dieser Streifen, der im hier gezeigten Beispiel ganz gerade ist, aber naturgemäss auch eine andere Konfiguration mit z.B. einer Krümmung aufweisen kann, bedeckt nur denjenigen Teil des Körpers 1, in dem die Schaltungselemente, wie die Transistoren T<sub>1</sub>, T<sub>2</sub>, Kontaktzo-10 nen und die Unterführung 8 in einem späteren Herstellungsschritt angebracht werden.

Dabei ist es wichtig, noch zu bemerken, dass die Abmessungen der herzustellenden Schaltungselemente T<sub>1</sub> und T<sub>2</sub>, der Kontaktzonen und der Unterführung 8 in einer Richtung musters 10 zum Vorschein und erstrecken sich zu der Oberflä- 15 bereits in dieser Stufe des Verfahrens definiert sind, und zwar durch die Breite des Streifens 23, wie aus dem Nachstehenden noch hervorgehen wird.

> Die Maske 23 kann auf an sich bekannte Weise z.B. dadurch erhalten werden, dass über die Nitridschicht bei einer wodurch auf dem Nitrid eine dünne Siliziumoxidschicht gebildet wird. Auf dieser Oxidschicht kann eine Atzmaske, die aus einer Photolackschicht besteht, angebracht werden, mit deren Hilfe dann durch Plasmaätzen aus der Nitridschicht der 25 Streifen 23 gebildet wird. Anschliessend kann die Photolackschicht wieder entfernt werden.

Unter Verwendung des Siliziumnitridstreifens 23 als Ätzmaske wird dann die Oxidschicht 22 einer Ätzbehandlung unterworfen, wodurch die die aktiven Gebiete umgebenden Oberflächenteile des Halbleiterkörpers rings um den Streifen 23 frei zu liegen kommen (Figuren 3, 4). In diesen frei liegenden Teilen wird dann durch Diffusion oder Implantation von Boratomen die Zone 21a erzeugt, aus der nach dem Erzeugen des versenkten Oxidmusters 10 die kanalunterbrechende tungstyp mit dem Anschluss 18 verbunden ist. Auf dem Oxid- 35 Zone 21 gebildet werden wird. Die Zonen 21, 21a sind genau in bezug auf die aktiven Gebiete des Halbleiterkörpers ausgerichtet, die von dem (den) Streifen 23 definiert sind.

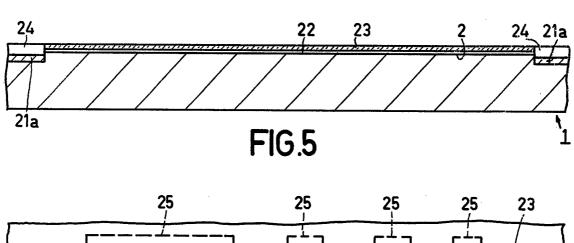

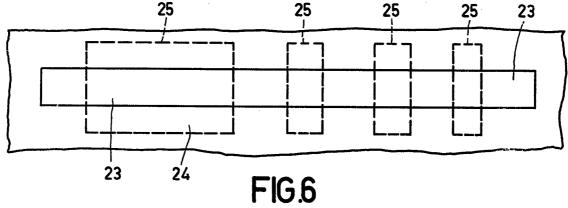

Während der Erzeugung der Zonen 21a kann auf der Oberfläche 2 des Halbleiterkörpers 1 eine borhaltige Glasren nicht mehr dargestellten Schaltungselementen verbunden 40 schicht gebildet werden. Diese Schicht kann wieder mit Hilfe einer maskenlosen Ätzbehandlung entfernt werden, wonach der Halbleiterkörper einer Oxidationsbehandlung während etwa 35 Minuten bei einer Temperatur von etwa 1000 °C unterworfen wird, wobei der Halbleiterkörper von dem Nitrid-45 streifen 23 gegen Oxidation maskiert wird. Durch diese Oxidationsbehandlung werden die frei liegenden Oberflächenteile des Halbleiterkörpers rings um den Nitridstreifen 23 wieder mit einer Schicht 24 aus Siliziumoxid mit einer Dicke von etwa 0,3 µm abgeschlossen (siehe Fig. 5). Die Anordnung 50 wird danach mit einer Photolackschicht abgedeckt, in der auf bekannte Weise Fenster angebracht werden, über die die Siliziumnitridschicht einer maskierten Ätzbehandlung unterworfen werden kann. Das Anbringen dieser Fenster 25 (in der Draufsicht nach Fig. 6 mit gestrichelten Linien angegeben) er-55 fordert keinen kritischen Ausrichtschritt, trotz der sehr geringen Breite des Nitridstreifens 23, weil die Fenster 25, wie aus Fig. 6 ersichtlich ist, zu beiden Seiten des Nitridstreifens 23 aus dem Nitridstreifen über die Oxidschicht 24 hinausragen dürfen.

> Die in den Fenstern 25 freigelegten Teile des Nitridstreifens 23 werden anschliessend z.B. durch Plasmaätzen entfernt. Diese Ätzbehandlung kann selektiv erfolgen, so dass das ebenfalls in den Fenstern 25 freiliegende Siliziumoxid der Schicht 24 nicht oder wenigstens in viel geringerem Masse als 65 das Siliziumnitrid angegriffen wird.

Nach dem Ätzen des Nitrids kann die Photomaske entfernt werden. Die freiliegenden Teile der dünnen Siliziumoxidschicht 22, die vor dem Nitrid auf der Oberfläche 2 ange-

wachsen war, können mittels einer maskenlosen Ätzbehandlung entfernt werden. Dabei wird zwar ein Teil der Oxidschicht 24 gleichfalls entfernt, aber dies wird nicht bedenklich sein, weil die Schicht 24 viele Male dicker als die Schicht 22 ist und die maskierenden Eigenschaften der Schicht 24 nicht oder nahezu nicht durch eine geringe Herabsetzung der Dicke beeinträchtigt zu werden brauchen.

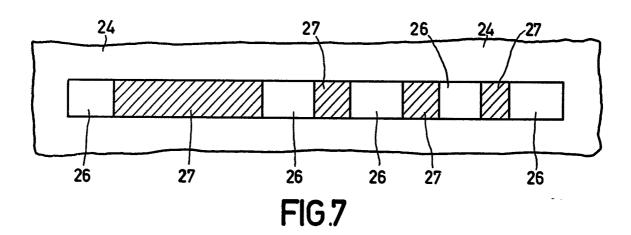

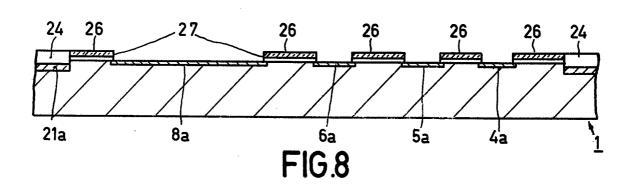

Aus der Siliziumnitridschicht ist nun eine zweite Maske gebildet, die, wie in der Draufsicht nach Fig. 7 dargestellt ist, eine Anzahl von Flecken 26 enthält. Die zweite Nitridmaske 26 bildet zusammen mit der Siliziumoxidschicht 24 eine dritte Maske, die den grössten Teil der Oberfläche bedeckt und Öffnungen 27 aufweist, die in der Draufsicht nach Fig. 7 schraffiert dargestellt sind. Es sei bemerkt, dass mit Hilfe derselben Photolackschichtmaske zugleich zwei Masken erhalten sind, und zwar eine Dotierungsmaske 24, 26 und eine Oxidationsmaske 26.

Über die Fenster 27 wird eine Verunreinigung, im vorliegenden Falle Arsen, in den Halbleiterkörper mit einer Dosis von etwa 10<sup>15</sup>/cm<sup>2</sup> z.B. durch Ionenimplantation eingeführt, wodurch die n-leitenden Zonen 4a, 5a, 6a und 8a erhalten werden. Ein Schnitt durch die Anordnung in dieser Stufe des Verfahrens ist in Fig. 8 dargestellt.

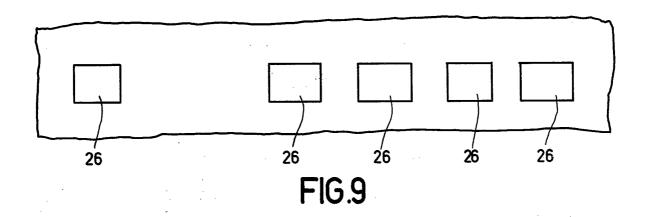

Bevor das versenkte Oxidmuster 10 erzeugt wird, wird in einem folgenden Schritt die genannten erste Oxidschicht 24 durch eine selektive maskenlose Ätzbehandlung entfernt, wobei das Siliziumnitrid nicht oder nahezu nicht angegriffen wird. Dieser Schritt ist nicht notwendig, aber wird vorzugsweise wohl durchgeführt, um ein versenktes Oxidmuster 10 mit einer möglichst gleichmässigen Dicke zu erhalten. Nach dieser Ätzbehandlung ist auf der Oberfläche 2 nur noch die Oxidationsmaske vorhanden, die durch die Siliziumnitridflecke 26 gebildet wird, wie in der Draufsicht nach Fig. 9 dargestellt ist. Der Halbleiterkörper wird dann während etwa 30 Minuten bei einer Temperatur von etwa 750 °C einer Nachheizbehandlung unterworfen, um die während der Ionenimplantation entstandenen Beschädigungen in der Kristallstruktur des Siliziums zu beseitigen.

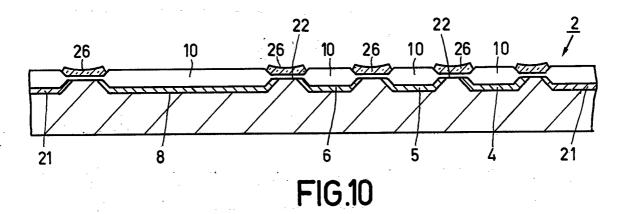

Das Oxidmuster 10 kann durch Oxidation der nicht von dem Nitrid 26 maskierten Oberflächenteile erzeugt werden. Die Oxidation wird in einem sauerstoffhaltigen Milieu bei einer Temperatur von etwa 1100 °C durchgeführt, bis die Dicke des Oxids etwa 2 µm beträgt. Während dieser Oxidation diffundiert die As-Verunreinigung tiefer in den Halbleiterkörper hinein und bildet, wie im Schnitt in Fig. 10 dargestellt ist, unter dem versenkten Oxidmuster 10 die n-leitenden Zonen 4 bis 6 und 8. Die Dicke der Zonen ist unter den gegebenen Bedingungen zwischen etwa 0,5 und 1 µm gelegen. Dabei sei bemerkt, dass die Diffusionskonstante von As in einkristallinem Silizium verhältnismässig niedrig ist. Überraschenderweise wurde aber gefunden, dass bei einer passenden Wahl der Dotierungsstoffkonzentration und/oder der Temperatur die Diffusion von As-Atomen in den Halbleiterkörper doch soviel schneller als die Oxidation vor sich geht, dass n-leitende Zonen erhalten werden können, die einen genügend niedrigen spezifischen Widerstand aufweisen und sich seitlich entlang der Ränder des Oxidmusters bis zu der Oberfläche der Mesas 12 erstrecken. Messungen haben ergeben, dass der Quadratwiderstand der Zonen 4 bis 6 und 8 etwa 74  $\Omega$  beträgt, was für viele Anwendungen genügend niedrig ist. Die Tiefe der Zonen 60 benenfalls über das Ganze noch eine Glasschicht 30 als Passi-4-6, 8 beträgt, vom Rande des versenkten Oxidmusters 10 her, etwa 0,5 bis 1 μm. Die geringe Tiefe, die im Vergleich zu z.B. Zonen, die weiter unter gleichen Bedingungen mit P oder mit p-typ Verunreinigungen, wie B, dotiert sind, sehr klein ist, weist wichtige Vorteile auf, wie u.a. geringe Streukapazitäten 65 zwischen den isolierten Gate-Elektroden und den Zonen. Ausserdem können dadurch zusätzlich kleine und kompakte Strukturen erhalten werden.

Während der Oxidation diffundieren die in den Zonen 21a angebrachten B-Atome auch tiefer in den Halbleiterkörper 1 hinein und bilden unter dem Oxidmuster die kanalunterbrechenden Zonen 21.

Nach der Oxidationsbehandlung werden die noch verbleibenden Teile 26 der Siliziumnitridschicht mittels einer selektiven Atzbehandlung entfernt.

Die nun freiliegenden Teile der Siliziumoxidschicht 22 können an den Stellen der noch anzubringenden Gate-Elek-10 troden als eine Gate-Isolierung benutzt werden. Vorzugsweise wird jedoch die Oxidschicht 22 mit Hilfe einer maskenlosen Atzbehandlung entfernt. Dabei wird auch eine dünne Schicht des Oxidmusters 10 entfernt werden, aber dies braucht nicht bedenklich zu sein, weil diese entfernte Schicht sehr viel dün-15 ner als das Muster 10 sein wird.

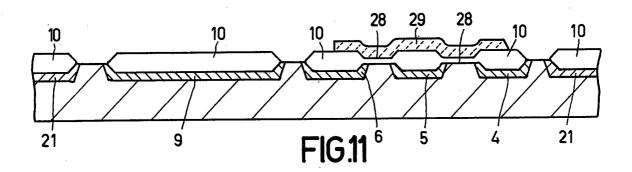

Dann wird durch thermische Oxidation in den Mesas das

Gate-Dielektrikum in Form einer neuen Oxidschicht 28 angebracht (siehe Schnitt Fig. 11), die eine Dicke von z.B. etwa 80 nm aufweist. An den Stellen der Kontaktmesas wird diese 20 Oxidschicht wieder mittels einer sogenannten Tauchätzbehandlung entfernt, wobei zugleich wieder eine dünne Schicht örtlich von dem versenkten Oxidmuster 10 entfernt werden kann, ohne dass die Eigenschaften dieses Musters beeinträchtigt werden. Die Mesas an den Stellen der Kanalgebiete der 25 Transistoren werden während dieser Ätzbehandlung von einer Photolackschicht 29 maskiert. Die Anbringung der Maske 29, die sich bis oberhalb des versenkten Oxidmusters erstrecken darf, erfordert keinen kritischen Ausrichtschritt. Nachdem die Schicht 28 örtlich weggeätzt worden ist, können 30 durch Ablagerung und anschliessende Ätzung eines geeigneten Leitermaterials die isolierten Gate-Elektroden 14, 15 und die Kontakte 16, 18 über den Mesas 12 angeordnet werden. Zugleich können auch die die Unterführung 8 kreuzenden Leiter 19 und 20 gebildet werden. Als Leitermaterial kann 35 z.B. dotiertes polykristallines Silizium verwendet werden, das bekanntlich ein Material ist, das allgemein bei der Herstellung von Feldeffekttransistoren mit isolierten Gate-Elektroden angewendet wird. Die vorher angebrachten Kontaktzonen 3, 7, 9, können dann gegebenenfalls weggelassen werden. 40 Die n-leitenden Bahnen 14, 16, 17 können dann ohmsche Kontakte mit den n-leitenden Zonen 4, 6 und 8 und einen pn-Übergang mit dem p-leitenden Substrat bilden, dass in den Mesas 12 auch an die Oberfläche 2 grenzt. Auch kann das polykristalline Silizium bei der Ablagerung eigenleitend (undotiert) sein und nachher zur Herabsetzung des Widerstandes ndotiert werden, wobei an den Stellen der Kontakte die Verunreinigung über das polykristalline Material in den Halbleiterkörper eindiffundiert. In einer anderen Ausführungsform kann, weil bei dem Verfahren nach der Erfindung die Gate-50 Elektroden 14, 15 nicht als Dotierungsmaske für die Anbringung der Source- und Drainzonen der Transistoren verwendet werden, statt polykristallinen Siliziums auch mit Vorteil ein Metall mit einem niedrigeren spezifischen Widerstand als polykristallines Silizium, z.B. A1, gewählt werden. In diesem 55 Fall müssen vor der Anbringung des Aluminiums die n-leitenden Kontaktzonen 3, 7, 9 durch Dotierung der Kontaktmesas mit einer n-Typ Verunreinigung, wie Phosphor, angebracht werden.

Die Anordnung ist dann grundsätzlich fertig, wobei gegevierungsschicht angebracht werden kann. Das hier beschriebene Verfahren ist einfach und weist, weil es völlig oder wenigstens praktisch völlig selbstregistrierend ist, grosse Vorteile auf. Insbesondere können die Abmessungen der Elemente klein und kann ihre Packungsdichte sehr gross sein. Für die Breite des Nitridstreifens 23 kann der Mindestwert, der mit Hilfe bekannter photolithographischer Techniken erreicht werden kann, gewählt werden. Ein Wert für diese Breite be-

trägt z.B. 5 µm, was bei einem 2 µm dicken Oxidmuster eine Breite von 3 µm der Kanalgebiete der Transistoren und der diffundierten Zonen 4–6, 8 ergibt.

Ein weiterer wichtiger Aspekt des hier beschriebenen Verfahrens besteht darin, dass zugleich mit den Source- und

Drainzonen der Transistoren auch diffundierte Unterführungen 8 gebildet werden können, wodurch eine vollständige Verbindungsschicht erhalten wird. Die Streukapazitäten zwischen der Unterführung 8 und den Leiterbahnen 19, 20 sind 5 dabei infolge des dicken Oxidmusters 10 sehr niedrig.

C 3 Blatt Zeichnungen

FIG.2