(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5649378号

(P5649378)

(45) 発行日 平成27年1月7日(2015.1.7)

(24) 登録日 平成26年11月21日(2014.11.21)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 618B |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 618Z |

| HO1L 21/316 | (2006.01) | HO1L 29/78 | 617L |

| HO1L 21/318 | (2006.01) | HO1L 29/78 | 617M |

| C23C 14/08  | (2006.01) | HO1L 29/78 | 619A |

請求項の数 3 (全 34 頁) 最終頁に続く

(21) 出願番号 特願2010-196444 (P2010-196444)

(22) 出願日 平成22年9月2日 (2010.9.2)

(65) 公開番号 特開2011-77510 (P2011-77510A)

(43) 公開日 平成23年4月14日 (2011.4.14)

審査請求日 平成25年8月29日 (2013.8.29)

(31) 優先権主張番号 特願2009-204801 (P2009-204801)

(32) 優先日 平成21年9月4日 (2009.9.4)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 佐々木 俊成

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 坂田 淳一郎

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 津吹 将志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタと第2のトランジスタと、を有し、

前記第1のトランジスタは、

第1のゲート電極層と、

前記第1のゲート電極層上の第1の絶縁層と、

前記第1の絶縁層上の第1の酸化物半導体層と、

前記第1の酸化物半導体層上の第2の絶縁層と、

前記第2の絶縁層上の第1のソース電極層及び第1のドレイン電極層と、を有し、

前記第2のトランジスタは、

第2のゲート電極層と、

前記第2のゲート電極層上の前記第1の絶縁層と、

前記第1の絶縁層上の第2の酸化物半導体層と、

前記第2の酸化物半導体層上の前記第2の絶縁層と、

前記第2の絶縁層上の第2のソース電極層及び第2のドレイン電極層と、を有し、

前記第1のゲート電極層と前記第2のゲート電極層とは、同一面上に設けられ、

前記第1のソース電極層及び前記第1のドレイン電極層上、並びに前記第2のソース電極層及び前記第2のドレイン電極層上の第3の絶縁層を有し、

前記第3の絶縁層上に、前記第1のソース電極層又は前記第1のドレイン電極層と電気的に接続される第1の電極を有し、

10

20

前記第1の電極上に接するE L層を有し、

前記第3の絶縁層上に、前記第2のゲート電極層と重なる領域を有する導電層を有し、

前記第2の絶縁層は、前記第1の酸化物半導体層の周縁を覆う第1の領域と、前記第1の酸化物半導体層上面と接する第2の領域と、前記第2の酸化物半導体層の周縁を覆う第3の領域と、前記第2の酸化物半導体層上面と接する第4の領域と、を有し、

前記第1のソース電極層又は前記第1のドレイン電極層は、前記第2の絶縁層の前記第1の領域と前記第2の領域との間において、前記第1の酸化物半導体層と電気的に接続され、

前記第2のソース電極層又は前記第2のドレイン電極層は、前記第2の絶縁層の前記第3の領域と前記第4の領域との間において、前記第2の酸化物半導体層と電気的に接続されることを特徴とする表示装置。 10

【請求項2】

第1のトランジスタと第2のトランジスタと容量と、を有し、

前記第1のトランジスタは、

第1のゲート電極層と、

前記第1のゲート電極層上の第1の絶縁層と、

前記第1の絶縁層上の第1の酸化物半導体層と、

前記第1の酸化物半導体層上の第2の絶縁層と、

前記第2の絶縁層上の第1のソース電極層及び第1のドレイン電極層と、を有し、

前記第2のトランジスタは、 20

第2のゲート電極層と、

前記第2のゲート電極層上の前記第1の絶縁層と、

前記第1の絶縁層上の第2の酸化物半導体層と、

前記第2の酸化物半導体層上の前記第2の絶縁層と、

前記第2の絶縁層上の第2のソース電極層及び第2のドレイン電極層と、を有し、

前記容量は、第1の導電膜と、第2の導電膜と、前記第1の導電膜と前記第2の導電膜とに挟まれた前記第1の絶縁層とを有し、

前記第1のゲート電極層と前記第2のゲート電極層と前記第1の導電膜とは、同一面上に設けられ、

前記第2の導電膜上、前記第1のソース電極層及び前記第1のドレイン電極層上、並びに前記第2のソース電極層及び前記第2のドレイン電極層上の第3の絶縁層を有し、

前記第3の絶縁層上に、前記第1のソース電極層又は前記第1のドレイン電極層と電気的に接続される第1の電極を有し、

前記第1の電極上に接するE L層を有し、

前記第3の絶縁層上に、前記第2のゲート電極層と重なる領域を有する導電層を有し、

前記第2の絶縁層は、前記第1の酸化物半導体層の周縁を覆う第1の領域と、前記第1の酸化物半導体層上面と接する第2の領域と、前記第2の酸化物半導体層の周縁を覆う第3の領域と、前記第2の酸化物半導体層上面と接する第4の領域と、を有し、

前記第1のソース電極層又は前記第1のドレイン電極層は、前記第2の絶縁層の前記第1の領域と前記第2の領域との間において、前記第1の酸化物半導体層と電気的に接続され、 40

前記第2のソース電極層又は前記第2のドレイン電極層は、前記第2の絶縁層の前記第3の領域と前記第4の領域との間において、前記第2の酸化物半導体層と電気的に接続され、

前記第1の電極は、前記容量と重なる領域を有することを特徴とする表示装置。

【請求項3】

請求項1または請求項2において、

前記第1及び前記第2の酸化物半導体層は、インジウムを含むことを特徴とする表示装置。

【発明の詳細な説明】

**【技術分野】****【0001】**

酸化物半導体を用いる表示装置に関する。

**【背景技術】****【0002】**

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数～数百nm程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。金属酸化物は多様に存在しそうな用途に用いられている。酸化インジウムはよく知られた材料であり、液晶ディスプレイなどで必要とされる透光性電極材料として用いられている。10

**【0003】**

金属酸化物の中には半導体特性を示すものがある。半導体特性を示す金属酸化物としては、例えば、酸化タンゲステン、酸化スズ、酸化インジウム、酸化亜鉛などがあり、このような半導体特性を示す金属酸化物をチャネル形成領域とする薄膜トランジスタが既に知られている（特許文献1及び特許文献2）。

**【0004】**

また、非晶質酸化物半導体を用いた薄膜トランジスタは、非晶質としては比較的電界効果移動度が高い。そのため、当該薄膜トランジスタを用いて、表示装置などの駆動回路を構成することもできる。20

**【先行技術文献】****【特許文献】****【0005】**

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

表示装置等において、画素部（画素回路とも言う）と駆動回路部を同一基板上に形成する場合、画素部に用いるトランジスタには、優れたスイッチング特性、例えばオンオフ比が大きいことが要求され、駆動回路部に用いるトランジスタには高速動作が要求される。30

**【0007】**

特に、表示装置の画素密度が高い程、表示画像の書き込み時間を短くするため、駆動回路部に用いるトランジスタは高速で動作することが好ましい。

**【0008】**

本明細書で開示する本発明の一態様は、上記課題を解決するトランジスタ及び該トランジスタを含む表示装置に関する。

**【課題を解決するための手段】****【0009】**

本明細書で開示する本発明の一態様は、ソース領域及びドレイン領域に酸化物導電層を含み、且つ半導体層が酸化物半導体によって構成されたトランジスタである。また、当該トランジスタを含んで構成される駆動回路部及び表示部（画素部とも言う）を同一基板上に形成した表示装置である。40

**【0010】**

本明細書で開示する本発明の一態様は、ゲート電極層と、ゲート電極層上にゲート絶縁層と、ゲート絶縁層上に酸化物半導体層と、ゲート絶縁層上に前記酸化物半導体層の一部と重なる酸化物導電層と、酸化物導電層上にソース電極層及びドレイン電極層と、酸化物半導体層と接する酸化物絶縁層と、を有し、酸化物導電層は結晶領域を有することを特徴とするトランジスタである。

**【0011】**

10

20

30

40

50

また、本明細書で開示する本発明の他の一態様は、ゲート電極層と、ゲート電極層上にゲート絶縁層と、ゲート絶縁層上にソース電極層及びドレイン電極層と、ソース電極層及びドレイン電極層上に酸化物導電層と、ゲート絶縁層上に前記酸化物導電層の一部と重なる酸化物半導体層と、酸化物半導体層と接する酸化物絶縁層と、を有し、酸化物導電層は結晶領域を有することを特徴とするトランジスタである。

【0012】

上記構成において、トランジスタのソース電極層及びドレイン電極層は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた金属元素を主成分とする膜、またはそれらの合金膜を用いることができる。また、ソース電極層及びドレイン電極層は、上述した元素を含む単層に限定されず、異なる膜の積層を用いることができる。

10

【0013】

トランジスタのソース電極層及びドレイン電極層と酸化物半導体層のそれぞれの間に、酸化物導電層を形成することで接触抵抗を低減することができ、高速動作が可能なトランジスタを実現できる。該酸化物導電層には、酸化インジウム、酸化インジウム酸化スズ合金、酸化インジウム酸化亜鉛合金、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、または酸化亜鉛ガリウム等の結晶領域を有したもの用いることができる。

【0014】

また、上記構成において、酸化物絶縁層は、トランジスタのチャネル保護層として機能する。該酸化物絶縁層には、スパッタ法で形成される酸化珪素、窒化酸化珪素、酸化アルミニウム、または酸化窒化アルミニウムなどを用いることができる。

20

【0015】

また、本発明の一態様であるトランジスタを用いて、駆動回路部及び表示部（画素部ともいう）を同一基板上に形成し、EL素子、液晶素子または電気泳動素子などを用いて表示装置を作製することができる。

【0016】

本明細書で開示する本発明の他の一態様は、同一基板上にトランジスタを有する画素部と駆動回路部を有し、トランジスタは、基板上にゲート電極層と、ゲート電極層上にゲート絶縁層と、ゲート絶縁層上に酸化物半導体層と、ゲート絶縁層上に前記酸化物半導体層の一部と重なる酸化物導電層と、酸化物導電層上にソース電極層及びドレイン電極層と、酸化物半導体層と接する酸化物絶縁層と、を有し、酸化物導電層は、結晶領域を有することを特徴とする表示装置である。

30

【0017】

また、本明細書で開示する本発明の他の一態様は、同一基板上にトランジスタを有する画素部と駆動回路部を有し、トランジスタは、基板上にゲート電極層と、ゲート電極層上にゲート絶縁層と、ゲート絶縁層上にソース電極層及びドレイン電極層と、ソース電極層及びドレイン電極層上に酸化物導電層と、ゲート絶縁層上に前記酸化物導電層の一部と重なる酸化物半導体層と、酸化物半導体層と接する酸化物絶縁層と、を有し、酸化物導電層は、結晶領域を有することを特徴とする表示装置である。

【0018】

本発明の一態様である表示装置においては、画素部に複数のトランジスタを有し、画素部においてもあるトランジスタのゲート電極と他のトランジスタのソース配線或いはドレイン配線を接続させる箇所を有している。また、本発明の一態様である表示装置の駆動回路部においては、トランジスタのゲート電極とそのトランジスタのソース配線或いはドレイン配線を接続させる箇所を有している。

40

【0019】

また、トランジスタは静電気などにより破壊されやすいため、ゲート線またはソース線に対して、画素部のトランジスタを保護するための保護回路を同一基板上に設けることが好ましい。保護回路は、酸化物半導体層を用いた非線形素子を用いて構成することが好ましい。

【発明の効果】

50

## 【0020】

ソース電極層及びドレイン電極層と酸化物半導体層のそれぞれの間に結晶領域を有する酸化物導電層を用いることにより、電気特性が良好で信頼性の高いトランジスタを作製することができる。

## 【図面の簡単な説明】

## 【0021】

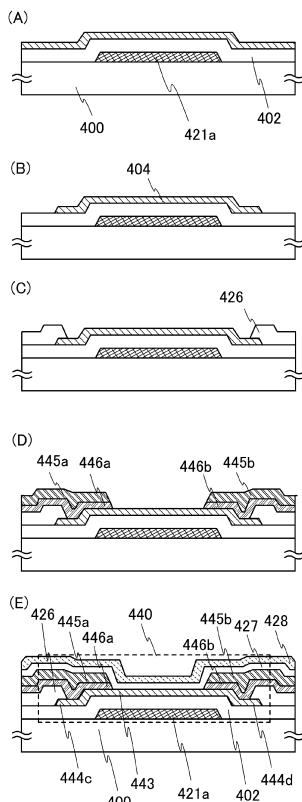

【図1】本発明の一態様におけるトランジスタの断面工程図。

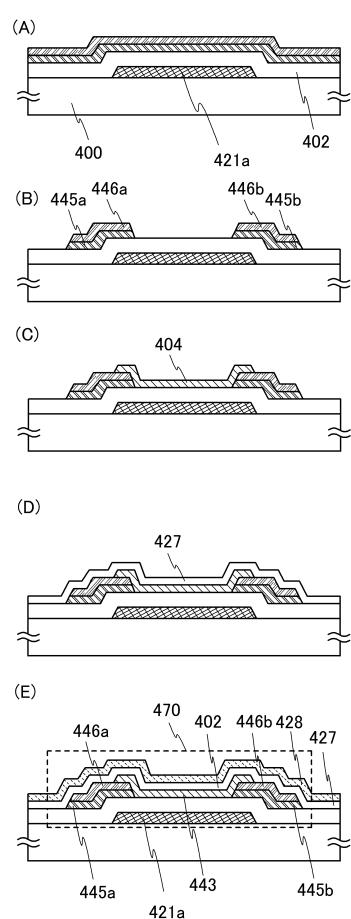

【図2】本発明の一態様におけるトランジスタの断面工程図。

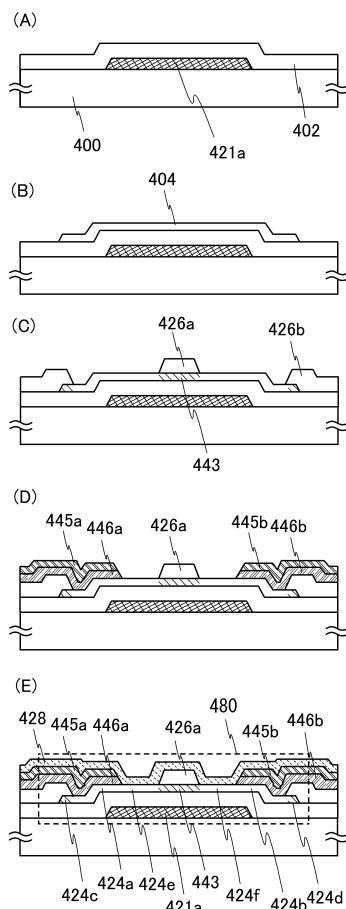

【図3】本発明の一態様におけるトランジスタの断面工程図。

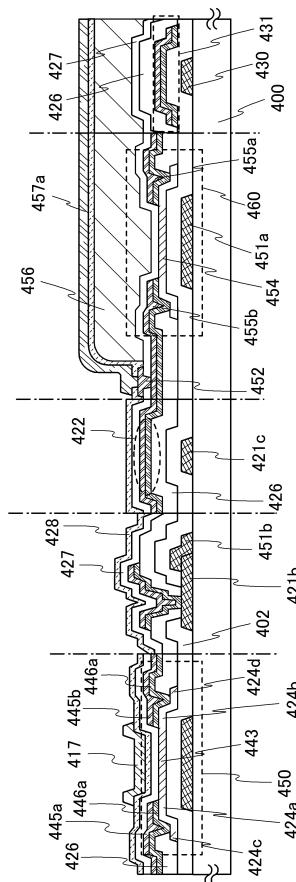

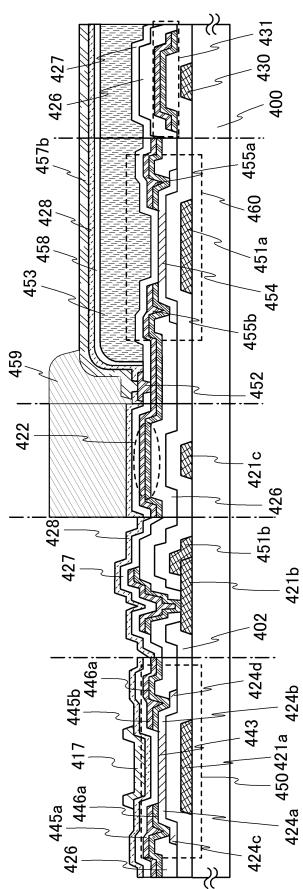

【図4】本発明の一態様における表示装置の断面図。

10

【図5】本発明の一態様における表示装置の断面図。

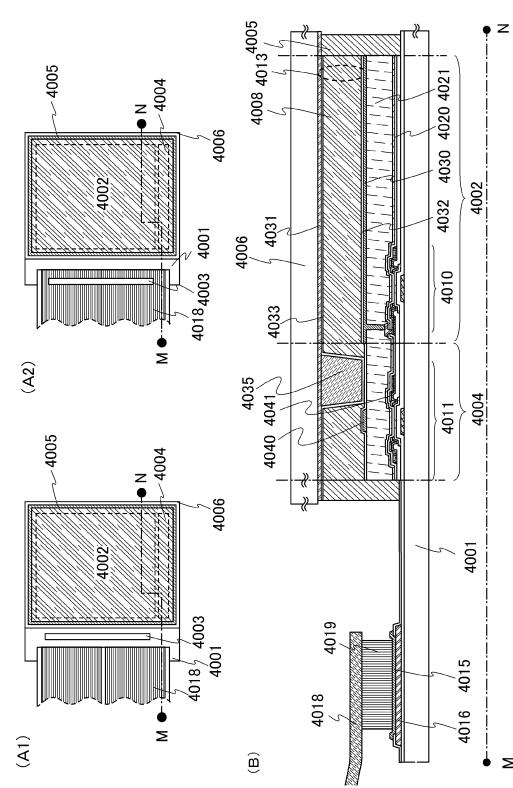

【図6】表示装置を説明する平面図及び断面図。

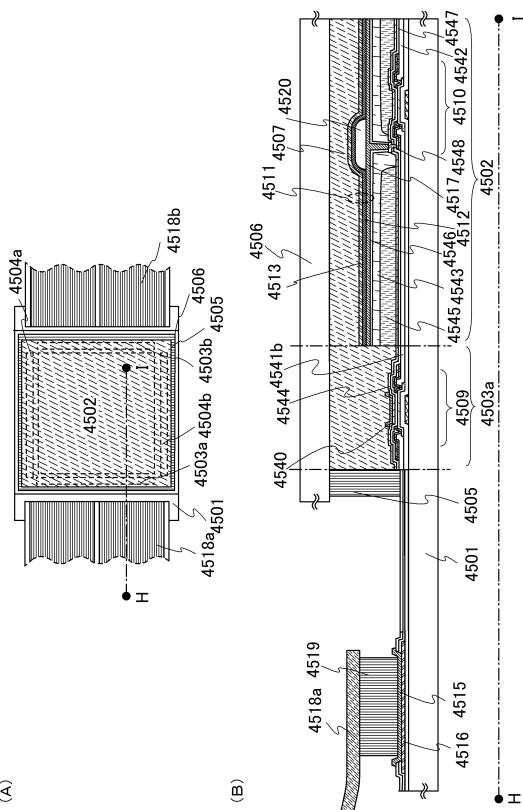

【図7】表示装置を説明する平面図及び断面図。

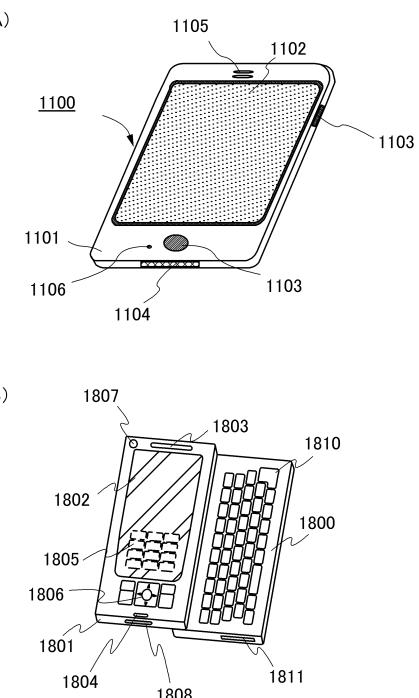

【図8】電子機器を示す図。

【図9】電子機器を示す図。

【図10】電子機器を示す図。

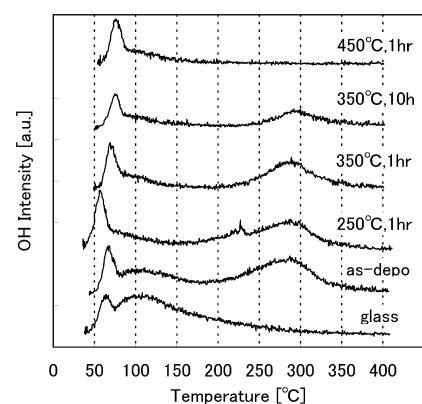

【図11】水分のTDSスペクトル。

【図12】HのTDSスペクトル。

【図13】OのTDSスペクトル。

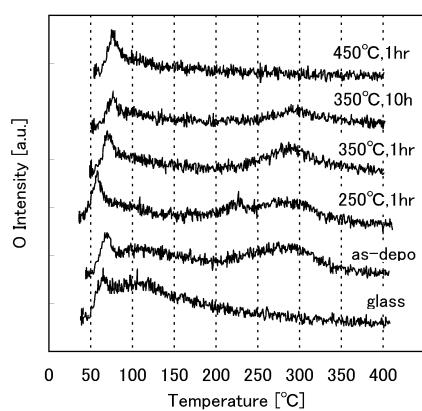

【図14】OHのTDSスペクトル。

20

## 【発明を実施するための形態】

## 【0022】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、本明細書中の図面において、同一部分または同様な機能を有する部分には同一の符号を付し、その説明は省略する場合がある。

## 【0023】

## (実施の形態1)

本実施の形態では、薄膜トランジスタ及びその作製方法の一形態を説明する。

30

## 【0024】

図1(E)にチャネルエッチ型と呼ばれるボトムゲート構造の薄膜トランジスタ440の断面図を示す。

## 【0025】

薄膜トランジスタ440は、絶縁表面を有する基板400上に、ゲート電極層421a、ゲート絶縁層402、チャネル形成領域443を有する酸化物半導体層、ソース電極層445a、及びドレイン電極層445bを有する。また、チャネル形成領域443、酸化物導電層446a、446b、ソース電極層445a、及びドレイン電極層445b上には絶縁層427及び保護絶縁層428が設けられる。

## 【0026】

40

また、酸化物絶縁層426と重なる酸化物半導体層の第1領域444c、第2領域444dを設け、チャネル形成領域443と同じ酸素過剰な状態とし、リーク電流の低減や、寄生容量を低減する機能を持たせても良い。

## 【0027】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

## 【0028】

ここで、酸化物導電層446a、446bは、結晶領域を有する導電率の高い材料からなると共に、酸化物半導体層とソース電極層445a及びドレイン電極層445bとの間の

50

接触抵抗を低減することができ、高速動作が可能な薄膜トランジスタを実現できる。

【0029】

以下、図1(A)、(B)、(C)、(D)、(E)を用い、薄膜トランジスタ440を作製する工程を説明する。

【0030】

まず、絶縁表面を有する基板400上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層421aを形成する。

【0031】

なお、フォトリソグラフィ工程に用いるレジストマスクはインクジェット法で形成してもよい。インクジェット法では、フォトマスクを使用しないため、製造コストを低減することができる。

10

【0032】

ゲート電極層421aを形成する導電膜としては、Al、Cr、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金、上述した元素を組み合わせた積層膜等が挙げられる。また、金属酸化物等を用いても良い。

【0033】

基板400としては、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス基板を用いることができる。また、後の加熱処理の温度が高い場合には、歪み点が730以上のものを用いると良い。

20

【0034】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いても良い。

【0035】

また、図示はしないが、下地膜となる絶縁層を基板400とゲート電極層421aの間に設けてもよい。下地膜は、基板400からの不純物元素の拡散を防止する機能があり、窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、または酸化窒化珪素膜から選ばれた膜の単層構造、または上記複数の膜の積層構造により形成することができる。

【0036】

次いで、ゲート電極層421a上にゲート絶縁層402を形成する。

30

【0037】

ゲート絶縁層402には、酸化珪素層、窒化珪素層、酸化窒化珪素層または窒化酸化珪素層等の透光性を有する絶縁膜を用いることができ、プラズマCVD法やスパッタ法等を用いて形成する。また、ゲート絶縁層402は、上記絶縁膜の単層に限らず、異なる膜の積層でも良い。例えば、成膜ガスとして、シラン(SiH<sub>4</sub>)、酸素及び窒素を用いてプラズマCVD法により酸化窒化珪素膜を形成することができる。ゲート絶縁層402の膜厚は、100nm以上500nm以下とし、積層の場合は、例えば、膜厚50nm以上200nm以下の第1のゲート絶縁層を形成し、第1のゲート絶縁層上に膜厚5nm以上300nm以下の第2のゲート絶縁層を形成する。

【0038】

本実施の形態では、ゲート絶縁層402にプラズマCVD法で形成した膜厚100nmの酸化窒化珪素層(SiON(組成比N<O))を用いる。

40

【0039】

次いで、ゲート絶縁層402上に、膜厚5nm以上200nm以下、好ましくは10nm以上20nm以下の酸化物半導体膜をスパッタ法で形成する(図1(A)参照)。酸化物半導体膜の形成後に脱水化または脱水素化のための加熱処理を行っても酸化物半導体膜を非晶質の状態にするため、膜厚を50nm以下と薄くすることが好ましい。酸化物半導体膜の膜厚を薄くすることで酸化物半導体層の形成後に加熱処理した場合に、結晶化してしまうのを抑制することができる。

【0040】

酸化物半導体膜としては、四元系金属酸化物であるIn-Sn-Ga-Zn-O系や、三

50

元系金属酸化物である In - Ga - Zn - O 系、In - Sn - Zn - O 系、In - Al - Zn - O 系、Sn - Ga - Zn - O 系、Al - Ga - Zn - O 系、Sn - Al - Zn - O 系や、二元系金属酸化物である In - Zn - O 系、Sn - Zn - O 系、Al - Zn - O 系、Zn - Mg - O 系、Sn - Mg - O 系、In - Mg - O 系や、In - O 系、Sn - O 系、Zn - O 系などの酸化物半導体膜を用いることができる。また、上記酸化物半導体膜に  $\text{SiO}_2$  を含んでもよい。

#### 【0041】

また、酸化物半導体膜は、 $\text{InMO}_3(\text{ZnO})_m$  ( $m > 0$ ) で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。 $\text{InMO}_3(\text{ZnO})_m$  ( $m > 0$ ) で表記される構造の酸化物半導体膜のうち、MとしてGaを含む構造の酸化物半導体を、上記した In - Ga - Zn - O 系酸化物半導体とよび、その薄膜を In - Ga - Zn - O 系膜ともよぶこととする。

10

#### 【0042】

本実施の形態では、酸化物半導体膜として、In - Ga - Zn - O 系酸化物半導体成膜用ターゲットを用いてスパッタ法により膜厚 15 nm の In - Ga - Zn - O 系膜を成膜する。

#### 【0043】

In - Ga - Zn - O 系膜は、In - Ga - Zn - O 系酸化物半導体ターゲット (In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol 数比] (すなわち、In : Ga : Zn = 1 : 1 : 0.5 [atom 比])) を用い、基板とターゲットの間との距離を 100 mm、圧力 0.6 Pa、直流 (DC) 電力 0.5 kW、酸素 (酸素流量比率 100%) 雰囲気下で成膜することができる。また、他にも、In : Ga : Zn = 1 : 1 : 1 [atom 比] や、In : Ga : Zn = 1 : 1 : 2 [atom 比] の組成比を有するターゲットを用いてもよい。これらのターゲットの充填率は 90% 以上 100% 以下、好ましくは 95% 以上 99.9% 以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

20

#### 【0044】

スパッタ法にはスパッタ用電源に高周波電源を用いる RF スパッタ法、直流電源を用いる DC スパッタ法、さらにパルス的にバイアスを与えるパルス DC スパッタ法がある。RF スパッタ法は主に絶縁層を成膜する場合に用いられ、DC スパッタ法は主に金属膜を成膜する場合に用いられる。

30

#### 【0045】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料を積層成膜することや、同一チャンバーで複数種類の材料を同時に放電させて成膜することができる。

#### 【0046】

また、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に基板にも電圧をかけるバイアススパッタ法などもある。

40

#### 【0047】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層 402 の表面に付着しているゴミを除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に RF 電源を用いて電圧を印加し、イオン化したアルゴンを基板に衝突させて表面を改質する方法である。なお、アルゴンに代えて窒素、ヘリウム、酸素などを用いてもよい。

#### 【0048】

また、酸化物半導体膜の成膜前に、不活性ガス雰囲気 (窒素、ヘリウム、ネオン、またはアルゴン等) 下において加熱処理 (400 以上基板の歪み点未満) を行い、ゲート絶縁

50

層 4 0 2 内に含まれる水素及び水などの不純物を除去してもよい。

【 0 0 4 9 】

次いで、酸化物半導体膜を第 2 のフォトリソグラフィ工程により島状の酸化物半導体層 4 0 4 に加工する(図 1 (B) 参照)。また、島状の酸化物半導体層 4 0 4 を形成するためのレジストマスクは、インクジェット法で形成してもよい。インクジェット法を用いることで、製造コストを低減することができる。

【 0 0 5 0 】

次いで、酸化物半導体層 4 0 4 の脱水化または脱水素化を行う。この脱水化または脱水素化を行う第 1 の加熱処理は、電気炉等を用い、窒素、または希ガス(ヘリウム、ネオン、アルゴン)等の不活性気体雰囲気下で、400 以上基板の歪点未満、好ましくは 425

10

以上で行う。なお、425 以上であれば熱処理時間は 1 時間以下でよいが、425 以下であれば加熱処理時間は、1 時間よりも長時間行うこととする。その他の加熱方法としては、高温の不活性ガスや光を用いて 650 、3 分間程度の RTA (Rapid Thermal Anneal) 処理を行っても良い。RTA 法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

【 0 0 5 1 】

なお、本明細書では、窒素、または希ガス等の不活性気体雰囲気下での加熱処理を脱水化または脱水素化のための加熱処理と呼ぶ。本明細書では、H<sub>2</sub> の脱離のみを脱水素化と呼んでいるわけではなく、H、OHなどの脱離も含めて脱水化または脱水素化と適宜呼ぶこととする。

20

【 0 0 5 2 】

脱水化または脱水素化を行った酸化物半導体層は大気に触れさせることなく、水または水素を再び混入させないことが重要である。脱水化または脱水素化を行い、i 型の酸化物半導体層を n 型化(n<sup>-</sup>、n<sup>+</sup>など)、即ち低抵抗化させた後、再び i 型として高抵抗化させた酸化物半導体層を用いたトランジスタは、そのしきい値電圧値が正であり、所謂ノーマリーオフ特性を示す。表示装置に用いるトランジスタは、ゲート電圧が 0 V にできるだけ近い正のしきい値電圧でチャネルが形成されることが好ましい。アクティブマトリクス型の表示装置においては、回路を構成するトランジスタの電気特性が重要であり、この電気特性が表示装置の性能を左右する。特に、トランジスタのしきい値電圧は重要である。トランジスタのしきい値電圧値が負であると、ゲート電圧が 0 V でもソース電極とドレイン電極の間に電流が流れる、所謂ノーマリーオン特性となり、該トランジスタで構成した回路を制御することが困難となる。また、しきい値電圧値が正であっても、その絶対値が高いトランジスタの場合には、駆動電圧が足りずにスイッチング動作そのものができないことがある。n チャネル型のトランジスタの場合は、ゲート電圧に正の電圧を印加してはじめてチャネルが形成されて、ドレイン電流が流れ出すトランジスタであることが望ましい。駆動電圧を高くしないとチャネルが形成されないトランジスタや、負の電圧状態でもチャネルが形成されてドレイン電流が流れるトランジスタは、回路に用いるトランジスタとしては不向きである。

30

【 0 0 5 3 】

脱水化または脱水素化を行った温度から降温させる際の雰囲気は、昇温時または加熱処理時の雰囲気と異なる雰囲気に切り替えてよい。例えば、脱水化または脱水素化を行った同じ炉で大気に触れさせることなく、炉の中を高純度の酸素ガス、N<sub>2</sub>O ガス、または超乾燥エア(露点が -40 以下、好ましくは -60 以下)で満たして冷却を行うことができる。

40

【 0 0 5 4 】

なお、第 1 の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水や水素などが含まれないことが好ましい。ここで、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度は、6 N (99.9999%) 以上、好ましくは 7 N (99.99999%) 以上とすることが好ましい。

50

## 【0055】

上記、不活性気体雰囲気下での加熱処理を行った場合、i型であった酸化物半導体層は加熱処理により酸素欠乏型となってn型化（n-化など）、即ち低抵抗化する。その後、酸化物半導体層に接する酸化物絶縁層の形成を行うことにより酸化物半導体層を酸素過剰な状態とすることで高抵抗化、即ちi型化させているとも言える。これにより、電気特性が良好で信頼性のよい薄膜トランジスタを作製することができる。

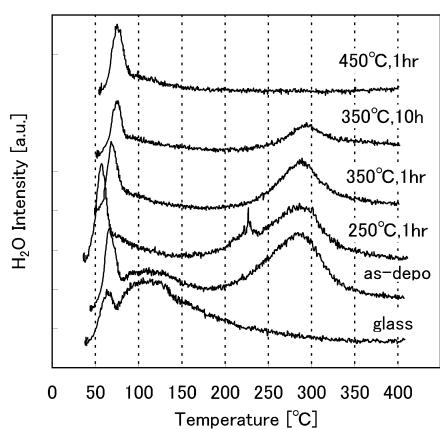

## 【0056】

上記条件で脱水化または脱水素化を十分に行つた酸化物半導体層は、昇温脱離ガス分析法（TDS: Thermal Desorption Spectroscopy）で450まで昇温しても水分の脱離を示すスペクトルに2つのピーク、少なくとも250～300付近に現れる1つのピークは検出されない。

10

## 【0057】

窒素雰囲気下での加熱処理温度の条件を振った複数の試料について、昇温脱離ガス分析法を用いて脱離する水分を分析した結果を図11に示す。

## 【0058】

昇温脱離ガス分析法は、試料を高真空中で加熱・昇温中に試料から脱離、発生するガス成分を四重極質量分析計で検出し、同定する方法であり、試料表面、内部から脱離するガス及び分子が観察できる。電子科学株式会社製の昇温脱離分析装置（製品名：EMD-WA1000S）を用い、測定条件は、昇温約10／分とし、 $1 \times 10^{-8}$ （Pa）から測定を開始して、測定中は約 $1 \times 10^{-7}$ （Pa）の真空度とした。

20

## 【0059】

図11は、ガラス基板上の膜厚50nmのIn-Ga-Zn-O系膜を準備し、非加熱（as-depo）、250 1時間、350 1時間、350 10時間、450 1時間でそれぞれ処理した試料とガラス基板単体（非加熱）の試料を作製し、水分についてのTDS測定結果を比較したグラフである。図11の結果から、窒素雰囲気での加熱温度が高ければ高いほど、In-Ga-Zn-O系膜中から脱離する水分が低減され、450の加熱試料では、水分の脱離を示すスペクトルにおいては、200～350の間にピークは観察されていないことがわかる。

## 【0060】

In-Ga-Zn-O系膜中から200以上の高温で脱離する水分を示すスペクトルのピークは2つあり、200～250の間に現れる第1のピークと、250～350の間に現れる第2のピークが観測される。200～250の間に現れる第1のピークは、250で加熱処理をした試料以外は明瞭でないが、as-depoの試料では2つのピークが重なり、見かけ上1つのピークを持つスペクトルとなっているためである。また、350で加熱処理をしたサンプルでは、水分がある程度放出されており、第1のピークは、ほとんど消失しているためである。これらは、各スペクトルのピーク位置からの対称性及びピーク位置の高温側へのシフトからも確認できる。

30

## 【0061】

また、図11のグラフの縦軸は任意単位であり、脱離ガスの有無を相対的に見たものである。このスペクトルの形状は、被測定物の面積や体積にかかわらず加熱処理に対して同様の変化を示すことから、プロセスマニターとしてのその場観察や不良解析の手段としても有効に用いることができる。すなわち、200～350の温度範囲におけるピークの有無を調べることで、適切なプロセスが施されたか否かの履歴の確認を行うことができる。

40

## 【0062】

なお、窒素雰囲気中で450の加熱処理を行つた試料は、その後、室温で大気中に1週間程度放置しても200以上で脱離する水分は観測されず、加熱処理によって、In-Ga-Zn-O系膜が安定化することが判明している。

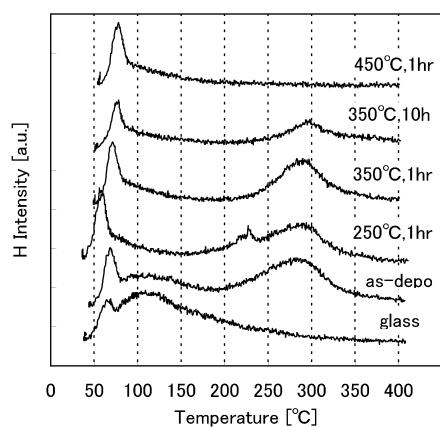

## 【0063】

また、水分の脱離を測定した試料と同条件で加熱工程を経た試料を用い、昇温脱離ガス分析法により、H<sub>2</sub>Oの他にH、O、OH、H<sub>2</sub>、O<sub>2</sub>、N、N<sub>2</sub>、及びArのそれぞれに

50

ついて測定を行ったところ、H、O、及びOHについては、それぞれの脱離を示すスペクトルが観測できた。図12にHのTDSスペクトル、図13はOのTDSスペクトル、図14にはOHのTDSスペクトルを示す。それぞれのスペクトルにガラス基板単体（非加熱）の測定結果を加えて比較している。なお、上記加熱条件における窒素雰囲気中の酸素濃度は、20 ppm以下である。

#### 【0064】

H、O、及びOHの脱離を示すスペクトルは、水分の脱離を示すスペクトルとほぼ同様の傾向を示しており、450の加熱試料においては、250～300付近に現れる各脱離成分を示すピークは観察されていないことがわかる。

#### 【0065】

以上の結果より、In-Ga-Zn-O系膜の加熱処理を行うことにより、水分、H、O及びOHが放出されることがわかる。H、O及びOHの脱離の様子は、水分の脱離の様子と同様の傾向を示していることから、そのほとんどは水分子に由来したものであると言える。

10

#### 【0066】

ここで、本実施の形態では加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下において加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層を得る。また、酸化物半導体層の脱水化または脱水素化を行う加熱温度Tから、再び水が入らないような十分な温度まで同じ炉を用い、具体的には加熱温度Tよりも100以下がるまで窒素雰囲気下で徐冷する。また、窒素雰囲気に限定されず、ヘリウム、ネオン、アルゴン等の希ガス雰囲気下において脱水化または脱水素化を行う。

20

#### 【0067】

また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層の一部が結晶化することがある。第1の加熱処理後は、酸素欠乏型となって低抵抗化した酸化物半導体層404となる（図1（B）参照）。第1の加熱処理後は、成膜直後の酸化物半導体膜よりもキャリア濃度が高まり、好ましくは $1 \times 10^{18} / \text{cm}^3$ 以上のキャリア濃度を有する酸化物半導体層404となる。なお、酸化物半導体層は非晶質状態であることが好ましいが、一部が結晶化していてもよい。なお、本明細書では、酸化物半導体層において一部が結晶化した状態であっても非晶質と表現する。

30

#### 【0068】

また、第1の加熱処理の条件、またはゲート電極層421aの材料によっては、ゲート電極層421aは結晶化し、微結晶膜または多結晶膜となる場合もある。例えば、ゲート電極層421aとして、酸化インジウム酸化スズ合金膜を用いる場合は450 1時間の第1の熱処理で結晶化がある。

#### 【0069】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うことでもできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、第2のフォトリソグラフィ工程を行う。

#### 【0070】

次いで、ゲート絶縁層402、及び酸化物半導体層404上に、スパッタ法で酸化物絶縁膜を形成した後、第3のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行って酸化物絶縁層426を形成し、その後レジストマスクを除去する工程を行っても良い。この段階で酸化物半導体層の周縁及び側面を覆う酸化物絶縁層426と重なる領域（酸化物半導体層の第1領域444c、第2領域444d）が形成され、リーケ電流や寄生容量を低減させることができる（図1（E）参照）。

40

#### 【0071】

酸化物絶縁層426は、少なくとも1nm以上の膜厚とし、上述した酸化物絶縁層に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。本実施の形態では、スパッタ法で成膜した酸化珪素膜で酸化物絶縁層426を形成する。

50

## 【0072】

成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化珪素膜のスパッタ法による成膜は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、または希ガス（代表的にはアルゴン）及び酸素混合雰囲気下において行うことができる。

## 【0073】

また、ターゲットとして酸化珪素ターゲットまたは珪素ターゲットを用いることができる。例えば、珪素ターゲットを用いて、酸素、及び希ガス雰囲気下でスパッタを行うことにより酸化珪素膜を形成することができる。低抵抗化した酸化物半導体層に接して形成する酸化物絶縁層は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらの外部からの侵入をブロックすることのできる無機絶縁膜を用いると良い。代表的には酸化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いることができる。

10

## 【0074】

本実施の形態では、ホウ素を添加した柱状多結晶珪素ターゲット（抵抗率0.01cm、純度6N）を用い、基板とターゲットの間との距離（T-S間距離）を89mm、圧力0.4Pa、直流（DC）電力6kW、酸素（酸素流量比率100%）雰囲気下でパルスDCスパッタ法により成膜する。膜厚は300nmとする。

## 【0075】

次いで、ゲート絶縁層402、酸化物絶縁層426、及び酸化物半導体層404上に、酸化物導電膜と金属膜の積層を形成する。スパッタ法を用いれば、酸化物導電膜と金属膜の積層を大気に触れることなく連続的に成膜を行うことができる。

20

## 【0076】

酸化物導電膜としては、例えばIn-Sn-O系、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、またはZn-O系の導電性の金属酸化物を用いることができ、膜厚は50nm以上300nm以下の範囲内で適宜選択する。本実施の形態では酸化亜鉛膜を用いる。

## 【0077】

また、金属膜としては、Ti、Mo、W、Al、Cr、Cu、及びTaから選ばれた元素、または上述した元素を成分とする合金等を用いる。また、上述した金属膜は単層に限定されず、異なる膜の積層を用いることができる。本実施の形態ではモリブデン膜とアルミニウム膜とモリブデン膜とを積層した三層積層膜を用いる。

30

## 【0078】

次いで、第4のフォトリソグラフィ工程によりレジストマスクを形成し、金属膜を選択的にエッチングしてソース電極層445a、ドレイン電極層445bを形成した後、レジストマスクを除去する。なお、レジストマスクを除去するために用いられるレジスト剥離液はアルカリ性溶液であり、レジスト剥離液を用いる場合は、ソース電極層445a、ドレイン電極層445bをマスクとして酸化亜鉛膜も選択的にエッチングされる。

## 【0079】

40

この様にして、ソース電極層445aの下に接して酸化物導電層446aが形成され、ドレイン電極層445bの下に接して酸化物導電層446bが形成される（図1（D）参照）。

## 【0080】

ソース電極層445aと酸化物半導体層との間に酸化物導電層446aを設けることによつて接触抵抗を下げ、低抵抗化を図ることができ、高速動作が可能な薄膜トランジスタを実現できる。ソース電極層445aと酸化物半導体層との間に設けられる酸化物導電層446aはソース領域として機能し、ドレイン電極層445bと酸化物半導体層との間に設けられる酸化物導電層446bはドレイン領域として機能するため、例えば、同一基板上に周辺回路（駆動回路）を形成する場合などでは、周波数特性を向上させることができる

50

。

## 【0081】

また、モリブデン膜は、酸化物半導体層に接すると接触抵抗が高くなる問題がある。これは、Tiに比べMoは酸化しにくいため酸化物半導体層から酸素を引き抜く作用が弱く、Moと酸化物半導体層の接触界面がn型化しないためである。しかし、この様な場合でも、酸化物半導体層とソース電極層またはドレイン電極層との間に酸化物導電層を介在させることで接触抵抗を低減することができる。

## 【0082】

なお、酸化物半導体層と酸化物導電層はエッティング速度に差があるため、酸化物半導体層上に接する酸化物導電層は、時間制御で除去することができる。

10

## 【0083】

また、金属膜を選択的にエッティングした後、酸素アッシング処理でレジストマスクを除去して、酸化亜鉛膜を残存させた後、ソース電極層445a、ドレイン電極層445b、をマスクとして酸化亜鉛膜を選択的にエッティングしてもよい。

## 【0084】

また、ソース電極層445a、ドレイン電極層445bを形成するためのレジストマスクをインクジェット法で形成してもよい。

## 【0085】

次いで、酸化物絶縁層426、ソース電極層445a、ドレイン電極層445b、酸化物半導体層404上に絶縁層427を形成する。絶縁層427としては、酸化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウムなどを用いる。本実施の形態では、RFスパッタ法を用いて酸化珪素膜を絶縁層427として形成する。

20

## 【0086】

この段階で、窒素ガス等の不活性ガス雰囲気下、200以上400以下、好ましくは250以上350以下で第2の加熱処理を行う。例えば、窒素雰囲気下で250、1時間の加熱処理を行う。

## 【0087】

第2の加熱処理では、酸化物である絶縁層427と酸化物半導体層404の一部が接した状態で加熱される。このため、第1の加熱処理で低抵抗化された酸化物半導体層404は、絶縁層427から酸素が供給されて酸素過剰な状態となり、高抵抗化(i型化)される。

30

## 【0088】

本実施の形態では、酸化珪素膜成膜後に第2の加熱処理を行ったが、加熱処理のタイミングは酸化珪素膜成膜以降であれば問題なく、酸化珪素膜成膜直後に限定されるものではない。

## 【0089】

また、ソース電極層445a及びドレイン電極層445bに耐熱性のある材料を用いる場合には、第2の加熱処理のタイミングで、第1の加熱処理条件を用いた工程を行うことができる。この場合、加熱処理は酸化珪素膜成膜後の1回のみとすることも可能である。

40

## 【0090】

この第2の加熱処理において、酸化物導電層446a、446bに酸化珪素のような結晶化阻害物質が含まれていない限り、酸化物導電層446a、446bは結晶化し、結晶領域を有するようになる。例えば、酸化物導電層に酸化亜鉛等を用いると柱状結晶になりやすく、酸化インジウム酸化スズ合金等の場合は、微結晶状態となりやすい。その結果、導電率が向上するとともに、酸化物半導体層とソース電極層445a及びドレイン電極層445bとの間の接触抵抗の低減が図られる。一方、第2の加熱処理においても本実施の形態で用いるIn-Ga-Zn-O系酸化物半導体層は結晶化せず、非晶質状態を維持する。

## 【0091】

次いで、絶縁層427上に保護絶縁層428を形成する(図1(E)参照)。保護絶縁層

50

428としては、窒化珪素膜、窒化酸化珪素膜、または窒化アルミニウムなどを用いることができる。本実施の形態では、RFスパッタ法を用いて窒化珪素膜を保護絶縁層428として形成する。

【0092】

以上の工程により、酸化物半導体層とソース電極層との間及び酸化物半導体層とドレイン電極層との間に、結晶領域を有する酸化物導電層を有した薄膜トランジスタ440を作製することができる。

【0093】

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【0094】

(実施の形態2)

本実施の形態では、ボトムコンタクト型の薄膜トランジスタ及びその作製工程として、実施の形態1と異なる例を図2を用いて説明する。図2は、図1と工程が一部異なる点以外は同じであるため、薄膜トランジスタの構成において、同じ部位を示す部分には同じ符号を用い、同部位の詳細な説明は省略する。

【0095】

図2(E)に示す薄膜トランジスタ470は、ボトムコンタクト型と呼ばれるボトムゲート構造の一つである。

【0096】

薄膜トランジスタ470は絶縁表面を有する基板400上に、ゲート電極層421a、ゲート絶縁層402、ソース電極層445a、ドレイン電極層445b、酸化物導電層446a、446b、及びチャネル形成領域443を有する酸化物半導体層を含む。また、チャネル形成領域443、ソース電極層445a、及びドレイン電極層445b上には絶縁層427及び保護絶縁層428が設けられる。

【0097】

ここで、酸化物導電層446a、446bは、結晶領域を有する導電率の高い材料からなると共に、酸化物半導体層とソース電極層445a及びドレイン電極層445bとの間の接触抵抗を低減することができ、高速動作が可能な薄膜トランジスタを実現できる。

【0098】

以下、図2(A)、(B)、(C)、(D)、(E)を用い、薄膜トランジスタ470を作製する工程を説明する。

【0099】

実施の形態1に従って、ゲート電極層421a、ゲート絶縁層402を形成する。

【0100】

次いで、ゲート絶縁層402上に、金属膜と酸化物導電膜の積層を形成する(図2(A)参照)。このとき、スパッタ法を用いれば、金属膜と酸化物導電膜の積層を大気に触れることなく連続的に成膜することができる。本実施の形態では、金属膜にモリブデン膜とアルミニウム膜とモリブデン膜を積層した三層積層膜、酸化物導電膜に酸化亜鉛膜を用いる。

【0101】

次いで、フォトリソグラフィ工程によりレジストマスクを形成し、酸化亜鉛膜、金属膜を選択的にエッティングして、ソース電極層445a、ドレイン電極層445b、酸化物導電層446a、及び酸化物導電層446bを形成する(図2(B)参照)。ここで、レジストマスクを除去するために用いられるレジスト剥離液はアルカリ性溶液であり、酸化亜鉛膜がエッティングされることもあるため、酸化亜鉛膜が薄膜化するのを防ぐため、酸素アッシングでレジストを除去することが好ましい。

【0102】

次いで、実施の形態1と同様に酸化物半導体膜を形成し、フォトリソグラフィ工程及びエッティング工程にて酸化物半導体層404を形成する(図2(C)参照)。

【0103】

10

20

30

40

50

ここで、実施の形態 1 で説明した第 1 の加熱処理の方法に従って、酸化物半導体層の脱水化または脱水素化を行う。

【 0 1 0 4 】

なお、酸化物半導体膜の成膜前に、不活性ガス雰囲気（窒素、ヘリウム、ネオン、またはアルゴン等）下において加熱処理（400 以上基板の歪み点未満）を行い、ゲート絶縁層 402 に含まれる水素及び水などの不純物を除去したゲート絶縁層としてもよい。

【 0 1 0 5 】

次いで、ソース電極層 445a、ドレイン電極層 445b、酸化物半導体層 404 上に絶縁層 427 を形成する（図 2 (D) 参照）。絶縁層 427 としては、酸化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウムなどを用いる。本実施の形態では、RFスパッタ法を用いて酸化珪素膜を絶縁層 427 として形成する。

10

【 0 1 0 6 】

ここで、実施の形態 1 で説明した第 2 の加熱処理の方法に従って、加熱処理を行う。

【 0 1 0 7 】

本実施の形態では、酸化珪素膜成膜後に第 2 の加熱処理を行ったが、加熱処理のタイミングは酸化珪素膜成膜以降であれば問題なく、酸化珪素膜成膜直後に限定されるものではない。

【 0 1 0 8 】

また、ソース電極層 445a 及びドレイン電極層 445b に耐熱性のある材料を用いる場合には、第 2 の加熱処理のタイミングで、第 1 の加熱処理条件を用いた工程を行うことができる。

20

【 0 1 0 9 】

ここまでいづれか一つの加熱処理工程を経れば、酸化物導電層 446a、446b に酸化珪素のような結晶化阻害物質が含まれていない限り、酸化物導電層 446a、446b は結晶化し、結晶領域を有するようになる。もちろん、複数回の加熱工程を経ても良い。一方で、複数回の加熱処理によっても酸化物半導体層は結晶化せず、非晶質状態を維持する。

【 0 1 1 0 】

次いで、絶縁層 427 上に保護絶縁層 428 を形成する（図 2 (E) 参照）。

30

【 0 1 1 1 】

以上の工程により、酸化物半導体層とソース電極層との間及び酸化物半導体層とドレイン電極層との間に、結晶領域を有する酸化物導電層を有した薄膜トランジスタ 470 を作製することができる。

【 0 1 1 2 】

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【 0 1 1 3 】

（実施の形態 3）

本実施の形態では、ボトムコンタクト型の薄膜トランジスタ及びその作製工程として、実施の形態 1 及び 2 と異なる例について図 3 を用いて説明する。なお、図 3 は、図 1 と工程が一部異なる点以外は同じであるため、薄膜トランジスタの構成において、同じ部位を示す部分には同じ符号を用い、同部位の詳細な説明は省略する。

40

【 0 1 1 4 】

図 3 (E) にチャネル保護型と呼ばれるボトムゲート構造の薄膜トランジスタ 480 の断面図を示す。

【 0 1 1 5 】

薄膜トランジスタ 480 は、絶縁表面を有する基板 400 上に、ゲート電極層 421a、ゲート絶縁層 402、酸化物半導体層、酸化物導電層 446a、446b、ソース電極層 445a、及びドレイン電極層 445b を含む。ここで、酸化物半導体層には、チャネル形成領域 443、高抵抗ソース領域 424a、及び高抵抗ドレイン領域 424b が含まれる。また、チャネル形成領域 443 に接してチャネル保護層として機能する酸化物絶縁層

50

426aが設けられている。また、ソース電極層445a、及びドレイン電極層445b、酸化物絶縁層426a、酸化物半導体層404上には保護絶縁層428が設けられる。

【0116】

酸化物絶縁層426bと重なる酸化物半導体層の第1領域424c、第2領域424dは、チャネル形成領域443と同じ酸素過剰な状態であり、リーク電流の低減や、寄生容量を低減する機能も果たしている。

【0117】

保護絶縁層428と接する酸化物半導体層の第3領域424eは、チャネル形成領域443と高抵抗ソース領域424aの間に設けられる。また、保護絶縁層428と接する酸化物半導体層の第4領域424fは、チャネル形成領域443と高抵抗ドレイン領域424bの間に設けられる。

10

【0118】

酸化物導電層446a、446bは、結晶領域を有する導電率の高い材料からなると共に、酸化物半導体層とソース電極層445a及びドレイン電極層445bとの間の接触抵抗を低減することができ、高速動作が可能な薄膜トランジスタを実現できる。

【0119】

酸化物半導体層の第3領域424e及び第4の領域424fには、酸素欠乏型である高抵抗ソース領域(H R S ( H i g h R e s i s t a n c e S o u r c e )領域とも呼ぶ)及び、高抵抗ドレイン領域(H R D ( H i g h R e s i s t a n c e D r a i n )領域とも呼ぶ)が形成される。具体的には、高抵抗ドレイン領域のキャリア濃度は、 $1 \times 10^{18} / \text{cm}^3$ 以上の範囲内であり、少なくともチャネル形成領域のキャリア濃度( $1 \times 10^{18} / \text{cm}^3$ 未満)よりも高い領域である。

20

【0120】

なお、本実施の形態のキャリア濃度は、室温にてH a l 1効果測定から求めたキャリア濃度の値を指す。この第3の領域及び第4の領域のチャネル長方向の幅を広くすれば、薄膜トランジスタのオフ電流の低減を図ることができる。また、この第3の領域及び第4の領域のチャネル長方向の幅を狭くすれば、薄膜トランジスタの動作速度の高速化を図ることができる。

【0121】

チャネル保護型の薄膜トランジスタは、チャネル保護層として機能する酸化物絶縁層の幅を狭くすることで実質的なチャネル長Lを短くすることが容易に可能となるが、該酸化物絶縁層上にソース電極層及びドレイン電極層を設けると短絡する恐れがある。従って、該酸化物絶縁層から端部を離してソース電極層445a及びドレイン電極層445bを設ける構成としている。

30

【0122】

また、図3(E)ではチャネル保護層として機能する酸化物絶縁層426a直下の酸化物半導体層の領域をチャネル形成領域と呼ぶこととする。従って、薄膜トランジスタ480のチャネル長Lは、酸化物絶縁層426aのチャネル長方向の幅と等しく、図3(E)に示す断面図においては、台形で示された酸化物絶縁層426aの底辺の長さに対応する。

40

【0123】

次に、図3(A)、(B)、(C)、(D)、(E)を用い、薄膜トランジスタ480を作製する工程を説明する。

【0124】

実施の形態1に従って、ゲート電極層421a、ゲート絶縁層402を形成する(図3(A)参照)。

【0125】

次いで、実施の形態1と同様に酸化物半導体膜を形成し、フォトリソグラフィ工程及びエッチング工程にて島状の酸化物半導体層404を形成する(図3(B)参照)。

【0126】

なお、酸化物半導体膜の成膜前に、不活性ガス雰囲気(窒素、ヘリウム、ネオン、または

50

アルゴン等)下において加熱処理(400以上基板の歪み点未満)を行い、ゲート絶縁層402に含まれる水素及び水などの不純物を除去したゲート絶縁層としてもよい。

【0127】

ここで、実施の形態1で説明した第1の加熱処理の方法に従って、酸化物半導体層の脱水化または脱水素化を行う。

【0128】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うこともできる。

【0129】

次いで、ゲート絶縁層402上、及び酸化物半導体層404上に、実施の形態1と同様にスパッタ法で酸化物絶縁膜を形成した後、フォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行って酸化物絶縁層426a、426bを形成し、その後レジストマスクを除去する。ここで、酸化物絶縁層426a直下の酸化物半導体層の領域がチャネル形成領域となる(図3(C)参照)。

10

【0130】

次いで、実施の形態1と同様に酸化物絶縁層426a、426b、及び酸化物半導体層上に、酸化物導電膜と金属膜の積層を形成し、部分的にエッチングしてソース電極層445a、ドレイン電極層445b、酸化物導電層446a、446bを形成する。スパッタ法を用いれば、金属膜と酸化物導電膜の積層を大気に触れることなく連続的に成膜を行うことができる。本実施の形態では、金属膜にモリブデン膜とアルミニウム膜とモリブデン膜とを積層した三層積層膜、酸化物導電膜に酸化亜鉛膜を用いる。(図3(D)参照)。

20

【0131】

次いで、窒素ガス等の不活性ガス雰囲気下、200以上400以下、好ましくは250以上350以下で第2の加熱処理を行う。例えば、窒素雰囲気下で250、1時間の加熱処理を行う。

【0132】

第2の加熱処理では、酸化物半導体層404の一部が酸化物絶縁層426a、426bと接した状態で加熱される。このため、第1の加熱処理で低抵抗化された酸化物半導体層404は、酸化物絶縁層426a、426bから酸素が供給されて酸素過剰な状態となり、高抵抗化(i型化)される。

30

【0133】

一方、酸化物絶縁層426a、426bと重ならない酸化物半導体層404の一部は露出した状態で加熱されるため、低抵抗が維持、または更に低抵抗化した第3の領域424e及び第4の領域424fを形成することができる。

【0134】

なお、本形態では酸化物絶縁層426a、426bの形成後に第2の加熱処理を行ったが、そのタイミングは酸化物絶縁層426a、426bの形成以降であれば問題なく、酸化物絶縁層426a、426bの形成直後に限定されるものではない。

【0135】

この第2の加熱処理において、酸化物導電層446a、446bに酸化珪素のような結晶化阻害物質が含まれていない限り、酸化物導電層446a、446bは結晶化し、結晶領域を有するようになる。一方で、第2の加熱処理によつても酸化物半導体層は結晶化せず、非晶質状態を維持する。

40

【0136】

次いで、酸化物半導体層404、酸化物絶縁層426a、426b、ソース電極層445a、ドレイン電極層445b上に保護絶縁層428を形成する(図3(E)参照)。保護絶縁層428としては、窒化珪素膜、窒化酸化珪素膜、または窒化アルミニウムなどを用いる。本実施の形態では、RFスパッタ法を用いて窒化珪素膜の保護絶縁層428を形成する。

【0137】

50

以上の工程により、酸化物半導体層とソース電極層との間及び酸化物半導体層とドレイン電極層との間に、結晶領域を有する酸化物導電層を有した薄膜トランジスタ480を作製することができる。

【0138】

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【0139】

(実施の形態4)

本実施の形態では、実施の形態1、2及び3に示した薄膜トランジスタを用いて同一基板上にアクティブマトリクス型の液晶表示装置、または発光装置を作製する一例を示す。

【0140】

アクティブマトリクス基板を用いた液晶表示装置の断面構造の一例を図4に示す。

【0141】

実施の形態1、2及び3では、薄膜トランジスタの形態について断面図を示したが、本実施の形態では、同一基板上に駆動回路部及び画素部を有する構成について、駆動回路部用の薄膜トランジスタ450、画素部用の薄膜トランジスタ460、ゲート配線コンタクト部、保持容量、ゲート配線、ソース配線及びその交差部、画素電極等を図示して説明する。保持容量、ゲート配線、ソース配線は、実施の形態1及び2に示す薄膜トランジスタの作製工程と同じ工程で形成することができ、フォトマスク枚数の増加や、工程数が増加することなく作製することができる。

【0142】

図4において、薄膜トランジスタ450は、駆動回路部に設けられる薄膜トランジスタであり、画素電極層457aと電気的に接続する薄膜トランジスタ460は、画素部に設けられる薄膜トランジスタである。

【0143】

基板400上に形成される薄膜トランジスタ460として、本実施の形態では、実施の形態1、2及び3の薄膜トランジスタと同じ構造を用いる。ここでは、例としてチャネルエッチ型の薄膜トランジスタを示す。

【0144】

薄膜トランジスタ460のゲート電極層と同じ材料、及び同じ工程で形成される容量配線層430は、誘電体となるゲート絶縁層402を介して容量電極層431と重なり、保持容量を形成する。なお、容量電極層431は、薄膜トランジスタ460のソース領域またはドレイン領域に設けられた電極層及び酸化物導電層と同じ材料、及び同じ工程で形成される。

【0145】

なお、保持容量は、画素電極層457aの下方に設けられる。図示はされていないが、容量電極層431が画素電極層457aと電気的に接続される。

【0146】

本実施の形態では、容量電極層431、及び容量配線層430を用いて保持容量を形成する例を示したが、保持容量を形成する構造については特に限定されない。例えば、容量配線層を設けず、画素電極を隣り合う画素のゲート配線と平坦化絶縁層、保護絶縁層、及びゲート絶縁層を介して重ねて保持容量を形成してもよい。

【0147】

また、ゲート配線、ソース配線、及び容量配線層は画素密度に応じて複数本設けられるものである。また、端子部においては、ゲート配線と同電位の第1の端子電極、ソース配線と同電位の第2の端子電極、容量配線層と同電位の第3の端子電極などが複数並べられて配置される。それぞれの端子電極の数は、それぞれ任意な数で設ければ良いものとし、実施者が適宜決定すれば良い。

【0148】

ゲート配線コンタクト部において、ゲート電極層421bは、低抵抗の金属材料で形成することができる。ゲート電極層421bは、ゲート配線に達するコンタクトホールを介し

10

20

30

40

50

てゲート配線と電気的に接続される。

【0149】

ここで、酸化物半導体層に対する脱水化・脱水素化のための熱処理は、酸化物半導体層の成膜後、酸化物半導体層上に酸化物導電層を積層させた後、ソース電極及びドレイン電極上にパッシベーション膜を形成した後、のいずれかで行えば良い。

【0150】

また、駆動回路部の薄膜トランジスタ450のゲート電極層は、酸化物半導体層の上方に設けられた導電層417と電気的に接続させる構造としてもよい。

【0151】

また、配線交差部において、図4に示すように寄生容量を低減するため、ゲート配線層421cとソース配線層422との間には、ゲート絶縁層402及び酸化物絶縁層426を積層する構成としている。

【0152】

また、アクティブマトリクス型の液晶表示装置を作製する場合には、アクティブマトリクス基板と、対向電極が設けられた対向基板との間に液晶層を設け、アクティブマトリクス基板と対向基板とを固定する。同様に、二つの電極の間に挟まれるようにプラスの電荷を有する第1の粒子と、マイナスの電荷を有する第2の粒子とを含むマイクロカプセルを複数配置すればアクティブマトリクス型の電気泳動表示装置を構成することもできる。なお、対向基板に設けられた対向電極と電気的に接続する共通電極をアクティブマトリクス基板上に設け、共通電極と電気的に接続する第4の端子電極を端子部に設ける。この第4の端子電極は、共通電極を固定電位、例えばGND、0Vなどに設定するための端子である。第4の端子電極は、画素電極層457aと同じ材料で形成することができる。

【0153】

また、ゲート電極、ソース電極、ドレイン電極、画素電極、またはその他の電極や、他の配線層に同じ材料を用いれば共通のスパッタターゲットや共通の製造装置を用いることができ、その材料コスト及びエッチング時に使用するエッチャント（またはエッチングガス）に要するコストを低減することができ、結果として製造コストを削減することができる。

【0154】

また、図4の構造において、平坦化絶縁層456として感光性の樹脂材料を用いる場合、レジストマスクを形成する工程を省略することができる。

【0155】

また、図5にアクティブマトリクス型発光装置として、第1電極（画素電極）上にEL層を形成する前の基板の状態を示す断面図を示す。

【0156】

図5においては、チャネルエッチ型の薄膜トランジスタが図示されているが、実施の形態2及び3と同様の構造の薄膜トランジスタを用いることもできる。また、下記に示す画素部の構成以外は前述した液晶表示装置と同様の構成とすることができます。

【0157】

絶縁層427を形成した後、カラーフィルタ層453を形成する。カラーフィルタ層は、赤色、緑色、及び青色があり、印刷法、インクジェット法、フォトリソグラフィ技術を用いたエッチング方法などでそれぞれを順次特定の位置に形成する。カラーフィルタ層453を基板400側に設けることによって、封止基板の貼り合わせ精度に依存することなくカラーフィルタ層453と発光素子の発光領域との位置合わせを行うことができる。

【0158】

次いで、カラーフィルタ層453を覆うオーバーコート層458を形成する。オーバーコート層458には、透光性を有する樹脂を用いる。

【0159】

ここでは赤色、緑色、及び青色の3色のカラーフィルタ層を用いてフルカラー表示する例を示したが、特に限定されず、シアン、マゼンタ、イエロー、またはホワイトのカラーフ

10

20

30

40

50

イルタ層を加えてフルカラー表示を行ってもよい。

【0160】

次いで、オーバーコート層458及び絶縁層427を覆う保護絶縁層428を形成する。保護絶縁層428は、無機絶縁膜を用い、窒化珪素膜、窒化アルミニウム膜、窒化酸化珪素膜、または酸化窒化アルミニウムなどを用いる。

【0161】

次いで、フォトリソグラフィ工程及びエッティング工程により保護絶縁層428及び絶縁層427に接続電極層452に達するコンタクトホールを形成する。また、このフォトリソグラフィ工程及びエッティング工程により端子部の保護絶縁層428及び絶縁層427を選択的にエッティングして端子電極の一部を露出させる。また、後に形成される発光素子の第2電極と共に電位線とを接続するため、共通電位線に達するコンタクトホールも形成する。

10

【0162】

次いで、透光性を有する導電膜を形成し、フォトリソグラフィ工程及びエッティング工程により接続電極層452と電気的に接続する第1電極457bを形成する。

【0163】

次いで、第1電極457bの周縁部を覆うように隔壁459を形成する。隔壁459は、ポリイミド、アクリル、ポリアミド、エポキシ等の有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。隔壁459は、有機絶縁材料、または無機絶縁材料を用いて形成することができる。隔壁459は、側壁が曲率を有する傾斜面となる様な開口部を第1の電極457b上有する様に形成することができる。この様な開口部は、感光性の樹脂材料を用いることで容易に形成することができる。

20

【0164】

以上の工程を経て図5に示す基板の状態を得ることができる。更に第1電極457b上にEL層を形成し、EL層上に第2電極を形成することで発光素子を形成する。なお、第2の電極は、共通電位線と電気的に接続する。

【0165】

また、図4及び図5に示す駆動回路部の薄膜トランジスタ450には、酸化物半導体層の上方に導電層417を設けてもよい。導電層417は、画素電極層457aまたは、第1電極457bと同じ材料、同じ工程で形成することができる。

30

【0166】

導電層417を酸化物半導体層のチャネル形成領域443と重なる位置に設けることによつて、薄膜トランジスタ450のしきい値電圧の経時変化量を低減することができる。また、導電層417は、ゲート電極層421aと同電位とすることで、第2のゲート電極層として機能させることもできる。また、導電層417にゲート電極層421aと異なる電位を与えても良い。また、導電層417の電位がGND、0V、或いはフローティング状態であつてもよい。

【0167】

また、薄膜トランジスタは静電気などにより破壊されやすいため、画素部または駆動回路部と同一基板上に保護回路を設けることが好ましい。保護回路は、酸化物半導体層を用いた非線形素子を用いて構成することができる。例えば、保護回路は画素部と、走査線入力端子及び信号線入力端子との間に配設されている。本実施の形態では複数の保護回路を配設して、走査線、信号線及び容量バス線に静電気等によりサージ電圧が印加され、画素トランジスタなどが破壊されないように構成されている。そのため、保護回路にはサージ電圧が印加されたときに、共通配線に電荷を逃がすように構成する。また、保護回路は、走査線に対して並列に配置された非線形素子によって構成されている。非線形素子は、ダイオードのような二端子素子またはトランジスタのような三端子素子で構成される。例えば、画素部の薄膜トランジスタ460と同じ工程で形成することも可能であり、例えばゲート端子とドレイン端子を接続することによりダイオードと同様の特性を持たせることができる。

40

50

## 【0168】

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

## 【0169】

## (実施の形態5)

実施の形態1、2及び3に示した薄膜トランジスタを用いて表示機能を有する半導体装置(表示装置ともいう)を作製することができる。また、薄膜トランジスタを有する駆動回路部及び画素部を同じ基板上に一体形成し、システムオンパネルを形成することができる。

## 【0170】

表示装置は表示素子を含んで構成される。表示素子としては液晶素子(液晶表示素子ともいう)、電子インクなど、電気的作用によりコントラストが変化する表示媒体を用いることができる。

10

## 【0171】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源(照明装置含む)を指す。また、FPC(Flexible printed circuit)もしくはTAB(Tape Automated Bonding)テープが取り付けられたモジュール、TABテープの先にプリント配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass)方式によりIC(集積回路)が直接実装されたモジュールも全て表示装置に含むものとする。

20

## 【0172】

表示装置の一形態に相当する液晶表示パネルの外観及び断面について、図6を用いて説明する。図6(A1)、(A2)は、薄膜トランジスタ4010、4011、及び液晶素子4013を第1の基板4001と第2の基板4006との間のシール材4005によって封止したパネルの平面図であり、図6(B)は、図6(A1)、(A2)のM-Nにおける断面図に相当する。

## 【0173】

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また画素部4002と、走査線駆動回路4004との上に第2の基板4006が設けられている。よって画素部4002と、走査線駆動回路4004は、第1の基板4001とシール材4005と第2の基板4006とによって、液晶層4008と共に封止されている。また、第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、単結晶半導体または多結晶半導体で形成された信号線駆動回路4003が実装されている。

30

## 【0174】

なお、信号線駆動回路4003の接続方法は、特に限定されるものではなく、COG法、ワイヤボンディング法、或いはTAB法などを用いることができる。図6(A1)は、COG法により信号線駆動回路4003を実装する例であり、図6(A2)は、TAB法により信号線駆動回路4003を実装する例である。

## 【0175】

また、第1の基板4001上に設けられた画素部4002と走査線駆動回路4004は、薄膜トランジスタを複数有しており、図6(B)では、画素部4002に含まれる薄膜トランジスタ4010と、走査線駆動回路4004に含まれる薄膜トランジスタ4011を例示している。薄膜トランジスタ4010、4011上には、絶縁層4041、4020、4021が設けられている。

40

## 【0176】

薄膜トランジスタ4010、4011には、実施の形態1、2及び3で示した酸化物半導体層を含む信頼性の高い薄膜トランジスタを用いることができる。本実施の形態において、薄膜トランジスタ4010、4011は、nチャネル型薄膜トランジスタである。

## 【0177】

絶縁層4021において、駆動回路用の薄膜トランジスタ4011の酸化物半導体層の

50

チャネル形成領域と重なる位置には、導電層 4040 が設けられている。導電層 4040 を酸化物半導体層のチャネル形成領域と重なる位置に設けることによって、薄膜トランジスタ 4011 のしきい値電圧の経時変化量を低減することができる。また、導電層 4040 は、薄膜トランジスタ 4011 のゲート電極と同電位とすることで、第 2 のゲート電極層として機能させることもできる。また、導電層 4040 に薄膜トランジスタ 4011 のゲート電極と異なる電位を与えてても良い。また、導電層 4040 の電位が GND、0V、或いはフローティング状態であってもよい。

#### 【 0178 】

また、液晶素子 4013 が有する画素電極 4030 は、薄膜トランジスタ 4010 と電気的に接続されている。そして、液晶素子 4013 の対向電極 4031 は、第 2 の基板 4006 上に形成されている。画素電極 4030 と対向電極 4031 と液晶層 4008 とが重なっている部分が、液晶素子 4013 に相当する。なお、画素電極 4030、対向電極 4031 には、それぞれ配向膜として機能する絶縁層 4032、4033 が設けられている。

#### 【 0179 】

なお、第 1 の基板 4001、第 2 の基板 4006 としては、透光性基板を用いることができ、ガラス、セラミックス、またはプラスチックを用いることができる。プラスチックとしては、FRP (Fiberglass-Reinforced Plastics) 板、PVF (ポリビニルフルオライド) フィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。

#### 【 0180 】

また、4035 は絶縁層を選択的にエッチングすることで得られる柱状のスペーサであり、画素電極 4030 と対向電極 4031 との間の距離 (セルギャップ) を制御するために設けられている。なお、球状のスペーサを用いても良い。また、対向電極 4031 は、薄膜トランジスタ 4010 と同一基板上に設けられる共通電位線と電気的に接続される。共通接続部を用いて、一対の基板間に配置される導電性粒子を介して対向電極 4031 と共通電位線とを電気的に接続することができる。なお、導電性粒子はシール材 4005 に含有させる。

#### 【 0181 】

また、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために 5 重量 % 以上のカイラル剤を混合させた液晶組成物を用いて液晶層 4008 に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が 1 msec 以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。

#### 【 0182 】

また、液晶表示装置では、基板の外側 (視認側) に偏光板を設け、内側に着色層、表示素子に用いる電極層という順に設ける例を示すが、偏光板は基板の内側に設けてもよい。また、偏光板と着色層の積層構造も本実施の形態に限定されず、偏光板及び着色層の材料や作製工程条件によって適宜設定すればよい。

#### 【 0183 】

薄膜トランジスタ 4011 は、チャネル形成領域を含む半導体層に接して絶縁層 4041 が形成されている。絶縁層 4041 は、実施の形態 1 で示した絶縁層 427 と同様な材料及び方法で形成すればよい。また、薄膜トランジスタの表面凹凸を低減するため、平坦化絶縁層として機能する絶縁層 4021 で覆う構成となっている。ここでは、絶縁層 4041 として、実施の形態 1 と同様にスパッタ法により酸化珪素膜を形成する。

#### 【 0184 】

また、絶縁層 4041 上に保護絶縁層 4020 が形成されている。保護絶縁層 4020 は実施の形態 1 で示した保護絶縁層 428 と同様な材料及び方法で形成すればよい。ここでは、保護絶縁層 4020 として、PCVD 法により窒化珪素膜を形成する。

10

20

30

40

50

## 【0185】

また、平坦化絶縁層として絶縁層4021を形成する。絶縁層4021としては、アクリル、ポリイミド、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。なお、これらの材料で形成される絶縁層を複数積層させることで、絶縁層4021を形成してもよい。

## 【0186】

なお、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基（例えばアルキル基やアリール基）やフルオロ基を用いても良い。また、有機基はフルオロ基を有していても良い。

10

## 【0187】

絶縁層4021の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。絶縁層4021の焼成工程と半導体層のアニールを兼ねることで効率よく表示装置を作製することが可能となる。

## 【0188】

画素電極4030、及び対向電極4031は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウムスズ酸化物、インジウムスズ酸化物（以下、ITOと示す。）、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウムスズ酸化物などの透光性を有する導電性材料を用いることができる。

20

## 【0189】

また、画素電極4030、対向電極4031として、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が10000 / 以下、波長550nmにおける光の透過率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

30

## 【0190】

導電性高分子としては、いわゆる電子共役系導電性高分子を用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの2種以上の共重合体などがあげられる。

## 【0191】

また、別途形成された信号線駆動回路4003と、走査線駆動回路4004及び画素部4002に与えられる各種信号及び電位は、FPC4018を介して供給されている。

## 【0192】

接続端子電極4015は、液晶素子4013が有する画素電極4030と同じ導電膜で形成され、端子電極4016は、薄膜トランジスタ4010、4011のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

40

## 【0193】

接続端子電極4015は、FPC4018が有する端子と異方性導電膜4019を介して電気的に接続されている。

## 【0194】

また、図6においては、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているがこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

## 【0195】

50

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【0196】

(実施の形態6)

本実施の形態では、発光表示パネル(発光パネルともいう)の外観及び断面について、図7を用いて説明する。図7(A)は、第1の基板上に形成された薄膜トランジスタ及び発光素子を、第2の基板との間にシール材によって封止した、パネルの平面図であり、図7(B)は、図7(A)のH-Iにおける断面図に相当する。

【0197】

第1の基板4501上に設けられた画素部4502、信号線駆動回路4503a、4503b、及び走査線駆動回路4504a、4504bを囲むようにして、シール材4505が設けられている。また画素部4502、信号線駆動回路4503a、4503b、及び走査線駆動回路4504a、4504bの上に第2の基板4506が設けられている。

10

【0198】

従って、画素部4502、信号線駆動回路4503a、4503b、及び走査線駆動回路4504a、4504bは、第1の基板4501と、シール材4505と、第2の基板4506によって、充填材4507と共に密封されている。この様に外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

【0199】

また、第1の基板4501上に設けられた画素部4502、信号線駆動回路4503a、4503b、及び走査線駆動回路4504a、4504bは、薄膜トランジスタを複数有しており、図7(B)では、画素部4502に含まれる薄膜トランジスタ4510と、信号線駆動回路4503aに含まれる薄膜トランジスタ4509とを例示している。

20

【0200】

薄膜トランジスタ4509、4510には、実施の形態1、2及び3で示した酸化物半導体層を含む信頼性の高い薄膜トランジスタを用いることができる。本実施の形態において、薄膜トランジスタ4509、4510は、nチャネル型薄膜トランジスタである。

【0201】

絶縁層4544上において、駆動回路用の薄膜トランジスタ4509の酸化物半導体層のチャネル形成領域と重なる位置に導電層4540が設けられている。導電層4540を酸化物半導体層のチャネル形成領域と重なる位置に設けることによって、BT試験前後における薄膜トランジスタ4509のしきい値電圧の経時変化量を低減することができる。また、導電層4540は、薄膜トランジスタ4509のゲート電極層と同電位とすることと、第2のゲート電極層として機能させることもできる。また、導電層4540に薄膜トランジスタ4509のゲート電極層と異なる電位を与えても良い。また、導電層4540の電位がGND、0V、或いはフローティング状態であってもよい。

30

【0202】

薄膜トランジスタ4509の酸化物半導体層周辺部には、酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層4542が形成されている。

【0203】

また、薄膜トランジスタ4510は、接続電極層4548を介して第1電極4517と電気的に接続されている。また、薄膜トランジスタ4510の酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層4542が形成されている。

40

【0204】

酸化物絶縁層4542は、実施の形態1で示した酸化物絶縁層426と同様な材料及び方法で形成すればよい。また、酸化物絶縁層4542を覆う絶縁層4544が形成されている。絶縁層4544は、実施の形態1で示した保護絶縁層428と同様な材料及び方法で形成すればよい。

【0205】

発光素子4511の発光領域と重なるようにカラーフィルタ層4545が、薄膜トランジ

50

スタ 4 5 1 0 上に形成される。

【 0 2 0 6 】

また、カラーフィルタ層 4 5 4 5 の表面凹凸を低減するため平坦化絶縁膜として機能するオーバーコート層 4 5 4 3 で覆う構成となっている。

【 0 2 0 7 】

また、オーバーコート層 4 5 4 3 上に絶縁層 4 5 4 6 が形成されている。絶縁層 4 5 4 6 は、実施の形態 1 で示した保護絶縁層 4 2 8 と同様な材料及び方法で形成すればよい。

【 0 2 0 8 】

また、発光素子 4 5 1 1 が有する画素電極である第 1 電極 4 5 1 7 は、薄膜トランジスタ 4 5 1 0 のソース電極層またはドレイン電極層と電気的に接続されている。なお、発光素子 4 5 1 1 の構成は、第 1 電極 4 5 1 7 、電界発光層 4 5 1 2 、第 2 電極 4 5 1 3 の積層構造であるが、示した構成に限定されない。発光素子 4 5 1 1 から取り出す光の方向などに合わせて、発光素子 4 5 1 1 の構成は適宜変えることができる。10

【 0 2 0 9 】

隔壁 4 5 2 0 は、有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。隔壁 4 5 2 0 は、側壁が曲率を有する傾斜面となる様な開口部を第 1 の電極 4 5 1 7 上に有する様に形成することが好ましい。この様な開口部は、感光性の樹脂材料を用いることで容易に形成することができる。

【 0 2 1 0 】

電界発光層 4 5 1 2 は、単層に限らず、複数の層の積層で構成されていても良い。20

【 0 2 1 1 】

発光素子 4 5 1 1 に酸素、水素、水分、二酸化炭素等が侵入しないように、第 2 の電極 4 5 1 3 及び隔壁 4 5 2 0 上に保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、DLC 膜等を形成することができる。

【 0 2 1 2 】

また、信号線駆動回路 4 5 0 3 a 、 4 5 0 3 b 、走査線駆動回路 4 5 0 4 a 、 4 5 0 4 b 、または画素部 4 5 0 2 に与えられる各種信号及び電位は、FPC 4 5 1 8 a 、 4 5 1 8 b を介して供給されている。

【 0 2 1 3 】

接続端子電極 4 5 1 5 は、発光素子 4 5 1 1 が有する第 1 電極 4 5 1 7 と同じ導電膜で形成され、端子電極 4 5 1 6 は、薄膜トランジスタ 4 5 0 9 のソース電極層及びドレイン電極層と同じ導電膜から形成されている。30

【 0 2 1 4 】

接続端子電極 4 5 1 5 は、FPC 4 5 1 8 a が有する端子と、異方性導電膜 4 5 1 9 を介して電気的に接続されている。

【 0 2 1 5 】

発光素子 4 5 1 1 からの光の取り出し方向に位置する基板であるので、第 2 の基板は透光性でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透光性を有する材料を用いる。

【 0 2 1 6 】

また、充填材 4 5 0 7 としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC (ポリビニルクロライド) 、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB (ポリビニルブチラル) またはEVA (エチレンビニルアセテート) を用いることができる。40

【 0 2 1 7 】

また、必要であれば、発光素子の射出面に偏光板、または円偏光板 (楕円偏光板を含む) 、位相差板 (1/4 板、1/2 板) 、カラーフィルタなどの光学フィルムを適宜設けてよい。また、偏光板または円偏光板に反射防止膜を設けてよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

【 0 2 1 8 】

信号線駆動回路 4503a、4503b、及び走査線駆動回路 4504a、4504bは、単結晶半導体または多結晶半導体によって形成された駆動回路が実装されていてもよい。また、信号線駆動回路のみ、或いはその一部、または走査線駆動回路のみ、或いはその一部のみを別途形成して実装しても良く、図7の構成に限定されない。

【0219】

以上の工程により、信頼性の高い発光表示装置（表示パネル）を作製することができる。

【0220】

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【0221】

（実施の形態7）

10

本明細書に開示する表示装置は、さまざまな電子機器（遊技機も含む）に用いることができる。電子機器としては、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

【0222】

図8（A）は、携帯電話機の一例を示している。携帯電話機1100は、筐体1101に組み込まれた表示部1102の他、操作ボタン1103、外部接続ポート1104、スピーカ1105、マイク1106などを備えている。

20

【0223】

また、携帯電話機1100は、表示部1102を指などで触れることで、情報を入力することができる。また、通話やメールの送受信などの操作は、表示部1102を指などで触れることにより行うことができる。

【0224】

表示部1102の画面は主として3つのモードがある。第1は、画像の表示を主とする表示モードであり、第2は、文字等の情報の入力を主とする入力モードである。第3は表示モードと入力モードの2つのモードが混合した表示+入力モードである。

【0225】

例えば、通話やメールを作成する場合は、表示部1102を文字の入力を主とする文字入力モードとし、画面に表示させた文字の入力操作を行えばよい。この場合、表示部1102の画面のほとんどにキーボードまたは番号ボタンを表示させることが好ましい。

30

【0226】

また、携帯電話機1100内部に、ジャイロ、加速度センサ等の傾きを検出するセンサを有する検出装置を設けることで、携帯電話機1100の向き（縦か横か）を判断して、表示部1102の画面表示を自動的に切り替えるようにすることができる。

【0227】

また、画面モードの切り替えは、表示部1102を触れること、または筐体1101の操作ボタン1103の操作により行われる。また、表示部1102に表示される画像の種類によって切り替えるようにすることもできる。例えば、表示部に表示する画像信号が動画のデータであれば表示モード、テキストデータであれば入力モードに切り替える。

40

【0228】

また、入力モードにおいて、表示部1102の光センサで検出される信号を検知して表示部1102のタッチ操作による入力が一定期間ない場合には、画面のモードを入力モードから表示モードに切り替えるように制御してもよい。

【0229】

表示部1102は、イメージセンサとして機能させることもできる。例えば、表示部1102に掌や指を触ることで、掌紋、指紋等を撮像することで、本人認証を行うことができる。また、表示部に近赤外光を発光するバックライトまたは近赤外光を発光するセンシング用光源を用いれば、指静脈、掌静脈などを撮像することもできる。

50

## 【0230】

図8(B)も携帯電話機の一例である。図8(B)を一例とした携帯型情報端末は、複数の機能を備えることができる。例えば、電話機能に加えて、コンピュータを内蔵し、様々なデータ処理機能を備えることもできる。

## 【0231】

図8(B)に示す携帯型情報端末は、筐体1800及び筐体1801の二つの筐体で構成されている。筐体1800は、表示パネル1802、スピーカ1803、マイクロフォン1804、ポインティングデバイス1806、カメラ1807、外部接続端子1808などを備え、筐体1801は、キーボード1810、外部メモリスロット1811などを備えている。また、アンテナは筐体1801内部に内蔵されている。

10

## 【0232】

また、表示パネル1802はタッチパネルを備えており、図8(B)には映像表示されている複数の操作キー1805を点線で示している。

## 【0233】

また、上記構成に加えて、非接触ICチップ、小型記録装置などを内蔵していてもよい。

## 【0234】

表示装置は、表示パネル1802として用いられ、使用形態に応じて表示の方向が適宜変化する。また、表示パネル1802と同一面上にカメラ1807を備えているため、テレビ電話が可能である。スピーカ1803及びマイクロフォン1804は音声通話に限らず、テレビ電話、録音、再生などにも使用できる。さらに、筐体1800と筐体1801は、スライドし、図8(B)のように展開している状態から重なり合った状態とすることができる、携帯に適した小型化が可能である。

20

## 【0235】

外部接続端子1808は、充電ケーブルやUSBケーブルなどの各種ケーブルと接続可能であり、充電及びパソコンなどとのデータ通信が可能である。また、外部メモリスロット1811に大容量の記録媒体を挿入し、より大量のデータの取り扱いにも対応できる。

## 【0236】

また、上記機能に加えて、赤外線通信機能、テレビ受信機能などを備えたものであってもよい。

30

## 【0237】

図9(A)は、テレビジョン装置の一例を示している。テレビジョン装置9600は、筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示することができる。また、ここでは、スタンド9605により筐体9601を支持した構成を示している。

## 【0238】

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、別体のリモコン操作機9610により行うことができる。リモコン操作機9610が備える操作キー9609により、チャンネルの切り替えや音量の操作を行うことができ、表示部9603に表示される映像を操作することができる。また、リモコン操作機9610に、当該リモコン操作機9610から出力する情報を表示する表示部9607を設ける構成としてもよい。

40

## 【0239】

なお、テレビジョン装置9600は、受信機やモデムなどを備えた構成とする。受信機により一般的のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

## 【0240】

図9(B)は、デジタルフォトフレームの一例を示している。例えば、デジタルフォトフレーム9700には、筐体9701に表示部9703が組み込まれている。表示部970

50

3は、各種画像を表示することが可能であり、例えばデジタルカメラなどで撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

【0241】

なお、デジタルフォトフレーム9700は、操作部、外部接続用端子（USB端子等）、外部メモリスロットなどを備える構成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの外部メモリスロットに、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像データを取り込み、取り込んだ画像データを表示部9703に表示させることができる。

【0242】

また、デジタルフォトフレーム9700は、無線で情報を送受信できる構成としてもよい。無線により、所望の画像データを取り込み、表示させる構成とすることもできる。

【0243】

図10は携帯型遊技機であり、筐体9881と筐体9891の2つの筐体で構成されており、連結部9893により、開閉可能に連結されている。筐体9881には表示部9882が組み込まれ、筐体9891には表示部9883が組み込まれている。

【0244】

また、図10に示す携帯型遊技機は、その他、スピーカ部9884、記録媒体挿入部9886、LEDランプ9890、入力手段（操作キー9885、接続端子9887、センサー9888（力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、においてまたは赤外線を測定する機能を含むもの）、マイクロフォン9889等を備えている。もちろん、携帯型遊技機の構成は上述のものに限定されず、少なくとも本明細書に開示する薄膜トランジスタを備えた構成であればよく、その他付属設備が適宜設けられた構成とすることができる。図10に示す携帯型遊技機は、記録媒体に記録されているプログラムまたはデータを読み出して表示部に表示する機能や、他の携帯型遊技機と無線通信を行って情報を共有する機能を有する。なお、図10に示す携帯型遊技機が有する機能はこれに限定されず、様々な機能を有することができる。

【0245】

以上の様に、他の実施の形態で示した表示装置は、上記の様な様々な電子機器の表示パネルに配置することができる。

【0246】

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【符号の説明】

【0247】

|     |          |

|-----|----------|

| 400 | 基板       |

| 402 | ゲート絶縁層   |

| 404 | 酸化物半導体層  |

| 417 | 導電層      |

| 422 | ソース配線層   |

| 426 | 酸化物絶縁層   |

| 427 | 絶縁層      |

| 428 | 保護絶縁層    |

| 430 | 容量配線層    |

| 431 | 容量電極層    |

| 440 | 薄膜トランジスタ |

| 442 | 接続電極層    |

| 443 | チャネル形成領域 |

| 449 | 接続電極層    |

| 450 | 薄膜トランジスタ |

10

20

30

40

50

|         |             |    |

|---------|-------------|----|

| 4 5 2   | 接続電極層       |    |

| 4 5 3   | カラーフィルタ層    |    |

| 4 5 6   | 平坦化絶縁層      |    |

| 4 5 8   | オーバーコート層    |    |

| 4 5 9   | 隔壁          |    |

| 4 6 0   | 薄膜トランジスタ    | 10 |

| 4 7 0   | 薄膜トランジスタ    |    |

| 4 8 0   | 薄膜トランジスタ    |    |

| 4 2 1 a | ゲート電極層      |    |

| 4 2 1 b | ゲート電極層      |    |

| 4 2 1 c | ゲート配線層      |    |

| 4 2 4 a | 高抵抗ソース領域    |    |

| 4 2 4 b | 高抵抗ドレイン領域   |    |

| 4 2 4 c | 領域          |    |

| 4 2 4 d | 領域          |    |

| 4 2 4 e | 領域          |    |

| 4 2 4 f | 領域          |    |

| 4 2 5 a | ソース電極層      |    |

| 4 2 5 b | ドレイン電極層     |    |

| 4 2 6 a | 酸化物絶縁層      | 20 |

| 4 2 6 b | 酸化物絶縁層      |    |

| 4 4 4 c | 領域          |    |

| 4 4 4 d | 領域          |    |

| 4 4 5 a | ソース電極層      |    |

| 4 4 5 b | ドレイン電極層     |    |

| 4 4 6 a | 酸化物導電層      |    |

| 4 4 6 b | 酸化物導電層      |    |

| 4 5 1 a | ゲート電極層      |    |

| 4 5 1 b | ゲート電極層      |    |

| 4 5 5 a | ソース電極層      | 30 |

| 4 5 5 b | ドレイン電極層     |    |

| 4 5 7 a | 画素電極層       |    |

| 4 5 7 b | 電極          |    |

| 1 1 0 0 | 携帯電話機       |    |

| 1 1 0 1 | 筐体          |    |

| 1 1 0 2 | 表示部         |    |

| 1 1 0 3 | 操作ボタン       |    |

| 1 1 0 4 | 外部接続ポート     |    |

| 1 1 0 5 | スピーカ        |    |

| 1 1 0 6 | マイク         | 40 |

| 1 8 0 0 | 筐体          |    |

| 1 8 0 1 | 筐体          |    |

| 1 8 0 2 | 表示パネル       |    |

| 1 8 0 3 | スピーカ        |    |

| 1 8 0 4 | マイクロフォン     |    |

| 1 8 0 5 | 操作キー        |    |

| 1 8 0 6 | ポインティングデバイス |    |

| 1 8 0 7 | カメラ         |    |

| 1 8 0 8 | 外部接続端子      |    |

| 1 8 1 0 | キー ボード      | 50 |

|           |           |    |

|-----------|-----------|----|

| 1 8 1 1   | 外部メモリスロット |    |

| 4 0 0 1   | 基板        |    |

| 4 0 0 2   | 画素部       |    |

| 4 0 0 3   | 信号線駆動回路   |    |

| 4 0 0 4   | 走査線駆動回路   |    |

| 4 0 0 5   | シール材      |    |

| 4 0 0 6   | 基板        |    |

| 4 0 0 8   | 液晶層       |    |

| 4 0 1 0   | 薄膜トランジスタ  | 10 |

| 4 0 1 1   | 薄膜トランジスタ  |    |

| 4 0 1 3   | 液晶素子      |    |

| 4 0 1 5   | 接続端子電極    |    |

| 4 0 1 6   | 端子電極      |    |

| 4 0 1 8   | F P C     |    |

| 4 0 1 9   | 異方性導電膜    |    |

| 4 0 2 0   | 保護絶縁層     |    |

| 4 0 2 1   | 絶縁層       |    |

| 4 0 3 0   | 画素電極      |    |

| 4 0 3 1   | 対向電極      |    |

| 4 0 3 2   | 絶縁層       | 20 |

| 4 0 4 0   | 導電層       |    |

| 4 0 4 1   | 絶縁層       |    |

| 4 5 0 1   | 基板        |    |

| 4 5 0 2   | 画素部       |    |

| 4 5 0 5   | シール材      |    |

| 4 5 0 6   | 基板        |    |

| 4 5 0 7   | 充填材       |    |

| 4 5 0 9   | 薄膜トランジスタ  |    |

| 4 5 1 0   | 薄膜トランジスタ  |    |

| 4 5 1 1   | 発光素子      | 30 |

| 4 5 1 2   | 電界発光層     |    |

| 4 5 1 3   | 電極        |    |

| 4 5 1 5   | 接続端子電極    |    |

| 4 5 1 6   | 端子電極      |    |

| 4 5 1 7   | 電極        |    |

| 4 5 1 9   | 異方性導電膜    |    |

| 4 5 2 0   | 隔壁        |    |

| 4 5 4 0   | 導電層       |    |

| 4 5 4 2   | 酸化物絶縁層    |    |

| 4 5 4 3   | オーバーコート層  | 40 |

| 4 5 4 4   | 絶縁層       |    |

| 4 5 4 5   | カラーフィルタ層  |    |

| 4 5 4 6   | 絶縁層       |    |

| 4 5 4 8   | 接続電極層     |    |

| 4 5 0 3 a | 信号線駆動回路   |    |

| 4 5 0 3 b | 信号線駆動回路   |    |

| 4 5 0 4 a | 走査線駆動回路   |    |

| 4 5 0 4 b | 走査線駆動回路   |    |

| 4 5 1 8 a | F P C     |    |

| 9 6 0 0   | テレビジョン装置  | 50 |

|         |             |    |

|---------|-------------|----|

| 9 6 0 1 | 筐体          |    |

| 9 6 0 3 | 表示部         |    |

| 9 6 0 5 | スタンド        |    |

| 9 6 0 7 | 表示部         |    |

| 9 6 0 9 | 操作キー        |    |

| 9 6 1 0 | リモコン操作機     |    |

| 9 7 0 0 | デジタルフォトフレーム |    |

| 9 7 0 1 | 筐体          | 10 |

| 9 7 0 3 | 表示部         |    |

| 9 8 8 1 | 筐体          |    |

| 9 8 8 2 | 表示部         |    |

| 9 8 8 3 | 表示部         |    |

| 9 8 8 4 | スピーカ部       |    |

| 9 8 8 5 | 操作キー        |    |

| 9 8 8 6 | 記録媒体挿入部     |    |

| 9 8 8 7 | 接続端子        |    |

| 9 8 8 8 | センサ         |    |

| 9 8 8 9 | マイクロフォン     |    |

| 9 8 9 0 | L E Dランプ    |    |

| 9 8 9 1 | 筐体          | 20 |

| 9 8 9 3 | 連結部         |    |

【図1】

【図2】

【 义 3 】

【 図 4 】

【 図 5 】

【図6】

【図7】

【 図 8 】

【 図 9 】

【 図 1 0 】

(B)

9700

9701

9703

【図 1-1】

【図12】

【図14】

【図13】

---

フロントページの続き

(51)Int.Cl.

F I

|        |        |         |

|--------|--------|---------|

| H 01 L | 29/78  | 6 1 2 B |

| H 01 L | 21/316 | X       |

| H 01 L | 21/316 | Y       |

| H 01 L | 21/318 | C       |

| H 01 L | 21/318 | B       |

| C 23 C | 14/08  |         |

審査官 山口 大志

(56)参考文献 特開2009-099953 (JP, A)

特開2002-175053 (JP, A)

特開2007-123861 (JP, A)

米国特許出願公開第2007/0072439 (US, A1)

国際公開第2009/041713 (WO, A1)

国際公開第2009/034953 (WO, A1)

特開2007-073559 (JP, A)

特開2009-176865 (JP, A)

国際公開第2009/093722 (WO, A1)

特開2008-281988 (JP, A)

国際公開第2008/126879 (WO, A1)

特開2003-273228 (JP, A)

米国特許出願公開第2009/0206332 (US, A1)

米国特許出願公開第2009/0155940 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 786

C 23 C 14 / 08

H 01 L 21 / 316

H 01 L 21 / 318

H 01 L 21 / 336