(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-124266

(P2008-124266A)

(43) 公開日 平成20年5月29日(2008.5.29)

| (51) Int.Cl.                  | F 1        |      | テーマコード (参考) |

|-------------------------------|------------|------|-------------|

| <b>H01L 29/786 (2006.01)</b>  | H01L 29/78 | 612B | 2H092       |

| <b>H01L 27/08 (2006.01)</b>   | H01L 27/08 | 331E | 5FO48       |

| <b>H01L 21/8234 (2006.01)</b> | H01L 27/08 | 102C | 5F110       |

| <b>H01L 27/088 (2006.01)</b>  | H01L 29/78 | 618Z | 5F152       |

| <b>H01L 21/336 (2006.01)</b>  | H01L 29/78 | 617L |             |

審査請求 未請求 請求項の数 17 O L (全 31 頁) 最終頁に続く

|           |                              |          |                                                          |

|-----------|------------------------------|----------|----------------------------------------------------------|

| (21) 出願番号 | 特願2006-306853 (P2006-306853) | (71) 出願人 | 502356528<br>株式会社 日立ディスプレイズ<br>千葉県茂原市早野3300番地            |

| (22) 出願日  | 平成18年11月13日 (2006.11.13)     | (74) 代理人 | 100083552<br>弁理士 秋田 収喜                                   |

|           |                              | (72) 発明者 | 野田 剛史<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内               |

|           |                              | (72) 発明者 | 賀茂 尚広<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内               |

|           |                              | (72) 発明者 | 新本 秀明<br>東京都千代田区外神田一丁目18番13号<br>株式会社日立製作所モノづくり技術事業<br>部内 |

最終頁に続く

(54) 【発明の名称】表示装置および表示装置の製造方法

## (57) 【要約】

【課題】 半導体層がアモルファス半導体のMISトランジスタと、半導体層が多結晶半導体のMISトランジスタが形成された表示装置において、各MISトランジスタをボトムゲート構造にしたときに多結晶半導体である半導体層の結晶性をよくする。

【解決手段】 基板の第1の領域に形成された第1のMISトランジスタ、および前記第1の領域とは異なる第2の領域に形成された第2のMISトランジスタは、それぞれ、前記基板と前記半導体層の間にゲート電極を有し、前記第1のMISトランジスタは、前記半導体層がアモルファス半導体であり、前記第2のMISトランジスタは、前記半導体層が多結晶半導体であり、前記第2のMISトランジスタのゲート電極は、前記第1のMISトランジスタのゲート電極よりも薄い表示装置。

【選択図】 図4(c)

**【特許請求の範囲】****【請求項 1】**

基板の上に導電層、絶縁層、および半導体層を積層して形成されたMISトランジスタを有する表示装置であって、

前記基板の第1の領域に形成された第1のMISトランジスタ、および前記第1の領域とは異なる第2の領域に形成された第2のMISトランジスタは、それぞれ、前記基板と前記半導体層の間にゲート電極を有し、

前記第1のMISトランジスタは、前記半導体層がアモルファス半導体でなり、前記第2のMISトランジスタは、前記半導体層が多結晶半導体でなり、

前記第2のMISトランジスタのゲート電極は、前記第1のMISトランジスタのゲート電極よりも薄いことを特徴とする表示装置。 10

**【請求項 2】**

前記第1のMISトランジスタのゲート電極は、前記第2のMISトランジスタのゲート電極よりも配線抵抗が低いことを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

前記第2のMISトランジスタのゲート電極は、前記第1のMISトランジスタのゲート電極よりも熱伝導率が低いことを特徴とする請求項1または請求項2に記載の表示装置。

**【請求項 4】**

前記第1のMISトランジスタのゲート電極と、前記第2のMISトランジスタのゲート電極とは、導電層の積層構成が異なることを特徴とする請求項1乃至請求項3のいずれか1項に記載の表示装置。 20

**【請求項 5】**

前記第1のMISトランジスタのゲート電極は、前記第2のMISトランジスタのゲート電極の導電層の積層構成に加え、1層以上の導電層を有することを特徴とする請求項4に記載の表示装置。

**【請求項 6】**

前記第1のMISトランジスタのゲート電極と、前記第2のMISトランジスタのゲート電極とは、導電層の積層構成が同じであることを特徴とする請求項1または請求項2に記載の表示装置。 30

**【請求項 7】**

前記第1の領域は、映像または画像を表示する表示領域であり、前記第2の領域は、前記表示領域の外側にある駆動回路が設けられた領域であることを特徴とする請求項1乃至請求項6のいずれか1項に記載の表示装置。

**【請求項 8】**

前記第1のMISトランジスタの前記ゲート電極と同一の積層構成であり、かつ、前記第1のMISトランジスタの前記ゲート電極と一体的に形成された走査信号線を有することを特徴とする請求項7に記載の表示装置。

**【請求項 9】**

絶縁基板と、前記絶縁基板の上の第1の領域に形成され、半導体層としてアモルファス半導体を用いた第1のMISトランジスタと、前記絶縁基板の上の第2の領域に形成され、半導体層として多結晶半導体を用いた第2のMISトランジスタとを有する表示装置の製造方法であって、 40

前記絶縁基板の上にゲート電極を形成する工程と、

前記ゲート電極を覆うゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の上にアモルファス半導体膜を成膜する工程と、

前記第1の領域および前記第2の領域のうちの、前記第2の領域のアモルファス半導体膜のみを溶融、結晶化させて多結晶半導体膜に改質する工程とを有し、

前記ゲート電極を形成する工程は、

前記第1の領域および前記第2の領域に第1の導電層を形成する第1の工程と、 50

前記第1の領域および前記第2の領域のうちの、前記第1の領域のみに第2の導電層を形成する第2の工程とを有するとともに、

前記第1の導電層と前記第2の導電層とを有する前記第1のMISトランジスタのゲート電極と、前記第1の導電層を有し、膜厚が前記第1のMISトランジスタのゲート電極よりも薄い前記第2のMISトランジスタのゲート電極とを形成する工程であることを特徴とする表示装置の製造方法。

#### 【請求項10】

前記第2の工程は、前記第1の工程の後で行われ、

前記第2の工程は、前記第1の領域および前記第2の領域に前記第2の導電層を形成した後、前記第2の領域にある前記第2の導電層を除去することを特徴とする請求項9に記載の表示装置の製造方法。 10

#### 【請求項11】

前記第2の工程は、前記第1の工程の前に行われ、

前記第2の工程は、前記第1の領域および前記第2の領域に前記第2の導電層を形成した後、前記第2の領域にある前記第2の導電層を除去することを特徴とする請求項9に記載の表示装置の製造方法。 20

#### 【請求項12】

前記第1の導電層と前記第2の導電層とは、同じ材料であることを特徴とする請求項9乃至請求項11のいずれか1項に記載の表示装置の製造方法。

#### 【請求項13】

前記第1の導電層と前記第2の導電層とは、異なる材料であり、

前記第1の導電層は、前記第2の導電層よりも熱伝導率が低い材料で形成することを特徴とする請求項9乃至請求項11のいずれか1項に記載の表示装置の製造方法。 30

#### 【請求項14】

前記第2の導電層は、前記第1の導電層よりも配線抵抗が低い材料で形成することを特徴とする請求項9乃至請求項11のいずれか1項に記載の表示装置の製造方法。

#### 【請求項15】

前記絶縁基板の上に、前記第1の導電層および前記第2の導電層を続けて形成する工程と、

前記第2の導電層を覆って、前記第2のMISトランジスタの前記ゲート電極を形成する領域における厚さが0より大きく、かつ、前記第1のMISトランジスタの前記ゲート電極を形成する領域における厚さよりも薄い第1のレジスト膜を形成する工程と、 30

前記第1のレジスト膜をマスクにして前記第1の導電層および前記第2の導電層を除去する工程と、

前記第1のレジスト膜を薄くして、前記第2のMISトランジスタの前記ゲート電極を形成する前記領域における厚さが0であり、かつ、前記第1のMISトランジスタの前記ゲート電極を形成する前記領域における厚さが0より大きい状態の第2のレジスト膜にする工程と、

前記第2のレジスト膜をマスクにして前記第2のMISトランジスタの前記ゲート電極を形成する前記領域における前記第2の導電層を除去する工程とを有することを特徴とする請求項9に記載の表示装置の製造方法。 40

#### 【請求項16】

前記第1の領域は、映像または画像を表示する表示領域であり、前記第2の領域は、前記表示領域の外側にある駆動回路が設けられた領域であることを特徴とする請求項9乃至請求項15のいずれか1項に記載の表示装置の製造方法。

#### 【請求項17】

前記第1のMISトランジスタの前記ゲート電極と同一の積層構成であり、かつ、前記第1のMISトランジスタの前記ゲート電極と一体的に形成された走査信号線を有することを特徴とする請求項16に記載の表示装置の製造方法。

#### 【発明の詳細な説明】

**【技術分野】****【0001】**

本発明は、表示装置および表示装置の製造方法に関し、特に、表示領域および表示領域の外側の周辺領域にMISトランジスタが形成された表示装置に適用して有効な技術に関するものである。

**【背景技術】****【0002】**

従来、液晶表示装置には、アクティブマトリクス型と呼ばれる液晶表示装置がある。前記アクティブマトリクス型液晶表示装置は、一対の基板の間に液晶材料を封入した液晶表示パネルを有し、前記一対の基板のうちの一方の基板（以下、TFT基板という）の表示領域に、アクティブ素子（スイッチング素子とも呼ばれる）として用いるTFT素子（MOSトランジスタを含むMISトランジスタ）がマトリクス状に配置されている。

10

**【0003】**

前記液晶表示パネルの前記TFT基板は、複数本の走査信号線および複数本の映像信号線を有し、前記TFT素子のゲート電極は走査信号線に接続されており、ドレイン電極またはソース電極のいずれか一方は映像信号線に接続されている。

**【0004】**

また、従来の液晶表示装置において、前記TFT基板の前記複数本の映像信号線は、たとえば、データドライバと呼ばれるドライバICチップが実装されたTCPまたはCOFなどの半導体パッケージに接続されており、前記TFT基板の前記複数本の走査信号線は、たとえば、走査ドライバまたはゲートドライバと呼ばれるドライバICチップが実装されたTCPまたはCOFなどの半導体パッケージに接続されている。また、液晶表示装置の種類によっては、前記各ドライバICチップを前記TFT基板に直接実装していることもある。

20

**【0005】**

またさらに、近年の液晶表示装置では、前記各ドライバICチップを用いる代わりに、TFT基板の表示領域の外側（以下、周辺領域という）に、前記各ドライバICチップと同等の機能を有する駆動回路を直接形成する方法も提案されている。

**【0006】**

前記TFT基板の前記周辺領域に駆動回路を直接形成する場合、たとえば、駆動回路を構成する多数のMOSトランジスタの構成を、表示領域のTFT素子と同じ構成にすれば、表示領域のTFT素子と一緒に駆動回路のMOSトランジスタも形成することができる。

30

**【0007】**

しかしながら、前記駆動回路のMOSトランジスタは、表示領域のTFT素子に比べて高速で動作をさせる必要がある。そのため、前記駆動回路のMOSトランジスタの半導体層は、キャリアの移動度が高い多結晶シリコンで形成することが望ましい。

**【0008】**

前記駆動回路のMOSトランジスタの半導体層を多結晶シリコンで形成する場合、たとえば、基板の全面にアモルファスシリコン膜を成膜した後、該アモルファスシリコン膜にエキシマレーザまたは連続発振レーザなどのエネルギービームを照射して溶融、結晶化させてアモルファスシリコン膜を多結晶シリコン化した後、パターニングして形成する。

40

**【0009】**

このとき、たとえば、表示領域のアモルファスシリコンも同時に多結晶シリコン化すれば、表示領域のTFT素子の半導体層も多結晶シリコンで形成することができるが、液晶テレビなどの大型の表示装置に用いられる大面積のTFT基板の場合、その全面にレーザを照射するには多大なエネルギーが必要であるとともに、多結晶シリコン化に要する時間が長くなり、TFT基板の生産性が悪くなる。

**【0010】**

そのため、最近では、たとえば、基板の全面に成膜したアモルファスシリコン膜のうち

50

、高速で動作（駆動）させる駆動回路のMOSトランジスタを形成する領域のみにレーザなどのエネルギー ビームを照射して多結晶シリコン化する方法が提案されている（たとえば、特許文献1を参照。）。この方法だと、たとえば、表示領域のTFT素子の半導体層はアモルファスシリコンで形成され、駆動回路のMOSトランジスタは多結晶シリコンで形成される。

【特許文献1】特開2003-124136号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

ところで、上記のように、前記表示領域のTFT素子の半導体層をアモルファスシリコンで形成する場合、そのTFT素子は、ガラス基板などの絶縁基板と半導体層の間にゲート電極を有する構造（以下、ボトムゲート構造という）にすることが望ましい。このとき、TFT基板の生産性をよくするには、周辺領域の駆動回路のMOSトランジスタも、ボトムゲート構造にすることが望ましい。

【0012】

しかしながら、周辺領域の駆動回路のMOSトランジスタをボトムゲート構造にする場合、半導体層を形成する工程においてアモルファスシリコンを多結晶シリコン化するときに、たとえば、以下のようないわゆる問題が生じる。

【0013】

まず、ゲート電極に用いる材料は熱伝導率が高いので、連続発振レーザなどを照射したときに、ゲート電極の上にあるアモルファスシリコンを溶融、結晶化するのに必要なエネルギーが、ゲート電極のない部分に比べて増大する。そのため、照射するビームのエネルギーを大きくする必要があり、生産性が低下するという問題がある。

【0014】

また、ボトムゲート構造のTFT素子（MOSトランジスタ）の半導体層は、ゲート電極と平面でみて重なる部分をチャネル領域として使い、その外側の部分をドレイン領域およびソース領域として使うので、1つの半導体層に着目した場合、各部分（領域）の結晶性が揃っていることが望ましい。しかしながら、ゲート電極の熱伝導の影響で、ゲート電極上のチャネル領域と、その外側のドレイン領域およびソース領域で結晶性を揃えることは困難であるという問題がある。このとき、たとえば、ゲート電極上の半導体膜において所望の結晶粒を得られるようにレーザのエネルギーを設定すると、それ以外の部分では、エネルギーが大きすぎて半導体膜がアブレーションを引き起こすこともある。またさらに、ゲート電極上の半導体膜には、ゲート電極の端部上と中央部上とで結晶性が異なるという問題も発生する。このように、ゲート電極の熱伝導の影響により、ゲート電極上とそれ以外とで、同等の結晶粒を得られるエネルギー範囲は狭くなり、製造が困難になる。

【0015】

また、ボトムゲート構造のTFT素子の場合、ゲート電極の膜厚は、そのまま半導体層の段差となる。そのため、たとえば、連続発振レーザによる多結晶シリコン化のように半導体層の溶融時間が長いと、溶融したシリコンが段差の上から下に移動し、段差部分で膜剥れを引き起こしやすいという問題もある。

【0016】

また、ゲート電極の熱伝導の影響を小さくする手法として、たとえば、ゲート電極の膜厚を薄くする方法が有効であることが知られている。しかしながら、この方法では、表示領域のTFT素子のゲート電極や走査信号線の配線抵抗が高くなり、消費電力の増大や画素部の信号遅延による不良を招きやすいという問題がある。

【0017】

また、アモルファスシリコンを多結晶シリコン化している間、ゲート電極は高温になるので、前記駆動回路のMOSトランジスタをボトムゲート構造にする場合、ゲート電極には、たとえば、Mo（モリブデン）、W（タンゲステン）、Cr（クロム）、Ta（タングタル）、MoW合金などの高融点材料を使う必要がある。しかしながら、これらの高融点

10

20

30

40

50

材料は、A1（アルミニウム）などと比較すると電気抵抗が高いので、膜厚を薄くすると、配線抵抗の高さがより目立ってしまうと言う問題がある。

【0018】

またさらに、ゲート電極の熱伝導の影響を小さくする手法として、ゲート電極を薄くする手法以外に、たとえば、ゲート絶縁膜を厚くするという手法がある。しかしながら、この方法では、トランジスタ特性のうちの $I_{ON}$ の低下、 $V_{th}$ のばらつきが大きくなりやすく、回路動作を困難にするなどの問題があるため、必ずしも有効な手法とはいえない。

【0019】

本発明の目的は、たとえば、半導体層がアモルファスシリコンのMOSトランジスタと、半導体層が多結晶シリコンのMOSトランジスタが形成された表示装置において、各MOSトランジスタをボトムゲート構造にしたときに多結晶シリコンでなる半導体層の結晶性をよくすることが可能な技術を提供することにある。

10

【0020】

本発明の他の目的は、たとえば、半導体層がアモルファスシリコンのMOSトランジスタと、半導体層が多結晶シリコンのMOSトランジスタが形成された表示装置において、各MOSトランジスタをボトムゲート構造にしたときの生産性および製造歩留まりを向上させることが可能な技術を提供することにある。

20

【0021】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面によって明らかになるであろう。

【課題を解決するための手段】

【0022】

本願において開示される発明のうち、代表的なものの概略を説明すれば、以下の通りである。

【0023】

(1) 基板の上に導電層、絶縁層、および半導体層を積層して形成されたMISトランジスタを有する表示装置であって、前記基板の第1の領域に形成された第1のMISトランジスタ、および前記第1の領域とは異なる第2の領域に形成された第2のMISトランジスタは、それぞれ、前記基板と前記半導体層の間にゲート電極を有し、前記第1のMISトランジスタは、前記半導体層がアモルファス半導体でなり、前記第2のMISトランジスタは、前記半導体層が多結晶半導体でなり、前記第2のMISトランジスタのゲート電極は、前記第1のMISトランジスタのゲート電極よりも薄い表示装置。

30

【0024】

(2) 前記(1)の表示装置において、前記第1のMISトランジスタのゲート電極は、前記第2のMISトランジスタのゲート電極よりも配線抵抗が低い表示装置。

【0025】

(3) 前記(2)の表示装置において、前記第2のMISトランジスタのゲート電極は、前記第1のMISトランジスタのゲート電極よりも熱伝導率が低い表示装置。

40

【0026】

(4) 前記(1)乃至(3)のいずれかの表示装置において、前記第1のMISトランジスタのゲート電極と、前記第2のMISトランジスタのゲート電極とは、導電層の積層構成が異なる表示装置。

【0027】

(5) 前記(4)の表示装置において、前記第1のMISトランジスタのゲート電極は、前記第2のMISトランジスタのゲート電極の導電層の積層構成に加え、1層以上の導電層を有する表示装置。

【0028】

(6) 前記(1)または(2)の表示装置において、前記第1のMISトランジスタのゲート電極と、前記第2のMISトランジスタのゲート電極とは、導電層の積層構成が同じである表示装置。

50

**【 0 0 2 9 】**

( 7 ) 前記 ( 1 ) 乃至 ( 6 ) のいずれかの表示装置において、前記第 1 の領域は、映像または画像を表示する表示領域であり、前記第 2 の領域は、前記表示領域の外側にある駆動回路が設けられた領域である表示装置。

**【 0 0 3 0 】**

( 8 ) 前記 ( 7 ) の表示装置において、前記第 1 の M I S トランジスタの前記ゲート電極と同一の積層構成であり、かつ、前記第 1 の M I S トランジスタの前記ゲート電極と一体的に形成された走査信号線を有する表示装置。

**【 0 0 3 1 】**

( 9 ) 絶縁基板と、前記絶縁基板の上の第 1 の領域に形成され、半導体層としてアモルファス半導体を用いた第 1 の M I S トランジスタと、前記絶縁基板の上の第 2 の領域に形成され、半導体層として多結晶半導体を用いた第 2 の M I S トランジスタとを有する表示装置の製造方法であって、前記絶縁基板の上にゲート電極を形成する工程と、前記ゲート電極を覆うゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の上にアモルファス半導体膜を成膜する工程と、前記第 1 の領域および前記第 2 の領域のうちの、前記第 2 の領域のアモルファス半導体膜のみを溶融、結晶化させて多結晶半導体膜に改質する工程とを有し、前記ゲート電極を形成する工程は、前記第 1 の領域および前記第 2 の領域に第 1 の導電層を形成する第 1 の工程と、前記第 1 の領域および前記第 2 の領域のうちの、前記第 1 の領域のみに第 2 の導電層を形成する第 2 の工程とを有するとともに、前記第 1 の導電層と前記第 2 の導電層とを有する前記第 1 の M I S トランジスタのゲート電極と、前記第 1 の導電層を有し、膜厚が前記第 1 の M I S トランジスタのゲート電極よりも薄い前記第 2 の M I S トランジスタのゲート電極とを形成する工程である表示装置の製造方法。10

**【 0 0 3 2 】**

( 10 ) 前記 ( 9 ) の表示装置の製造方法において、前記第 2 の工程は、前記第 1 の工程の後で行われ、前記第 2 の工程は、前記第 1 の領域および前記第 2 の領域に前記第 2 の導電層を形成した後、前記第 2 の領域にある前記第 2 の導電層を除去する表示装置の製造方法。20

**【 0 0 3 3 】**

( 11 ) 前記 ( 9 ) の表示装置の製造方法において、前記第 2 の工程は、前記第 1 の工程の前に行われ、前記第 2 の工程は、前記第 1 の領域および前記第 2 の領域に前記第 2 の導電層を形成した後、前記第 2 の領域にある前記第 2 の導電層を除去する表示装置の製造方法。30

**【 0 0 3 4 】**

( 12 ) 前記 ( 9 ) 乃至 ( 11 ) のいずれかの表示装置の製造方法において、前記第 1 の導電層と前記第 2 の導電層とは、同じ材料である表示装置の製造方法。

**【 0 0 3 5 】**

( 13 ) 前記 ( 9 ) 乃至 ( 11 ) のいずれかの表示装置の製造方法において、前記第 1 の導電層と前記第 2 の導電層とは、異なる材料であり、前記第 1 の導電層は、前記第 2 の導電層よりも熱伝導率が低い材料で形成する表示装置の製造方法。

**【 0 0 3 6 】**

( 14 ) 前記 ( 9 ) 乃至 ( 11 ) のいずれかの表示装置の製造方法において、前記第 2 の導電層は、前記第 1 の導電層よりも配線抵抗が低い材料で形成する表示装置の製造方法。40

**【 0 0 3 7 】**

( 15 ) 前記 ( 9 ) の表示装置の製造方法において、前記絶縁基板の上に、前記第 1 の導電層および前記第 2 の導電層を続けて形成する工程と、前記第 2 の導電層を覆って、前記第 2 の M I S トランジスタの前記ゲート電極を形成する領域における厚さが 0 より大きく、かつ、前記第 1 の M I S トランジスタの前記ゲート電極を形成する領域における厚さよりも薄い第 1 のレジスト膜を形成する工程と、前記第 1 のレジスト膜をマスクにして前記第 1 の導電層および前記第 2 の導電層を除去する工程と、前記第 1 のレジスト膜を薄く50

して、前記第2のMISトランジスタの前記ゲート電極を形成する前記領域における厚さが0であり、かつ、前記第1のMISトランジスタの前記ゲート電極を形成する前記領域における厚さが0より大きい状態の第2のレジスト膜にする工程と、前記第2のレジスト膜をマスクにして前記第2のMISトランジスタの前記ゲート電極を形成する前記領域における前記第2の導電層を除去する工程とを有する表示装置の製造方法。

#### 【0038】

(16) 前記(9)乃至(15)のいずれかの表示装置の製造方法において、前記第1の領域は、映像または画像を表示する表示領域であり、前記第2の領域は、前記表示領域の外側にある駆動回路が設けられた領域である表示装置の製造方法。

#### 【0039】

(17) 前記(16)の表示装置の製造方法において、前記第1のMISトランジスタの前記ゲート電極と同一の積層構成であり、かつ、前記第1のMISトランジスタの前記ゲート電極と一体的に形成された走査信号線を有する表示装置の製造方法。

#### 【発明の効果】

#### 【0040】

本発明の表示装置およびその製造方法によれば、たとえば、半導体層がアモルファスシリコンの第1のMISトランジスタと、半導体層が多結晶シリコンの第2のMISトランジスタとが、ともにボトムゲート構造であっても、第2のMISトランジスタの半導体層(多結晶シリコン)の結晶性をよくすることができる。そのため、第2のMISトランジスタを用いて形成される第2の領域の駆動回路の動作特性を向上できるとともに、第1のMISトランジスタの動作特性の低下を防ぐことができる。

#### 【0041】

また、本発明の表示装置の製造方法によれば、表示装置の生産性および製造歩留まりを向上させることできる。

#### 【発明を実施するための最良の形態】

#### 【0042】

以下、本発明について、図面を参照して実施の形態(実施例)とともに詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは、同一符号を付け、その繰り返しの説明は省略する。

#### 【0043】

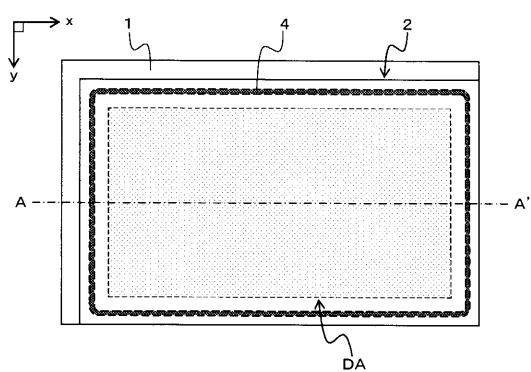

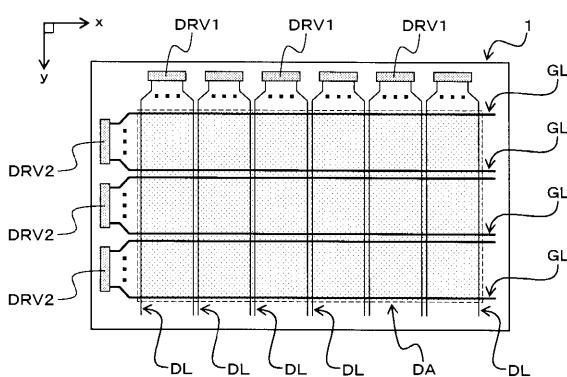

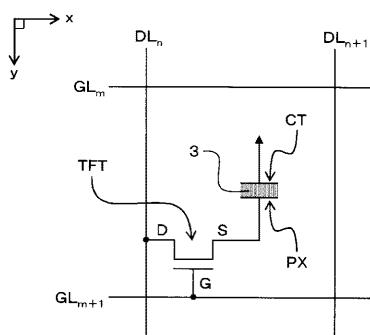

図1(a)乃至図3は、本発明に関わる表示パネル(表示装置)の概略構成の一例を示す模式図である。

図1(a)は、液晶表示パネルの概略構成の一例を示す模式平面図である。図1(b)は、図1(a)に示した液晶表示パネルのA-A'線における断面構成の一例を示す模式断面図である。図2は、本発明の適用が望まれるTFT基板の概略構成の一例を示す模式平面図である。図3は、液晶表示パネルの1画素の回路構成の一例を示す模式回路図である。

#### 【0044】

本発明は、たとえば、液晶テレビ、パソコンコンピュータ(PC)向けの液晶ディスプレイなどの液晶表示装置に用いるアクティブマトリクス型液晶表示パネル(以下、単に液晶表示パネルという)に適用される。

#### 【0045】

液晶表示パネルは、たとえば、図1(a)および図1(b)に示すように、第1の基板1および第2の基板2の2枚(一対)の基板の間に液晶材料3が封入されている表示パネルである。このとき、第1の基板1と第2の基板2は、映像や画像などを表示する表示領域DAの外側に設けられた環状のシール材4で接着されており、液晶材料3は、第1の基板1および第2の基板2ならびにシール材4で囲まれた空間に封入されている。また、液晶表示パネルが透過型または半透過型の場合、第1の基板1および第2の基板2の外側を向いた面には、たとえば、偏光板5A, 5Bが貼り付けられている。またこのとき、第1

10

20

30

40

50

の基板 1 と偏光板 5 A の間、第 2 の基板 2 と偏光板 5 B の間には、1 層から数層の位相差板が設けられていることもある。

#### 【 0 0 4 6 】

液晶表示パネルの第 1 の基板 1 は、一般に、TFT 基板と呼ばれており、ガラス基板などの絶縁基板の上に、複数本の走査信号線、複数本の映像信号線、表示領域 DA を構成する複数の画素のそれぞれに対して配置される TFT 素子（スイッチング素子）、および画素電極などが形成されている。

#### 【 0 0 4 7 】

第 1 の基板（以下、TFT 基板という）1 は、たとえば、図 2 に示すように、x 方向に長く延びる走査信号線 GL が y 方向に複数本並んでおり、y 方向に長く延びる映像信号線 DL が x 方向に複数本並んでいる。

10

#### 【 0 0 4 8 】

このような TFT 基板 1 では、2 本の隣接する走査信号線 GL と 2 本の隣接する映像信号線 DL で囲まれた領域が 1 つの画素領域に相当し、各画素領域に TFT 素子や画素電極などが配置されている。このとき、たとえば、図 3 に示すように、2 本の隣接する走査信号線 GL<sub>m</sub>, GL<sub>m+1</sub> と、2 本の隣接する映像信号線 DL<sub>n</sub>, DL<sub>n+1</sub> とで囲まれた領域を画素領域とする画素に着目すると、その画素に対して配置される TFT 素子は、ゲート（G）が 2 本の隣接する走査信号線 GL<sub>m</sub>, GL<sub>m+1</sub> のうちの一方の走査信号線 GL<sub>m+1</sub> に接続されている。またこのとき、当該 TFT 素子は、たとえば、ドレイン（D）が 2 本の隣接する映像信号線 DL<sub>n</sub>, DL<sub>n+1</sub> のうちの一方の映像信号線 DL<sub>n</sub> に接続されており、ソース（S）が画素電極 PX に接続されている。また、画素電極 PX は、共通電極 CT（対向電極とも呼ばれる）および液晶材料 3 とともに画素容量を形成している。なお、共通電極 CT は、対向基板 2 に設けられている場合もあるし、TFT 基板 1 に設けられている場合もある。

20

#### 【 0 0 4 9 】

また、本発明は、たとえば、図 2 に示すように、表示領域 DA の外側に、第 1 の駆動回路DRV 1 および第 2 の駆動回路DRV 2 が、内蔵回路として前記絶縁基板上に一体的に形成されている TFT 基板 1 への適用が望まれる。第 1 の駆動回路DRV 1 および第 2 の駆動回路DRV 2 はそれぞれ、MOS ドラゴンジスタやダイオードなどの半導体素子を多数個組み合わせた集積回路であり、TFT 基板 1 の製造過程において、走査信号線 GL、映像信号線 DL、表示領域 DA の TFT 素子などとともに形成される。以下、第 1 の駆動回路DRV 1 および第 2 の駆動回路DRV 2 の MOS ドラゴンジスタを、周辺領域の MOS ドラゴンジスタという。

30

#### 【 0 0 5 0 】

第 1 の駆動回路DRV 1 は、たとえば、従来の液晶表示装置で用いられているチップ状のデータドライバ IC と同等の機能を有する回路であり、たとえば、各映像信号線 DL に加える映像信号（階調データ）を生成する回路、生成した映像信号を各映像信号線 DL に出力するタイミングを制御する回路などを有する。また、第 2 の駆動回路DRV 2 は、従来の液晶表示装置で用いられているチップ状の走査ドライバ IC と同等の機能を有する回路であり、たとえば、各走査信号線 GL に加える走査信号を生成する回路、生成した走査信号を各走査信号線 GL に出力するタイミングを制御する回路などを有する。

40

#### 【 0 0 5 1 】

またこのとき、第 1 の駆動回路DRV 1 および第 2 の駆動回路DRV 2 は、シール材 4 よりも内側、すなわちシール材 4 と表示領域 DA の間に形成することが望ましいが、シール材 4 と平面でみて重なる領域やシール材 4 の外側に形成されていてもよい。

#### 【 0 0 5 2 】

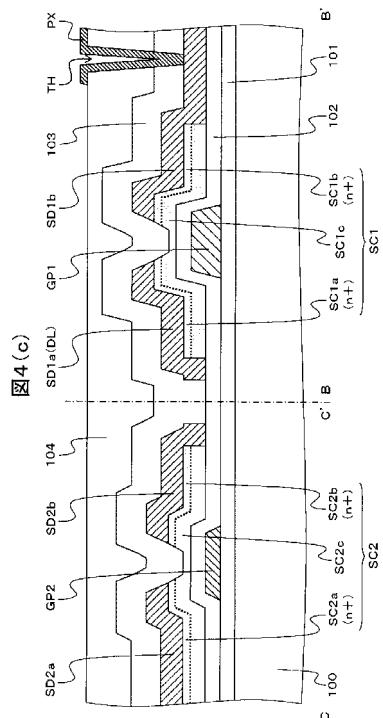

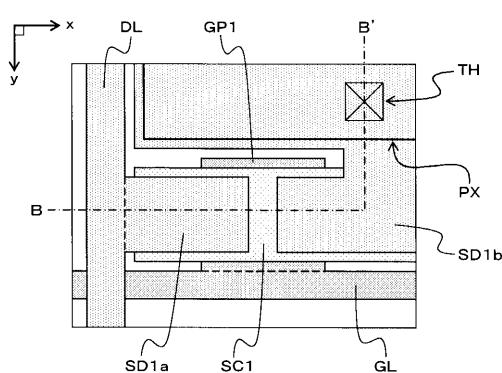

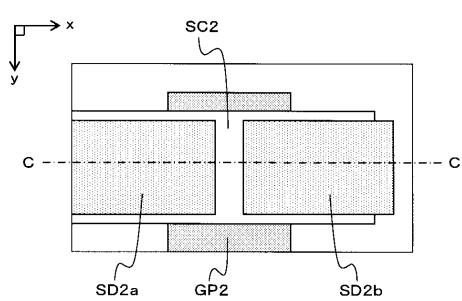

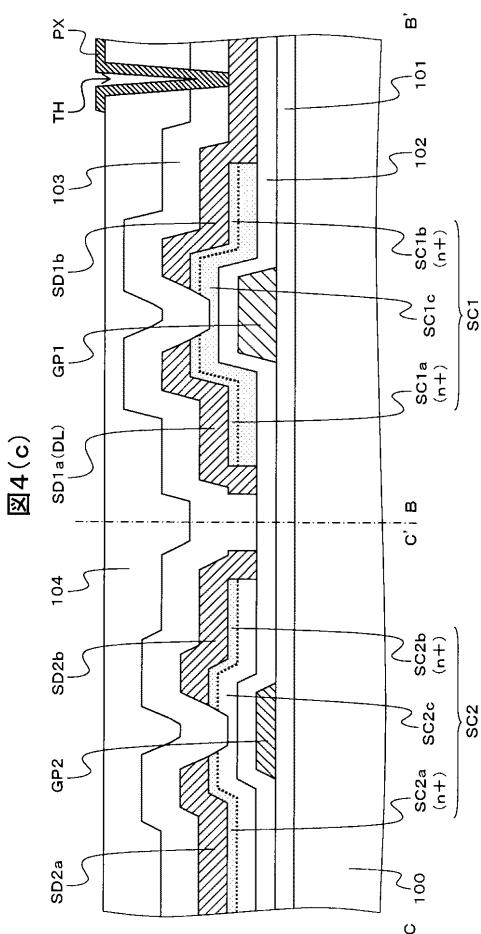

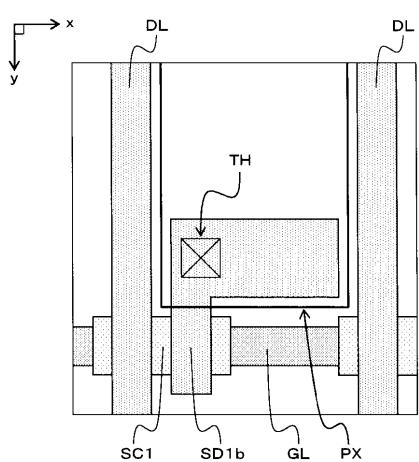

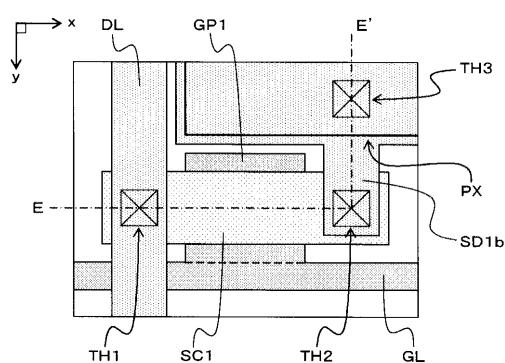

図 4 (a) 乃至図 4 (c) は、本発明の概要を説明するための模式図である。

図 4 (a) は、本発明を適用した TFT 基板における表示領域の TFT 素子の概略構成の一例を示す模式平面図である。図 4 (b) は、本発明を適用した TFT 基板における周辺回路の MOS ドラゴンジスタの概略構成の一例を示す模式平面図である。図 4 (c) は、

50

図4(a)のB-B'線における断面構成の一例および図4(b)のC-C'線における断面構成の一例を横に並べて示した模式断面図である。なお、図4(c)において、(n+)は高濃度のn型不純物領域であることを示している。

#### 【0053】

本発明は、図2および図3に示したような構成のTFT基板1において、表示領域DAのTFT素子(MOSトランジスタ)や、周辺領域のMOSトランジスタをボトムゲート型と呼ばれる構成、すなわち、ガラス基板などの基板と半導体層の間に各トランジスタのゲート電極が設けられている構成にする場合に適用される。

#### 【0054】

このとき、表示領域DAの各画素に対して配置されるMOSトランジスタ(TFT素子)は、たとえば、図4(a)および図4(c)に示すような構成になっており、ガラス基板100の表面に形成された下地絶縁層101の上にゲート電極GP1が形成されている。ゲート電極GP1は、たとえば、走査信号線GLと一体であり、走査信号線GLの幅(y方向の寸法)を部分的に広くして設けた矩形状の突出部分を利用している。

#### 【0055】

また、ガラス基板100からみてゲート電極GP1の上には、TFT素子のゲート絶縁膜としての機能を有する第1の絶縁層102を介して半導体層SC1が形成されている。半導体層SC1は、ドレイン領域SC1a、ソース領域SC1b、およびチャネル領域SC1cの3つの領域からなり、3つの領域すべてがアモルファスシリコンなどのアモルファス半導体で形成されている。TFT素子がNチャネルMOSトランジスタの場合、半導体層SC1のドレイン領域SC1aおよびソース領域SC1bは、たとえば、不純物としてP<sup>+</sup>(リンイオン)を注入したn型のアモルファス半導体である。また、NチャネルMOSトランジスタの場合、チャネル領域SC1cは真性(i型)のアモルファス半導体、または不純物濃度が非常に低いn型のアモルファス半導体、もしくは不純物濃度が非常に低いp型のアモルファス半導体のうちのいずれか1つである。

#### 【0056】

また、ガラス基板100からみて半導体層SC1のドレイン領域SC1aの上にはドレイン電極SD1aが形成され、ソース領域SC1bの上にはソース電極SD1bが形成されている。ドレイン電極SD1aは、たとえば、映像信号線DLと一体であり、映像信号線DLの幅(x方向の寸法)を部分的に広くして設けた矩形状の突出部分を利用している。

#### 【0057】

また、ガラス基板100からみてドレイン電極SD1aおよびソース電極SD1bなどのさらに上には、第2の絶縁層103および第3の絶縁層104を介して画素電極PXが形成されている。画素電極PXは、スルーホールTHによりソース電極SD1bと接続している。

#### 【0058】

またこのとき、周辺領域のMOSトランジスタ、たとえば、第1の駆動回路DRV1のMOSトランジスタは、図4(b)および図4(c)に示したような構成になっており、ガラス基板100の表面に形成された下地絶縁層101の上にゲート電極GP2が形成されている。なお、本発明を適用したTFT基板1では、周辺領域のMOSトランジスタのゲート電極GP2の厚さが、表示領域DAのTFT素子のゲート電極GP1の厚さよりも薄くなっている。

#### 【0059】

また、ガラス基板100からみてゲート電極GP2の上には、第1の絶縁層102を介して半導体層SC2が形成されている。半導体層SC2は、ドレイン領域SC2a、ソース領域SC2b、およびチャネル領域SC2cの3つの領域からなり、ドレイン領域SC2aおよびソース領域SC2bはアモルファスシリコンなどのアモルファス半導体で形成されており、チャネル領域SC2cは多結晶シリコンなどの多結晶半導体で形成されている。周辺領域のMOSトランジスタがNチャネルMOSトランジスタの場合、半導体層S

10

20

30

40

50

C 2 のドレイン領域 S C 2 a およびソース領域 S C 2 b は、たとえば、不純物として P<sup>+</sup> (リンイオン) を注入した n 型のアモルファス半導体である。また、N チャネル MOS トランジスタの場合、チャネル領域 S C 2 c は真性 (i 型) の多結晶半導体、または不純物濃度が非常に低い n 型の多結晶半導体、もしくは不純物濃度が非常に低い p 型の多結晶半導体のうちのいずれか 1 つである。特に、半導体層 S C 2 のように多結晶シリコンで形成されている場合、チャネル領域 S C 2 c に不純物をわずかに加えることで、MOS トランジスタのしきい値の制御が可能になる。

#### 【0060】

また、ガラス基板 100 からみて半導体層 S C 2 のドレイン領域 S C 2 a の上にはドレイン電極 S D 2 a が形成され、ソース領域 S C 2 b の上にはソース電極 S D 2 b が形成されている。10

#### 【0061】

また、ガラス基板 100 からみてドレイン電極 S D 2 a およびソース電極 S D 2 b のさらに上には、第 2 の絶縁層 103 および第 3 の絶縁層 104 が形成されている。

#### 【0062】

本発明は、上記のように、表示領域 D A ( 第 1 の領域 ) の TFT 素子 ( MOS トランジスタ ) と、周辺領域 ( 第 2 の領域 ) の MOS トランジスタが、それぞれ、ガラス基板と半導体層の間にゲート電極を有するボトムゲート型であり、かつ、表示領域 D A の MOS トランジスタの半導体層 S C 1 の各領域をアモルファスシリコンなどのアモルファス半導体で形成し、周辺領域の MOS トランジスタの半導体層 S C 2 のチャネル領域 S C 2 c を多結晶シリコンなどの多結晶半導体で形成する場合に適用される。20

#### 【0063】

以下、本発明が適用された液晶表示装置の TFT 基板 1 における表示領域 D A および周辺領域 S A の各 MOS トランジスタのゲート電極 G P 1 , G P 2 の構成および製造方法について説明する。

#### 【実施例 1】

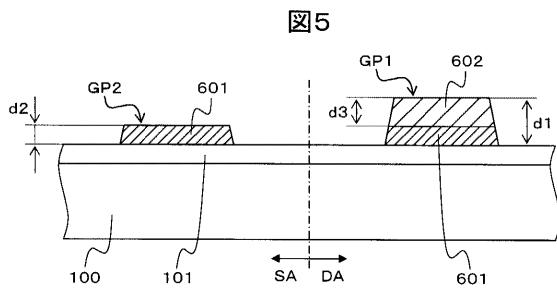

#### 【0064】

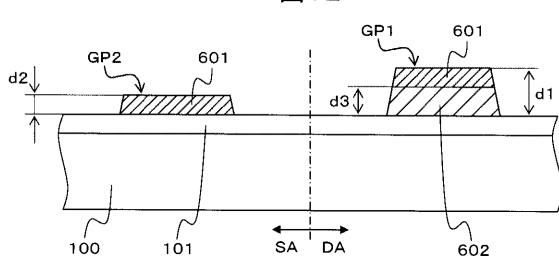

図 5 は、本発明による実施例 1 の TFT 基板の特徴を示す模式断面図である。なお、図 5 において、一点鎖線の右側は表示領域 D A に形成される TFT 素子 ( MOS トランジスタ ) のゲート電極 G P 1 の断面構成の一例を示しており、一点鎖線の左側は周辺領域 S A に形成される MOS トランジスタのゲート電極 G P 2 の断面構成の一例を示している。30

#### 【0065】

実施例 1 の TFT 基板 1 は、たとえば、図 5 に示すように、周辺領域 S A に配置された第 1 の駆動回路 D R V 1 などの MOS トランジスタのゲート電極 G P 2 の厚さ d 2 が、表示領域 D A の TFT 素子のゲート電極 G P 1 の厚さ d 1 よりも薄い。このとき、表示領域 D A の TFT 素子のゲート電極 G P 1 は、周辺領域 S A の MOS トランジスタのゲート電極 G P 2 に用いられている第 1 の導電層 601 の上に、厚さ d 3 の第 2 の導電層 602 が積層された構成になっている。

#### 【0066】

実施例 1 において、周辺領域 S A の MOS トランジスタのゲート電極 G P 2 および表示領域 D A の TFT 素子のゲート電極 G P 1 の下層に用いられている第 1 の導電層 601 と、表示領域 D A の TFT 素子のゲート電極 G P 1 のみに用いられている第 2 の導電層 602 は、同じ材料であってもよいし、異なる材料であってもよい。ただし、第 1 の導電層 601 の材料と第 2 の導電層 602 の材料との組み合わせは、第 1 の導電層 601 の材料の熱伝導率が第 2 の導電層 602 の材料の熱伝導率よりも低いことが望ましい。またこのとき、第 2 の導電層 602 の材料の電気抵抗 ( 配線抵抗 ) が第 1 の導電層 601 の材料の電気抵抗 ( 配線抵抗 ) よりも低い組み合わせであると、さらに望ましい。40

#### 【0067】

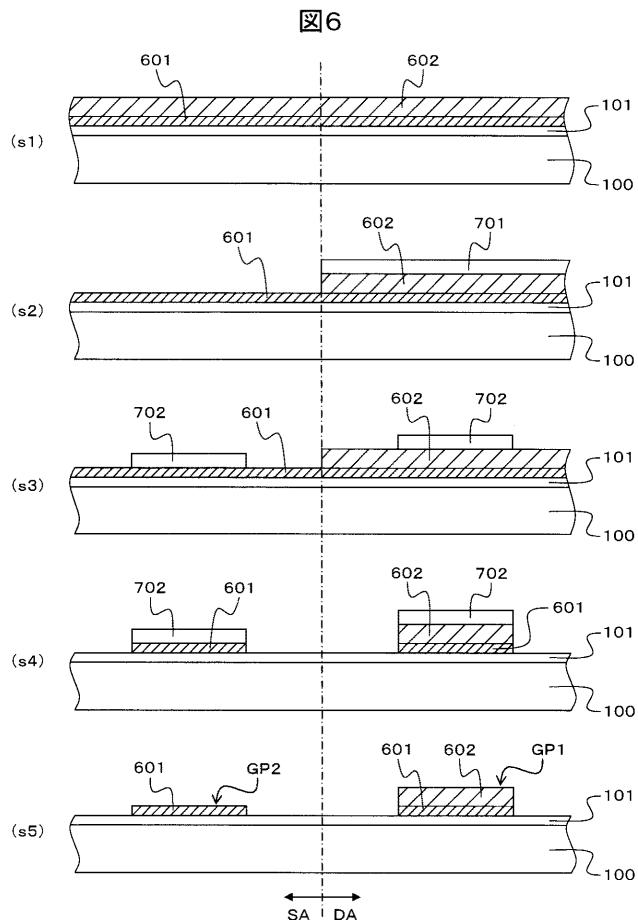

図 6 は、実施例 1 の TFT 基板のゲート電極の製造方法を説明するための模式断面図である。なお、図 6 には、ゲート電極を形成する手順において特徴となる部分のみを ( s 1

)から(s5)として示している。また、図6において、一点鎖線の右側は表示領域DAに形成されるTFT素子(MOSトランジスタ)のゲート電極GP1の形成手順を示しており、一点鎖線の左側は周辺領域SAに形成されるMOSトランジスタのゲート電極GP2の形成手順を示している。

#### 【0068】

実施例1のTFT基板1の製造方法において、表示領域DAのTFT素子のゲート電極GP1および周辺領域SAのMOSトランジスタのゲート電極GP2を形成する工程は、まず、図6の(s1)に示すように、ガラス基板100(絶縁基板)上に、たとえば、シリコン窒化膜(SiN膜)などの下地絶縁層101を成膜した後、第1の導電層601および第2の導電層602を続けて成膜する。

10

#### 【0069】

次に、図6の(s2)に示すように、第2の導電層602の上のうちの、表示領域DAの上のみにレジスト701を形成した後、そのレジスト701をマスクにしてエッチングを行い、表示領域DAの外側(周辺領域SAなど)にある第2の導電層602を除去する。

#### 【0070】

次に、レジスト701を除去した後、図6の(s3)に示すように、表示領域DAおよび周辺領域SAのゲート電極を形成する領域に別のレジスト702を形成する。

#### 【0071】

次に、図6の(s4)に示すように、レジスト702をマスクにしてエッチングを行い、表示領域DAは第2の導電層602および第1の導電層601の不要な部分を除去し、周辺領域SAは第1の導電層601の不要な部分を除去する。

20

#### 【0072】

その後、レジスト702を除去すると、図6の(s5)に示すように、表示領域DAには第1の導電層601および第2の導電層602が積層したゲート電極GP1が形成され、周辺領域SAには第1の導電層601のみからなる薄いゲート電極GP2が形成される。

#### 【0073】

なお、図6に示したような手順でゲート電極GP1, GP2を形成する場合、前記第1の導電層601および第2の導電層602は、同じ材料であってもよいが、異なる材料であるほうが望ましい。特に、周辺領域SAのMOSトランジスタのゲート電極GP2に用いる第1の導電層601は、半導体層SC2のチャネル領域SC2cに用いる多結晶シリコンを形成する工程で高温になるので、第1の導電層601には高融点金属材料を用いることが望ましい。

30

#### 【0074】

第1の導電層601および第2の導電層602に同じ材料を用いる場合、その材料としては、たとえば、MoW合金が挙げられる。しかしながら、第1の導電層601および第2の導電層602に同じ材料を用いた場合、図6の(s2)に示した工程、すなわち周辺領域SAにある第2の導電層602をエッチングするときに第2の導電層602のみを除去することが難しい。そのため、第1の導電層601の表面もエッチングされるおそれがあり、周辺領域SAのゲート電極GP2の平坦性が悪くなる可能性がある。

40

#### 【0075】

このことから、第1の導電層601には、たとえば、第2の導電層602よりも融点が高く、熱伝導率が低い材料を用いることが望ましい。また、第1の導電層601には、たとえば、第2の導電層602のエッチングに用いるエッチング液に対して不溶性または難溶性を示す材料を用いることが望ましい。またさらに、第1の導電層601は、たとえば、第2の導電層よりも電気伝導率が低い材料を用いることが望ましい。このような条件を満たす材料の組み合わせとしては、たとえば、第1導電層601をTa, Ti(チタン), MoWのいずれかにし、第2の導電層602をAl(アルミニウム)にする組み合わせがある。

50

## 【0076】

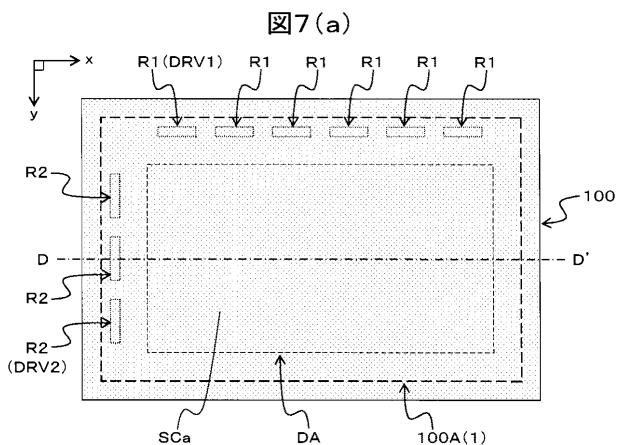

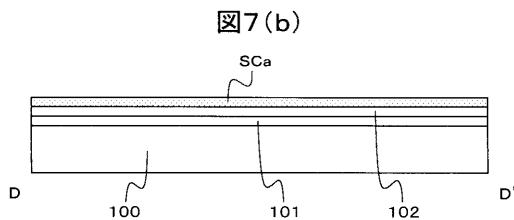

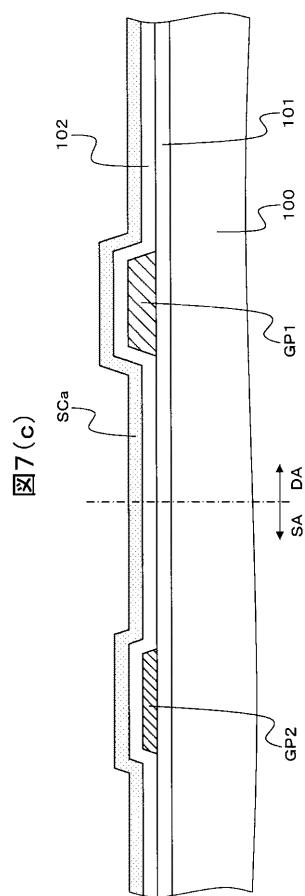

図7(a)乃至図8(b)は、実施例1のTFT基板の半導体層の製造方法を説明するための模式断面図である。

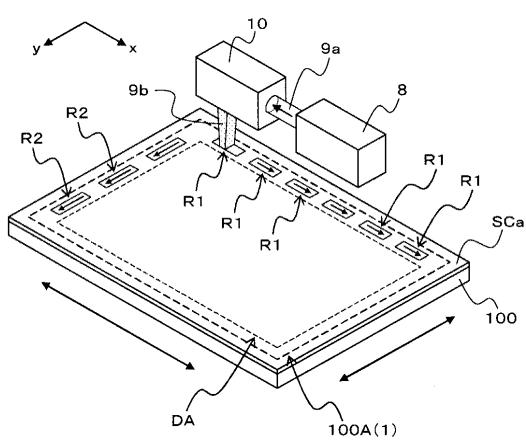

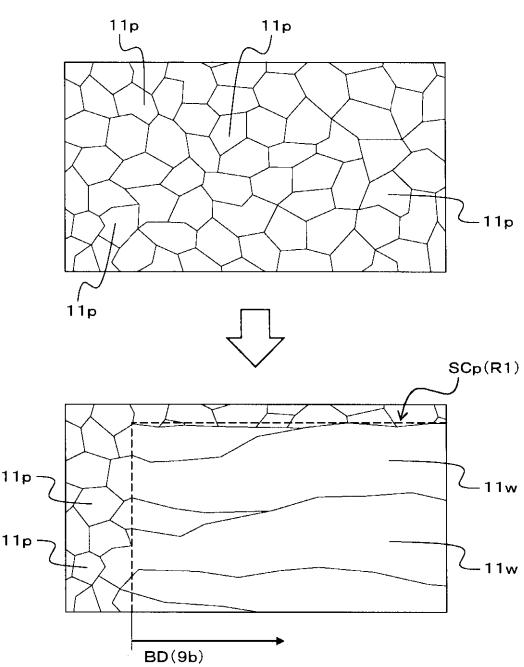

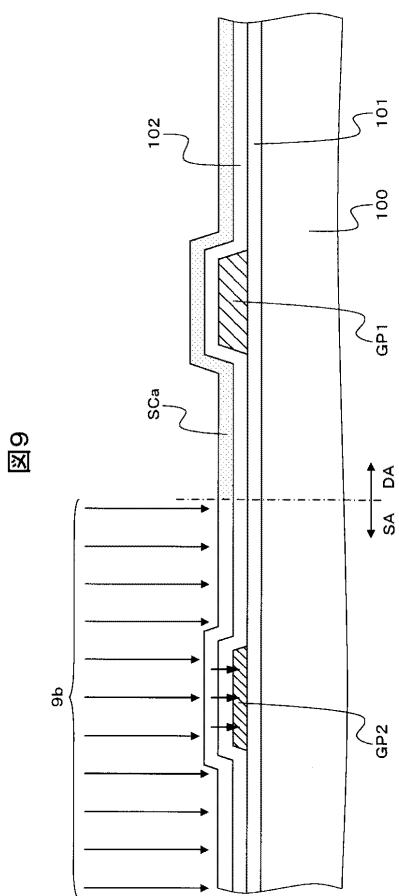

図7(a)は、アモルファスシリコン膜を成膜した直後の基板の概略構成を示す模式平面図である。図7(b)は、図7(a)のD-D'線における模式断面図である。図7(c)は、図7(b)に示した断面図において、周辺領域のMOSトランジスタのゲート電極が形成された領域と表示領域のTFT素子のゲート電極が形成された領域を拡大して並べた模式断面図である。図8(a)は、アモルファスシリコンを多結晶シリコン化する方法の一例を示す模式斜視図である。図8(b)は、多結晶シリコン化された領域の半導体層の概略構成を示す模式平面図である。

なお、図7(c)および図9において、一点鎖線の右側は表示領域DAに形成されるTFT素子(MOSトランジスタ)のゲート電極GP1の周辺における断面構成の一例を示しており、一点鎖線の左側は周辺領域SAに形成されるMOSトランジスタのゲート電極GP2の周辺における断面構成の一例を示している。

## 【0077】

実施例1の液晶表示装置(TFT基板1)を製造するときに用いるガラス基板100は、たとえば、図7(a)に示すように、TFT基板1として用いるときの大きさよりも大きいマザーガラスと呼ばれるガラス基板100を用いて製造される。そして、マザーガラス100の上に前記手順でゲート電極GP1, GP2を形成した後、続けて、第1の絶縁層102、半導体層SC1, SC2、映像信号線DL(ドレイン電極SD1aを含む)およびソース電極SD1b、画素電極PXなどを形成し、最後にマザーガラス100から領域100Aを切り出すと、図2および図3に示したような構成のTFT基板1が得られる。

## 【0078】

前記手順でゲート電極GP1, GP2を形成した後は、たとえば、図7(a)および図7(b)に示すように、マザーガラス100の全面にゲート絶縁膜としての機能を有する第1の絶縁層102を成膜し、続けて、アモルファスシリコン膜SCaを成膜する。このとき、アモルファスシリコン膜SCaは、表示領域DAだけでなく、周辺領域SAを含むマザーガラス100の全面に成膜する。また、図7(b)では省略しているが、表示領域DAや、周辺領域SAのうちの第1の駆動回路を形成する領域R1および第2の駆動回路を形成する領域R2には、たとえば、図7(c)に示すように、ゲート電極GP1, GP2や走査信号線GLなどが形成されている。そのため、アモルファスシリコン膜SCaは、たとえば、ゲート電極GP1, GP2の上にある部分と、その外側にある部分の境目に、各ゲート電極GP1, GP2の厚さに応じた段差が生じている。

## 【0079】

実施例1のTFT基板1の製造方法では、アモルファスシリコン膜SCaを成膜した後、たとえば、周辺領域SAの全域、または第1の駆動回路を形成する領域R1および第2の駆動回路を形成する領域R2のアモルファスシリコン膜SCaを多結晶シリコン化する。

## 【0080】

アモルファスシリコン膜SCaを多結晶シリコン化するときには、たとえば、エキシマレーザや連続発振レーザなどのエネルギーービームを、多結晶シリコン化したい領域に照射してアモルファスシリコン膜SCaを溶融させた後、溶融したシリコンを結晶化させる。より具体的には、まず、多結晶シリコン化したい領域にエキシマレーザまたは連続発振レーザなどを照射して、アモルファスシリコン膜SCaを脱水素化する。そして、脱水素化したアモルファスシリコン膜に、別のレーザなどを照射して溶融させた後、結晶化させる。このとき、マザーガラス100は、たとえば、x方向およびy方向に移動可能なステージの上に載せて固定しておく。そして、たとえば、図8(a)に示すように、レーザ発振器8で発生させた連続発振レーザ9aを光学系10で所望のエネルギー密度および形状に変換し、その変換した連続発振レーザ9bをマザーガラス100のアモルファスシリコン

S C a に照射する。このとき、マザーガラス 100 を載せたステージを、x 方向および y 方向に移動させながら、マザーガラス 100 上における連続発振レーザ 9 b の照射位置を移動させ、多結晶シリコン化したい領域の全域に連続発振レーザ 9 b を照射する。

#### 【0081】

またこのとき、溶融したシリコンを多結晶シリコン化させるには、たとえば、照射する連続発振レーザ 9 b のエネルギー密度と照射領域の移動速度（走査速度）を調整すればよい。照射する連続発振レーザ 9 b のエネルギー密度と照射領域の移動速度（走査速度）がある条件を満たす場合、溶融したシリコンが固化する過程でラテラル成長が起こり、照射領域の移動方向に沿って長く延びる帯状結晶の集合体でなる多結晶シリコンが得られる。

#### 【0082】

また、アモルファスシリコン膜 S C a を多結晶シリコン化するときには、たとえば、まず、図 8 (b) の上側に示すように、微結晶または粒状結晶などの微小な結晶 11 p の集合体でなる多結晶シリコンを形成してもよい。この場合、微小な結晶 11 p の集合体でなる多結晶シリコンに再度連続発振レーザ 9 b を照射して溶融、再結晶化させて、図 8 (b) の下側に示すように、連続発振レーザ 9 b の照射位置の移動方向 B D に沿って長く延びる帯状結晶 11 w の集合体でなる多結晶シリコン S C p を形成する。

#### 【0083】

このような帯状結晶 11 w の集合体でなる多結晶シリコン S C p を形成した場合、帯状結晶 11 w の長く延びる方向がチャネル長の方向、すなわち M O S トランジスタにおけるキャリアの移動方向になるようにドレイン電極 S D 2 a およびソース電極 S D 2 b を形成すれば、キャリアの移動を阻害する結晶粒界がほとんど無く、各駆動回路 D R V 1 , D R V 2 の M O S トランジスタを高速で動作させることができる。

#### 【0084】

上記のような手順で周辺領域 S A のアモルファスシリコン膜 S C a を多結晶シリコン S C p にした後の、T F T 基板の製造方法（手順）について、以下、簡単に説明する。

#### 【0085】

周辺領域 S A のアモルファスシリコン膜 S C a を多結晶シリコン S C p にしたら、次に、たとえば、マザーガラス 100 の全面に n 型のアモルファスシリコン膜を成膜し、当該 n 型のアモルファスシリコン膜、アモルファスシリコン膜 S C a および多結晶シリコン S C p を島状にパターニングする。

#### 【0086】

次に、マザーガラス 100 の全面に導電膜を成膜し、当該導電膜をパターニングして映像信号線 D L 、ドレイン電極 S D 1 a , S D 2 a 、およびソース電極 S D 1 b , S D 2 b などを形成する。

#### 【0087】

次に、ドレイン電極 S D 1 a , S D 2 a 、およびソース電極 S D 1 b , S D 2 b をマスクにして、アモルファスシリコン膜 S C a および多結晶シリコン膜 S C p の上にある n 型のアモルファスシリコン膜をエッチングする。このとき、アモルファスシリコン膜 S C a の上にある n 型のアモルファスシリコン膜はドレイン領域 S C 1 a とソース領域 S C 1 b に分離され、多結晶シリコン膜 S C p の上にある n 型のアモルファスシリコン膜はドレイン領域 S C 2 a とソース領域 S C 2 b に分離される。またこのとき、n 型のアモルファスシリコン膜をエッチングすると、たとえば、図 4 (c) に示したように、アモルファスシリコン膜 S C a および多結晶シリコン S C p の一部も除去されて薄くなる。このような手順で半導体層を形成することにより、表示領域 D A の T F T 素子の半導体層 S C 1 は、ドレイン領域 S C 1 a 、ソース領域 S C 1 b 、およびチャネル領域 S C 1 c がともにアモルファスシリコンで形成された半導体層になる。一方、周辺領域 S A の M O S トランジスタの半導体層 S C 2 は、ドレイン領域 S C 2 a およびソース領域 S C 2 b がアモルファスシリコンで形成され、チャネル領域 S C 1 c が多結晶シリコンで形成された半導体層になる。

#### 【0088】

10

20

30

40

50

また、その後は、第2の絶縁層103および第3の絶縁層104を成膜し、スルーホールTHを形成した後、たとえば、ITOなどの光透過率が高い導電膜を成膜し、当該導電膜(ITO膜)をパターニングして画素電極PXを形成する。

#### 【0089】

図9は、実施例1のTFT基板の製造方法の作用効果を説明するための模式断面図である。

#### 【0090】

前述のアモルファスシリコン膜SCaを多結晶シリコン化する工程は、たとえば、連続発振レーザなどのエネルギービームを照射してアモルファスシリコン膜SCaを加熱し、溶融させる必要がある。このとき、たとえば、周辺領域SAのアモルファスシリコン膜SCaに連続発振レーザを照射すると、たとえば、図9に示すように、周辺領域SAのゲート電極GP2の上にあるアモルファスシリコンSCaに照射されたエネルギービームによる熱が、第1の絶縁膜102を介してゲート電極GP2に伝導する。このとき、ゲート電極GP2の上にある部分と、その外側にある部分でアモルファスシリコンSCaが受ける熱量(エネルギー)の総量に差が生じ、結晶性にばらつきが生じことがある。そのため、実施例1のTFT基板1の製造方法のように、レーザが照射される領域(多結晶シリコン化する領域)のゲート電極GP2を薄く形成して熱伝導の量を小さくすると、ゲート電極GP2の上にある部分と、その外側にある部分でアモルファスシリコン膜SCaが受ける熱量の総量の差を小さくでき、結晶性のばらつきを低減できる。この効果は、ゲート電極GP2に用いる第1の導電層601の熱伝導率が低いほど大きく、また、膜厚が薄いほど大きい。

10

20

30

40

#### 【0091】

また、実施例1のTFT基板1の製造方法のように、レーザが照射される領域(多結晶シリコン化する領域)のゲート電極GP2を薄く形成すると、ゲート電極GP2の上にある部分と、その外側にある部分の境目に生じるアモルファスシリコン膜SCaの段差を小さく(低く)することができる。そのため、レーザを照射してアモルファスシリコン膜SCaを溶融させたときに、段差の上の部分から下の部分に流れ落ちる溶融シリコンの量を少なくでき、段差部分での膜剥れを低減することができる。この効果は、ゲート電極GP2に用いる第1の導電層601の膜厚が薄いほど大きい。

#### 【0092】

また、実施例1のTFT基板の製造方法では、レーザが照射される領域、すなわち高速での動作が要求される第1の駆動回路DRV1を形成する領域R1および第2の駆動回路DRV2を形成する領域R2のMOSトランジスタのゲート電極GP2のみを薄くでき、表示領域DAのTFT素子のゲート電極GP1は、従来の液晶表示装置(TFT基板)におけるゲート電極と同程度の厚さにすることができる。そのため、たとえば、ゲート電極GP1と一緒に走査信号線GLを形成する場合、走査信号線GLの配線抵抗が高くなるのを防ぎ、消費電力の増大や画素部の信号遅延による動作不良を低減することができる。走査信号線GLは、その一端が表示領域DAの外側にある第2の駆動回路DRV2を形成する領域R2まで延びているが、表示領域DAを通る部分の配線長のほうが長い。そのため、走査信号線GLのうちの表示領域DAを通る部分をゲート電極GP1と同じ積層構成にすることで、配線抵抗を小さくする効果が大きくなる。またこのとき、第1の導電層601と第2の導電層602が同じ材料でも配線抵抗を小さくする効果は得られるが、第2の導電層602に、第1の導電層601よりも電気伝導率が高い材料を用いと、さらに大きな効果が得られる。また、第2の導電層602は、第1の導電層601に比べて融点の低い材料を用いることも可能であり、たとえば、A1を用いることもできる。

40

#### 【0093】

また、実施例1のTFT基板の製造方法では、表示領域DAのTFT素子(MOSトランジスタ)および周辺領域SAのMOSトランジスタのゲート絶縁膜102の膜厚を厚くしなくても、ゲート電極GP2の熱伝導の影響による多結晶シリコン膜の結晶性のばらつきを小さくできる。そのため、ゲート絶縁膜の膜厚を厚くすることにより生じる別の問題

50

、たとえば、トランジスタ特性のうちの  $I_{oN}$  の低下、 $V_{th}$  のばらつきの増加という問題や、生産性の低下といった問題を回避できる。

#### 【0094】

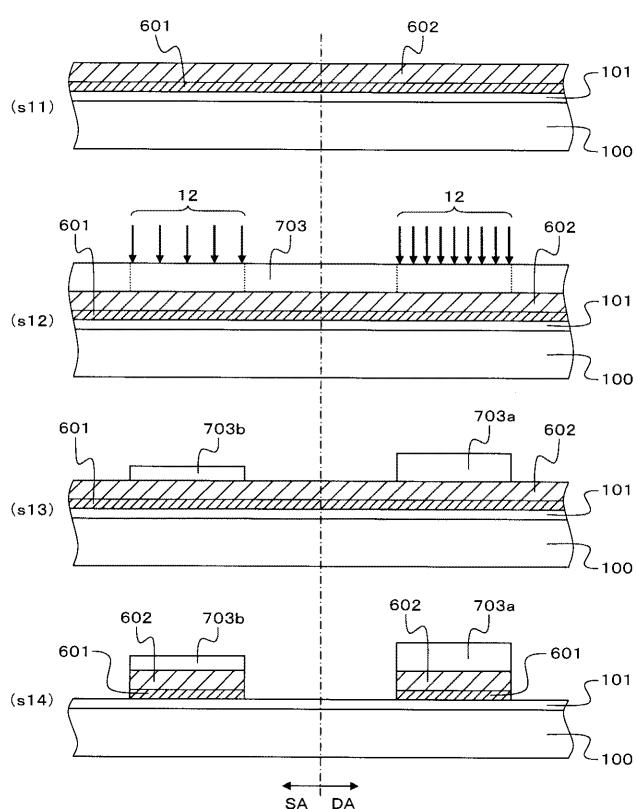

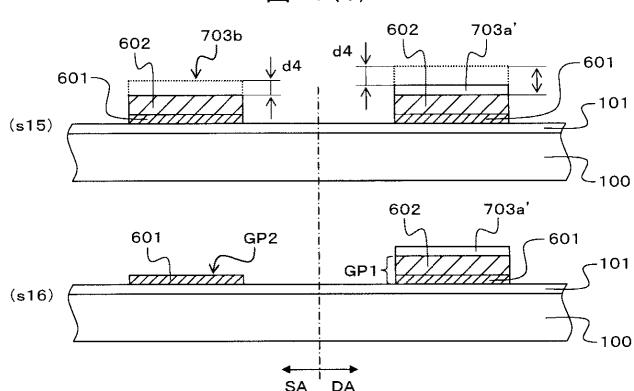

図10(a)および図10(b)は、実施例1のTFT基板の製造方法の変形例を説明するための模式断面図である。なお、図10(a)および図10(b)には、ゲート電極を形成する手順において特徴となる部分のみを(s11)から(s16)として示している。また、図10(a)および図10(b)において、一点鎖線の右側は表示領域DAに形成されるTFT素子(MOSトランジスタ)のゲート電極GP1の形成手順を示しており、一点鎖線の左側は周辺領域SAに形成されるMOSトランジスタのゲート電極GP2の形成手順を示している。

10

#### 【0095】

実施例1のTFT基板の製造方法において、ゲート電極GP1, GP2を形成する手順としては、たとえば、図6に示したように、1つめのレジスト701で表示領域DAの外側にある第2の導電層602を除去し、2つめのレジスト702でゲート電極GP1, GP2をパターニングする手順が考えられる。しかしながら、この手順では、1つめのレジスト701を形成する際と、2つめのレジスト702を形成する際に、それぞれ異なるマスクを用いて露光、現像する必要があるので生産性が悪い。そこで、実施例1のTFT基板1のゲート電極GP1, GP2を形成するときには、たとえば、ハーフ露光またはハーフトーン露光と呼ばれる露光技術を用いてレジストを形成し、1回の露光、現像で形成したレジストで周辺領域SAの第2の導電層602の除去と、ゲート電極GP1, GP2のパターニングを行うことが望ましい。

20

#### 【0096】

ハーフ露光技術を用いたレジストでゲート電極GP1, GP2を形成するときにも、まず、図10(a)の(s11)に示すように、ガラス基板100(絶縁基板)上のシリコン窒化膜(SiN膜)などの下地絶縁層101を成膜した後、第1の導電層601および第2の導電層602を続けて成膜する。

30

#### 【0097】

次に、図10(a)の(s12)に示すように、第2の導電層602の上に塗布した感光性レジスト703に対してハーフ露光を行う。ハーフ露光を行うときには、たとえば、周辺領域SAの薄いゲート電極GP2を形成する領域の光の透過量が、表示領域DAのゲート電極GP1を形成する領域の光の透過量よりも小さくなるようにしたマスク(図示しない)を用い、各領域に照射される光12(たとえば紫外線)の光量を変化させる。このとき、たとえば、表示領域DAのゲート電極GP1を形成する領域のレジスト703が完全に感光する最短時間で露光を終了すると、周辺領域SAの薄いゲート電極GP2を形成する領域のレジスト703は不完全な状態で感光が終了する。そのため、このレジスト703を現像すると、たとえば、図10(a)の(s13)に示すように、周辺領域SAの薄いゲート電極GP2を形成する領域におけるレジスト703bの膜厚が、表示領域DAのゲート電極GP1を形成する領域におけるレジスト703aの膜厚よりも薄くなる。

30

#### 【0098】

なお、図10(a)の(s12)および(s13)に示した手順では、ネガ型の感光性レジストを用いてレジスト703a, 703bを形成する場合を例を挙げているが、これに限らず、たとえば、ポジ型の感光性レジストを用いてレジスト703a, 703bを形成することも可能である。

40

#### 【0099】

次に、図10(a)の(s14)に示すように、表示領域DAのゲート電極GP1を形成する領域のレジスト703a、および周辺領域SAの薄いゲート電極GP2を形成する領域のレジスト703bをマスクにして、各領域の第2の導電層602および第1の導電層601のうちの不要な部分を除去する。このとき、周辺領域SAの薄いゲート電極は、平面でみた形状は最終的なゲート電極GP2と同じパターンであるが、まだ第2の導電層602(不要な導電層)が残っている状態である。

50

**【0100】**

そこで、次に、たとえば、O<sub>2</sub>アッシングを行い、図10(b)の(s15)に示すように、マザーガラス100に形成されているすべてのレジスト703a, 703bを、周辺領域SAの薄いゲート電極GP2を形成する部分にあるレジスト703bの厚さd4の分だけ薄くする。このようにすると、周辺領域SAの薄いゲート電極GP2を形成する部分はレジストが無くなり、表示領域DAのゲート電極GP1を形成する部分のみにレジスト703bの厚さd4分だけ薄くなったレジスト703a'が残る。

**【0101】**

次に、たとえば、図10(b)の(s16)に示すように、O<sub>2</sub>アッシング後に残ったレジスト703a'をマスクにしたエッチングで第2の導電層602を除去すると、周辺領域SAに第1の導電層601のみからなる薄いゲート電極GP2を形成することができる。

10

**【0102】**

このように、ハーフ露光技術を用いれば、厚さが異なるゲート電極GP1, GP2を形成するためのレジストを露光、現像する工程を1回にすることができる。

**【0103】**

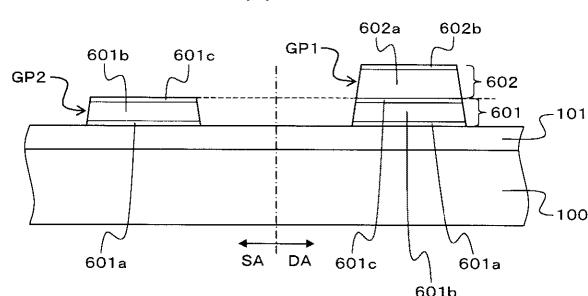

図11は、実施例1のTFT基板の応用例を説明するための模式断面図である。なお、図11において、一点鎖線の右側は表示領域DAに形成されるTFT素子(MOSトランジスタ)のゲート電極GP1の断面構成を示しており、一点鎖線の左側は周辺領域SAに形成されるMOSトランジスタのゲート電極GP2の断面構成を示している。

20

**【0104】**

実施例1では、たとえば、第1の導電層601および第2の導電層602が、それぞれ単一の材料である場合を例に挙げたが、これに限らず、第1の導電層601または第2の導電層602のいずれか一方、あるいはその両方が、2層以上の導電層を積層した構成であってもよい。すなわち、第1の導電層601のみで形成される周辺領域SAのゲート電極GP2において、当該第1の導電層601は、たとえば、図11に示すように、3つの導電層601a, 601b, 601cが積層された構成であってもよい。このとき、第1の導電層601および第2の導電層602で形成される表示領域DAのゲート電極GP1は、たとえば、図11に示すように、3つの導電層601a, 601b, 601cからなる第1の導電層601の上に、2つの導電層602a, 602bからなる第2の導電層602が積層されていてもよい。このような構成の場合、たとえば、導電層601b, 602aにはAlを用い、導電層601a, 601c, 602bにはMoまたはMoW合金を用いる。

30

**【0105】**

なお、図11に示した例は、第1の導電層601の積層構成および第2の導電層602の積層構成の組み合わせの一例であり、表示領域DAのゲート電極GP1および周辺領域SAのゲート電極GP2ならびに走査信号線GLについての電気的な特性および熱的な特性の関係が、実施例1で説明した条件を満たすものであれば、他の積層構成であってもよいことはもちろんである。

**【実施例2】****【0106】**

図12は、本発明による実施例2のTFT基板の特徴を示す模式断面図である。なお、図12において、一点鎖線の右側は表示領域DAに形成されるTFT素子(MOSトランジスタ)のゲート電極GP1の断面構成の一例を示しており、一点鎖線の左側は周辺領域SAに形成されるMOSトランジスタのゲート電極GP2の断面構成の一例を示している。

40

**【0107】**

実施例2のTFT基板1は、たとえば、図12に示すように、周辺領域SAに配置された第1の駆動回路DRV1などのMOSトランジスタのゲート電極GP2の厚さd2が、表示領域DAのTFT素子のゲート電極GP1の厚さd1よりも薄い。このとき、周辺領

50

域 S A のゲート電極 G P 2 が第 1 の導電層 6 0 1 のみで形成されており、表示領域 D A のゲート電極 G P 1 が第 1 の導電層 6 0 1 と第 2 の導電層 6 0 2 とで形成されている点は、実施例 1 の TFT 基板 1 と同じである。

#### 【 0 1 0 8 】

ただし、実施例 2 の TFT 基板 1 において、表示領域 D A のゲート電極 G P 1 は、第 2 の導電層 6 0 2 が、ガラス基板 1 0 0 (下地絶縁層 1 0 1 ) と、第 1 の導電層 6 0 1 との間に設けられた構成になっている。

#### 【 0 1 0 9 】

また、実施例 2 においても、周辺領域 S A の MOS テランジスタのゲート電極 G P 2 および表示領域 D A の TFT 素子のゲート電極 G P 1 に用いられている第 1 の導電層 6 0 1 と、表示領域 D A の TFT 素子のゲート電極 G P 1 のみに用いられている第 2 の導電層 6 0 2 は、同じ材料であってもよいし、異なる材料であってもよい。ただし、第 1 の導電層 6 0 1 の材料と第 2 の導電層 6 0 2 の材料との組み合わせは、実施例 1 でも説明したように、第 1 の導電層 6 0 1 の熱伝導率が第 2 の導電層 6 0 2 の熱伝導率よりも低いことが望ましい、またこのとき、第 2 の導電層 6 0 2 の電気抵抗 (配線抵抗) が第 1 の導電層 6 0 1 の電気抵抗 (配線抵抗) よりも低い組み合わせであると、さらに望ましい。

10

#### 【 0 1 1 0 】

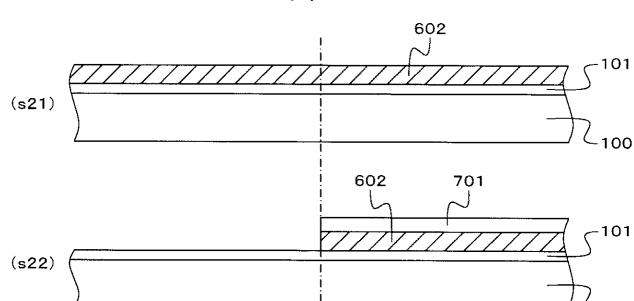

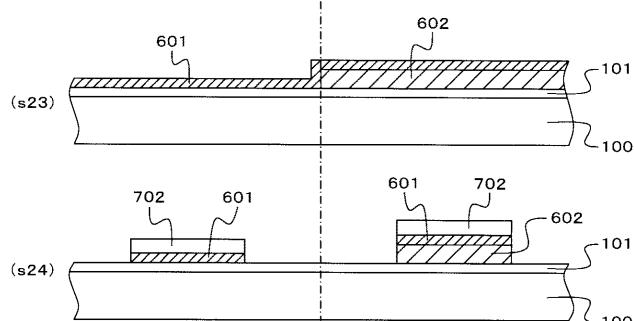

図 1 3 は、実施例 2 の TFT 基板のゲート電極の製造方法を説明するための模式断面図である。なお、図 1 3 には、ゲート電極を形成する手順において特徴となる部分のみを ( s 2 1 ) から ( s 2 5 ) として示している。また、図 1 3 において、一点鎖線の右側は表示領域 D A に形成される TFT 素子 (MOS テランジスタ) のゲート電極 G P 1 の形成手順を示しており、一点鎖線の左側は周辺領域 S A に形成される MOS テランジスタのゲート電極 G P 2 の形成手順を示している。

20

#### 【 0 1 1 1 】

実施例 2 の TFT 基板 1 の製造方法において、表示領域 D A の TFT 素子のゲート電極 G P 1 、第 1 の駆動回路 D R V 1 および第 2 の駆動回路 D R V 2 の MOS テランジスタのゲート電極 G P 2 を形成する工程は、まず、図 1 3 の ( s 2 1 ) に示すように、ガラス基板 (絶縁基板) 1 0 0 上にシリコン窒化膜 (SiN 膜) などの下地絶縁層 1 0 1 を成膜した後、第 2 の導電層 6 0 2 を成膜する。

30

#### 【 0 1 1 2 】

次に、図 1 3 の ( s 2 2 ) に示すように、第 2 の導電層 6 0 2 の上のうちの、表示領域 D A の上のみにレジスト 7 0 1 を形成し、表示領域 D A の外側 (周辺領域 S A ) にある第 2 の導電層 6 0 2 をエッティングで除去する。

#### 【 0 1 1 3 】

次に、レジスト 7 0 1 を除去した後、図 1 3 の ( s 2 3 ) に示すように、ガラス基板 1 0 0 の全面、すなわち表示領域 D A および周辺領域 S A に第 1 の導電層 6 0 1 を成膜する。

#### 【 0 1 1 4 】

次に、図 1 3 の ( s 2 4 ) に示すように、レジスト 7 0 2 を形成し、レジスト 7 0 2 をマスクにしたエッティングを行い、表示領域 D A は第 1 の導電層 6 0 1 および第 2 の導電層 6 0 2 の不要な部分を除去し、その外側の周辺領域 S A は第 1 の導電層 6 0 1 の不要な部分を除去する。

40

#### 【 0 1 1 5 】

その後、レジスト 7 0 2 を除去すると、図 1 3 の ( s 2 5 ) に示すように、表示領域 D A には第 1 の導電層 6 0 1 および第 2 の導電層 6 0 2 が積層したゲート電極 G P 1 が形成され、周辺領域 S A には第 1 の導電層 6 0 1 のみからなる薄いゲート電極 G P 2 が形成される。

#### 【 0 1 1 6 】

なお、図 1 3 に示したような手順でゲート電極 G P 1 , G P 2 を形成する場合、前記第 2 の導電層 6 0 2 および第 1 の導電層 6 0 1 は、同じ材料であってもよいし、異なる材料

50

であってもよい。同じ材料を用いる場合は、たとえば、MoW合金を用いる。また、異なる材料を用いる場合は、たとえば、周辺領域SAのMOSトランジスタのゲート電極GP2にも用いられる第1の導電層601にMoW合金を用い、第2の導電層602にAlを用いる。

#### 【0117】

また、このような手順で表示領域DAとその外側の周辺領域SAとで厚さが異なり、かつ、周辺領域SAのほうが薄くなるように各領域DA, SAのゲート電極GP1, GP2を形成した後は、アモルファスシリコン膜SCaを成膜し、たとえば、周辺領域SAのアモルファスシリコンSCaを多結晶シリコン化する。このときの手順、および得られる効果については、実施例1で説明した通りである。また、周辺領域SAのアモルファスシリコン膜SCaを多結晶シリコン化した後の工程については、実施例1で説明した手順で行えよので、その説明は省略する。10

#### 【0118】

このように、実施例2のTFT基板1の製造方法においても、周辺領域SAのMOSトランジスタを形成する領域のアモルファスシリコンSCaを多結晶シリコン化したときに、ゲート電極GP2の上にある部分とその外側にある部分の結晶性のばらつきや、段差部分での膜剥がれを低減することができる。

#### 【0119】

また、表示領域DAのTFT素子のゲート電極GP1や走査信号線GLの配線抵抗が高くなるのを防ぎ、消費電力の増大や画素部の信号遅延による不良を低減することができる。20

#### 【0120】

また、各領域のTFT素子(MOSトランジスタ)のゲート絶縁膜102の膜厚を厚くすることにより生じる別の問題、たとえば、トランジスタ特性のうちの $I_{ON}$ の低下、 $V_{th}$ のばらつきの増加という問題や、生産性の低下といった問題を回避できる。

#### 【0121】

またさらに、実施例2のTFT基板1の製造方法では、表示領域DAのみに第2の導電層602を形成した後、第1の導電層601を全面に形成するので、周辺領域SAは第1の導電層601のみをエッチングすればよい。そのため、第2の導電層602と第1の導電層601が同じ材料、たとえば、MoW合金であっても、周辺領域SAのゲート電極GP2の表面の平坦性が悪くなるのを防げる。30

#### 【0122】

また、実施例2では、たとえば、第1の導電層601および第2の導電層602が、それぞれ単一の材料である場合を例に挙げたが、これに限らず、第1の導電層601または第2の導電層602のいずれか一方、あるいはその両方が、2層以上の導電層を積層した構成であってもよいことはもちろんである。

#### 【実施例3】

#### 【0123】

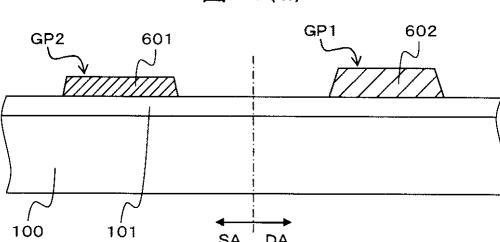

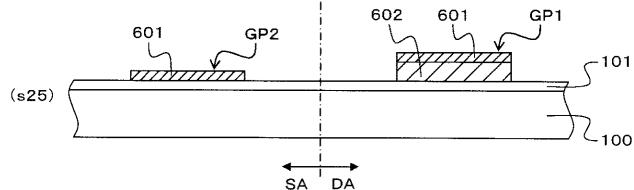

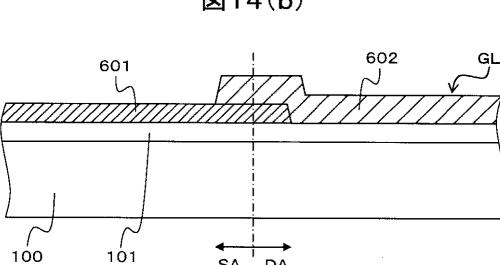

図14(a)および図14(b)は、本発明による実施例3のTFT基板の特徴を示す模式断面図である。

図14(a)は、表示領域のゲート電極と周辺領域のゲート電極との断面構成の一例を示す模式断面図である。図14(b)は、表示領域の走査信号線と周辺領域の走査信号線の接続部分の断面構成の一例を示す模式断面図である。なお、図14(a)において、一点鎖線の右側は表示領域DAに形成されるTFT素子(MOSトランジスタ)のゲート電極GP1の断面構成の一例を示しており、一点鎖線の左側は周辺領域SAに形成されるMOSトランジスタのゲート電極GP2の断面構成の一例を示している。また、図14(b)において、一点鎖線の右側は表示領域DAにおける走査信号線GLの断面構成の一例を示しており、一点鎖線の左側は周辺領域SAにおける走査信号線GLの断面構成の一例を示している。

#### 【0124】

10

20

30

40

50

実施例 1 および実施例 2 では、表示領域 D A の T F T 素子のゲート電極 G P 1 に、周辺領域 S A の M O S ドラジスタのゲート電極 G P 2 に用いる第 1 の導電層 6 0 1 が含まれている場合の構成について説明した。実施例 3 では、これらの構成とは異なり、表示領域 D A の T F T 素子のゲート電極 G P 1 に、周辺領域 S A の M O S ドラジスタのゲート電極 G P 2 に用いる第 1 の導電層 6 0 1 が含まれていない場合の構成について説明する。

#### 【 0 1 2 5 】

実施例 3 の T F T 基板 1 は、たとえば、図 14 ( a ) に示すように、周辺領域 S A に配置された第 1 の駆動回路 D R V 1 などの M O S ドラジスタのゲート電極 G P 2 の厚さが、表示領域 D A の T F T 素子のゲート電極 G P 1 の厚さよりも薄い。このとき、周辺領域 S A のゲート電極 G P 2 が第 1 の導電層 6 0 1 のみで形成されている点は、実施例 1 や実施例 2 の T F T 基板 1 と同じである。10

#### 【 0 1 2 6 】

ただし、実施例 3 の T F T 基板 1 において、表示領域 D A の T F T 素子のゲート電極 G P 1 は、たとえば、第 2 の導電層 6 0 2 のみで形成されている。このとき、表示領域 D A のゲート電極 G P 1 に接続されている走査信号線 G L は、たとえば、図 14 ( b ) に示すように、表示領域 D A を通る部分は第 2 の導電層 6 0 2 で形成され、周辺領域 S A を通る部分は第 1 の導電層 6 0 1 で形成される。そして、1 本の走査信号線 G L を構成する第 1 の導電層 6 0 1 と第 2 の導電層 6 0 2 とは、たとえば、表示領域 D A と周辺領域 S A の境界あるいはその近傍で、第 2 の導電層 6 0 2 の端部が第 1 の導電層 6 0 1 の端部の上に乗り上げる形で電気的に接続される。20

#### 【 0 1 2 7 】

実施例 3 のような構成の T F T 基板 1 の製造方法において、ゲート電極 G P 1 , G P 2 や走査信号線 G L を形成するときには、たとえば、まず、ガラス基板 1 0 0 の上にシリコン窒化膜などの下地絶縁層 1 0 1 を成膜した後、続けて第 1 の導電層 6 0 1 を成膜する。次に、第 1 の導電層 6 0 1 の上にレジストを形成し、第 1 の導電層 6 0 1 をエッチングして、表示領域 D A の外側（周辺領域 S A ）のみに、走査信号線 G L 、第 1 の駆動回路 D R V 1 および第 2 の駆動回路 D R V 2 の M O S ドラジスタのゲート電極 G P 2 などを形成する。

#### 【 0 1 2 8 】

次に、ガラス基板 1 0 0 の上に第 2 の導電層 6 0 2 を成膜する。その後、第 2 の導電層 6 0 2 の上にレジストを形成し、第 2 の導電層 6 0 2 をエッチングして、表示領域 D A のみに、周辺領域 S A に形成されている走査信号線 G L と接続される走査信号線 G L 、表示領域 D A の T F T 素子のゲート電極 G P 1 などを形成する。30

#### 【 0 1 2 9 】

このとき、たとえば、第 1 の導電層 6 0 1 の材料として、第 2 の導電層 6 0 2 （たとえば、アルミニウム）よりも熱伝導率が低い材料を用いることが望ましい。そして、第 1 の導電層 6 0 1 を第 2 の導電層 6 0 2 よりも薄く成膜してゲート電極 G P 2 などを形成すれば、実施例 1 および実施例 2 で説明した T F T 基板 1 と同様の効果を得ることができる。

#### 【 0 1 3 0 】

なお、実施例 3 のような構成の T F T 基板 1 の場合、たとえば、第 1 の導電層 6 0 1 の材料として、第 2 の導電層 6 0 2 （たとえば、アルミニウム）よりも熱伝導率が低い材料を用いるのであれば、各導電層 6 0 1 , 6 0 2 の厚さはほぼ同じであってもよいことはもちろんである。しかしながら、アモルファスシリコン S C a を多結晶シリコン化する工程で、溶融したシリコンが段差の上側から下側に流れ落ちて段差部分に膜剥れが起こるのを防ぐには、第 1 の導電層 6 0 1 を可能な限り薄く成膜することが望ましい。40

#### 【 0 1 3 1 】

以上、本発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において、種々変更可能であることはもちろんである。

#### 【 0 1 3 2 】

たとえば、TFT基板1の表示領域DAのTFT素子、第1の駆動回路DRV1および第2の駆動回路DRV2のMOSトランジスタは、ボトムゲート構造であればよく、図4(a)乃至図4(c)に示したような構造に限らず、他の構造であってもよい。

### 【0133】

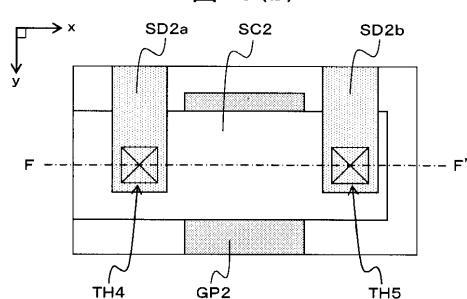

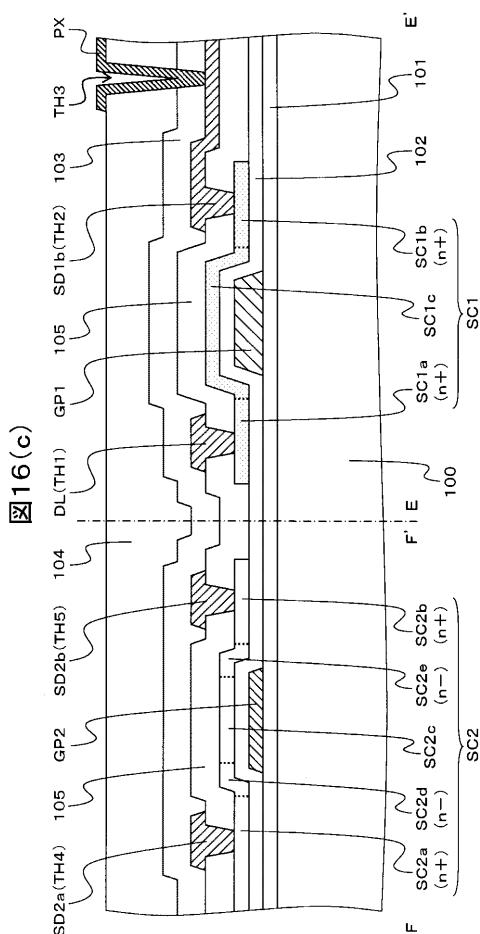

図15および図16(a)乃至図16(c)は、本発明のTFT基板におけるMOSトランジスタの構造の他の一例を示す模式図である。

図15は、図4(a)に示したTFT素子の平面構成の変形例を説明するための模式平面図である。

図16(a)は、本発明を適用したTFT基板における表示領域のTFT素子の概略構成の他の一例を示す模式平面図である。図16(b)は、本発明を適用したTFT基板における周辺回路のMOSトランジスタの概略構成の他の一例を示す模式平面図である。図16(c)は、図16(a)のE-E'線における断面構成の一例および図16(b)のF-F'線における断面構成の一例を横に並べて示した模式断面図である。なお、図16(c)において、(n+)は高濃度のn型不純物領域であることを示し、(n-)は低濃度のn型不純物領域であることを示している。

10

### 【0134】

前記実施例1乃至実施例3では、表示領域DAにおけるTFT素子の周辺を平面でみたときの構成が、たとえば、図4(a)に示したような構成になっており、走査信号線GLの幅(y方向の寸法)を部分的に広くして設けた矩形状の突出部分をゲート電極GP1として利用している。しかしながら、表示領域DAのTFT素子の平面構成は、これに限らず、たとえば、図15に示すように、走査信号線GLの幅を一定にして、当該走査信号線GLの上に半導体層SC1を設けてもよい。また、映像信号線DLについても、映像信号線DLの幅(x方向の寸法)を部分的に広くして設けた矩形状の突出部分をドレイン電極SD1aとして利用する代わりに、たとえば、図15に示すように、映像信号線DLの幅を一定にして、映像信号線DLの下に半導体層SC1を設けてもよいことはもちろんである。

20

### 【0135】

また、表示領域DAのTFT素子(MOSトランジスタ)や、周辺領域SAの第1の駆動回路DRV1および第2の駆動回路DRV2のMOSトランジスタをボトムゲート構成にする場合、各領域DA, SAに形成されるMOSトランジスタは、図4(a)乃至図4(c)に示したような構成に限らず、たとえば、図16(a)乃至図16(c)に示したような構成にすることもできる。このとき、表示領域DAの各画素に対して配置されるMOSトランジスタ(TFT素子)は、たとえば、図16(a)および図16(c)に示すような構成になっており、ガラス基板100の表面に形成された下地絶縁層101の上にゲート電極GP1が形成されている。ゲート電極GP1は、たとえば、走査信号線GLと一体であり、走査信号線GLの幅(y方向の寸法)を部分的に広くして設けた矩形状の突出部分を利用している。

30

### 【0136】

また、ガラス基板100からみてゲート電極GP1の上には、第1の絶縁層(ゲート絶縁膜)102を介して半導体層SC1が形成されている。半導体層SC1は、ドレイン領域SC1a、ソース領域SC1b、およびチャネル領域SC1cの3つの領域からなり、各領域は、アモルファスシリコンなどのアモルファス半導体で形成されている。TFT素子がNチャネルMOSトランジスタの場合、半導体層SC1のドレイン領域SC1aおよびソース領域SC1bは、たとえば、不純物としてリンが注入されたn型半導体領域であり、チャネル領域SC1cは真性(i型)のアモルファス半導体、または不純物濃度が非常に低いn型のアモルファス半導体、もしくは不純物濃度が非常に低いp型のアモルファス半導体のいずれか1つである。

40

### 【0137】

また、ガラス基板100からみて半導体層SC1のさらに上には、第4の絶縁層105を介して映像信号線DLおよびソース電極SD1bが形成されており、映像信号線DLは

50

スルーホールTH1により半導体層SC1のドレイン領域SC1aと接続しており、ソース電極SD1bはスルーホールTH2により半導体層SC1のソース領域SC1bと接続している。

#### 【0138】

また、映像信号線DLおよびソース電極SD1bのさらに上には、第2の絶縁層103および第3の絶縁層104を介して画素電極PXが形成されている。画素電極PXは、スルーホールTH3によりソース電極SD1bと接続している。

#### 【0139】

なお、図16(a)に示した例では、映像信号線DLの幅(×方向の寸法)を一定にして、映像信号線DLと半導体層SC1とが平面でみて重なる領域にスルーホールTH1を形成しているが、これに限らず、たとえば、映像信号線DLの幅を部分的に広くした矩形状の突出部分を形成し、当該突出部分をTFT素子のドレイン電極SD1aとして利用してもよいことはもちろんである。

10

#### 【0140】

またこのとき、周辺領域のMOSトランジスタは、たとえば、図16(b)および図16(c)に示したような構成になっており、ガラス基板100の表面に形成された下地絶縁層101の上にゲート電極GP2が形成されている。

#### 【0141】

また、ガラス基板100からみてゲート電極GP2の上には、第1の絶縁層102を介して半導体層SC2が形成されている。周辺領域のMOSトランジスタをNチャネルMOSトランジスタにする場合、たとえば、よりスマーズにキャリアが移動するLDD構造(Lightly Doped Drain構造)にすることが望ましい。このとき、半導体層SC2は、2つのドレイン領域SC2a, SC2d、2つのソース領域SC2b, SC2e、およびチャネル領域SC2cの5つの領域からなり、5つの領域すべてが多結晶シリコンなどの多結晶半導体で形成されている。またこのとき、2つのドレイン領域SC2a, SC2dは、たとえば、不純物としてP<sup>+</sup>(リンイオン)が注入されたN型半導体領域であり、かつ、チャネル領域SC2cに近いほうの領域SC2dは、遠いほうの領域SC2aよりも不純物濃度が低い。同様に、2つのソース領域SC2b, SC2eも、たとえば、不純物としてP<sup>+</sup>(リンイオン)が注入されたN型半導体領域であり、かつ、チャネル領域SC2cに近いほうの領域SC2eは、遠いほうの領域SC2bよりも不純物濃度が低い。また、チャネル領域SC2cは真性(i型)の多結晶半導体、または不純物濃度が非常に低いn型の多結晶半導体、もしくは不純物濃度が非常に低いp型の多結晶半導体のうちのいずれか1つである。特に、半導体層SC2のように多結晶半導体(多結晶シリコン)で形成されている場合、チャネル領域SC2cに不純物をわずかに加えることで、MOSトランジスタのしきい値の制御が可能になる。

20

#### 【0142】

また、ガラス基板100からみて半導体層SC2のドレイン領域SC2aの上にはドレイン電極SD2aが形成され、ソース領域SC2bの上にはソース電極SD2bが形成されている。ドレイン電極SD2aは、スルーホールTH4によりドレイン領域SC2aと接続しており、ソース電極SD2bは、スルーホールTH5によりソース領域SC2bと接続している。

30

#### 【0143】

TFT基板1の表示領域DAに形成されるTFT素子の構成、および周辺領域SAに形成される駆動回路DRV1, DRV2のMOSトランジスタの構成が、図16(a)乃至図16(c)に示したような構成の場合も、たとえば、各領域DA, SAのMOSトランジスタのゲート電極GP1, GP2の構成を実施例1乃至実施例3で説明した構成にすることで、各実施例に挙げたTFT基板1およびその製造方法により得られる効果と同じ効果が得られる。

40

#### 【0144】

また、図16(a)乃至図16(b)に示したような構成のMOSトランジスタ(TF

50

T 素子 ) を形成する場合、たとえば、アモルファスシリコン膜 S C a を成膜し、周辺領域 S A のアモルファスシリコン膜 S C a を多結晶シリコン化した後、実施例 1 で説明したような n 型のアモルファスシリコン膜を成膜する必要はない。その代わり、たとえば、周辺領域 S A の一部または全部を多結晶シリコン化したアモルファスシリコン膜 S C a を島状にパターニングした後、島状のアモルファスシリコン膜 S C a ( 半導体層 S C 1 ) および多結晶シリコン膜 S C p ( 半導体層 S C 2 ) に不純物を注入して、半導体層 S C 1 のドレイン領域 S C 1 a およびソース領域 S C 1 b と、半導体層 S C 2 のドレイン領域 S C 2 a , S C 2 d およびソース領域 S C 2 b , S C 2 e とを形成する。このときの不純物の注入の手順は、従来の TFT 基板 1 の製造方法で適用されている手順でよいので、詳細な説明は省略する。

10

## 【 0 1 4 5 】

このように、本発明は、表示領域 D A ( 第 1 の領域 ) に形成される TFT 素子 ( MOS トランジスタ ) と、周辺領域 S A ( 第 2 の領域 ) に形成される MOS トランジスタが、基板と半導体層の間にゲート電極を有するボトムゲート型であり、かつ、一方の領域に形成される MOS トランジスタの半導体層がアモルファスシリコン膜でなり、他方の領域に形成される MOS トランジスタの半導体層が多結晶シリコン膜を有する構成であれば、どのような構成の場合にも適用することができる。

## 【 0 1 4 6 】

また、実施例 1 乃至実施例 3 では、表示領域 D A の TFT 素子の半導体層 S C 1 はアモルファスシリコン S C a で形成し、周辺領域 S A の MOS トランジスタの半導体層 S C 2 は帯状結晶の集合体でなる多結晶シリコン S C p で形成する場合を例に挙げたが、これに限らず、周辺領域 S A の MOS トランジスタの半導体層 S C 2 を、たとえば、図 8 ( b ) の上側に示したような微結晶または粒状結晶などの微小結晶 1 1 p の集合体でなる多結晶シリコンで形成する場合にも、本発明を適用できることはもちろんである。

20

## 【 0 1 4 7 】

また、実施例 1 乃至実施例 3 では、半導体層 S C 1 , S C 2 を形成するための半導体材料としてシリコンを用いた場合を例に挙げたが、アモルファス状態のものを加熱して多結晶状態に改質する半導体材料であれば、シリコンに限らず、他の半導体材料を用いてもよいことはもちろんである。

30

## 【 0 1 4 8 】

またさらに、本発明は、ゲート絶縁膜が酸化膜である MOS トランジスタに限らず、ゲート絶縁膜が酸化膜以外の絶縁膜である場合にも適用できることはもちろんである。すなわち、本発明は、半導体層がアモルファス半導体のみで形成された MIS トランジスタと半導体層が多結晶半導体を有する MIS トランジスタとを有する TFT 基板に適用できる。

## 【 0 1 4 9 】

また、実施例 1 乃至実施例 3 に示したような手順でゲート電極 G P 1 , G P 2 や走査信号線 G L を形成する場合、たとえば、表示領域 D A のゲート電極 G P 1 および走査信号線 G L は、下から MoW 合金 , A 1 , MoW 合金の順に積層された積層配線にし、周辺領域 S A のゲート電極 G P 2 およびその配線は、 MoW 合金の単層の配線にすることが望ましい。

40

## 【 0 1 5 0 】

また、実施例 1 乃至実施例 3 において、表示領域 D A のゲート電極 G P 1 および走査信号線 G L は、同一のプロセスで一括して形成することが望ましい。すなわち、走査信号線 G L は、表示領域 D A のゲート電極 G P 1 と同一の積層構成でゲート電極 G P 1 と一緒に形成されることが望ましい。

## 【 0 1 5 1 】

ゲート電極 G P 1 と走査信号線 G L とは、別のプロセスで形成することも可能であるが、その場合、ゲート電極 G P 1 を加工するためのマスクと、走査信号線 G L を加工するためのマスクの合わせずれを考慮して、画素内の他の構成要素を加工するためのマスクを設

50

計する必要がある。そのため、各マスクのマージンを大きく取る必要があり、その結果として、たとえば、画素の開口率の低下を招くおそれがある。

#### 【0152】

これに対し、ゲート電極G P 1 と走査信号線G L とを同一のプロセスで一括して形成することで、画素内の他の構成要素を加工するためのマスクのマージンを小さくでき、画素の開口率を向上させることができる。

#### 【0153】

また、実施例1乃至実施例3は、たとえば、図1(a)乃至図3に示したような構成の液晶表示パネルのTFT基板1に本発明を適用したときのゲート電極G P 1 , G P 2 の構成および製造方法について説明した。しかしながら、本発明は、このような液晶表示パネルのTFT基板1に限らず、たとえば、有機EL(ElectroLuminescence)を用いた自発光型の表示パネルなどに用いられる基板にも適用できることはもちろんである。

10

#### 【図面の簡単な説明】

#### 【0154】

【図1(a)】液晶表示パネルの概略構成の一例を示す模式平面図である。

20

【図1(b)】図1(a)に示した液晶表示パネルのA-A'線における断面構成の一例を示す模式断面図である。

【図2】本発明の適用が望まれるTFT基板の概略構成の一例を示す模式平面図である。

【図3】液晶表示パネルの1画素の回路構成の一例を示す模式回路図である。

20

【図4(a)】本発明を適用したTFT基板における表示領域のTFT素子の概略構成の一例を示す模式平面図である。

【図4(b)】本発明を適用したTFT基板における周辺回路のMOSトランジスタの概略構成の一例を示す模式平面図である。

30

【図4(c)】図4(a)のB-B'線における断面構成の一例および図4(b)のC-C'線における断面構成の一例を横に並べて示した模式断面図である。

【図5】本発明による実施例1のTFT基板の特徴を示す模式断面図である。

【図6】実施例1のTFT基板のゲート電極の製造方法を説明するための模式断面図である。

【図7(a)】アモルファスシリコン膜を成膜した直後の基板の概略構成を示す模式平面図である。

30

【図7(b)】図7(a)のD-D'線における模式断面図である。

【図7(c)】図7(b)に示した断面図において、周辺領域のMOSトランジスタのゲート電極が形成された領域と表示領域のTFT素子のゲート電極が形成された領域を拡大して並べた模式断面図である。

40

【図8(a)】アモルファスシリコンを多結晶シリコン化する方法の一例を示す模式斜視図である。

【図8(b)】多結晶シリコン化された領域の半導体層の概略構成を示す模式平面図である。

【図9】実施例1のTFT基板の製造方法の作用効果を説明するための模式図である。

40

【図10(a)】実施例1のTFT基板の製造方法の変形例を説明するための模式断面図である。

【図10(b)】実施例1のTFT基板の製造方法の変形例を説明するための模式断面図である。

【図11】実施例1のTFT基板の応用例を説明するための模式断面図である。

【図12】本発明による実施例2のTFT基板の特徴を示す模式断面図である。

【図13】実施例2のTFT基板のゲート電極の製造方法を説明するための模式断面図である。

50

【図14(a)】表示領域のゲート電極と周辺領域のゲート電極との断面構成の一例を示す模式断面図である。

【図14( b )】表示領域の走査信号線と周辺領域の走査信号線の接続部分の断面構成の一例を示す模式断面図である。

【図15】図4( a )に示したTFT素子の平面構成の変形例を説明するための模式平面図である。

【図16( a )】本発明を適用したTFT基板における表示領域のTFT素子の概略構成の他の一例を示す模式平面図である。

【図16( b )】本発明を適用したTFT基板における周辺回路のMOSトランジスタの概略構成の他の一例を示す模式平面図である。

【図16( c )】図16( a )のE-E'線における断面構成の一例および図16( b )のF-F'線における断面構成の一例を横に並べて示した模式断面図である。

10

#### 【符号の説明】

##### 【0155】

1 ... TFT基板

100 ... ガラス基板(マザーガラス)

101 ... 下地絶縁層

102 ... 第1の絶縁層(ゲート絶縁膜)

103 ... 第2の絶縁層

104 ... 第3の絶縁層

105 ... 第4の絶縁層

G P 1 , G P 2 ... ゲート電極

20

S D 1 , S D 1' ... ドレイン電極

S D 2 , S D 2' ... ソース電極

S C 1 , S C 2 ... 半導体層

S C 1 a , S C 2 a , S C 2 d ... ドレイン領域

S C 1 b , S C 2 b , S C 2 e ... ソース領域

S C 1 c , S C 2 c ... チャネル領域

S C a ... アモルファスシリコン膜(アモルファスシリコン)

S C p ... 多結晶シリコン膜(多結晶シリコン)

P X ... 画素電極

30

C T ... 対向電極

D R V 1 ... 第1の駆動回路

D R V 2 ... 第2の駆動回路

D A ... 表示領域

S A ... 周辺領域

2 ... 対向基板

3 ... 液晶材料

4 ... シール材

5 A , 5 B ... 偏光板

601 ... 第1の導電層

602 ... 第2の導電層

40

701 , 702 , 703 , 703 a , 703 b ... レジスト

8 ... レーザ発振器

9 a , 9 b ... 連続発振レーザ

10 ... 光学系

11 p ... 微小結晶

11 w ... 帯状結晶

【図1(a)】

図1(a)

【図1(b)】

図1(b)

【図2】

図2

【図3】

図3

【図4(a)】

図4(a)

【図4(b)】

図4(b)

【図4(c)】

【図5】

【図6】

【図7(a)】

【図7(b)】

【図7(c)】

【図 8 ( a )】

図8(a)

【図 8 ( b )】

図8(b)

【図 9】

【図 10 ( a )】

図10(a)

【図10(b)】

図10(b)

【図12】

図12

【図11】

図11

【図13】

図13

【図14(a)】

図14(a)

【図14(b)】

図14(b)

【図15】

図15

【図16(a)】

図16(a)

【図16(b)】

図16(b)

【図16(c)】

## フロントページの続き

| (51) Int.CI.             | F I            | テーマコード(参考) |

|--------------------------|----------------|------------|

| H 0 1 L 21/20 (2006.01)  | H 0 1 L 29/78  | 6 1 7 M    |

| G 0 2 F 1/1368 (2006.01) | H 0 1 L 21/20  |            |

| G 0 2 F 1/1345 (2006.01) | G 0 2 F 1/1368 |            |

|                          | G 0 2 F 1/1345 |            |

|                          | H 0 1 L 29/78  | 6 2 7 G    |

F ターム(参考) 2H092 GA59 JA26 JA28 KA04 KA05 MA30 NA13 NA27 NA29

5F048 AB10 AC01 BA16 BB01 BB09 BB10 BB11 BB12 BB13 BC15

BC16

5F110 AA16 AA26 BB02 CC08 DD02 DD14 EE03 EE04 EE06 EE14

GG02 GG13 GG15 GG35 HJ01 HJ13 NN78 PP03 PP05 PP06

PP23 PP35 QQ01

5F152 AA02 AA06 BB02 BB03 CC02 CD14 CD17 CE05 CE43 FF03

FF28 FF30 FG01 FH03 FH08