(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5858997号

(P5858997)

(45) 発行日 平成28年2月10日(2016.2.10)

(24) 登録日 平成27年12月25日(2015.12.25)

|                        |                    |

|------------------------|--------------------|

| (51) Int.Cl.           | F 1                |

| HO 1 S 5/026 (2006.01) | HO 1 S 5/026 6 1 6 |

| GO 2 F 1/025 (2006.01) | GO 2 F 1/025       |

| GO 2 B 6/12 (2006.01)  | GO 2 B 6/12 3 0 1  |

請求項の数 11 (全 18 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-518723 (P2013-518723)  |

| (86) (22) 出願日 | 平成23年6月30日 (2011.6.30)        |

| (65) 公表番号     | 特表2013-534059 (P2013-534059A) |

| (43) 公表日      | 平成25年8月29日 (2013.8.29)        |

| (86) 国際出願番号   | PCT/US2011/042633             |

| (87) 国際公開番号   | W02012/003346                 |

| (87) 国際公開日    | 平成24年1月5日 (2012.1.5)          |

| 審査請求日         | 平成26年6月27日 (2014.6.27)        |

| (31) 優先権主張番号  | 12/827,776                    |

| (32) 優先日      | 平成22年6月30日 (2010.6.30)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 506115514<br>ザ リージェンツ オブ ザ ユニバーシティ オブ カリフォルニア<br>アメリカ合衆国 カリフォルニア州 94607 オークランド フランクリン ストリート 1111 トゥエルフス フロア |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                                      |

| (74) 代理人  | 100064908<br>弁理士 志賀 正武                                                                                      |

| (74) 代理人  | 100089037<br>弁理士 渡邊 隆                                                                                       |

| (74) 代理人  | 100110364<br>弁理士 実広 信哉                                                                                      |

最終頁に続く

(54) 【発明の名称】損失変調シリコンエバネセントレーザー

## (57) 【特許請求の範囲】

## 【請求項 1】

損失変調半導体レーザーデバイスであって、

第1の基板上に設けられたセミコンダクター・オン・インシュレーター(SOI)構造であって、前記SOI構造の半導体層に導波路及び前記導波路を前記半導体層の面内方向に挟んで配置された一対のギャップを含む、SOI構造；

前記SOI構造の前記半導体層の上に接合された半導体構造であって、前記半導体構造が、量子井戸層及び前記量子井戸層上に形成されたIII-V族半導体層またはII-VI族半導体層を含み、前記半導体構造が前記導波路及び前記一対のギャップの上に接合され、前記半導体構造と前記導波路とが併せてレーザーキャビティの少なくとも一部を画定する、半導体構造；並びに

前記レーザーキャビティ内の損失を制御するように動作可能である変調器であって、前記変調器の全体が前記レーザーキャビティ内に配置され、前記変調器が前記損失変調半導体レーザーデバイスの群速度、キャビティの長さ及び分布損失の少なくとも1つを制御することにより、前記損失変調半導体レーザーデバイス内の光子の寿命を制御するようにさらに動作可能であり、前記変調器が前記導波路に近接するn型ドープされた領域及びp型ドープされた領域を含み、前記n型ドープされた領域が前記一対のギャップのうち一方のギャップの下部にあり、前記p型ドープされた領域が前記一対のギャップのうち他方のギャップの下部にある、変調器、を含む、

損失変調半導体レーザーデバイス。

10

20

**【請求項 2】**

前記 n 型ドープされた領域及び前記 p 型ドープされた領域の少なくとも 1 つが前記半導体層内に配置された、請求項 1 に記載の損失変調半導体レーザーデバイス。

**【請求項 3】**

前記半導体層がシリコンを含む、請求項 1 に記載の損失変調半導体レーザーデバイス。

**【請求項 4】**

前記損失変調半導体レーザーデバイスの光学モードが、前記半導体層及び前記半導体構造の少なくとも一部の内部に存在する、請求項 1 に記載の損失変調半導体レーザーデバイス。

**【請求項 5】**

前記変調器が前記導波路の第 1 の部分をさらに含み、前記 n 型ドープされた領域及び前記 p 型ドープされた領域が、前記第 1 の部分内のキャリア密度を制御するように動作可能である、請求項 1 に記載の損失変調半導体レーザーデバイス。

**【請求項 6】**

前記変調器が前記レーザーキャビティ内の分布損失を制御するように動作可能である、請求項 1 に記載の損失変調半導体レーザーデバイス。

**【請求項 7】**

前記半導体層がシリコンを含み、前記半導体層内の導波路が前記半導体構造とエバネセント的に結合された、請求項 1 に記載の損失変調半導体レーザーデバイス。

**【請求項 8】**

前記半導体層がシリコンを含み、前記半導体層内の前記導波路が前記半導体構造とエバネセント的に結合された、請求項 1 に記載の損失変調半導体レーザーデバイス。

**【請求項 9】**

半導体構造と S O I 構造の半導体層とを接合する段階であって、前記半導体構造が増幅領域及び前記増幅領域上に形成された I I I - V 族半導体層または I I - V I 族半導体層を含み、前記半導体層が第 1 の導波路及び前記第 1 の導波路を前記半導体層の面内方向に挟んで配置された一対のギャップを含み、前記接合された半導体構造及び前記半導体層が共にレーザーキャビティを有するハイブリッドレーザー構造の少なくとも一部を画定する段階；並びに

前記第 1 の導波路に近接した n 型ドープされた領域及び p 型ドープされた領域を形成し、前記 n 型ドープされた領域が前記一対のギャップのうち一方のギャップの下部にあり、前記 p 型ドープされた領域が前記一対のギャップのうち他方のギャップの下部にあり、前記 n 型ドープされた領域、前記 p 型ドープされた領域と前記第 1 の導波路とが併せて前記レーザーキャビティ内に全体的に配置された変調器を画定し、前記レーザーキャビティ内の損失を制御するように動作可能である、n 型ドープされた領域及び p 型ドープされた領域を形成する段階を含む、損失変調半導体レーザーデバイスを製造する方法。

**【請求項 10】**

前記変調器が、前記損失変調半導体レーザーデバイス内の群速度、キャビティの長さ及び分布損失のうち少なくとも 1 つを制御することによって、前記損失変調半導体レーザーデバイス内の光子の寿命を制御するように動作可能であるように形成される、請求項 9 に記載の方法。

**【請求項 11】**

前記 S O I 構造の前記半導体層を、シリコンを含むように提供する段階をさらに含む、請求項 9 に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、一般的には半導体デバイスに関し、より具体的には、損失変調シリコンエバネセントレーザーに関する。

**【背景技術】**

10

20

30

40

50

## 【0002】

米国連邦政府による資金提供を受けた研究開発の記載

本発明は、DARPAによって提供された助成金番号482530-25615の下で米国連邦政府の支援で行われた。米国連邦政府は、本発明について特定の権利を有する。

## 【0003】

本出願に関する相互参照

本出願は、以下の同時係属出願及び譲受人に譲渡された出願の合衆国法典35編119条(e)における優先権を主張する: 2010年6月30日に、John E. Bowers及びDixon Daiによって出願された、「損失変調シリコンエバネセントレーザー」と題する、代理人整理番号30794.382-US-01、米国実用特許出願第12/827776。この出願は、参照によって本明細書に組み込まれている。

10

## 【0004】

半導体チップレベル接合されたデバイスが、複数の消費者及び商業用途で用いられるようになっている。典型的には、半導体デバイスは、単一の種類の材料からなり、または異なる種類の材料が、結晶構造に適合する結晶格子に基づいて、基板上に成長される。そのような、周期表のIII族及びV族からなる半導体材料(III-V材料)から製造されるデバイスは、典型的にはガリウムヒ素または他の組成の半導体基板上に成長され、シリコンデバイスはシリコン基板上に成長または形成される。シリコンとIII-V材料との間の結晶格子の不適合及び結晶構造の不適合のために、III-V材料系デバイスは、シリコン上に形成された電子デバイスと集積することが困難である。

20

## 【0005】

光学伝送器は、あらゆる光学通信システムにおいて最も重要な素子の1つである。典型的には、光学伝送器は、周期表のIII族及びV族(III-V)半導体材料、例えばガリウムヒ素(GaAs)で形成される。シリコン(Si)が、典型的には電子通信システムに用いられるが、シリコンを光子(光)放出に不向きにさせる間接バンドギャップを有し、そのためシリコンは光学伝送応用において良好な性能を発揮しないため、典型的にはこのような材料が用いられる。間接バンドギャップ及びその結果のシリコンの低い光放出は、電気的励起Si系レーザーの実現を制限してきた。これは光学伝送器及びSi系光学通信システムに対する鍵となる素子の1つである。

30

## 【0006】

シリコンは様々な方法で容易に加工することができ、既に高品質、低成本で利用可能であり、通信システムのための電子回路を支持する複合体が既にシリコンで利用可能であるため、シリコンは好適な半導体材料である。近年、低成本光電子ソリューションの可能性のために、シリコンフォトニックデバイス(例えば光子を放出するシリコンデバイス)が幅広く研究されている。製造がシリコン系電子部品、特に相補型金属酸化膜半導体(CMOS)プロセスと互換性があるため、シリコンフォトニックデバイスは、III-V材料に対してデバイスコストを低減するであろう。

## 【0007】

近年、III-V活性領域及びシリコン光学導波路を組み合わせるハイブリッド構造が、電気的励起シリコン系レーザーの解決方法として実施されている。このようなデバイスは、105までの温度、30mWまでの連続波出力、40Gbit/sのモードロッキングでの連続波レーザー出力(レージング)を含む、多くの好適な特性を有する。このようなハイブリッドIII-Vシリコン「エバネセント」構造は、シリコン・オン・インシユレーター(SOI)ウェハに接合されたIII-V量子井戸領域を、Si層におけるトレーナによって画定された光学導波路とともに含む。この方法で、ハイブリッド構造は、逆リッジ導波路のように振る舞う。このようなデバイスは、デバイスの光学モードがIII-V/シリコン境界と交差するためにデバイス内のIII-V構造とシリコン構造との間の遷移が接合後に消滅する傾向にある場合には、「エバネセント」と呼ばれる。

40

## 【0008】

このようなレーザーが現在可能であるが、このようなデバイスで実現される光学伝送器

50

に関して、光学信号の高速変調もまた望まれている。注入される励起電流の直接変調は、そのような問題に対する単純なアプローチであるが、注入電流が増加するにつれて、消滅比が減少するため、印加可能な注入電流の量が制限される。さらに、直接変調は典型的には 10 GHz よりも小さい速度に限られており、直接変調によって導入される波長の「チャーブ」のために、直接変調信号の伝送距離が限られる。電流の直接変調もまた、レーザーの増幅率を変化させ、このことによってレーザーの光出力が変化し、その全てが通信システムにおける望ましいデバイス特性となるわけではない。

【0009】

外部変調器もまた、変調率及び伝送距離の拡張を決定するために評価されてきた。マッハ・ツエンダー干渉 (MZI) 変調器は、大型 (ミリメートルサイズ) のデバイスであるが、導波路内のキャリア空乏を通して変調率及び伝送距離を増大させることができるのであり、このことにより、高速屈折率変調が導入される。しかしながら、このような変調器は、その比較的大きなサイズのために、シリコン及び / またはハイブリッドデバイスと共に集積することが困難である。

10

【0010】

そこで、当技術分野において、光学伝送システムにおいて用いることのできるシリコン系レーザーが必要であることが分かる。また、当技術分野において、シリコン系レーザーと変調器との間の集積が必要であることが分かる。さらに、当技術分野において、半導体レーザーデバイスと共に容易に集積可能である変調技術が必要であることが分かる。

20

【先行技術文献】

【特許文献】

【0011】

【特許文献 1】米国特許出願第 11/534560 号明細書

【発明の概要】

【発明が解決しようとする課題】

【0012】

従来技術の制限を最小化し、本明細書を読み、理解するうえで明らかになるその他の制限を最小化するために、本発明は、損失変調レーザーの製造方法及び損失変調レーザーデバイスを提供する。

【課題を解決するための手段】

30

【0013】

本発明の 1 つまたは複数の実施形態に従う損失変調半導体レーザーデバイスは、第 1 の基板上に設けられたセミコンダクター・オン・インシュレーター (SOI) 構造であって、前記 SOI 構造の半導体層内に導波路を含む SOI 構造；及び前記 SOI 構造の前記半導体層に接合された半導体構造を含み、前記 SOI 構造の前記半導体層内の少なくとも 1 つの領域が、内部の光子の寿命を制御する。

【0014】

このようなデバイスはさらに任意に、前記導波路に近接した少なくとも 1 つのドープされた領域である前記 SOI 構造の前記半導体層内の少なくとも 1 つの前記領域、前記導波路の第 1 の側部上において n 型ドープされた領域及び前記導波路の第 2 の側部において p 型ドープされた領域である前記導波路に近接する少なくとも 1 つのドープされた領域、半導体層内及び前記半導体構造の少なくとも一部に存在する前記損失変調半導体レーザーデバイスの光学モード、前記損失変調半導体レーザーデバイスの分布損失を制御する前記 n 型ドープされた領域及び前記 p 型ドープされた領域、並びに前記損失変調半導体デバイスの光学キャビティ内における分布損失を制御する少なくとも 1 つの前記ドープされた領域を含む。

40

【0015】

このようなデバイスはまたさらに任意に、前記損失変調半導体レーザーデバイスの増幅領域に接続された光学フィードバック線である前記 SOI 構造の前記半導体層における少なくとも 1 つの前記領域、前記光学フィードバック線に接続され、前記損失変調半導体レ

50

ーバイスの前記増幅領域への光学フィードバックを制御するための変調区域、前記光学フィードバック線における信号の位相及び強度のうち少なくとも1つを制御する前記変調区域及び、前記損失変調半導体レーザーデバイスを変調する損失変調半導体レーザーデバイスのフィードバック係数を制御する前記光学フィードバック線を含む。

【0016】

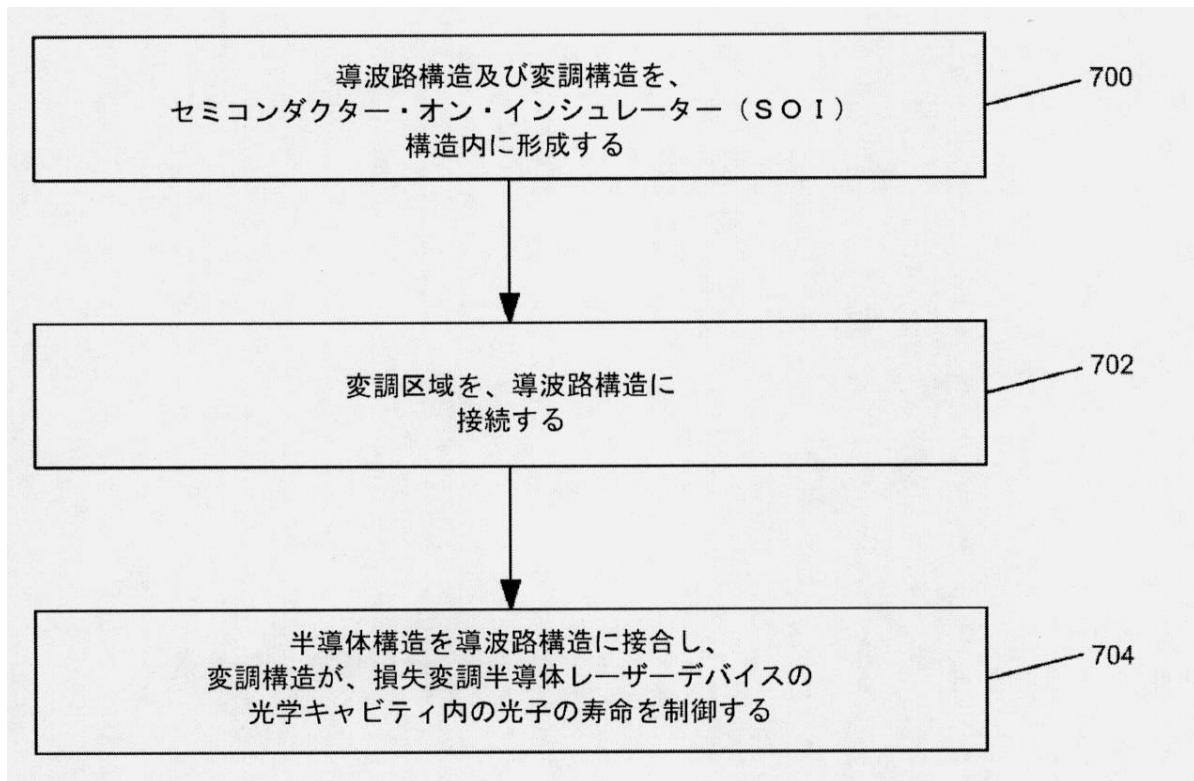

本発明の1つまたは複数の実施形態に従う損失変調半導体レーザーデバイスを製造する方法は、セミコンダクター・オン・インシュレーター（SOI）構造内に導波路構造及び変調構造を形成する段階、前記変調区域を前記導波路構造に接続する段階及び半導体構造を前記導波路構造に接合する段階を含み、前記変調構造が、前記損失変調半導体レーザーデバイスの光学キャビティ内における光子の寿命を制御する。

10

【0017】

このような方法はさらに任意に、前記導波路構造に、光学フィードバック線を介して接続される前記変調区域、前記SOI構造の半導体層内における少なくとも1つのドープされた領域である前記変調区域並びに、前記損失変調半導体レーザーデバイス内における分布損失及びフィードバック係数の少なくとも1つを制御する前記変調区域を含む。

【0018】

本発明の1つまたは複数の実施形態に従う半導体レーザーは、導波路及び変調領域を含む半導体層を含むセミコンダクター・オン・インシュレーター（SOI）領域並びに前記SOI領域の前記半導体層に接合されたIII族-V族（III-V）領域を含み、前記変調領域が、前記半導体レーザー内の光子の寿命を制御することによって、前記半導体レーザーの出力を変調する。

20

【0019】

のようなレーザーはさらに任意に、光学遷移システム内で動作する前記半導体レーザー、前記半導体層内における少なくとも1つのドープされた領域である前記変調領域、シリコンを含む前記SOI構造の前記半導体層、光学フィードバック線の位相遅延を制御する前記変調領域及び光学フィードバック線の強度を制御する前記変調領域を含む。

【0020】

本発明の1つまたは複数の実施形態に従う半導体レーザーデバイスは、光学キャビティを有する第1の導波路構造を含み、前記半導体レーザーデバイスの前記光学キャビティ内の損失が変調される。

30

【0021】

このような半導体レーザーデバイスはさらに任意に、前記光学キャビティに接続されたミラーを用いて変調される前記光学キャビティ内の前記損失、前記ミラーの実効反射率を変調することによって変調される前記光学キャビティ内の前記損失、前記光学キャビティに接続される第2の導波路構造で変調され、前記第2の導波路内の光が前記第1の導波路構造内の光と干渉する前記光学キャビティ内の前記損失、前記第1の導波路に接続された第2の導波路内に延長する前記半導体レーザーデバイスの光学モード、前記第2の導波路内の損失を変調することによって変調される前記光学キャビティ内の前記損失を含む。

【0022】

その他の特徴及び利点は、開示されるシステム内に備わっており、または以下の詳細な説明および添付する図面から当業者に対して明らかになるものである。

40

【0023】

ここで、全体を通して類似した参照番号は対応する要素を指す図面を参照する。

【図面の簡単な説明】

【0024】

【図1】関連する技術分野のハイブリッド構造の断面図を示す。

【図2】本発明の損失変調ハイブリッドレーザーの一実施形態の断面図を示す。

【図3】図2に示される本発明の実施形態の電流の流れ及び光学モードを示す。

【図4】本発明の損失変調ハイブリッドレーザーの他の一実施形態を示す。

【図5】本発明に従う<sub>p</sub>変調レーザーの周波数応答の計算結果を示す。

50

【図6A】本発明に従って製造されたデバイスの閾値より高い電流の平方根としての3dB帯域幅を示す。

【図6B】本発明に従って製造された<sub>p</sub>変調レーザーについて数値計算されたアイダイアグラムを示す。

【図7】本発明に従うプロセスチャートを示す。

【発明を実施するための形態】

【0025】

以下の説明において、本明細書の一部分を構成し、本発明のいくつかの実施形態を図示によって示す添付図面を参照する。その他の実施形態を利用してもよく、構造の変更が、本発明の範囲を逸脱しないように行われてもよい。

10

【0026】

概略

本発明は、ハイブリッドシリコンエバネセントレーザーの直接変調を記載する。レーザーに対する電流の変化よりもむしろ、本発明は、相対的に固定された量に電流を保ち、キャビティの損失が変調される。このようなアプローチにより、出力のより高速な変調が可能となるとともに、レーザー出力照度均一性（「パターン効果」としても知られる）及びレーザー出力におけるレーザー出力周波数の変化（「チャーブ」）を制御することが可能となる。

【0027】

本発明の損失変調アプローチの範囲内で、安定性を実現し、望ましくない出力効果を低減するために、増幅及び/または注入電流もまた変更されて出力を補償することが可能である。

20

【0028】

本発明はまた、小型の内部変調器でレーザーの変調を行うことを意図し、このことにより、小型のシリコン系光学伝送器を従来技術よりも容易に集積して実現する。本発明に示された技術を通して、レーザーキャビティ内の光子の寿命が変化されて、それまでに設計されたシステム及びデバイスに対して、高い変調率を実現し、光学伝送器の周波数の変化を最小化させる。

【0029】

本明細書に示される技術を通して伝送器に存在するチャーブを減少させることにより、本発明は、パワー出力を安定させ、そのためより長い伝送距離を可能とし、さらに、そうでなければ光学システム内の保護帯域またはその他のチャンネルサイジング問題のために必要とされるであろう信号伝送のために利用可能な追加的な帯域幅を提供する。チャーブの低いシステムにおいてはビットエラーレートが減少するため、チャーブの低いシステムによれば、より高いデータのスループットも可能となる。本明細書では特定のIIII族-V族(IIII-V)材料、つまり、インジウムリン(IndP)、インジウムガリウムヒ素(IndGaAs)などについて記載されているが、IIII-V類の範囲内で、他の2元系、3元系、4元系、またはその他の組み合わせの材料、さらにII-VIまたはその他の材料を、本発明に従って用いることが可能である。

30

【0030】

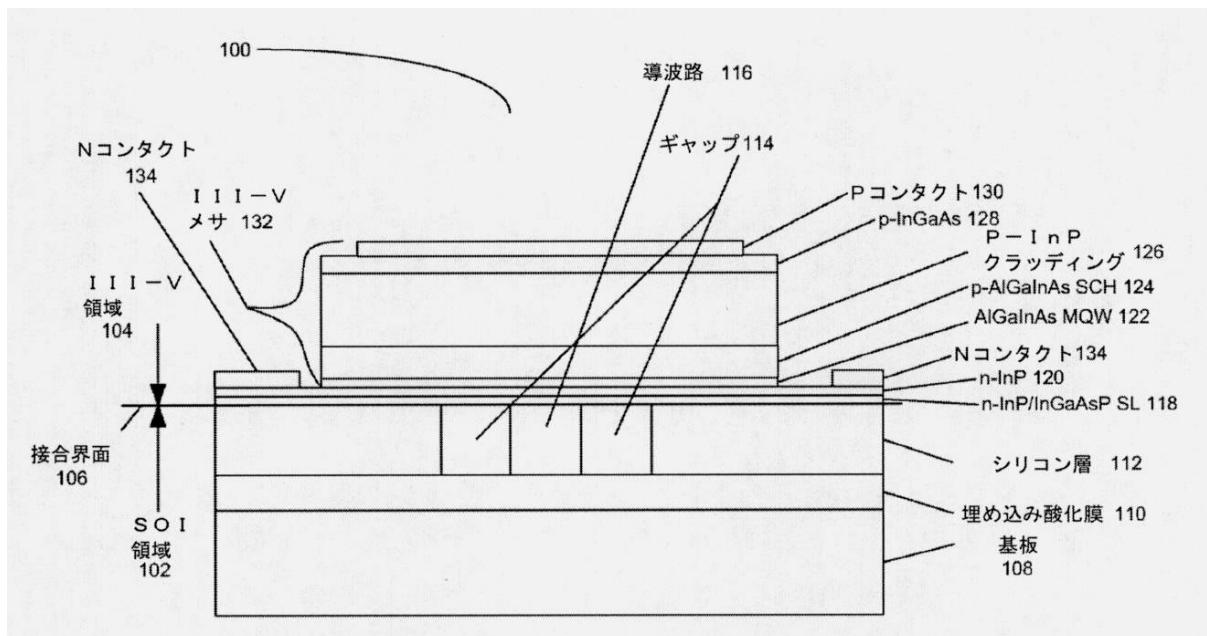

図1は、関連する技術分野のハイブリッド構造を示す。

40

【0031】

接合界面106においてIIII族-V族(IIII-V)領域104に接合されたシリコン・オン・インシュレーター(SOI)領域102を有するデバイス100が示されている。SOI領域は典型的には、シリコン基板108、埋め込み酸化膜層110及びシリコン層112を含み、これは、デバイス100の場合には、シリコン導波路層112であるが、本発明の範囲内で、その他の材料または材料プラットフォームを用いることができる。基板108は、本発明の範囲を逸脱しないように、好適にシリコン以外の材料から形成することができる。

【0032】

50

シリコン導波路 112 は、導波路 116 がギャップ 114 の間にるように、1つまたは複数のギャップ 114 を有する。デバイス 100 内の光学信号は、導波路 116 に沿って進み、デバイスの光学モードは典型的には導波路 116 内に含まれる。

#### 【0033】

##### 損失変調

本発明は、光子の寿命  $\tau_p$  を変調する。寿命変調を通したレーザー出力制御のこの方法を通して、本発明は、高速変調を低いチャープと共に実現する。

#### 【0034】

##### 理論および構造

本発明の範囲内で、レーザー内の光子の寿命  $\tau_p$  を変更するいくつかの方法が存在する。本発明は、群速度  $v_g$ 、キャビティ長  $l$ 、フィードバック係数  $R$  及び分布損失  $\alpha$  の1つまたは複数を変更することにより、光子の寿命を変更する。これらのアプローチのうち、2つの簡単で効果的な方法が、分布損失  $\alpha$  及びフィードバック係数  $R$  の変更である。本発明は、 $\alpha$  及び  $R$  の変更に対応する、2つの方法を示す。

#### 【0035】

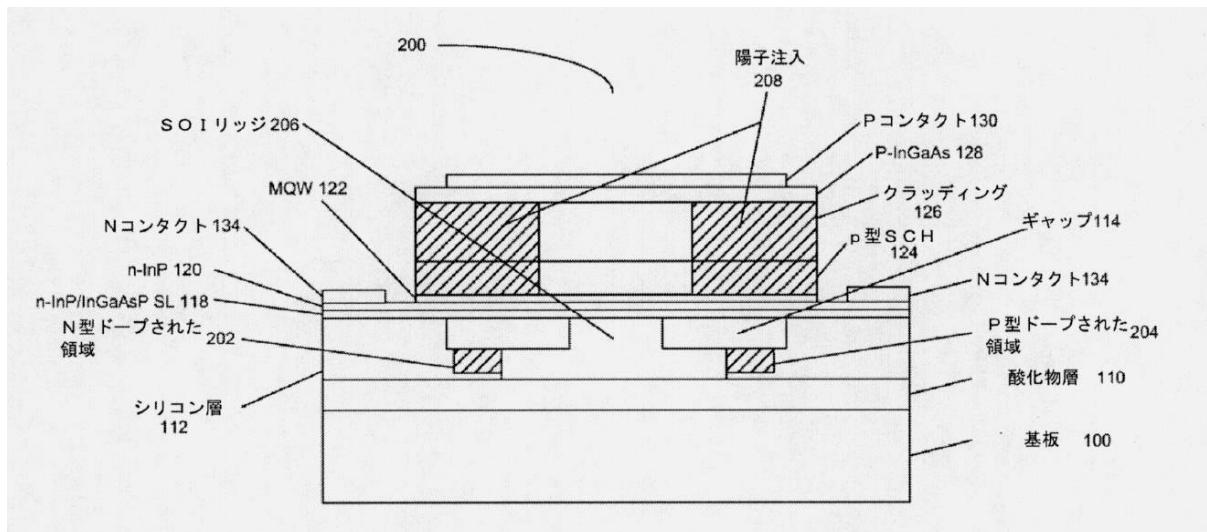

図2は、本発明の損失変調ハイブリッドレーザーの実施形態を示す。

#### 【0036】

デバイス 200 が示され、シリコン層 112 には、n型ドープされた領域 202 及び p型ドープされた領域 204 が、ギャップ 114 の下部に位置する。このことによって、デバイス 200 は、 $\tau_p$  変調ハイブリッド II III VSi エバネセントレーザー 200 とも称されるが、デバイス 200 内で分布損失  $\alpha$  を変更することが可能になる。領域 202 及び 204 の追加によって、デバイス 200 内に追加的な p-n 接合が形成される。層 120 及び III - V メサ 132 における層 124 によって形成された P-N 接合は、増幅領域に対して電荷注入部（励起部）として用いられる。領域 202 及び 204 によって形成される、SOI リッジ 206 の2つの側部における第2の P-N 接合は、領域 202 及び 204 を渡って印加される外部信号を有し、領域 202 及び 204 は SOI リッジ 206 内のキャリア密度の空乏化による変調信号を提供する。要約すれば、領域 202 及び 204 は、デバイス 200 内部のデバイス 200 に対する変調区域として働く。デバイス 200 のこのような構造によって、本発明は、微小リングキャビティまたはファブリーペロー（FP）キャビティアプローチに基づく高速ハイブリッドレーザー変調器を提供する。望む場合には、対称場を提供せず、2つまたはそれ以上の領域 202 および 204 を有する場合のように制御可能ではない可能性があるアプローチであるが、ドープされた領域 202 または 204 の一方のみ、例えばドープされた領域 202 のみが、導波路内の変調を提供するように用いられることもできる。

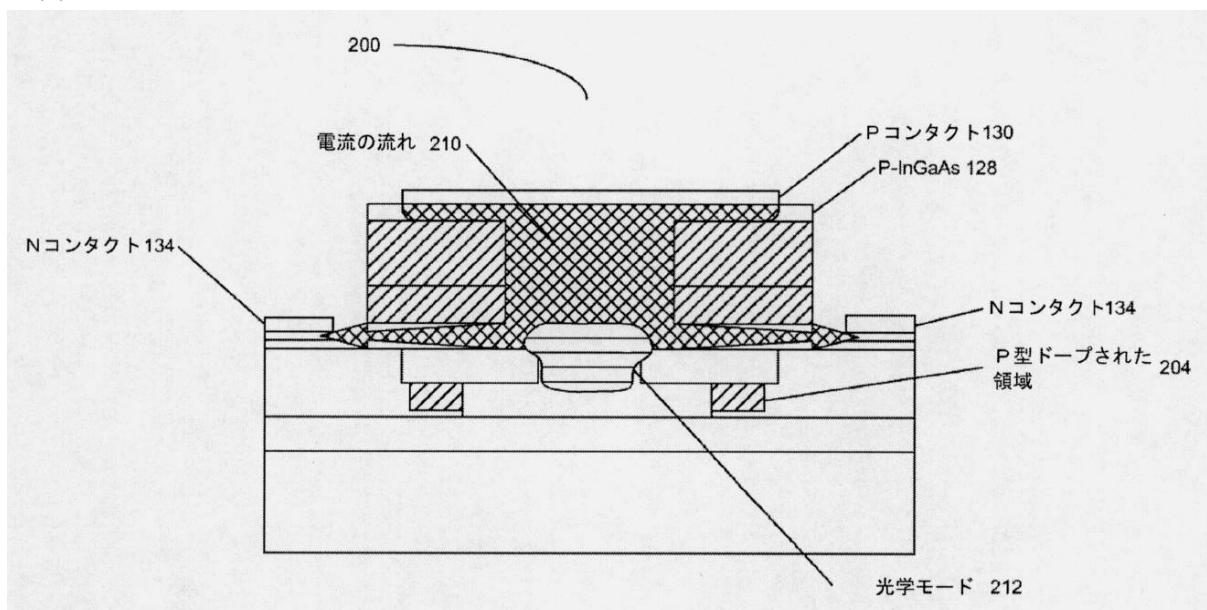

#### 【0037】

p コンタクト 130 から n コンタクト 134 への電流は、クラッディング層 126 及び SCH 層 124 を通し、陽子注入領域 208 を通して導かれる。デバイス 200 に対する電流の流れ 210 及び光学モード 212 が、明確化のために図3に示されている。

#### 【0038】

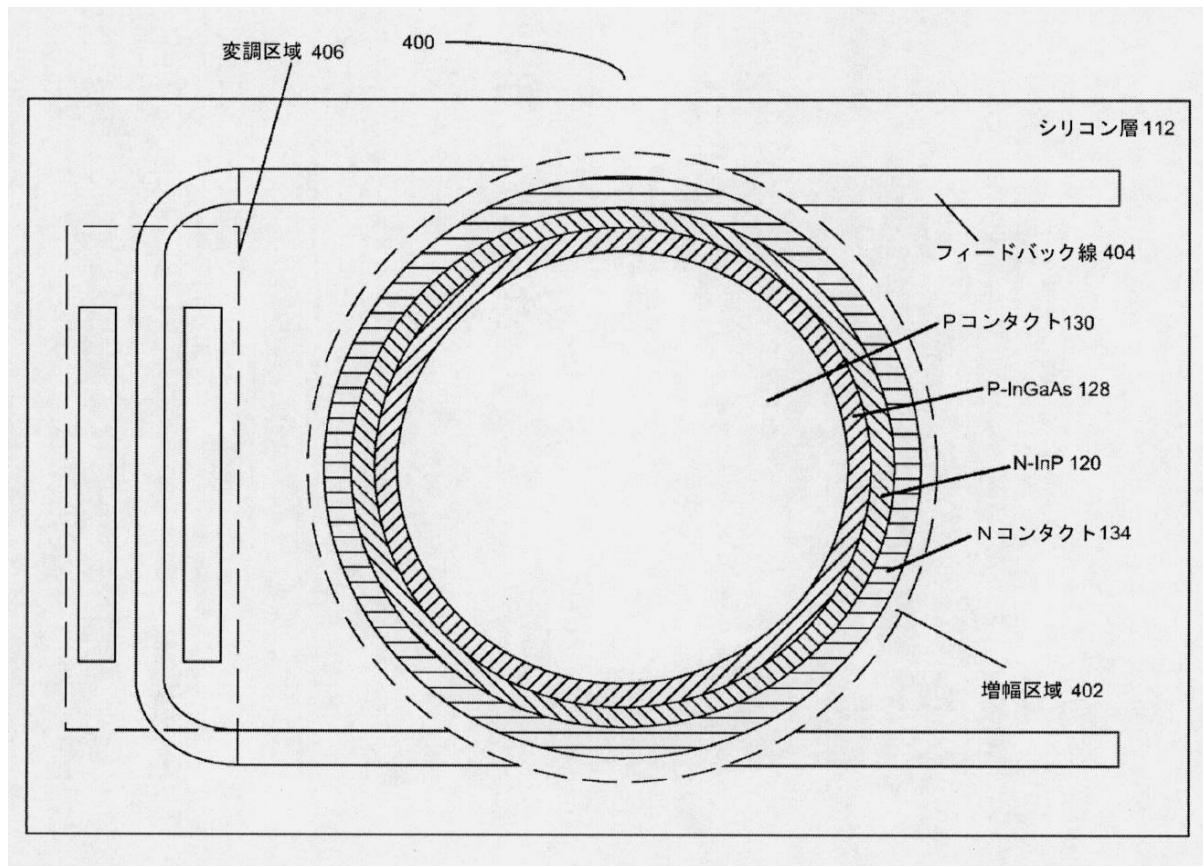

図4は、本発明の損失変調ハイブリッドレーザーの他の実施形態を示す。

#### 【0039】

デバイス 400 が、上面視で示され、増幅区域 402、フィードバック線 404 及び変調区域 406 が示される。増幅区域は図2及び3で示されたのと類似しており、そこでは p コンタクト 130、p - InGaAs 層 128 及び n - InP 層 120 を III - V メサ内に見ることができ、n コンタクト 134 もまた III - V メサを取り囲んで示され、シリコン層 112 もまた、上面透視によって見ることができる。

#### 【0040】

デバイス 400 において、フィードバック線 404（シリコン層 112 内）は、増幅領域 402 を通して、微小リング光学フィードバック線となり、関連する技術分野の微小リングレーザー構造で用いられるのと類似した増幅を提供する。変調区域 406 内のフィー

10

20

30

30

40

40

50

ドバック線 404 上の光波の位相遅延及び / または強度を変更することにより、フィードバック係数  $R$  が変更され、その結果としてデバイス 400 において  $\text{p}_\text{p}$  变調が得られる。例えば P N 接合をシリコン層 112 内に配置し、領域 202 及び 204 について上述したように P N 接合内のキャリアを注入 / 空乏化することにより；光学場がキャリアの I II - V 層内への注入または空乏化により閉じ込められる領域内のキャリア密度を変更することができる、電子吸収区域、例えば I II - V 層をシリコン層 112 の上に配置し、それによりデバイス 400 の吸収をデバイス 400 の屈折率と共に変更することにより；及び電場の電気光学材料への付加が電気光学材料の屈折率を変化させそれによって導波路内の光の位相を変調するような電気光学材料をシリコン導波路と組み合わせることによって、位相遅延及び / または強度を変更することができる。このような構造は、本明細書で説明されるように、InGaAsP レーザーのような他の材料に基づくプラットフォームと同様にハイブリッド I II - V Si プラットフォームデバイスに対して用いることが可能である。10

#### 【0041】

測定及び計算されたデバイスの特性

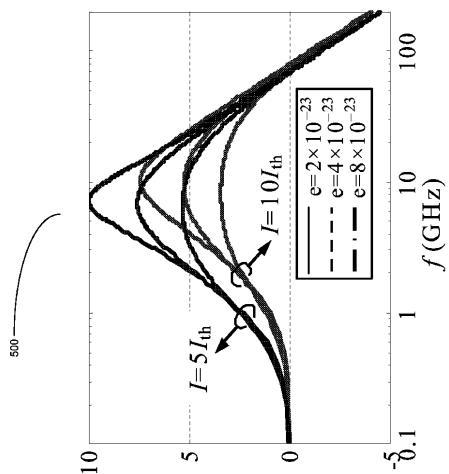

図 5 は、本発明に従う  $\text{p}_\text{p}$  变調レーザーの周波数応答の計算結果を示す。

#### 【0042】

グラフ 500 は、周波数に対する  $10 \log [s(\text{---})s(0)]$  のデシベルでの小信号モデルのグラフを示し、本発明のデバイス 200 から 400 の周波数応答を与える。  $I = 5 I_{th}$  ( $I_{th}$  はデバイスの閾電流値) の場合及び  $I = 10 I_{th}$  の場合に対するイプシロンの様々な値である。グラフ 500 は、本発明のデバイス 200 から 400 の帯域が高い帯域 ( $> 100 \text{ GHz}$ ) を有することができることを示している。20

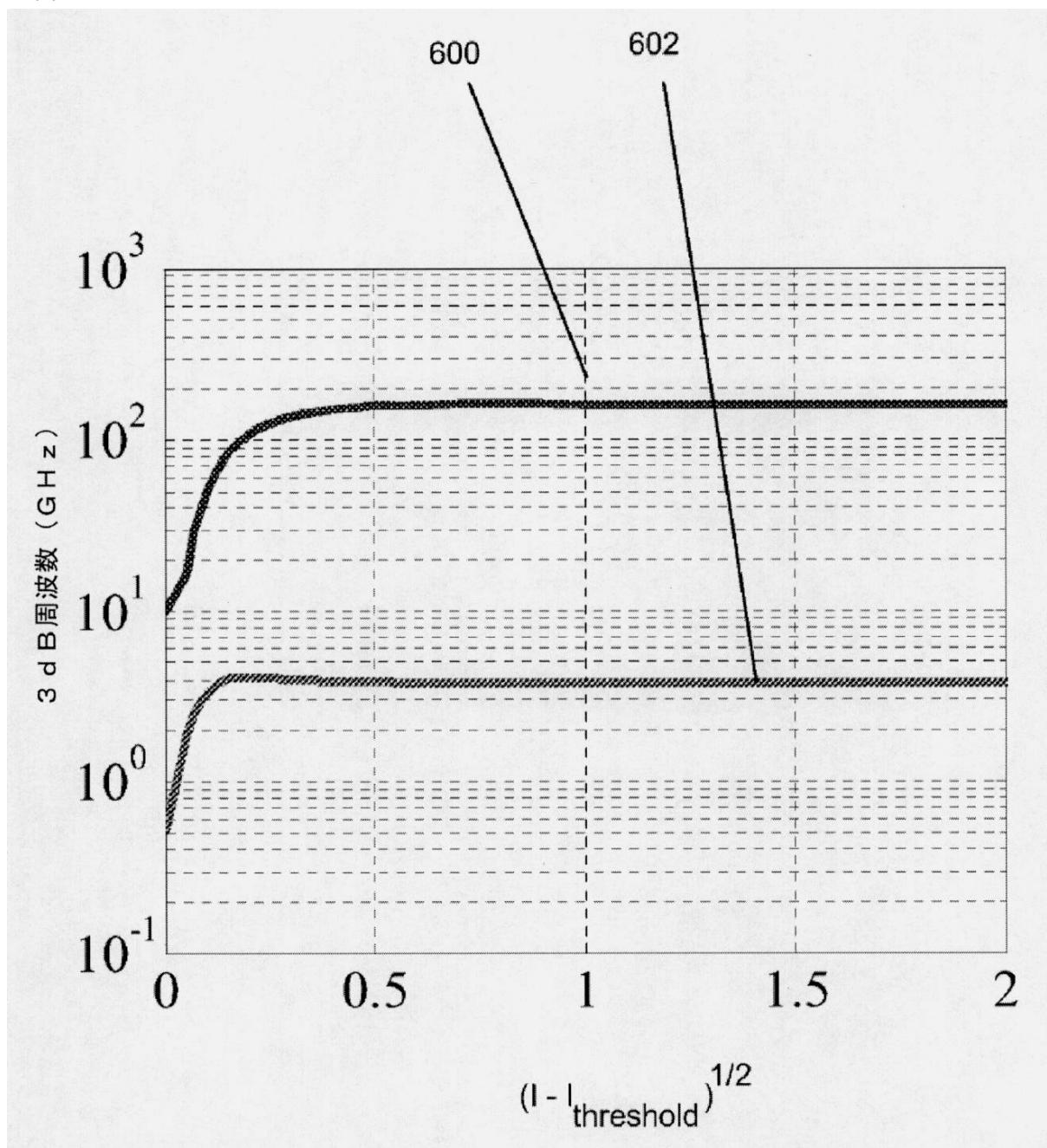

#### 【0043】

図 6 A には、閾値より上の電流の平方根としての 3 dB 帯域幅が示されている。グラフ 600 は、本発明のデバイス 200 から 400 について帯域を示し、グラフ 602 は、比較のために、関連する技術分野の直接電流変調レーザーについて帯域を示している。図 6 A は、 $\text{p}_\text{p}$  变調レーザーについて 3 dB 帯域 ( $100 \text{ GHz}$  超) が、同じデバイス構造で直接電流変調の場合のそれ ( $< 10 \text{ GHz}$ ) よりもはるかに高いことを示している。

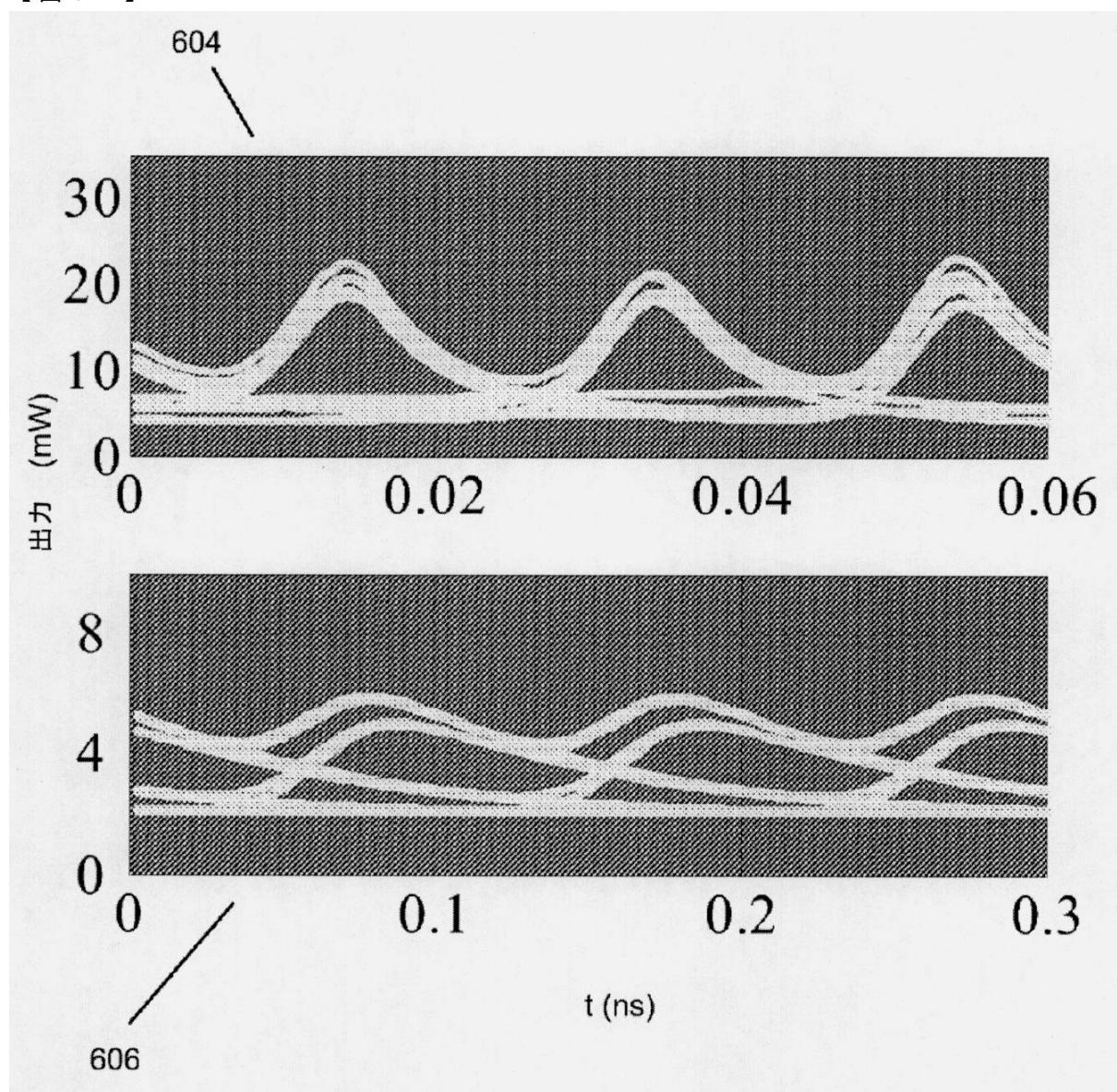

#### 【0044】

時間領域における応答についての数値解析によって、我々は、図 6 B に示されるような、この  $\text{p}_\text{p}$  变調レーザーについての数値計算されたアイダイアグラム 604 を得る。この計算について、光子の寿命は、 $50 \text{ Gb/s}$  のビットレートで、ガウシアン型パルス変調を有する。デバイスのオン状態及びオフ状態に対して  $\text{p}_\text{on} = 1.073 \text{ ps}$  及び  $\text{p}_\text{off} = 1.788 \text{ ps}$  並びに一定 ( $I_0 = 0.15 \text{ A}$ ) に保たれた注入電流で、図 6 B は、 $50 \text{ Gb/s}$  における動作についてのアイダイアグラム 604 に目が開くことを示している。図 6 A は、より高いビットレートも、本発明の範囲内で可能であることを示している。比較のために、選択されたオン状態及びオフ状態について、それぞれ  $I_{on} = 0.15 \text{ A}$  及び  $I_{off} = 0.05 \text{ A}$  の電流で、 $10 \text{ Gb/s}$  のビットレートでの従来の I 变調レーザーについてのアイダイアグラム 606 も示されている。数値計算結果は、 $\text{Gb ps}$  のデータレートを達成できることを示している。しかしながら、アイダイアグラム 606 は、比較的高いビットレート (例えば、 $10 \text{ Gb/s}$ ) では閉じてしまう。30

#### 【0045】

代替的な構造

その他の構造が、本発明で議論される変調損失を提供することができる。例えば、しかしながら限定するものではなく、分布プラグ反射体 (DBR) 及びその他のレーザー構造において共通の、增幅領域 (MQW122) 及びミラー構造を含み、ここで、ミラーの実効反射率が、上述のように SOI リッジ 206 / 光学キャビティ 210 内の損失を変調するために領域 204 及び 202 を用いるのと同様に、レーザーキャビティ / SOI リッジ 206 の損失を変調するために変調することができるレーザー構造である。そのような変調は、いくつかの方法、例えば、光学キャビティ内で導波路 / SOI リッジ 206 と接4050

続する第2の導波路を用いて制御することができ、このとき、第2の導波路の光が重ね合わせ及び/または干渉を通じて光学キャビティ210内の光を変調し、またはSOIリッジの光学モードの一部が、第2の導波路/SOIリッジ206内に延設して損失が本明細書で説明されたように変調されることができる。そのような構造は、例えば特許文献1に示され、この出願は本明細書に参照によって組み込まれている。本明細書の教示で与えられるその他の方法もまた可能である。

【0046】

プロセスチャート

図7は、本発明に従うプロセスチャートを示す。

【0047】

ボックス700は、導波路構造及び変調構造をセミコンダクター・オン・インシュレーター(SOI)構造内に形成する段階を示す。

【0048】

ボックス702は、変調区域を導波路構造に接続する段階を示す。

【0049】

ボックス704は、半導体構造を導波路構造に接合する段階を示し、ここで、変調構造は、損失変調半導体レーザーデバイスの光学キャビティ内の光子の寿命を制御する。

【0050】

参照文献

以下の参照文献は、参照によって本明細書に組み込まれている。

【0051】

Hsu-Hao Changら著，“1310nmシリコンエバネセントレーザー”，Opt. Expr. 15, 11466-11471 (2007). Y-H Kuoら著，“高速ハイブリッドシリコンエバネセント電子吸収変調器”，Optics Express 16 (13), 9936-9941, June 20 (2008).

【0052】

H. Parkら著，“ハイブリッドAlGaNAs-シリコンエバネセント導波路光検出器”，Optics Express, 15 (10), pp. 6044-6052, May (2007).

【0053】

R. S. Tucke r著，“半導体レーザーの高速変調”，J. Lightwave Technol. 3: 1180-1192 (1985).

【0054】

A. S. Liuら著，“シリコン導波路内のキャリア空乏に基づく高速光学変調”，Opt. Expr. 15, 660-668 (2007).

【0055】

J. E. Bowers, B. R. Hemenway, A. H. Gnauck, D. P. Wilt著，“高速InGaAsP抑制メサレーザー”，IEEE J. Quantum Electron. 22, 833-843 (1986).

【0056】

結論

要約すれば、本発明の実施形態は、損失変調レーザーを製造する方法及び損失変調レーザーデバイスを提供する。

【0057】

本発明の1つまたは複数の実施形態に従う損失変調半導体レーザーデバイスは、第1の基板上に設けられたセミコンダクター・オン・インシュレーター(SOI)構造であって、SOI構造の半導体層内に導波路を含むSOI構造及びSOI構造の半導体層に接合された半導体構造を含み、SOI構造の半導体層内の少なくとも1つの領域が、半導体レーザーデバイス内部の光子の寿命を制御する。

【0058】

10

20

30

40

50

このようなデバイスはさらに任意に、導波路に近接した少なくとも1つのドープされた領域であるS O I構造の半導体層内の少なくとも1つの領域、導波路の第1の側部上においてn型ドープされた領域及び導波路の第2の側部においてp型ドープされた領域である導波路に近接する少なくとも1つのドープされた領域、半導体層内及び半導体構造の少なくとも一部に存在する損失変調半導体レーザーデバイスの光学モード、損失変調半導体レーザーデバイスの分布損失を制御する、n型ドープされた領域及びp型ドープされた領域、並びに損失変調半導体デバイスの光学キャビティ内における分布損失を制御する少なくとも1つのドープされた領域を含む。

【0059】

このようなデバイスはまたさらに任意に、損失変調半導体レーザーデバイスの増幅領域に接続された光学フィードバック線であるS O I構造の半導体層における少なくとも1つの領域、光学フィードバック線に接続され、損失変調半導体レーザーデバイスの増幅領域への光学フィードバックを制御するための変調区域、光学フィードバック線における信号の位相及び強度のうち少なくとも1つを制御する変調区域及び、損失変調半導体レーザーデバイスを変調する損失変調半導体レーザーデバイスのフィードバック係数を制御する光学フィードバック線を含む。

【0060】

本発明の1つまたは複数の実施形態に従う損失変調半導体レーザーデバイスを製造する方法は、セミコンダクター・オン・インシュレーター(S O I)構造内に導波路構造及び変調構造を形成する段階、変調区域を導波路構造に接続する段階及び半導体構造を導波路構造に接合する段階を含み、変調構造が、損失変調半導体レーザーデバイスの光学キャビティ内における光子の寿命を制御する。

【0061】

このような方法はさらに任意に、導波路構造に、光学フィードバック線を介して接続される変調区域、S O I構造の半導体層内における少なくとも1つのドープされた領域である変調区域並びに、損失変調半導体レーザーデバイス内における分布損失及びフィードバック係数の少なくとも1つを制御する変調区域を含む。

【0062】

本発明の1つまたは複数の実施形態に従う半導体レーザーは、導波路及び変調領域を含む半導体層を含むセミコンダクター・オン・インシュレーター(S O I)領域並びにS O I領域の半導体層に接合されたI I I族-V族(I I I-V)領域を含み、変調領域が、半導体レーザー内の光子の寿命を制御することによって、半導体レーザーの出力を変調する。

【0063】

そのようなレーザーはさらに任意に、光学遷移システム内で動作する半導体レーザー、半導体層内における少なくとも1つのドープされた領域である変調領域、シリコンを含むS O I構造の半導体層、光学フィードバック線の位相遅延を制御する変調領域及び光学フィードバック線の強度を制御する変調領域を含む。

【0064】

本発明の1つまたは複数の実施形態に従う半導体レーザーデバイスは、光学キャビティを有する第1の導波路構造を含み、半導体デバイスの光学キャビティ内の損失が変調される。

【0065】

このような半導体レーザーデバイスはさらに任意に、光学キャビティに接続されたミラーを用いて変調される光学キャビティ内の損失、ミラーの実効反射率を変調することによって変調される光学キャビティ内の損失、光学キャビティに接続される第2の導波路構造で変調され、第2の導波路内の光が第1の導波路構造内の光と干渉する光学キャビティ内の損失、第1の導波路に接続された、第2の導波路内に延長する半導体レーザーデバイスの光学モード、第2の導波路内の損失を変調することによって変調される光学キャビティ内の損失を含む。

10

20

30

40

50

## 【0066】

本発明の好適な実施形態の前述の説明は、例示及び説明の目的のために提示されたものである。これは包括的なものであることを意図せず、または開示された正確な形状に本発明を限定することを意図しない。多くの修正及び変形が、上述の教示に照らして可能である。本発明の範囲はこの詳細な説明によって限定されるものではなく、次に添付する特許請求の範囲及び特許請求の範囲の等価物の完全な範囲によることを意図している。

## 【符号の説明】

## 【0067】

|                   |                  |    |

|-------------------|------------------|----|

| 1 0 0             | デバイス             |    |

| 1 0 2             | S O I 領域         | 10 |

| 1 0 4             | ( I I I - V ) 領域 |    |

| 1 0 6             | 接合界面             |    |

| 1 0 8             | 基板               |    |

| 1 1 0             | 埋め込み酸化膜層         |    |

| 1 1 2             | シリコン導波路層         |    |

| 1 1 4             | ギャップ             |    |

| 1 1 6             | 導波路              |    |

| 1 2 0             | 層                |    |

| 1 2 4             | S C H 層          |    |

| 1 2 6             | クラッディング層         | 20 |

| 1 3 0             | p コンタクト          |    |

| 1 3 2             | メサ               |    |

| 1 3 4             | n コンタクト          |    |

| 2 0 0             | デバイス             |    |

| 2 0 2             | n 型ドープされた領域      |    |

| 2 0 4             | p 型ドープされた領域      |    |

| 2 0 6             | S O I リッジ        |    |

| 2 0 8             | 陽子注入領域           |    |

| 2 1 0             | 電流の流れ            |    |

| 2 1 2             | 光学モード            | 30 |

| 4 0 0             | デバイス             |    |

| 4 0 2             | 増幅区域             |    |

| 4 0 4             | フィードバック線         |    |

| 4 0 6             | 変調区域             |    |

| 5 0 0、6 0 0、6 0 2 | グラフ              |    |

| 6 0 4、6 0 6       | アイダイアグラム         |    |

| 7 0 0、7 0 2、7 0 4 | プロセスフローチャート      |    |

【図5】

FIG. 5

【図1】

【図2】

【図3】

【図4】

【図 6 A】

【図 6 B】

【図7】

---

フロントページの続き

(72)発明者 ジョン・イー・バウワーズ

アメリカ合衆国・カリフォルニア・93110・サンタ・バーバラ・シエラ・マドレ・ロード・4

601

(72)発明者 ダオシン・ダイ

中華人民共和国・310058・ゼジアン・ハンチョウ・ゼジアン・ユニバーシティ・ジジンガン

・キャンパス・ガンワン・ガーデン

審査官 佐藤 宙子

(56)参考文献 特表2009-537871(JP, A)

特開2002-217484(JP, A)

特開2010-102045(JP, A)

米国特許出願公開第2009/0016399(US, A1)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00-5/50

G02B 6/12-6/14

G02F 1/025

IEEE Explore