(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3731447号

(P3731447)

(45) 発行日 平成18年1月5日(2006.1.5)

(24) 登録日 平成17年10月21日(2005.10.21)

(51) Int.C1.

F 1

|             |               |                  |             |              |             |

|-------------|---------------|------------------|-------------|--------------|-------------|

| <b>G09F</b> | <b>9/30</b>   | <b>(2006.01)</b> | <b>G09F</b> | <b>9/30</b>  | <b>338</b>  |

| <b>G02F</b> | <b>1/136</b>  | <b>(2006.01)</b> | <b>G02F</b> | <b>1/136</b> |             |

| <b>H01L</b> | <b>29/786</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b> | <b>619B</b> |

請求項の数 15 (全 27 頁)

(21) 出願番号 特願2000-179899 (P2000-179899)

(22) 出願日 平成12年6月15日 (2000.6.15)

(65) 公開番号 特開2001-356709 (P2001-356709A)

(43) 公開日 平成13年12月26日 (2001.12.26)

審査請求日 平成16年1月16日 (2004.1.16)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 高原 研一

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 星野 浩一

最終頁に続く

(54) 【発明の名称】電気光学装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に、相交差する走査線及びデータ線と、該走査線及びデータ線に接続された薄膜トランジスタと、該薄膜トランジスタに接続された画素電極と、該画素電極に接続され画素電極電位とされる画素電位側容量電極と該画素電位側容量電極に誘電体膜を介して対向配置され固定電位とされる固定電位側容量電極とを含む蓄積容量と、前記薄膜トランジスタを構成する半導体層の少なくともチャネル領域を平面的に見て覆う位置に積層されたカバー層とを備えており、

前記画素電位側容量電極及び前記固定電位側容量電極のうち一方の電極と前記カバー層とは同一シリコン層から形成されていることを特徴とする電気光学装置。 10

## 【請求項2】

前記カバー層の膜厚は、100nm～300nmであることを特徴とする請求項1に記載の電気光学装置。

## 【請求項3】

前記一方の電極をなすシリコン層部分は、不純物がドープされることにより導電性があり、

前記カバー層をなすシリコン層部分は、前記不純物がドープされないことにより前記一方の電極よりも導電性が小さいことを特徴とする請求項1又は2に記載の電気光学装置。

## 【請求項4】

前記カバー層は、前記一方の電極からパターン的に分離されていないことを特徴とする

請求項 3 に記載の電気光学装置。

【請求項 5】

前記カバー層をなすシリコン層部分及び前記一方の電極をなすシリコン層部分は、不純物がドープされることにより導電性があることを特徴とする請求項 1 又は 2 に記載の電気光学装置。

【請求項 6】

前記一方の電極は前記固定電位側容量電極であり、

前記カバー層は、前記一方の電極からパターン的に分離されていないことを特徴とする請求項 5 に記載の電気光学装置。

【請求項 7】

前記カバー層は、前記一方の電極からパターン的に分離されていることを特徴とする請求項 3 又は 6 に記載の電気光学装置。

【請求項 8】

前記基板上における前記薄膜トランジスタの上側に積層されており画素の非開口領域を少なくとも部分的に規定する導電性の上層遮光膜を更に備えており、前記固定電位側容量電極は、前記上層遮光膜に接続され、前記上層遮光膜を介して固定電位に落とされていることを特徴とする請求項 1 から 7 のいずれか一項に記載の電気光学装置。

【請求項 9】

前記基板上における前記薄膜トランジスタの下側に積層されており前記チャネル領域を該下側から覆う導電性の下層遮光膜を更に備えており、

前記固定電位側容量電極は、前記下層遮光膜に接続され、前記下層遮光膜を介して固定電位に落とされていることを特徴とする請求項 1 から 7 のいずれか一項に記載の電気光学装置。

【請求項 10】

前記画素電位側容量電極及び前記固定電位側容量電極のうち他方の電極は、前記画素電極と同一層から形成されていることを特徴とする請求項 1 から 9 のいずれか一項に記載の電気光学装置。

【請求項 11】

基板上に、相交差する走査線及びデータ線を形成する工程と、

該走査線及びデータ線に接続される薄膜トランジスタを形成する工程と、

該薄膜トランジスタに接続される画素電極を形成する工程と、

前記画素電極に接続され画素電極電位とされる画素電位側容量電極と該画素電位側容量電極に誘電体膜を介して対向配置され固定電位とされる固定電位側容量電極とを含む蓄積容量を形成する工程と、

前記薄膜トランジスタを構成する半導体層の少なくともチャネル領域を平面的に見て覆う位置に積層されるカバー層を形成する工程と

を備えており、

前記蓄積容量を形成する工程及び前記カバー層を形成する工程では、同一起点から前記画素電位側容量電極及び前記固定電位側容量電極のうち一方の電極と前記カバー層とを形成することを特徴とする電気光学装置の製造方法。

【請求項 12】

前記蓄積容量を形成する工程では、前記カバー層をなすシリコン層部分をマスクしてのイオン打ち込みにより、前記一方の電極をなすシリコン層部分に導電性の与えることを特徴とする請求項 11 に記載の電気光学装置の製造方法。

【請求項 13】

基板上に、相交差する走査線及びデータ線と、

該走査線及びデータ線に接続された薄膜トランジスタと、

該薄膜トランジスタに接続された画素電極と、

該画素電極に接続され画素電極電位とされる画素電位側容量電極と該画素電位側容量電極に誘電体膜を介して対向配置され固定電位とされる固定電位側容量電極とを含む蓄積容

10

20

30

40

50

量と、

前記薄膜トランジスタを構成する半導体層の少なくともチャネル領域を平面的に見て覆う位置に積層されたシリコンでなる遮光層と

を備えており、

前記蓄積容量の一方の電極は前記遮光層と同層で形成されていることを特徴とする電気光学装置。

【請求項 1 4】

前記遮光層と同層で形成された前記蓄積容量の一方の電極は、前記遮光層を覆う第 2 の遮光層に接続されることを特徴とする請求項 1 3 に記載の電気光学装置。

【請求項 1 5】

前記遮光層と同層で形成された前記蓄積容量の一方の電極は、前記半導体層の下層で前記半導体層を覆う第 3 の遮光層を備えることを特徴とする請求項 1 3 又は 1 4 に記載の電気光学装置。

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は、アクティブマトリクス駆動方式の電気光学装置の技術分野に属し、特に画素電極に書き込まれた電位を保持するための蓄積容量と、画素スイッチング用の薄膜トランジスタ (Thin Film Transistor:以下適宜、TFTと称す) と、基板上の積層構造中に備えた形式の電気光学装置及びその製造方法の技術分野に属する。

【0 0 0 2】

【背景技術】

TFT アクティブマトリクス駆動形式の電気光学装置では、各画素に設けられた画素スイッチング用 TFT のチャネル領域に入射光が照射されると光による励起で電流が発生して TFT の特性が変化する。特に、プロジェクタのライトバルブ用の電気光学装置の場合には、入射光の強度が高いため、TFT のチャネル領域やその周辺領域に対する入射光の遮光を行うことは重要となる。そこで従来は、対向基板に設けられた各画素の開口領域を規定する遮光膜により、或いは TFT の上を通過すると共に A1 等の金属膜からなるデータ線により、係るチャネル領域やその周辺領域を遮光するように構成されている。また特開平 9 - 33944 号公報には、屈折率が大きい a - Si (アモルファスシリコン) から形成された遮光膜で、チャネル領域に入射する光を減少させる技術が開示されている。更に、TFT アレイ基板上において画素スイッチング用 TFT に対向する位置 (即ち、TFT の下側) にも、例えば高融点金属からなる遮光膜を設けることがある。このように TFT の下側にも遮光膜を設ければ、TFT アレイ基板側からの裏面反射や、複数の電気光学装置をプリズム等を介して組み合わせて一つの光学系を構成する場合に他の電気光学装置からプリズム等を突き抜けてくる投射光が、当該電気光学装置の TFT に入射するのを未然に防ぐことができる。

【0 0 0 3】

他方、一般にこの種の電気光学装置においては、TFT のゲート電極に走査線を介して走査信号が供給されると、TFT はオン状態とされ、半導体層のソース領域にデータ線を介して供給される画像信号が当該 TFT のソース - ドレイン間を介して画素電極に供給される。このような画像信号の供給は、各 TFT を介して画素電極毎に極めて短時間しか行われないので、TFT を介して供給される画像信号の電圧を、このオン状態とされた時間よりも遙かに長時間に亘って保持するために、各画素電極には (液晶容量等と並列に) 蓄積容量が付加されるのが一般的である。そして、このような蓄積容量は一般に、画素電極に接続された TFT のドレイン領域を構成する導電性のポリシリコン膜等から延設され画素電極電位とされる容量電極と、この容量電極に誘電体膜を介して対向配置された電極部分を含み固定電位とされる容量線とを備えて構成されている。

【0 0 0 4】

【発明が解決しようとする課題】

10

20

30

40

50

しかしながら、上述した各種遮光技術によれば、以下の問題点がある。即ち、先ず対向基板上やTFTアレイ基板上に遮光膜を形成する技術によれば、遮光膜とチャネル領域との間は、3次元的に見て例えば液晶層、電極、層間絶縁膜等を介してかなり離間しており、両者間へ斜めに入射する光に対する遮光が十分ではない。加えて、遮光膜のない領域から電気光学装置内に侵入した光が、遮光膜やデータ線の内面（即ち、チャネル領域に面する側の面）で反射された後に、係る反射光或いはこれが更に遮光膜やデータ線の内面で反射された多重反射光が最終的にTFTのチャネル領域に到達してしまう場合もある。またデータ線で遮光する技術によれば、データ線は平面的に見て走査線に直交して伸びるストライプ状に形成されており且つデータ線とチャネル領域との容量カップリングの悪影響が無視できる程度に両者間に厚い層間絶縁膜を配置する必要があるため、十分に遮光することは、基本的に困難である。また特開平9-33944号公報に記載の技術によれば、ゲート線上にa-Si膜を形成するため、ゲート電極とa-Si膜との容量カップリングの悪影響を低減するために両者間に比較的厚い層間絶縁膜を積むことが必要となる。この結果、追加的に形成されるa-Si膜や層間絶縁膜等により積層構造が複雑肥大化すると共にやはり斜めの入射光や内面反射光に対して十分な遮光を行うことは困難である。特に近年の表示画像の高品位化という一般的要請に沿うべく電気光学装置の高精細化或いは画素ピッチの微細化を図るに連れて、上述した従来の各種遮光技術によれば、十分な遮光を施すのがより困難となり、TFTのトランジスタ特性の変化により、フリッカ等が生じて、表示画像の品位が低下してしまうという問題点がある。

#### 【0005】

他方、上述した蓄積容量を付加する技術によれば、以下の問題点がある。即ち、この種の電気光学装置においては、表示画像の高品位化のために画素ピッチを微細化しつつ画素開口率を高める（即ち、各画素において、表示光が透過しない各画素における非開口領域に対して、表示光が透過する開口領域を広げる）ことが重要となるが、このように微細ピッチな画素の高開口率化に伴い走査線や容量線を配線可能な各画素の非開口領域は狭くなる。このため、画素ピッチの微細化が進む程、十分な大きさの蓄積容量を作り込むことや、走査線や容量線に十分な導電性を与えることが困難になる。そして、十分な蓄積容量が得られなかったり、走査線や容量線に十分な導電性が得られなかったりすると、最終的には、表示画像中におけるクロストークやゴーストが増大して画質劣化するという問題点が生じる。

#### 【0006】

本発明は上述の問題点に鑑みなされたものであり、耐光性に優れ且つ蓄積容量を効率良く作り込むことが可能な電気光学装置及びその製造方法を提供することを課題とする。

#### 【0007】

##### 【課題を解決するための手段】

本発明の電気光学装置は上記課題を解決するために、基板上に、相交差する走査線及びデータ線と、該走査線及びデータ線に接続された薄膜トランジスタと、該薄膜トランジスタに接続された画素電極と、該画素電極に接続され画素電極電位とされる画素電位側容量電極と該画素電位側容量電極に誘電体膜を介して対向配置され固定電位とされる固定電位側容量電極とを含む蓄積容量と、前記薄膜トランジスタを構成する半導体層の少なくともチャネル領域を平面的に見て覆う位置に積層されたカバー層とを備えており、前記画素電位側容量電極及び前記固定電位側容量電極のうち一方の電極と前記カバー層とは同一シリコン層から形成されている。

#### 【0008】

本発明の電気光学装置によれば、p-Si（ポリシリコン膜）、a-Si（アモルファスシリコン膜）或いはドープシリコン、ノンドープシリコン等の各種のシリコン層からなるカバー層により、薄膜トランジスタは平面的に見て（即ち、基板上において上側から又は下側から）覆われている。このようなシリコン層は、一般に褐色味を帯びてあり、層間絶縁膜を構成するPSG（リンシリケートガラス）、BSG（ボロンシリケートガラス）等のガラス材料と比べて光吸収率が高く（即ち透過率が低く）、光を吸収する性質を持

10

20

30

40

50

つ。ここでシリコン層であれば、Ti(チタン)、Cr(クロム)等の金属層で遮光する場合と異なり、薄膜トランジスタを構成する半導体層やゲート電極層等との間で発生するストレスが小さくて済む分だけ薄膜トランジスタに近接して配置可能である。即ち、薄膜トランジスタ上に薄い層間絶縁膜を介して当該シリコン層からなるカバー層を配置しても、製造中や製品完成後に発生するストレスが問題となることは殆どない。特に光強度を高めると、このような遮光用の金属層の場合でも、より厚くする必要があり、これに伴うストレス緩和のためにより遠くへ離して配置する必要が出てくるので、シリコン層からなるカバー層は非常に有利である。更に、カバー層を、導電性を持たないノンドープシリコン層から形成することにより、或いは導電性を持つシリコン層から形成すると共に固定電位に落とすことにより、カバー層と薄膜トランジスタ(特にそのゲート電極や半導体層)とを相互に近接配置しても、両者間における容量カップリングが問題となることは殆どない。従って、本発明によれば、ストレス及び容量カップリングに係る問題を引き起こすこと無く近接配置可能なカバー層により、チャネル領域に入射しようとする光(例えば、斜めの入射光、内面反射光、多重反射光、裏面からの戻り光等)に対する遮光を当該チャネル領域の近くで行える。このため本発明によれば、前述した背景技術の如く相対的に遠くに配置された遮光膜によって斜めの入射光等を十分に遮光できないことはないので大変有利である。

#### 【0009】

しかも、本発明によれば、このようにカバー層と同一シリコン層から一方の電極が形成された蓄積容量により、データ線及び薄膜トランジスタを介して画素電極に書き込まれた電位を比較的長時間に渡って保持できる。即ち、専ら蓄積容量の電極としてのみ用いられる導電層を追加的に積層することによる積層構造の複雑化或いは肥大化を避けつつ当該蓄積容量を構築できる。この際、一方の電極が固定電位側容量電極であれば、カバー層を形成するシリコン層部分を導電性の無いノンドープシリコンとするか導電性のあるドープシリコンとするかに拘わらず、カバー層と一方の電極とを分離してパターニングする必要はない。また一方の電極が画素電位側容量電極であれば、カバー層を形成するシリコン層部分を導電性の無いノンドープシリコン層とすればよい(この場合、カバー層の電位は、浮遊電位でもよい)。或いは、カバー層を形成するシリコン層部分を導電性のあるドープシリコン層とすると共にカバー層と一方の電極とを分離してパターニングすればよく、この場合には好ましくはカバー層を固定電位に落とすとよい。尚、固定電位としては、接地電位でもよいし、対向電極電位でもよい。いずれにせよカバー層は、チャネル領域に近接配置可能なように、導電性を持たせて固定電位に落とすのか或いは導電性を持たせない方がよい。このように本発明によれば、カバー層における光吸収のために望ましい条件を満足させつつカバー層と同一シリコン層を蓄積容量の一方の電極として利用できるので、全体として積層構造が複雑化或いは肥大化するのを防止しつつ、限られた基板上の領域内に効率的に蓄積容量を作り込める。

#### 【0010】

以上の結果本発明によれば、耐光性に優れ且つ蓄積容量を効率良く作り込むことが可能であり、特に優れた耐光性によって薄膜トランジスタのトランジスタ特性の変化によりフリック等が生じて表示画像の品位が低下してしまうという問題を回避しつつ、同時に効率的に作り込まれる蓄積容量によって特に微細ピッチな画素の高開口率化を図りつつ表示画像中におけるクロストークやゴーストを低減して画質を向上できる。

#### 【0011】

尚、このような薄膜トランジスタとしては、走査線の一部からなるゲート電極がチャネル領域の上側に位置する所謂トップゲート型でもよいし、走査線の一部からなるゲート電極がチャネル領域の下側に位置する所謂ボトムゲート型でもよい。また、蓄積容量の層間位置は、基板上で走査線の上方でも下方でもよい。加えて画素電極の層間位置も、基板上で走査線の上方でも下方でもよい。また、カバー層の積層位置としても、薄膜トランジスタの上側でもよいし下側でもよい。更に、画素電位側容量電極と固定電位側容量電極との基板上における上下関係についてはどちらでもよく、他方の電極は、半導体層、走査線、デ

10

20

30

40

50

一タ線、遮光膜、画素電極等の各導電膜と同一膜から構成可能である。加えて、以上の如く構成される本発明の電気光学装置は、透過型の電気光学装置でもよいし、反射型の電気光学装置でもよい。

【0012】

本発明の電気光学装置の一態様では、前記カバー層の膜厚は、100nm～300nmである。

【0013】

この態様によれば、カバー層の膜厚を、100nm～300nm、好ましくは200nm程度とすることにより、その光吸収率を実用上十分に高められる。しかも、この程度の膜厚であれば、当該カバー層の存在により発生するストレスも実用上殆ど問題とならず、更にカバー層の存在に起因して発生する画素電極の下地面における段差も実用上殆ど問題とならない程度に抑えられる。10

【0014】

本発明の電気光学装置の他の態様では、前記一方の電極をなすシリコン層部分は、不純物がドープされることにより導電性があり、前記カバー層をなすシリコン層部分は、前記不純物がドープされないことにより前記一方の電極よりも導電性が小さい。

【0015】

この態様によれば、一方の電極は、不純物がドープされることにより導電性がある（即ち、ドープトシリコンからなる）ので、蓄積容量の電極として良好に機能し得る。これに対して、カバー層は、不純物がドープされないことにより導電性が小さい（即ち、ノンドープトシリコンからなる）。このため、カバー層を薄膜トランジスタ（特にそのゲート電極や半導体層）に近接配置しても容量カッピングは殆ど問題とならないので、チャネル領域に近接配置されたカバー層により、チャネル領域に入射しようとする斜めの入射光等を吸収できる。特に、導電性のあるカバー層と一方の電極とをパターン的に分離しておく場合と比較して、ドープの有無で両者を分ける本態様によれば、より高い信頼性が得られる。20

【0016】

このカバー層の導電性が小さい態様では、前記カバー層は、前記一方の電極からパターン的に分離されていなくてもよい。

【0017】

即ち、このように構成すれば、一方の電極からパターン的に分離されていなくてもカバー層は（ノンドープトシリコンからなり）導電性が小さいため、一方の電極が画素電位側容量電極の場合にも、カバー層の電位が画素電極電位に従って振れることはない。従って、カバー層の電位変動がチャネル領域に対して悪影響を及ぼすことは殆ど無い。或いは、一方の電極が固定電位側容量電極であれば、やはりカバー層の電位変動がチャネル領域に対して悪影響を及ぼすことは殆ど無い。従って、同シリコン層からなるカバー層と一方の電極とをパターン的に分離することによる積層構造の複雑化や装置の信頼性低下を招かなくて済む。同時に、分離する場合と比較して蓄積容量の一方の電極の面積を広げられるため、蓄積容量の増加を図れる。30

【0018】

或いは本発明の他の態様では、前記カバー層をなすシリコン層部分及び前記一方の電極をなすシリコン層部分は、不純物がドープされることにより導電性がある。

【0019】

この態様によれば、一方の電極は、不純物がドープされることにより導電性がある（即ち、ドープトシリコンからなる）ので、蓄積容量の電極として良好に機能し得る。そしてカバー層も同様に、不純物がドープされることにより導電性がある（即ち、ドープトシリコンからなる）。従って、この場合には、カバー層を固定電位に落とすことにより、薄膜トランジスタ（特にそのゲート電極や半導体層）に近接配置しても容量カッピングは殆ど問題とならないので、チャネル領域に近接配置されたカバー層により、チャネル領域に入射しようとする斜めの入射光等を吸収できる。40

## 【0020】

このカバー層に導電性がある態様では、前記一方の電極は前記固定電位側容量電極であり、前記カバー層は、前記一方の電極からパターン的に分離されていなくてもよい。

## 【0021】

このように構成すれば、一方の電極は固定電位側容量電極であるので、この一方の電極からパターン的に分離されていないカバー層は、固定電位とされる。従って、カバー層を薄膜トランジスタ（特にそのゲート電極や半導体層）に近接配置しても容量カップリングは殆ど問題とならない。同時に、分離する場合と比較して蓄積容量の一方の電極の面積を広げられるため、蓄積容量の増加を図れる。

## 【0022】

或いはこれらのカバー層の導電性が小さい態様やカバー層に導電性がある態様では、前記カバー層は、前記一方の電極からパターン的に分離されていてもよい。

## 【0023】

このように構成すれば、先ずカバー層の導電性が小さい態様の場合には、一方の電極が固定電位側容量電極であるか画素電位側容量電極であるかによらず、より確実にカバー層の電位変動を低減できる。また、カバー層に導電性がある態様の場合には、一方の電極が固定電位側容量電極であるか画素電位側容量電極であるかによらず、一方の電極からパターン的に分離されている導電性のあるカバー層を固定電位にすれば、カバー層を薄膜トランジスタ（特にそのゲート電極や半導体層）に近接配置しても容量カップリングは殆ど問題とならない。加えて、両者を分離することにより、両者を積層構造内に追加的に作り込むことに起因するストレスの緩和が図れる。尚、このようなカバー層は、画素毎に島状に分離されていてもよい。

10

## 【0024】

本発明の電気光学装置の他の態様では、前記固定電位側容量電極は、固定電位配線に接続されている。

## 【0025】

この態様によれば、固定電位側容量電極は、例えば画像表示領域内に格子状或いはストライプ状に張り巡らされ且つ画像表示領域外に延設されて接地電位又は対向電極電位に落とされる容量線などの固定電位配線に接続されているので、確実且つ安定的に固定電位とされる。

20

## 【0026】

或いは本発明の電気光学装置の他の態様では、前記基板上における前記薄膜トランジスタの上側に積層されており画素の非開口領域を少なくとも部分的に規定する導電性の上層遮光膜を更に備えており、前記固定電位側容量電極は、前記上層遮光膜に接続され、前記上層遮光膜を介して固定電位に落とされている。

30

## 【0027】

この態様によれば、各画素の非開口領域は、トランジスタの上側に積層された格子状、ストライプ状又は島状などの上層遮光膜により少なくとも部分的に規定される。しかも、係る上層遮光膜には導電性があり、遮光機能のみならず固定電位配線としての機能も有するので、積層構造の複雑化を低減しつつ、このような二つの機能を果たすことが可能となる。そして特にこのように薄膜トランジスタの上側に積層された上層遮光膜を固定電位配線として利用することにより、基板上で平面的に見て半導体層が存在する個所でも、上層遮光膜と固定電位側容量電極との間のコンタクトをとれる。更にこのように薄膜トランジスタの上側に積層された上層遮光膜を固定電位配線として利用することにより、蓄積容量の誘電体膜形成後に直ちに、シリコン層を積めるので、製造工程上も大変有利である。

40

## 【0028】

或いは本発明の電気光学装置の他の態様では、前記基板上における前記薄膜トランジスタの下側に積層されており前記チャネル領域を該下側から覆う導電性の下層遮光膜を更に備えており、前記固定電位側容量電極は、前記下層遮光膜に接続され、前記下層遮光膜を介して固定電位に落とされている。

50

## 【0029】

この態様によれば、各画素の非開口領域は、トランジスタの下側に積層された格子状、ストライプ状又は島状などの下層遮光膜により少なくとも部分的に規定される。しかも、係る下層遮光膜には導電性があり、遮光機能のみならず個定電位配線としての機能も有するので、積層構造の複雑化を低減しつつ、このような二つの機能を果たすことが可能となる。

## 【0030】

本発明の電気光学装置の他の態様では、前記画素電位側容量電極及び前記固定電位側容量電極のうち他方の電極は、前記薄膜トランジスタを構成するゲート電極層と同一層から形成されている。

10

## 【0031】

この態様によれば、一方の電極は、カバー層と同一シリコン層からなり、他方の電極は、例えば導電性のポリシリコン膜からなるゲート電極層と同一層からなるので、積層構造の複雑化や肥大化を避けつつ蓄積容量を構築可能となる。尚この場合、ゲート電極層と他方の電極とはパターン的に分離しておけばよい。

## 【0032】

本発明の電気光学装置の他の態様では、前記画素電位側容量電極及び前記固定電位側容量電極のうち他方の電極は、前記半導体層と同一層から形成されている。

## 【0033】

この態様によれば、一方の電極は、カバー層と同一シリコン層からなり、他方の電極は、例えばポリシリコン膜からなる半導体層と同一層からなるので、積層構造の複雑化や肥大化を避けつつ蓄積容量を構築可能となる。尚この場合、半導体層のドレイン領域から他方の電極を形成すればよい（即ち、半導体層と他方の電極とはパターン的に分離しておく必要はない）。

20

## 【0034】

本発明の電気光学装置の他の態様では、前記画素電位側容量電極及び前記固定電位側容量電極のうち他方の電極は、前記画素電極と同一層から形成されている。

## 【0035】

この態様によれば、一方の電極は、カバー層と同一シリコン層からなり、他方の電極は、例えばITO (Indium Tin Oxide) 膜からなる画素電極と同一層からなるので、積層構造の複雑化や肥大化を避けつつ蓄積容量を構築可能となる。尚この場合、他方の電極を画素電位側容量電極とすれば、他方の電極と画素電極とをパターン的に分離しないだけで、両差間の電気的接続が得られるので有利である。

30

## 【0036】

本発明の電気光学装置の製造方法は上記課題を解決するために、基板上に、相交差する走査線及びデータ線を形成する工程と、該走査線及びデータ線に接続される薄膜トランジスタを形成する工程と、該薄膜トランジスタに接続される画素電極を形成する工程と、前記画素電極に接続され画素電極電位とされる画素電位側容量電極と該画素電位側容量電極に誘電体膜を介して対向配置され固定電位とされる固定電位側容量電極とを含む蓄積容量を形成する工程と、前記薄膜トランジスタを構成する半導体層の少なくともチャネル領域を平面的に見て覆う位置に積層されるカバー層を形成する工程とを備えており、前記蓄積容量を形成する工程及び前記カバー層を形成する工程では、同一シリコン層から前記画素電位側容量電極及び前記固定電位側容量電極のうち一方の電極と前記カバー層とを形成する。

40

## 【0037】

本発明の電気光学装置の製造方法によれば、走査線及びデータ線を形成する工程と、薄膜トランジスタを形成する工程と、画素電極を形成する工程と、蓄積容量を形成する工程と、カバー層を形成する工程とが、当該電気光学装置の積層構造に応じた順序で相前後して或いは同時に行われる。ここで特に、蓄積容量を形成する工程及びカバー層を形成する工程では、同一シリコン層から、画素電位側容量電極及び固定電位側容量電極のうち一方の

50

電極とカバー層とを形成するので、前述した本発明の電気光学装置を比較的容易に製造できる。

【0038】

本発明の電気光学装置の製造方法の他の態様では、前記蓄積容量を形成する工程では、前記カバー層をなすシリコン層部分をマスクしてのイオン打ち込みにより、前記一方の電極をなすシリコン層部分に導電性を与える。

【0039】

この態様によれば、一方の電極からパターン的に分離されていないカバー層であって薄膜トランジスタとの容量カップリングが問題とならないカバー層を、比較的容易に製造できる。

10

【0040】

本発明の他の電気光学装置は上記課題を解決するために、基板上に、相交差する走査線及びデータ線と、該走査線及びデータ線に接続された薄膜トランジスタと、該薄膜トランジスタに接続された画素電極と、該画素電極に接続され画素電極電位とされる画素電位側容量電極と該画素電位側容量電極に誘電体膜を介して対向配置され固定電位とされる固定電位側容量電極とを含む蓄積容量と、前記薄膜トランジスタを構成する半導体層の少なくともチャネル領域を平面的に見て覆う位置に積層されたシリコンでなる遮光層とを備えており、前記蓄積容量の一方の電極は前記遮光層と同層で形成されている。

【0041】

従って、耐光性に優れ且つ蓄積容量を効率良く作り込むことが可能であり、特に優れた耐光性によって薄膜トランジスタのトランジスタ特性の変化によりフリッカ等が生じて表示画像の品位が低下してしまうという問題を回避しつつ、同時に効率的に作り込まれる蓄積容量によって特に微細ピッチな画素の高開口率化を図りつつ表示画像中におけるクロストークやゴーストを低減して画質を向上できる。

20

【0042】

このような本発明の他の電気光学装置では、前記遮光層と同層で形成された前記蓄積容量の一方の電極は、前記遮光層を覆う第2の遮光層に接続されてもよい。或いは、前記遮光層と同層で形成された前記蓄積容量の一方の電極は、前記半導体層の下層で前記半導体層を覆う第3の遮光層を備えてもよい。

【0043】

30

本発明のこのような作用及び他の利得は次に説明する実施の形態から明らかにされる。

【0044】

【発明の実施の形態】

以下、本発明の実施形態を図面に基づいて説明する。以下の各実施形態は、本発明の電気光学装置を液晶装置に適用したものである。

【0045】

(第1実施形態)

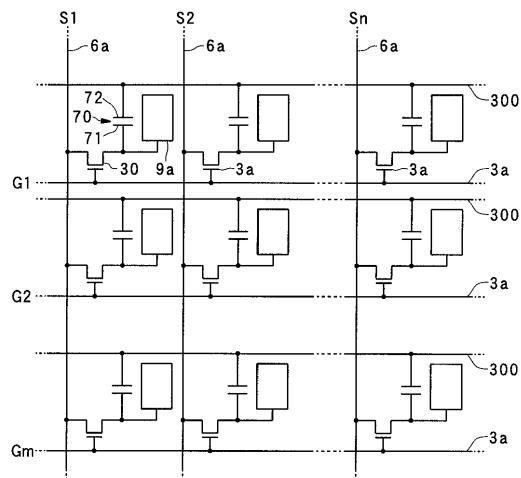

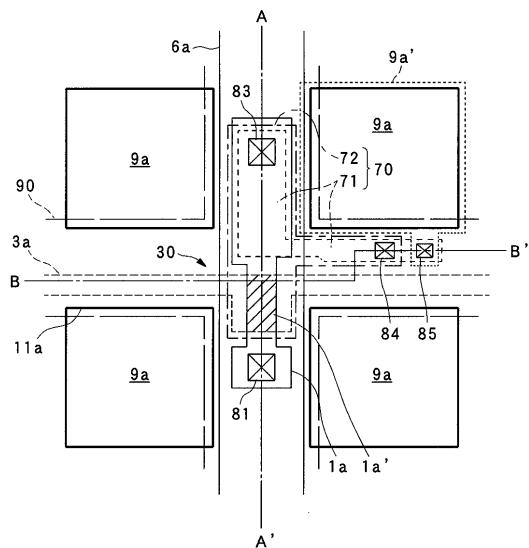

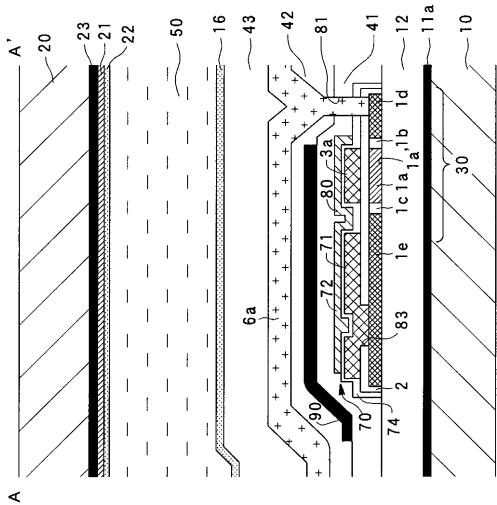

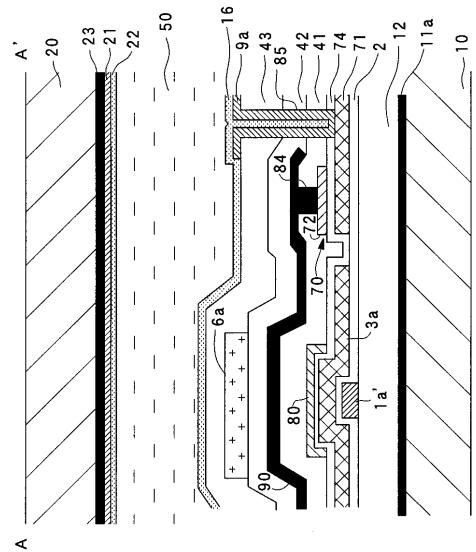

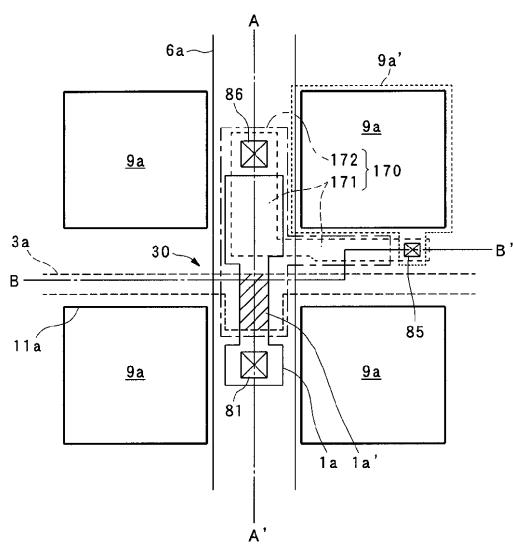

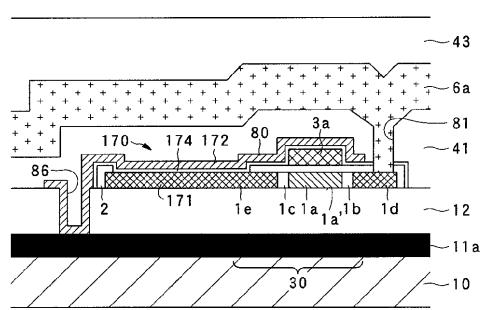

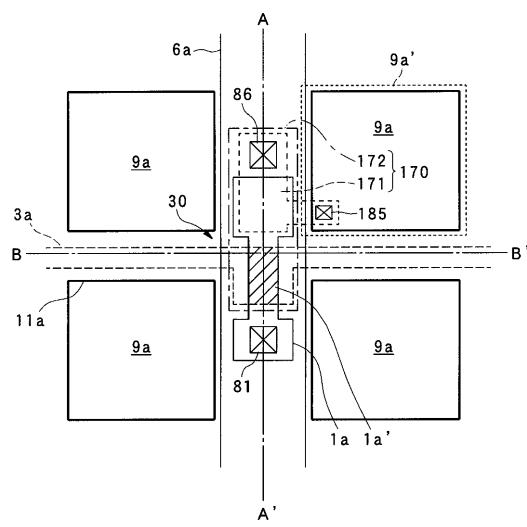

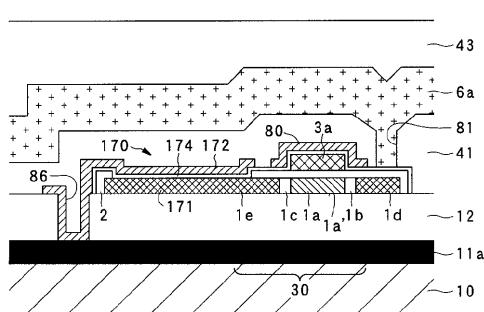

本発明の第1実施形態における電気光学装置の構成について、図1から図4を参照して説明する。図1は、電気光学装置の画像表示領域を構成するマトリクス状に形成された複数の画素における各種素子、配線等の等価回路である。図2は、データ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図である。図3は、図2のA-A'断面図であり、図4は、図2のB-B'断面図である。尚、図3及び図4においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を異ならしめてある。

40

【0046】

図1において、本実施形態における電気光学装置の画像表示領域を構成するマトリクス状に形成された複数の画素は、画素電極9aと当該画素電極9aをスイッチング制御するためのTFT30が形成されており、画像信号が供給されるデータ線6aが当該TFT30のソースに電気的に接続されている。データ線6aに書き込む画像信号S1、S2、…、Snは、この順に線順次に供給しても構わないし、相隣接する複数のデータ線6a同士に

50

対して、グループ毎に供給するようにしても良い。また、TFT30のゲートに走査線3aが電気的に接続されており、所定のタイミングで、走査線3aにパルス的に走査信号G1、G2、…、Gmを、この順に線順次で印加するように構成されている。画素電極9aは、TFT30のドレインに電気的に接続されており、スイッチング素子であるTFT30を一定期間だけそのスイッチを閉じることにより、データ線6aから供給される画像信号S1、S2、…、Snを所定のタイミングで書き込む。画素電極9aを介して電気光学物質の一例としての液晶に書き込まれた所定レベルの画像信号S1、S2、…、Snは、対向基板（後述する）に形成された対向電極（後述する）との間で一定期間保持される。液晶は、印加される電圧レベルにより分子集合の配向や秩序が変化することにより、光を変調し、階調表示を可能にする。ノーマリーホワイトモードであれば、各画素の単位で印加された電圧に応じて入射光に対する透過率が減少し、ノーマリーブラックモードであれば、各画素の単位で印加された電圧に応じて入射光に対する透過率が増加され、全体として電気光学装置からは画像信号に応じたコントラストを持つ光が出射する。ここで、保持された画像信号がリークするのを防ぐために、画素電極9aと対向電極との間に形成される液晶容量と並列に蓄積容量70を付加する。

#### 【0047】

本実施形態では特に、蓄積容量70は、TFT30のドレイン（及び画素電極9a）に接続された画素電位側容量電極71と、後述の如く遮光膜からなる固定電位配線の一例たる容量線300に接続された固定電位側容量電極72とが、誘電体膜を介して対向配置されることにより形成されている。そして、画素電位側容量電極71及び固定電位側容量電極72のうちいずれか一方は、後述の如くTFT30を構成する半導体層のチャネル領域を覆うカバー層と同一シリコン層から形成されている。

#### 【0048】

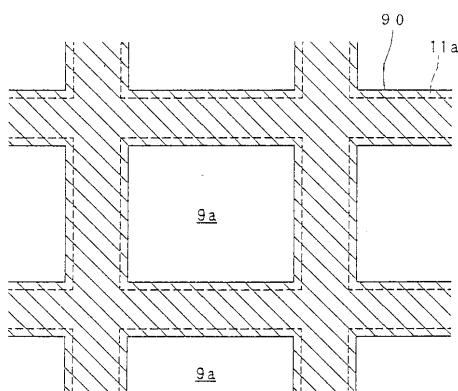

図2において、電気光学装置のTFTアレイ基板上には、マトリクス状に複数の透明な画素電極9a（点線部9a'により輪郭が示されている）が設けられており、画素電極9aの縦横の境界に各々沿ってデータ線6a、走査線3aが設けられている。

#### 【0049】

また、半導体層1aのうち図中右上がりの斜線領域で示したチャネル領域1a'に対向するように走査線3aが配置されており、走査線3aはゲート電極として機能する（特に、本実施形態では、走査線3aは、当該ゲート電極となる部分において幅広に形成されている）。このように、走査線3aとデータ線6aとの交差する個所には夫々、チャネル領域1a'に走査線3aがゲート電極として対向配置された画素スイッチング用のTFT30が設けられている。尚、図2では、4つの画素の内、右上の画素についてのみ、TFT30、蓄積容量70等を詳細に図示しているが、実際にはこれと同様に各画素にTFT30、蓄積容量70等が作り込まれている。

#### 【0050】

本実施形態では、図1に示した容量線300を構成する導電性の上層遮光膜90が（後述のように基板上においてTFT30の上層側に）各画素電極の間隙に沿って格子状に設けられており、下層遮光膜11aも（後述のように基板上においてTFT30の下層側に）同様に格子状に設けられている。これらの上層遮光膜90及び下層遮光膜11aは夫々、例えば、Ti（チタン）、Cr（クロム）、W（タンゲステン）、Ta（タンタル）、Mo（モリブデン）、Nb（鈸）等の高融点金属のうちの少なくとも一つを含む、金属単体、合金、金属シリサイド、ポリシリサイド、これらを積層したもの等からなる。本実施形態では、特に上層遮光膜90が容量線300としての機能も兼ねるので、これら遮光膜のうち少なくとも上層遮光膜90は導電性材料から形成する必要があるが、下層遮光膜11aが容量線300としての機能を兼ねるように構成するのであれば、逆に少なくとも下層遮光膜11aを導電性材料から形成する必要がある。

#### 【0051】

図2から図4に示すように、本実施形態では特に、TFT30のゲート電極付近の上層側に、シリコン層からなるカバー層80が設けられており、チャネル領域1a'を上側から

10

20

20

30

40

50

覆っている。更に走査線 3 a と同一層から蓄積容量 7 0 の画素電位側容量電極 7 1 が形成されており、カバー層 8 0 と同シリコン層から蓄積容量 7 0 の固定電位側容量電極 7 2 が形成されている。これらの画素電位側容量電極 7 1 と固定電位側容量電極 7 2 とが誘電体膜 7 4 を介して対向配置されることにより、平面的に見て主にデータ線 6 a に重なる領域及び走査線 3 a に重なる領域に、データ線 6 a 及び走査線 3 a に沿って伸びる部分を含む略 L 字型の蓄積容量 7 0 が構築されている。また、誘電体膜 7 4 は、例えば膜厚 5 ~ 2 0 0 nm 程度の比較的薄いHTO膜、LTO膜等の酸化シリコン膜、あるいは窒化シリコン膜等から構成される。蓄積容量 7 0 を増大させる観点からは、膜厚の信頼性が十分に得られる限りにおいて、誘電体膜 7 4 は薄い程良い。

## 【0052】

10

また本実施形態では特に、固定電位側容量電極 7 2 をなすシリコン層部分は、不純物がドープされることにより導電性があり、これと同シリコン層からなるカバー層 8 0 をなすシリコン層部分は、不純物がドープされないことにより導電性がない。そして、これらの同シリコン層からなるカバー層 8 0 と固定電位側容量電極 7 2 とは、パターン的に分離されている。

## 【0053】

図 2 及び図 3 に示すように、データ線 6 a は、コンタクトホール 8 1 を介して例えばポリシリコン膜からなる半導体層 1 a のうち高濃度ソース領域 1 d に電気的に接続されている。

## 【0054】

20

また図 2 及び図 4 に示すように、固定電位側容量電極 7 2 は、図 1 の容量線 3 0 0 を構成する上層遮光膜 9 0 にコンタクトホール 8 4 を介して接続されている。

容量線 3 0 0 として機能する上層遮光膜 9 0 は、画素電極 9 a が配置された画像表示領域からその周囲に延設され、定電位源と電気的に接続されて、固定電位とされる。定電位源としては、TFT 3 0 を駆動するための走査信号を走査線 3 a に供給するための走査線駆動回路（後述する）や画像信号をデータ線 6 a に供給するサンプリング回路を制御するデータ線駆動回路（後述する）に供給される正電源や負電源の定電位源でも良いし、対向基板の対向電極に供給される定電位でも構わない。

## 【0055】

30

尚、TFT 3 0 の下側に設けられる下層遮光膜 1 1 a についても、その電位変動が TFT 3 0 に対して悪影響を及ぼすことを避けるために、上層遮光膜 9 0 と同様に、画像表示領域からその周囲に延設して定電位源に接続するとよい。

## 【0056】

更に図 2 から図 4 に示すように、画素電極 9 a は、画素電位側容量電極 7 1 を中継することにより、コンタクトホール 8 3 及び 8 5 を介して半導体層 1 a のうち高濃度ドレイン領域 1 e に電気的に接続されている。

## 【0057】

40

尚、図 3 においてコンタクトホール 8 1 は、比較的その深度が深いので、中間にある他の導電層（例えば、画素電位側容量電極 7 1 と同一層、固定電位側容量電極 7 2 と同一層、上層遮光膜 9 0 と同一層）を中継層として利用して、2つ以上の直列なコンタクトホールから構成してもよい。同様に図 4 においてコンタクトホール 8 5 は、比較的その深度が深いので、中間にある他の導電層（例えば、固定電位側容量電極 7 2 と同一層、上層遮光膜 9 0 と同一層、データ線 6 a と同一層）を中継層として利用して、2つ以上の直列なコンタクトホールから構成してもよい。このように中間にある他の導電層を中継層として利用すれば、例えば層間距離が例えば 1 0 0 0 nm 程度に長くても、両者間を一つのコンタクトホールで接続する技術的困難性を回避しつつ比較的小径の二つ以上の直列なコンタクトホールで両者間を良好に接続でき、画素開口率を高めること可能となり、コンタクトホール開孔時におけるエッチングの突き抜け防止にも役立つ。加えて、このように深度の深いコンタクトホール 8 1 や 8 5 については、エッチングの深度制御の困難性に鑑み、エッチング突き抜け防止用の膜を半導体層 1 a の下側（コンタクトホール 8 1 の場合）や画素電

50

位側容量電極 7 1 の下側 (コンタクトホール 8 5 の場合) に、島状に設けるようにしてもよい。

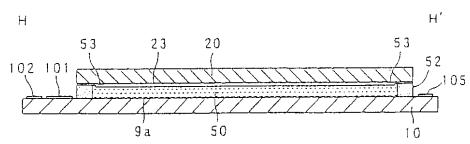

【0058】

図 3 及び 4 に示すように、電気光学装置は、透明な TFT アレイ基板 10 と、これに対向配置される透明な対向基板 20 とを備えている。TFT アレイ基板 10 は、例えば石英基板、ガラス基板、シリコン基板からなり、対向基板 20 は、例えばガラス基板や石英基板からなる。TFT アレイ基板 10 には、画素電極 9 a が設けられており、その上側には、ラビング処理等の所定の配向処理が施された配向膜 16 が設けられている。画素電極 9 a は例えば、ITO (Indium Tin Oxide) 膜などの透明導電性薄膜からなる。また配向膜 16 は例えば、ポリイミド薄膜などの有機薄膜からなる。

10

【0059】

他方、対向基板 20 には、その全面に渡って対向電極 21 が設けられており、その下側には、ラビング処理等の所定の配向処理が施された配向膜 22 が設けられている。対向電極 21 は例えば、ITO 膜などの透明導電性薄膜からなる。また配向膜 22 は、ポリイミド薄膜などの有機薄膜からなる。

【0060】

対向基板 20 には、更に図 3 及び図 4 に示すように、格子状又はストライプ状の第 2 遮光膜 23 を設けるようにしてもよい。このような構成を探ることで、上層遮光膜 90 と共に、対向基板 20 側から入射光がチャネル領域 1 a' や低濃度ソース領域 1 b 及び低濃度ドレイン領域 1 c に侵入するのを確実に阻止する。更に、第 2 遮光膜 23 は、少なくとも入射光が照射される面を高反射な膜で形成することにより、電気光学装置の温度上昇を防ぐ働きをする。加えて、本実施形態では、A1 膜等からなる遮光性のデータ線 6 a で、各画素の遮光領域のうちデータ線 6 a に沿った部分を遮光してもよい。

20

【0061】

このように構成された、画素電極 9 a と対向電極 21 とが対面するように配置された TFT アレイ基板 10 と対向基板 20 との間には、後述のシール材により囲まれた空間に電気光学物質の一例である液晶が封入され、液晶層 50 が形成される。液晶層 50 は、画素電極 9 a からの電界が印加されていない状態で配向膜 16 及び 22 により所定の配向状態をとる。液晶層 50 は、例えば一種又は数種類のネマティック液晶を混合した液晶からなる。シール材は、TFT アレイ基板 10 及び対向基板 20 をそれらの周辺で貼り合わせるための、例えば光硬化性樹脂や熱硬化性樹脂からなる接着剤であり、両基板間の距離を所定値とするためのグラスファイバー或いはガラスピーブ等のギャップ材が混入されている。

30

【0062】

更に、画素スイッチング用 TFT 30 の下には、下地絶縁膜 12 が設けられている。下地絶縁膜 12 は、TFT アレイ基板 10 の全面に形成されることにより、TFT アレイ基板 10 の表面の研磨時における荒れや、洗浄後に残る汚れ等で画素スイッチング用 TFT 30 の特性の劣化を防止する機能を有する。

【0063】

図 3 において、画素スイッチング用 TFT 30 は、LDD (Lightly Doped Drain) 構造を有しており、走査線 3 a、当該走査線 3 a からの電界によりチャネルが形成される半導体層 1 a のチャネル領域 1 a'、走査線 3 a と半導体層 1 a とを絶縁するゲート絶縁膜を含む絶縁薄膜 2、半導体層 1 a の低濃度ソース領域 1 b 及び低濃度ドレイン領域 1 c、半導体層 1 a の高濃度ソース領域 1 d 並びに高濃度ドレイン領域 1 e を備えている。

40

【0064】

固定電位側容量電極 7 2 上には、高濃度ソース領域 1 d へ通じるコンタクトホール 8 1、固定電位側容量電極 7 2 へ通じるコンタクトホール 8 4 及び画素電位側容量電極 7 1 へ通じるコンタクトホール 8 5 が各々開孔された第 1 層間絶縁膜 4 1 が形成されている。

【0065】

第 1 層間絶縁膜 4 1 上には上層遮光膜 9 0 が形成されており、これらの上には、高濃度ソース領域 1 d へ通じるコンタクトホール 8 1 及び画素電位側容量電極 7 1 へ通じるコンタ

50

クトホール 8 5 が各々開孔された第 2 層間絶縁膜 4 2 が形成されている。

【 0 0 6 6 】

第 2 層間絶縁膜 4 2 上にはデータ線 6 a が形成されており、これらの上には、画素電位側容量電極 7 1 へ通じるコンタクトホール 8 5 が形成された第 3 層間絶縁膜 4 3 が形成されている。画素電極 9 a は、このように構成された第 3 層間絶縁膜 4 3 の上面に設けられている。

【 0 0 6 7 】

以上のように構成された本実施形態によれば、対向基板 2 0 側から TFT 3 0 のチャネル領域 1 a' 及びその付近に入射光が入射しようとすると、第 2 遮光膜 2 3 、データ線 6 a 及び上層遮光膜 9 0 で遮光を行う。他方、TFT アレイ基板 1 0 側から、TFT 3 0 のチャネル領域 1 a' 及びその付近に戻り光が入射しようとすると、下層遮光膜 1 1 a で遮光を行う（特に、複板式のカラー表示用のプロジェクタ等で複数の電気光学装置をプリズム等を介して組み合わせて一つの光学系を構成する場合には、他の電気光学装置からプリズム等を突き抜けて来る投射光部分からなる戻り光は強力であるので、有効である。）。そして、斜めの入射光、内面反射光、多重反射光などの TFT 3 0 から層間距離を隔てて遮光するのでは、遮光効果が薄い光成分については、TFT 3 0 に近接して積層されたカバー層 8 0 により吸収する。これらの結果、TFT 3 0 の特性が光リークにより劣化することは殆ど無くなり、当該電気光学装置では、非常に高い耐光性が得られる。即ち、本実施形態では、ストレス及び容量カップリングに係る問題を引き起こすこと無くカバー層 8 0 を TFT 3 0 に近接配置可能であるので、当該カバー層 8 0 により、耐光性を十分に高められる。

【 0 0 6 8 】

しかも本実施形態では特に、前述の如く固定電位側容量電極 7 2 をなすシリコン層部分は、不純物がドープされることにより導電性があるドープドシリコンからなり、カバー層 8 0 をなすシリコン層部分は、不純物がドープされないことにより導電性がないノンドープドシリコンからなる。このため、カバー層 8 0 を TFT 3 0 に近接配置しても容量カップリングは、より一層問題とならないので、チャネル領域 1 a' に対してカバー層 8 0 を、より一層近接配置できるので大変有利である。

【 0 0 6 9 】

このようなカバー層の膜厚を、100 nm ~ 300 nm、好ましくは200 nm 程度とすることにより、その光吸収率を実用上十分に高められる。同時にカバー層 8 0 の存在により発生するストレスも実用上殆ど問題とならず更にカバー層 8 0 の存在に起因して発生する画素電極 9 a の下地面（第 3 層間絶縁膜 4 3 の表面）における段差も実用上殆ど問題とならない。また、固定電位側容量電極 7 2 としても、この程度の膜厚があれば支障はない。そして、より具体的な膜厚については、装置仕様に応じて求められる透過率（光吸収率）、段差、ストレス等の影響を総合的に勘案して設定すればよい。

【 0 0 7 0 】

更に本実施形態によれば、カバー層 8 0 と同一シリコン層から固定電位側容量電極 7 2 が形成された蓄積容量 7 0 により、データ線 6 a 及び TFT 3 0 を介して画素電極 9 a に書き込まれた電位を比較的長時間に渡って保持できる。即ち、専ら蓄積容量 7 0 の電極としてのみ用いられる導電層を追加的に積層することによる積層構造の複雑化或いは肥大化を避けつつ、限られた TFT アレイ基板 1 0 上の領域内に効率的に蓄積容量 7 0 を作り込む。

【 0 0 7 1 】

本実施形態では特に、固定電位側容量電極 7 2 は、TFT 3 0 の上層側に積層された上層遮光膜 9 0 に接続されることにより、固定電位に落とされているので、基板上で平面的に見て半導体層 1 a が存在する個所でも、上層遮光膜 9 0 と固定電位側容量電極 7 2 との間のコンタクトをとれる（即ち、コンタクトホール 8 4 を避けるために、平面的に見て半導体層 1 a を括れさせたり小さくする必要はない）。更にこのように TFT 3 0 の上層側に積層された上層遮光膜 9 0 を容量線 3 0 0（図 1 参照）として利用することにより、後述

10

20

30

40

50

する当該電気光学装置の製造プロセスにおいて、蓄積容量 70 の誘電体膜 74 を形成後に直ちに（即ち、下側にある固定電位配線に接続するためのコンタクトホールを開孔する作業を挟むこと無く）、カバー層 80 及び固定電位側容量電極 72 となるシリコン層を積めるという利益も得られる。

【0072】

加えて本実施形態では特に、同一シリコン層からなるカバー層 80 と固定電位側容量電極 72 とはパターン的に分離されていないため、これらをパターン的に分離することによる積層構造の複雑化や装置の信頼性低下を招かなくて済むと同時に、分離する場合と比較して蓄積容量 70 の構築面積を広げられるため、蓄積容量 70 の増加を図れる。

【0073】

以上説明した実施形態では、多数の導電層を積層することにより、画素電極 9a の下地面（即ち、第3層間絶縁膜 43 の表面）におけるデータ線 6a や走査線 3a に沿った領域に段差が生じるが、TFTアレイ基板 10、下地絶縁膜 12、第1層間絶縁膜 41、第2層間絶縁膜 42、第3層間絶縁膜 43 に溝を掘って、データ線 6a 等の配線や TFT30 等を埋め込むことにより平坦化処理を行ってもよいし、第3層間絶縁膜 43 や第2層間絶縁膜 42 の上面の段差を CMP (Chemical Mechanical Polishing) 処理等で研磨することにより、或いは有機 SOG を用いて平らに形成することにより、当該平坦化処理を行ってもよい。

【0074】

更に以上説明した実施形態では、画素スイッチング用 TFT30 は、好ましくは図 3 に示したように LDD 構造を持つが、低濃度ソース領域 1b 及び低濃度ドレイン領域 1c に不純物の打ち込みを行わないオフセット構造を持ってよいし、走査線 3a の一部からなるゲート電極をマスクとして高濃度で不純物を打ち込み、自己整合的に高濃度ソース及びドレイン領域を形成するセルフアライン型の TFT であってもよい。また本実施形態では、画素スイッチング用 TFT30 のゲート電極を高濃度ソース領域 1d 及び高濃度ドレイン領域 1e 間に 1 個のみ配置したシングルゲート構造としたが、これらの間に 2 個以上のゲート電極を配置してもよい。このようにデュアルゲート或いはトリプルゲート以上で TFT を構成すれば、チャネルとソース及びドレイン領域との接合部のリーク電流を防止でき、オフ時の電流を低減することができる。

【0075】

（製造プロセス）

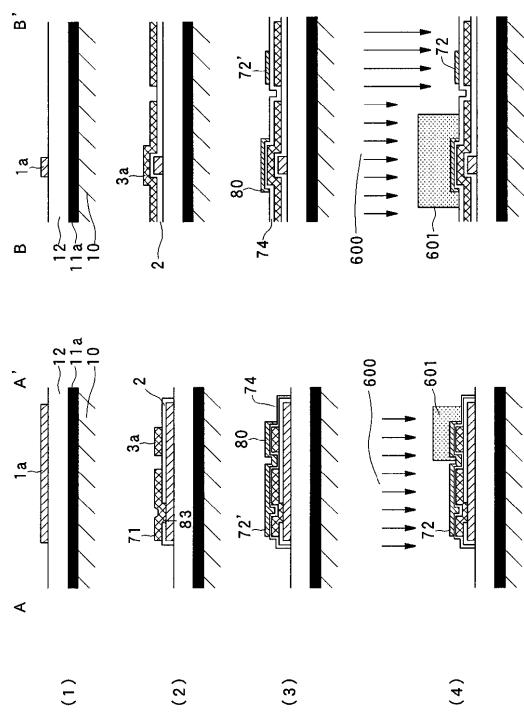

次に、上述の如き構成を持つ第1実施形態における電気光学装置の製造プロセスについて、図 5 及び図 6 を参照して説明する。ここに図 5 及び図 6 は、第1実施形態の電気光学装置の製造プロセスにおける各工程における TFT アレイ基板側の各層を、図 4 及び図 5 と同様に図 2 の A - A' 断面及び B - B' 断面に対応させて示す工程図である。

【0076】

先ず図 5 の工程（1）に示すように、石英基板、ハードガラス、シリコン基板等の TFT アレイ基板 10 を用意する。ここで、好ましくは N<sub>2</sub> (窒素) 等の不活性ガス雰囲気且つ約 900 ~ 1300 の高温でアニール処理し、後に実施される高温プロセスにおける TFT アレイ基板 10 に生じる歪みが少なくなるように前処理しておく。そして、このように処理された TFT アレイ基板 10 の全面に、Ti、Cr、W、Ta、Mo 及び Pd 等の金属や金属シリサイド等の金属合金膜を、スパッタリングにより、100 ~ 500 nm 程度の膜厚、好ましくは約 200 nm の膜厚の遮光膜を形成する。そしてフォトリソグラフィ及びエッチングにより、図 2 に示した如き所定パターンの下層遮光膜 11a を形成する。

【0077】

続いて、下層遮光膜 11a 上に、例えば、常圧又は減圧 CVD 法等により TEOS (テトラ・エチル・オルソ・シリケート) ガス、TEB (テトラ・エチル・ボートレート) ガス、TMOP (テトラ・メチル・オキシ・フォスレート) ガス等を用いて、NSG、PSG、BSG、BPSG などのシリケートガラス膜、窒化シリコン膜や酸化シリコン膜等から

10

20

30

40

50

なる下地絶縁膜12を形成する。この下地絶縁膜12の膜厚は、例えば約500～200nmとする。

【0078】

続いて、下地絶縁膜12上に、約450～550、好ましくは約500の比較的低温環境中で、流量約400～600cc/minのモノシランガス、ジシランガス等を用いた減圧CVD（例えば、圧力約20～40PaのCVD）により、アモルファスシリコン膜を形成する。その後、窒素雰囲気中で、約600～700にて約1～10時間、好ましくは、4～6時間のアニール処理を施すことにより、ポリシリコン膜1を約50～200nmの厚さ、好ましくは約100nmの厚さとなるまで固相成長させる。固相成長させる方法としては、RTA（Rapid Thermal Anneal）を使ったアニール処理でも良いし、エキシマレーザー等を用いたレーザーアニールでも良い。この際、画素スイッチング用のTFT30を、nチャネル型とするかpチャネル型にするかに応じて、V族元素やIII族元素のドーパントを僅かにイオン注入等によりドープしても良い。そして、フォトリソグラフィ及びエッティングにより、図2に示した如き所定パターンを有する半導体層1aを形成する。

【0079】

次に工程(2)に示すように、TFT30を構成する半導体層1aを約900～1300の温度、好ましくは約1000の温度により熱酸化することにより、又は減圧CVD法等により、若しくは両者を続けて行うことにより、単層又は多層の高温酸化シリコン膜（HTO膜）や窒化シリコン膜からなる（ゲート絶縁膜を含む）絶縁薄膜2を形成する。この結果、半導体層1aの厚さは、約30～150nmの厚さ、好ましくは約35～50nmの厚さとなり、絶縁薄膜2の厚さは、約20～150nmの厚さ、好ましくは約30～100nmの厚さとなる。

【0080】

続いて、絶縁薄膜2に対する反応性イオンエッティング、反応性イオンビームエッティング等のドライエッティングにより、コンタクトホール83を開孔する。更に、減圧CVD法等によりポリシリコン膜を堆積し、更にリン（P）を熱拡散し、このポリシリコン膜を導電化する。又は、Pイオンをこのポリシリコン膜の成膜と同時に導入したドープシリコン膜を用いてもよい。このポリシリコン膜の膜厚は、約100～500nmの厚さ、好ましくは約300nmである。そして、フォトリソグラフィ及びエッティングにより、図2に示した如き所定パターンの走査線3aと画素電位側容量電極71とを同時形成する。

【0081】

続いてTFT30をLDD構造を持つnチャネル型のTFTとする場合、半導体層1aに、先ず低濃度ソース領域1b及び低濃度ドレイン領域1cを形成するために、走査線3a（ゲート電極）をマスクとして、PなどのV族元素のドーパントを低濃度で（例えば、Pイオンを $1 \sim 3 \times 10^{13} / \text{cm}^2$ のドーズ量にて）ドープする。これにより走査線3a以下の半導体層1aはチャネル領域1a'となる。この不純物のドープにより画素電位側容量電極71及び走査線3aも低抵抗化される。更に、画素スイッチング用TFT30を構成する高濃度ソース領域1d及び高濃度ドレイン領域1eを形成するために、走査線3aよりも幅の広いマスクでレジスト層600を走査線3a上に形成した後、同じくPなどのV族元素のドーパントを高濃度で（例えば、Pイオンを $1 \sim 3 \times 10^{15} / \text{cm}^2$ のドーズ量にて）ドープする。また、画素スイッチング用TFT30をpチャネル型とする場合、半導体層1aに、低濃度ソース領域1b及び低濃度ドレイン領域1c並びに高濃度ソース領域1d及び高濃度ドレイン領域1eを形成するために、BなどのIII族元素のドーパントを用いてドープする。尚、例えば、低濃度のドープを行わずに、オフセット構造のTFTとしてもよく、走査線3aをマスクとして、Pイオン、Bイオン等を用いたイオン注入技術によりセルファーライン型のTFTとしてもよい。この不純物のドープにより画素電位側容量電極71及び走査線3aも更に低抵抗化される。

【0082】

尚、これらのTFT30の素子形成工程と並行して、nチャネル型TFT及びpチャネル

10

20

30

40

50

型 TFT から構成される相補型構造を持つデータ線駆動回路、走査線駆動回路等の周辺回路を TFT アレイ基板 10 上の周辺部に形成してもよい。

【 0083 】

次に工程 (3) に示すように、画素電位側容量電極 71 及び走査線 3a 並びに絶縁薄膜 2 上に、減圧 CVD 法、プラズマ CVD 法等により高温酸化シリコン膜 (HTO 膜) や窒化シリコン膜からなる誘電体膜 74 を 25 nm 以上 50 nm 以下の比較的薄い厚さに堆積する。但し、誘電体膜 74 は、絶縁薄膜 2 の場合と同様に、単層膜或いは多層膜のいずれから構成してもよく、一般に TFT のゲート絶縁膜を形成するのに用いられる各種の公知技術により形成可能である。そして、誘電体膜 74 を薄くする程、蓄積容量 70 は大きくなるので、結局、膜破れなどの欠陥が生じないことを条件に、膜厚 50 nm 以下の極薄い絶縁膜となるように誘電体膜 74 を形成すると本実施形態の効果を増大させることができる。

10

【 0084 】

続いて、誘電体膜 74 上に導電性のないポリシリコン層を減圧 CVD 法等により堆積した後、フォトリソグラフィ及びエッチングにより、図 2 に示した如きカバー層 80 及び固定電位側容量電極 72' (導電性が付与される前の電極) を含む所定パターンのシリコン層とする。この際のシリコン層の膜厚としては、100 nm 以上 300 nm 以下程度が好ましいが、前述の如く装置仕様に応じて求められる透過率 (光吸収率)、段差、ストレス等の影響を総合的に勘案して設定する。

【 0085 】

次に、工程 (4) では、フォトリソグラフィ及びエッチングにより、カバー層 80 となるシリコン層部分をマスクするレジスト 601 を形成した後に、矢印 600 で示した方向からイオン打ち込みを行って、固定電位側容量電極 72' を低抵抗化する。即ち、ドープシリコンからなる固定電位側容量電極 72 が完成する。この際、カバー層 80 についてはドープされない。即ち、カバー層 80 は、ノンドープシリコンからなる。

20

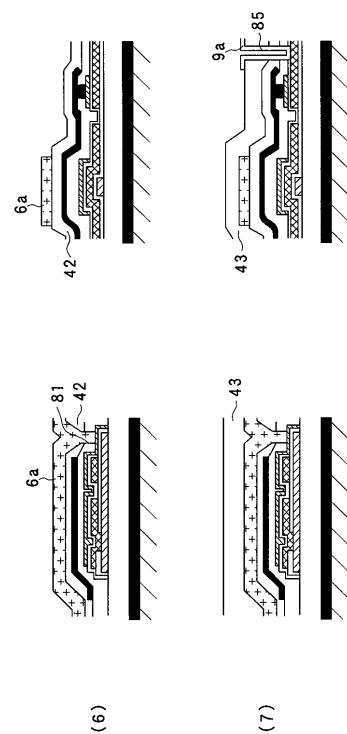

【 0086 】

次に、図 6 の工程 (5) に示すように、レジスト 500 を除去した後に、例えば、常圧又は減圧 CVD 法や TEOS ガス等を用いて、NSG、PSG、BSG、BPSG などのシリケートガラス膜、窒化シリコン膜や酸化シリコン膜等からなる第 1 層間絶縁膜 41 を形成する。第 1 層間絶縁膜 41 の膜厚は、例えば 500 ~ 1500 nm 程度である。

30

【 0087 】

更に、第 1 層間絶縁膜 41 に対する反応性イオンエッチング、反応性イオンビームエッチング等のドライエッチングにより、コンタクトホール 84 を開孔する。その後、第 1 層間絶縁膜 41 上の全面に、Ti、Cr、W、Ta、Mo 及び Pd 等の金属や金属シリサイド等の金属合金膜を、スパッタリングにより例えば 100 ~ 500 nm 程度の膜厚に形成した後に、フォトリソグラフィ及びエッチングを行って、図 2 に示した如き所定パターンを有する上層遮光膜 90 を形成する。

【 0088 】

次に、工程 (6) では、上層遮光膜 90 上に、例えば、常圧又は減圧 CVD 法や TEOS ガス等を用いて、NSG、PSG、BSG、BPSG などのシリケートガラス膜、窒化シリコン膜や酸化シリコン膜等からなる第 2 層間絶縁膜 42 を形成する。第 2 層間絶縁膜 42 の膜厚は、例えば 500 ~ 1500 nm 程度である。

40

【 0089 】

続いて、第 2 層間絶縁膜 42 に対する反応性イオンエッチング、反応性イオンビームエッティング等のドライエッティングにより、コンタクトホール 81 を開孔する。この際、走査線 3a や上層遮光膜 90 を基板周辺領域において図示しない配線と接続するためのコンタクトホールも、コンタクトホール 81 と同一の工程により第 2 層間絶縁膜 42 に開孔することができる。その後、第 1 層間絶縁膜 41 上の全面に、スパッタリング等により、遮光性の Al 等の低抵抗金属や金属シリサイド等を金属膜として、約 100 ~ 500 nm の厚さ、好ましくは約 300 nm に堆積する。そして、フォトリソグラフィ及びエッティングによ

50

り、図 2 に示した如き所定パターンを有するデータ線 6 a を形成する。

【0090】

次に工程 (7) に示すように、データ線 6 a 上を覆うように、例えば、常圧又は減圧 CVD 法や TEOS ガス等を用いて、NSG、PSG、BSG、BPSG などのシリケートガラス膜、窒化シリコン膜や酸化シリコン膜等からなる第 3 層間絶縁膜 4 3 を形成する。第 3 層間絶縁膜 4 3 の膜厚は、例えば 500 ~ 1500 nm 程度である。

【0091】

続いて、第 3 層間絶縁膜 4 3 に対する反応性イオンエッティング、反応性イオンビームエッティング等のドライエッティングにより、コンタクトホール 8 5 を開孔する。

【0092】

続いて、第 3 層間絶縁膜 4 3 上に、スパッタ処理等により、ITO 膜等の透明導電性薄膜を、約 50 ~ 200 nm の厚さに堆積する。そして、フォトリソグラフィ及びエッティングにより、図 2 に示した如き所定パターンを有する画素電極 9 a を形成する。尚、当該液晶装置を反射型の液晶装置に用いる場合には、A1 等の反射率の高い不透明な材料から画素電極 9 a を形成してもよい。

【0093】

続いて、画素電極 9 a の上にポリイミド系の配向膜の塗布液を塗布した後、所定のプレティルト角を持つように且つ所定方向でラビング処理を施すこと等により、配向膜 1 6 (図 3 及び図 4 参照) が形成される。

【0094】

他方、図 3 及び図 4 に示した対向基板 2 0 については、ガラス基板等が先ず用意され、第 2 遮光膜 2 3 及び額縁としての遮光膜 (図 1 4 及び図 1 5 参照) が、例えば金属クロムをスパッタした後、フォトリソグラフィ及びエッティングを経て形成される。尚、これらの遮光膜は、導電性である必要はなく、Cr、Ni、Al などの金属材料の他、カーボンやTi をフォトレジストに分散した樹脂ブラックなどの材料から形成してもよい。尚、TFT アレイ基板 1 0 上で、データ線 6 a、カバー層 8 0 、下層遮光膜 1 1 a 等で遮光領域を規定すれば、対向基板 2 0 上の第 2 遮光膜 2 3 を省くことができる。

【0095】

その後、対向基板 2 0 の全面にスパッタ処理等により、ITO 等の透明導電性薄膜を、約 50 ~ 200 nm の厚さに堆積することにより、対向電極 2 1 を形成する。更に、対向電極 2 1 の全面にポリイミド系の配向膜の塗布液を塗布した後、所定のプレティルト角を持つように且つ所定方向でラビング処理を施すこと等により、配向膜 2 2 (図 3 及び図 4 参照) が形成される。

【0096】

最後に、上述のように各層が形成された TFT アレイ基板 1 0 と対向基板 2 0 とは、配向膜 1 6 及び 2 2 が対面するようにシール材 (図 1 4 及び図 1 5 参照) により貼り合わされ、真空吸引等により、両基板間の空間に、例えば複数種類のネマティック液晶を混合してなる液晶が吸引されて、所定層厚の液晶層 5 0 が形成される。

【0097】

以上説明したように本製造プロセスでは、図 5 の工程 (3) 及び (4) で、同一シリコン層から、カバー層 8 0 及び固定電位側容量電極 7 2 を形成するので、前述した第 1 実施形態の電気光学装置を比較的容易に製造できる。特に、工程 (4) で、カバー層 8 0 をなすシリコン層部分をマスクしてのイオン打ち込みにより、カバー層 8 0 に導電性を与えることなく、固定電位側容量電極 7 2 をなすシリコン層部分にのみ導電性の与えることができる。これにより、パターン的に分離されていないカバー層 8 0 であって、TFT 3 0 に近接配置しても TFT 3 0 との容量カップリングが問題とならない導電性のないカバー層 8 0 を、比較的容易に製造できる。

【0098】

(第 2 実施形態)

次に、図 7 から図 9 を参照して本発明の電気光学装置の第 2 実施形態について説明する。

10

20

30

40

50

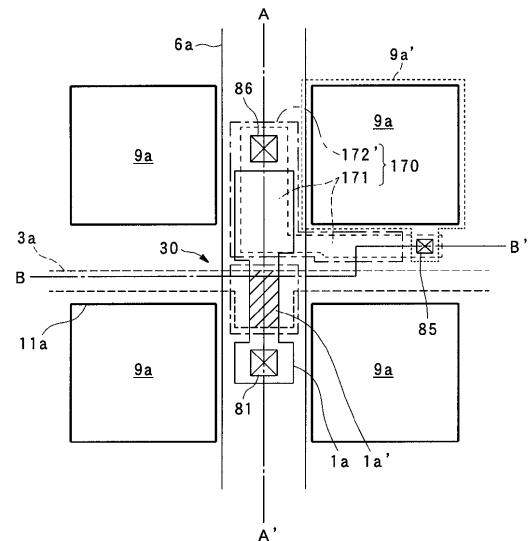

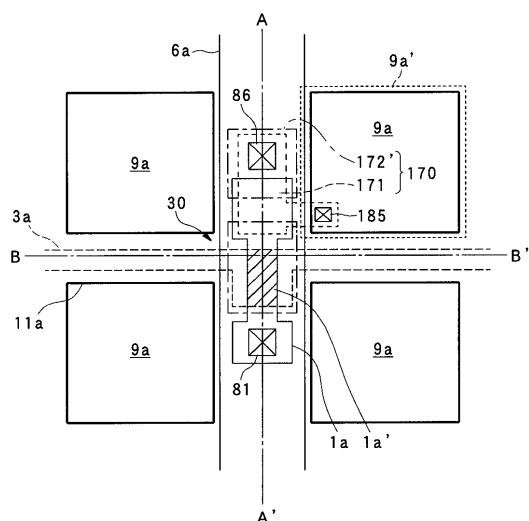

ここに、図7は、データ線、走査線、画素電極等が形成されたTFTアレイ基板の画素の平面図であり、図8は、図7におけるカバー層を中心とする主な積層構造を示すA-A'断面図であり、図9は、その変形例におけるA-A'断面図である。尚、図8及び図9においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を適宜異ならしめてある。また、図7から図9において、図1から図3(第1実施形態)と同様の構成要素には、同様の参照符号を付し、その説明は省略する。

#### 【0099】

図7及び図8に示すように、第2実施形態では、第1実施形態と異なり、上層遮光膜90が存在しておらず(更に、これに伴って第2層間絶縁膜42及びコンタクトホール84が存在しておらず)、代りに、カバー層80と同シリコン層からなる固定電位側容量電極172が、コンタクトホール86を介して下層遮光膜11aに接続されて、固定電位に落とされている。また、走査線3aと同一層からではなく、半導体層1aの高濃度ドレイン領域1aから延設された導電性ポリシリコン膜部分から、画素電位側容量電極171が形成されており、この画素電位側容量電極171と固定電位側容量電極172とが誘電体膜174を介して対向配置されることで蓄積容量170が構築されている。更に、半導体層1aの平面形状については、コンタクトホール86が開孔可能なように、図8における上端付近が若干短くされ、蓄積容量170を増大させるように画素電位側容量電極171をなす部分が、走査線に沿った領域にも(図8中、右側に)延設されている。また、半導体層1aの図8中の右端付近に画素電極9aからのコンタクトホール85が開孔されている。他方、蓄積容量170の誘電体膜を厚くしないように、この領域におけるゲート絶縁膜2を含む絶縁薄膜2がエッチングにより除去されている。その他の構成については、図8で省略されている画素電極9a、対向基板20等の構成を含めて、図2から図4に示した第1実施形態の場合と同様である。

#### 【0100】

従って第2実施形態によれば、各画素の非開口領域を少なくとも部分的に規定する下層遮光膜11aは、遮光機能のみならず図1に示した容量線300としての機能も有する。そして、このような下層遮光膜11aは好ましくは、第1実施形態における上層遮光膜90の場合と同様に、画素電極9aが配置された画像表示領域からその周囲に延設され、定電位源と電気的に接続される。

#### 【0101】

尚、図9に示したように蓄積容量170を、走査線3aに重なる領域にまで(L字型に)作り込むことなく、データ線6aに重なる領域にのみに(矩形に)作り込んでよい。この場合、走査線3aに沿った画素非開口領域を不必要に広げないように、半導体層1aの高濃度ドレイン領域1eから延設された角状部を画素電極9a下に突出させおき、この部分に画素電極9aからのコンタクトホール185が開孔されている。

#### 【0102】

##### (第3実施形態)

次に、図10から図12を参照して本発明の電気光学装置の第3実施形態について説明する。ここに、図10は、データ線、走査線、画素電極等が形成されたTFTアレイ基板の画素の平面図であり、図11は、図10におけるカバー層を中心とする主な積層構造を示すA-A'断面図であり、図12は、その変形例におけるA-A'断面図である。尚、図11及び図12においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を適宜異ならしめてある。また、図10から図13において、図1から図3(第1実施形態)或いは図と同様の構成要素には、同様の参照符号を付し、その説明は省略する。

#### 【0103】

図10及び図11に示すように、第3実施形態では、第2実施形態と比べて、同シリコン層からなるカバー層80'、と固定電位側容量電極172'、とが、パターン的に分離されている。その他の構成については、第2実施形態の場合と同様である。

#### 【0104】

10

20

30

40

50

従って第3実施形態によれば、各画素の非開口領域を少なくとも部分的に規定する下層遮光膜11aは、遮光機能のみならず図1に示した容量線300としての機能も有する。そして特にカバー層80'と固定電位側容量電極172'とが分離されているため、これらを積層構造内に追加的に作り込むことに起因するストレスの緩和が図れる。更に固定電位側容量電極72における微弱な電位変動がカバー層80を介してTFT30に悪影響を及ぼす事態を防止できる。

#### 【0105】

尚、図12に示したように蓄積容量170を、走査線3aに重なる領域にまで(L字型に)作り込むことなく、データ線6aに重なる領域にのみに(矩形に)作り込んでもよい。この場合、走査線3aに沿った画素非開口領域を必要に広げないように、半導体層1aの高濃度ドレイン領域1eから延設された角状部を画素電極9a下に突出させおき、この部分に画素電極9aからのコンタクトホール185が開孔されている。

10

#### 【0106】

以上説明した第2及び第3実施形態では、第1実施形態の場合とは異なり、下層遮光膜11aに図1における容量線300としての機能を与えるが故に、容量線300としての機能を持たない上層遮光膜を省略しているが、第2及び第3実施形態でも、第1実施形態の上層遮光膜90の如き遮光膜を専ら遮光の目的で設けるようにしてもよい。即ち、耐光性を高めるためには、TFT30の上下に上層遮光膜及び下層遮光膜が夫々配置されている方がより好ましい。

#### 【0107】

20

ここで、図13を参照して本発明の各実施形態の電気光学装置における下層遮光膜と上層遮光膜との形状についての好ましい関係について説明を加える。ここに、図13は、下層遮光膜及び上層遮光膜のみを抽出して示すTFTアレイ基板の画素の平面図である。

#### 【0108】

図13に示すように、各実施形態では、下層遮光膜11a及び上層遮光膜90共に格子状に形成されており、下層遮光膜11aは、平面的に見て上層遮光膜90の形成領域からはみ出さないように(即ち、一回り小さく)構成されている。従って上層遮光膜90により各画素の開口領域の輪郭が規定される。また、両者間にある不図示の走査線、データ線及びTFT等は、平面的に見て下層遮光膜11aの形成領域からはみ出さないように構成されている。

30

#### 【0109】

従って、対向基板20側からの入射光が上層遮光膜90の形成領域からはみ出した下層遮光膜11a(更に、走査線、データ線等)で反射することで、当該電気光学装置の内部における内面反射光や多重反射光が発生することを効果的に未然防止できる。尚、TFTアレイ基板10側からの戻り光が下層遮光膜11aの形成領域からはみ出した上層遮光膜90部分で反射することで、当該電気光学装置の内部における内面反射光や多重反射光は若干発生する。しかしながら、戻り光は入射光に比べて遙かに光強度が低いために、戻り光による内面反射や多重反射光の悪影響は入射光のそれに比べて軽微である。そして、このような軽微な内面反射光や多重反射光であれば、TFT30に近接配置されたシリコン層からなるカバー層80によって十分に吸収可能である。従って本実施形態の構成は有利である。

40

#### 【0110】

##### (その他の変形形態)

以上説明した各実施形態では、カバー層80をなすシリコン層部分は、ノンドープシリコンからなり導電性がないが、カバー層80も、同一シリコン層から形成される固定電位側容量電極72と同様に、不純物がドープされることにより導電性があるドープシリコンから形成されてもよい。この場合には、カバー層80を固定電位に落とすことにより、TFT30に近接配置しても容量カップリングは殆ど問題とならない。このようにカバー層80を導電性のドープシリコンから構成する場合には、TFT30との寄生容量を確実に抑制する観点からは、カバー層80とTFT30(即ち、ゲート電極を構成する走査

50

線 3 a )との間に介在する層間絶縁膜(誘電体膜)の膜厚を 4 0 0 n m 以上とするのが好ましい。従って、このような比較的厚い層間絶縁膜を蓄積容量の誘電体膜をしてそのまま用いることは望ましくない(即ち、誘電体膜の膜厚に反比例して容量が小さくなってしまう)ので、当該層間絶縁膜を誘電体膜となる部分において局所的にエッチングして、2 5 n m ~ 5 0 n m の薄い誘電体膜にすればよい。尚、このような電気光学装置は、例えば図 5 の工程(4)において、カバー層 8 0 となる部分をマスクすることなく、カバー層 8 0 及び固定電位側容量電極 7 2 をなすシリコン層に対してイオン打ち込みを行って、低抵抗のドープトシリコン層とすればよい。更に、このようにカバー層 8 0 に導電性を持たせる場合には、これと同一シリコン層からなる電極からパターン的に分離して、更に別途コンタクトホールを介して上層遮光膜、下層遮光膜等からなる固定電位配線に接続しても、導電性のあるカバー層 8 0 を固定電位に落とせる。特に、カバー層 8 0 と同一シリコン層からなる電極を画素電位電極として用いる場合にはこのような構成を採るとよい。

#### 【 0 1 1 1 】

以上説明した各実施形態においては、固定電位側容量電極 7 2 がカバー層 8 0 と同一シリコン膜から形成されているが、画素電位側容量電極 7 1 がカバー層 8 0 と同一シリコン膜から形成されてもよい。また、以上説明した各実施形態では、カバー層 8 0 と同一シリコン層から形成されない方の電極については、導電性のポリシリコン膜からなる走査線 3 a や半導体層 1 a と同一層から形成されているが、例えば I T O 膜からなる画素電極 9 a と同一層、上層又は下層遮光膜と同一層、データ線と同一層等から形成されてもよい。更に、固定電位側容量電極は、T F T 3 0 の上側(例えば、走査線 3 a と画素電位側容量電極 7 1 との間やデータ線 6 a と画素電位側容量電極 7 1 との間)に積層されてもよいし、T F T 3 0 の下側に積層されてもよい。但し、容量線 3 0 0 として機能する遮光膜と固定電位側容量電極との層間距離が短いほど両者をコンタクトホール等により接続するのが容易となり積層構造の複雑化を招かないで済むと共に装置信頼性が高まる。

#### 【 0 1 1 2 】

加えて、上述した各実施形態は、画素電極等が透明であり入射光を透過する透過型の電気光学装置として構築されているが、画素電極が反射膜であるか或いは反射膜が画素電極下に配置されており入射光を反射する反射型の電気光学装置として構築されてもよい。

#### 【 0 1 1 3 】

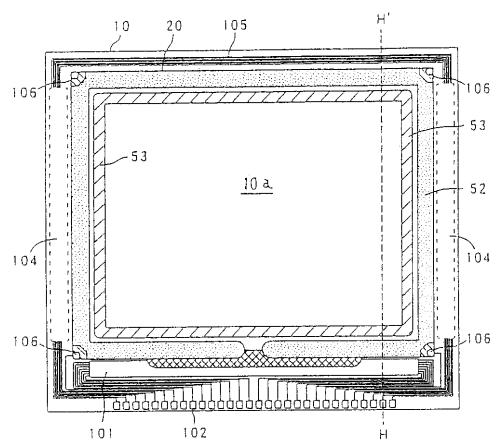

(電気光学装置の全体構成)

以上のように構成された各実施形態における電気光学装置の全体構成を図 1 4 及び図 1 5 を参照して説明する。尚、図 1 4 は、T F T アレイ基板 1 0 をその上に形成された各構成要素と共に対向基板 2 0 の側から見た平面図であり、図 1 5 は、図 1 4 の H - H ' 断面図である。

#### 【 0 1 1 4 】

図 1 5において、T F T アレイ基板 1 0 の上には、シール材 5 2 がその縁に沿って設けられており、その内側に並行して、例えば第 2 遮光膜 2 3 と同じ或いは異なる材料から成る画像表示領域 1 0 a の周辺を規定する額縁としての第 3 遮光膜 5 3 が設けられている。シール材 5 2 の外側の領域には、データ線 6 a に画像信号を所定タイミングで供給することによりデータ線 6 a を駆動するデータ線駆動回路 1 0 1 及び外部回路接続端子 1 0 2 がT F T アレイ基板 1 0 の一辺に沿って設けられており、走査線 3 a に走査信号を所定タイミングで供給することにより走査線 3 a を駆動する走査線駆動回路 1 0 4 が、この一辺に隣接する 2 辺に沿って設けられている。走査線 3 a に供給される走査信号遅延が問題にならないのならば、走査線駆動回路 1 0 4 は片側だけでも良いことは言うまでもない。また、データ線駆動回路 1 0 1 を画像表示領域 1 0 a の辺に沿って両側に配列してもよい。更にT F T アレイ基板 1 0 の残る一辺には、画像表示領域 1 0 a の両側に設けられた走査線駆動回路 1 0 4 間をつなぐための複数の配線 1 0 5 が設けられている。また、対向基板 2 0 のコーナー部の少なくとも 1 箇所においては、T F T アレイ基板 1 0 と対向基板 2 0 との間で電気的に導通をとるための導通材 1 0 6 が設けられている。そして、図 1 5 に示すように、図 1 4 に示したシール材 5 2 とほぼ同じ輪郭を持つ対向基板 2 0 が当該シール材 5

10

20

30

40

50

2 により TFT アレイ基板 10 に固着されている。

【 0115 】

尚、 TFT アレイ基板 10 上には、これらのデータ線駆動回路 101、走査線駆動回路 104 等に加えて、複数のデータ線 6a に画像信号を所定のタイミングで印加するサンプリング回路、複数のデータ線 6a に所定電圧レベルのプリチャージ信号を画像信号に先行して各々供給するプリチャージ回路、製造途中や出荷時の当該電気光学装置の品質、欠陥等を検査するための検査回路等を形成してもよい。

【 0116 】

以上図 1 から図 15 を参照して説明した各実施形態では、データ線駆動回路 101 及び走査線駆動回路 104 を TFT アレイ基板 10 の上に設ける代わりに、例えば TAB (Tape Automated bonding) 基板上に実装された駆動用 LSI に、 TFT アレイ基板 10 の周辺部に設けられた異方性導電フィルムを介して電気的及び機械的に接続するようにしてもよい。また、対向基板 20 の投射光が入射する側及び TFT アレイ基板 10 の出射光が出射する側には各々、例えば、TN モード、VA (Vertically Aligned) モード、PDL C (Polymer Dispersed Liquid Crystal) モード等の動作モードや、ノーマリー ホワイトモード / ノーマリーブラックモードの別に応じて、偏光フィルム、位相差フィルム、偏光板などが所定の方向で配置される。

【 0117 】

以上説明した各実施形態における電気光学装置は、プロジェクタに適用されるため、3 枚の電気光学装置が RGB 用のライトバルブとして各々用いられ、各ライトバルブには各々 RGB 色分解用のダイクロイックミラーを介して分解された各色の光が投射光として各々入射されることになる。従って、各実施形態では、対向基板 20 に、カラーフィルタは設けられていない。しかしながら、第 2 遮光膜 23 の形成されていない画素電極 9a に対向する所定領域に RGB のカラーフィルタをその保護膜と共に、対向基板 20 上に形成してもよい。このようにすれば、プロジェクタ以外の直視型や反射型のカラー電気光学装置について、各実施形態における電気光学装置を適用できる。また、対向基板 20 上に 1 画素 1 個対応するようにマイクロレンズを形成してもよい。あるいは、TFT アレイ基板 10 上の RGB に対向する画素電極 9a 下にカラーレジスト等でカラーフィルタ層を形成することも可能である。このようにすれば、入射光の集光効率を向上することで、明るい電気光学装置が実現できる。更にまた、対向基板 20 上に、何層もの屈折率の相違する干渉層を堆積することで、光の干渉を利用して、RGB 色を作り出すダイクロイックフィルタを形成してもよい。このダイクロイックフィルタ付き対向基板によれば、より明るいカラー電気光学装置が実現できる。

【 0118 】

本発明は、上述した各実施形態に限られるものではなく、請求の範囲及び明細書全体から読み取れる発明の要旨或いは思想に反しない範囲で適宜変更可能であり、そのような変更を伴なう電気光学装置及びその製造方法もまた本発明の技術的範囲に含まれるものである。

【 図面の簡単な説明 】

【 図 1 】本発明の第 1 実施形態の電気光学装置における画像表示領域を構成するマトリクス状の複数の画素に設けられた各種素子、配線等の等価回路である。

【 図 2 】第 1 実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成された TFT アレイ基板の相隣接する複数の画素群の平面図である。

【 図 3 】図 2 の A - A' 断面図である。

【 図 4 】図 2 の B - B' 断面図である。

【 図 5 】第 1 実施形態の電気光学装置の製造プロセスにおける各工程における TFT アレイ基板側の各層を、図 4 及び図 5 と同様に図 2 の A - A' 断面及び B - B' 断面に対応させて示す工程図 ( その 1 ) である。

【 図 6 】第 1 実施形態の電気光学装置の製造プロセスにおける各工程における TFT アレイ基板側の各層を、図 4 及び図 5 と同様に図 2 の A - A' 断面及び B - B' 断面に対応さ

10

20

30

40

50

せて示す工程図（その2）である。

【図7】第2実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図である。

【図8】第2実施形態におけるカバー層を中心とする主な積層構造を示す図7のA-A'断面図である。

【図9】第2実施形態の変形例における図7のA-A'断面図である。

【図10】第3実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図である。

【図11】第3実施形態におけるカバー層を中心とする主な積層構造を示す図10のA-A'断面図である。

【図12】第3実施形態の変形例における図10のA-A'断面図である。

【図13】各実施形態における上層遮光膜及び下層遮光膜を抽出して示すTFTアレイ基板の画素の平面図である。

【図14】各実施形態の電気光学装置におけるTFTアレイ基板をその上に形成された各構成要素と共に対向基板の側から見た平面図である。

【図15】図14のH-H'断面図である。

【符号の説明】

1 a ... 半導体層

1 a' ... チャネル領域

1 b ... 低濃度ソース領域

1 c ... 低濃度ドレイン領域

1 d ... 高濃度ソース領域

1 e ... 高濃度ドレイン領域

2 ... 絶縁薄膜

3 a ... 走査線

6 a ... データ線

9 a ... 画素電極

10 ... TFTアレイ基板

11 a ... 下層遮光膜

12 ... 下地絶縁膜

16 ... 配向膜

20 ... 対向基板

21 ... 対向電極

22 ... 配向膜

23 ... 第2遮光膜

30 ... TFT

50 ... 液晶層

70 ... 蓄積容量

71 ... 画素電位側容量電極

72 ... 固定電位側容量電極

74 ... 誘電体膜

80 ... カバー層

90 ... 上層遮光膜

81、83、85 ... コンタクトホール

300 ... 容量線

10

20

30

40

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図15】

【図14】

---

フロントページの続き

(56)参考文献 特開2001-177100(JP,A)

特開2000-091581(JP,A)

特開平11-084423(JP,A)

特開平10-301100(JP,A)

特開平10-142636(JP,A)

特開平10-096956(JP,A)

特開平10-048608(JP,A)

特開平10-026770(JP,A)

特開平09-171195(JP,A)

特開平08-179374(JP,A)

特開平06-214253(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09F 9/30 338

G02F 1/1368

H01L 29/786