## (12) 发明专利

(10) 授权公告号 CN 107026645 B

(45) 授权公告日 2022.01.11

(21) 申请号 201611121749.7

H03B 5/32 (2006.01)

(22) 申请日 2016.12.08

## (56) 对比文件

US 2011193600 A1, 2011.08.11

(65) 同一申请的已公布的文献号

US 2010289591 A1, 2010.11.18

申请公布号 CN 107026645 A

US 8638146 B1, 2014.01.28

(43) 申请公布日 2017.08.08

US 2011193600 A1, 2011.08.11

(30) 优先权数据

CN 104753529 A, 2015.07.01

2015-240400 2015.12.09 JP

CN 101610084 A, 2009.12.23

(73) 专利权人 株式会社巨晶片

CN 101944910 A, 2011.01.12

地址 日本大阪府大阪市

US 8049569 B1, 2011.11.01

(72) 发明人 坪田英俊 佐藤秀幸

TW 201115926 A, 2011.05.01

(74) 专利代理机构 北京铭硕知识产权代理有限公司 11286

US 2011304367 A1, 2011.12.15

代理人 金玉兰 王颖

李泽文.基于全数字锁相环的电力系统高精度同步时钟.《电力自动化设备》.2015,第35卷(第7期),

(51) Int.Cl.

审查员 李桂英

H03L 7/099 (2006.01)

权利要求书3页 说明书9页 附图6页

## (54) 发明名称

频率校正电路及频率校正方法

## (57) 摘要

本发明提供一种频率校正电路和频率校正方法，在本发明的频率校正电路中，第1时钟信号为从第1振荡器输入的第1频率精度的时钟信号，第2时钟信号为从第2振荡器输入的比第1频率精度低的第2频率精度的时钟信号，数字PLL电路重复进行输出与第1时钟信号和第2时钟信号之间的时差对应的数字控制信号，将第2振荡器用作数字控制振荡器，并根据数字控制信号使离散型电容组的电容值变化，根据离散型电容组的电容值使第2时钟信号的振荡频率变化的校正动作，由此使第2时钟信号的相位校正为第1时钟信号的相位。

1. 一种频率校正电路,其特征在于,具备:

第1振荡器,输出第1频率精度的第1时钟信号;

第2振荡器,输出第2频率精度的第2时钟信号;及

数字PLL电路,

所述第2振荡器具备离散型电容组,该离散型电容组具有各自的电容值以二进制的方式变化的多个离散型电容,并保持数字控制信号,根据保持的所述数字控制信号使所述多个离散型电容的电容值发生变化,由此整体的电容值发生变化,

所述数字PLL电路重复进行输出与所述第1时钟信号和所述第2时钟信号之间的时差对应的所述数字控制信号,将所述第2振荡器用作数字控制振荡器,并根据所述数字控制信号使所述离散型电容组的电容值变化,根据所述离散型电容组的电容值使所述第2时钟信号的振荡频率变化的校正动作,由此使所述第2时钟信号的相位校正为所述第1时钟信号的相位,

所述频率校正电路还具备:

校正动作控制电路,在所述第2振荡器首次从待机状态成为激活状态的情况下,将所述数字PLL电路设定为闭环而开始所述校正动作,在所述第2时钟信号的相位被校正为所述第1时钟信号的相位之后,将所述数字PLL电路设定为开环而结束所述校正动作。

2. 根据权利要求1所述的频率校正电路,其中,

所述第1振荡器为温度补偿晶体振荡器。

3. 根据权利要求1所述的频率校正电路,其中,

所述第2振荡器具备:

谐振器;及

振荡电路,其为使所述谐振器振荡的振荡电路,且包括所述离散型电容组,并根据所述数字控制信号使所述离散型电容组的电容值变化,输出振荡频率根据所述离散型电容组的电容值而变化的所述第2时钟信号。

4. 根据权利要求1所述的频率校正电路,其中,

所述数字PLL电路具备:

第1分频器,将所述第1时钟信号进行分频而输出第1分频信号;

第2分频器,将所述第2时钟信号进行分频而输出第2分频信号;

时间数字转换器,将所述第1分频信号与所述第2分频信号之间的时差转换为数字值而输出数字时差信号;

数字环路滤波器,输出对所述数字时差信号进行滤波而去除了高频成分的所述数字控制信号;及

所述第2振荡器,作为所述数字控制振荡器。

5. 根据权利要求4所述的频率校正电路,其中,

所述第1分频器及所述第2分频器将所述第1时钟信号及所述第2时钟信号进行分频,以使所述第1分频信号及所述第2分频信号被整数分频。

6. 根据权利要求4所述的频率校正电路,其中,

所述第1分频器及所述第2分频器将所述第1时钟信号及所述第2时钟信号进行分频,以使所述第1分频信号及所述第2分频信号中的至少一方被分数分频。

7. 根据权利要求1所述的频率校正电路,其中,

每当所述第2振荡器从待机状态成为激活状态时,所述校正动作控制电路开始所述校正动作。

8. 根据权利要求1所述的频率校正电路,其中,还具备:

温度传感器,测量所述频率校正电路的环境温度,

在所述第2振荡器从待机状态成为激活状态的情况下,仅在所述环境温度不是预先设定的一定范围内的温度时,所述校正动作控制电路开始所述校正动作。

9. 根据权利要求1所述的频率校正电路,其中,还具备:

温度传感器,测量所述频率校正电路的环境温度,

在所述第2振荡器处于激活状态的期间,每当所述环境温度成为不是预先设定的一定范围内的温度时,所述校正动作控制电路开始所述校正动作。

10. 根据权利要求1所述的频率校正电路,其中,还具备:

温度传感器,测量所述频率校正电路的环境温度,

在所述第2振荡器从待机状态成为激活状态的情况下,仅在所述环境温度为预先设定的一定范围内的温度且从上一次的校正动作起经过了预先设定的时间时,所述校正动作控制电路开始所述校正动作。

11. 根据权利要求1所述的频率校正电路,其中,还具备:

温度传感器,测量所述频率校正电路的环境温度,

在所述第2振荡器处于激活状态的期间,每当所述环境温度为预先设定的一定范围内的温度且从上一次的校正动作起经过了预先设定的时间时,所述校正动作控制电路开始所述校正动作。

12. 一种频率校正方法,其特征在于,包括:

第1振荡器输出第1频率精度的第1时钟信号的步骤;

具有各自的电容值以二进制的方式变化的多个离散型电容的离散型电容组保持数字控制信号,并根据保持的所述数字控制信号使所述多个离散型电容的电容值发生变化,由此使整体的电容值发生变化的步骤;

具备所述离散型电容组的第2振荡器根据所述离散型电容组的电容值而输出第2频率精度的第2时钟信号的步骤;

数字PLL电路重复进行输出与所述第1时钟信号和所述第2时钟信号之间的时差对应的所述数字控制信号,将所述第2振荡器用作数字控制振荡器,并根据所述数字控制信号使所述离散型电容组的电容值变化,根据所述离散型电容组的电容值使所述第2时钟信号的振荡频率变化的校正动作,由此使所述第2时钟信号的相位校正为所述第1时钟信号的相位的步骤;

在所述第2振荡器首次从待机状态成为激活状态的情况下,校正动作控制电路将所述数字PLL电路设定为闭环而开始所述校正动作的步骤;及

在所述第2时钟信号的相位被校正为所述第1时钟信号的相位之后,所述校正动作控制电路将所述数字PLL电路设定为开环而结束所述校正动作的步骤。

13. 根据权利要求12所述的频率校正方法,其中,

每当所述第2振荡器从待机状态成为激活状态时,所述校正动作控制电路开始所述校

正动作。

14. 根据权利要求12所述的频率校正方法，其中，

在所述第2振荡器从待机状态成为激活状态的情况下，仅在通过温度传感器而测量的环境温度不是预先设定的一定范围内的温度时，所述校正动作控制电路开始所述校正动作。

15. 根据权利要求12或14所述的频率校正方法，其中，

在所述第2振荡器处于激活状态的期间，每当通过温度传感器而测量的环境温度成为不是预先设定的一定范围内的温度时，所述校正动作控制电路开始所述校正动作。

16. 根据权利要求12所述的频率校正方法，其中，

在所述第2振荡器从待机状态成为激活状态的情况下，仅在通过温度传感器而测量的环境温度为预先设定的一定范围内的温度且从上一次的校正动作起经过了预先设定的时间时，所述校正动作控制电路开始所述校正动作。

17. 根据权利要求12或16所述的频率校正方法，其中，

在所述第2振荡器处于激活状态的期间，每当通过温度传感器而测量的环境温度为预先设定的一定范围内的温度且从上一次的校正动作起经过了预先设定的时间时，所述校正动作控制电路开始所述校正动作。

## 频率校正电路及频率校正方法

### 技术领域

[0001] 本发明涉及一种对从振荡器输出的时钟信号的振荡频率进行校正的频率校正电路及频率校正方法。

### 背景技术

[0002] 在一部分通信标准等中存在如下标准,即对控制通信装置的内部电路的动作的时钟信号要求 $\pm 10\text{ppm}$ (part per million: $10^{-6}$ )等非常高的频率精度的标准。为了实现该频率精度,通常,需要输出MHz(兆赫: $10^6\text{Hz}$ )频带的时钟信号的TCXO(Temperature Compensated Crystal Oscillator:温度补偿晶体振荡器)。然而,TCXO在价格方面及耗电量上存在问题。

[0003] 时钟信号的振荡频率发生变动的最大的原因在于环境温度的变化。然而,在实现 $\pm 10\text{ppm}$ 的频率精度的情况下,既有谐振器本身的随时间劣化等,也存在频率精度在2~3年内偏差 $\pm 1\sim 2\text{ppm}$ 的问题。

[0004] 以下,对通信装置进行说明。

[0005] 在通常的通信装置中,多数情况下是并用两种输出振荡频率不同的时钟信号的振荡器。从这2个振荡器输出的时钟信号通常被用于不同用途。

[0006] 第1个振荡器输出如26MHz、32MHz、35MHz等那样用于控制通信装置的内部电路的动作的两位数的MHz频带的时钟信号。第2个振荡器输出用于控制测量当前时刻的RTC(Real-Time Clock:实时时钟)的动作的32.768kHz(千赫: $10^3\text{Hz}$ )的时钟信号。

[0007] 如上所述,控制通信装置的内部电路的动作的时钟信号有时会被要求非常高的频率精度。另一方面,控制RTC的动作的时钟信号仅使用于当前时刻的测量,因此不会被要求高的频率精度。并且,RTC非常普及,因此存在例如使用TCXO来输出 $\pm 10\text{ppm}$ 以下的频率精度的时钟信号且消耗电流为 $1\mu\text{A}$ 以下的低价的RTC。

[0008] 接着,关于输出对通信装置的内部电路的动作进行控制的时钟信号的振荡器进行说明。

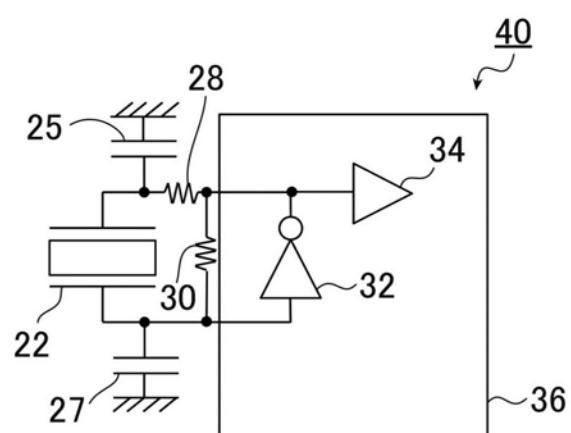

[0009] 图10是表示晶体振荡器的结构的一例的电路图。图10所示的晶体振荡器40除了包含32MHz的晶体谐振器22之外,还包含构成使所述晶体谐振器22振荡的振荡电路的负载电容25、27、电阻元件28、30、反相器32及缓冲器34。晶体谐振器22、负载电容25、27及电阻元件28、30配置于通信用LSI(large scale integration:大规模集成电路)36的外部,反相器32及缓冲器34配置于通信用LSI 36的内部。

[0010] 使用该晶体振荡器40作为输出对通信装置的内部电路的动作进行控制的时钟信号的振荡器的情况下,消耗电流为 $200\mu\text{A}$ 左右,但时钟信号的频率精度成为 $\pm 20\text{ppm}$ 左右,无法实现 $\pm 10\text{ppm}$ 的频率精度。

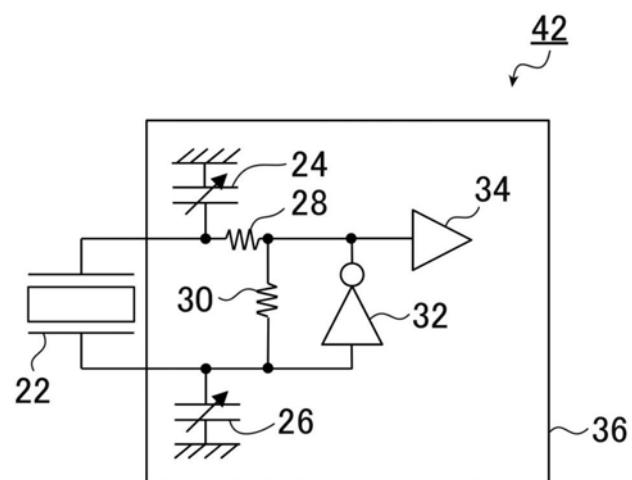

[0011] 接着,图11是表示晶体振荡器的结构的另一例的电路图。图11所示的晶体振荡器42是在图10所示的晶体振荡器40中,将负载电容25、27替换为离散型电容组,进而将该离散型电容组与电阻元件28、30配置于通信用LSI 36的内部的振荡器。

[0012] 该情况下,离散型电容组24、26的布局面积比较大,所以通信用LSI 36的布局面积增大,但由于可以减少外围元件的数量,因此,近年来采用该结构的晶体振荡器42的情况增加。

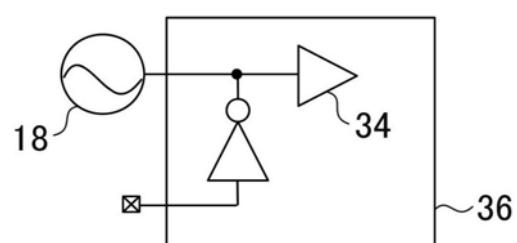

[0013] 图12是表示TCXO的结构的一例的电路图。如图12所示,32MHz的TCXO 18在通信用LSI 36的外部构成,从TCXO 18输出的时钟信号输入到配置于通信用LSI 36的内部的缓冲器34。

[0014] 使用该TCXO 18作为输出对通信装置的内部电路的动作进行控制的时钟信号的振荡器的情况下,能够将时钟信号的频率精度设为±10ppm以下,但价格比晶体振荡器40、42高,消耗电流也增大为2mA左右。

[0015] 在此,作为与本发明具有相关性的现有技术文献,有日本特开2014-197746号公报、日本特开2014-062816号公报、日本特开2013-051677号公报、日本特开平9-214336号公报及日本特开平9-133753号公报。

[0016] 在日本特开2014-197746号公报中记载有如下晶体振荡器,其检测来自基准晶体谐振器的相对于湿度稳定的基准频率信号与来自湿度传感器的根据湿度而变动的频率信号之间的频率的差分,并存储对应于差分的修正电压值,将与所检测到的差分对应的修正电压值输出,并对修正电压值进行数字/模拟转换而生成修正电压,将修正电压输出到负载电容电路,通过修正电压而调整晶体谐振器的振荡频率。

[0017] 在日本特开2014-062816号公报中记载有如下第1晶体谐振器与第2晶体谐振器组合的晶体温度测量探针,其生成使用第1晶体谐振器而生成的信号的振荡频率与使用第2晶体谐振器而生成的信号的振荡频率之差的频率成分的信号,所生成的信号的频率在预先设定的测定温度范围内成为10kHz以下,其中,第1晶体谐振器具有振荡频率相对于温度而稳定的温度特性,第2晶体谐振器具有振荡频率相对于温度而大幅变化的温度特性。

[0018] 在日本特开2013-051677号公报中记载有如下晶体振荡器,其求出温度检测值,该温度检测值对应于与第1振荡电路的振荡频率f1与其基准温度下的振荡频率f1r之间的差分对应的值和与第2振荡电路的振荡频率f2与其基准温度下的振荡频率f2r之间的差分对应的值的差分值,并根据配置有晶体谐振器的环境的温度的温度设定值与温度检测值的偏差分,对供给到实现温度的恒定化的加热部的电力进行控制。

[0019] 在日本特开平9-214336号公报中记载有如下双重比较式合成振荡器,其将压控振荡器的输出分别与2个基准时钟进行比较,并检测各频率的差分分量,以分别设定的不同的分频比对各频率的差分分量进行分频,比较各分频得到的频率,制作与该频率差成比例的电压信号并控制压控振荡器。

[0020] 在日本特开平9-133753号公报中记载有如下GPS接收机,其根据局部振荡单元的振荡频率、基准振荡单元的振荡频率、时钟振荡单元的时钟振荡频率来修正基准振荡单元的振荡频率,其中,局部振荡单元使转换接收信号的频率的频率转换单元用的局部振荡频率进行振荡,基准振荡单元使成为局部振荡单元的基准的频率进行振荡,时钟振荡单元使进行由频率转换单元转换频率的接收信号的信号处理的信号处理单元的时钟信号进行振荡。

## 发明内容

[0021] 本发明的目的在于提供一种频率校正电路及频率校正方法,其消除现有技术的问题点,且无需使价格和/或耗电量增加便能够校正从振荡器输出的时钟信号的振荡频率,并能够提高其频率精度。

[0022] 为了实现上述目的,本发明提供一种频率校正电路,其特征在于,具备:

[0023] 第1振荡器,输出第1频率精度的第1时钟信号;

[0024] 第2振荡器,输出第2频率精度的第2时钟信号;及

[0025] 数字PLL电路,

[0026] 所述第2振荡器具备离散型电容组,该离散型电容组具有各自的电容值以二进制的方式变化的多个离散型电容,并保持数字控制信号,根据所述保持的数字控制信号使所述多个离散型电容的电容值发生变化,由此整体的电容值发生变化,

[0027] 所述数字PLL电路重复进行输出与所述第1时钟信号和所述第2时钟信号之间的时差对应的所述数字控制信号,将所述第2振荡器用作数字控制振荡器,并根据所述数字控制信号使所述离散型电容组的电容值变化,根据所述离散型电容组的电容值使所述第2时钟信号的振荡频率变化的校正动作,由此使所述第2时钟信号的相位校正为所述第1时钟信号的相位。

[0028] 并且,本发明提供一种频率校正方法,其特征在于,包括:

[0029] 第1振荡器输出第1频率精度的第1时钟信号的步骤;

[0030] 具有各自的电容值以二进制的方式变化的多个离散型电容的离散型电容组保持数字控制信号,并根据所述保持的数字控制信号使所述多个离散型电容的电容值发生变化,由此使整体的电容值发生变化的步骤;

[0031] 具备所述离散型电容组的第2振荡器根据所述离散型电容组的电容值而输出第2频率精度的第2时钟信号的步骤;

[0032] 所述数字PLL电路重复进行输出与所述第1时钟信号和所述第2时钟信号之间的时差对应的所述数字控制信号,将所述第2振荡器用作数字控制振荡器,并根据所述数字控制信号使所述离散型电容组的电容值变化,根据所述离散型电容组的电容值使所述第2时钟信号的振荡频率变化的校正动作,由此使所述第2时钟信号的相位校正为所述第1时钟信号的相位的步骤。

[0033] 根据本发明,第2时钟信号的频率精度通过校正动作而成为与第1时钟信号的频率精度相等。因此,在校正动作结束之后,即使由于环境温度的变化和/或谐振器本身的同时劣化等导致第2时钟信号的频率精度变动,在变动后的第2时钟信号的频率精度高于目标频率精度的期间,第2时钟信号能够达到目标频率精度。

[0034] 并且,本发明使用布局面积大的离散型电容组作为数字PLL电路的数字控制振荡器的构成要件。然而,近年来的通信用LSI中采用内置负载电容的晶体振荡器的情况正在增加。并且,本发明使用第2振荡器作为数字控制振荡器,因此通信用LSI的布局面积不会因离散型电容组而增加。

[0035] 并且,第2振荡器在校正动作结束之后,数字PLL电路被设定为开环而成为待机状态,其动作被停止,因此也几乎不产生数字PLL电路的耗电量的增加。

## 附图说明

- [0036] 图1是表示本发明的频率校正电路的结构的一实施方式的电路图。

- [0037] 图2A及图2B是分别表示第2振荡器进行连续动作及间歇动作的情况的一例的概念图。

- [0038] 图3是表示数字PLL电路成为激活状态而被设定为闭环的状态的一例的概念图。

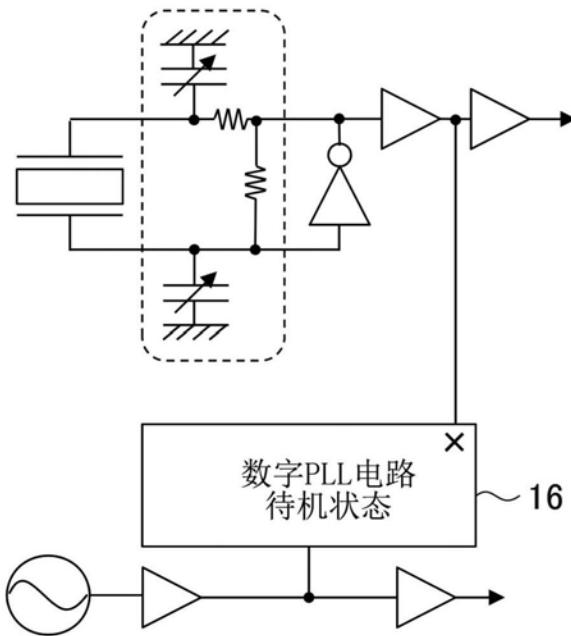

- [0039] 图4是表示数字PLL电路成为待机状态而被设定为开环的状态的一例的概念图。

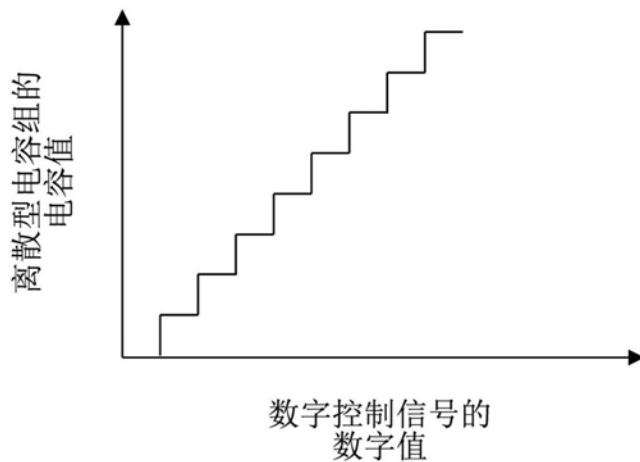

- [0040] 图5是表示数字控制信号的数字值与离散型电容组的电容值的关系的一例的曲线图。

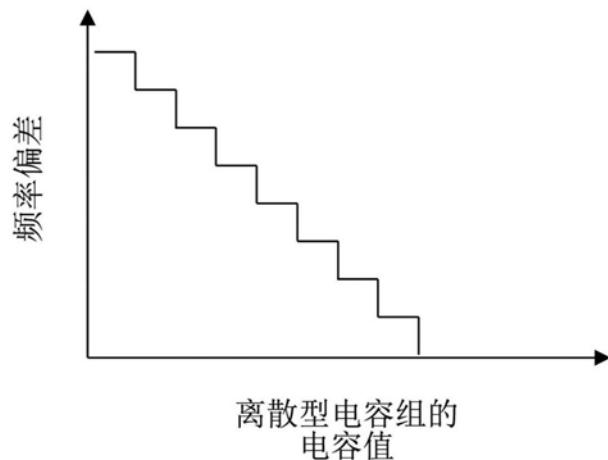

- [0041] 图6是表示离散型电容组的电容值与第2时钟信号的频率偏差的关系的一例的曲线图。

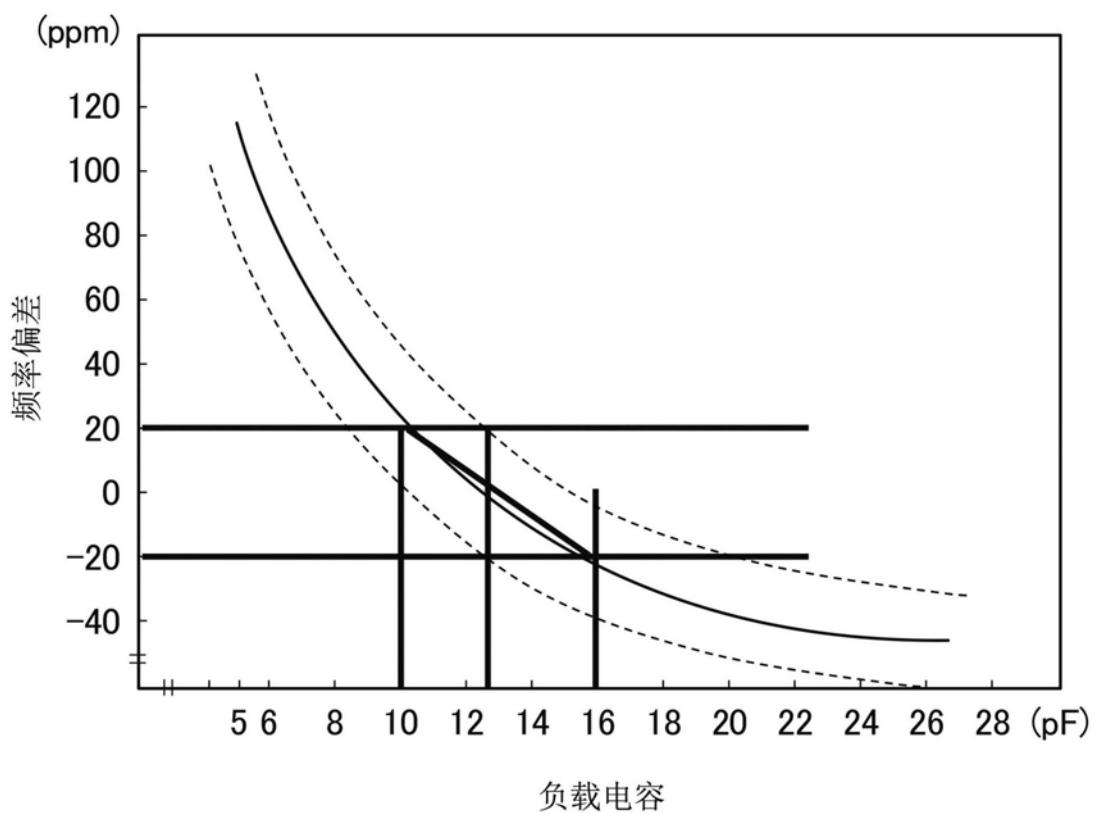

- [0042] 图7是表示从晶体振荡器输出的时钟信号的频率偏差与负载电容的特性的一例的曲线图。

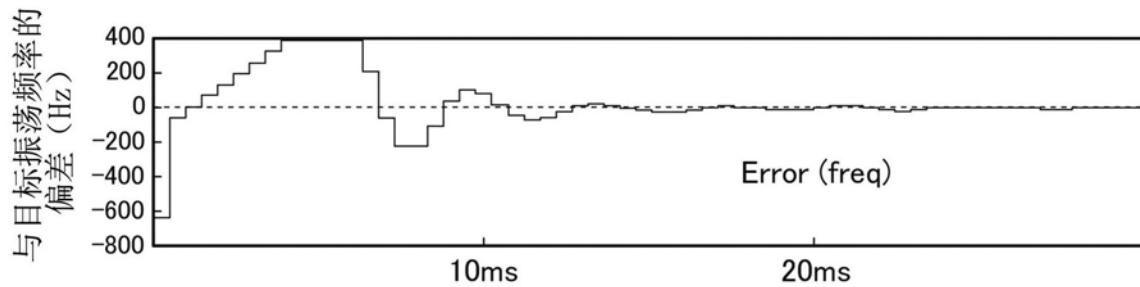

- [0043] 图8A及图8B是分别表示在第1分频信号及第2分频信号被整数分频的情况下、第2时钟信号的与目标振荡频率及目标频率精度的偏差的模拟结果的一例的曲线图。

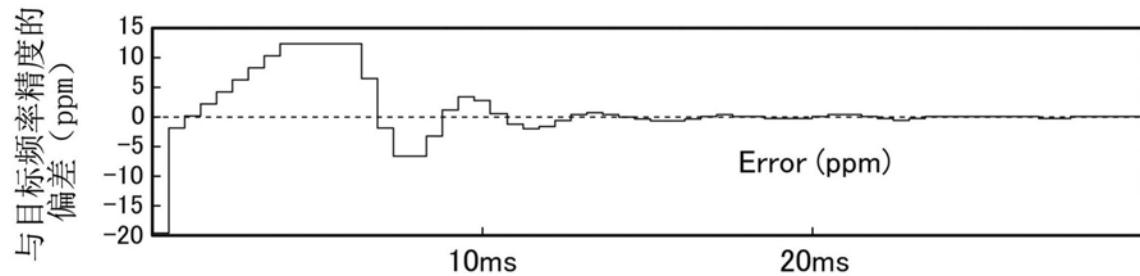

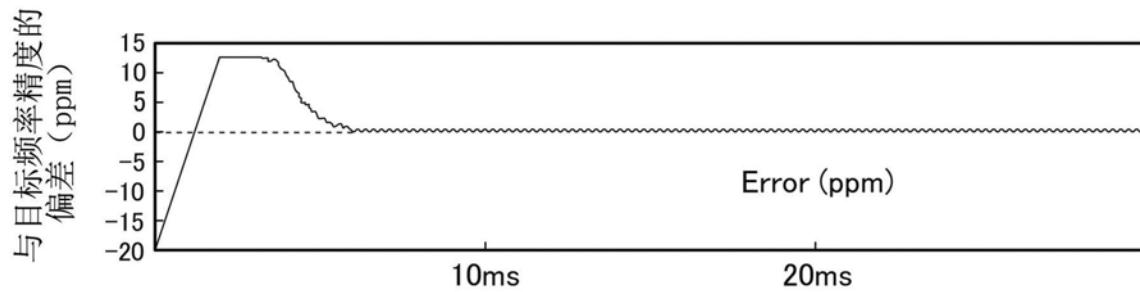

- [0044] 图9是表示在第1分频信号及第2分频信号被分数分频的情况下、第2时钟信号的与目标频率精度的偏差的模拟结果的一例的曲线图。

- [0045] 图10是表示晶体振荡器的结构的一例的电路图。

- [0046] 图11是表示晶体振荡器的结构的另一例的电路图。

- [0047] 图12是表示TCXO的结构的一例的电路图。

## 具体实施方式

- [0048] 以下,根据附图所示的优选实施方式,对本发明的频率校正电路及频率校正方法进行详细的说明。

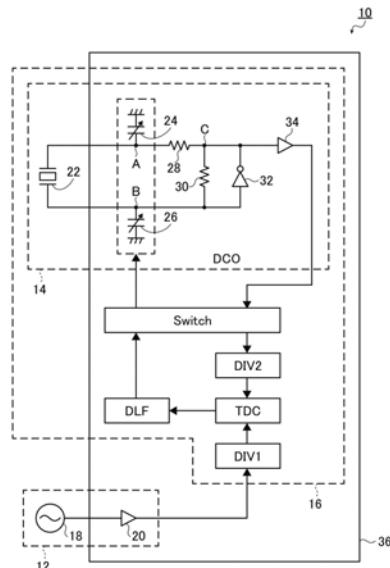

- [0049] 图1是表示本发明的频率校正电路的结构的一实施方式的电路图。图1所示的频率校正电路10使用对通信用LSI 36的RTC的动作进行控制的时钟信号来校正对通信用LSI 36的内部电路的动作进行控制的时钟信号的振荡频率。频率校正电路10由第1振荡器12、第2振荡器14及数字PLL电路(Phase Locked Loop:锁相环路)16构成。

- [0050] 首先,第1振荡器12由温度补偿晶体振荡器(TCXO)18和缓冲器20而构成,并且以第1频率精度输出第1振荡频率的第1时钟信号。

- [0051] 本实施方式的情况下,使用输出对通信用LSI 36的RTC的动作进行控制的时钟信号的振荡器作为第1振荡器12。第1频率精度比对通信用LSI 36的内部电路的动作进行控制的时钟信号的目标频率精度高。

- [0052] TCXO 18用于对晶体谐振器的频率温度特性进行补偿,且在较广的温度范围输出频率精度高的时钟信号,在本实施方式的情况下,对通信用LSI 36的内部电路的动作进行控制的时钟信号的目标频率精度为±10ppm,相对于此,使用以比其高的±5ppm的频率精度输出32.768kHz的振荡频率的时钟信号的TCXO 18。

- [0053] 如上所述,对控制RTC的动作的时钟信号不要求高的频率精度,但由于RTC非常普及,因此只要为输出32.768kHz的振荡频率的时钟信号的TCXO即可,例如能够比较低价地利用以上述±5ppm的频率精度输出32.768kHz的振荡频率的时钟信号,且1μA以下的消耗电流

的TCXO。

[0054] 从TCXO 18输出的时钟信号输入到缓冲器20,从缓冲器20输出有第1时钟信号。

[0055] 在第1振荡器12中,TCXO 18配置于通信用LSI 36的外部,缓冲器20配置于通信用LSI 36的内部。

[0056] 接着,第2振荡器14为以比第1频率精度低的第2频率精度输出比第1振荡频率高的第2振荡频率的第2时钟信号的数字振荡器,除了包含晶体谐振器22之外,还包含构成使晶体谐振器22振荡的振荡电路的离散型电容组24、26、电阻元件28、30、反相器32及缓冲器34。

[0057] 第2振荡器14为输出对通信用LSI 36的内部电路的动作进行控制的时钟信号的振荡器。第2频率精度比第2时钟信号的目标频率精度低。

[0058] 在本实施方式的情况下,晶体谐振器22以32MHz的振荡频率进行振荡,并连接于通信用LSI 36的内部节点A与内部节点B之间。

[0059] 离散型电容组24、26具有各自的电容值以二进制的方式变化的多个离散型电容,并保持从数字PLL电路16输入的数字控制信号,根据保持的数字控制信号使多个离散型电容的电容值发生变化,由此其整体的电容值发生变化。离散型电容组24、26的一个端子分别连接于内部节点A及内部节点B,离散型电容组24、26的另一端子连接于地。

[0060] 电阻元件28、30的一个端子分别连接于内部节点A及内部节点B,电阻元件28、30的另一端子连接于内部节点C。

[0061] 反相器32的输入端子连接于内部节点B,其输出端子连接于内部节点C。

[0062] 反相器32的输出信号输入到缓冲器34,从缓冲器34输出有第2时钟信号。

[0063] 在第2振荡器14中,晶体谐振器22配置于通信用LSI 36的外部,构成振荡电路的离散型电容组24、26、电阻元件28、30、反相器32及缓冲器34配置于通信用LSI 36的内部。

[0064] 接着,数字PLL电路16将第2振荡器14用作数字控制振荡器DCO,并使第2时钟信号的相位校正为第1时钟信号的相位,数字PLL电路16由第1分频器DIV1、第2分频器DIV2、时间数字转换器TDC、数字环路滤波器DLF及校正动作控制电路Switch构成。

[0065] 第1分频器DIV1将从第1振荡器12输入的第1时钟信号进行分频而输出第1分频信号。

[0066] 第2分频器DIV2将从第2振荡器14输入的第2时钟信号进行分频而输出第2分频信号。

[0067] 时间数字转换器TDC检测从第1分频器DIV1输入的第1分频信号与从第2分频器DIV2输入的第2分频信号之间的时差,并将检测到的时差转换为数字值而输出数字时差信号。

[0068] 数字环路滤波器DLF对从时间数字转换器TDC输入的数字时差信号进行滤波而去除高频成分,并输出被去除高频成分的数字控制信号。

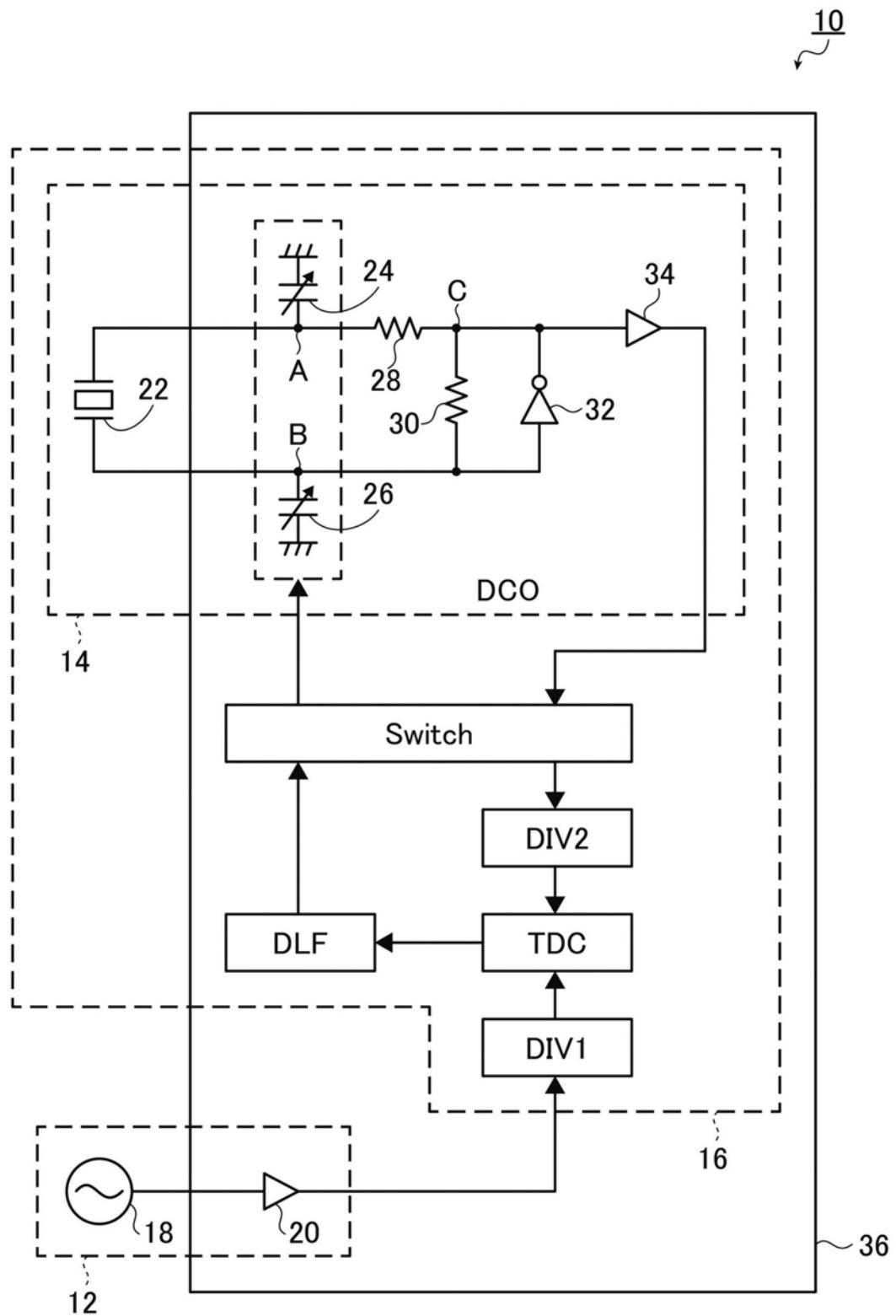

[0069] 图2A及图2B是分别表示第2振荡器进行连续动作及间歇动作时的情况的一例的概念图。图2A及图2B的横轴表示时间的经过,纵轴表示谐振器的开启状态(ON)及关闭状态(OFF)。

[0070] 在移动电话等中,进行无论是否正在进行通话或数据通信,而始终使用移动电话网络这样的连续动作。该情况下,如图2A所示,谐振器始终被设为开启状态,第2振荡器14始终被设为激活状态。

[0071] 另一方面,在IoT(Internet of Things:物联网)等中,进行仅在需要使用的情况下使用无线传感器网络这样的间歇动作。该情况下,如图2B所示,仅在需要使用无线网络的期间,谐振器被设为开启状态,第2振荡器14被设为激活状态。另一方面,在不需要使用无线网络的期间,为了削减耗电量,谐振器被设为关闭状态,第2振荡器14被设为待机状态。

[0072] 另一方面,由于第1振荡器12需要进行当前时刻的测量,因此与连续动作、间歇动作无关,始终被设为激活状态。

[0073] 校正动作控制电路Switch根据从频率校正电路10的外部输入的状态信号,在第2振荡器14从待机状态成为激活状态的情况下,将数字PLL电路16设定为闭环而开始校正动作,并在第2时钟信号的相位通过数字PLL电路16而被校正为第1时钟信号的相位之后,将数字PLL电路16设定为开环而结束校正动作。

[0074] 在频率校正电路10中,第2振荡器14被用作构成数字PLL电路16的数字控制振荡器DCO。数字控制振荡器DCO保持从数字环路滤波器DLF输入的数字控制信号,并根据数字控制信号使离散型电容组24、26的电容值变化,输出振荡频率根据离散型电容组24、26的电容值而变化的第2时钟信号。

[0075] 接着,对第2振荡器14进行间歇动作时的频率校正电路10的动作进行说明。

[0076] 在频率校正电路10中,第2时钟信号的目标频率精度为±10ppm,相当于此,以比第2时钟信号的目标频率精度高的±5ppm的频率精度从第1振荡器12输出32.768kHz的振荡频率的第1时钟信号。并且,作为初始状态,以比第2时钟信号的目标频率精度低的±20ppm的频率精度从第2振荡器14输出32MHz的振荡频率的第2时钟信号。

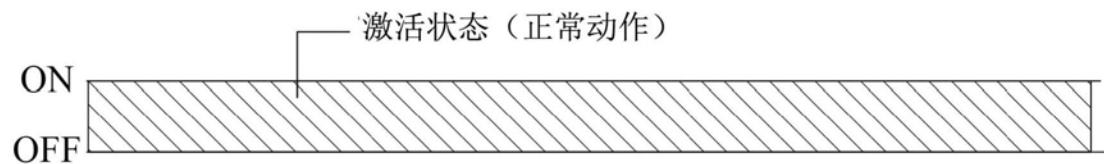

[0077] 如图2B所示,根据状态信号,若第2振荡器14首次从待机状态成为激活状态,则如图3所示通过校正动作控制电路Switch,使数字PLL电路16成为激活状态而设定为闭环,开始校正动作而使第2时钟信号的相位校正为第1时钟信号的相位。即,开始校正第2时钟信号的振荡频率。

[0078] 若数字PLL电路16成为闭环,则通过第1分频器DIV1将32.768kHz的第1时钟信号分频为1/16的振荡频率,而输出2.048kHz的第1分频信号作为比较频率。并且,通过第2分频器DIV2将32MHz的第2时钟信号分频为1/15625的振荡频率,而输出约为2.048kHz的第2分频信号作为校正后的目标频率。

[0079] 即,以使第1分频信号及第2分频信号相对于第2振荡器的目标频率而被整数分频的方式将第1时钟信号及第2时钟信号进行分频得到比较频率。

[0080] 接着,通过时间数字转换器TDC来检测第1分频信号与第2分频信号的时差,并将所检测到的时差转换成数字值而输出数字时差信号。

[0081] 接着,通过数字环路滤波器DLF对从时间数字转换器TDC输入的数字时差信号进行滤波而去除高频成分,并输出被去除高频成分的数字控制信号。

[0082] 接着,第2振荡器14被用作数字控制振荡器DCO,根据数字控制信号使离散型电容组24、26的电容值变化,并从第2振荡器14输出振荡频率根据离散型电容组24、26的电容值而变化的第2时钟信号。

[0083] 图5是表示数字控制信号的数字值与离散型电容组的电容值的关系的一例的曲线图。图5所示的曲线图的横轴为数字控制信号的数字值,纵轴为离散型电容组的电容值。在该曲线图所示的例子的情况下,可知随着数字控制信号的数字值变大,离散型电容组的电

容值逐级变大。

[0084] 接着,图6是表示离散型电容组的电容值与第2时钟信号的频率偏差的关系的一例的曲线图。图6所示的曲线图的横轴为离散型电容组的电容值,纵轴为第2时钟信号的频率偏差(与目标频率的偏差)。在该曲线图所示的例子的情况下,可知随着离散型电容组的电容值变大,第2时钟信号的频率偏差逐级变小(与目标频率的偏差变小)。

[0085] 图7是表示从晶体振荡器输出的时钟信号的频率偏差与负载电容的特性的一例的曲线图。图7所示的曲线图的横轴为构成晶体振荡器的负载电容的电容值,纵轴为时钟信号的频率偏差。在该曲线图所示的例子的情况下,可知若负载电容的电容值以约13pF为中心在±3pF的范围变化,则时钟信号的频率偏差在±20ppm的范围变化。

[0086] 例如,考虑如下情况,即数字控制信号的数字值以512级进行变化,离散型电容组的电容值在±3pF的范围变化,且能够在±20ppm的范围修正第2时钟信号的频率精度。在该情况下,若进行线性近似,则在数字控制信号的数字值的每1级,使离散型电容组的电容值以约12fF为单位变化,能够以约0.1ppm单位的精度来控制第2时钟信号的频率偏差。

[0087] 如上所述,在数字PLL电路16中,重复进行输出与第1时钟信号和第2时钟信号之间的时差对应的数字控制信号,将第2振荡器14用作数字控制振荡器DCO,并根据数字控制信号使离散型电容组24、26的电容值变化,根据离散型电容组24、26的电容值使第2时钟信号的振荡频率变化的校正动作,由此第2时钟信号的相位被校正为第1时钟信号的相位。

[0088] 图8A及图8B是分别表示在第1分频信号及第2分频信号被整数分频的情况下的、第2时钟信号的与目标振荡频率及目标频率精度的偏差的模拟结果的一例的曲线图。图8A及图8B所示的曲线图的横轴表示时间的经过,纵轴分别表示第2时钟信号的与目标振荡频率的偏差Error (freq) 及与目标频率精度的偏差(频率偏差) Error (ppm)。

[0089] 该曲线图为如下情况的模拟结果,即第1时钟信号为理想状态(无频率误差),其振荡频率为32.768kHz,频率精度为±5ppm(即± $163.84 \times 10^{-3}$ Hz),在校正前的第2时钟信号的振荡频率为32MHz、频率精度为±20ppm(即±640Hz)的情况下,校正后的第2时钟信号的目标振荡频率为32MHz、目标频率精度为±10ppm(即±320Hz)。

[0090] 如该曲线图所示,第2时钟信号的振荡频率的偏差Error (freq) 相对于目标振荡频率的偏差0Hz从-600Hz左右开始逐渐向正值侧变大而成为+400Hz左右,接着,逐渐向负值侧变小而成为-200Hz左右这样重复向正值侧及负值侧的变化,最终收敛于目标振荡频率的偏差0Hz,即目标振荡频率32MHz。

[0091] 同样地,第2时钟信号的频率精度的偏差Error (ppm) 相对于目标频率精度的偏差0ppm从-20ppm左右开始逐渐向正值侧变大而成为+12ppm左右,接着,逐渐向负值侧变小而成为-7ppm左右这样重复向正值侧及负值侧的变化,最终收敛于目标频率精度的偏差0ppm,即目标频率精度±10ppm。

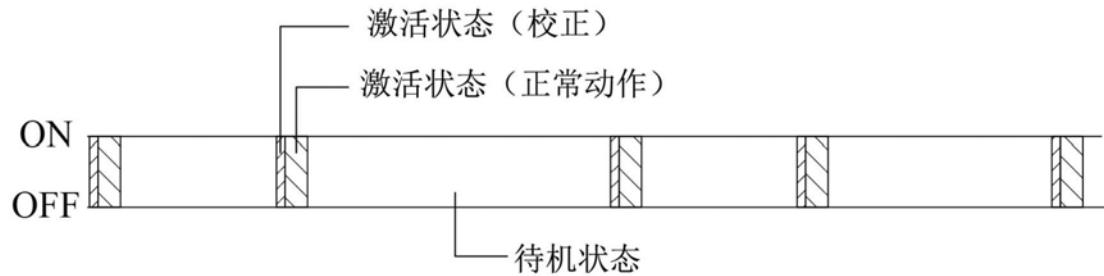

[0092] 在第2时钟信号的相位被校正为第1时钟信号的相位之后,如图4所示,通过校正动作控制电路Switch,使数字PLL电路16成为待机状态而设定为开环,结束校正动作。此后,进行通信时的正常动作。

[0093] 第2时钟信号的频率精度通过校正动作而成为与第1时钟信号的频率精度相等的±5ppm左右。因此,在校正动作结束之后,即使由于环境温度的变化和/或谐振器本身的随时间劣化等导致第2时钟信号的频率精度变动,例如变动了±1ppm左右,其频率精度也为±

6ppm左右,在变动后的第2时钟信号的频率精度高于目标频率精度 $\pm 10\text{ppm}$ 的期间,第2时钟信号能达到目标频率精度 $\pm 10\text{ppm}$ 。

[0094] 并且,频率校正电路10作为数字PLL电路16的数字控制振荡器DCO的构成要件而使用布局面积大的离散型电容组24、26。然而,如上所述,近年来的通信用LSI中采用内置负载电容的晶体振荡器的情况正在增加。并且,由于频率校正电路10使用第2振荡器14作为数字控制振荡器DCO,因此通信用LSI 36的布局面积不会因离散型电容组24、26而增加。

[0095] 并且,在第2振荡器14进行间歇动作的情况下,如图2B所示,在校正动作结束之后,数字PLL电路16被设定为开环而成为待机状态,其动作被停止,因此也几乎不产生数字PLL电路16的耗电量的增加。

[0096] 另外,可以通过校正动作控制电路Switch,每当第2振荡器14从待机状态成为激活状态时,将数字PLL电路16设定为闭环,开始第2时钟信号的振荡频率的校正动作,并在校正动作之后,将数字PLL电路16设定为开环,结束校正动作。

[0097] 并且,也可以具备测量频率校正电路10的环境温度的温度传感器,并在第2振荡器14从待机状态成为激活状态的情况下,仅在环境温度不是预先设定的一定范围内的温度时,换言之,仅在环境温度的变动幅度大于预先设定的值时,通过校正动作控制电路Switch,将数字PLL电路16设定为闭环而开始校正动作,在校正动作之后,将数字PLL电路16设定为开环而结束校正动作。

[0098] 同样地,也可以具备温度传感器,并在第2振荡器14从待机状态成为激活状态的情况下,仅在环境温度为预先设定的一定范围内的温度且从上一次的校正动作起经过了预先设定的时间时,通过校正动作控制电路Switch,将数字PLL电路16设定为闭环而开始校正动作,在校正动作之后,将数字PLL电路16设定为开环而结束校正动作。

[0099] 并且,以第2振荡器14进行间歇动作的情况为例进行了说明,但如图2A所示,频率校正电路10同样也可以适用于第2振荡器14进行连续动作的情况。在连续动作的情况下,在通信过程中,即在使用第2时钟信号的期间无法进行该校正动作。因此,可以考虑例如暂时停止通信而在此期间进行第2时钟信号的校正动作。

[0100] 例如可以具备温度传感器,并在第2振荡器14处于激活状态的期间,每当环境温度成为不是预先设定的一定范围内的温度时,通过校正动作控制电路Switch而开始所述校正动作。

[0101] 同样地,也可以具备温度传感器,并在第2振荡器14处于激活状态的期间,每当环境温度为预先设定的一定范围内的温度且从上一次的校正动作起经过了预先设定的时间时开始校正动作。

[0102] 并且,以第1分频信号及第2分频信号被整数分频的情况为例进行了说明,但同样也可以适用于第1分频信号及第2分频信号中的至少一方被分数分频的情况。

[0103] 在该情况下,例如,通过第1分频器DIV1,32.768kHz的第1时钟信号被分频为1/1的振荡频率,即第1时钟信号的振荡频率而将其本身的32.768kHz的第1分频信号输出。并且,通过第2分频器DIV2,32MHz的第2时钟信号被分频为16/15625的振荡频率,而将32.768kHz的第2分频信号输出。

[0104] 即,以使第1分频信号及第2分频信号被分数分频的方式,即成为包括小数点以下的值的分数值的振荡频率的方式将第1时钟信号及第2时钟信号进行分频。

[0105] 图9是表示在第1分频信号及第2分频信号被分数分频的情况下、第2时钟信号的与目标频率精度的偏差的模拟结果的一例的曲线图。图9所示的曲线图的横轴表示时间的经过,纵轴表示第2时钟信号的与目标频率精度的偏差(频率偏差)中,仅相对于第1分频信号及第2分频信号的整数部分的偏差Error (ppm)。

[0106] 该曲线图同样为如下情况的模拟结果,即第1时钟信号为理想状态(无频率误差),其振荡频率为32.768kHz、频率精度为±5ppm(即± $163.84 \times 10^{-3}$ Hz),在校正前的第2时钟信号的振荡频率为32MHz、频率精度为±20ppm(即±640Hz)的情况下,校正后的第2时钟信号的目标振荡频率为32MHz,目标频率精度为±10ppm(即±320Hz)。

[0107] 如该曲线图所示,第2时钟信号的频率精度的偏差Error (ppm)相对于目标频率精度的偏差0ppm从-20ppm左右开始逐渐向正值侧变大而成为+12ppm左右,接着,逐渐向负值侧变小这样重复向正值侧及负值侧的变化,最终收敛于目标频率精度的偏差0ppm左右,即目标频率精度±10ppm以下。

[0108] 在分数分频的情况下,第2时钟信号的频率精度在收敛于目标频率精度±10ppm以下之后,也从目标频率精度±10ppm内的中心值向正值侧及负值侧重复±0.25ppm左右的细微的变化。

[0109] 如上所述,在第2振荡器14进行间歇动作的情况下,如图2B所示,在校正动作结束之后,数字PLL电路16被设定为开环而成为待机状态,其动作被停止。因此,不会产生第2时钟信号的频率精度收敛于目标频率精度左右之后的前述的细微的变化,也不会对通信时的正常动作产生影响。

[0110] 另外,第1振荡器12并不限于TCXO,只要是作为第1时钟信号输出比目标频率精度高的频率精度的时钟信号的振荡器,则其具体的结构无任何限定。并且,作为第1振荡器12而使用输出对RTC的动作进行控制的时钟信号的振荡器,但并不限于此,也可以使用其它用途的振荡器或频率校正电路10专用的振荡器。

[0111] 第2振荡器14并不限于晶体谐振器22,例如可以使用包括陶瓷谐振器、TCXO、MEMS (Micro Electro Mechanical Systems:微机电系统) 谐振器等的各种谐振器。并且,第2振荡器14只要是具备离散型电容组且根据其电容值使第2时钟信号的振荡频率变化的振荡器,则其具体的结构无任何限定。

[0112] 以上,关于本发明进行了详细的说明,但本发明并不限于上述实施方式,在不脱离本发明宗旨的范围内,当然可以进行各种改进或变更。

图1

图2A

图2B

图3

图4

图5

图6

图7

图8A

图8B

图9

图10

图11

图12