(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4083816号

(P4083816)

(45) 発行日 平成20年4月30日(2008.4.30)

(24) 登録日 平成20年2月22日(2008.2.22)

(51) Int.Cl.

F 1

|                   |                  |            |         |

|-------------------|------------------|------------|---------|

| <b>G06F 12/08</b> | <b>(2006.01)</b> | G06F 12/08 | 5 7 9   |

| <b>G06F 1/32</b>  | <b>(2006.01)</b> | G06F 12/08 | 5 3 1 C |

| <b>G06F 1/04</b>  | <b>(2006.01)</b> | G06F 1/00  | 3 3 2 B |

|                   |                  | G06F 1/04  | 3 0 1 C |

請求項の数 8 (全 18 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願平10-548035                 |

| (86) (22) 出願日 | 平成10年1月27日(1998.1.27)        |

| (65) 公表番号     | 特表2002-510413(P2002-510413A) |

| (43) 公表日      | 平成14年4月2日(2002.4.2)          |

| (86) 國際出願番号   | PCT/US1998/001519            |

| (87) 國際公開番号   | W01998/050846                |

| (87) 國際公開日    | 平成10年11月12日(1998.11.12)      |

| 審査請求日         | 平成16年10月7日(2004.10.7)        |

| (31) 優先権主張番号  | 08/841,858                   |

| (32) 優先日      | 平成9年5月5日(1997.5.5)           |

| (33) 優先権主張国   | 米国(US)                       |

|           |                                                                       |

|-----------|-----------------------------------------------------------------------|

| (73) 特許権者 | インテル・コーポレーション<br>アメリカ合衆国・95052・カリフォルニア州・サンタクララ・ミッション・カレッジ・ブーレバード・2200 |

| (74) 代理人  | 弁理士 山川 政樹                                                             |

| (74) 代理人  | 弁理士 黒川 弘朗                                                             |

| (74) 代理人  | 弁理士 紺野 正幸                                                             |

| (74) 代理人  | 弁理士 西山 修                                                              |

| (74) 代理人  | 弁理士 鈴木 二郎                                                             |

最終頁に続く

(54) 【発明の名称】低電力状態で動作する集積回路でキャッシュコヒーレンシを維持する方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

キャッシュ・コヒーレンシ動作を実行する必要のある第1組の機能ユニットとキャッシュ・コヒーレンシ動作を実行する必要のない第2組の機能ユニットとを含む集積回路を、全電力状態ならびに第1および第2の低電力状態で動作する装置であって、

集積回路が全電力状態から第1の低電力状態に遷移するか、それとも第2の低電力状態に遷移するかを示す構成信号を受け取る第1の入力と、

構成信号に応じて集積回路を全電力状態から第1または第2の低電力状態に遷移させる電力供給停止信号を受け取る第2の信号入力と、

集積回路の外部の装置による、集積回路からアクセスできるメモリ資源への、メモリ・アクセスを示すアクセス信号を受け取る第3の入力と、

構成信号および電力供給停止信号に応じて集積回路を全電力状態から第1または第2の低電力状態に遷移させ、

(1) 第1の低電力状態のときには、キャッシュ・コヒーレンシ動作を実行するのに必要な、集積回路内の第1組の機能ユニットにクロック信号を連続的に伝搬し、

(2) 第2の低電力状態のときには、集積回路内の第1組の機能ユニットと第2組の機能ユニットとの両方にクロック信号を伝播せず、アクセス信号に応答して、クロック信号を第1組の機能ユニットには伝播するが、第2組の機能ユニットには伝搬しないことによって、集積回路が第1の低電力状態と第2の低電力状態との両方でキャッシュ・コヒーレンシ動作を実行することを可能にする電力低減論理と

10

20

を備えることを特徴とする装置。

【請求項 2】

全電力消費量モードならびに第1の低電力消費量モードおよび第2の低電力消費量モードで動作することのできる集積回路であって、

集積回路が全電力消費量モードから第1の低電力消費量モードに遷移するか、それとも第2の低電力消費量モードに遷移するかを示す構成信号を受け取る構成入力と、

集積回路からアクセスできるメイン・メモリとキャッシュ・メモリとの間のコヒーレンシを維持するキャッシュ・コヒーレンシ回路と、

集積回路内で命令を処理する命令処理回路と、

(1) 電力供給停止信号に応答し、かつ構成信号に従って、集積回路が第1の低電力消費量モードに遷移するときには、命令処理回路へのクロック信号をディスエーブルするが、キャッシュ・コヒーレンシ回路へのクロック信号はディスエーブルせず、

(2) 電力供給停止信号に応答し、かつ構成信号に従って、集積回路が第2の低電力消費量モードに遷移するときには、キャッシュ・コヒーレンシ回路と命令処理回路の両方へのクロック信号をディスエーブルし、かつ集積回路が第2の低電力消費量モードであるときに、メモリ・アクセスを示す入力信号に応答してキャッシュ・コヒーレンシ回路へのクロック信号を一時的にイネーブルする電力低減回路と

を備えることを特徴とする集積回路。

【請求項 3】

プロセッサ・バスと、

プロセッサ・バスに結合されたプロセッサと、

システム・バスと、

システム・バスに結合された周辺装置と、

プロセッサおよび周辺装置からアクセスできるメイン・メモリと、

プロセッサからアクセスできるキャッシュ・メモリとを備え、

プロセッサが、全電力消費量モードならびに第1の低電力消費量モードおよび第2の低電力消費量モードで動作することができ、

プロセッサが全電力消費量モードから第1の低電力消費量モードに遷移するか、それとも第2の低電力消費量モードに遷移するかを示す構成信号を受け取る構成入力と、

メイン・メモリと、キャッシュ・メモリとの間のコヒーレンシを維持するキャッシュ・コヒーレンシ回路と、

プロセッサ内で命令を処理する命令処理回路と、

(1) 電力供給停止信号に応答し、かつ構成信号に従って、プロセッサが第1の低電力消費量モードに遷移するときには、命令処理回路へのクロック信号をディスエーブルするが、キャッシュ・コヒーレンシ回路へのクロック信号はディスエーブルせず、

(2) 電力供給停止信号に応答し、かつ構成信号に従って、プロセッサが第2の低電力消費量モードに遷移するときには、キャッシュ・コヒーレンシ回路と命令処理回路の両方へのクロック信号をディスエーブルし、かつプロセッサが第2の低電力消費量モードであるときに、メモリ・アクセスを示す入力信号に応答してキャッシュ・コヒーレンシ回路へのクロック信号を一時的にイネーブルする電力低減回路と

を備えることを特徴とするコンピュータ・システム。

【請求項 4】

キャッシュ・コヒーレンシ動作を実行する必要のある第1組の機能ユニットとキャッシュ・コヒーレンシ動作を実行する必要のない第2組の機能ユニットとを含む集積回路を全電力状態と第1または第2の低電力状態との間で遷移させる方法であって、

電力供給停止信号が検出されたことに応答して、全電力状態と第1または第2の低電力状態との間の遷移を指定する構成信号に応じて設定された構成表示の状態を判定するステップと、

構成表示が第1の状態に設定されている場合、集積回路が全電力状態から第1の低電力状態に遷移するように第2組の機能ユニットへのクロック信号をゲートするステップと、

10

20

30

40

50

構成表示が第2の状態に設定されている場合、集積回路を全電力状態から第2の低電力状態に遷移させ、クロック信号が、集積回路内の第1組の機能ユニットへのクロック信号と第2組の機能ユニットへのクロック信号の両方をゲートし、かつクロック信号が、集積回路の外部の装置によるメモリ・アクセスを示す信号に応答して、第1組の機能ユニットには伝搬されるが、第2組の機能ユニットには伝搬されないステップとを含むことを特徴とする方法。

**【請求項5】**

第1および第2の低電力消費量モードで動作するときにキャッシュ・コヒーレンシを維持するように集積回路を構成する方法であって、

所定の構成例において構成信号が第1の状態を占めるか、それとも第2の状態を占めるかを判定するステップと、

10

構成信号が第1の状態を占める場合に、第1の低電力消費量モードに入り、命令処理回路への電力供給を停止し、キャッシュ・コヒーレンシ回路に電力を供給するように集積回路を構成するステップと、

構成信号が第2の状態を占める場合に、第2の低電力消費量モードに入り、命令処理回路とキャッシュ・コヒーレンシ回路の両方への電力供給を停止し、メモリ・アクセスを示す入力信号に応答してキャッシュ・コヒーレンシ回路に一時的に電力を投入するように集積回路を構成するステップとを含む方法。

**【請求項6】**

キャッシュ・コヒーレンシ動作を実行するのに必要な第1組の機能ユニットとキャッシュ・コヒーレンシ動作を実行するのに必要なない第2組の機能ユニットとを含む集積回路に関連する電力低減論理であって、

20

電力低減信号を受け取る第1の入力と、

電力低減論理に関連する集積回路が、電力低減信号がアサートされたことに応答して、電力投入モードから第1の電力供給停止モードに遷移するか、又は第2の電力供給停止モードに遷移するかを示す構成信号を受け取る第2の入力と、

メモリ・アクセスを示すアクセス信号を受け取る第3の入力と、

集積回路が第1の電力供給停止モードであるときには、集積回路の第2組の機能ユニットへのクロック信号をディスエーブルするが、集積回路の第1組の機能ユニットへのクロック信号はディスエーブルせず、集積回路が第2の電力供給停止モードであるときには、集積回路の第1組の機能ユニットと第2組の機能ユニットとの両方へのクロック信号をディスエーブルするが、アクセス信号がアサートされたことに応答して第1組の機能ユニットがキャッシュ・コヒーレンシ動作を実行できるように、アクセス信号がアサートされたことに応答して第1組の機能ユニットへのクロック信号を一時的にイネーブルし、その後、第1組の機能ユニットへのクロック信号を再びディスエーブルするクロック・ディスエーブル回路とを備えることを特徴とする電力低減論理。

30

**【請求項7】**

全電力消費量モードならびに第1および第2の低電力消費量モードで動作することのできる集積回路であって、

集積回路が全電力消費量モードから第1の低電力消費量モードに遷移するか、それとも第2の低電力消費量モードに遷移するかを示す構成信号を受け取る構成手段と、

40

メイン・メモリと、集積回路からアクセスできるキャッシュ・メモリとの間のコヒーレンシを維持するキャッシュ・コヒーレンシ回路と、

集積回路内で命令を処理する命令処理回路と、

(1) 電力供給停止信号に応答し、かつ構成信号に従って、集積回路が第1の低電力消費量モードに遷移したときに、命令処理回路へのクロック信号をディスエーブルするが、キャッシュ・コヒーレンシ回路へのクロック信号はディスエーブルせず、

(2) 電力供給停止信号に応答し、かつ構成信号に従って、集積回路が第2の低電力消費量モードに遷移したときに、命令処理回路とキャッシュ・コヒーレンシ回路との両方へのクロック信号をディスエーブルし、集積回路が第2の低電力消費量モードであるときに、

50

メモリ・アクセスを示す入力信号に応答して、キャッシュ・コヒーレンシ回路へのクロック信号を一時的にイネーブルする電力低減手段と

を備えることを特徴とする集積回路。

**【請求項 8】**

キャッシュ・コヒーレンシ動作を実行するのに必要な第1組の機能ユニットとキャッシュ・コヒーレンシ動作を実行するのに必要なない第2組の機能ユニットとを含む集積回路に

関連する電力低減論理であって、

電力低減信号を受け取る第1の入力手段と、

電力低減論理に関連する集積回路が、電力低減信号がアサートされたことに応答して、電力投入モードから第1の電力供給停止モードに遷移するか、それとも第2の電力供給停止モードに遷移するかを示す構成信号を受け取る第2の入力手段と、

10

メモリ・アクセスを示すアクセス信号を受け取る第3の入力手段と、

集積回路が第1の電力供給停止モードであるときには、集積回路の第2組の機能ユニットへのクロック信号をディスエーブルするが、集積回路の第1組の機能ユニットへのクロック信号はディスエーブルせず、集積回路が第2の電力供給停止モードであるときには、集積回路の第1組の機能ユニットと第2組の機能ユニットとの両方へのクロック信号をディスエーブルするが、アクセス信号がアサートされたことに応答して第1組の機能ユニットがキャッシュ・コヒーレンシ動作を実行することを可能にするように、アクセス信号がアサートされたことに応答して第1組の機能ユニットへのクロック信号を一時的にイネーブルするクロック・ディスエーブル手段と

20

を備えることを特徴とする電力低減論理。

**【発明の詳細な説明】**

**発明の分野**

本発明は、全般的にはコンピュータおよびコンピュータ・システムに関する。詳細には、本発明は、低電力状態で動作することのできる集積回路と、この集積回路が低電力状態で動作するときにキャッシュ・コヒーレンシを維持する方法とに関する。

**発明の背景**

プロセッサなどの集積回路（I C）内の電力消費量を低減する多数の技法の1つとして、プロセッサの一部または全体へのクロック信号を停止または遮断する技法がある。この方法では、「クロック停止」信号のアサートが必要とされることがあり、その場合、プロセッサは低電力消費量状態（すなわち、低電力状態）に入り、プロセッサの多数の機能ユニットはもはやクロックされなくなる。プロセッサに関連するキャッシュ・メモリによって与えられる性能上の利点を維持するには、プロセッサが低電力状態であるときでもキャッシュ・コヒーレンシを維持することが望ましい。

30

多くのコンピュータ・システムは複数のプロセッサを使用する。任意の一時点では、これらのプロセッサのうちの1つまたは多くが低電力状態であり、それに対して他のプロセッサは完全電力供給状態の間、引き続きデータに作用することができる。このようなコンピュータ・システムでキャッシュ・コヒーレンシを維持するには、低電力状態で動作するプロセッサは、他のプロセッサの活動の結果として得られるいくつかの信号を監視し、これらに応答しなければならない。他のプロセッサの活動の結果として得られるストップ要求に応答するのに必要なキャッシュ・コヒーレンシ・ストップ回路の電力供給では、多量の電力が消費され、したがって、プロセッサが低電力状態に入ったときはこの電力消費量を最小限に抑えることが望ましい。

40

**発明の概要**

本発明によれば、集積回路を低電力消費量状態で動作させる装置が提供される。この装置は、集積回路の外部の装置による、集積回路からアクセスできるメモリ資源への、メモリ・アクセスを示すアクセス信号を受け取るように結合された入力を含む。電力低減論理は、集積回路内の第1組の機能ユニットと第2組の機能ユニットの両方にクロック信号をゲートし、第1組の機能ユニットは、集積回路内でキャッシュ・コヒーレンシ動作を実行することが要求される。電力低減論理は、アクセス信号のアサートに応答してクロック信号

50

を第1組の機能ユニットに伝搬する。本発明の他の特徴は、添付の図面および以下の詳細な説明から明らかになろう。

#### 【図面の簡単な説明】

本発明は、一例として図示されており、添付の図面の図に限るものではない。

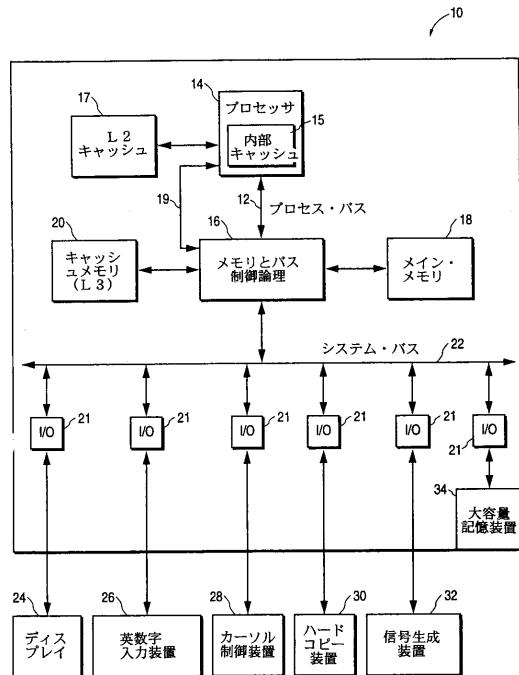

第1図は、本発明を実現することのできるコンピュータ・システムの概略図である。

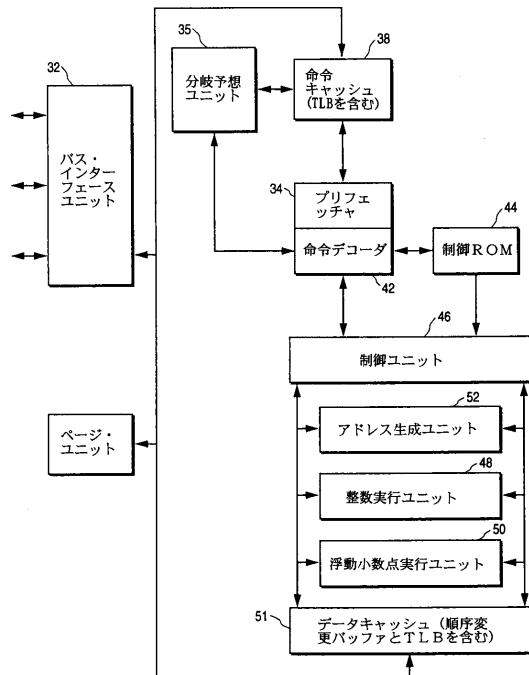

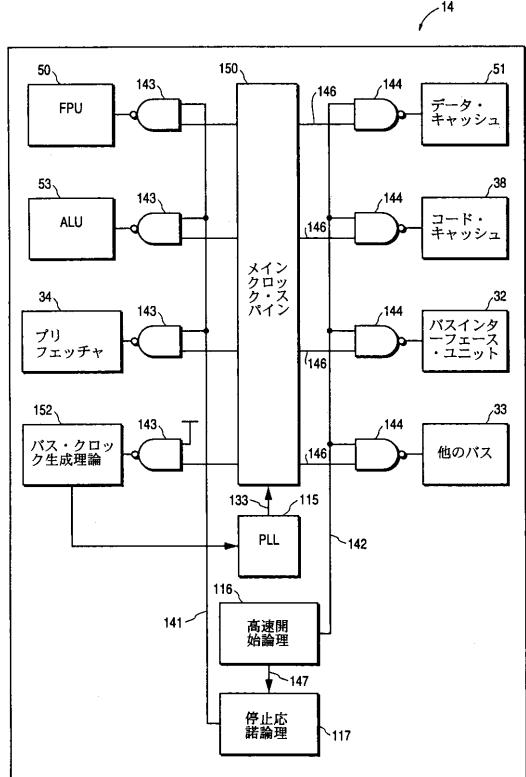

第2図は、本発明を実現することのできるプロセッサの概略図である。

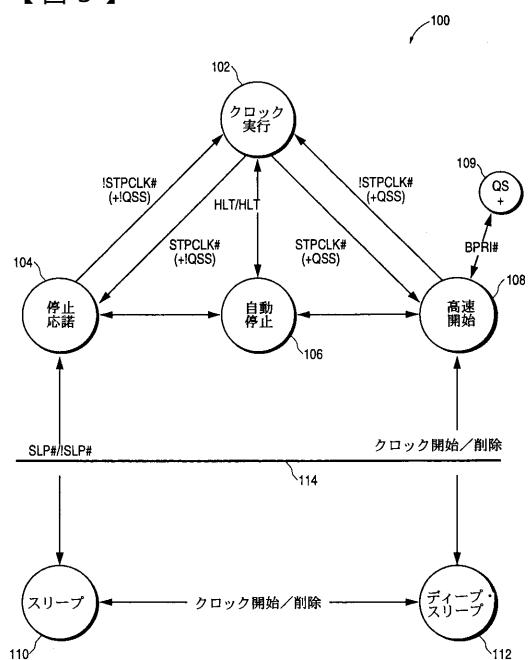

第3図は、本発明の一実施形態によって動作するプロセッサによって占有できる様々なクロック状態を示す状態図である。

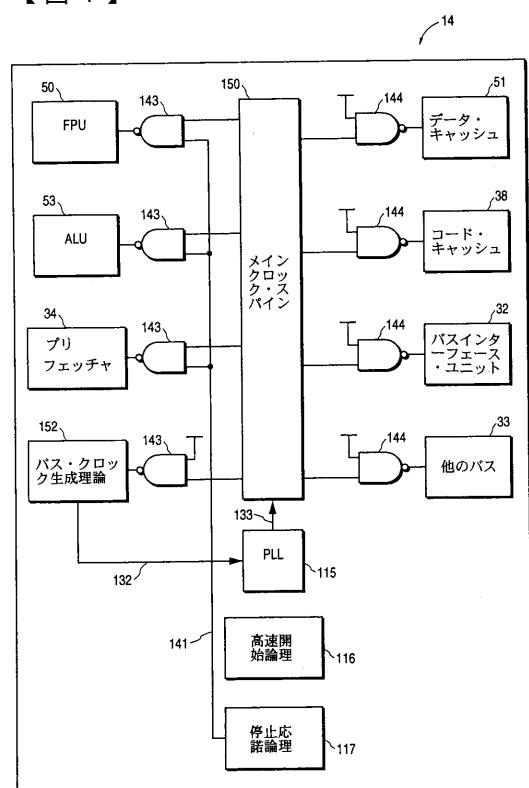

第4図は、本発明によって停止応諾モードで動作するように構成された第2図のプロセッサの概略図である。

10

第5図は、本発明による高速開始モードで動作するように構成された第2図のプロセッサを示す図である。

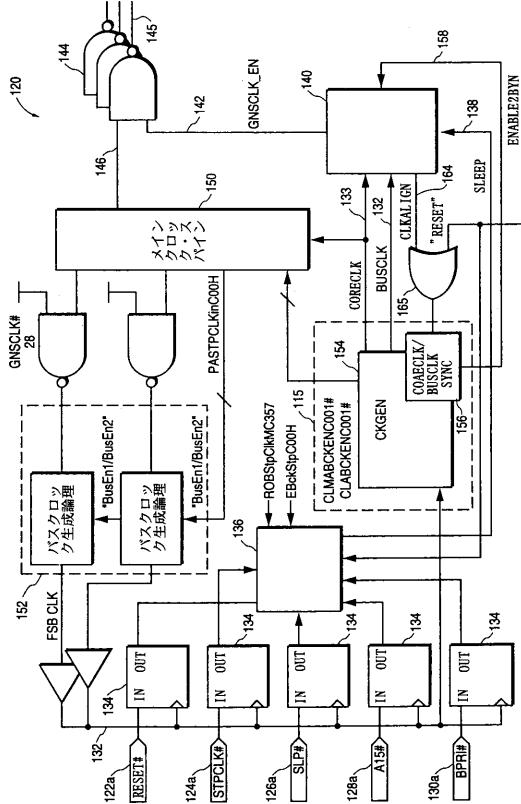

第6図は、本発明によって集積回路を低電力消費量状態で動作するクロック回路の概略図である。

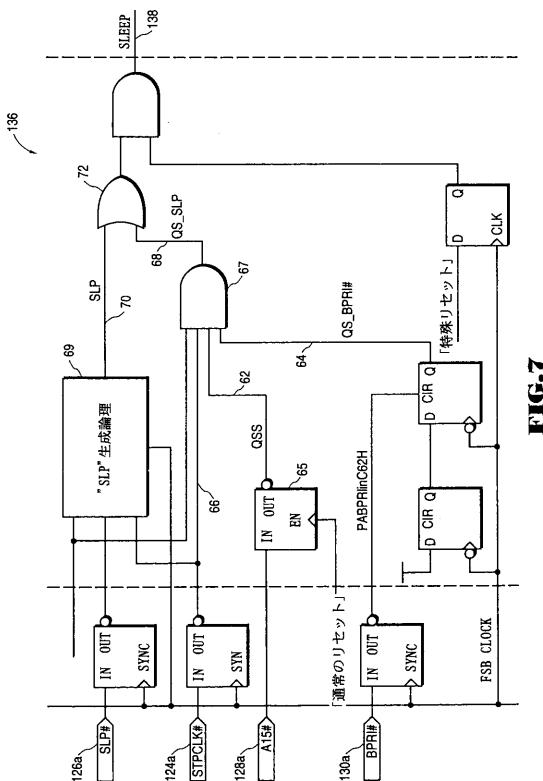

第7図は、第6図のクロック回路内に組み込まれる開始停止論理をさらに詳しく示す概略図である。

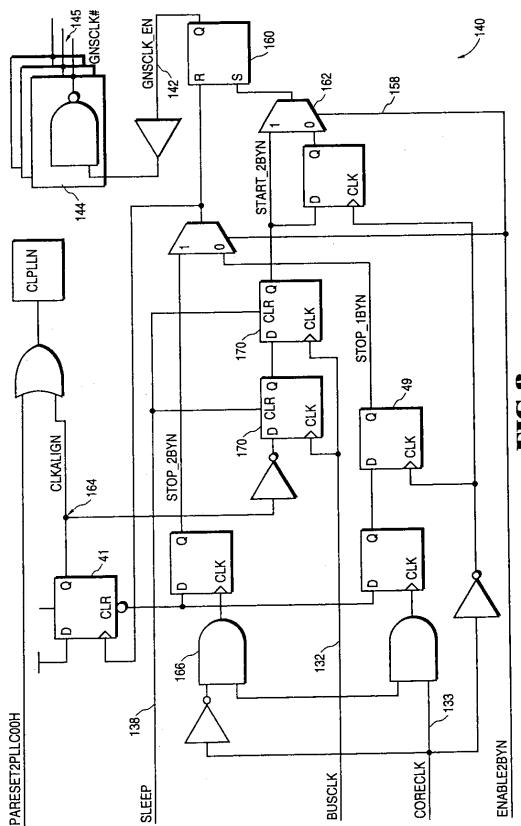

第8図は、第6図に示すクロック回路内に組み込まれるクロック・イネーブル／ディスエーブル論理の構造をさらに詳しく示す概略図である。

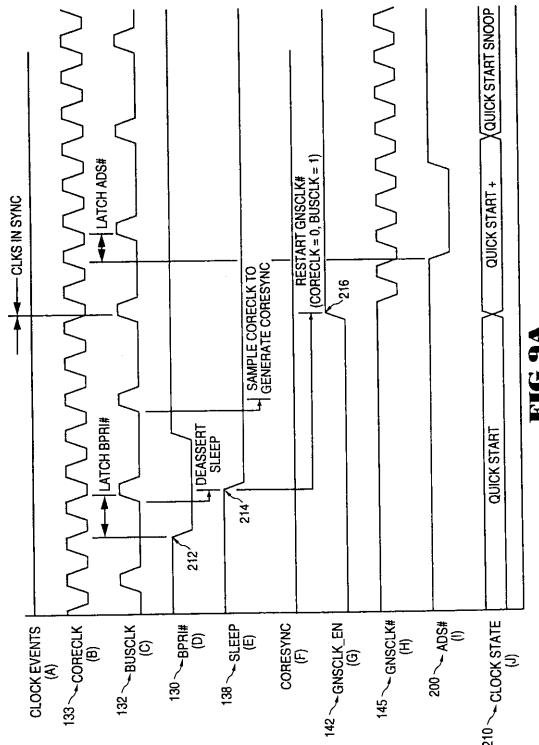

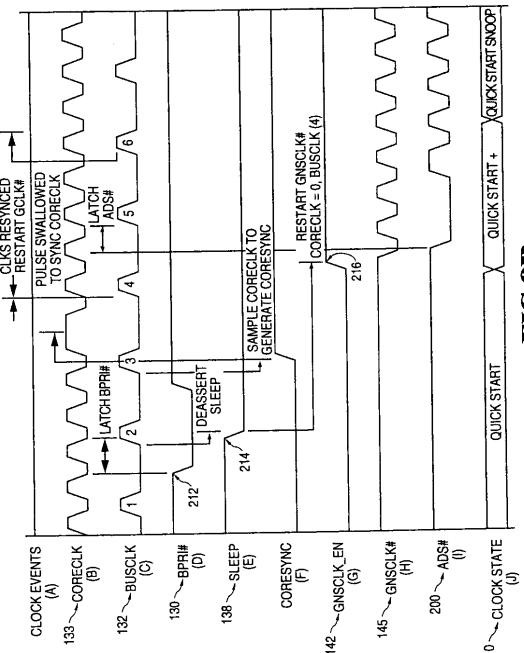

第9A図および第9B図は、第4図ないし第8図を参照して説明した様々な信号のタイミングを示すタイミング図である。

20

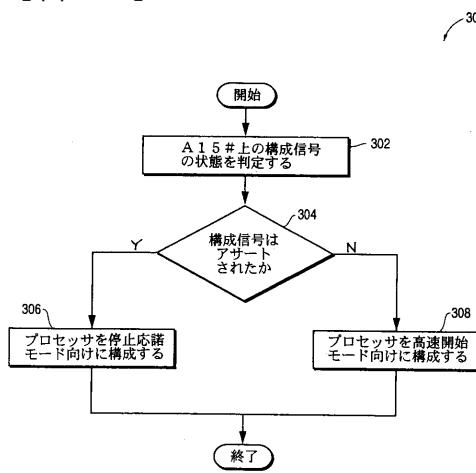

第10図は、低電力消費量状態のときにキャッシュ・コヒーレンシを維持するようにプロセッサを構成する、本発明による方法の一実施形態を示すフローチャートである。

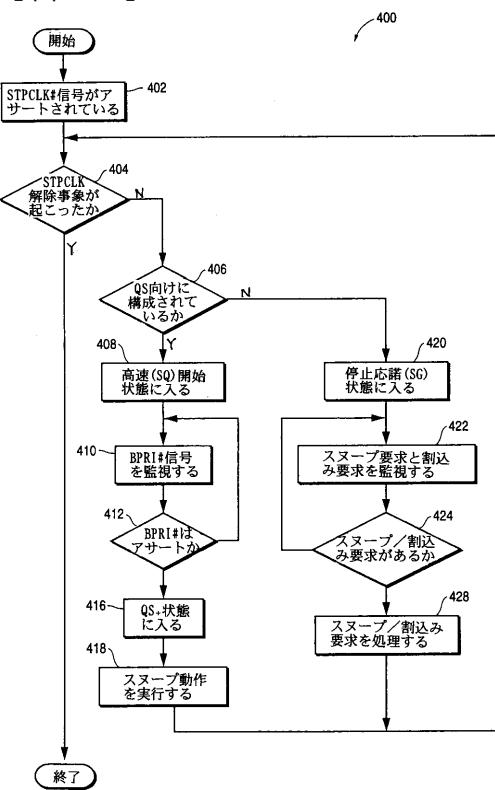

第11図は、プロセッサ内で低電力消費量状態に入る、本発明による方法を示すフローチャートである。

第12図は、集積回路を低電力消費量状態で動作する、本発明による方法を示すフローチャートである。

#### 詳細な説明

集積回路が低電力状態であるときにキャッシュ・コヒーレンシを維持する方法および装置について説明する。以下の説明では、説明の都合上、本発明を完全に理解していただくために多数の特定の詳細について述べる。しかし、当業者には、これらの特定の詳細なしに本発明を実施できることが明白であろう。

30

#### コンピュータ・システムおよびマイクロプロセッサの概要

第1図を参照すると、本発明の後述の実施形態のうちのどれかと共に使用できるコンピュータ・システム10がブロック図形で示されている。第1図はコンピュータ・システムを全体的に説明するうえで有用であるが、システムのいくつかの詳細が示されていないことが理解されよう。本発明の開示の必要に応じて、本明細書と共に提示した他の図を参照して他の詳細について述べる。さらに、本発明を例示的な実施形態を参照して説明する。当業者なら代替実施形態を構想することができ、このような代替実施形態は本発明の範囲内とみなされる。第1図に示すように、コンピュータ・システム10は、ユニプロセッサ・システムであり、プロセッサ・バス12によってメモリ・バス制御論理16（バス・ブリッジとも呼ばれる）に結合されたプロセッサ14を備える。プロセッサ・バス12に他のプロセッサを結合し、マルチプロセッサ・システムとすることができる。プロセッサ14は、内部データ命令キャッシュ15を含み、また、専用バスを介してレベル2（L2）キャッシュ17にアクセスできるプロセッサとして示されている。メモリ・バス論理16は、エージェント・バス要求19をプロセッサにアサートし、周辺装置のためにプロセッサ・バス12の制御を要求することもできる。たとえば、バス要求19は、カリフォルニア州サンタクララのIntel Corporationによって開発されたインテル・アーキテクチャ（IA）内に定義された優先エージェント・バス要求（BPRI#）信号でよい。プロセッサ14は、メモリ・バス制御論理16を介してメイン・メモリ18にアクセスすることができる。メイン・メモリ18は通常、ランダム・アクセス・メモリ（RAM）

40

M)を備え、プロセッサ14によって使用される命令および情報を記憶する。プロセッサ14は、論理16を介してレベル3(L3)キャッシュ・メモリ20にアクセスすることもできる。メモリ・バス制御論理16はシステム・バス22に結合され、入出力(I/O)ポート21によってシステム・バス22に結合されたいくつかの周辺装置は、このシステム・バス22を介して互いに通信すると共に、メモリ18および20ならびにプロセッサ14と通信する。周辺装置には、表示ユニット24(陰極線管(CRT)や液晶ディスプレイLCDなど)、英数字入力装置26(キーボードなど)、カーソル制御装置28(マウスや他のポインティング・デバイスなど)、ハード・コピー装置30(コンピュータ画像のハード・コピーを生成するプリンタやプロッタなど)、および信号生成装置32(拡声器など)が含まれる。コンピュータ・システム10は、システム・バス22に結合された大容量記憶装置34も含む。

10

次に第2図を参照すると、第1図のプロセッサ14のより詳細な図がブロック図形で示されている。プロセッサ14は、バス・インターフェース・ユニット32を含むいくつかの機能ユニット・ブロック(FUB)を備えている。バス・インターフェース・ユニット32は、プロセッサ14とコンピュータ・システム10のプロセッサ・バス12との間のインターフェースを実現する。バス・インターフェース・ユニット32には、いくつかの機能エンティティ、すなわち、書き込みバッファ、バス制御論理、L2キャッシュ制御、内部キャッシュ制御、ならびにアドレス・ドライバおよびアドレス受信機が含まれる。バス・インターフェース・ユニット32は、プリフェッチャ34が命令キャッシュ38を介してコンピュータ・システムのメイン・メモリ18にアクセスできるように結合される。プリフェッチャ34は、命令ポインタでインデックス付けされた命令を命令キャッシュ38から取り出すか、あるいはバス・インターフェース・ユニット32を介してメイン・メモリ18から取り出す。分岐予測ユニット35は、プリフェッチャ34によって検索された分岐命令をスペキュラティブに予測し、次いで、分岐が行われると予測されるか、あるいは行われないと予測されるかに応じて、順次メモリ・アドレスまたはターゲット・メモリ・アドレスを示す命令ポインタも出力する。プリフェッチャ34は、命令キャッシュ38またはメイン・メモリ18から受け取った命令を、下流処理用の1組のマイクロ命令(μops)に復号するように命令デコーダ42に伝搬する。制御読み取り専用メモリ(ROM)44は、命令デコーダ42に結合され、デコーダ42からエントリ・ポイントを受け取る。デコーダ42および制御ROM44は、制御ユニット46にマイクロ命令を供給する。制御ユニット46は、整数パイプライン実行ユニット48および浮動小数点パイプライン実行ユニット50にそれぞれ整数命令および浮動小数点命令を供給して実行させる。整数パイプライン実行ユニット48および浮動小数点パイプライン実行ユニット50は、命令を実行する際にデータ・キャッシュ51にアクセスすることができる。マイクロ命令は制御ユニット46からアドレス生成ユニット52にも供給され、アドレス生成ユニット52はアドレス情報を生成し変換する。

20

30

#### クロック状況

第3図を参照すると、本発明の一実施形態によるプロセッサの様々なクロック状態を示す状態図100が示されている。図のクロック状態は、ユニプロセッサ(UP)移動コンピュータ・システムと対称型マルチプロセッサ(SMP)デスクトップ・サーバ・コンピュータ・システムの両方でプロセッサの電力制御を容易にする。6つの異なるクロック状態、すなわち、クロック実行状態102、停止応諾状態104、自動停止状態106、高速開始状態108、スリープ状態110、およびディープ・スリープ状態112が図示されている。線114の上方に示されたクロック状態102ないし108では、キャッシュ・コヒーレンシのためにある程度のプロセッサ・バス・スヌーピングが推進され、それに対して、線114の下方の状態110および112では、プロセッサ・バスはスヌープされない。様々なクロック状態間の相違をさらに詳しく述べる。

40

プロセッサのクロック実行状態102は通常の動作モードであり、プロセッサの内部クロックが実行され、プロセッサは命令をアクティブに実行する。クロック停止(STPCLK#)信号がアサートされると、プロセッサは、プロセッサのブートアップ時またはリセ

50

ット時に「電源オン・ストラッピング・オプション」がどのように実行されたかに応じて、停止応諾状態 104 または高速開始状態 108 に入る。具体的には、プロセッサは、ストラッピング・オプション線上に論理 0 または論理 1 を配置することによって電源オン時に停止応諾状態 104 または高速開始状態 108 に入るように構成される。一実施形態では、このストラッピング・オプションは、リセット時にアドレス線 15 (A15#) 上に 0 または 1 をドライブすることによって実行することができる。もちろん、いくつかの他の方法のうちのどれでもストラッピング・オプションを実行できることが理解されよう。プロセッサが（たとえば、A15#を論理 1 に設定することによって）停止応諾状態 104 に入るよう電源オン時に構成されたものと仮定すると、プロセッサは、S T P C L K # 信号がアサートされたときに停止応諾状態 104 に入る。この状態では、プロセッサの多数の内部機能ユニット・ロック (FUB) がディスエーブルされるので、クロック実行状態 102 と比べて電力消費量が低減される。しかし、以下で詳しく説明するように、プロセッサがスヌープ要求に応答し割込みをラッチすることができるよう、停止応諾状態 104 のプロセッサ内の十分な回路がアクティブに維持されクロックされ続ける。このように、低電力状態のときでもキャッシュ・コヒーレンシが維持される。停止応諾状態 104 からクロック実行状態 102 への遷移は、S T P C L K # 信号がアサート解除されたときか、あるいはプロセッサ初期設定、フラッシュ、リセットなどの停止解除事象が起きたときに行われる。

プロセッサが（たとえば、A15#を論理 0 に設定することによって）高速開始状態 108 に入るよう電源オン時に構成されたものと仮定すると、プロセッサは、S T P C L K # 信号がアサートされたときに高速開始状態 108 に入る。この状態では、プロセッサの大多数の機能ユニット・ロック (FUB) がディスエーブルされるので、クロック実行状態 102 および停止応諾状態 104 と比べて電力消費量が低減される。ただし、プロセッサのフェーズ・ロック・ループ (PLL) は機能状態に維持される。この深い低電力状態は、高速開始状態 108 のときに、低下された応答機能をプロセッサに与えることによって実現される。一実施形態では、高速開始状態 108 のプロセッサは、ラッチング割込み（たとえば、NMI 信号や SMI # 信号や INT R 信号）に応答できず、また、リセット要求や初期設定要求やフラッシュ要求に応答しない。したがって、停止応諾状態 104 とは異なり、これらの要求に応答する回路には電力が供給されず、したがって、高速開始状態 108 では高度の電力節約を実現することができる。プロセッサが高速開始状態 108 であるときに割込み要求、初期設定、リセット要求、またはフラッシュ要求が生成された場合、これらの要求は、認識されず、したがって、S T P C L K # 信号がアサート解除され、プロセッサがクロック実行状態 102 に戻り、その時点でこのような要求が実行されるまで保持（またはラッチ）しなければならない。本発明の一実施形態では、高速開始状態 108 のプロセッサは、外部入出力 (I/O) 装置がプロセッサ・バスの制御を要求したときに、プロセッサ・バスをスヌープすることによってスヌープ要求に応答することしかできない。他のある実施形態では、高速開始状態のプロセッサ 108 は、インテル・アーキテクチャ (IA) によって定義された優先エージェント・バス要求 (BPRI#) 信号のアサートに依存する入出力ブリッジ・アクセスに応答することしかできない。第 1 図を参照するとわかるように、BPRI# 信号 19 は、入出力装置 21 による要求に応答してプロセッサ（または CPU）バス 12 の制御を得るためにメモリ・バス制御論理 16（バス・ブリッジとも呼ばれる）によってアサートされる。以下で詳しく説明するように、BPRI# 信号 19 がアサートされてから 3 クロック・サイクル後に、プロセッサは高速開始プラス (QS+) モード 109 に入る。このモードでは、スヌープ・サイクルを受け入れるのに必要なプロセッサの FUB が電力を供給されクロックされる。一実施形態では、高速開始プラス・モード 109 で動作するプロセッサのスヌーピング動作は、プロセッサが、BPRI# 信号 19 を用いて開始されたアクセス以外のアクセスについてはプロセッサ・バスをスヌープせず、したがって、プロセッサ・バス 12 に結合された、マルチプロセッサ環境で使用される他のプロセッサによって実行されるデータ演算についてはバス・スヌープを実行しないので、プロセッサがユニプロセッサ (UP) 構成のみで使用で 10 20 30 40 50

きるような動作である。

自動停止状態 106 は、停止( HLT )命令が実行されたときに入る状態であり、自動停止解除事象が起こったときにクロック実行状態 102 に戻る。インテル・アーキテクチャ仕様を満たすプロセッサでは、NMI 信号、INTR 信号、INT# 信号、FLUSH# 信号、又はSMI# 信号がアクティブになるか、あるいはプロープ・モード要求が出されたときに、自動停止解除事象が生じる。

本発明によるプロセッサは、スリープ状態 110 およびディープ・スリープ 112 状態でも動作することができる。スリープ状態 110 は、停止応諾状態 104 から入る状態であり、この遷移はスリープ(SLP#)信号がアサートされたときに行われる。スリープ状態 110 では、プロセッサは、そのコンテキストを維持し、すべての内部クロックを停止するが、フェーズ・ロック・ループ(PLL)回路をアクティブに保持し、したがって、プロセッサが最小待ち時間でスリープ状態 110 を終了することができる。すべての内部クロックが停止されるので、スリープ状態 110 のプロセッサはスヌーピングを行うことも、あるいは割込み信号をラッチすることもできず、スリープ状態 110 のプロセッサをリセットすることもできない。10

プロセッサの PLL 回路への電力供給を停止することによって、ディープ・スリープ状態 112 に入る。これは、プロセッサへの入力クロック周波数を停止することによって行われる。

#### クロック回路

第4図および第5図は、プロセッサ 14 の概略図であり、本発明の教示によって動作する様々な機能ユニット・ブロック(FUB)、クロック制御回路、および他の関連回路を示す。第4図は、停止応諾モード 104 で動作するように構成されたプロセッサ 14 を示し、それに対して、第5図は、高速開始モード 108 で動作するように構成されたプロセッサ 14 を示す。第4図および第5図に示すプロセッサ 14 は、いくつかの FUB、すなわち、浮動小数点ユニット(FPU) 50、演算論理装置(ALU) 53、プリフェッチャ 34、バス・クロック生成論理 152、データ・キャッシュ 51、コード・キャッシュ 38、およびバス・インターフェース・ユニット 32 を備える。プロセッサ 14 は他のいくつかの FUB を含み、これらの FUB はブロック 33 で表わされている。上記の FUB が例示的なものに過ぎず、FUB の網羅的なリスト形成するものでも、あるいは FUB の必要なリストを形成するものでもないことが理解されよう。プロセッサ 14 の右側に示す FUB(すなわち、FUB 51、38、32、および 33) は、内部スヌーピング動作および外部スヌーピング動作を実行するように動作する必要があることを特徴とする。それとは対称的に、プロセッサ 14 の左側にある FUB 50、53、34 はスヌープ動作中に動作する必要がない。2030

各 FUB は、NAND ゲート 143 または 144 を介してメイン・クロック・スペイン 150 からクロック信号を受け取るように結合される。さらに、バス・クロック生成論理 152 はフェーズ・ロック論理(PLL) 115 にフィードバック・バス・クロック信号 132 を供給し、フェーズ・ロック論理(PLL) 115 はクロック・スペイン 150 にコア・クロック・ロック信号 133 を供給する。プロセッサ 14 は、高速開始論理 116 および停止応諾論理 117 も含む。第4図を参照すると、プロセッサ 14 は停止応諾モード 104 で動作するように構成されるように示されている。停止応諾論理 117 は、クロック・スペイン 150 から FUB 50、53、および 34 へのクロック信号の供給をディスエーブルすることによって、これらの FUB への電力供給を選択的に停止することができる。具体的には、停止応諾論理 117 は、グローバル・クロック・イネーブル停止(GSCLK\_EN) 信号 141 をアサート解除し、かつアサートすることにより、クロック・スペイン 150 から FUB 50、53、および 34 へのクロック信号の供給をゲートまたは遮断するようにこれらの FUB に関連する NAND ゲート 143 を動作させることができる。したがって、プロセッサ 14 を停止応諾モード 104 にする場合、停止応諾論理 117 は GSCLK\_EN 信号 141 をアサート解除し、したがって FUB 50、53、および 34 で切換え活動が行われるのを妨げる。停止応諾モード 104 では、キャッシング4050

・コヒーレンシに必要なF U B 5 1、3 8、3 2、および3 3が、ディスエーブルされず、しかもクロック・スペイン1 5 0から供給されるクロック信号を用いてクロックされることに留意されたい。したがって、これらのF U Bは、内部スヌーピング動作と外部スヌーピング動作の両方を従来の方式で開始し、したがって、プロセッサ1 4が低電力の停止応諾モード1 0 4であるときでもキャッシュ・コヒーレンシを維持することができる。さらに、バス・クロック生成論理1 5 2へのクロック信号の供給がゲートされないことを留意されたい。したがって、フィードバック信号1 3 2は引き続きP L L 1 1 5に供給され、P L L 1 1 5はロック状態のままになる。

これは、ディープ・スリープ・モード1 1 2と対称的であり、このモードでは、P L L 1 1 5およびバス・クロック生成論理1 5 2への電力供給が停止され、したがって、クロック・スペイン1 5 0へのコア・クロック信号1 3 3の供給が終了する。回路1 5 2および1 1 5への電力供給が停止されることと、クロック・スペイン1 5 0がもはやクロック信号を搬送しないことに鑑みて、ディープ・スリープ・モード1 1 2でのプロセッサによる電力消費量は漏れによるものだけである。しかし、クロック・スペイン1 5 0上で信頼できるクロック信号を再び供給するには、P L L 1 1 5に電力を再び供給し、P L L 1 1 5をロックさせなければならず、そのため、最大で1 m sの長いアクセス待ち時間が生じる。

次に第5図を参照すると、高速開始モード1 0 8で動作するように構成されたプロセッサ1 4の一実施形態が示されている。具体的には、グローバル・クロック非停止(G N S C L K)信号1 4 6がF U B 5 1、3 8、3 2、および3 3に供給されるときに通過するN A N Dゲート1 4 4が、グローバル・イネーブル非停止(G N S C L K\_E N)信号1 4 2をアサートし、かつアサート解除することによって高速開始論理1 1 6によって選択的にイネーブルされ、かつディスエーブルされる。高速開始論理1 1 6はまた、信号1 4 7を停止応諾論理1 1 7に伝搬し、それによって、停止応諾論理1 1 7は信号1 4 1をアサート解除し、それによってF U B 5 0、5 3、および3 4へのクロック信号の供給をゲートする。したがって、高速開始モード1 0 8に入ると、高速開始モード論理自体がF U B 5 1、3 8、3 2、および3 3をディスエーブルし、信号を停止応諾論理1 1 7に伝搬し、それによって、論理1 1 7にF U B 5 0、5 3、および3 4をディスエーブルさせる。以下に詳しく説明するように、コンピュータ・システム内の周辺ユニットからのメモリ・アクセスを示す所定のアクセス信号(たとえば、B P R I #信号)がアサートされると、高速開始論理1 1 6は、G N S C L K\_E N信号1 4 2をアサートすることによってプロセッサ1 4を高速開始プラス・モード1 0 9にして、それによって、データ・キャッシュ5 1、コード・キャッシュ3 8、バス・インターフェース・ユニット3 2、およびその他のF U B 3 3へのクロック信号1 4 6の供給を再イネーブルする。しかし、停止応諾論理1 1 7への信号1 4 7は変更されず、したがって、F U B 5 0、5 3、および3 4は電力停止状態のままである。したがって、高速停止プラス・モード1 1 0 9では、キャッシュ・コヒーレンシに必要なF U B 5 1、3 8、3 2、および3 3は、動作可能であり、スヌープ要求に応答することができる。したがって、高速開始プラス・モード1 0 9で電力を投入されるのは、スヌープ要求に応答するのに必要なF U Bだけであり、それに対して、電力供給を停止されたままの回路はその状態のままである。スヌーピング動作が完了すると、高速開始論理1 1 6によって、プロセッサ1 4は再び高速開始モード1 0 8に入り、高速開始論理1 1 6は信号1 4 2をアサート解除する。

簡単に言えば、プロセッサ1 4は、停止応諾モード1 0 4で動作する際、第1組の信号(たとえば、スヌープ対話信号や初期設定信号やリセット信号など)に応答してキャッシュ・コヒーレンシ動作を実行することができ、それに対して、高速開始モード1 0 8では、プロセッサは、外部周辺装置によるメモリ・アクセス要求を示す信号(たとえば、B P R I #信号)にのみ応答する。プロセッサ1 4は、上記のモードのとき、関連する信号に応答し、たとえば、プロセッサ1 4に関連するキャッシュ・メモリ資源内のキャッシュ・ラインを無効化することによって、キャッシュ・コヒーレンシを維持する。

第6図は、クロック・スペイン1 5 0、バス・クロック生成論理1 5 2、P L L 1 1 5、

10

20

30

40

50

および高速開始論理 116 のより詳細な図である。具体的には、第 6 図は、ピン 122A を介してリセット (RESET) 信号 122 を受け取り、ピン 124A を介してクロック停止 (STPCLK#) 信号 124 を受け取り、ピン 126A を介してスリープ (SLP#) 信号 126 を受け取り、アドレス (A15#) ピン 128A を介して構成（またはストラッピング・オプション）信号 128 を受け取り、ピン 130A を介して優先エージェント・バス要求 (BPRI#) 信号 130 を受け取るように結合されたクロック制御回路 112 を示す。ピン 122A - 130A に加えられた各信号は、適切なラッチ 134 によるフロント・サイド・バス (FSB) クロック信号 132 に応答してラッチされ、スリープ / 開始状態論理 136 に供給される。スリープ / 開始状態論理 136 は第 5 図に詳しく示されている。スリープ / 開始状態論理 136 は、クロック・イネーブル / ディスエーブル論理 140 と共に、第 4 図および第 5 図に示す高速開始論理 116 を構成する。スリープ / 開始状態論理 136 は、ラッチ 134 から受け取った様々な入力に応答して、クロック・イネーブル / ディスエーブル論理 140 にスリープ信号 138 を出力する。クロック・イネーブル / ディスエーブル論理 140 は、スリープ信号 138 の状態に応答して、グローバル・クロック・イネーブル非停止 (GNSCLK\_EN) 信号 142 を生成し、この信号がNANDゲート 144 に伝搬される。NANDゲート 144 はそれぞれ、GNSCLK\_EN 信号 142 および GNSCLK 信号 146 を入力として受け取るように結合される。NANDゲート 144 の出力は、スヌープ動作中にキャッシュ・コヒーレンシを維持するのに必要なFUBに伝搬されるクロック信号 145 (GNSCLK) を含む。したがって、GNSCLK\_EN 信号 142 をアサートし、かつアサート解除することによって、プロセッサ 14 の FUB 51、38、32、33 へのクロック信号をそれぞれ、イネーブルし、かつディスエーブルすることができる。

クロック制御回路 120 は、メイン・クロック・スペイン 150、バス・クロック生成論理 152、および PLL 115 も含む。メイン・クロック・スペイン 150 は、プロセッサ内でコア・クロック信号を分散する責任を負い、それに対して、バス・クロック生成論理 152、コア・クロック生成論理 154、および PLL 115 はそれぞれ、クロック信号 132 および コア・クロック信号 133 を生成する責任を負う。コア・クロック信号 133 はバス・クロック信号 132 と同期し、バス・クロック信号 132 は、コア・クロック生成論理 154 にフィードバックされ、バス・クロック信号 132 の全倍数（たとえば、2 倍や 3 倍）でも、あるいはバス・クロック信号 132 の半倍数（たとえば、2.5 倍や 3.5 倍）でもよい。

コア・クロック生成論理 154 は、これらの組合せ信号の間の同期を維持するコア・クロック / バス・クロック同期回路 156 も含む。回路 156 は、バス・クロック・マルチプライヤが整数であるかどうかを示す ENABLE2BYN 信号 158 をクロック・イネーブル / ディスエーブル論理 140 に出力する。クロック・イネーブル / ディスエーブル論理 140 は、OR ゲート 165 を介して同期回路 156 にクロック整列 (CLKALIGN) 信号 164 を供給する。クロック・イネーブル / ディスエーブル論理 160 は、ENABLE2BYN 信号 158 の状態に応じて、適当な時間に CLKALIGN 信号 164 をアサートする。リセット時、または CLKALIGN 信号 164 のアサート時に、コア・クロック生成回路 154 は、バス・クロックとコア・クロックとの間の立下り同期を生成するようにコア・クロック信号 133 (CORECLK) の位相を強制的にシフトさせる。コア・クロック生成論理 154 は、バス・クロック信号 132 をフィードバックとして受け取るように結合される。同期回路 156 は、バス・クロック信号 132 の位相をコア・クロック信号 133 と比較することによって、ENABLE2BYN 信号 158 をクロック・イネーブル / ディスエーブル論理 140 へのフィードバックとして供給する。

次に入力信号に戻るかのように、RESET# 信号 122 はピン 122A を介してスリープ / 開始状態論理 136 に伝搬され、それによってクロック制御回路 120 がリセットされ、それに対して、SLP# 信号 126 がアサートされると、クロック制御回路 120 は、スリープ信号 138 をアサートすることによってプロセッサをスリープ状態 110 にする。RESET# 信号および SLP# 信号の詳細は、本発明の理解とは無関係である

。

電力投入（「リセット」または「ポートアップ」とも呼ぶ）時に A15 # ピン 128A に加えられる構成信号 128 は、ピン 126A 上で STPCLK # 信号がアサートされたときにスリープ / 開始状態論理 136 がプロセッサを停止応諾状態 104 にするか、それとも高速開始状態 108 にするかを決定する。具体的には、電力投入時にピン 128A に論理 1 が加えられた場合、スリープ / 開始状態論理 136 は、STPCLK # 信号 124 がアサートされたときにプロセッサを停止応諾状態 104 にするように構成され、それに対して、電力投入時にピン 128A に論理 0 が加えられた場合、スリープ / 開始状態論理 136 は、STPCLK # 信号 124 がアサートされたときにプロセッサを停止応諾状態 104 にするように構成される。

10

停止応諾状態 104 のとき、スヌープ要求に応答するのに必要なプロセッサの FUB は、アクティブであり、かつクロックされ、したがって、必要に応じてキャッシュ・コヒーレンシ動作を実行することができる。

高速停止状態 108 のとき、スリープ / 開始状態論理 136 は、BPRI # 信号 130 がアサートされたかどうかについてピン 130A を監視する。BPRI # 信号がアサートされたことに応答して、スリープ / 開始状態論理 136 は、プロセッサがプロセッサ・バス 12 のスヌープを実行できるようにスリープ信号 138 をアサート解除する。

第 7 図を参照すると、スリープ / 開始状態論理 136 のより詳細な図が示されている。論理 136 はスリープ生成論理 69 を備え、スリープ生成論理 69 は、SLP # 信号 126 または STPCLK # 信号 124 のアサートに応答して SLP 信号 70 を出力する。重要なこととして、高速開始モード 108 はラッチ 65 であり、コンピュータ・システムのポートアップ時にアドレス・ピン 128A に加えられた構成信号 128 をラッチする。ポートアップ時にピン 128A に論理ゼロが加えられた場合、ラッチ 65 は、4 入力 AND ゲート 67 に論理 1QSS 信号 62 を出力するように構成される。AND ゲート 67 はまた、STPCLK # 信号 124 の逆数および BPRI # 信号 130 の逆数を受け取るよう結合される。したがって、STPCLK # 信号 124 がアサートされ、QSS 信号 62 が（ラッチ 65 を構成した構成信号 128 によって）ハイになると、BPRI # 信号 130 がアサートされることによって、AND ゲート 67 の出力がハイになり、したがって、OR ゲート 72 を介してスリープ信号 138 がアサートされる。前述のように、スリープ信号 138 がアサートされると、クロック・イネーブル / ディスエーブル論理 140 は、必要に応じて GNSCLK\_EN 信号 142 をアサートする。

20

第 8 図は、クロック・イネーブル / ディスエーブル論理 140 の一実施形態の詳細を示す。クロック・イネーブル / ディスエーブル論理 140 の一次機能は、GNSCLK\_EN 信号 142 が所望のタイミングでアサートまたはアサート解除されることである。論理 140 はスリープ信号 138 を受け取るように結合され、スリープ信号 138 はクロック実行状態 102 の間アサート解除される（ロー状態）。クロック整列（CLKALIGN）信号 164 は同様に、クロック実行状態 102 でアサート解除される。GNSCLK\_EN 信号 142 は、R/S ラッチ 160 の SET 入力を介してアサートされ、R/S ラッチ 160 の RESET 入力がアサート解除される。ENABLE2BYN 信号 158 は、2/N（非整数）動作モードまたは 1/N（整数）動作モードでバス・クロックとコア・クロックが整列したときにクロック停止 / 再開事象を駆動する 2 つの経路のうちの一方を選択するようにマルチブレクサ 162 を動作する。グリッキングまたは最小パルス幅未満のパルス幅を回避するために、NAND ゲート 144 から伝搬された GNSCLK # 信号 145 は、コア・クロック（CORECLK）信号がローになったときは常に（NAND ゲート 144 への GNSCLK\_EN 信号 142 をアサート解除またはアサートすることによって）停止または再開される。この要件を満たすために、2/N モードでは、位置ずれした境界上で GNSCLK\_EN 信号 142 がアサートまたはアサート解除され、したがって、コア・クロック（CORECLK）信号 133 はロー状態になる。2/N モードのとき、CORECLK のクロック・パルスの幅が「狭く」なり、コア・クロック（CORECLK）とバス・クロック（BUSCLK）との間のクロック整列が可能に

40

50

なる。1/Nモードでは、バス・クロック(BUSCLK)信号とコア・クロック(CORECLK)信号が常に整列し、したがって、GNSCLK#の停止または再開は、整列した境界の直後のCORECLKのロー・フェーズまで遅延される。したがって、1/Nモードで動作しているとき、R/Sラッチ160は、スリープ信号138がアサート解除されてから1プロセッサ・クロック・サイクル後にANDゲート166を介してリセットされ、次いでスリープ信号がアサート解除されてから2プロセッサ・サイクル後にDフリップフロップ170によってセットされる。

#### タイミング図

第9A図および第9B図は、上記で第4図ないし第8図を参照して説明した様々な信号を示すタイミング図である。第9A図は、CORECLK信号133、BUSCLK信号132、BPRI#信号130、SLEEP信号138、GNCLK\_EN信号142、GNSCLK#信号145、アドレス状況(ADSS)#信号200の、非整数(2/N)モードでの相対タイミングを示す。クロック状態も、210で示されている。第9B図は、整数(1/N)モードでの同じ信号の相対タイミングを示す。各タイミング図は高速開始状態108のプロセッサで始まり、この状態ではGNSCLK#信号145がディスエーブルされる。高速開始状態108では、スリープ/開始状態論理136は引き続き、前述のようにBPRI#信号130がアサートされたかどうかを監視する。スリープ/開始状態論理136が点212でBPRI#信号130がアサートされたことが検出すると、スリープ信号138は、点214に示すように、BUSCLK信号132の次の立上りでアサート解除される。スリープ信号138がアサート解除されたことに応答して、クロック・イネーブル論理140は、点216で示し上記で説明したように、クロック回路が2/Nモードで動作しているか、それとも1/Nモードで動作しているかに依存し、かつそれによって決定される遅延の後にGNCLK\_EN信号142をアサートする。GNCLK\_EN信号142は、CORECLK信号133がローになったときにアサート解除される。GNCLK\_EN信号142がアサートされたことに応答して、NANDゲート144は、スヌープ要求を処理するのに必要なFUBにGNSCLK145を出力し、プロセッサは「高速開始プラス」モード109に入る。

具体的に、メモリ・アクセスの(ADS#信号200がアサートされたときに有効になる)アドレスをスヌープすることを可能にする時間にGNCLK信号145が再開される。次いで、プロセッサは「高速開始スヌープ」状態に入り、スヌープ要求が処理される。

#### フローチャート

第10図は、低電力状態のときにキャッシュ・コヒーレンシを維持するようにプロセッサを構成する、本発明による方法300の一実施形態を示すフローチャートである。電力投入時に、ステップ302で、プロセッサのA15#ピン128Aに加えられた構成(またはストラッピング)信号128の状態に関する判定が下される。方法300は、構成信号128の状態を判定した後、判定ボックス304に進み、構成信号が論理1である場合にはステップ306に進み、構成信号が論理0である場合にはステップ308に進む。ステップ306で、プロセッサは、STPCLK#信号124がアサートされている場合に高速開始状態108に入り、したがって、キャッシュ・コヒーレンシを維持することだけを目的として第1組の信号に応答するように構成される。一実施形態では、第1組の信号はBPRI#信号130を含む。別法として、ステップ308で、プロセッサは、STPCLK#信号124がアサートされたときに停止応諾状態104に入り、したがって、第2組の信号に応答するように構成される。一実施形態では、第2組の信号にADS#信号が含まれる。

第11図は、プロセッサ内で低電力モードに入る方法400を示すフローチャートである。方法400はステップ402から始まり、STPCLK#信号がアサートされる。方法400は判定ボックス404に進み、後続のSTPCLK解除事象が起こったかどうかを検出する。そうである場合、方法400は終了する。そうでない場合、方法400は判定ボックス406に進み、プロセッサが高速開始状態108に入るように構成されているかどうかが判定される。これは、プロセッサに電力が投入されたときにA15#ピン128

10

20

30

40

50

Aに構成信号128が加えられたかどうかに依存する。プロセッサが高速開始モード108に入るように構成されている場合、ステップ408でこのモードに入り、その後、ステップ410でBPRI#信号130が監視される。判定ポックス412で、BPRI#信号130がアサートされているかどうかが判定される。そうでない場合、再びステップ410に進み、方法400は、BPRI#信号130がアサートされるか、あるいはSTPCLK解除事象が起こるまで、引き続きステップ410ないしステップ412を循環する。BPRI#信号130がアサートされている場合、プロセッサは、ステップ416で高速開始+状態に入り、その後、ステップ418でプロセッサ・バスのスヌープ動作が実行される。その後、方法400は判定ブロック404に戻る。

別法として、判定ブロック406で、プロセッサが高速開始状態108に入るように構成されていないと判定された場合、プロセッサは、ステップ420で停止応諾状態104に入る。その後、プロセッサは、ステップ422でスヌープ要求または割込み要求があるかどうかを監視する。このような要求が検出された場合、再びステップ422に進み、方法400は、スヌープ要求または割込み要求を受け取るか、あるいはSTPCLK解除事象が起こるまで、ステップ422ないしステップ424を循環し続ける。割込み要求のスヌープが行われると、この要求がステップ428で処理され、その後、方法400は判定ポックス404に戻る。

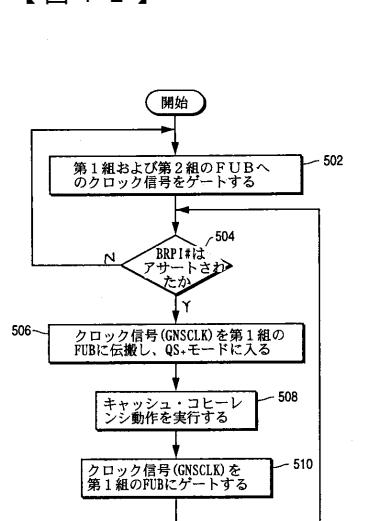

第12図は、集積回路が低電力消費量状態で動作する、本発明による方法500を示すフロー チャートである。具体的には、方法500は、高速開始モード108で動作するプロセッサ14の動作を示す。プロセッサは、高速開始モードに入り、次いでステップ502に進み、クロック信号、すなわちGNSCLKクロックおよびGSQLKクロックがゲートされ、したがって第1組のFUBおよび第2組のFUBに伝搬するのが妨げられる。

第1組のFUBと第2組のFUBは、第1組のFUBがプロセッサ内でキャッシュ・コヒーレンシ動作を実行する必要があり（たとえば、データ・キャッシュ51や、コード・キャッシュ38や、バス・インターフェース・ユニット32）、それに対して第2組のFUBが命令処理機能を実行する（たとえば、浮動小数点実行ユニット50や、整数実行ユニット48や、プリフェッチャ34）という点で区別される。したがって、第1組のFUB内でも、あるいは第2組のFUB内でも切換え事象は起こらない。次いで、方法は判定ブロック504に進み、集積回路の外部の装置によるメモリ・アクセスを示す信号が検出されたかどうかを判定する。一実施形態では、このような信号は、インテル・アーキテクチャによって定義されたBPRI#信号を含む。この信号がアサートされていない場合、方法500はステップ502に戻る。一方、この信号が実際にアサートされる場合、方法は、ステップ506に進み、GNSCLKクロック信号が再びイネーブルされ、第1組のFUBに伝搬され、したがって、第1組のFUBが再び動作可能になる。ステップ508で、第1組のFUBは、外部装置によるメモリ・アクセスに応答してキャッシュ・コヒーレンシ動作を実行し、その後ステップ510で、GNSCLKクロック信号が再び第1組のFUBにゲートされ、したがって、第1組のFUBは低電力消費量状態に戻る。次いで、方法は判定ポックス504に戻る。

したがって、集積回路が低電力状態であるときにキャッシュ・コヒーレンシを維持する方法および装置について説明した。特定の例示的な実施形態を参照して本発明を説明したが、本発明の広義の趣旨および範囲から逸脱せずにこれらの実施形態に様々な修正および変更を加えられることは明白であろう。したがって、明細書および図面は、制限的なものではなく例示的なものとみなすべきである。

【図1】

【図2】

FIG.2

FIG.1

【図3】

FIG.3

【図4】

FIG.4

【図5】

FIG.5

【図6】

FIG.6

【図7】

FIG.7

【図8】

FIG.8

【図 9 A】

FIG.9A

【図 9 B】

FIG.9B

【図 10】

FIG.10

【図 11】

FIG.11

【図12】

FIG.12

---

フロントページの続き

(74)代理人

弁理士 山川 茂樹

(72)発明者 カーダッチ , ジェイムス・ピイ

アメリカ合衆国・95070・カリフォルニア州・サラトガ・ラ パロマ アベニュー・20271

(72)発明者 ホリガン , ジョン

アメリカ合衆国・94041・カリフォルニア州・マウンテン ビュー・ビラ ストリート・12

09

(72)発明者 エカムバラム , ラベル

アメリカ合衆国・95131・カリフォルニア州・サン ホゼ・エイプリル ソング コート・1

758

(72)発明者 ナカニシ , トオサク

アメリカ合衆国・97124・オレゴン州・ヒルズ ボロ・183番・ノースイースト タンデム

ウェイ・23

(72)発明者 チヤン , チン - ハン

アメリカ合衆国・95051・カリフォルニア州・サンタ クララ・ウィックカム プレイス・25

34

(72)発明者 セニク , ポリス・エス

アメリカ合衆国・95117・カリフォルニア州・サン ホゼ・ポーク レーン・1020

審査官 清木 泰

(56)参考文献 特開平10-301659(JP,A)

特開平09-097128(JP,A)

特開平08-297607(JP,A)

特開平05-233275(JP,A)

特開平04-143819(JP,A)

米国特許第5530932(US,A)

(58)調査した分野(Int.Cl. , DB名)

G06F 12/08 - 12/12

G06F 1/26 - 1/32

G06F 1/04 - 1/14