(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-282405

(P2010-282405A)

(43) 公開日 平成22年12月16日(2010.12.16)

(51) Int.Cl.

G06F 13/362 (2006.01)

F 1

G 06 F 13/362 5 1 O B

テーマコード(参考)

5 B 0 6 1

審査請求 未請求 請求項の数 3 O L (全 21 頁)

(21) 出願番号

特願2009-134981 (P2009-134981)

(22) 出願日

平成21年6月4日 (2009.6.4)

(71) 出願人 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100109162

弁理士 酒井 将行

(74) 代理人 100111246

弁理士 荒川 伸夫

最終頁に続く

(54) 【発明の名称】データ処理システム

## (57) 【要約】

【課題】固定優先順位バスアクセス調停方式を用いる階層バス構造において、システム動作に応じて優先順位が更新される場合においても、バスアクセス要求の調停を正確に実行する。

【解決手段】複数の上位階層バス回路(6A, 6B)各々において、対応のバスマスター群(2A, 2B)に含まれるバスマスターのアクセス要求を優先順位に従って調停し、アクセス要求が許可された選択バスマスターの優先順位情報を示す優先順位伝達信号(PRA, PRB)を下位階層のバスコントローラ(10)へ転送する。下位階層バス回路(9)において、下位バスコントローラが、転送された優先順位伝達信号(PRA, PRB)に従ってアクセス要求の調停を実行して、優先順位の高い上位階層バス回路またはバスマスターを選択する。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

各々が優先順位が与えられるとともに予め割当てられた処理を実行する1以上のバスマスターを各々が含む複数のバスマスター群、

各バスマスター群に対応して配置され、各々が対応のバスマスター群からの情報を転送する複数の第1のバス、

各前記第1バスに対応して配置され、各々が対応のバスマスター群からのアクセス要求を優先順位に基いて調停するとともにアクセスが許可されたバスマスターの優先順位を示す優先順位信号を伝達する複数の第1バスコントローラ、

前記複数の第1バスに共通に配置される第2のバス、

前記複数の第1のバスに共通にかつ前記第2のバスに対応して配置され、各前記第1のバスからのアクセス要求を、伝達された優先レベル信号に基いて調停するとともに、アクセスが許可されたバスマスターの優先順位を示す優先順位信号を前記第2バスの下位階層に転送するとともに前記アクセス許可されたバスマスターからの転送情報を前記第2のバスを介して下位階層へ転送する第2バスコントローラを備える、データ処理システム。

## 【請求項 2】

前記データ処理システムは、各前記第1バスに対応して配置され、各々が対応の第1バスと前記第2バスとの間の通信を調整する複数のバスブリッジをさらに備え、

各前記バスブリッジは、対応の第1バスコントローラから転送された優先順位伝達信号を対応のバスマスターからの転送情報とともに順次格納して出力するキューバッファを備える、請求項1記載のデータ処理システム。

## 【請求項 3】

前記キューバッファは、複数段のキューバッファレジスタを含み、

各前記バスブリッジは、さらに、

各前記のキューバッファレジスタの格納する優先順位伝達信号および対応の第1バスコントローラから転送される優先順位伝達信号とを受け、最も高い優先順位を示す優先順位伝達信号を選択して前記第2バスコントローラへ転送する最優先セレクタを備え、

前記キューバッファは、ファーストイン・ファーストアウト様で格納されたバスマスターからの転送情報を順次第2バスに転送する、請求項2記載のデータ処理システム。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

この発明は、情報(データ)を処理するデータ処理システムに関し、特に、上位バスおよび下位バスの階層化されたバス構造を有するデータ処理システムの処理の効率化を実現するためのバスのアクセス制御に関する。

## 【背景技術】

## 【0002】

携帯端末機器および車載情報機器などにおいては、音声信号および画像信号などの情報を処理することが要求される。複数種類の情報を統合的に処理するために、マルチメディア用システムLSI(大規模集積回路装置)が用いられる。このマルチメディア用システムLSIは、画像圧縮、画像処理、画像表示および音声処理などの多くのモジュールを含む。これらのモジュールにおいて処理に必要とされるデータは、たとえばクロック同期型ダイナミック・ランダム・アクセス・メモリ(SDRAM)に格納されるのが一般的である。SDRAMへアクセスを行なうモジュールとSDRAMとは、内部バスおよびSDRAMコントローラを介して結合される。

## 【0003】

複数のモジュールがバスを介してSDRAMに並行してアクセス要求を発行した場合、これらのアクセス競合を調停するために、バスコントローラが設けられる。このバスアクセス要求の調停方式には、固定優先方式およびラウンドロビン方式等種々の方式がある。固定優先方式においては、各モジュールに予め優先順位が割当てられており、優先順位の

10

20

30

40

50

高いモジュールにバスアクセス権を与える。ラウンドロビン方式においては、モジュールに対するバスアクセス権の優先順位が、順次更新され、一度バスアクセスを実行したモジュールに対し低いバスアクセス優先順位が割当てられる。

#### 【0004】

しかしながら、このようなバスアクセス権調停方式においては、ある優先順位の低いモジュールが、長期にわたってバスアクセスを行なうことができず、処理が中断され、処理効率が低下する可能性がある。

#### 【0005】

このようなモジュールの待ち時間を調整することを図る構成が、特許文献1（特開2008-203989号公報）および特許文献2（特開2003-167842号公報）に示されている。特許文献1においては、バスアクセス要求を発行するバスマスターとバスマスターによりアクセスが要求されるバススレーブとを有するシステム構成において、バスマスターのバス使用要求待ち時間に応じてバス使用要求を選択する。各バスマスターの待ち合わせ時間に応じてバスアクセス権を与えることにより、各バスマスターの待ち合わせ時間を平均化することを図る。

10

#### 【0006】

特許文献2に示される構成においては、第1および第2のバスの間にバスブリッジを設ける。第1および第2のバスには、それぞれ、複数のエージェントが接続される。バスブリッジ内において各エージェントのトランザクションの処理回数をモニタし、トランザクション回数に応じてバス使用要求を発行するエージェントの優先順位を変更する。処理回数の多いエージェントの優先順位を低下させることにより、優先順位の低いエージェントの待ち時間を低減することを図る。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

【特許文献1】特開2008-203989号公報

【特許文献2】特開2003-167842号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

マルチメディア用システムLSIにおいては、階層バス構造が用いられる。この階層バス構造においては、バスが上位階層バスおよび下位階層バスに分割される。上位階層バスが複数設けられ、各上位階層バスに1つの処理に関連するモジュールを並列に接続する。たとえば、第1の上位階層バスには、画像処理に関連するモジュールを接続し、画像表示に関連するモジュールを別の第2の上位階層バスに接続する。これらの第1および第2の上位階層バスが、下位階層バスに結合される。上位階層バスを分割することにより、各上位階層バスの負荷容量を低減するとともに、モジュールとバスの間の配線錯綜を回避する。

30

#### 【0009】

いま、バスアクセス調停が固定優先方式に従って行なわれるデータ処理システムを想定する。また、以下の説明において、アクセス要求を発行するモジュールを、「バスマスター」と称し、このバスマスターによりアクセスされるモジュールを、「バススレーブ」と称す。この固定優先方式においては、各バスマスターに対しては、固定的に優先順位が与えられる。この優先順位は、以下のようにして定められる。すなわち、マルチメディア用システムLSIにおいては、SDRAMを含むバスシステムは、いくつかのバスマスターに対してリアルタイム応答をすることが要求される。ここで、「リアルタイム応答」は、バスマスターがバスアクセス要求を発行してからデータ転送が完了するまでの処理が、必ず、システムで決まる制限時間内で行なわれることを意味する。

40

#### 【0010】

このリアルタイム応答が必要なバスマスターに対しては、その制限時間が短い順に高い優

50

先順位を与える。固定優先調停方式を用いる階層バス構造においては、従来、データ転送制限時間に基づいてバスマスターをグループ化し、各上位階層バスに接続する。この場合、各バスマスター群においてバスマスターに対して固定優先順位が与えられており、異なるバスマスター群においては、同じ優先順位が割当てられるバスマスターが存在する。したがって、各上位階層バスに対しても、下位階層バスに対する優先順位が割当てられる。バスの優先順位およびバスマスター群内の優先順位により、各バスマスターに対する優先順位が固定的に設定される。

【0011】

異なる上位階層バスから同じ優先順位のバスマスターのアクセス要求が下位階層バスに発行されても、下位階層バスにおいては、優先順位の高い上位階層バスからのアクセス要求を受付ける。

【0012】

しかしながら、マルチメディアシステムにおいては、バスマスターが有するデータ転送の制限時間は、システムの処理モードに応じて異なる場合がある。たとえば、画像表示において表示モードが変更される場合、画像データを SDRAMへの転送速度を速くする必要が生じる場合がある。この場合、対応のバスマスターのデータ転送制限時間が、短くされる。

【0013】

いま、第1の上位階層バスおよび第2の上位階層バスが設けられ、下位階層バス回路またはバススレーブに対する第1の上位階層バスの優先順位が、第2の上位階層バスよりも高い階層バス構造を考える。また、第1の上位階層バスに含まれるバスマスターの転送制限時間よりも、第2の上位階層バスに接続されるバスマスターの転送制限時間が短くされる状態を考える。この場合、第1および第2の上位階層バスは、下位階層バスに対してそれぞれ固定的に優先順位が割当てられている。これらの第1および第2の上位階層バスから同時に下位階層バスに対してアクセス要求を発行した場合、優先順位の高い第1の上位階層バスからのアクセス要求が許可される。

【0014】

第2の上位階層バスのバスマスターのほうがデータ転送制限時間が短く、実質的には第1の上位階層バスからのアクセス要求を発行するバスマスターよりも優先順位を高くする必要がある。しかしながら、従来の固定優先調停方式においては、データ転送制限時間の長い第1の上位階層バスのバスマスターが選択されることとなる。この結果、固定優先方式におけるデータ転送制限時間の短いバスマスターのアクセスを優先するという原則を維持することができず、データ処理を効率的に行なうことことができなくなるという問題が生じる。

【0015】

また、階層バス構造を有するデータ処理システムにおいては、固定優先方式に従ってバスアクセスを調停する構成でない場合においても、バスマスターの実効的優先順位が変更される場合、同様に、上位階層バスの下位階層バスに対するアクセスの調停の問題が生じる。

【0016】

前述の特許文献1および特許文献2においては、1つの上位階層バスに接続されるバスマスターまたはエージェントの間で、待ち時間またはトランザクション処理回数に応じて優先順位を変更して、バスアクセス権利を割当てている。しかしながら、複数の上位階層バスが下位階層バスに対して並列に配置される階層バス構造における下位階層バスに対する上位階層バス間のアクセス調停の構成については何ら考察していない。

【0017】

それゆえ、この発明の目的は、複数の上位階層バスが下位階層バスに対して設けられる階層バス構造において、確実に、バスマスターの実効的優先順位が変更される場合においても、優先順位の決定原則を維持してバスアクセスの調停を行なうことのできるデータ処理システムを提供することである。

【0018】

10

20

30

40

50

この発明の他の目的は、固定優先調停方式の階層バス構造において、システムのモードに応じてデータ転送制限時間が変更されるバスマスターが存在する場合でも、正確にバスアクセス権の調停を行なうことのできるデータ処理システムを提供することである。

【課題を解決するための手段】

【0019】

この発明に係るデータ処理システムにおいては、上位階層バスでバスアクセス権の調停に使用される優先順位情報を下位階層バスに伝達し、下位階層バスにおいても、その伝達された優先順位情報を用いてバスアクセス権の調停を行なう。

【発明の効果】

【0020】

上位階層バスでバスアクセス権調停に使用される優先順位情報を下位階層バスに伝達している。したがって、階層バス構造において、階層間をまたがって、統一された優先順位を用いてバスアクセス権の調停を行なうことができる。応じて、上位階層バスに接続されるバスマスターの優先順位が変更されても、正確に、アクセス権の調停を行なうことができる。

【0021】

また、上位階層バスに接続されるバスマスターの優先順位の変更が許容されるため、上位階層バスに接続するバスマスターのグループ分けの自由度を大きくすることができる。また、システムの動作モードが変更され、バスマスターのデータ転送制限時間が変更された場合でも、このデータ転送制限時間に応じた優先順位をバスマスターに割当ることができ、正確に、バスアクセス要求の調停を行なうことができ、データ処理効率の劣化を抑制することができる。

【0022】

特に、固定優先権調停方式を用いる階層バス構造においては、バスマスターの優先順位が変更されても、バスマスターの優先順位割当の原則を維持することができ、優先順位に従つて正確にバスアクセス調停を行うことができる。

【図面の簡単な説明】

【0023】

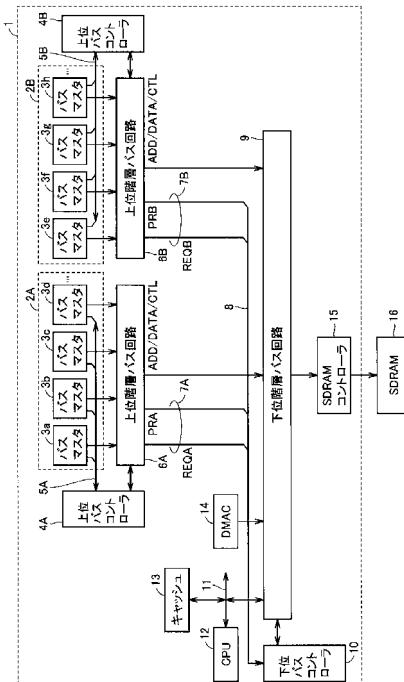

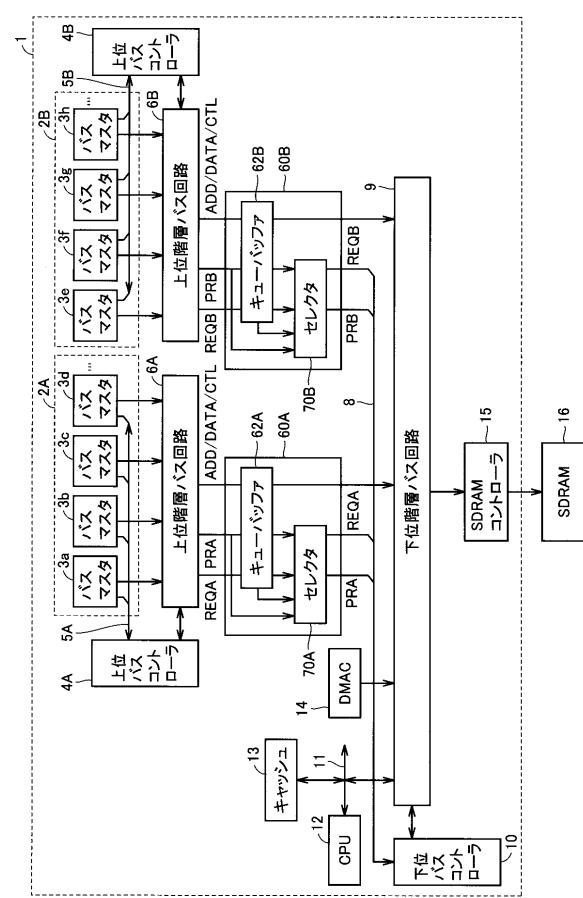

【図1】この発明の実施の形態1に従うデータ処理システムの全体の構成を概略的に示す図である。

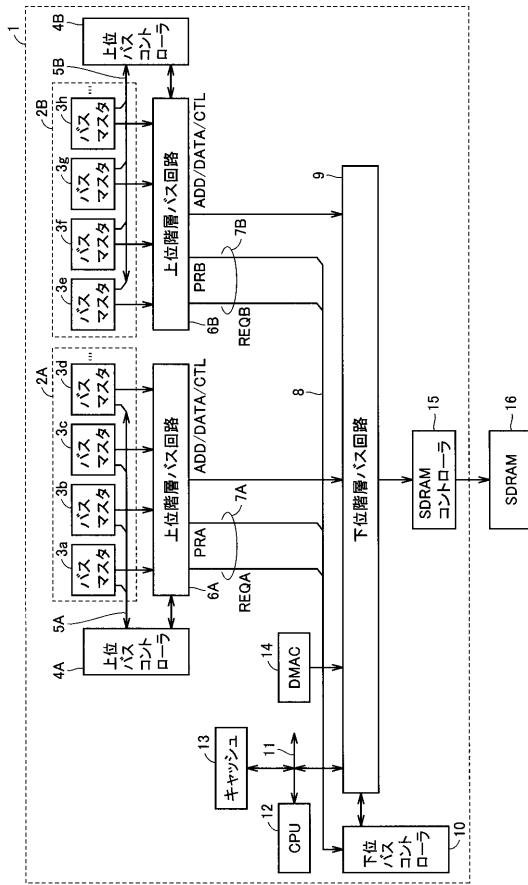

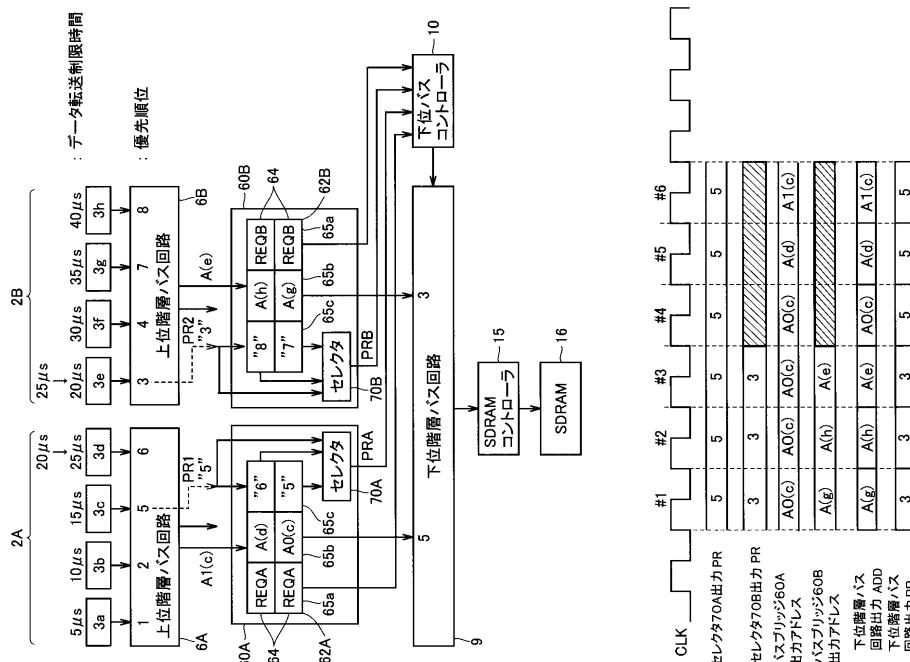

【図2】図1に示すデータ処理システムのバスアクセス調停動作を示す図である。

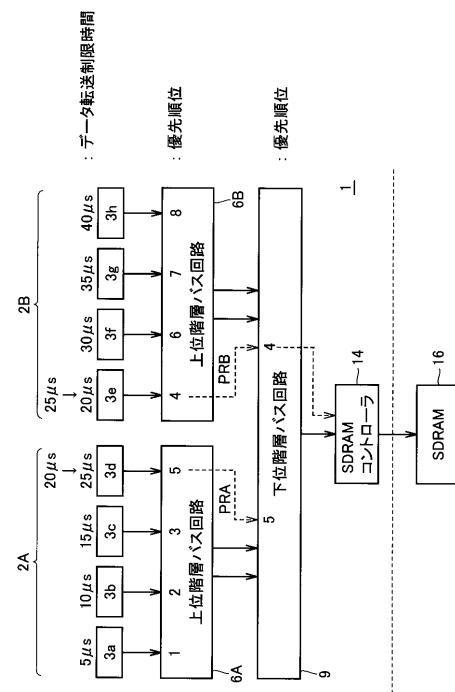

【図3】図1に示す上位バスコントローラおよび上位階層バス回路の構成の一例を概略的に示す図である。

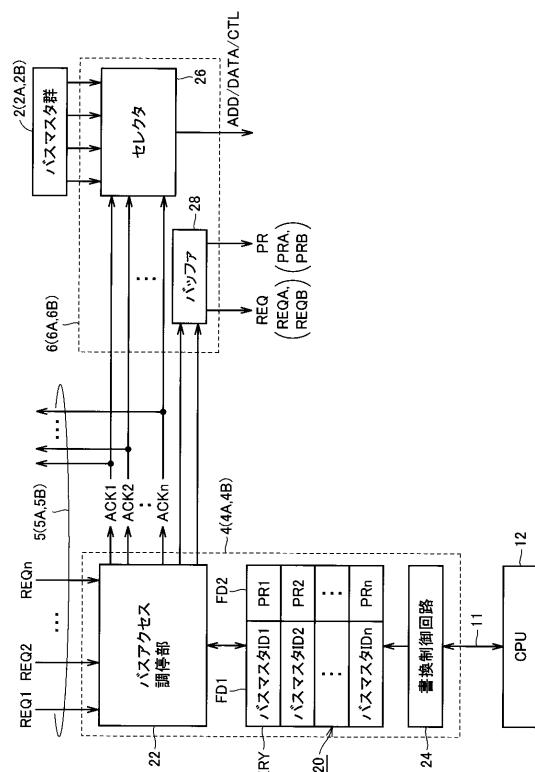

【図4】図1に示す下位階層バス回路および下位バスコントローラの構成の一例を概略的に示す図である。

【図5】この発明の実施の形態1のデータ転送許可発生部の構成を概略的に示す図である。

【図6】この発明の実施の形態2に従うデータ処理システムの全体の構成を概略的に示す図である。

【図7】図6に示すデータ処理システムのアクセス固定動作の一例を示す図である。

【図8】この発明の実施の形態3に従うデータ処理システムの全体の構成を概略的に示す図である。

【図9】図8に示すデータ処理システムのバスアクセス調停動作の一例を示す図である。

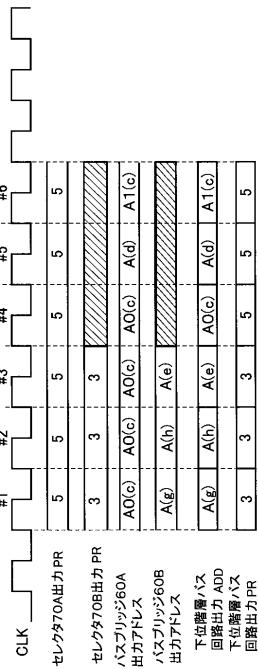

【図10】図9に示すデータ処理システムのアクセス調整動作を示すタイミング図である。

【発明を実施するための形態】

【0024】

[実施の形態1]

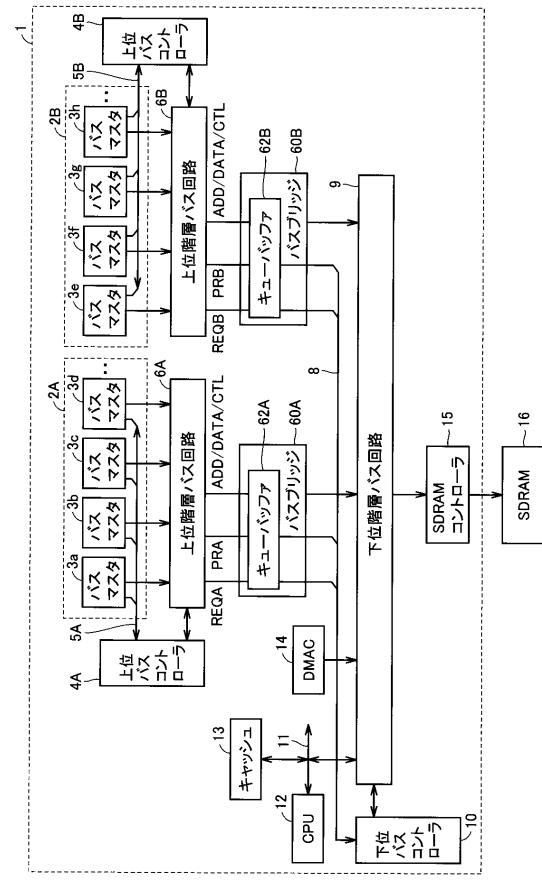

図1は、この発明の実施の形態1に従うデータ処理システムの全体の構成を概略的に示す図である。図1において、データ処理システムは、一例として、マルチメディア用シス

10

20

30

40

50

システムLSI1で構成される。このシステムLSI1は、処理内容が予め割当てられるバスマスター群2Aおよび2Bを含む。バスマスター群2Aは、バスマスター3a-3d、...を含み、バスマスター群2Bは、バスマスター3e-3h、...を含む。

【0025】

バスマスター群2Aは、一例として、画像処理を担当し、バスマスター群2Bは、画像表示を担当する。画像処理は、入力画像の変換処理などの画像からある情報を抽出する処理を示す。画像表示は、処理画像の表示装置への表示を行い、受信画像データの表示装置への表示の処理も含む。これらのバスマスター群2Aおよび2Bには、他の画像圧縮処理などが割当てられてもよく、マルチメディア用システムLSI1が処理するデータの種類に応じて、その処理内容が定められればよい。

10

【0026】

バスマスター3a-3hの各々は、対応のバスマスター群2Aおよび2Bに割当てられる処理内容内の単位処理を実行する。画像処理を担当するバスマスター群2Aにおいてバスマスター3a-3dは、たとえば、一例として、フィルタ処理、画像の重ね合わせ、色相の変更などの処理を実行する。画像表示を担当するバスマスター群2Bにおいては、バスマスター3e-3hは、一例として、各々、表示画像データの倍速表示のための画像データ配列、画像データの転送周波数の変換などの処理をそれぞれ実行する。

【0027】

バスマスター群2Aに対して、上位バスコントローラ4Aおよび上位階層バス回路6Aが設けられ、バスマスター群2Bに対して、上位バスコントローラ4Bおよび上位階層バス回路6Bが設けられる。

20

【0028】

上位バスコントローラ4Aは、バスマスター群2Aに含まれるバスマスター3a-3d、...とコントロールバス5Aを介して結合され、これらのバスマスター3a-3d、...のバスアクセス要求の調停を行なう。上位階層バス回路6Aにおいては、一例として、内蔵のセレクタにより、上位バスコントローラ4Aによりアクセス要求が許可されたバスマスターを選択する。

【0029】

上位バスコントローラ4Bも同様、コントロールバス5Bを介してバスマスター3e-3h、...に結合され、これらのバスマスター3e-3h、...のアクセス要求の調停を行なう。一例として、上位階層バス回路6Bにおいても、セレクタが含まれてあり、上位バスコントローラ4Bによりアクセス要求が許可されたバスマスターを、この内部のセレクタにより選択する。

30

【0030】

上位バスコントローラ4Aおよび4Bは、それぞれ、バスアクセス要求が許可されたバスマスターに割当てられている優先順位を示す優先順位伝達信号PRAおよびPRBを、それぞれアクセス要求が許可されたバスマスターのアクセス要求REQAおよびREQBならびにアドレス(ADD)、データ(DATA:データ書込時)およびコマンド(CTL)とともに転送する。

40

【0031】

このアクセス要求が許可されたバスマスターに割当てられた優先順位を示す優先順位伝達信号PRAおよびPRBを下位階層へ伝達することにより、バスマスター3a-3h、...においてデータ転送制限時間(優先順位)が変更される場合においても、正確なバスアクセス要求の調停を実現することができる(この動作については後に説明する)。

【0032】

上位階層バス回路6Aおよび6Bに対し共通に、下位階層バス回路9が設けられる。下位階層バス回路9に対して下位バスコントローラ10が設けられる。上位階層バス回路6Aおよび6Bからの優先順位伝達信号PRAおよびPRBとアクセス要求REQA1およびREQBは、それぞれローカルコントロールバス7Aおよび7Bに結合されるコントロールバス8を介して下位バスコントローラ10へ与えられる。

50

## 【0033】

下位バスコントローラ10は、転送された優先順位伝達信号PRAおよびPRBに従つてバスアクセス要求を調停し、一例として、下位階層バス回路9に含まれるセレクタにより、アクセス許可された上位階層バス回路6(6Aまたは6B)の出力するアドレス(ADD)、データ(DATA:データ書込時)およびコマンド(CTL)を選択する。

## 【0034】

下位階層バス回路9に対しては、バススレーブとして、外部メインメモリとして設けられるSDRAM(クロック同期型ダイナミック・ランダム・アクセス・メモリまたはクロック同期型半導体記憶装置)16に対するアクセスを制御するSDRAMコントローラ15が設けられる。SDRAMコントローラ15は、下位階層バス回路9から転送されたアドレス、データおよびコマンドに従つて図示しないクロック信号に同期してSDRAM16へアクセスし、必要なデータの転送(書込または読出)を実行する。このSDRAMコントローラ15のアクセス制御動作は、通常のメモリコントローラのアクセス制御様と同様である。

10

## 【0035】

下位階層バス回路9は、また、CPUバス11を介してCPU(中央演算処理装置)12に結合される。CPUバス11にはキャッシュメモリ13が設けられ、CPU12が処理を実行する際に用いられるデータおよび命令がキャッシュメモリ13にキャッシュされる。

20

## 【0036】

下位階層バス回路9に対してさらに、DMAC(ダイレクト・メモリ・アクセス・コントローラ)14が設けられ、SDRAM16へのアクセスが、CPU12の制御を離れてDMAC14の制御のもとに実行される。これにより、CPU12の演算処理に並行して、SDRAM16とバスマスターとの間でデータ転送を実行する。

30

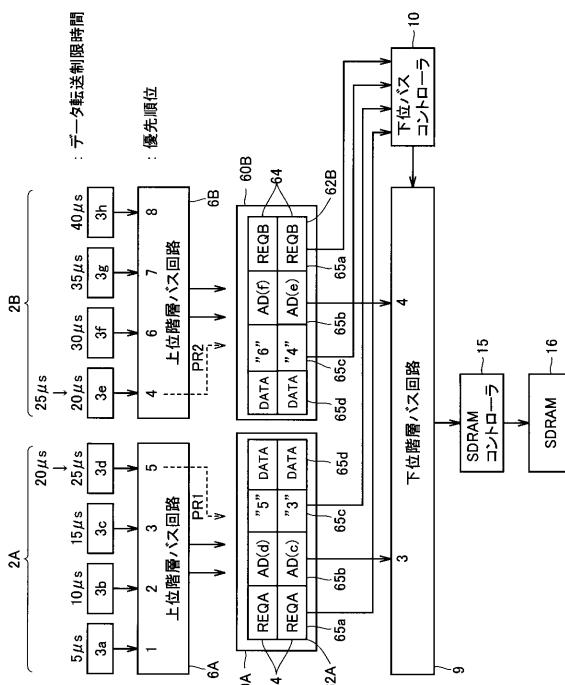

## 【0037】

図2は、この発明の実施の形態1に従うデータ処理システムの具体的なバスアクセス調停動作の一例を概略的に示す図である。図2において、一例として、バスマスター群2Aにおいてバスマスター3a-3dが用いられ、バスマスター群2Bにおいては、バスマスター3e-3hが利用される。バスマスター群2Aのバスマスター3a-3cに対し、データ転送制限時間として、5μs、10μs、15μsがそれぞれ割当てられる。システムの動作モードに応じて、バスマスター3dのデータ転送制限時間が20μsから25μsに変更される。一方、バスマスター群2Bにおいて、バスマスター3f-3hに対して、データ転送制限時間として、30μs、35μsおよび40μsがそれぞれ割当てられる。システムの動作モードの変更に伴って、バスマスター3eのデータ転送制限時間として25μsに代えて20μsが割当てられる。

30

## 【0038】

バスマスター3a-3hの優先順位は、バスマスター全体においてデータ転送制限時間が短いものに高い優先順位が割当てられるように割当てられる。したがって、バスマスター3a-3cに対して優先順位“1”、“2”、“3”が割当てられる。一方、バスマスター3f-3hに対しては、優先順位“6”、“7”および“8”が割当てられる。一方、システムの動作モードの変更に伴い、バスマスター3dおよび3eには、それぞれ、優先順位“5”、“4”が割当てられる。すなわち、バスマスターの優先順位は、バスマスター群内において個々に設定されるのではなく、バスマスター全体において、そのデータ転送制限時間に応じて割当てられる。従って、バスマスター群2Aに含まれるバスマスター3dの優先順位が、バスマスター群2Bのバスマスター3eの優先順位よりも低くなる状態が生じる。この処理モードに応じたバスマスターの優先順位の設定は、例えば、以下のようにして行なわれる。すなわち、図1に示すCPU12が、実行する処理モードに応じて各バスマスターに割り当たるデータ転送制限時間を算出し、その算出結果に基づいて最も短いデータ転送制限時間のバスマスターから順に高い優先順位を設定する。

40

## 【0039】

50

この図2に示す状態において、今、上位階層バス回路6Aにおいては、バスマスター3dからのバスアクセス要求が認められ、上位階層バス回路6Bにおいては、バスマスター3eからのバスアクセス要求が認められた状態を考える。この場合、上位階層バス回路6Aは、バスマスター3dの有する優先順位“5”を示す優先順位伝達信号PRAを下位階層バス回路9に転送する。一方、上位階層バス回路6Bは、このバスマスター3eの有する優先順位“4”を示す優先順位伝達信号PRBを下位階層バス回路9に転送する。

【0040】

下位階層バス回路9においては、この転送された優先順位伝達信号PRAおよびPRBに基づいて、優先順位の高いバスマスター3eのアクセス要求を選択する。したがって、上位階層バス回路6Aおよび6Bの下位階層バス回路9に対するアクセス優先順位は、固定的に上位階層バス回路6Aの方が高いように定められるのではなく、優先順位伝達信号PRAおよびPRBに従ってアクセス優先順位を判定してバスアクセス要求の調停を実行する。これにより、システムの処理動作に応じて、バスマスターのデータ転送制限時間が更新され、その優先順位が変更される場合においても、正確に、データ転送制限時間の短いバスマスターのアクセス要求を許可することができる。すなわち、固定優先方式のバスアクセス調停における、データ転送制限時間が短いバスマスターに対して高い優先順位を割当ててバスアクセス権の調停を行うという原則を、維持することができる。

10

【0041】

下位階層バス回路9に対しては、バススレーブとしてSDRAMコントローラ14およびSDRAM16が設けられており、SDRAMコントローラ14を介してSDRAM16に対しアクセスをして、データ転送を行なう。これにより、バスマスター3eは、設定されたデータ転送制限時間内に、必要なデータの転送を行なうことができる。

20

【0042】

図3は、図1に示す上位バスコントローラ4A、4Bおよび上位階層バス回路6A、6Bの構成の一例を概略的に示す図である。図3において、上位バスコントローラ4Aおよび4Bが同一構成を有し、また、上位階層バス回路6Aおよび6Bも同一構成を有するため、上位バスコントローラ4により、上位バスコントローラ4Aおよび4Bを代表的に示し、上位階層バス回路6により、上位階層バス回路6Aおよび6Bを代表的に示す。

30

【0043】

図3において、上位バスコントローラ4(4A, 4B)は、各バスマスターの優先順位を示す情報を格納するレジスタファイル20と、バスマスターからのバスアクセス要求REQ1-REQnに従ってレジスタファイル20を参照してバスアクセス要求の調停を行なうバスアクセス調停部22と、レジスタファイル20の各バスマスターの優先順位をCPU12からの指令に従って変更する書換制御回路24とを含む。

【0044】

レジスタファイル20は、各バスマスターに対応して配置されるエントリERYを含む。このエントリERYは、それぞれ、バスマスターを特定するバスマスターIDを格納する識別フィールドFD1と、各バスマスターに割当てられた優先順位を示す情報を格納する優先順位フィールドFD2を含む。

40

【0045】

但し、このレジスタファイル20の構成としては、夫々のエントリERYを対応するバスマスターに括り付けて(エントリERYの一番目をバスマスター3a、二番目のエントリをバスマスター3B、...等)優先順位を示す情報を格納するものであってもよく、逆に、夫々のエントリERYを対応する優先順位に括り付けてバスマスターを特定するバスマスター識別子IDを格納するものであってもよく、構成上の都合に応じて決定されればい。

【0046】

図3においては、一例として、レジスタファイル20内において、n個のバスマスターに対して割当てられるバスマスター識別子ID1-IDnと、バスマスターそれぞれに対して割当てられる優先順位を示す情報PR1-PRnが格納される。

【0047】

50

バスアクセス調停部 22 は、コントロールバス 5 ( 5A, 5B ) を介して与えられるバスマスターからのバスアクセス要求 REQ1 - REQn を受けると、バスアクセス要求が競合するとき、レジスタファイル 20 を参照し、最も優先順位の高いバスマスターのバスアクセス要求を識別し、この最も優先順位の高いバスマスターに対しバスアクセス要求を許可するバスアクセス許可 ACK をアサートする。

【 0048 】

バスアクセス調停部 22 からのバスアクセス許可 ACK1 - ACKn のうちの 1 つがアサートされ、コントロールバス 5 を介してそれぞれ対応のバスマスターに転送される。バスマスターは、対応のバスアクセス許可 ACKi ( i = 1 - n のいずれか ) がアサートされると、対応の上位階層バス回路に対して SDRAMへのデータ転送要求 ( データの書き込みまたは読み出し要求 ) を発行する。他のバスマスターは、自身に割当てられたバスアクセス許可 ACKi がアサートされるまで、バスアクセスは待ち合わせられる。

10

【 0049 】

書換制御回路 24 は、CPU12 から書換指示が与えられると、レジスタファイル 20 内の対応のバスマスターの優先順位を書換える。CPU12 は、バスコントローラ 4 と CPUバス 11 を介して結合され、システムの動作モードが変更され、各バスマスターに割当てられるデータ転送制限時間が変更されると、その変更に応じて、各バスマスターに対する優先順位を再編成する。この優先順位の再編成は、一例として、以下のようにして行なわれる。すなわち、テーブルメモリ内に、システムの処理モードに応じて各バスマスターに割当てられるデータ転送制御時間を各バスマスターに対応して格納する。CPU12 は、処理モード変更が指示されると、その変更後の処理モードに基いてテーブルメモリを参照して、各バスマスターのデータ転送制御時間情報を読み出し、全バスマスターに対して、この読み出したデータ転送制限時間の昇順に従って、優先順位を降順に割当てる ( 短いデータ転送制御時間に対してより高い優先順位を割当てる ) 。

20

【 0050 】

CPU12 は、実行する処理モードに応じて再編成された各バスマスターの優先順位情報を生成すると、一旦、レジスタファイルに生成したバスマスターの優先順位情報を格納する。この後、CPU12 は、CPUバス 11 を介して書換制御回路 24 に対し優先順位書換指示を与え先順位変更対象のバスマスターを特定するアドレス ( バスマスター識別情報 ID ) および対応の優先順位情報を転送する。これにより、各システム動作モードに応じてバスマスターの優先順位が変更される場合においても、各バスマスターに対して、最もデータ転送制限時間が短いバスマスターを優先的にアクセス許可するという固定優先方式のバスアクセス権調停の原則を維持することができる。

30

【 0051 】

上位階層バス回路 6 ( 6A, 6B ) は、バスアクセス調停部 22 からのバスアクセス許可 ACK1 - ACKn に従ってバスマスター群 2 ( 2A, 2B ) の出力情報を選択するセレクタ 26 と、下位階層に対するバスアクセス要求 IDQA およびアクセス許可されたバスマスターの優先順位を示す信号 PRA を伝達するバッファ 28 を含む。

【 0052 】

セレクタ 26 は、バスアクセス調停部 22 からのバスアクセス許可 ACK1 - ACKn に従って、アサートされたバスアクセス許可に対応するバスマスターの出力を対応のバスマスター群 2 から選択し、アクセス許可されたバスマスターから転送されたアドレス ADD 、データ DATA およびコマンド CTL を下位階層バス回路に転送する。

40

【 0053 】

バスマスター群 2 は、データ読み出しが要求されると、SDRAM ( 16 ) からデータの転送を要求する場合には、対応のバスマスターは、アドレスおよび読み出しへモード指示を出力し、セレクタ 26 からは、これらのアドレス ADD および読み出しへモードを指定するコマンド CTL が出力される。所定期間経過後、セレクタ 26 を介してバスマスター群 2 のアクセスが許可されたバスマスターに対し、SDRAM からの読み出しへデータ DATA が転送される。

【 0054 】

50

バッファ28は、バスアクセス調停部22からのバスアクセス要求およびアクセス許可されたバスマスターの優先順位情報を受け、バッファ処理して下位階層に対するバスアクセス要求REQ(REQA、REQB)および優先順位伝達信号PR(PRA、PRB)を生成する。

【0055】

なお、この図3に示す構成において、上位階層バス回路6においては、セレクタ26によりバスマスター群2に含まれるバスマスターの出力を選択している。しかしながら、以下の構成の場合には、このセレクタ26は、設ける必要はない。すなわち、バスマスター群2に含まれるバスマスターの出力部(インターフェース部)が、上位階層バスに並列に結合され、バスマスターは、それぞれ、対応のバスアクセス許可ACK1-ACKnがアサートされるときに出力がイネーブルされ、対応のバスアクセス許可ACKiがネゲート状態の場合には、バスマスターが出力ハイインピーダンス状態に維持される。この構成の場合には、セレクタ26は、機能的には、バス回路6に含まれる上位階層バスと、各バスマスターの出力部に設けられるバスインターフェイスとの組合せに対応することになる。

10

【0056】

図3に示す構成を利用することにより、システム動作モードに応じてバスマスターの優先順位が変更される場合においても、上位階層バス回路6におけるバッファ28により、下位階層バス回路またはバススレーブへ更新後の優先順位情報を伝達することができる。

20

【0057】

[バスコントローラの構成]

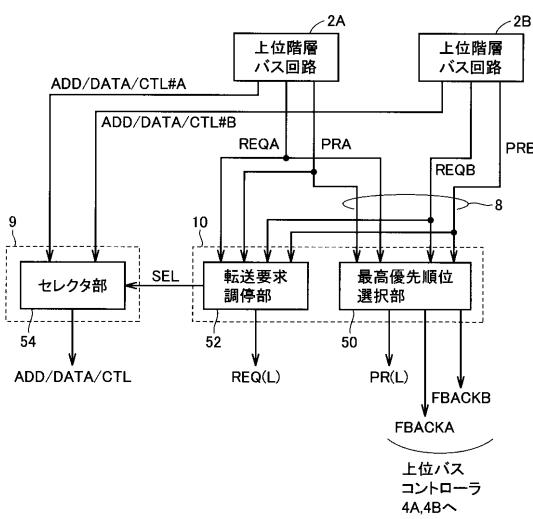

図4は、図1に示す下位階層バス回路9および下位バスコントローラ10の構成を概略的に示す図である。図4において、下位バスコントローラ10は、上位階層バス回路2Aおよび2Bから転送される優先順位伝達信号PRAおよびPRBのうち最も高い優先順位を選択する最高優先順位選択部50と、これらの上位階層バス回路2Aおよび2Bからの転送要求REQAおよびREQBと優先順位伝達信号PRAおよびPRBに従って競合アクセスを調停する転送要求調停部50を含む。

30

【0058】

最高優先順位選択部50は、上位階層バス回路2Aおよび2Bからのアクセス要求(転送要求)REQAおよびREQBがともにアサートされているとき、並行して伝達される優先順位伝達信号PRAおよびPRBのうち高いほうの優先順位を示す優先順位値を選択してバススレーブまたは下位階層バス回路に対し優先順位伝達信号PR(L)を生成して伝達する。この最高優先順位選択部50は、アクセス要求REQAおよびREQBの一方のみがアサートされている場合には、対応の優先順位伝達信号を選択して下位階層バス回路またはバススレーブに伝達する。

30

【0059】

この最高優先順位選択部50は、また、転送要求調停部52が生成したアクセスが許可されたバスを示す最終バスアクセス許可FBACKAおよびFBACKBを、上位バスコントローラ4Aおよび4Bへそれぞれ転送する。下位階層バス回路においてアクセスが許可されたバスマスターに対して、最終のバスアクセス許可ACKを生成して、バスマスターの転送動作を許可する。下位階層バス回路によりアクセスが待ち合わせられるバスマスターは、データ転送を以後に許可されるまで待合せる。この最終バスアクセス許可FBACKAおよびFBACKBを用いた転送処理については、後に詳細に説明する。

40

【0060】

転送要求調停部52は、これらの転送要求REQAおよびREQBと優先順位伝達信号PRAおよびPRBとに従って、最も優先順位の高い上位階層バス回路またはバスマスターを指定する選択信号SELを生成するとともに、下位階層バス回路またはバススレーブに対しアクセス要求REQ(L)および対応の優先順位伝達信号に従って下位への優先順位伝達信号PR(L)を生成して転送する。

【0061】

下位階層バス回路9は、セレクタ部54を含む。セレクタ部54は、上位階層バス回路

50

2 A および 2 B からのアドレス信号、データおよびコマンド ADD / DATA / CTL A および ADD / DATA / CTL B の一方を、転送要求調停部 52 からの選択信号 SEL に従って選択し、下位階層バス回路またはバススレーブに対するアドレス、データおよびコマンド (ADD / DATA / CTL) を転送する。

【0062】

この下位バスコントローラ 10 において、アクセス要求 (転送要求) REQ A および REQ B がともにアサートされているとき、伝達された優先順位伝達信号 PRA および PRB のうち高いほうの優先順位を示す上位階層バス回路またはバスマスターを選択する。これにより、下位階層バス回路 9 において、バスマスターの優先順位が変更されていても、伝達された優先順位伝達信号 PRA および PRB により高いほうの優先順位を有する上位階層バス回路 (またはバスマスター) を選択して下位階層バス回路またはバススレーブへ上位からの転送情報 (アドレス、データおよびコマンド) を転送することができる。

10

【0063】

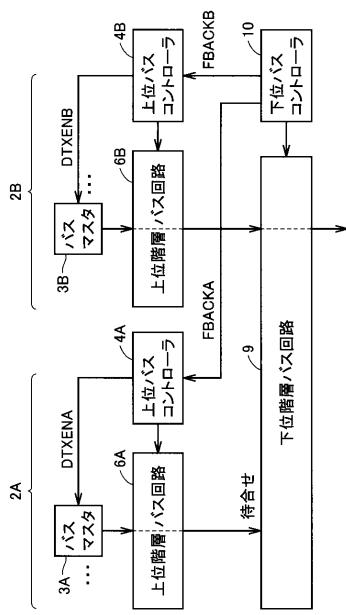

図 5 は、この発明の実施の形態 1 に従うデータ処理システムのデータ転送制御の構成を概略的に示す図である。図 5 において、下位バスコントローラ 10 は、その内部に含まれる最高優先順位選択部 50 においてアクセス許可されたバスマスターを示す最終バスアクセス許可 FBACKA および FBACKB を生成し、それぞれ、上位バスコントローラ 4A および 4B へ与える。

20

【0064】

上位バスコントローラ 4A および 4B は、最終バスアクセス許可 FBACKA および FBACKB のアサート時、対応の上位階層バス回路 6A および 6B においてアクセス許可されたバスマスター 3A および 3B に対して、データ転送許可 DTENA および DTEXNA をアサートする。バスマスター 3A および 3B は、それぞれ、データ転送許可 DTEXNA および DTEXNB のアサート時、データ転送を実行する。このときには、すでに、上位バスコントローラ 4 によりアクセスが許可されたバスマスターは、対応のバスアクセス許可 ACKi に従って転送がイネーブル状態に設定されている。書込データの転送を行なうライトデータ転送時においては、残りの書込データの転送を行なう。一方、読み出データ転送時においては、SDRAM (16) から転送されたデータが、対応の最終にバスアクセスが許可されたバスマスターに転送される。

30

【0065】

すなわち、上位バスコントローラ 4A および 4B は、バスアクセスが許可されたバスマスターをバスアクセス許可 ACKi により識別し、最終バスアクセス許可 FBACKA および FBACKB のアサート時、アサート状態のバスアクセス許可 ACKi に対応するバスマスターに対して、データ転送許可 DTENA および DTEXNB をアサートする。各バスマスターにおいて、バスアクセス許可 ACKi と最終バスアクセス許可 FBACK (FBACKA または FBACKB) との論理積演算を行なうことにより、両者がアサートされたバスマスターに対するデータ転送を許可することができる。

30

【0066】

なお、上述の構成において、階層バス構造は、上位階層バス回路および下位階層バス回路の 2 段階のバス構成とされる。しかしながら、さらに複数のバス階層が設けられていてよい。また、上位階層バス回路が、下位階層バス回路に対し 2 つ設けられているだけである。しかしながら、1 つの下位階層バス回路に対し 2 よりも大きい複数の上位階層バス回路が配置され、バスマスターが 3 以上のバスグループに分割されてもよい。

40

【0067】

個々に上位階層バス回路により優先順位の判定を行ない、また、下位階層バス回路においては、伝達された優先順位情報に従って最も高い優先順位のバスマスターを選択する。

【0068】

以上のように、この発明の実施の形態 1 に従えば、上位から下位に向かって、選択されたバスマスターの優先順位を示す優先順位情報を伝達している。これにより、データ転送制限時間の値がある範囲のバスマスターをまとめてグループ化し、各グループをそれぞれ 1 つ

50

の上位階層バス回路に接続することが特に要求されない。これにより、バス構成の自由度を改善することができる。また、システムの動作モードが変更され、バスマスターのデータ転送制限時間が変更された場合でも、優先順位を変更することにより、データ転送制限時間が短いバスマスターに対してより高い優先順位を与えるという原則を維持することができる。

【0069】

この図1に示す構成において上位階層バス回路と下位階層バス回路の間に、バスブリッジが設けられてもよい。データバス幅の変更およびデータ転送タイミングの調整をこのバスブリッジを用いて行なう。

【0070】

また、バスマスターがリードデータ転送を要求する場合、下位階層バス回路でアクセスが待ち合わせられた場合、アクセスが待ち合せ状態のバスマスターに対するデータ転送を待ち合わせる必要がある。この場合、下位バスコントローラ10からのバスアクセス許可FBA CKに従って、上位バスコントローラ4が、アクセス許可されたバスマスターに対し、要求したデータが、SDRAMから転送されたことを報知する構成が用いられてもよい。

10

【0071】

[実施の形態2]

図6は、この発明の実施の形態2に従うデータ処理システムの構成を概略的に示す図である。この図6に示すデータ処理システム1においては、上位階層バス回路6Aおよび上位階層バス回路6Bそれぞれと下位階層バス回路9の間にバスブリッジ60Aおよび60Bが設けられる。これらのバスブリッジ60Aおよび60Bは、それぞれキューバッファ62Aおよび62Bを含む。

20

【0072】

これらのキューバッファ62Aおよび62Bは、対応の上位階層バス回路6Aおよび6Bからそれぞれ転送されるアドレス、データおよびコマンド(ADD/DATA/CTL)に加えて、バスアクセス要求REQ(REQA,REQB)および優先順位伝達信号PRAをそれぞれ FIFO(ファーストイン・ファーストアウト)態様で格納する。キューバッファ62Aおよび62Bは、たとえば複数段のフリップフロップ(FF)で構成され、複数のバスマスターからのバスアクセス要求を待ち行列化することができる。図6に示すデータ処理システム1の他の構成は、図1に示すデータ処理システムの構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

30

【0073】

図7は、図6に示すデータ処理システムのアクセス要求選択態様を、バスブリッジの構成の一例とともに示す図である。図7において、バスブリッジ60Aおよび60Bにおいて、キューバッファ62Aおよび62Bは、それぞれ、2段のバッファレジスタ64を含む。キューバッファ62Aおよび62Bのバッファレジスタの段数は、システムの要求に応じて決定される。

30

【0074】

また、バスマスター群2Aにおいては、バスマスター3a-3dが設けられ、バスマスター群2Bにおいては、バスマスター3e-3hが設けられる。

40

【0075】

バッファレジスタ64は、バスアクセス要求REQ(REQA,REQB)を格納するバスアクセス要求フィールド65aと、転送アドレスを格納するアドレスフィールド65bと、優先順位伝達信号を格納する優先順位フィールド65cと、転送データを格納するデータフィールド65dとを含む。転送アドレスは、SDRAM16のメモリアクセス位置を示すアドレスである。転送データは、書込アクセス時にSDRAM16に転送されるデータである。

【0076】

図7において、いま、キューバッファ62Aにおいては、バスマスター3cの転送するアドレスAD(c)がその対応の優先順位“3”を示す情報および転送データDATA(c)

50

)とともにフィールド 65b、65c および 65d にそれぞれ格納され、また、バスマタ 3d が転送するアドレス A D (d) とリンクして、バスマスタ 3d の優先順位 “5” を示す情報が転送データ D A T A (d) とともに、それぞれ、フィールド 65b、65c および 65d に格納され、この場合、アクセス要求を行なっているため、バスアクセス要求 R E Q A がアサートされて対応のバスアクセス要求フィールド 65a に格納される。

#### 【0077】

キューバッファ 62Bにおいては、バスマスタ 3e が転送するアドレス A D (e) とリンクしてこのバスマスタ 3e の優先順位 “4” を示すデータおよび転送データ D A T A (e)、それぞれ、フィールド 65b、65c および 65d に格納される。また、バスマスタ 3f の転送アドレス A D (f) が、その優先順位 “6” とともにリンクしてフィールド 65b および 65c に格納される。また、上位階層バス回路 6B からアクセス要求が行なわれてあり、バスアクセス要求 R E Q B がアサートされて各対応のバスアクセス要求フィールド 65a に格納される。

10

#### 【0078】

上述のように、バッファレジスタ 64 は、一例として、フリップフロップ (F F) で構成される。上位階層バス回路 6A および 6B からバスアクセス要求が優先順位伝達信号とともに転送されるごとに、キューバッファ 62A および 62B に順次 F I F O (ファーストイン・ファーストアウト) 様様で対応の上位バス回路 6A および 6B からの転送情報がそれぞれ格納される。各クロック信号に同期して、キューバッファ 62A および 62B それぞれから、最初に格納されたバッファレジスタ 64 の内容が、下位バスコントローラ 10 に転送され、さらに、バスアクセス要求の調停が行なわれる。

20

#### 【0079】

図 7 に示す配置においては、下位階層バス回路 9において、バスマスタ 3c および 3e からのアクセス要求の調停が行なわれる。バスマスタ 3c の優先順位が “3” であり、バスマスタ 3e の優先順位が “4” である。従って、キューバッファ 62A からの転送アドレス A D (c) および転送データ D A T A (c) が選択され、対応の優先順位伝達信号とともに下位階層バス回路 9 を介して S D R A M コントローラ 15 に転送される。転送データ D A T A は、S D R A M に対する書き込みデータである。

#### 【0080】

なお、データ転送についても、キューバッファ 62A および 62B 内にバッファレジスタがそれぞれ書き込みデータ転送経路および読み出しだけ転送経路に設けられる。上述の転送データ D A T A を格納するバッファレジスタ 65d は、書き込みデータ転送部において設けられ、アドレスと同様にバッファレジスタ 65d に転送データが、F I F O 様様で格納される。一方、読み出しだけ転送経路においては、S D R A M コントローラ 15 を介して転送されるデータを F I F O 様様で格納して上位階層バス回路 6A および 6B に転送する F I F O バッファレジスタが設けられる。この場合、下位バスコントローラ 10においては、先の実施の形態 1において図 4 および 7 を参照して説明したように、読み出しだけ転送時、最終バスアクセス許可 F B A C K A および F B A C K B に従って読み出しだけ転送を要求したバスマスタが特定されてイネーブルされるため、読み出しだけデータがアクセス要求したバスマスタに対して正確に F I F O 様様で転送される。

30

#### 【0081】

したがって、上位階層バス回路 6A および 6B の内部構成およびこの上位バスコントローラ、および下位階層バス回路 9 および下位バスコントローラ 10 の構成としては、先の実施の形態 1において説明した構成を利用することができる。

40

#### 【0082】

なお、この図 7 に示す構成においてキューバッファ 62A および 62B においてバスアクセス要求 R E Q A および R E Q B が格納されている。この構成の場合、キューバッファ 62A および 62B に、さらに、各バスアクセスを要求するバスマスタを識別するバスマスタ識別子 I D を格納し、下位バスコントローラ 10 においては、最終的にバスアクセスが許可されたバスマスタを、転送されたバスマスタ識別子に基づいて判別して、最終バス

50

アクセス許可を、バスマスター識別子とともに上位バスコントローラに転送する構成が用いられてもよい。上位バスコントローラが、最終バスアクセス許可 F B A C K およびバスマスター識別子 I D に基いて、アクセス許可されたバスマスターを識別して、転送データ取り込みイネーブル状態に設定してもよい。

【 0 0 8 3 】

以上のように、この発明の実施の形態 2 に従えば、バスブリッジ内において、バスブリッジ内に、優先順位を示す優先順位を格納するバッファを配置しており、この格納した優先順位情報を下位階層バス回路に伝達することができる。したがって階層バス構造において、この上位階層バスと下位階層バスの間にバスブリッジが配置される場合においても、正確に上位階層バスから下位階層バスに優先順位を示す情報を伝達することができ、実施の形態 1 において示す構成と同様の効果を得ることができる。また、上位および下位階層バス回路において、パイプライン的にバスアクセス調停を行うことができ、上位階層バス回路においても、下位階層バス回路での調停結果により、調停を待合せる必要がなく、高速処理が実現される。

【 0 0 8 4 】

[ 実施の形態 3 ]

図 8 は、この発明の実施の形態 3 に従うデータ処理システムの構成を概略的に示す図である。図 8 に示すデータ処理システムにおいては、バスブリッジ 60A および 60B において、さらに、セレクタ 70A および 70B が設けられる。セレクタ 70A は、キューバッファ 62A に格納される優先順位情報をすべてと上位階層バス回路 6A から転送される優先順位伝達信号 P R A とを受け、これらの優先順位を判定し、最も優先順位の高い優先順位伝達信号を選択する。セレクタ 70B も、同様、キューバッファ 62B に格納される全ての優先順位情報をと、上位階層バス回路 6B から与えられる優先順位伝達信号 P R B とを受け、これらの与えられた優先順位情報のうち最も優先順位の高い優先順位情報を選択して出力する。

【 0 0 8 5 】

キューバッファ 62A および 62B には、複数のバスマスターからのバスアクセス要求 R E Q が、優先順位情報 P R i とともにリンクして格納される。セレクタ 70A および 70B 各々は、対応のバスアクセス要求 R E Q がアサートされているとき、対応の優先順位情報をすべて比較する。

【 0 0 8 6 】

図 8 に示すデータ処理システムの他の構成は、図 6 に示すデータ処理システムの構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

【 0 0 8 7 】

図 9 は、図 8 に示すデータ処理システムの転送処理動作の一例を概略的に示す図である。図 9 において、バスマスター群 2A において、バスマスター 3a - 3d が用いられ、バスマスター群 2B においてバスマスター 3e - 3h が用いられる。

【 0 0 8 8 】

バスマスター群 2A において、バスマスター 3a、3b、3c および 3d に対し優先順位 “1”、“2”、“5”、および “6” が割当てられる。一方、バスマスター群 2B において、バスマスター 3e、3f、3g および 3h に対しそれぞれ、優先順位 “3”、“4”、“7” および “8” が割当てられる。すなわち、上位階層バス回路 6A において、バスマスター 3c、3d および 3e が順次アクセス要求が許可され、また、上位階層バス回路 6B において、バスマスター 3g、3h および 3i が順次バスアクセスが許可された状態を考える。

【 0 0 8 9 】

この場合、バスブリッジ 62A において、バスマスター 3c に対して、キューバッファ 62A のバッファレジスタに、バスアクセス要求 R E Q A、アドレス A 0 (c) および優先順位情報 “5” が格納される。次のバッファレジスタ 64 において、バスマスター 3d に対するバスアクセス要求 R E Q A、アドレス A (d) および優先順位情報 “6” が格納され

10

20

30

40

50

る。また、この状態において、上位階層バス回路 6 A から、次のバスマスター 3 c からのアクセス要求に従って転送先アドレス A 1 ( c ) が優先順位情報 “ 5 ” とともに転送される。この場合、キューバッファ 6 2 A においては、バッファレジスタ 6 4 すべてに有効情報が格納されており、上位階層バス回路 6 A から転送されるアドレス A 1 ( c ) および優先順位情報 “ 5 ” は待ち合わせられる。

【 0 0 9 0 】

一方、バスブリッジ 6 0 B において、キューバッファ 6 2 B において、バスマスター 3 g からのバスアクセス要求 R E Q B が転送要求アドレス A ( g ) と優先順位情報 “ 7 ” が格納される。またバスマスター 3 h からの要求に従ってバスアクセス要求 R E Q B 、転送先アドレス A ( h ) および優先順位情報 “ 8 ” が格納される。次のサイクルにおいて、バスマスター 3 e からの転送要求アドレス A ( e ) が優先順位情報 “ 3 ” とともにキューバッファ 6 2 B に与えられてその格納が待ち合わせられる。

10

【 0 0 9 1 】

なお、キューバッファ 6 2 A および 6 2 B において、先の実施の形態 2 と同様、転送データを格納するデータフィールドが設けられるが、図 9 においては、図面の煩雑化を避けるために示していない。アドレス信号の転送経路に関連する部分のみを示す。

【 0 0 9 2 】

この状態において、セレクタ 7 0 A は、対応のキューバッファ 6 2 A に格納される有効優先順位情報および上位バス回路からの優先順位伝達信号のすべてを受け、最も優先順位の高い優先順位情報を選択して優先順位伝達信号 P R A を生成する。セレクタ 7 0 B も、キューバッファ 6 2 B に格納されるフィールド 6 5 c に格納される優先順位情報および上位バス回路 6 B からの待合せ状態の優先順位伝達信号を並列に受け、最も優先順位の高い優先順位を選択して優先順位伝達信号 P R B を生成する。このセレクタ 7 0 A および 7 0 B からの優先順位伝達信号 P R A および P R B が、下位バスコントローラ 1 0 へ与えられる。このとき下位階層バス回路 9 において、バスブリッジ 6 0 A および 6 0 B から転送されたアドレス ( およびデータ ) の転送制御を行なう。

20

【 0 0 9 3 】

図 10 は、図 9 に示すデータ処理システムの動作を示すタイミング図である。以下、図 10 を参照して、図 9 に示すアクセス要求調停動作について説明する。

30

【 0 0 9 4 】

バスブリッジ 6 0 A および 6 0 B におけるキューバッファ 6 2 A および 6 2 B は、クロック信号 C L K に同期して動作する。

【 0 0 9 5 】

サイクル 1 において、セレクタ 7 0 A は、優先順位として “ 5 ” 、 “ 6 ” および “ 5 ” が与えられており、優先順位伝達信号 P R A として、最も優先順位の高い優先順位 “ 5 ” を選択して下位バスコントローラ 1 0 へ対応のアドレスおよびデータとともに与える。一方、セレクタ 7 0 B は、優先順位として “ 7 ” 、 “ 8 ” および “ 3 ” を受け、最も高い優先順位 “ 3 ” を選択して優先順位伝達信号 P R B を生成して下位バスコントローラ 1 0 へ与える。

40

【 0 0 9 6 】

したがって、この場合、上位階層バス回路 6 A および 6 B に対してはそれぞれ、優先順位 “ 5 ” および “ 3 ” が割当てられる。このとき、下位階層バス回路 9 に対しては、キューバッファ 6 2 A および 6 2 B のアドレスフィールド 6 5 b に格納されるアドレス ( および転送データ ) が並行して与えられる。下位階層バス回路 9 においては、下位バスコントローラ 1 0 の制御のもとに、優先順位 “ 3 ” が割当てられたキューバッファ 6 2 B からのアドレス A ( e ) が選択されて S D R A M コントローラ 1 5 へ与えられる。

【 0 0 9 7 】

次のサイクル 2 において、キューバッファ 6 2 A の内容の発行は行なわれていないため、セレクタ 7 0 A は、サイクル 1 と同様に、優先順位伝達信号 P R A として、優先順位 “ 5 ” を選択して下位バスコントローラ 1 0 へ与える。セレクタ 7 0 B は、このとき、

50

優先順位“3”を選択して優先順位伝達信号PRBを生成して下位バスコントローラ10へ与える。ここで、クロック信号CLKに同期してキューバッファ62Bにおいては、バスマスター3gからの転送アドレスおよび転送データが下位階層バス回路9へ発行されており、バスマスター3eからの優先順位伝達信号PR2(=“3”)および対応ORドレス信号A(e)がキューバッファ62Bのバッファレジスタ64に格納される。

#### 【0098】

このときには、下位階層バス回路9においては、バスブリッジ62Aおよび62Bからの優先順位情報“5”および“3”に従って、キューバッファ62Bのアドレスフィールド65bの次のアドレスA(h)に優先順位“3”が割当てられており、このアドレスA(h)が対応の転送データおよび優先順位伝達信号PR(=“3”)とともに下位階層バス回路9を介してSDRAMコントローラ15へ転送される。

10

#### 【0099】

次のサイクル3においても、バスブリッジ60Aのキューバッファ62Aおよび上位階層バス回路6Aの出力優先情報は変化しないため、セレクタ70Aは、これまでのサイクルと同様、優先順位“5”を示す情報を選択して出力する。

#### 【0100】

バスブリッジ60Bにおいては、セレクタ72Bが、優先順位“3”を選択して、優先順位伝達信号PRBを生成して下位バスコントローラ10へ与える。下位階層バス回路9は、バスブリッジ60Bからの優先順位伝達信号PRBが、優先順位“3”を示しており、下位バスコントローラ10の制御の下に、バスブリッジ60Bからのアドレス信号A(e)を選択して対応の転送データとともに下位階層バス回路9へ転送する。

20

#### 【0101】

サイクル3において、バスブリッジ60B内のキューバッファ62Bに格納されたアドレスすべての転送が完了すると、上位階層バス回路6Bからの優先順位情報はすべて転送されており、以後のサイクルにおいては無視される(以後のサイクルにおいてバスマスター群2Bからのアクセス要求は発行されないとする)。

#### 【0102】

サイクル4においては、キューバッファ62Aから、優先順位“5”がセレクタ70Aにより選択されて出力される。従って、キューバッファ62Aのアドレスフィールド65aに格納されるアドレスA0(c)、A(d)およびA1(c)が対応の転送データとともに、クロックサイクル4、5および6において、それぞれ、選択されて下位バスコントローラ10へ与えられる。

30

#### 【0103】

この図9に示すように、優先順位が高いバスマスター3eがアクセス要求を発行した場合、バスマスター3eの待ち合わせは、先に格納された優先順位の低いアドレス情報の転送の後、続いて実行することができ、この優先順位の高いバスマスター3eの待ち合わせ時間を短縮することができる。

#### 【0104】

これにより、以下のような状況を回避することができる。すなわち、キューバッファ62Aにバスマスター3cおよび3dからの転送情報が格納され、また、キューバッファ62Bにバスマスター3gおよび3hからの転送情報が格納された後、バスマスター3cおよびバスマスター3eが、上位バス回路6Aおよび6Bにより選択された状態を考える。この場合、セレクタ70Aおよび70Bが設けられていない場合、以下のようにアクセス調停が行われる。バスブリッジ60Aに格納される優先順位“5”および“6”および次の優先順位“5”的バスマスター3c、3dおよび3cからのアクセス要求の発行が完了した後に、バスブリッジ60Bの優先順位“7”および“8”を有するバスマスター3gおよび3hのアドレスおよびデータの転送が行われる。この後に、優先順位“3”を有するバスマスター3eが、アクセスが許可されアドレスおよびデータの転送が実行される。この場合、優先順位の高いバスマスター3eの待ち合わせ時間が長くなり、効率的なデータ転送を実現することができなくなり、また、バスマスター3eのデータ転送制限時間内に必要データを転送する

40

50

ことができなくなり、データ処理を正確に行なうことができなくなる。

【0105】

従って、図8および図9に示すように、バスブリッジ60Aおよび60B内にセレクタを設けて、各バスブリッジに対する優先順位の最も高い優先順位を選択して下位階層バス回路に転送することにより、優先順位の高いバスマスターのアクセス要求の待ち時間短縮することができる。

【0106】

また、単に優先順位を選択しているだけであり、データ転送要求の発行順序は変更されていない。従って、システム内において必要とされるデータの転送順序を維持することができ、データ処理順序が維持され、処理データのインテグリティ(integrity)を確保することができ、正確なデータ処理を保障することができる。

10

【0107】

以上のように、この発明の実施の形態3に従えば、各上位バス回路において、複数の優先順位情報のうち最も優先順位の高いバスマスターの優先順位を選択している。したがって、優先順位の高いバスマスターのアクセス要求が、優先順位の低いバスマスターのアクセス要求により待ち合わせられる時間を、短くすることができ、処理効率を改善することができる。

【0108】

なお、上述の構成においては、各バスマスターに対して優先順位が各処理モードにおいて固定的に割当てられている。しかしながら、各バスマスターに対して割当てられる優先順位情報として、たとえば、バスマスターのアクセス待ち合わせ時間、またはトランザクション回数に基づいて待ち合わせ時間の最も長いものを優先順位が最も高い情報として転送する、または、トランザクション回数が最も少ない回数を、最も優先順位の高い優先順位情報として生成し、これらの優先順位情報を、各バスマスターの優先順位情報をとして用いて、これまでの実施の形態1から3の方式に従ってバスアクセスの調停を処理する構成が利用されてもよい。

20

【0109】

従って、上位バス回路において与えられる優先順位情報が各処理モード毎に固定的に設定される調停方式に加えて、バスマスターの優先順位が、バスアクセス要求の発効状況に応じて変更されるバスアクセス調停方式に対しても、本発明は適用することができる。

30

【産業上の利用可能性】

【0110】

この発明は、複数のバスマスターを含み、優先順位に従ってバススレーブに対するアクセス要求が調整される階層バス構造のデータ処理システムに適用することにより、階層バス構造において正確に、優先順位に従ってバスアクセスを調停することができる。特に、固定優先調停方式を用いる階層バス構造のデータ処理システムに適用することにより、システムの動作モードに応じて優先順位が更新される場合においても、正確に、短いデータ転送制限時間に高い優先順位を割当てるという優先順位設定原則を維持して、バスアクセスの調停を行なうことができる。

40

【符号の説明】

【0111】

1 マルチメディアシステムLSI、2, 2A, 2B バスマスター群、3a-3h バスマスター、6, 6A, 6B 上位階層バス回路、9 下位階層バス回路、4, 4A, 4B 上位バスコントローラ、10 下位バスコントローラ、20 レジスタファイル(テーブルメモリ)、22 バスアクセス調停部、26 セレクタ、28 バッファ、44 優先順位生成部、45 CPUインターフェイスI/F、46 優先順位レジスタ、47 選択レジスタ、48 セレクタ、12 CPU、50 最高優先順位選択部、52 転送要求調停部、54 セレクタ部、60A, 60B バスブリッジ、62A, 62B キューバッファ、70A, 70B セレクタ。

【 四 1 】

【 図 2 】

### 【 义 3 】

【 図 4 】

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

---

フロントページの続き

(74)代理人 100124523

弁理士 佐々木 真人

(72)発明者 樋口 良平

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

F ターム(参考) 5B061 BB02 BC01 PP05