(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7251412号**

**(P7251412)**

(45)発行日 令和5年4月4日(2023.4.4)

(24)登録日 令和5年3月27日(2023.3.27)

(51)国際特許分類

|         |                  |     |         |         |   |

|---------|------------------|-----|---------|---------|---|

| H 0 4 L | 25/02 (2006.01)  | F I | H 0 4 L | 25/02   | S |

| H 0 3 K | 5/12 (2006.01)   |     | H 0 3 K | 5/12    |   |

| H 0 3 K | 19/0175(2006.01) |     | H 0 3 K | 19/0175 |   |

請求項の数 7 (全24頁)

(21)出願番号 特願2019-158359(P2019-158359)

(22)出願日 令和1年8月30日(2019.8.30)

(65)公開番号 特開2021-40171(P2021-40171A)

(43)公開日 令和3年3月11日(2021.3.11)

審査請求日 令和3年9月22日(2021.9.22)

|          |                                          |

|----------|------------------------------------------|

| (73)特許権者 | 000004260<br>株式会社デンソー<br>愛知県刈谷市昭和町1丁目1番地 |

| (74)代理人  | 110000567<br>弁理士法人サトー                    |

| (72)発明者  | 本多 良充<br>愛知県刈谷市昭和町1丁目1番地 株式<br>会社デンソー内   |

| (72)発明者  | 糸 進介<br>愛知県刈谷市昭和町1丁目1番地 株式<br>会社デンソー内    |

| 審査官      | 北村 智彦                                    |

最終頁に続く

(54)【発明の名称】 通信装置

**(57)【特許請求の範囲】****【請求項1】**

伝送路を介してデータを送受信する複数の通信装置のうちいずれか一つの通信装置の通信に同期して他の通信装置が送信を行う通信システムにおいて用いられる前記通信装置であって、

前記伝送路上で優位な信号レベルを優位レベルとし、劣位な信号レベルを劣位レベルとしたとき、

前記伝送路の信号レベルが前記劣位レベルから前記優位レベルに変化するエッジを検出するエッジ検出回路(5、42)と、

オンすることにより前記伝送路の信号レベルを前記優位レベルとすることができるスイッチング素子(Q1)と、

前記スイッチング素子を駆動する駆動回路(9、22、32、52)と、

前記駆動回路の動作を制御するものであり、前記エッジ検出回路により前記エッジが検出されると前記駆動回路に対して前記スイッチング素子のオン駆動を指令するオン指令を与える制御回路(6、43、53)と、

を備え、

前記駆動回路または前記制御回路には、前記エッジから前記スイッチング素子がオンする時点までに要する遅延時間を短縮する遅延短縮部(14、23、34、57)が設けられており、

前記遅延短縮部(14、23、34)は、

10

20

前記駆動回路（9、22、32）に設けられたものであり、

前記駆動回路が前記スイッチング素子をオン駆動するオン期間の開始時点を含む期間に

、前記スイッチング素子の制御端子に対して一定の電圧を供給する電圧制御を行うことにより

前記スイッチング素子の制御端子の電圧である制御電圧を、前記スイッチング素子が

オンに転じる閾値電圧よりも所定値だけ低い第1電圧まで上昇させることで前記遅延時間を短縮する通信装置。

#### 【請求項2】

前記遅延短縮部（14、23）が設けられた駆動回路（9、22）は、

前記電圧制御を行うことにより前記制御電圧が前記第1電圧まで上昇した後、前記スイ

ッキング素子の制御端子に一定の電流を供給する定電流制御を行う請求項1に記載の通信

装置。

10

#### 【請求項3】

前記遅延短縮部（34）が設けられた駆動回路（32）は、

前記電圧制御を行うことにより前記制御電圧が前記第1電圧まで上昇した後、前記制御

端子の電圧が前記閾値電圧よりも高い第2電圧まで上昇するように電圧制御を継続する請

求項1に記載の通信装置。

20

#### 【請求項4】

前記遅延短縮部は、

前記スイッチング素子の制御端子に対する前記第2電圧の供給経路に直列に介在するフ

ィルタ回路（33）を備える請求項3に記載の通信装置。

20

#### 【請求項5】

伝送路を介してデータを送受信する複数の通信装置のうちいずれか一つの通信装置の通

信に同期して他の通信装置が送信を行う通信システムにおいて用いられる前記通信装置で

あって、

前記伝送路上で優位な信号レベルを優位レベルとし、劣位な信号レベルを劣位レベルと

したとき、

前記伝送路の信号レベルが前記劣位レベルから前記優位レベルに変化するエッジを検出

するエッジ検出回路（5、42）と、

オノンすることにより前記伝送路の信号レベルを前記優位レベルとすることができるスイ

ッキング素子（Q1）と、

前記スイッチング素子を駆動する駆動回路（9、22、32、52）と、

前記駆動回路の動作を制御するものであり、前記エッジ検出回路により前記エッジが検

出されると前記駆動回路に対して前記スイッチング素子のオン駆動を指令するオン指令を

与える制御回路（6、43、53）と、

30

を備え、

前記駆動回路または前記制御回路には、前記エッジから前記スイッチング素子がオンす

る時点までに要する遅延時間を短縮する遅延短縮部（14、23、34、57）が設けられ

てあり、

さらに、前記伝送路の信号を所定のサンプリングタイミングにおいてサンプリングするこ

とにより前記伝送路を介して伝送される符号を判定する判定部（44）と、

前記伝送路の信号レベルを検出し、その検出結果に基づいて前記伝送路に重畠するノイズ

を検出するノイズ検出部（45）と、

を備え、

前記判定部は、前記ノイズ検出部によりノイズが検出されると、前記サンプリングタイミ

ングを前記ノイズが検出された期間に応じた所定時間だけ遅らせる通信装置。

#### 【請求項6】

伝送路を介してデータを送受信する複数の通信装置のうちいずれか一つの通信装置の通

信に同期して他の通信装置が送信を行う通信システムにおいて用いられる前記通信装置で

あって、

前記伝送路上で優位な信号レベルを優位レベルとし、劣位な信号レベルを劣位レベルと

50

したとき、

前記伝送路の信号レベルが前記劣位レベルから前記優位レベルに変化するエッジを検出するエッジ検出回路(5、42)と、

オンすることにより前記伝送路の信号レベルを前記優位レベルとすることができるスイッチング素子(Q1)と、

前記スイッチング素子を駆動する駆動回路(9、22、32、52)と、

前記駆動回路の動作を制御するものであり、前記エッジ検出回路により前記エッジが検出されると前記駆動回路に対して前記スイッチング素子のオン駆動を指令するオン指令を与える制御回路(6、43、53)と、

を備え、

前記駆動回路または前記制御回路には、前記エッジから前記スイッチング素子がオンする時点までに要する遅延時間を短縮する遅延短縮部(14、23、34、57)が設けられており、

前記遅延短縮部(57)は、

前記制御回路(53)に設けられたものであり、

前記エッジ検出回路による検出結果に基づいて前記エッジの周期を学習する学習制御と、

前記学習制御により学習された前記エッジの周期に基づいて、次回の前記エッジが検出されるタイミングを予測する予測制御と、

前記予測制御により予測されたタイミングよりも前の時点において前記駆動回路に対して前記オン指令を与える先出し制御と、

を実行することにより前記遅延時間を短縮する通信装置。

#### 【請求項7】

前記遅延短縮部は、

前記エッジ検出回路により前記エッジが検出された時点から次に前記エッジ検出回路により前記エッジが検出される時点までカウント動作を実行するカウンタ(54a)を備え、

前記学習制御では、前記カウンタのカウント値に基づいて前記エッジの周期を学習するようになっており、

前記カウンタのカウント値が前記エッジの周期として想定される値よりも大きい上限値に達すると、前記学習制御による学習結果を一旦リセットして前記学習制御を再度実行するようになっており、

前記学習制御による学習結果が得られるまでの期間は前記予測制御および前記先出し制御の実行を停止するようになっている請求項6に記載の通信装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、伝送路を介してデータを送受信する複数の通信装置のうちいずれか一つの通信装置の通信に同期して他の通信装置が送信を行う通信システムにおいて用いられる通信装置に関する。

##### 【背景技術】

##### 【0002】

従来、車両に搭載された車載通信の方式として、例えばCXP1など、マスタの通信に同期してスレーブが送信を行う通信方式が知られている。なお、CXP1とは、Clock Extension Peripheral Interfaceの略称である。特許文献1には、このような通信において、伝送路上で優位な信号レベルを優位レベルとするとともに劣位な信号レベルを劣位レベルとしたとき、伝送路の信号レベルを劣位レベルから優位レベルに変化させるときのドライバ回路の動作を高速化させるための技術が開示されている。

##### 【先行技術文献】

##### 【特許文献】

##### 【0003】

##### 【文献】特許第5609930号公報

10

20

30

40

50

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

このような通信において、マスタにより生成されるクロックのエッジから伝送路の信号レベルを低位レベルから高位レベルに変化させる時点までの遅延時間は、通信プロトコルを満足しなければならないことから極力短いほうが望ましい。その一方で、ノイズ対策として、受信バッファの前段にフィルタ回路を挿入したという要望がある。しかし、フィルタ回路を挿入すると、その影響により、遅延時間が長くなり、通信プロトコルを満足できなくなるおそれがある。

**【0005】**

本発明は上記事情に鑑みてなされたものであり、その目的は、遅延時間を短縮することができる通信装置を提供することにある。

**【課題を解決するための手段】****【0006】**

請求項1に記載の通信装置は、伝送路を介してデータを送受信する複数の通信装置のうちいずれか一つの通信装置の通信に同期して他の通信装置が送信を行う通信システムにおいて用いられる通信装置であり、エッジ検出回路(5、42)、スイッチング素子(Q1)、駆動回路(9、22、32、52)および制御回路(6、43、53)を備える。この場合、伝送路上で高位な信号レベルを高位レベルとし、低位な信号レベルを低位レベルとする。エッジ検出回路は、伝送路の信号レベルが低位レベルから高位レベルに変化するエッジを検出する。スイッチング素子は、オンすることにより伝送路の信号レベルを高位レベルとすることができます。駆動回路は、スイッチング素子を駆動する。制御回路は、駆動回路の動作を制御するものであり、エッジ検出回路によりエッジが検出されると駆動回路に対してスイッチング素子のオン駆動を指令するオン指令を与える。

**【0007】**

上記構成において、駆動回路または制御回路には、伝送路の信号レベルが低位レベルから高位レベルに変化するエッジからスイッチング素子がオンする時点までに要する遅延時間を短縮する遅延短縮部(14、23、34、57)が設けられている。したがって、上記構成によれば、遅延時間を短縮することが可能となり、受信バッファの前段にフィルタ回路を挿入するような場合であっても、通信プロトコルを十分に満足することができる。

**【0008】**

請求項1に記載の通信装置では、遅延短縮部(14、23、34)は、駆動回路(9、22、32)に設けられたものである。この場合、遅延短縮部は、駆動回路がスイッチング素子をオン駆動するオン期間の開始時点を含む期間に、スイッチング素子の制御端子に

対して一定の電圧を供給する電圧制御を行うことによりスイッチング素子の制御端子の電圧である制御電圧を、スイッチング素子がオンに転じる閾値電圧よりも所定値だけ低い第1電圧まで上昇させることで遅延時間を短縮する。

**【0009】**

例えば、スイッチング素子をオン期間を通じて定電流駆動によりオン駆動するような従来の構成では、スイッチング素子の制御電圧は、オン期間を通じて一定の傾きで比較的緩やかに上昇する。そのため、上記した従来の構成では、制御電圧が閾値電圧に達してスイッチング素子がオンに転じるまでには、比較的長い時間を要することになり、その結果、駆動回路の動作に起因する遅延時間が長くなるおそれがある。これに対し、上記構成では、前述した電圧制御が行われることにより、スイッチング素子の制御電圧は、オン期間の開始時点を含む期間に第1電圧まで比較的急峻に一度に上昇する。

**【0010】**

上記構成では、このような電圧制御を行うことにより制御電圧が第1電圧まで上昇した後は、請求項2に記載されるように定電流制御が行われることにより、または、請求項3に記載されるように電圧制御が継続されることにより、制御電圧が閾値電圧に達してスイッチング素子がオンに転じる。このような構成によれば、上記した従来の構成に比べ、少

10

20

30

40

50

なくとも制御電圧が第1電圧まで一度に上昇される分だけ、スイッチング素子のターンオン時間、つまり駆動回路の動作に起因する遅延時間が短縮される。

#### 【0011】

請求項2に記載の通信装置では、遅延短縮部(14、23)が設けられた駆動回路(9、22)は、電圧制御を行うことにより制御電圧が第1電圧まで上昇した後、スイッチング素子の制御端子に一定の電流を供給する定電流制御を行う。このような構成によれば、スイッチング素子の制御電圧は、第1電圧まで上昇した後は、一定の傾きで比較的緩やかに上昇して閾値電圧に達することになる。制御電圧が急峻に上昇して閾値電圧に達してスイッチング素子がオンされると、そのオン動作に伴うエミッションの悪化が懸念される。しかし、上記構成によれば、制御電圧が比較的緩やかに上昇して閾値電圧に達してスイッチング素子がオンされるため、このようなエミッション悪化のリスクが軽減される。

10

#### 【図面の簡単な説明】

#### 【0012】

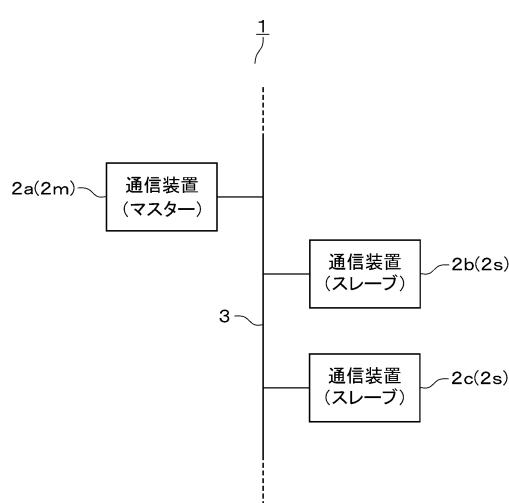

【図1】第1実施形態に係る通信システムの構成を模式的に示す図

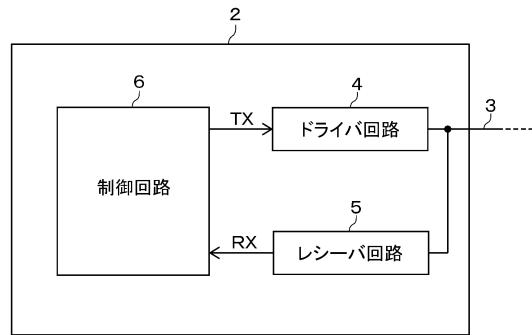

【図2】第1実施形態に係る通信装置の構成を模式的に示す図

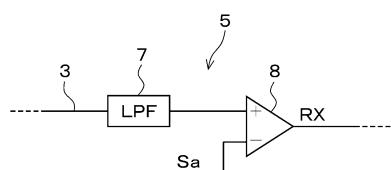

【図3】第1実施形態に係るレシーバ回路の具体的な構成を模式的に示す図

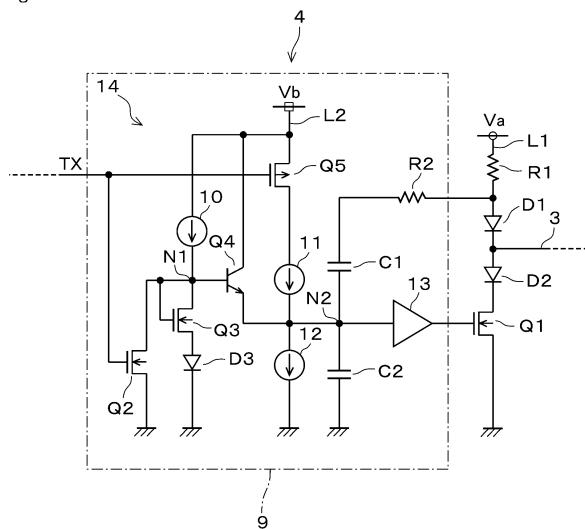

【図4】第1実施形態に係るドライバ回路の具体的な構成を模式的に示す図

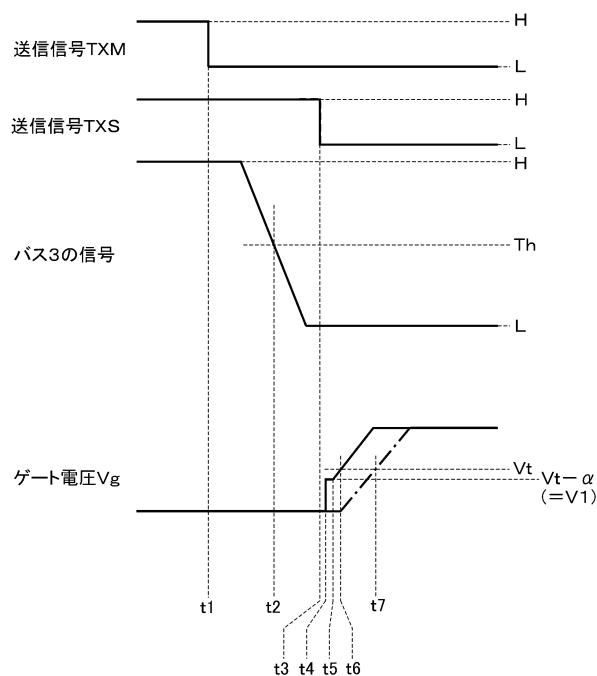

【図5】第1実施形態に係る通信装置の動作を説明するための図であり、送信信号、バス波形およびゲート電圧を模式的に示すタイミングチャート

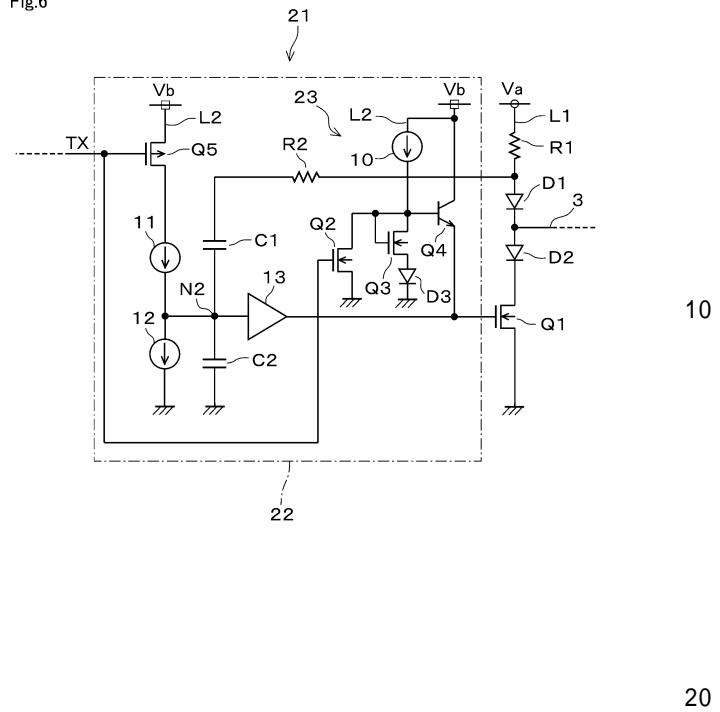

【図6】第2実施形態に係るドライバ回路の具体的な構成を模式的に示す図

20

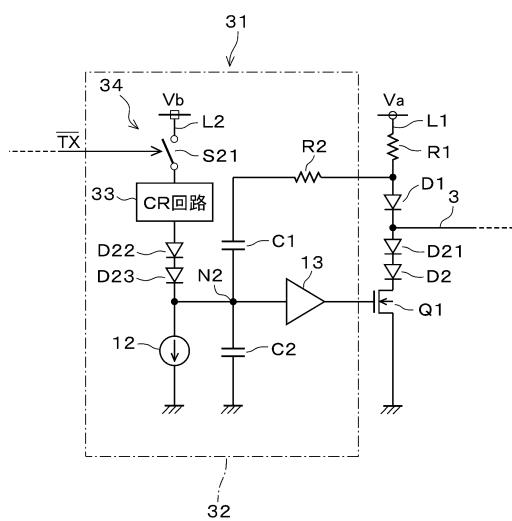

【図7】第3実施形態に係るドライバ回路の具体的な構成を模式的に示す図

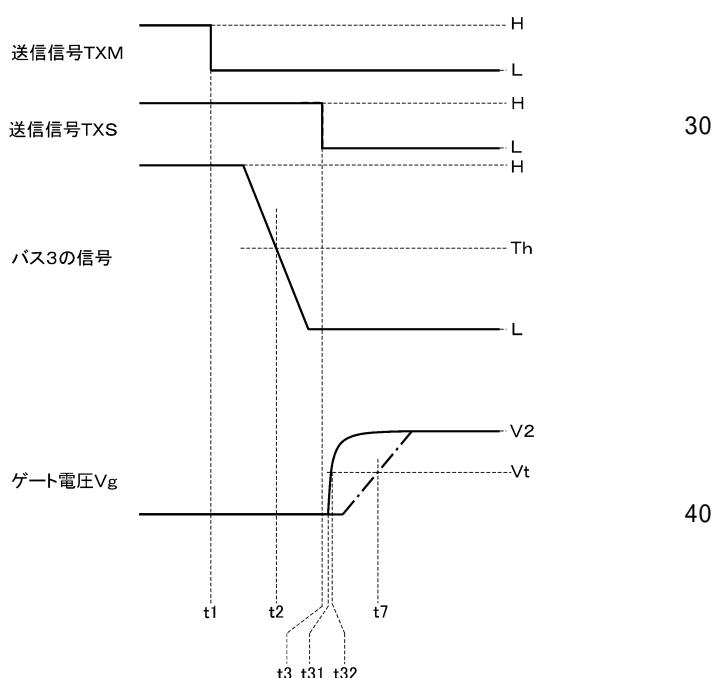

【図8】第3実施形態に係る通信装置の動作を説明するための図であり、送信信号、バス波形およびゲート電圧を模式的に示すタイミングチャート

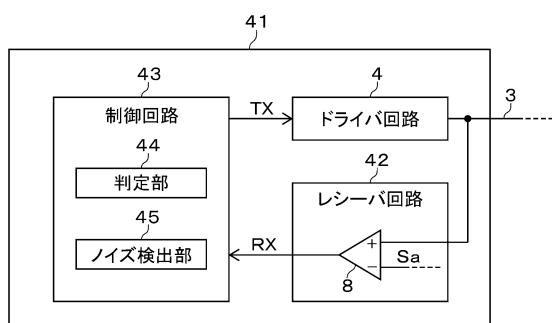

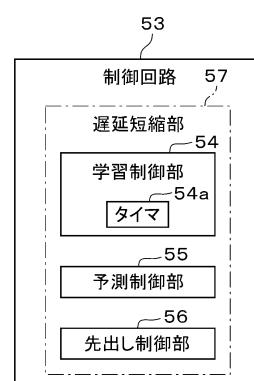

【図9】第4実施形態に係る通信装置の構成を模式的に示す図

【図10】第4実施形態に係る制御回路における各信号および加減算カウンタのカウント値を模式的に示すタイミングチャート

【図11】第5実施形態に係るドライバ回路の具体的な構成を模式的に示す図

【図12】第5実施形態に係る制御回路の具体的な構成を模式的に示す図

【図13】第5実施形態に係る通信装置の動作を説明するための図であり、送信信号、バス波形およびゲート電圧を模式的に示すタイミングチャート

30

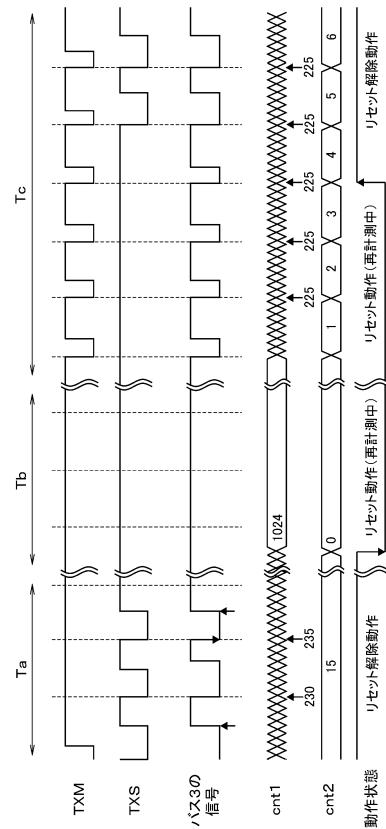

【図14】第6実施形態に係るバスがハイレベルに固着した場合の動作を説明するための図であり、送信信号、バス波形、カウント値および制御回路の動作状態を模式的に示すタイミングチャート

#### 【発明を実施するための形態】

#### 【0013】

以下、本発明の複数の実施形態について図面を参照して説明する。なお、各実施形態において実質的に同一の構成には同一の符号を付して説明を省略する。

##### (第1実施形態)

以下、第1実施形態について図1～図5を参照して説明する。

#### 【0014】

40

##### <通信システムの構成について>

図1に示す通信システム1は、例えば車両に搭載された複数の電子制御装置間の制御通信のために用いられるものである。通信システム1は、複数の通信装置2a、2b、2cが伝送路に相当するバス3を介して接続された構成となっている。以下では、通信装置2a、2b、2cについて、それぞれを区別する必要がない場合には通信装置2と総称することとする。この場合、通信システム1は、3つの通信装置2を備えているが、2つの通信装置2を備えていてもよいし、4つ以上の通信装置2を備えていてもよい。

#### 【0015】

複数の通信装置2は、半導体集積回路、つまりICとして構成されており、バス3を介してデータを送受信する。通信システム1では、複数の通信装置2のうちいずれか一つの

50

通信装置 2、具体的には通信装置 2 a の通信に同期して他の通信装置 2 b、2 c が送信を行いうようになっている。以下では、通信装置 2 a のことをマスター 2 m とも称するとともに、通信装置 2 b、2 c のことをスレーブ 2 s とも称することとする。

#### 【 0 0 1 6 】

通信システム 1 では、C X P I 通信によりデータの送受信が実行されるようになっている。C X P I 通信では、マスター 2 m は、スレーブ 2 s にバス 3 を介してクロックを供給し、スレーブ 2 s は、バス 3 を介して供給されるクロックに同期した通信を実行する。この場合、バス 3 は、異なる通信装置 2 からハイレベルの信号とロウレベルの信号とが同時に出力されると、バス 3 上の信号レベルがロウレベルとなるように構成されており、この機能を利用してバス調停が実現される。すなわち、この場合、ロウレベルの信号がバス 3 上で優位な信号レベルである優位レベルに相当し、ハイレベルの信号がバス 3 上で劣位な信号レベルである劣位レベルに相当する。

#### 【 0 0 1 7 】

バス 3 上では、伝送路符号として、ビットの境界で信号レベルがハイレベルからロウレベルに変化するとともに、ビットの途中で信号レベルがロウレベルからハイレベルに変化するパルス幅変調信号、つまり P W M 信号が用いられ、二値の信号が、デューティ比の異なる二種類の P W M 信号で表現される。以下では、ロウレベルの期間が比較的短いほうをレセシシブ符号と称するとともに、ロウレベルの期間が比較的長いほうをドミナント符号と称する。レセシシブ符号は「論理値 = 1」に対応し、ドミナント符号は「論理値 = 0」に対応する。

#### 【 0 0 1 8 】

この場合、レセシシブ符号では、1 ビットの最初の 1 / 3 の期間がロウレベルになるとともに、その後の 2 / 3 の期間がハイレベルになるように設定されている。また、この場合、ドミナント符号では、1 ビットの最初の 2 / 3 の期間がロウレベルになるとともに、その後の 1 / 3 の期間がハイレベルになるように設定されている。このようなことから、バス 3 上でレセシシブ符号とドミナント符号とが衝突すると、ドミナント符号が調停勝ちするようになっている。

#### 【 0 0 1 9 】

##### < 通信装置の構成について >

マスター 2 m とスレーブ 2 s とは、クロックを供給するための構成の有無など一部構成が異なるが、概ね同様の構成を有している。すなわち、図 2 に示すように、通信装置 2 は、ドライバ回路 4、レシーバ回路 5 および制御回路 6 を備えている。ドライバ回路 4 には、制御回路 6 から出力される送信信号 T X が与えられている。

#### 【 0 0 2 0 】

ドライバ回路 4 は、送信信号 T X に応じたデータをバス 3 を介して送信する。レシーバ回路 5 は、バス 3 を介して送信されたデータを受信し、受信信号 R X として制御回路 6 へ出力する。制御回路 6 は、ロジック回路として構成されたものであり、送信信号 T X を生成し、その送信信号 T X をドライバ回路 4 に出力する。また、制御回路 6 は、レシーバ回路 5 から出力される受信信号 R X を入力し、その入力した受信信号 R X に基づいて所定の処理を実行する。

#### 【 0 0 2 1 】

##### < レシーバ回路の具体的な構成について >

図 3 に示すように、レシーバ回路 5 は、フィルタ回路 7 およびコンパレータ 8 を備えている。この場合、バス 3 の信号は、フィルタ回路 7 を介してコンパレータ 8 の非反転入力端子に与えられている。フィルタ回路 7 は、例えば低域通過フィルタ、つまり L P F などであり、ノイズ対策として挿入されたものである。フィルタ回路 7 の出力信号は、バス 3 の信号に対し、ノイズが除去されるとともにフィルタ回路 7 の時定数に応じた遅れが生じた信号となる。

#### 【 0 0 2 2 】

コンパレータ 8 の反転入力端子には、閾値信号 S a が与えられている。閾値信号 S a は

10

20

30

40

50

、バス3の信号レベルがハイレベルからロウレベルに変化するエッジを検出するための閾値 $T_h$ に対応した信号である。以下、このようなエッジのことを境界エッジとも称する。このような構成により、コンパレータ8は、バス3の信号レベルが閾値 $T_h$ より高い場合にはハイレベルの信号を出力するとともに、バス3の信号レベルが閾値 $T_h$ より低い場合にはロウレベルの信号を出力するようになっている。コンパレータ8の出力信号は、前述した受信信号RXとして制御回路6に与えられる。

#### 【0023】

上記構成のレシーバ回路5は、バス3の信号レベルがハイレベルからロウレベルに変化するエッジ、つまり境界エッジを検出することができる。具体的には、レシーバ回路5は、コンパレータ8の出力信号である受信信号RXがハイレベルからロウレベルへと転じたことをもって境界エッジを検出することができる。このように、本実施形態では、レシーバ回路5は、エッジ検出回路としての機能を有する。

10

#### 【0024】

<ドライバ回路の具体的な構成について>

図4に示すように、ドライバ回路4は、前述したバス調停が可能となるように、オープンドレイン出力の回路構成となっており、その出力段を構成するトランジスタQ1、ダイオードD1、D2、抵抗R1および駆動回路9を備えている。ドライバ回路4において、バス3にはダイオードD1のカソードが接続されている。ダイオードD1のアノードは、プルアップ用の抵抗R1を介して電源電圧Vaが供給される電源線L1に接続されている。電源電圧Vaは、車両に搭載されるバッテリーの電源+Bから生成される+B系の電源電圧である。

20

#### 【0025】

トランジスタQ1は、Nチャネル型のMOSトランジスタであり、そのドレインはダイオードD2を逆方向に介してバス3に接続されている。トランジスタQ1のソースは、回路の基準電位(0V)となるグランドに接続されている。トランジスタQ1は、オンすることによりバス3の信号レベルをロウレベル(0V)とすることができるスイッチング素子として機能する。

#### 【0026】

駆動回路9は、制御回路6から与えられる送信信号TXに基づいてトランジスタQ1を駆動する。言い換えると、駆動回路9の動作は、制御回路6により制御される。駆動回路9は、トランジスタQ2～Q5、ダイオードD3、電流源10～12、コンデンサC1、C2、抵抗R2およびゲートドライバ13を備えている。トランジスタQ2は、Nチャネル型のMOSトランジスタであり、そのゲートには送信信号TXが与えられている。トランジスタQ2のソースはグランドに接続され、そのドレインはノードN1に接続されている。

30

#### 【0027】

トランジスタQ3は、Nチャネル型のMOSトランジスタであり、そのソースはダイオードD3を順方向に介してグランドに接続されている。トランジスタQ3は、いわゆるダイオード接続されており、そのゲートおよびドレインは、共通接続されるとともにノードN1に接続されている。電流源10は、電源電圧Vbが供給される電源線L2とノードN1との間に接続されている。

40

#### 【0028】

電源電圧Vbは、例えば5V電源系など+B系の電源電圧とは別系統の電源電圧である。なお、電源電圧Vbは、+B系の電源電圧であってもよい。トランジスタQ4は、NPN形のバイポーラトランジスタであり、そのベースはノードN1に接続されている。トランジスタQ4のコレクタは電源線L2に接続され、そのエミッタはノードN2に接続されている。トランジスタQ5は、Pチャネル型のMOSトランジスタであり、そのゲートには送信信号TXが与えられている。

#### 【0029】

トランジスタQ5のソースは電源線L2に接続され、そのドレインは電流源11を介し

50

てノードN2に接続されている。電流源12は、ノードN2とグランドとの間に接続されている。本実施形態では、電流源11は、電流源12に対して例えば2倍の電流を出力するようになっている。すなわち、電流源11の電流値I1と、電流源12の電流値I2とは、例えば下記(1)式に示す関係となっている。

$$I_1 = 2 \times I_2 \dots (1)$$

#### 【0030】

コンデンサC1の一方の端子は、抵抗R2を介してダイオードD1のアノードに接続されている。コンデンサC1の他方の端子は、ノードN2に接続されている。コンデンサC2は、ノードN2とグランドとの間に接続されている。この場合、コンデンサC1、C2は、静電容量値が互いに同一のものが用いられている。ゲートドライバ13は、単なるバッファとして機能するものであり、その入力端子はノードN2に接続されており、その出力端子はトランジスタQ1のゲートに接続されている。この場合、トランジスタQ1のゲートがスイッチング素子の制御端子に相当し、ゲート電圧が制御電圧に相当する。

10

#### 【0031】

制御回路6から出力される送信信号TXは、2値の信号であり、ハイレベルのときにはトランジスタQ1のオフ駆動を指令するオフ指令となり、ロウレベルのときにはトランジスタQ1のオン駆動を指令するオン指令となる。この場合、送信信号TXのハイレベルは、トランジスタQ2をオンするとともにトランジスタQ5をオフすることができる電圧値であり、例えば電源電圧Vbと同等の電圧値となっている。また、送信信号TXのロウレベルは、トランジスタQ2をオフするとともにトランジスタQ5をオンすることができる電圧値であり、例えば0Vとなっている。

20

#### 【0032】

##### <遅延短縮部について>

CXP1通信では、マスター2mは、常にレセシプ符号を出力しており、これが前述したクロックとなる。スレーブ2sは、このクロックに同期して動作する。具体的には、スレーブ2sは、レシーバ回路5により前述したようにして境界エッジが検出されたタイミング、つまりクロックの立ち下がりエッジが検出されたタイミングに同期して動作する。スレーブ2sでは、制御回路6は、境界エッジが検出されると、駆動回路9に対してロウレベルの送信信号TXを与える。そして、駆動回路9は、ロウレベルの送信信号TXが与えられるとトランジスタQ1をオン駆動する。

30

#### 【0033】

ただし、上記構成では、バス3上の信号レベルがハイレベルからロウレベルに変化したタイミング、つまりクロックの立ち下がりタイミングである境界エッジからトランジスタQ1のゲート電圧が閾値電圧Vt(Q1)に達してトランジスタQ1がオンする時点までに要する時間である遅延時間が存在する。この遅延時間は、フィルタ回路7での遅延、コンパレータ8での遅延、制御回路6におけるロジック遅延およびドライバ回路4の回路動作に伴う遅延などにより定まる時間となる。このような遅延時間は、CXP1の通信プロトコルにより規定された時間(例えば0.11Tbit)を満足する必要がある。なお、1Tbitは、バスのボーレート周期である。

40

#### 【0034】

上記構成では、レシーバ回路5の前段にノイズ除去用のフィルタ回路7が挿入されており、このようなフィルタ回路が設けられていない構成に比べて遅延時間が長くなる。そこで、本実施形態の通信装置2には、このような遅延時間を短縮するための遅延短縮部14が設けられている。この場合、駆動回路9のトランジスタQ2、Q3、Q4、ダイオードD3および電流源10により、遅延短縮部14が構成されている。つまり、本実施形態では、遅延短縮部14は、駆動回路9に設けられている。

40

#### 【0035】

また、この場合、トランジスタQ3は、その閾値電圧Vt(Q3)が、トランジスタQ1がオンに転じる閾値電圧Vt(Q1)に対して所定値だけ低いものが用いられている。すなわち、閾値電圧Vt(Q3)と閾値電圧Vt(Q1)との関係は、下記(2)式に

50

より表される。

$$V_t(Q_3) = V_t(Q_1) - \dots \quad (2)$$

#### 【0036】

詳細は後述するが、遅延短縮部14は、駆動回路9がトランジスタQ1をオン駆動するオン期間の開始時点を含む期間に、トランジスタQ1のゲート電圧が、閾値電圧 $V_t(Q_1)$ よりも所定値だけ低い閾値電圧 $V_t(Q_3)$ まで上昇するように電圧制御を行うことで遅延時間を短縮するようになっている。なお、この場合、閾値電圧 $V_t(Q_3)$ が第1電圧 $V_1$ に相当する。また、このような遅延短縮部14が設けられた駆動回路9は、上記した電圧制御が行われることによりトランジスタQ1のゲート電圧が閾値電圧 $V_t(Q_3)$ まで上昇した後、トランジスタQ1のゲートに一定の電流を供給する定電流制御を行うようになっている。10

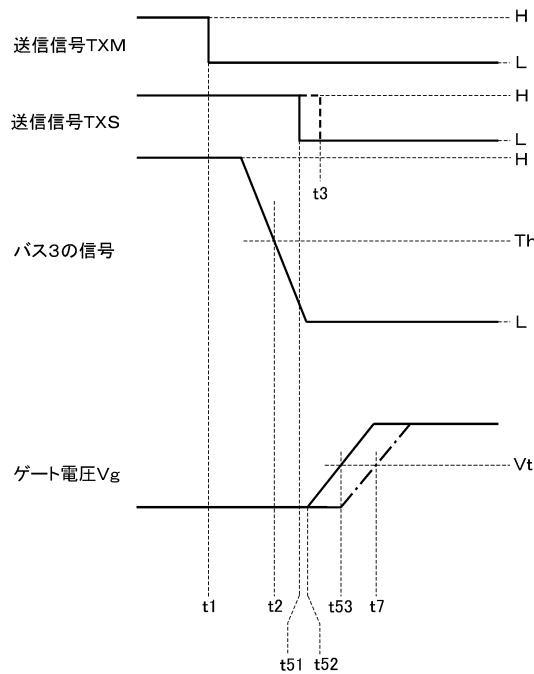

#### 【0037】

次に、上記構成の作用について図5のタイミングチャートに基づいて説明する。なお、図5などでは、マスター2mにおける送信信号TXを送信信号TXMと称し、スレーブ2sにおける送信信号TXを送信信号TXSと称し、トランジスタQ1のゲート電圧をVgと称し、トランジスタQ1の閾値電圧 $V_t(Q_1)$ を $V_t$ と称している。また、図5などのタイミングチャートでは、2値の信号について、ロウレベルを「L」と称し、ハイレベルを「H」と称している。

#### 【0038】

この場合、送信信号TXMがハイレベルからロウレベルに転じる時点t1がクロックの立ち下がりであり、境界エッジに相当する。時点t1以前の期間、送信信号TXSはハイレベルとなっている。このような期間、駆動回路9は、トランジスタQ1をオフ駆動する。駆動回路9がトランジスタQ1をオフ駆動するオフ期間における各部の動作は、次のようなものとなる。20

#### 【0039】

すなわち、送信信号TXSがハイレベルであることから、トランジスタQ2がオンするとともにトランジスタQ5がオフする。トランジスタQ5がオフすることから、電流源12の電流によりトランジスタQ1のゲート・ソース間容量が放電されることでゲート電圧Vgが低下してトランジスタQ1がオフする。そのため、時点t1以前の期間、バス3の信号レベルはハイレベルに維持されている。また、トランジスタQ2がオンすることから、トランジスタQ3、Q4がオフする。そのため、遅延短縮部14は、ノードN2の電圧VN2ひいてはトランジスタQ1のゲート電圧Vgに何ら影響を及ぼさない。30

#### 【0040】

時点t1において送信信号TXMがロウレベルに転じた後、バス3の信号レベルが低下して閾値Thに達した時点t2において、レシーバ回路5により境界エッジが検出される。なお、時点t1から時点t2までの時間には、マスター2m側での信号出力に関する遅延、フィルタ回路7およびコンパレータ8による遅延時間などが含まれる。このように境界エッジが検出されると、制御回路6は、送信信号TXSをハイレベルからロウレベルに転じさせる。なお、時点t2から送信信号TXSがロウレベルに転じる時点t3までの時間には、制御回路6によるロジック遅延などが含まれる。40

#### 【0041】

時点t3以降の期間、送信信号TXSはロウレベルとなる。このような期間、駆動回路9は、トランジスタQ1をオン駆動する。駆動回路9がトランジスタQ1をオン駆動するオン期間における各部の動作は、次のようなものとなる。すなわち、送信信号TXSがロウレベルであることから、トランジスタQ2がオフするとともにトランジスタQ5がオンする。トランジスタQ2がオフすることから、トランジスタQ3、Q4がオンする。トランジスタQ3がオンすることから、電源線L2から電流源10、トランジスタQ3およびダイオードD3を介してグランドへと電流が流れれる。

これにより、ノードN1の電圧VN1は、下記(3)式により表される電圧となる。ただし、ダイオードD3の順方向電圧をVfとする。

10

20

30

40

50

$$V_N 1 = V_t (Q_3) + V_f \quad \dots (3)$$

#### 【0042】

また、トランジスタQ4がオンすることから、トランジスタQ4のエミッタ電圧、つまりノードN2の電圧VN2は、下記(4)式により表される電圧となる。ただし、トランジスタQ4のベース・エミッタ間電圧Vbeが、ダイオードD3の順方向電圧Vfと同程度の電圧であるものとする。

$$V_N 2 = V_t (Q_3) = V_t (Q_1) - \dots (4)$$

#### 【0043】

上記構成では、トランジスタQ1のゲート電圧Vgは、電圧VN2と同等の電圧となる。そのため、トランジスタQ1のゲート電圧Vgは、時点t3から僅かな時間が経過した時点t4において、0Vから「Vt-」へと急峻に上昇する。なお、時点t3から時点t4までの時間には、各トランジスタの動作に伴う遅延時間などが含まれる。10

#### 【0044】

この場合、トランジスタQ5がオンしていることから、トランジスタQ1のゲートに向けて、電流源11の出力電流と電流源12の出力電流との差に相当する電流値I2の電流が供給されることになる。そのため、上述した電圧制御が行われることによりトランジスタQ1のゲート電圧Vgが「Vt-」まで上昇した後、トランジスタQ1のゲートに対して一定の電流が供給される定電流制御が行われる。

#### 【0045】

このような定電流制御が行われることにより、トランジスタQ1のゲート電圧Vgは、時点t4から僅かな時間が経過した時点t5から一定の傾きで比較的緩やかに上昇する。このときのゲート電圧Vgの上昇の傾きは、電流源11、12の各電流値I1、I2およびコンデンサC1、C2の静電容量値などにより定まる。そして、トランジスタQ1のゲート電圧Vgが閾値電圧Vtに達した時点t6において、トランジスタQ1がオンする。20

#### 【0046】

以上説明した本実施形態によれば、次のような効果が得られる。

本実施形態の通信装置2は、境界エッジからトランジスタQ1がオンする時点までに要する遅延時間を短縮する遅延短縮部14を備えている。このような構成によれば、遅延時間を短縮することが可能となり、本実施形態の構成のようにレシーバ回路5の前段にフィルタ回路7を挿入するような場合であっても、通信プロトコルを十分に満足することができる。30

#### 【0047】

この場合、遅延短縮部14は、ドライバ回路4の駆動回路9に設けられたものであり、駆動回路9がトランジスタQ1をオン駆動するオン期間の開始時点を含む期間に、トランジスタQ1のゲート電圧が、閾値電圧Vtよりも所定値だけ低い第1電圧V1まで上昇するように電圧制御を行うことで遅延時間を短縮する。以下、このような本実施形態による遅延時間の短縮効果について、トランジスタQ1をオン期間を通じて定電流駆動によりオン駆動するような従来構成に相当する比較例と比較しながら説明する。

#### 【0048】

比較例では、図5に一点鎖線で示すように、トランジスタQ1のゲート電圧は、本実施形態においてゲート電圧が上昇を開始する時点t4よりも後の時点t6付近から一定の傾きで比較的緩やかに上昇する。このように、比較例では、トランジスタQ1のゲート電圧が、オン期間を通じて一定の傾きで比較的緩やかに上昇するため、ゲート電圧が閾値電圧Vtに達してトランジスタQ1がオンに転じるまでには、比較的長い時間を要することになる。40

#### 【0049】

そのため、比較例では、駆動回路9の動作に起因する遅延時間は、時点t1から時点t7までの時間となり、本実施形態における遅延時間である時点t1から時点t6までの時間に比べて長い時間となる。これに対し、本実施形態では、前述した電圧制御が行われることにより、トランジスタQ1のゲート電圧は、オン期間の開始時点を含む期間に第1電

圧  $V_1$  まで比較的急峻に一度に上昇する。

#### 【 0 0 5 0 】

そして、本実施形態では、このような電圧制御を行うことによりゲート電圧が第 1 電圧  $V_1$  まで上昇した後は、定電流制御が行われることにより、ゲート電圧が閾値電圧  $V_t$  に達してトランジスタ Q 1 がオンに転じる。このような本実施形態によれば、比較例に比べ、少なくともトランジスタ Q 1 のゲート電圧が第 1 電圧  $V_1$  まで一度に上昇される分だけ、トランジスタ Q 1 のターンオン時間、つまり駆動回路 9 の動作に起因する遅延時間が短縮される。

#### 【 0 0 5 1 】

また、本実施形態の駆動回路 9 は、上述したように電圧制御を行うことによりトランジスタ Q 1 のゲート電圧が第 1 電圧  $V_1$  まで上昇した後、トランジスタ Q 1 のゲートに一定の電流を供給する定電流制御を行う。このような構成によれば、トランジスタ Q 1 のゲート電圧は、第 1 電圧  $V_1$  まで上昇した後は、一定の傾きで比較的緩やかに上昇して閾値電圧  $V_t$  に達することになる。ゲート電圧が急峻に上昇して閾値電圧  $V_t$  に達してトランジスタ Q 1 がオンされると、そのオン動作に伴うエミッഷンの悪化が懸念される。しかし、上記構成によれば、ゲート電圧が比較的緩やかに上昇して閾値電圧  $V_t$  に達してトランジスタ Q 1 がオンされる。そのため、本実施形態によれば、駆動回路 9 の動作に起因する遅延時間を短縮しつつ、このようなエミッഷン悪化のリスクを軽減することができる。

10

#### 【 0 0 5 2 】

##### ( 第 2 実施形態 )

20

以下、第 1 実施形態に対しドライバ回路の具体的な構成が変更された第 2 実施形態について図 6 を参照して説明する。

第 1 実施形態の遅延短縮部 1 4 は、ノード N 2、つまりゲートドライバ 1 3 の入力端子の電圧を制御することにより、トランジスタ Q 1 のゲート電圧を間接的に制御する構成となっていた。しかし、遅延短縮部は、トランジスタ Q 1 のゲート電圧を直接的に制御する構成であってもよい。

#### 【 0 0 5 3 】

そこで、本実施形態のドライバ回路 2 1 は、図 6 に示すような構成となっている。すなわち、本実施形態のドライバ回路 2 1 は、図 4 に示した第 1 実施形態のドライバ回路 4 に対し、駆動回路 9 に代えて駆動回路 2 2 を備えている点などが異なる。駆動回路 2 2 は、駆動回路 9 と同様の構成を備えているが、トランジスタ Q 4 のエミッタの接続先が異なっている。

30

#### 【 0 0 5 4 】

すなわち、トランジスタ Q 4 のエミッタは、ノード N 2 ではなく、ゲートドライバ 1 3 の出力端子、つまりトランジスタ Q 1 のゲートに接続されている。この場合、駆動回路 2 2 のトランジスタ Q 2、Q 3、Q 4、ダイオード D 3 および電流源 1 0 により、遅延短縮部 2 3 が構成されている。このように、本実施形態の遅延短縮部 2 3 は、トランジスタ Q 1 のゲート電圧を直接的に制御する構成となっている。

#### 【 0 0 5 5 】

以上説明した本実施形態の構成によっても、第 1 実施形態と同様、駆動回路 2 2 がトランジスタ Q 1 をオン駆動するオン期間の開始時点を含む期間に、トランジスタ Q 1 のゲート電圧が、閾値電圧  $V_t$  ( Q 1 ) よりも所定値だけ低い閾値電圧  $V_t$  ( Q 3 ) まで上昇するように電圧制御を行うことが可能となる。したがって、本実施形態によっても、第 1 実施形態と同様に遅延時間を短縮することができる。

40

#### 【 0 0 5 6 】

##### ( 第 3 実施形態 )

以下、第 1 実施形態に対しドライバ回路の具体的な構成が変更された第 3 実施形態について図 7 および図 8 を参照して説明する。

図 7 に示すように、本実施形態のドライバ回路 3 1 は、図 4 に示した第 1 実施形態のドライバ回路 4 に対し、ダイオード D 2 1 が追加されている点、駆動回路 9 に代えて駆動回

50

路 3 2 を備えている点などが異なる。

【 0 0 5 7 】

ダイオード D 2 1 のアノードはバス 3 に接続され、そのカソードはダイオード D 2 のアノードに接続されている。つまり、この場合、トランジスタ Q 1 のドレインは、2 つのダイオード D 2 および D 2 1 をいずれも逆方向に介してバス 3 に接続されている。なお、このようなダイオード D 2 1 は、スレーブ 2 s にだけ設けられており、マスター 2 m には設けられていないものとする。つまり、マスター 2 m において、トランジスタ Q 1 のドレインは、第 1 実施形態のドライバ回路 4 と同様、1 つのダイオード D 2 を逆方向に介してバス 3 に接続されているものとする。

【 0 0 5 8 】

駆動回路 3 2 は、駆動回路 9 に対し、トランジスタ Q 2 ~ Q 5 、電流源 1 0 、 1 1 およびダイオード D 3 に代えて、スイッチ S 2 1 、フィルタ回路 3 3 およびダイオード D 2 2 、 D 2 3 を備えている点などが異なっている。スイッチ S 2 1 は、電源線 L 2 とノード N 2 との間を開閉するものであり、そのオンオフは送信信号 T X の反転信号である送信信号 T X バーにより制御される。

【 0 0 5 9 】

なお、図 7 では、送信信号 T X バーについて、 T X の上に「 - 」を付して示している。スイッチ S 2 1 は、送信信号 T X バーがハイレベルのときにオンされるとともに、送信信号 T X バーがロウレベルのときにオフされる。この場合、スイッチ S 2 1 の一方の端子は電源線 L 2 に接続され、その他方の端子はフィルタ回路 3 3 の入力端子に接続されている。フィルタ回路 3 3 は、例えば抵抗およびコンデンサからなる C R フィルタなどである。

【 0 0 6 0 】

フィルタ回路 3 3 の出力端子は、ダイオード D 2 2 および D 2 3 をいずれも順方向に介してノード N 2 に接続されている。なお、スイッチ S 2 1 は、例えば M O S トランジスタなどの半導体スイッチング素子を用いて構成することができる。

【 0 0 6 1 】

本実施形態では、スイッチ S 2 1 、フィルタ回路 3 3 およびダイオード D 2 2 、 D 2 3 により遅延短縮部 3 4 が構成されている。つまり、遅延短縮部 3 4 は、駆動回路 3 2 に設けられている。この場合、電源電圧 V b は、トランジスタ Q 1 の閾値電圧 V t よりも十分に高い電圧となっている。遅延短縮部 3 4 が設けられた駆動回路 3 2 は、トランジスタ Q 1 のゲート電圧が閾値電圧 V t よりも高い第 2 電圧 V 2 まで上昇するように電圧制御を行う。なお、第 2 電圧 V 2 は、電源電圧 V b からダイオード D 2 2 、 D 2 3 の各順方向電圧を加算した電圧 ( = 2 · V f ) を減算した電圧に相当する。

【 0 0 6 2 】

言い換えると、遅延短縮部 3 4 が設けられた駆動回路 3 2 は、遅延短縮部 1 4 と同様に電圧制御が行われることによりトランジスタ Q 1 のゲート電圧が第 1 電圧 V 1 に相当する「 V t - 」まで上昇した後も、ゲート電圧が閾値電圧 V t よりも高い第 2 電圧 V 2 まで上昇するように電圧制御を継続するようになっている。この場合、遅延短縮部 3 4 には、トランジスタ Q 1 のゲートに対する第 2 電圧 V 2 の供給経路に直列に介在するフィルタ回路 3 3 が含まれている。

【 0 0 6 3 】

次に、上記構成の作用について図 8 のタイミングチャートに基づいて説明する。

この場合、駆動回路 3 2 がトランジスタ Q 1 をオフ駆動するオフ期間における各部の動作は、次のようなものとなる。すなわち、送信信号 T X S がハイレベルであることから、スイッチ S 2 1 がオフする。これにより、電流源 1 2 の電流によりトランジスタ Q 1 のゲート・ソース間容量が放電されることでゲート電圧 V g が低下してトランジスタ Q 1 がオフする。

【 0 0 6 4 】

また、この場合、駆動回路 3 2 がトランジスタ Q 1 をオン駆動するオン期間における各部の動作は、次のようなものとなる。すなわち、送信信号 T X S がロウレベルであること

10

20

30

40

50

から、スイッチ S 2 1 がオンする。スイッチ S 2 1 がオンしていることから、ノード N 2 、ひいてはトランジスタ Q 1 のゲートに対して第 2 電圧 V 2 が供給される。

#### 【 0 0 6 5 】

これにより、ノード N 2 の電圧 V N 2 、ひいてはトランジスタ Q 1 のゲート電圧 V g は、送信信号 T X S がロウレベルに転じた時点 t 3 から僅かな時間が経過した時点 t 3 1 から比較的急峻な傾きで、0 V から第 2 電圧 V 2 に向けて上昇する。ただし、この場合、トランジスタ Q 1 のゲートに対する第 2 電圧 V 2 の供給経路にはフィルタ回路 3 3 が直列に介在している。そのため、トランジスタ Q 1 のゲート電圧 V g の波形は、フィルタ回路 3 3 の作用により若干鈍った波形となる。そして、トランジスタ Q 1 のゲート電圧 V g が閾値電圧 V t に達した時点 t 3 2 において、トランジスタ Q 1 がオンする。

10

#### 【 0 0 6 6 】

以上説明した本実施形態によっても、境界エッジからトランジスタ Q 1 がオンする時点までに要する遅延時間を短縮する遅延短縮部 3 4 を備えているため、第 1 実施形態と同様の効果が得られる。さらに、この場合、遅延短縮部 3 4 は、トランジスタ Q 1 をオン駆動するオン期間を通じてトランジスタ Q 1 のゲート電圧が閾値電圧 V t よりも高い第 2 電圧 V 2 まで上昇するように電圧制御を行うようになっている。そのため、本実施形態によれば、比較例はもちろん、第 1 実施形態に比べて、駆動回路 3 2 の動作に起因する遅延時間を短縮することができる。

#### 【 0 0 6 7 】

このようにオン期間を通じて電圧制御を行う構成では、第 1 実施形態の構成に比べ、閾値電圧 V t に達する際のゲート電圧の上昇の傾きが急峻なものとなるため、エミッション悪化の懸念がある。しかし、この場合、トランジスタ Q 1 のゲートに対する第 2 電圧 V 2 の供給経路に直列に介在するフィルタ回路 3 3 の作用により、トランジスタ Q 1 のゲート電圧の波形が若干鈍った波形となっている。そのため、本実施形態では、閾値電圧 V t に達する際のゲート電圧の上昇の傾きが若干緩やかなものとなり、エミッション悪化のリスクが軽減されるようになっている。

20

#### 【 0 0 6 8 】

本実施形態のドライバ回路 3 1 では、その出力段のトランジスタ Q 1 のゲート電圧が比較的急峻に上昇し、トランジスタ Q 1 が比較的急峻にターンオンする。そのため、マスター 2 m からバス 3 を通じてスレーブ 2 s へと電流が引き込まれるおそれがある。具体的には、マスター 2 m の電源電圧 V a が供給される電源線 L 1 から抵抗 R 1 、ダイオード D 1 およびバス 3 を介してスレーブ 2 s へと電流が引き込まれるおそれがある。このような電流は、エミッションの悪化に繋がる。

30

#### 【 0 0 6 9 】

ただし、本実施形態のドライバ回路 3 1 、つまり本実施形態のスレーブ 2 s のドライバ回路 3 1 では、その出力段のトランジスタ Q 1 のドレンは、2 つのダイオード D 2 および D 2 1 を逆方向に介してバス 3 に接続されている。一方、マスター 2 m のドライバ回路では、その出力段のトランジスタ Q 1 のドレンは、1 つのダイオード D 2 を逆方向に介してバス 3 に接続されている。そのため、スレーブ 2 s の出力端子のほうが、マスター 2 m の出力端子よりも、ダイオード D 2 1 の順方向電圧 V f だけ電圧が高くなる。

40

#### 【 0 0 7 0 】

したがって、スレーブ 2 s のドライバ回路 3 1 のトランジスタ Q 1 が急峻にオンに転じても、マスター 2 m の電源線 L 1 からの電流は、スレーブ 2 s 側へ流れ込むことはなく、マスター 2 m の出力段のトランジスタ Q 1 を介してグランドへと流れる。このように、本実施形態によれば、マスター 2 m からスレーブ 2 s へと電流が引き込まれる可能性が低く抑えられるため、それによるエミッション悪化のリスクが軽減される。

#### 【 0 0 7 1 】

なお、第 1 実施形態の構成では、本実施形態の構成に比べ、トランジスタ Q 1 のゲート電圧が比較的緩やかに上昇し、トランジスタ Q 1 が比較的緩やかにターンオンするようになっているため、マスター 2 m からスレーブ 2 s へと電流が引き込まれる可能性は低い。

50

しかし、第1実施形態の構成についても、本実施形態の構成と同様、トランジスタQ1のドレインを2つのダイオードD2およびD21を逆方向に介してバス3に接続するようすれば、マスター2mからスレーブ2sへと電流が引き込まれる可能性を一層低く抑え、それによるエミッション悪化のリスクを一層軽減することができる。

#### 【0072】

##### (第4実施形態)

以下、第4実施形態について図9および図10を参照して説明する。

図9に示すように、本実施形態の通信装置41は、第1実施形態の通信装置2に対し、レシーバ回路5に代えてレシーバ回路42を備えている点、制御回路6に代えて制御回路43を備えている点などが異なっている。レシーバ回路42は、図3に示したレシーバ回路5に対し、フィルタ回路7が省かれている点などが異なっている。この場合、コンパレータ8の非反転入力端子には、バス3の信号が直接与えられている。10

#### 【0073】

制御回路43は、判定部44およびノイズ検出部45としての機能を備えている。判定部44は、バス3の信号を所定のサンプリングタイミングにおいてサンプリングすることによりバス3を介して伝送される符号を判定する。ノイズ検出部45は、バス3の信号レベルを検出し、その検出結果に基づいてバス3に重畳するノイズを検出する。これら各機能は、具体的には、次のようにして実現されている。

#### 【0074】

すなわち、制御回路43は、コンパレータ8の出力信号である受信信号RXのレベルに基づいて加算または減算する加減算カウンタを含むデジタルフィルタ回路を備えている。この場合、加減算カウンタは、受信信号RXをデジタルフィルタ回路に含まれる2度一致フィルタを通過させることで得られる信号RX1がハイレベルであるときに加算を行い、信号RX1がロウレベルであるときに減算を行う。20

#### 【0075】

そのため、図10に示すように、加減算カウンタのカウント値cntは、信号RX1がハイレベルであるときに加算され、信号RX1がロウレベルであるときに減算される。制御回路43では、このような加減算カウンタのカウント値cntに基づいて、受信信号RXに応じた信号RX2が生成される。この場合、図10に示すように、信号RX2は、カウント値cntが下限値に達するとロウレベルに転じるとともに、カウント値cntが上限値に達するとハイレベルに転じる信号となっている。30

#### 【0076】

判定部44は、このようにして生成される信号RX2を所定のサンプリングタイミングにおいてサンプリングすることによりバス3を介して伝送される符号を判定する。この場合、信号RX2がロウレベルである期間をLo幅とすると、前回のLo幅に対してビットレートの6%に相当する所定の規定時間を加えた時間に応じて、今回のサンプリングタイミングが決定される。具体的には、今回の信号RX2の立ち下がり時点から、前回のLo幅に規定時間を加えた時間が経過した時点が、今回のサンプリングタイミングとなる。

#### 【0077】

上記した加減算カウンタは、バス3にノイズが重畳していない正常時には、一旦減算が開始されると、その後の所定期間は継続して減算が行われ、また、一旦加算が開始されると、その後の所定期間は継続して加算が行われる。しかし、バス3にノイズが重畳したことなどによりコンパレータ8の出力にチャタリングが生じて受信信号RXのレベルが変動する場合、加減算カウンタは加算および減算を繰り返し行うことになる。40

#### 【0078】

そうすると、図10に示すように、加減算カウンタのカウント値cntが増減する期間が生じることになる。ノイズ検出部45は、このような点を考慮し、加減算カウンタによる加算および減算が繰り返して行われると、バス3にノイズが重畳していると判断する。また、ノイズ検出部45は、加減算カウンタのカウント値cntが増減する期間TNf、TNrが、ノイズが検出された期間であるノイズ検出期間であると判定する。50

**【 0 0 7 9 】**

上記した L<sub>o</sub> 幅は、バス 3 にノイズが重畠していない正常時には、バス 3 の信号がロウレベルであるロウ期間を正確に表すものになるが、バス 3 にノイズが重畠すると、実際のロウ期間とは異なるものになるおそれがある。具体的には、ノイズの影響によりバス 3 の信号の立ち下がり付近に対応する受信信号 RX に変動が生じると、カウント値 c<sub>n</sub>t が下限値に達するまでの時間に遅延が生じ、その結果、信号 RX 2 の L<sub>o</sub> 幅が実際のロウ期間よりも短くなる。また、ノイズの影響によりバス 3 の信号の立ち上がり付近に対応する受信信号 RX に変動が生じると、カウント値 c<sub>n</sub>t が上限値に達するまでの時間に遅延が生じ、その結果、信号 RX 2 の L<sub>o</sub> 幅が実際のロウ期間よりも長くなる。

**【 0 0 8 0 】**

例えば、前回の L<sub>o</sub> 幅がノイズの影響を受けて実際のロウ期間よりも短くなり、且つ、今回の L<sub>o</sub> 幅が実際のロウ期間を正確に表すものになった場合、次のような問題が生じるおそれがある。なお、以下では、このような場合のことを第 1 ケースと称する。第 1 ケースにおいて、今回のサンプリングタイミングは、実際のロウ期間よりも短い前回の L<sub>o</sub> 幅に基づいて決定されるが、今回の L<sub>o</sub> 幅は実際のロウ期間を正確に表すものになっている。そのため、第 1 ケースにおいて、今回のサンプリングタイミングは、本来あるべきタイミングよりも前倒しされたタイミングとなり、その結果、バス 3 の信号がハイレベルであるにもかかわらず、ロウレベルであると誤判定されるおそれがある。

**【 0 0 8 1 】**

また、例えば、前回の L<sub>o</sub> 幅が実際のロウ期間を正確に表すものであり、且つ、今回の L<sub>o</sub> 幅がノイズの影響を受けて実際のロウ期間よりも長くなった場合、次のような問題が生じる。なお、以下では、このような場合のことを第 2 ケースと称する。第 2 ケースにおいて、今回のサンプリングタイミングは、実際のロウ期間を正確に表す前回の L<sub>o</sub> 幅に基づいて決定されるが、今回の L<sub>o</sub> 幅は実際のロウ期間よりも長くなっている。そのため、バス 3 の信号がハイレベルであるにもかかわらず、ロウレベルであると誤判定されるおそれがある。

**【 0 0 8 2 】**

そこで、判定部 4 4 は、ノイズ検出部 4 5 によりノイズが検出されると、サンプリングタイミングをノイズが検出された期間に応じた所定時間だけ遅らせるようになっている。この場合、所定時間としては、上述した期間 TN<sub>f</sub> と期間 TN<sub>r</sub> とが加算された期間となる。このようにすれば、第 1 ケースおよび第 2 ケースのいずれにおいても、本来サンプリングすべきではないタイミングで信号 RX 2 をサンプリングすること、ひいては、バス 3 を介して伝送される符号の誤判定の発生を防止することができる。

**【 0 0 8 3 】**

本実施形態のように、レシーバ回路 4 2 にフィルタ回路 7 が設けられていない構成によれば、第 1 実施形態の構成などに比べ、境界エッジからトランジスタ Q 1 がオンする時点までに要する遅延時間が短縮されるというメリットがある。その一方で、ノイズ除去用のフィルタ回路 7 が設けられていない構成では、ノイズの影響による誤判定が発生する可能性が高まるというデメリットがある。しかし、本実施形態によれば、前述したようにしてノイズの影響による誤判定の発生が防止されるため、フィルタ回路 7 が設けられないことによるデメリットが生じることはなく、そのメリットだけを享受することができる。

**【 0 0 8 4 】****( 第 5 実施形態 )**

以下、第 1 実施形態に対しドライバ回路および制御回路の具体的な構成が変更された第 5 実施形態について図 1 1 ~ 図 1 3 を参照して説明する。

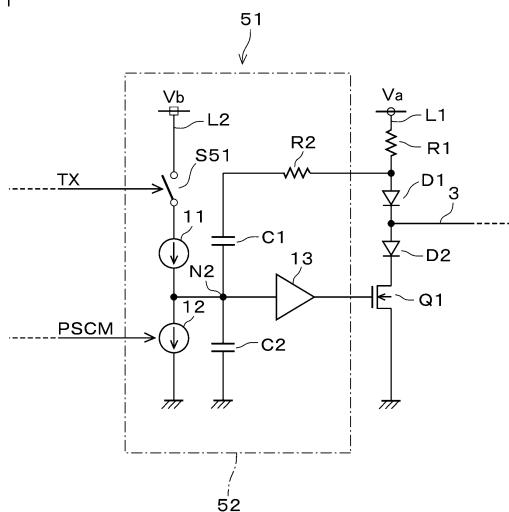

図 1 1 に示すように、本実施形態のドライバ回路 5 1 は、図 4 に示した第 1 実施形態のドライバ回路 4 に対し、駆動回路 9 に代えて駆動回路 5 2 を備えている点などが異なっている。

**【 0 0 8 5 】**

駆動回路 5 2 は、駆動回路 9 に対し、遅延短縮部 1 4 が省かれている点、トランジスタ

10

20

30

40

50

Q 5 に代えてスイッチ S 5 1 を備えている点などが異なっている。スイッチ S 5 1 の一方の端子は電源線 L 2 に接続され、その他方の端子は電流源 1 1 を介してノード N 2 に接続されている。スイッチ S 5 1 のオンオフは、送信信号 T X により制御される。スイッチ S 5 1 は、送信信号 T X がハイレベルのときにオフされるとともに、送信信号 T X がロウレベルのときにオンされる。

#### 【 0 0 8 6 】

スイッチ S 5 1 は、例えばM O S ロジックなどの半導体スイッチング素子を用いて構成することができる。この場合、電流源 1 2 は、その動作を停止することができる構成となっている。具体的には、電流源 1 2 は、後述するカット信号 P S C M がハイレベルである期間には動作を停止するとともに、カット信号 P S C M がロウレベルである期間には動作を実行するようになっている。

10

#### 【 0 0 8 7 】

図 1 2 に示すように、本実施形態の制御回路 5 3 は、学習制御部 5 4 、予測制御部 5 5 および先出し制御部 5 6 としての機能を備えている。学習制御部 5 4 は、エッジ検出回路として機能するレシーバ回路 5 による境界エッジの検出結果に基づいて境界エッジの周期を学習する学習制御を実行する。この場合、学習制御部 5 4 は、1 ビットレートを計測するハードウェアタイマカウンタであるカウンタ 5 4 a を備えている。カウンタ 5 4 a は、境界エッジが検出された時点から次に境界エッジが検出される時点までカウント動作を実行する。

20

#### 【 0 0 8 8 】

具体的には、カウンタ 5 4 a は、境界エッジが検出された時点でカウント動作を開始し、以降は、境界エッジが検出される時点毎にカウント値をクリアした後にカウント動作を再開する。学習制御部 5 4 は、カウンタ 5 4 a のカウント値に基づいて境界エッジの周期を学習する。すなわち、学習制御部 5 4 は、カウンタ 5 4 a がクリアされるときのカウント値を境界エッジの周期の学習値として毎回学習する。このような学習値は、ビットレートが一定であることから、一定の値を示すことになる。例えばビットレートが 2 0 k b p s であり且つカウンタ 5 4 a が 4 . 5 M H z のシステムクロックで動作する場合、学習値は「 2 2 5 」で一定となる。

#### 【 0 0 8 9 】

予測制御部 5 5 は、学習制御部 5 4 が学習制御を実行することにより学習された境界エッジの周期に基づいて、次回の境界エッジが検出されるタイミングを予測する予測制御を実行する。具体的には、予測制御部 5 5 は、学習制御により学習された学習値およびカウンタ 5 4 a の現在のカウント値に基づいて次回の境界エッジが検出されるタイミングを予測することができる。

30

#### 【 0 0 9 0 】

先出し制御部 5 6 は、予測制御部 5 5 が予測制御を実行することにより予測されたタイミングよりも前の時点において駆動回路 5 2 に対してオン指令、つまりロウレベルの送信信号 T X を与える先出し制御を実行する。具体的には、先出し制御部 5 6 は、カウンタ 5 4 a のカウント値が学習値に一致する時点よりも所定のクロック数だけ前の時点においてロウレベルの送信信号 T X の出力を開始する。

40

#### 【 0 0 9 1 】

例えばビットレートおよびシステムクロックが前述したような条件である場合、先出し制御部 5 6 は、カウンタ 5 4 a のカウント値が「 2 2 0 」でカウンタマッチしたときにロウレベルの送信信号 T X の出力を開始するようになっている。なお、上記所定のクロック数の設定、つまり予測されたタイミングよりもどれだけ前の時点において出力を開始するかの設定については、各種の仕様などに応じて適宜変更および調整することができる。

#### 【 0 0 9 2 】

詳細は後述するが、学習制御部 5 4 、予測制御部 5 5 および先出し制御部 5 6 により上述した各制御が実行されることにより、境界エッジからトランジスタ Q 1 がオンする時点までに要する遅延時間が短縮される。つまり、この場合、学習制御部 5 4 、予測制御部 5

50

5 および先出し制御部 5 6 により、遅延短縮部 5 7 が構成されている。このように、本実施形態では、遅延短縮部 5 7 は、制御回路 5 3 に設けられている。

#### 【 0 0 9 3 】

制御回路 5 3 は、前述したカット信号 P S C M を生成する。カット信号 P S C M は、先出し制御が実行されることによりロウレベルの送信信号 T X の出力が開始される時点から予測制御により予測された次の境界エッジが検出されるタイミングまでの期間である先出し期間においてハイレベルとなるとともに、その他の期間においてロウレベルとなる。

#### 【 0 0 9 4 】

次に、上記構成の作用について図 1 3 のタイミングチャートに基づいて説明する。

この場合、駆動回路 5 2 がトランジスタ Q 1 をオフ駆動するオフ期間における各部の動作は、次のようなものとなる。すなわち、送信信号 T X S がハイレベルであることから、スイッチ S 5 1 がオフする。これにより、電流源 1 2 の電流によりトランジスタ Q 1 のゲート・ソース間容量が放電されることでゲート電圧 V g が低下してトランジスタ Q 1 がオフする。

#### 【 0 0 9 5 】

この場合、制御回路 5 3 は、前述した各制御を実行することにより、第 1 実施形態の制御回路 6 が送信信号 T X S をハイレベルからロウレベルに転じさせる時点 t 3 よりも前の時点 t 5 1 において、送信信号 T X S をハイレベルからロウレベルに転じさせる。時点 t 5 1 以降の期間、送信信号 T X S がロウレベルとなる。このような期間、駆動回路 5 2 は、トランジスタ Q 1 をオン駆動する。駆動回路 5 2 がトランジスタ Q 1 をオン駆動するオン期間における各部の動作は、次のようなものとなる。

#### 【 0 0 9 6 】

すなわち、送信信号 T X S がロウレベルであることから、スイッチ S 5 1 がオンする。また、時点 t 5 1 から時点 t 3 の先出し期間には、カット信号 P S C M がハイレベルとなる。そのため、先出し期間、電流源 1 1 の出力電流は、コンデンサ C 1、C 2 のそれぞれを充電するように分岐して流れる。その後、時点 t 3 においてカット信号 P S C M がロウレベルに転じると、トランジスタ Q 1 のゲートに向けて、電流源 1 1 の出力電流と電流源 1 2 の出力電流との差に相当する電流値 I 2 の電流が供給されることになる。

#### 【 0 0 9 7 】

このような定電流制御が行われることにより、トランジスタ Q 1 のゲート電圧 V g は、時点 t 5 1 から僅かな時間が経過した時点 t 5 2 から一定の傾きで比較的緩やかに上昇する。このときのゲート電圧 V g の上昇の傾きは、電流源 1 1、1 2 の各電流値 I 1、I 2 およびコンデンサ C 1、C 2 の静電容量値などにより定まる。そして、トランジスタ Q 1 のゲート電圧 V g が閾値電圧 V t に達した時点 t 5 3 において、トランジスタ Q 1 がオンする。

#### 【 0 0 9 8 】

以上説明した本実施形態によっても、境界エッジからトランジスタ Q 1 がオンする時点までに要する遅延時間を短縮する遅延短縮部 5 7 を備えているため、第 1 実施形態と同様の効果が得られる。この場合、制御回路 5 3 に設けられた遅延短縮部 5 7 が、各種の制御を実行することにより、送信信号 T X を従来構成に相当する比較例よりも前倒ししたタイミングでロウレベルに切り替えるようになっている。そのため、本実施形態によれば、送信信号 T X を前倒しするタイミングの設定によって、駆動回路 5 2 の動作に起因する遅延時間だけでなく、制御回路 5 3 におけるロジック遅延、フィルタ回路 7 での遅延、コンパレータ 8 での遅延なども含めた総合的な遅延時間を大幅に短縮することが可能となる。

#### 【 0 0 9 9 】

本実施形態の駆動回路 5 2 は、第 1 実施形態において説明した比較例と同様、トランジスタ Q 1 をオン期間を通じて定電流駆動によりオン駆動する構成となっている。そのため、本実施形態では、ゲート電圧が比較的緩やかに上昇して閾値電圧 V t に達してトランジスタ Q 1 がオンされる。したがって、本実施形態によれば、トランジスタ Q 1 のオン動作に伴うエミッション悪化のリスクを軽減することができる。

10

20

30

40

50

**【0100】****(第6実施形態)**

以下、第6実施形態について図14を参照して説明する。

第5実施形態の構成では、制御回路53は、バス3の信号が変化したことをトリガとしてロウレベルの送信信号TXSの出力を開始するのではなく、学習された境界エッジの周期の学習値に基づいてロウレベルの送信信号TXSの出力を前倒しして開始するようになっており、バス3の信号の変化を待つことはない。つまり、制御回路53は、たとえマスター2mからクロックが出力されていなくとも、ドミナント符号を出力する場合には、ロウレベルの送信信号TXSの出力を開始するようになっている。

**【0101】**

10

このようなことから、第5実施形態の構成では、次のような問題が生じる可能性がある。すなわち、マスター2m側にて何らかの異常が生じたことによりクロックの供給が停止されてバス3がハイレベルに固着する場合、制御回路53は、学習値に基づいてロウレベルの送信信号TXSの出力をを行う、つまりバス3の信号レベルを変化させ、たかも、マスター2mからのクロックが供給されているかのような振る舞いを見せる可能性がある。したがって、第5実施形態の構成では、バス3がハイレベルに固着していたとしても、スレーブ2sは、連続でドミナント符号を出力する場合には自走してしまうおそれがあった。なお、以下では、バス3がハイレベルに固着することをHi固着と称する。

**【0102】**

20

そこで、本実施形態では、制御回路53の制御内容に次のような変更を加えることにより、このような問題の発生を防止するようにしている。まず、CXP1通信では、UARTフレームをデコードしてバス3に信号を乗せるようになっている。UARTには、必ずストップビットが少なくとも1ビット含まれている。このようなことから、スレーブ2sの動作において、バス3に対して「論理値：1」に相当するレセシシブ符号を出力するタイミングが必ず含まれることになる。

**【0103】**

バス3がHi固着した状態においてスレーブ2sがストップビットに対応するレセシシブ符号を出力する際、境界エッジが比較的長期間にわたって検出されなくなることから、カウンタ54aのカウント値が境界エッジの周期として想定される値（例えば）「225」）に比べて非常に大きい値となる。そこで、制御回路53は、カウンタ54aのカウント値が境界エッジの周期として想定される値よりも大きい上限値（例えば「1024」）に達すると、学習制御による学習結果を一旦リセットして学習制御を再度実行するようになっている。

30

**【0104】**

そして、制御回路53は、学習制御による学習結果が得られるまでの期間は予測制御および先出し制御の実行を停止するようになっている。本実施形態では、制御回路53は、正しく学習値が得られた回数をカウントする再計測カウンタを備えており、その再計測カウンタのカウント値が「3」になるまでの期間、つまり学習値が3回得られるまでの期間、予測制御および先出し制御の実行を停止するようになっている。

**【0105】**

40

次に、マスター2m側の異常などに起因してバス3がHi固着した場合の動作について図14のタイミングチャートを参照して説明する。図14では、カウンタ54aのカウント値をcnt1とし、再計測カウンタのカウント値をcnt2としている。期間Taでは、スレーブ2sは、ドミナント符号を連続して出力する状態となっている。そのため、スレーブ2sは、マスター2mからクロックの供給が停止されているにもかかわらず、学習値に基づいてロウレベルの送信信号TXSの出力をを行う、つまりバス3の信号レベルを変化させている。このとき、スレーブ2sによってバス3の信号が、境界エッジの周期に近い周期でハイレベルからロウレベルに変化されるため、カウント値cnt1は、「230」、「235」などであり、境界エッジの周期として想定される値から大きく離れた値とはならない。

50

**【0106】**

期間 T<sub>b</sub> では、スレーブ 2 s は、例えばストップビットに対応するレセッシュップ符号を出力する状態となっている。そのため、カウンタ 5 4 a のカウント値 c<sub>n t 1</sub> が境界エッジの周期として想定される値を超えて上昇し、上限値「1 0 2 4」に達する。これにより、制御回路 5 3 は、学習制御による学習結果を一旦リセットして学習制御を再度実行するとともに、予測制御および先出し制御の実行を停止する。なお、図 1 4 では、このような動作状態のことをリセット動作（再計測中）と表している。このとき、再計測カウンタのカウント値が「0」にクリアされる。

**【0107】**

期間 T<sub>b</sub> の後の期間 T<sub>c</sub> の開始時点において、マスター 2 m 側の異常が解消されるなどしてバス 3 の H<sub>i</sub> 固着が解消されると、マスター 2 m からクロックの供給が再開される。これにより、学習制御により正常に学習値が得られ始め、学習値が 3 回得られた時点において、制御回路 5 3 は、予測制御および先出し制御の実行を再開する。これにより、スレーブ 2 s は、マスター 2 m からのクロックに同期して動作を行う正常の動作状態となる。なお、図 1 4 では、このような動作状態のことをリセット解除動作と表している。

10

**【0108】**

以上説明した本実施形態によれば、マスター 2 m 側の異常などに起因してバス 3 が H<sub>i</sub> 固着した場合であっても、制御回路 5 3 は、カウンタ 5 4 a のカウント値が上限値に達した時点でバス 3 が H<sub>i</sub> 固着していると判断して予測制御および先出し制御の実行を停止するため、スレーブ 2 s がマスター 2 m から供給されるクロックに同期せずに動作し続けるおそれがない。また、この場合、制御回路 5 3 は、バス 3 が H<sub>i</sub> 固着していると判断すると、学習値をリセットするとともに学習制御を再開し、再開した学習制御により学習値が正しく得られると、予測制御および先出し制御を再開するようになっている。そのため、スレーブ 2 s は、マスター 2 m 側の異常が解消されると、速やかに予測制御および先出し制御を再開することが可能となり、正常動作へと復帰することができる。

20

**【0109】**

（その他の実施形態）

なお、本発明は上記し且つ図面に記載した各実施形態に限定されるものではなく、その要旨を逸脱しない範囲で任意に変形、組み合わせ、あるいは拡張することができる。

上記各実施形態で示した数値などは例示であり、それに限定されるものではない。

30

**【0110】**

本発明は、上記各実施形態において例示した C X P I 通信を行う通信装置 2、4 1 に限らず、伝送路を介してデータを送受信する複数の通信装置のうちいずれか一つの通信装置の通信に同期して他の通信装置が送信を行う通信システムにおいて用いられる通信装置全般に適用することができる。

**【0111】**

ドライバ回路 4 などの出力段に設けられるスイッチング素子としては、トランジスタ Q 1 のような M O S トランジスタに限らずともよく、例えば、バイポーラトランジスタ、G a A s - M E S F E T など、各種の半導体スイッチング素子を用いることができる。

**【0112】**

本開示は、実施例に準拠して記述されたが、本開示は当該実施例や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。

40

**【符号の説明】****【0113】**

1 ... 通信システム、2、4 1 ... 通信装置、3 ... バス、4、2 1、3 1、5 1 ... ドライバ回路、5、4 2 ... レシーバ回路、6、4 3、5 3 ... 制御回路、9、2 2、3 2、5 2 ... 駆動回路、1 4、2 3、3 4、5 7 ... 遅延短縮部、3 3 ... フィルタ回路、4 4 ... 判定部、4 5 ... ノイズ検出部、5 4 a ... カウンタ、Q 1 ... スイッチング素子。

50

## 【図面】

## 【図1】

Fig.1

## 【図2】

Fig.2

10

20

## 【図3】

Fig.3

## 【図4】

Fig.4

30

40

50

【図 5】

Fig.5

【図 6】

Fig.6

【図 7】

Fig.7

【図 8】

Fig.8

【図9】

Fig.9

【図10】

Fig. 10

10

20

〔図 1 1 〕

Fig. 11

( 四 1 2 )

Fig.12

30

40

50

【図 1 3】

Fig.13

【図14】

14

---

フロントページの続き

- (56)参考文献

- 特開2004-241930(JP,A)

特開2018-007237(JP,A)

特開2017-041693(JP,A)

車載向けCXPIトランシーバ BD41000FJ-C, ROHM SEMICONDUCTOR

新商品速報, 2015年09月, [検索日:2020.11.06], インターネット<URL:[https://www.rohm.co.jp/documents/11401/3280383/58F6937J\\_CXPI-transceiver\\_ss\\_J.pdf](https://www.rohm.co.jp/documents/11401/3280383/58F6937J_CXPI-transceiver_ss_J.pdf)>

- (58)調査した分野 (Int.Cl., DB名)

- H04L 25/02

H03K 5/12

H03K 19/0175

IEEE Explore