(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 602 20 762 T2 2007.10.11

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 320 130 B1

(21) Deutsches Aktenzeichen: 602 20 762.2

(96) Europäisches Aktenzeichen: 02 252 913.5

(96) Europäischer Anmeldetag: 25.04.2002

(97) Erstveröffentlichung durch das EPA: 18.06.2003

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 20.06.2007

(47) Veröffentlichungstag im Patentblatt: 11.10.2007

(51) Int Cl.<sup>8</sup>: H01L 21/8238 (2006.01)

H01L 29/49 (2006.01)

(30) Unionspriorität:

**2001377623** 11.12.2001 JP

(84) Benannte Vertragsstaaten:

**DE, FR, GB, IT**

(73) Patentinhaber:

**Fujitsu Ltd., Kawasaki, Kanagawa, JP**

(72) Erfinder:

**Kumeno, Kazuyuki, Kawasaki-shi, Kanagawa

211-8588, JP**

(74) Vertreter:

**W. Seeger und Kollegen, 81369 München**

(54) Bezeichnung: Halbleiterbauelement und zugehöriges Herstellungsverfahren

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung betrifft ein Halbleiterbauelement und ein Herstellungsverfahren davon, und insbesondere ist die vorliegende Erfindung am Besten geeignet, wenn sie auf ein Halbleiterbauelement angewendet wird, das mit einer Gateelektrode versehen ist, die Silicid umfasst.

**[0002]** In einem System-LSI der letzten Jahre wird, um den Widerstand einer Verdrahtungsverbindung zwischen einer Polysilicium-Gateelektrode und einem Element zu verringern, eine Schichtstruktur aus Polysilicium und Silicid übernommen und wird eine Doppelstruktur, in welcher ein Gate eines NMOS-Transistors ein n-Typ ist und ein Gate eines PMOS-Transistors ein p-Typ ist, übernommen.

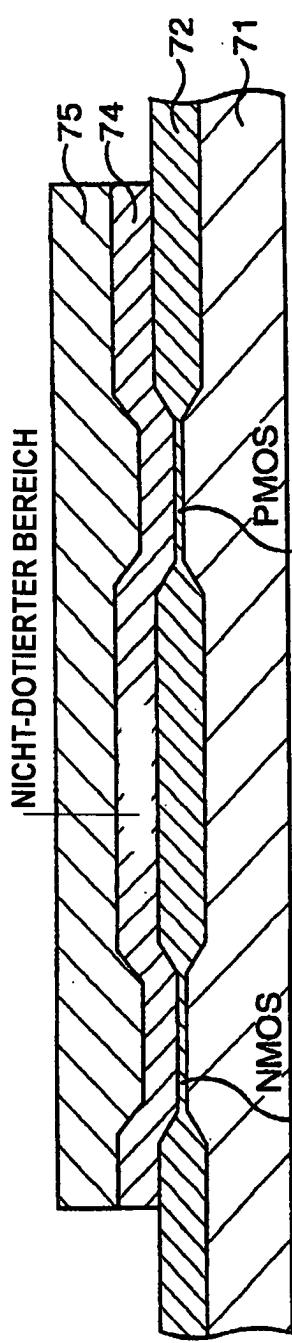

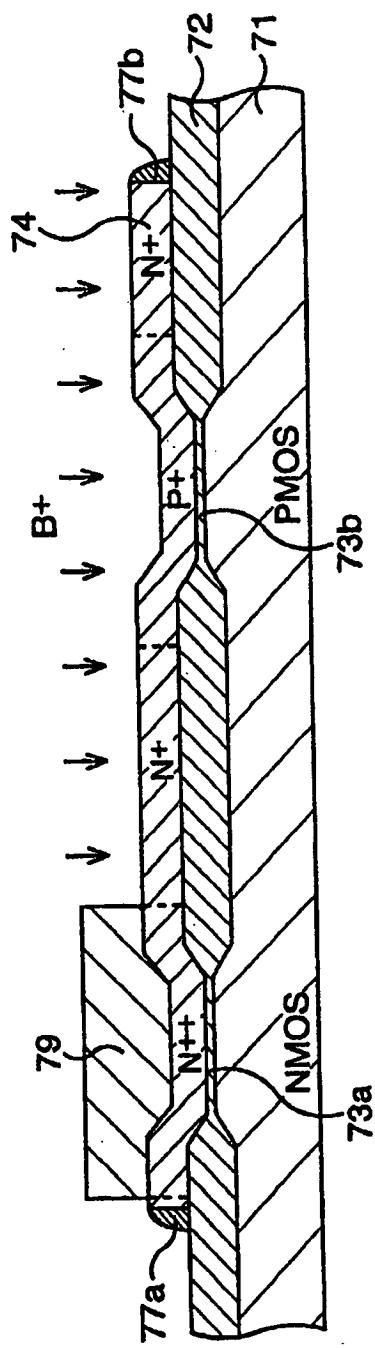

**[0003]** [Fig. 13A](#), [Fig. 13B](#) und [Fig. 13C](#) und [Fig. 14A](#) und [Fig. 14B](#) sind schematische Schnittsichten, welche ein Herstellungsverfahren eines herkömmlichen CMOS-Transistors zeigen, welches die oben beschriebene Doppelgatestruktur in der Reihenfolge seiner Prozesse übernimmt.

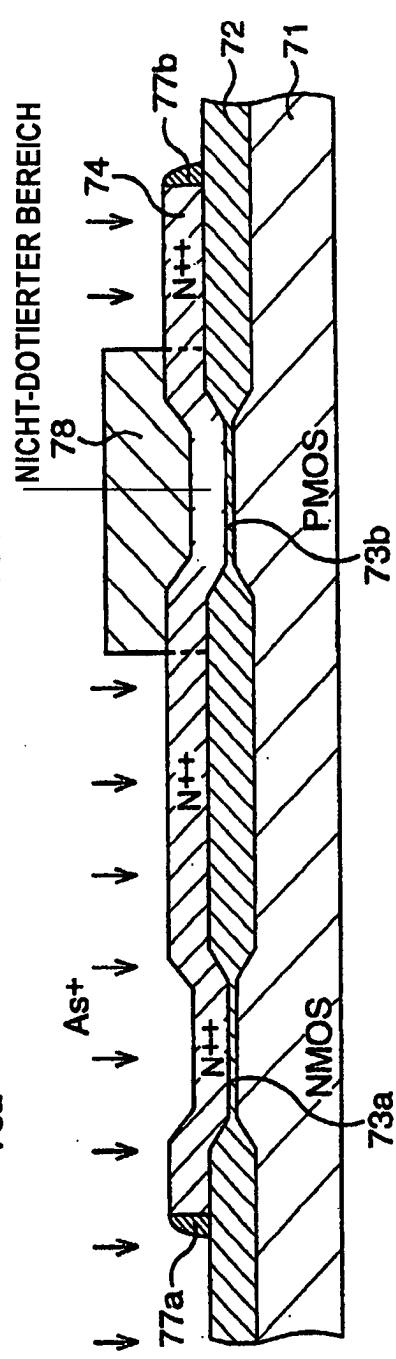

**[0004]** Wie in [Fig. 13A](#) gezeigt, nachdem eine Feldoxidschicht **72** und Gateoxidschichten **73a** und **73b** auf einem Siliciumsubstrat **71** ausgebildet werden, wird eine nicht-dotierte Polysiliciumschicht geschichtet. Dann wird eine Abdeckmaske **75** in einem Bereich ausgebildet, um ein Gate auszubilden, und die nicht-dotierte Polysiliciumschicht wird gemustert, indem die Abdeckmaske **75** als eine Maske verwendet wird, um eine Polysiliciumschicht **74** zum Ausbilden des Gates auszubilden.

**[0005]** Dann, wie in [Fig. 13B](#) gezeigt, wird die Abdeckmaske **75** entfernt, wird erneut eine Abdeckmaske **76** auf der Polysiliciumschicht **74** ausgebildet, welche in einem PMOS-Ausbildungsbereich positioniert ist, und wird eine Ionenimplantation mit einem Arsenion ( $\text{As}^+$ ) durchgeführt, indem die Abdeckmaske **76** als eine Maske verwendet wird.

**[0006]** Dann, wie in [Fig. 13C](#) gezeigt, nachdem eine Isolierschicht ausgebildet wird, um die Polysiliciumschicht **74** abzudecken, in welche das Arsenion ( $\text{As}^+$ ) injiziert wird, wird ein anisotropes Ätzen durchgeführt, um seitliche Wandabstandshalter **77a** und **77b** an den Seitenwänden der Gateelektrode auszubilden. Dann wird die Oberfläche der Polysiliciumschicht **74** im PMOS-Ausbildungsbereich mit einer Abdeckmaske **78** abgedeckt, und ein Arsenion ( $\text{As}^+$ ) wird in eine NMOS-Seite injiziert, um Source- und Drain-Bereiche mit hoher Konzentration im NMOS-Ausbildungsbereich auszubilden.

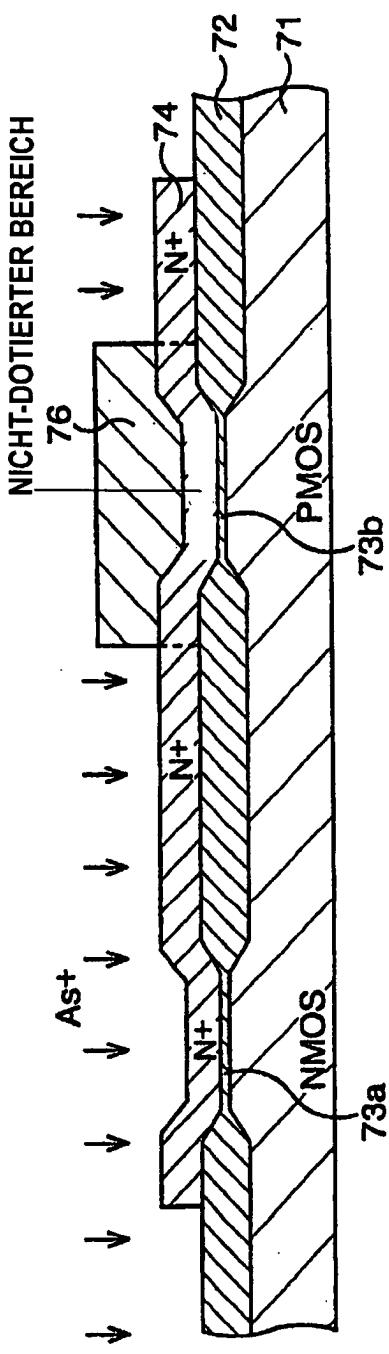

**[0007]** Dann, wie in [Fig. 14A](#) gezeigt, wird die Oberfläche der Polysiliciumschicht **74** im NMOS-Ausbildungsbereich mit einer Abdeckmaske **79** abgedeckt,

und ein Borion ( $\text{B}^+$ ) wird in die PMOS-Seite injiziert, um Source- und Drain-Bereiche mit hoher Konzentration im PMOS-Ausbildungsbereich auszubilden.

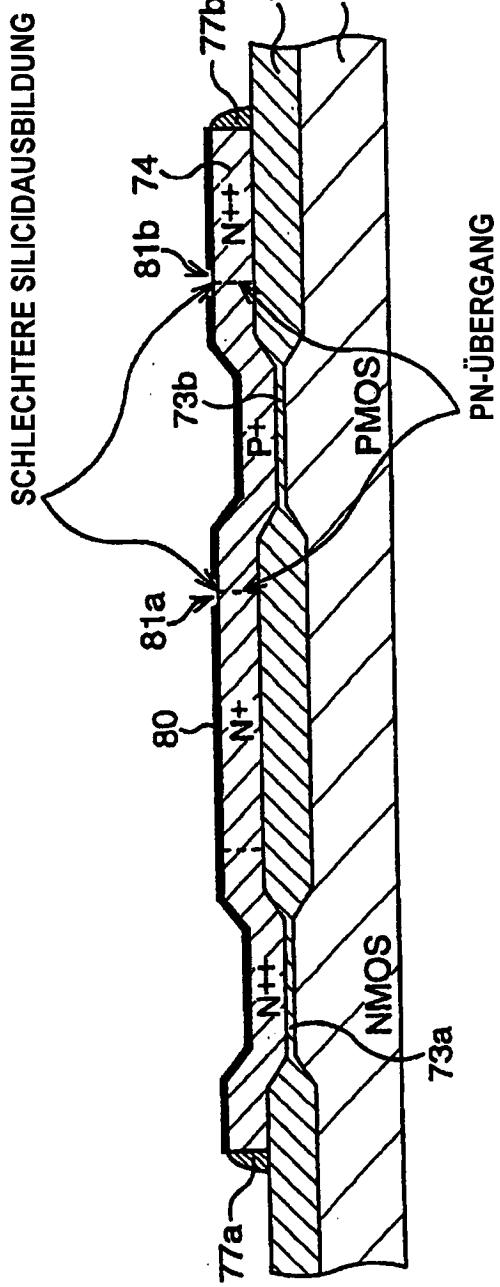

**[0008]** Dann, wie in [Fig. 14B](#) gezeigt, wird ein Siliciumsubstrat **71** erhitzt, um die Störstelle zu aktivieren, die mit den Ionen injiziert wird. Dann wird Silicid **80** in der Gateelektrode ausgebildet, und Source- und Drain-Bereiche, indem ein Metall mit einem hohem Schmelzpunkt verwendet wird.

**[0009]** Die Abdeckmasken **76** bis **79**, welche wie oben beschrieben zum Ausbilden eines CMOS-Transistors verwendet werden, sind im Allgemeinen aus einer Polymermischung hergestellt.

**[0010]** Jedoch, wenn eine Ionenimplantation mit einer Abdeckmaske durchgeführt wird, die mit der Polymermischung als eine Maske ausgebildet ist, wird Carbid, das die Abdeckmasken **76** bis **79** bildet, in die Oberfläche der Polysiliciumschicht **74** getrieben, die im Randbereich der Abdeckmaske positioniert ist.

**[0011]** Ein so angetriebenes Carbid kann nicht durch eine Abdeckungsveraschung und -waschung entfernt werden. Daher, wie in [Fig. 14B](#) gezeigt, wird angenommen, dass kein Silicid in den Bereichen **81a** und **81b** ausgebildet wird, in denen das Carbid verbleibt, aufgrund der Verhinderung einer Silicid-Ausbildung, was von Nachteil ist, da ein Halbleiterbauelement keine vorbestimmte Operation durchführen kann.

**[0012]** Dementsprechend ist es vorstellbar, eine Ionenimplantation durchzuführen, nachdem die Siliciumoxidschicht auf die Polysiliciumschicht geschichtet wird, welche auf dem Halbleitersubstrat ausgebildet ist, und dann wird die Siliciumoxidschicht entfernt, um Silicid auszubilden, wie im japanischen Patent 2000-138293 beschrieben, das in der offiziellen Gazette offenlegen ist.

**[0013]** Jedoch gibt es die folgenden Nachteile in der Technologie, die im japanischen Patent 2000-138293 beschrieben wird, das in der offiziellen Gazette offenlegen ist.

**[0014]** Zuerst ist ein Prozess zum Entwickeln der Siliciumoxidschicht erforderlich, was zu einer Erhöhung der Herstellungskosten führt.

**[0015]** Zweitens, da eine Ionenimplantation durch die Siliciumoxidschicht durchgeführt wird, bedarf es einer Erhöhung einer Ionenimplantationsenergie. Dementsprechend werden Diffusionsschichten von Source und Drain tief innerhalb des Halbleitersubstrats ausgebildet, was es schwierig macht, die Ausbildung eines dünnen Transistors zu realisieren.

**[0016]** Infolge der obigen Nachteile ist es wün-

schenkenswert, ein Halbleiterbauelement und ein Herstellungsverfahren davon bereitzustellen, welche es möglich machen, eine normale Operation mit einer Verdrahtung mit niedrigem Widerstand durchzuführen, während Silicid auf Polysilicium ausgebildet wird, und eine Kostenreduzierung und Ausbildung des dünnen Halbleiterbauelements zu realisieren.

**[0017]** Die Erfindung ist in den unabhängigen Ansprüchen definiert, auf welche nun Bezug genommen wird. Merkmale unabhängiger Ansprüche können kombiniert werden, wenn sie nicht implizit im Widerspruch stehen. Bevorzugte Merkmale sind in den Unteransprüchen genau beschrieben.

**[0018]** In einem ersten Ausführungsbeispiel der vorliegenden Erfindung umfasst ein Halbleiterbauelement eine Halbleiterschicht, die über einem Halbleitersubstrat ausgebildet ist (die Halbleiterschicht besitzt dotierte Teile), und eine Silicidschicht, die auf der oben beschriebenen Halbleiterschicht ausgebildet ist, wobei mindestens eine der gleichen (ersten) leitfähigen (vom leitfähigen Typ) Halbleiterschicht(en) (Teil), die auf dem Halbleitersubstrat ausgebildet ist, verbunden ist, umfassend einen, zwei oder mehr (Ionen-)Konzentrationsunterschiede entlang der Oberfläche des Halbleitersubstrats.

**[0019]** Vorzugsweise ist es dadurch gekennzeichnet, dass ein Bereich, in dem die Silicidschicht nicht ausgebildet ist, an einem Bereich ist, der den oben beschriebenen Konzentrationsunterschied besitzt.

**[0020]** Mit solch einer Ausbildung überlappen der Bereich, in dem die Silicidschicht nicht ausgebildet ist, und der Übergang unterschiedlicher leitfähiger Halbleiterschichten nicht. Bezugnahmen hierin auf Schichten umfassen Schichtteile, beispielsweise ein Ausbilden einzelner Teile derselben Schicht in einem Halbleiterbauelement.

**[0021]** Im ersten Ausführungsbeispiel umfasst die oben beschriebene Halbleiterschicht eine erste leitfähige Halbleiterschicht (oder einen dotierten Teil), welche zwei oder mehr Konzentrationsunterschiede besitzt, und eine zweite leitfähige Halbleiterschicht (oder einen dotierten Teil), die sich vom ersten leitfähigen Typ unterscheidet, wobei ein Bereich (oder Abschnitt) geringer Konzentration an der ersten leitfähigen Halbleiterschicht mit dem zweiten leitfähigen Halbleiterschichtbereich verbunden ist. Dann ist es bevorzugt, da der Bereich, in dem die Silicidschicht nicht ausgebildet ist, nicht mit dem Übergang unterschiedlicher leitfähiger Halbleiterschichtbereiche überlappt, wenn ein erster leitfähiger Transistor ausgebildet wird.

**[0022]** Des Weiteren kann im ersten Ausführungsbeispiel die oben beschriebene Halbleiterschicht speziell den ersten leitfähigen Halbleiterschichtbe-

reich, der zwei oder mehr Konzentrationsunterschiede besitzt, den zweiten leitfähigen Halbleiterschichtbereich, der sich vom ersten leitfähigen Typ unterscheidet, und einen nicht-dotierten Halbleiterschichtbereich umfassen, in den keine Störstelle dotiert ist, wobei der nicht-dotierte Halbleiterschichtbereich zwischen den Bereich geringer Konzentration in der ersten leitfähigen Halbleiterschicht und die zweite leitfähige Halbleiterschicht entlang der Oberfläche des Halbleitersubstrats verbindend eingelegt ist. Dann ist es bevorzugter, da die Störstelle vom ersten leitfähigen Typ und die Störstelle vom zweiten leitfähigen Typ in einer beliebigen Konzentration injiziert werden können.

**[0023]** Des Weiteren kann im ersten Ausführungsbeispiel die oben beschriebene Halbleiterschicht konkret den ersten leitfähigen Halbleiterschichtbereich umfassen, der zwei oder mehr Konzentrationsunterschiede besitzt, und den zweiten leitfähigen Halbleiterschichtbereich umfassen, der zwei oder mehr Konzentrationsunterschiede besitzt und der sich vom ersten leitfähigen Typ unterscheidet, wobei ein Bereich geringer Konzentration in der ersten leitfähigen Halbleiterschicht mit einem Bereich geringer Konzentration in der zweiten leitfähigen Halbleiterschicht verbunden ist. Dann ist es bevorzugt, dass der nicht-bildende Bereich der Silicidschicht nicht mit dem Übergang unterschiedlicher leitfähiger Halbleiterschichten überlappt, wenn ein zweiter leitfähiger Transistor ausgebildet wird.

**[0024]** Des Weiteren kann im ersten Ausführungsbeispiel eine Störstelle mit hoher Konzentration der Halbleiterschicht existieren, welche schwerer ist als die Störstelle, die in dem Bereich geringer Konzentration in der Halbleiterschicht existiert.

**[0025]** Des Weiteren kann im ersten Ausführungsbeispiel ein Halbleiterbauelement eine Isolierschicht umfassen, die auf der Oberfläche des Halbleitersubstrats ausgebildet ist, und Diffusionsschichten umfassen, die in dem Halbleitersubstrat in einer Weise ausgebildet sind, um einen unteren Bereich der gleichen leitfähigen Halbleiterschicht einzulegen, um einen Transistor auszubilden, in welchem die Halbleiterschicht als ein Gate dient, die Isolierschicht als eine Gate-Isolierschicht dient und die Diffusionsschichten als eine Source und ein Drain dienen.

**[0026]** Des Weiteren kann im ersten Ausführungsbeispiel die Halbleiterschicht beispielsweise eine Polysiliciumschicht sein.

**[0027]** In einem zweiten Ausführungsbeispiel der vorliegenden Erfindung umfasst ein Herstellungsverfahren eines Halbleiterbauelements: einen ersten Schritt eines Ausbildens einer Halbleiterschicht über einem Halbleitersubstrat; einen zweiten Schritt eines Ausbildens einer ersten Maskenschicht, die einen

Teilbereich der Halbleiterschicht abdeckt; einen dritten Schritt eines Ausbildens einer ersten leitfähigen Halbleiterschicht in der Halbleiterschicht durch Injizieren einer ersten Störstelle eines ersten leitfähigen Typs in die Halbleiterschicht, wobei die erste Maskenschicht als eine Maske verwendet wird; einen vierten Schritt eines Entfernens der ersten Maskenschicht; einen fünften Schritt eines Ausbildens einer zweiten Maskenschicht, die einen Teilbereich der ersten leitfähigen Halbleiterschicht und einen Halbleiterschichtbereich abdeckt, der sich vom ersten leitfähigen Halbleiterschichtbereich unterscheidet, um einen Grenzbereich zwischen dem ersten leitfähigen Halbleiterschichtbereich und einer Halbleiterschicht zu umfassen, die sich vom ersten leitfähigen Halbleiterschichtbereich unterscheidet; einen sechsten Schritt eines Ausbildens des ersten leitfähigen Halbleiterschichtbereichs hoher Konzentration und des ersten leitfähigen Halbleiterschichtbereichs geringer Konzentration durch Injizieren der zweiten Störstelle vom gleichen leitfähigen Typ wie der erste leitfähige Typ, welche aus einem schwereren Element besteht als die erste Störstelle, in die Halbleiterschicht, wobei die zweite Maskenschicht als eine Maske verwendet wird; einen siebten Schritt eines Entfernens der zweiten Maskenschicht; und einen acht Schritt eines Ausbildens von Silicid auf der Halbleiterschicht, so dass der nicht-bildende Bereich aus Silicid nicht mit dem Übergang von Halbleiterschichten überlappt, welche unterschiedliche leitfähige Typen besitzen.

**[0028]** In einem dritten Ausführungsbeispiel der vorliegenden Erfindung, beim Herstellen eines Halbleiterbauelements durch Ausbilden einer Silicidschicht auf einer Gatehalbleiterschicht nach einem Ausbilden der Gatehalbleiterschicht, in der zwei unterschiedliche leitfähige Halbleiterschichten miteinander verbunden sind, über einem Halbleitersubstrat, umfasst das Herstellungsverfahren des Halbleiterbauelements: einen ersten Schritt eines Ausbildens eines Bereichs geringer Konzentration in der gleichen leitfähigen Halbleiterschicht durch Injizieren eines Störstellenions eines leichten Elements in mindestens eine Halbleiterschicht des gleichen leitfähigen Typs aus den Gatehalbleiterschichten; einen zweiten Schritt eines Ausbildens eines Bereichs hoher Konzentration in der gleichen leitfähigen Halbleiterschicht durch Injizieren eines Störstellenions eines schweren Elements, das schwerer ist als das leichte Element, in eine Bereichsseite geringerer Konzentration in Bezug auf den Übergang zwischen den zwei unterschiedlichen leitfähigen Halbleiterschichten aus den gleichen leitfähigen Halbleiterschichten; und einen dritten Schritt eines Ausbildens einer Silicidschicht auf dem Übergang zwischen den zwei unterschiedlichen leitfähigen Halbleiterschichtbereichen, so dass der nicht-bildende Bereich der Silicidschicht nicht mit dem Übergang zwischen den zwei unterschiedlichen leitfähigen Halbleiterschichtbereichen überlappt.

**[0029]** In einem weiteren bevorzugten Ausführungsbeispiel wird ein Halbleiterbauelement bereitgestellt, in welchem eine Halbleiterschicht einen dotierten Teil mit einer ersten Leitfähigkeit besitzt, der mit mindestens einem Ionenkonzentrationsunterschied ausgebildet ist. Eine Silicidschicht kann über der Schicht ausgebildet sein und ein nicht-bildender Bereich aus Silicid überlappt nicht mit einem pn-Übergang des Halbleiterbauelements. In einem Prozess, wenn ein Arsenion ( $\text{As}^+$ ), das schwer ist, injiziert wird, werden Halbleiterschichten (z. B. Polysilicium) mit einer Abdeckmaske abgedeckt, um ein Ende der Abdeckmaske abzudecken, welche die Polysiliciumschichten abdeckt, um einen PMOS-Ausbildungsbereich auszubilden. Durch diesen Prozess wird ein nicht-bildender Bereich aus Silicid so angeordnet, um nicht mit einem pn-Übergang zu überlappen, um den nicht-bildenden Bereich aus Silicid daran zu hindern, dass sein Widerstand ansteigt.

**[0030]** Bevorzugte Ausführungsbeispiele der vorliegenden Erfindung werden nachfolgend nur beispielhaft mit Bezugnahme auf die beigefügten Zeichnungen beschrieben, in welchen:

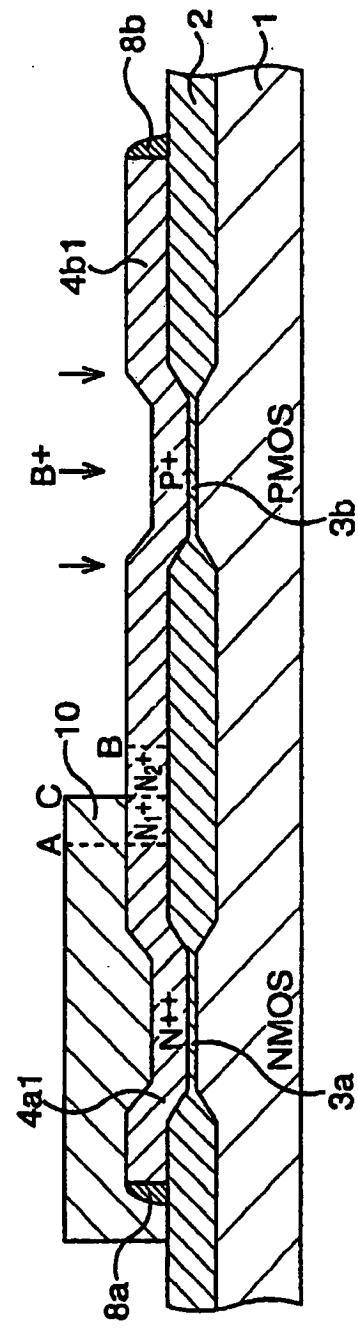

**[0031]** [Fig. 1A](#), [Fig. 1B](#) und [Fig. 1C](#) ein erstes Ausführungsbeispiel der vorliegenden Erfindung indizieren und schematische Schnittansichten sind, welche ein Herstellungsverfahren eines Halbleiterbauelements zeigen, in der Reihenfolge seiner Prozesse;

**[0032]** [Fig. 2A](#), [Fig. 2B](#) und [Fig. 2C](#) das erste Ausführungsbeispiel der vorliegenden Erfindung indizieren und schematische Schnittansichten sind, welche ein Herstellungsverfahren des Halbleiterbauelements zeigen, welches den Prozessen in den [Fig. 1A](#), [Fig. 1B](#) und [Fig. 1C](#) folgt, in der Reihenfolge seiner Prozesse;

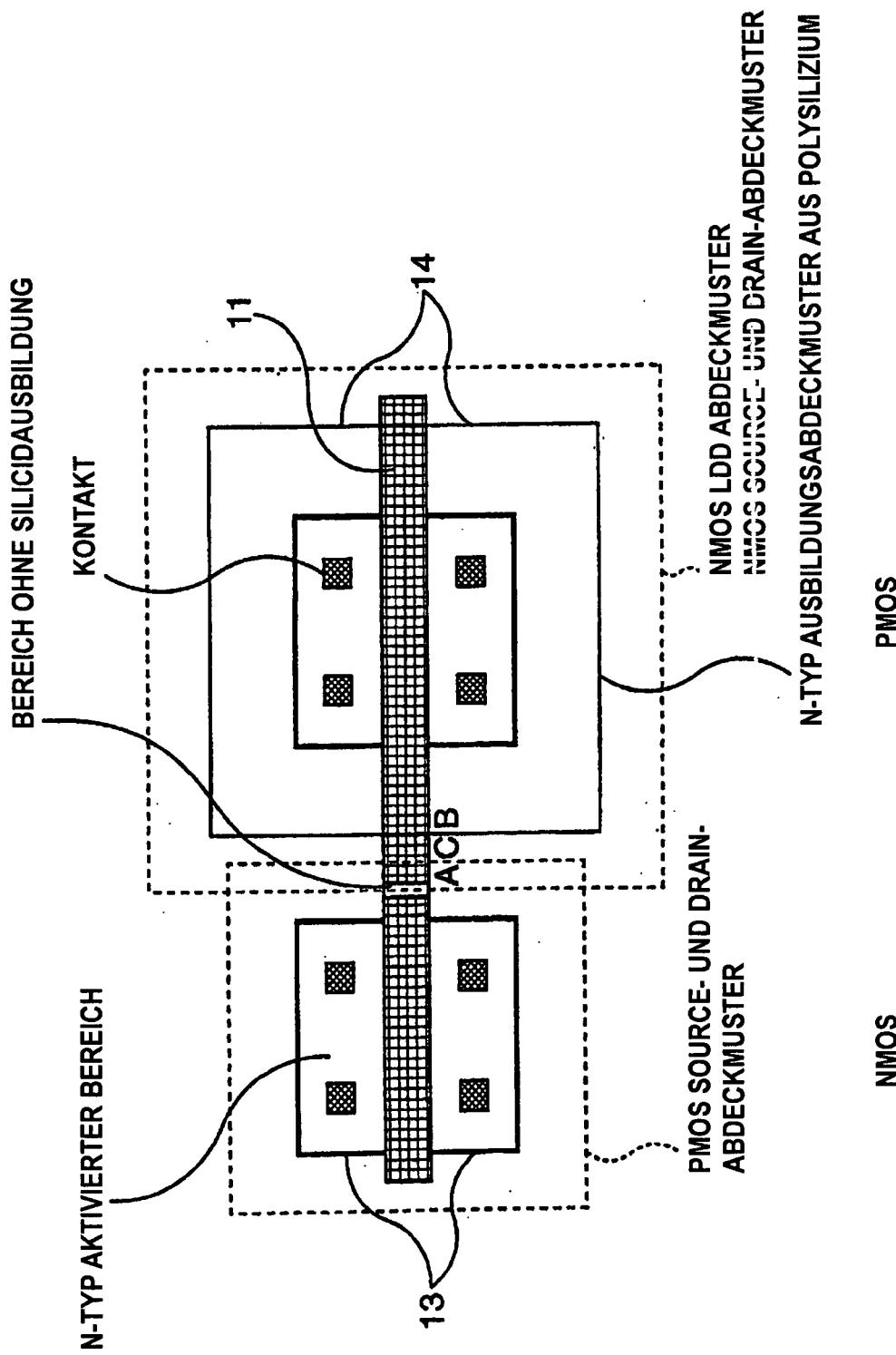

**[0033]** [Fig. 3](#) das erste Ausführungsbeispiel der vorliegenden Erfindung indiziert und eine schematische Draufsicht ist, welche das Halbleiterbauelement zeigt, das durch die Prozesse hergestellt wird, die in den [Fig. 1A](#), [Fig. 1B](#) und [Fig. 1C](#) und in den [Fig. 2A](#), [Fig. 2B](#) und [Fig. 2C](#) gezeigt sind, von oben gesehen;

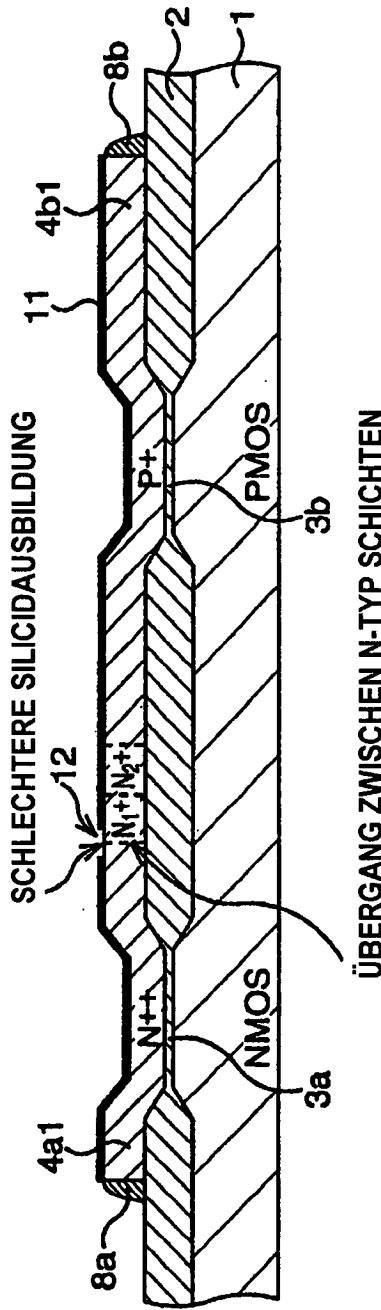

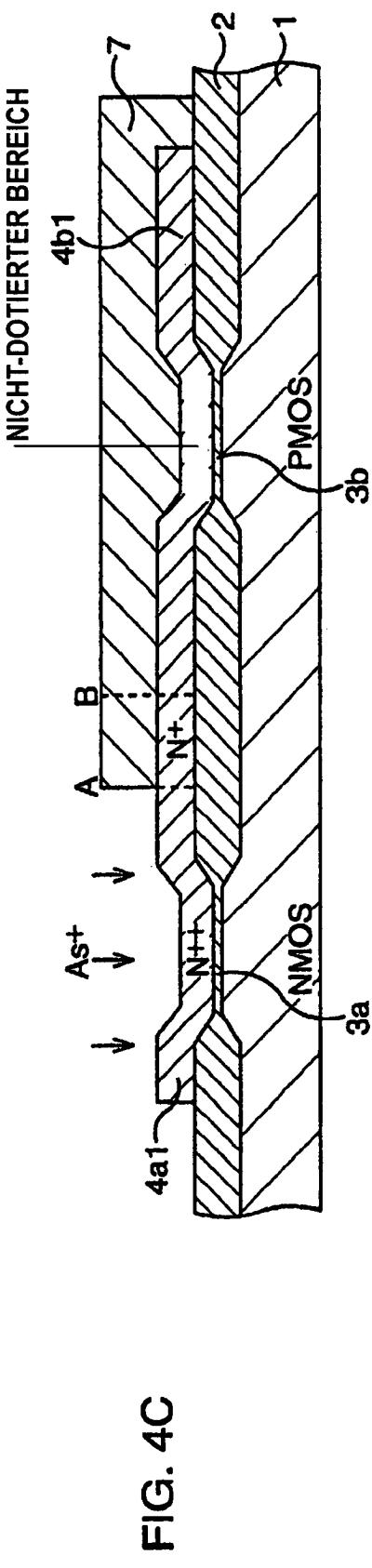

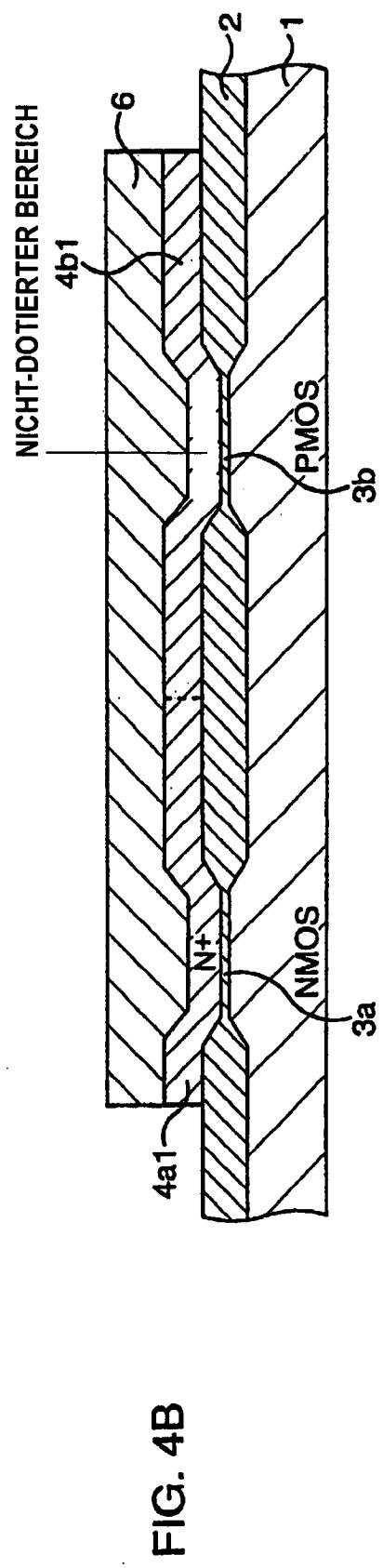

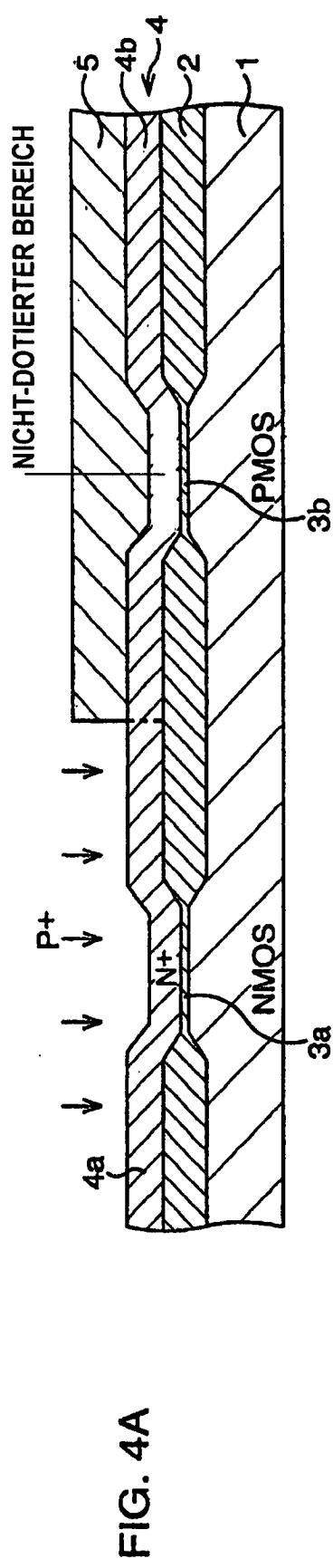

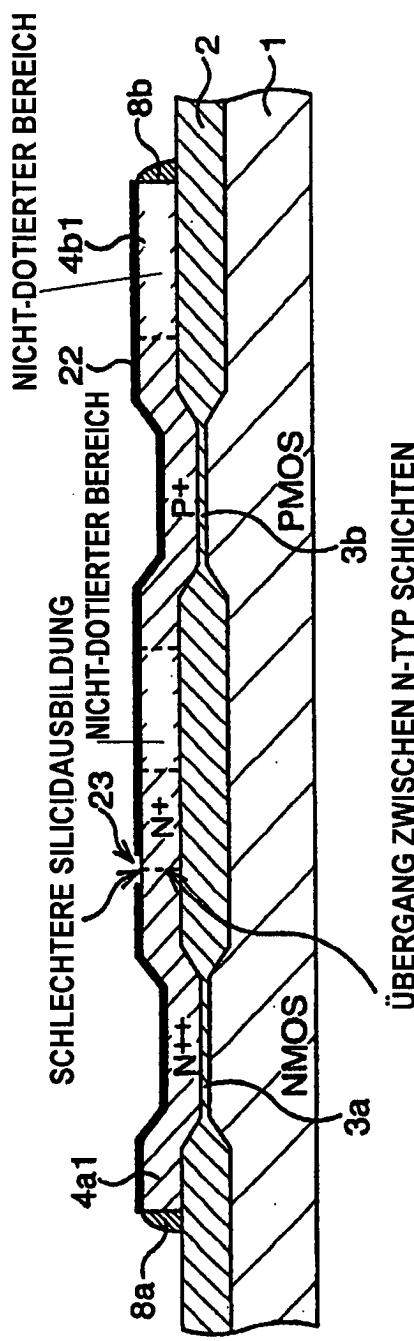

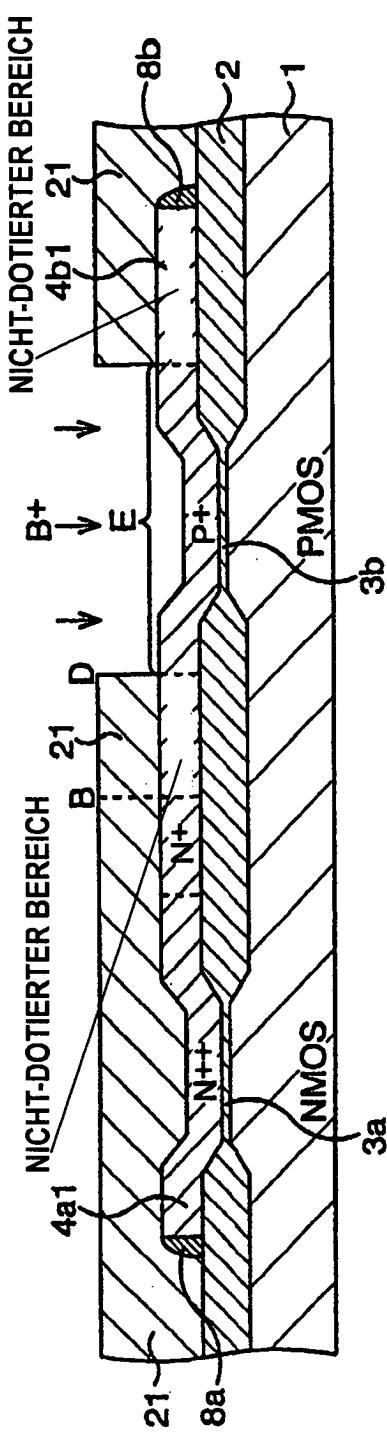

**[0034]** [Fig. 4A](#), [Fig. 4B](#) und [Fig. 4C](#) ein zweites Ausführungsbeispiel der vorliegenden Verbindung indizieren und schematische Schnittansichten sind, welche ein Herstellungsverfahren eines Halbleiterbauelements in der Reihenfolge seiner Prozesse zeigen;

**[0035]** [Fig. 5A](#), [Fig. 5B](#) und [Fig. 5C](#) das zweite Ausführungsbeispiel der vorliegenden Erfindung indizieren und schematische Schnittansichten sind, welche ein Herstellungsverfahren des Halbleiterbauelements zeigen, welches den Prozessen in den [Fig. 4A](#), [Fig. 4B](#) und [Fig. 4C](#) folgt, in der Reihenfolge seiner Prozesse;

[0036] [Fig. 6](#) das erste Ausführungsbeispiel der vorliegenden Erfindung indiziert und eine erste schematische Draufsicht ist, welche das Halbleiterbauelement zeigt, das durch die Prozesse hergestellt wird, die in den [Fig. 4A](#), [Fig. 4B](#) und [Fig. 4C](#) und in den [Fig. 5A](#), [Fig. 5B](#) und [Fig. 5C](#) gezeigt sind, von oben gesehen;

[0037] [Fig. 7](#) das erste Ausführungsbeispiel der vorliegenden Erfindung indiziert und eine zweite schematische Draufsicht ist, welche das Halbleiterbauelement zeigt, das durch die Prozesse hergestellt wird, die in den [Fig. 4A](#), [Fig. 4B](#) und [Fig. 4C](#) und in den [Fig. 5A](#), [Fig. 5B](#) und [Fig. 5C](#) gezeigt sind, von oben gesehen;

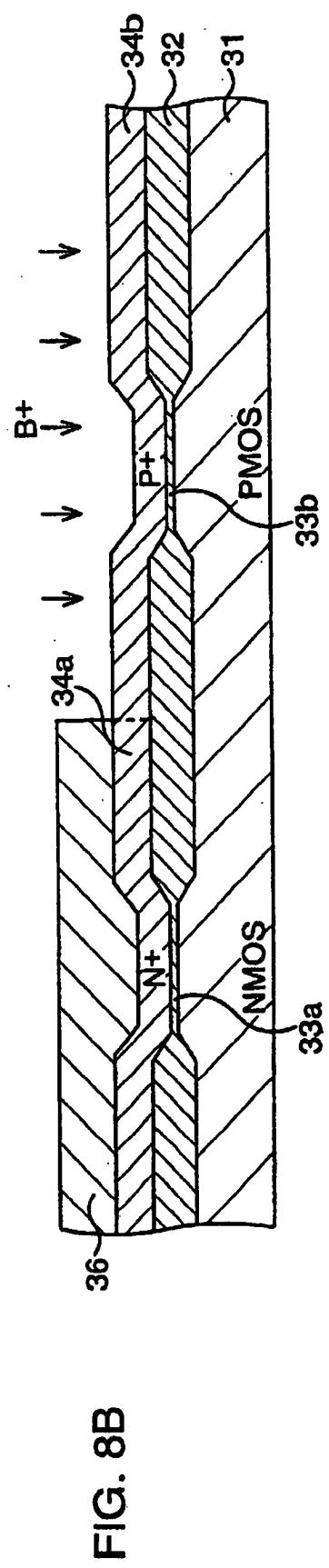

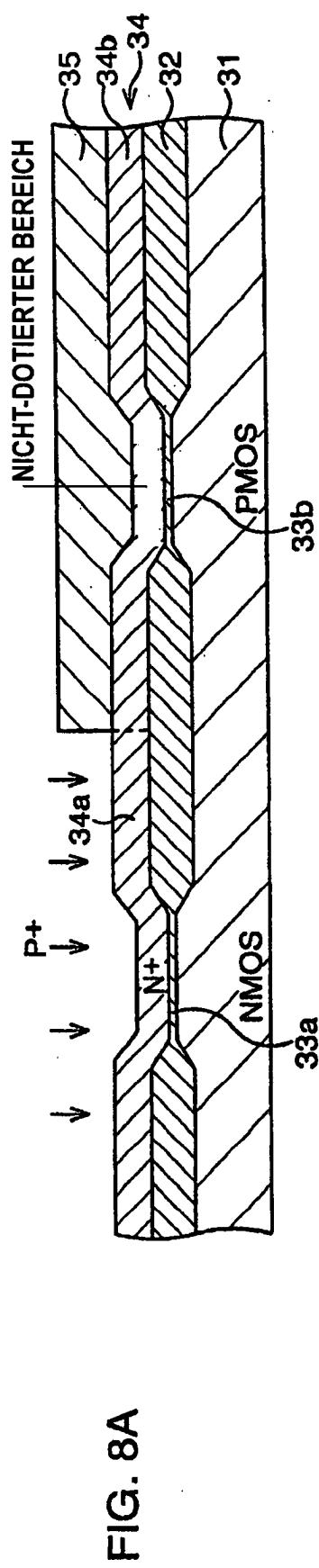

[0038] [Fig. 8A](#), [Fig. 8B](#) und [Fig. 8C](#) ein drittes Ausführungsbeispiel der vorliegenden Erfindung indizieren und schematische Schnittansichten sind, welche ein Herstellungsverfahren eines Halbleiterbauelements zeigen, in der Reihenfolge seiner Prozesse;

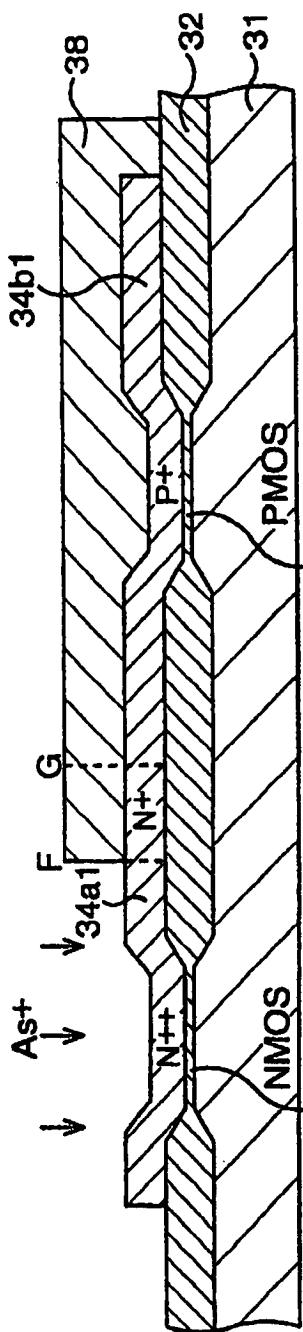

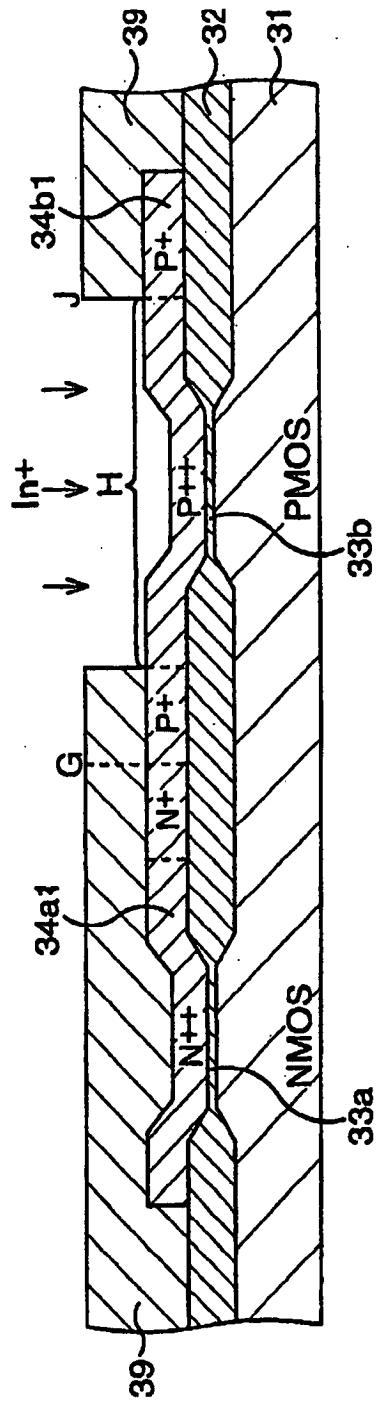

[0039] [Fig. 9A](#), [Fig. 9B](#) und [Fig. 9C](#) das dritte Ausführungsbeispiel der vorliegenden Erfindung indizieren und schematische Schnittansichten sind, die ein Herstellungsverfahren des Halbleiterbauelements zeigen, welches den Prozessen in den [Fig. 8A](#), [Fig. 8B](#) und [Fig. 8C](#) folgt, in der Reihenfolge seiner Prozesse;

[0040] [Fig. 10A](#) und [Fig. 10B](#) das dritte Ausführungsbeispiel der vorliegenden Erfindung indizieren und schematische Schnittansichten sind, welche ein Herstellungsverfahren des Halbleiterbauelements zeigen, welches den Prozessen in den [Fig. 9A](#), [Fig. 9B](#) und [Fig. 9C](#) folgt, in der Reihenfolge seiner Prozesse;

[0041] [Fig. 11A](#), [Fig. 11B](#) und [Fig. 11C](#) ein viertes Ausführungsbeispiel der vorliegenden Erfindung indizieren und schematische Schnittansichten sind, welche ein Herstellungsverfahren eines Halbleiterbauelements zeigen, in der Reihenfolge seiner Prozesse;

[0042] [Fig. 12A](#), [Fig. 12B](#) und [Fig. 12C](#) das vierte Ausführungsbeispiel der vorliegenden Erfindung indizieren und schematische Schnittansichten sind, welche ein Herstellungsverfahren des Halbleiterbauelements zeigen, welches den Prozessen in den [Fig. 11A](#), [Fig. 11B](#) und [Fig. 11C](#) in der Reihenfolge seiner Prozesse folgt;

[0043] [Fig. 13A](#), [Fig. 13B](#) und [Fig. 13C](#) Stand der Technik indizieren und schematische Schnittansichten sind, welche ein Herstellungsverfahren eines Halbleiterbauelements zeigen, in der Reihenfolge seiner Prozesse; und

[0044] [Fig. 14A](#) und [Fig. 14B](#) den Stand der Technik indizieren und schematische Schnittansichten

sind, welche ein Herstellungsverfahren des Halbleiterbauelements zeigen, welches den Prozessen in den [Fig. 13A](#), [Fig. 13B](#) und [Fig. 13C](#) folgt, in der Reihenfolge seiner Prozesse.

[0045] Bevor eine detaillierte Beschreibung von Ausführungsbeispielen eines Halbleiterbauelements und eines Herstellungsverfahrens davon gemäß der vorliegenden Erfindung erklärt wird, wird zuerst die Theorie der Erfinder in Bezug auf die Basis der vorliegenden Erfindung beschrieben werden, ohne dass die Anmeldung auf diese Theorie beschränkt werden soll.

[0046] Die Erfinder der vorliegenden Erfindung studierten im Detail die Effekte unterschiedlicher Ionen, die in Polysilicium injiziert wurden, auf das Silicid, das danach auf dem Polysilicium ausgebildet wurde. Als Ergebnis wurden die folgenden wichtigen Fakten herausgefunden.

[0047] Das heißt, die Erfinder der vorliegenden Erfindung haben herausgefunden, dass das Silicid, das auf dem Polysilicium ausgebildet ist, stark von der Art des Ions, das injiziert wird, der Ionenimplantationsenergie und der Dosierungsmenge abhängt, und insbesondere ist die Silicid-Ausbildung extrem schwierig, wenn ein Arsenion ( $As^+$ ) verwendet wird, während die Verhinderung der Silicium-Ausbildung nicht mit dem Ausmaß einer hohen Dosis wiedererkannt werden kann, wenn ein Phosphorion ( $P^+$ ) oder ein Borion ( $B^+$ ) verwendet wird, und haben erforscht, dass die Ausbildung von Silicid entsprechend der Art ausgewählter Ionen manchmal leicht und manchmal schwierig ist.

[0048] Detaillierter beschrieben, wenn das Arsenion ( $As^+$ ) in das Polysilicium mit der Bedingung 10 keV,  $6 \times 10^{13} cm^{-2}$  injiziert wird, um Silicid auszubilden, kann kein perfektes Silicid auf Polysilicium ausgebildet werden, und ein nicht-bildender Bereich aus Silicid wird entwickelt.

[0049] Andererseits, wenn eine Ionenimplantation auf Polysilicium mit einem Phosphorion ( $P^+$ ) mit der Bedingung 20 keV,  $4 \times 10^{15} cm^{-2}$  durchgeführt wird, oder mit einem Borion ( $B^+$ ) mit der Bedingung 7 keV,  $4 \times 10^{15} cm^{-2}$ , wird der nicht-bildende Bereich aus Silicid nicht auf dem Polysilicium entwickelt.

[0050] Somit haben die Erfinder der vorliegenden Erfindung herausgefunden, dass die Silicid-Ausbildung dazu neigt, behindert zu werden, wenn eine Ionenimplantation mittels eines Elements durchgeführt wird, das eine relativ hohe Ordnungszahl besitzt (d. h., eine große Masse), und umgekehrt die Silicid-Ausbildung leicht ist, wenn die Ionenimplantation mittels eines Elements durchgeführt wird, das eine kleine Ordnungszahl besitzt (d. h., geringe Masse).

**[0051]** Jedes Ausführungsbeispiel des Halbleiterbauelements und des Verfahrens zum Herstellen davon, welche die obigen herausgefundenen Charakteristika verwenden, werden erklärt werden.

– Erstes Ausführungsbeispiel –

**[0052]** Ein erstes Ausführungsbeispiel des Halbleiterbauelements und des Verfahrens zum Herstellen davon gemäß der vorliegenden Erfindung wird mit Bezugnahme auf die beigefügten Zeichnungen erklärt werden.

**[0053]** [Fig. 1A](#), [Fig. 1B](#) und [Fig. 1C](#), und [Fig. 2A](#), [Fig. 2B](#) und [Fig. 2C](#) sind schematische Schnittsichten, welche ein Herstellungsverfahren eines Halbleiterbauelements gemäß dem vorliegenden Ausführungsbeispiel in der Reihenfolge seiner Prozesse zeigen, und [Fig. 3](#) ist eine schematische Draufsicht, welche das Halbleiterbauelement zeigt, das durch die Prozesse hergestellt wird, welche in den [Fig. 1A](#), [Fig. 1B](#) und [Fig. 1C](#) und in den [Fig. 2A](#), [Fig. 2B](#) und [Fig. 2C](#) gezeigt sind, in der Prozessreihenfolge, die aus Obigem ersichtlich ist.

**[0054]** Zuerst, wie in [Fig. 1A](#) gezeigt, nach dem Ausbilden einer Gate-Isolierschicht, die beispielsweise aus einer  $\text{SiO}_2$ -Schicht hergestellt ist, wobei ein Wärmeoxidationsverfahren oder Ähnliches verwendet wird, auf einem Elementausbildungsbereich **1** eines Halbleitersubstrats, wird eine Feldisolierschicht **2** in einem Elementtrennungsbereich ausgebildet, indem ein LOCOS-Verfahren oder Ähnliches verwendet wird. Durch den Prozess werden eine Gate-Isolierschicht **3a** in einem NMOS-Ausbildungsbereich und eine Gate-Isolierschicht **3b** in einem PMOS-Ausbildungsbereich, welche durch die Feldisolierschicht **2** getrennt sind, ausgebildet.

**[0055]** Dann wird eine Polysiliciumschicht **4** auf die Gate-Isolierschichten **3a** und **3b** und die Feldisolierschicht **2** durch ein Verfahren wie z. B. eine Pyrolyse von  $\text{SiH}_4$ -Gas in einer Stickstoffgas-Atmosphäre geschichtet.

**[0056]** Dann wird ein Fenster für eine Ausbildung einer Gateelektrode vom n-Typ ausgebildet, durch Abdecken eines PMOS-Ausbildungsbereichs **4b** der Polysiliciumschicht **4** mit einer ersten Abdeckmaske **5** als eine erste Maskenschicht, und ein Phosphorion ( $\text{P}^+$ ) als eine erste Störstelle wird beispielsweise unter der obigen Bedingung 20 keV,  $4 \times 10^{15} \text{ cm}^{-2}$  injiziert.

**[0057]** Durch diesen Prozess wird der NMOS-Ausbildungsbereich **4a** der Polysilicium-Gateschicht **4** in einen n-Typ umgewandelt in einer Konzentration von ungefähr  $2,5 \times 10^{20} \text{ cm}^{-3}$ . Dann wird die erste Abdeckmaske **5** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

**[0058]** Es sollte beachtet werden, dass Musterdaten für eine n-Typ-Ausbildung (ein Polysilicium-Abdeckmuster für eine n-Typ-Ausbildung in [Fig. 3](#)), um die Polysiliciumschicht **4** als n-Typ auszubilden, indem die erste Abdeckmaske **5** abgedeckt wird, erzeugt werden können, indem nur die n-Wannen-Daten verschoben werden, so dass sie auf einfache Weise automatisch erzeugt werden.

**[0059]** Als Nächstes, wie in [Fig. 1B](#) gezeigt, wird ein Gate-Ausbildungsbereich der Polysiliciumschicht **4**, welche den NMOS-Ausbildungsbereich **4a** der Polysilicium-Gateschicht **4** und den PMOS-Ausbildungsbereich **4b** der Polysilicium-Gateschicht **4** umfasst, wo kein Ion dotiert ist, mit einer zweiten Abdeckmaske **6** abgedeckt, und die Polysiliciumschicht **4** wird gemustert, indem beispielsweise Photolithographie und Trockenätzung verwendet wird, um Ausbildungsschichten **4a1** und **4b1** für eine Gateelektrode auszubilden. Dann wird die zweite Abdeckmaske **6** abgeblättert und gewaschen.

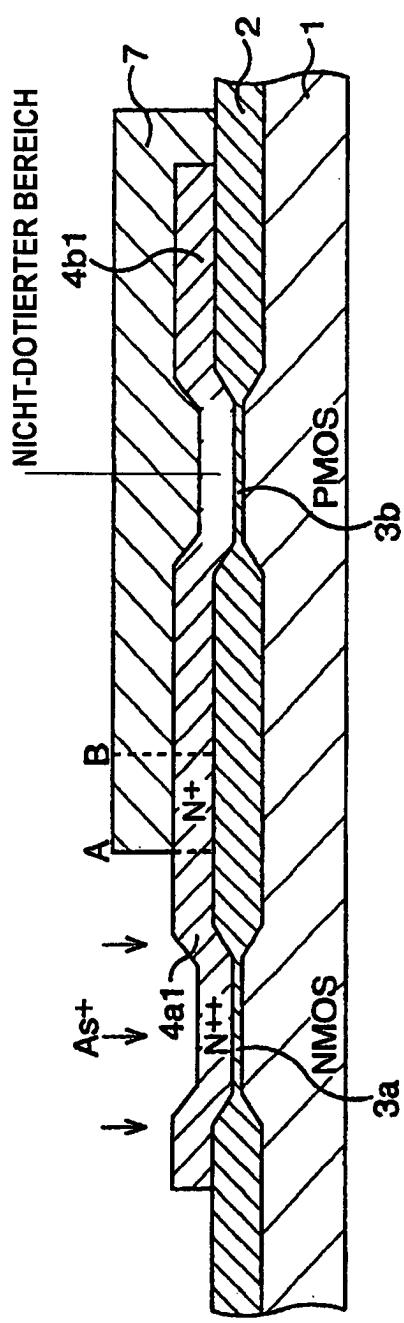

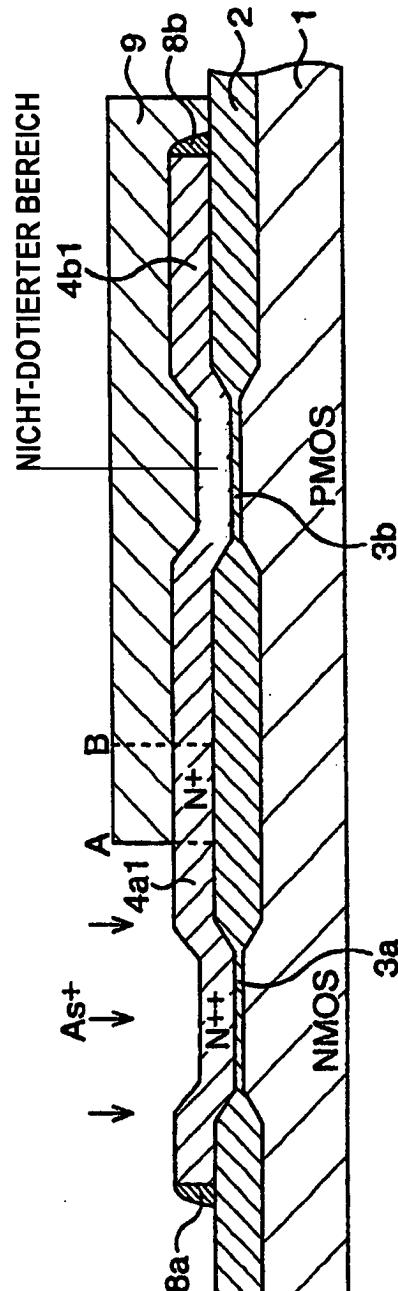

**[0060]** Als Nächstes, wie in [Fig. 1C](#) gezeigt, um einen LDD (Leicht Dotierter Drain) im NMOS-Ausbildungsbereich auszubilden, werden ein nicht-dotierter Bereich **4b1** und ein Teilbereich eines Ausbildungsbereichs **4a1** vom n-Typ mit einer dritten Abdeckmaske **7** als eine zweite Maskenschicht abgedeckt, um einen Grenzabschnitt zwischen dem Bereich **4b1**, wo keine Ionen in den Ausbildungsschichten **4a1** und **4b1** für eine Gateelektrode dotiert sind (nachfolgend als ein nicht-dotierter Bereich bezeichnet), und einem ausgebildeten Bereich **4a1** vom n-Typ zu umfassen (nachfolgend als ein Ausbildungsbereich vom n-Typ bezeichnet).

**[0061]** Genauer gesagt ist ein NMOSLDD-Ionenimplantationsfenster, um einen LDD im NMOS-Ausbildungsbereich auszubilden (ein Ende A der dritten Abdeckmaske **7** auf der Seite des NMOS-Ausbildungsbereichs), angeordnet, um es zwischen einem Ausbildungsfenster vom n-Typ der Gateelektrode (ein Ende B der ersten Abdeckmaske **5** auf der Seite des NMOS-Ausbildungsbereichs) und der NMOS-Gateelektrode (ein Ende der Polysiliciumschicht **4**, die auf der Gate-Isolierschicht **3a** auf der Seite des PMOS-Ausbildungsbereichs positioniert ist) zu positionieren.

**[0062]** Zu diesem Zeitpunkt beträgt der Abstand zwischen dem Ausbildungsfenster vom n-Typ der Gateelektrode (das Ende B der ersten Abdeckmaske) und dem NMOSLDD-bildenden Ionenimplantationsfenster (das Ende A der dritten Abdeckmaske **7**) vorzugsweise ungefähr 0,3  $\mu\text{m}$ , beispielsweise im Falle eines 0,25  $\mu\text{m}$  Bauelements.

**[0063]** Dann wird ein Arsenion ( $\text{As}^+$ ) als eine zweite Störstelle von oben injiziert, beispielsweise mit der Bedingung 10 keV,  $3 \times 10^{14} \text{ cm}^{-2}$ , um eine Ionenimp-

Iantation für eine LDD-Ausbildung eines NMOS-Transistors durchzuführen.

**[0064]** Der Grund, ein Arsenion ( $\text{As}^+$ ) zum Ausbilden des LDD wie oben zu verwenden, liegt darin, dass es notwendig ist, einen flachen Übergang im Halbleitersubstrat **1** auszubilden.

**[0065]** Außerdem bringt die Verwendung eines Arsenions ( $\text{As}^+$ ) den Vorteil, dass nicht nur eine Ionenimplantationsenergie gering gehalten werden kann, sondern auch der Widerstand des Elements gering gehalten wird, so dass die Ansteuerungskapazität verbessert werden kann.

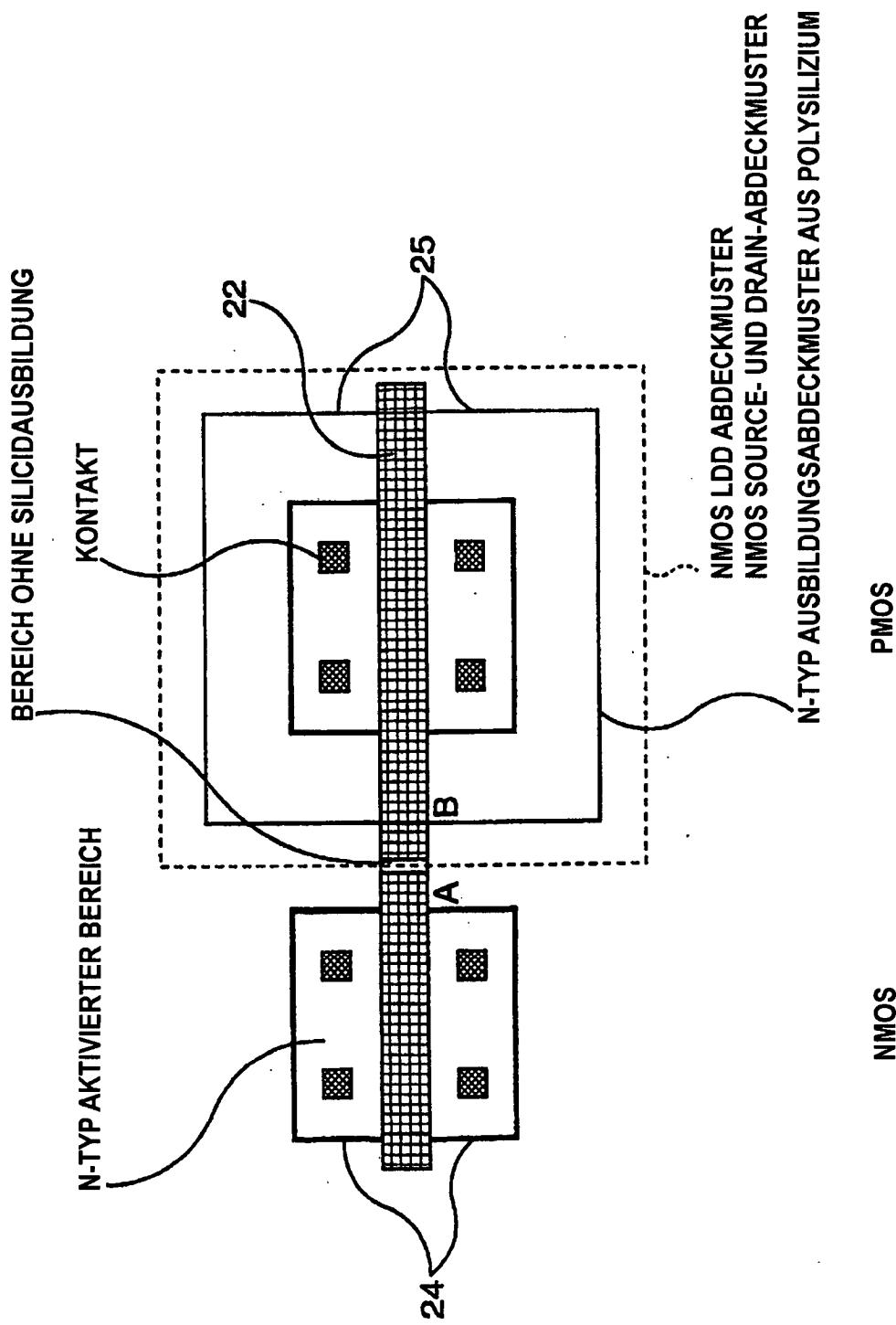

**[0066]** Implantationsfensterdaten für den LDD (das NMOSLDD-Abdeckmuster in [Fig. 3](#)), um das oben beschriebene NMOSLDD-Ionenimplantationsfenster auszubilden, können durch Verschieben der n-Typ-Ausbildungsmusterdaten (das n-Typ-Ausbildungsabdeckungsmuster aus Polysilicium in [Fig. 3](#)) der Gateelektrode automatisch erzeugt werden.

**[0067]** Dann wird die dritte Abdeckungsmaske **7** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

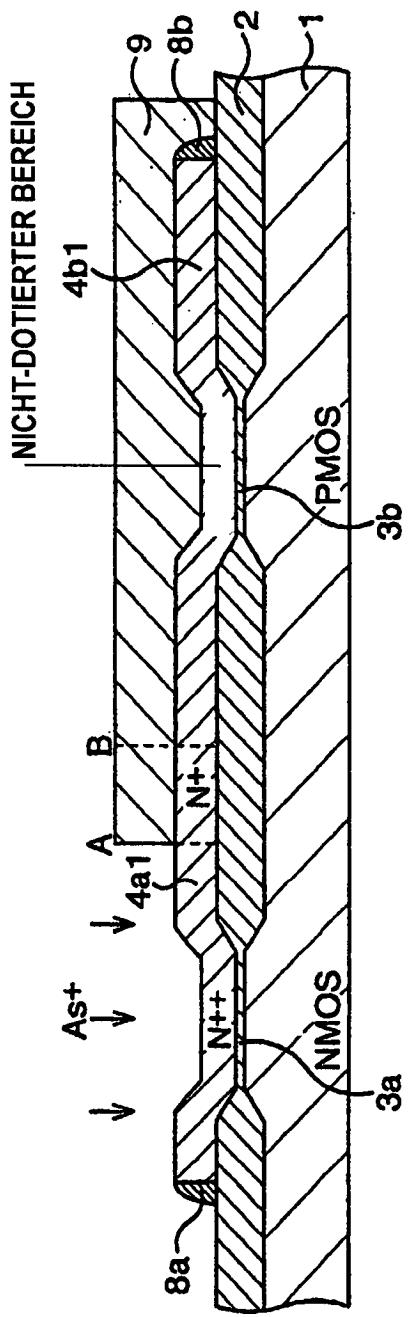

**[0068]** Als Nächstes, wie in [Fig. 2A](#) gezeigt, nach einem Abdecken der obersten Flächen und der Seitenflächen der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode und Ausbilden einer Isolierschicht, werden eine anisotrope Ätzung und Ähnliches angewendet, um seitliche Wandabstandshalter **8a** und **8b** an Seitenwänden der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode auszubilden.

**[0069]** Dann wird, um Source- und Drain-Bereiche im NMOS-Ausbildungsbereich auszubilden, ein nicht-dotierter Bereich **4b1** und ein Teilbereich des n-Typ-Ausbildungsbereichs **4a1** mit einer vierten Abdeckmaske **9** als eine vierte Maskenschicht abgedeckt, um einen nicht-dotierten Bereich **4b1** der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode und einen Grenzabschnitt zwischen dem nicht-dotierten Bereich **4b1** und dem n-Typ-Ausbildungsbereich **4a1** zu umfassen.

**[0070]** Genauer gesagt wird ein Ende A der vierten Abdeckmaske **9** auf der Seite des NMOS-Ausbildungsbereichs so gehandhabt, um es zwischen einem Ende des n-Typ-Ausbildungsfensters der Gateelektrode (ein Ende B der ersten Abdeckmaske **5** auf der Seite des NMOS-Ausbildungsbereichs) und der NMOS-Gateelektrode (ein Ende der Polysiliciumschicht **4**, die auf der Gate-Isolierschicht **3a** auf der Seite des PMOS-Ausbildungsbereichs positioniert ist) zu positionieren, in einer ähnlichen Weise zu dem Fall einer NMOSLDD-Ionenimplantation, die oben beschrieben wird.

**[0071]** Zu diesem Zeitpunkt ist der Abstand zwischen dem n-Typ-Ausbildungsfenster der Gateelektrode (das Ende B der ersten Abdeckmaske **5**) und dem NMOS-Source- und -Drain ausbildenden Ionenimplantationsfenster (das Ende A der vierten Abdeckmaske **9**) vorzugsweise ungefähr  $0,3 \mu\text{m}$ , beispielsweise in dem Fall eines  $0,25 \mu\text{m}$  Bauteils.

**[0072]** Dann wird ein Arsenion ( $\text{As}^+$ ) als eine vierte Störstelle von oben injiziert, beispielsweise mit der Bedingung  $40 \text{ keV}, 2 \times 10^{15} \text{ cm}^{-2}$ . Durch diesen Prozess werden ein Source-Bereich und ein Drain-Bereich hoher Konzentration (NMOS LDD Source und Drain **13** in [Fig. 3](#)) im NMOS-Ausbildungsbereich des Halbleitersubstrats ausgebildet.

**[0073]** Der Grund für die Verwendung des Arsenions ( $\text{As}^+$ ), um den Source-Bereich und den Drain-Bereich auszubilden, liegt darin, dass die erforderliche Ionenimplantationsenergie gering sein kann und das Element mit einem geringen Widerstand vorgesehen werden kann, so dass die Ansteuerungskapazität verbessert werden kann.

**[0074]** Somit beträgt die Differenz zwischen der Ionenkonzentration  $\text{N}^+$  in einem Bereich, der mit der vierten Abdeckmaske **9** abgedeckt ist, und der Ionenkonzentration  $\text{N}^{++}$  in einem Bereich, der nicht damit abgedeckt ist, im n-Typ-Ausbildungsbereich **4a1** der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode ungefähr  $1,5 \times 10^{20} \text{ cm}^{-3}$ .

**[0075]** Die NMOS-Source- und -Drain ausbildenden Implantationsfensterdaten (das NMOS-Source- und -Drain-Abdeckmuster in [Fig. 3](#)), um Source- und Drain-Bereiche im NMOS-Ausbildungsbereich auszubilden, sind die gleichen wie die LDD-Implantationsfensterdaten (das NMOSLDD-Abdeckmuster in [Fig. 3](#)), um das NMOSLDD-Ionenimplantationsfenster auszubilden.

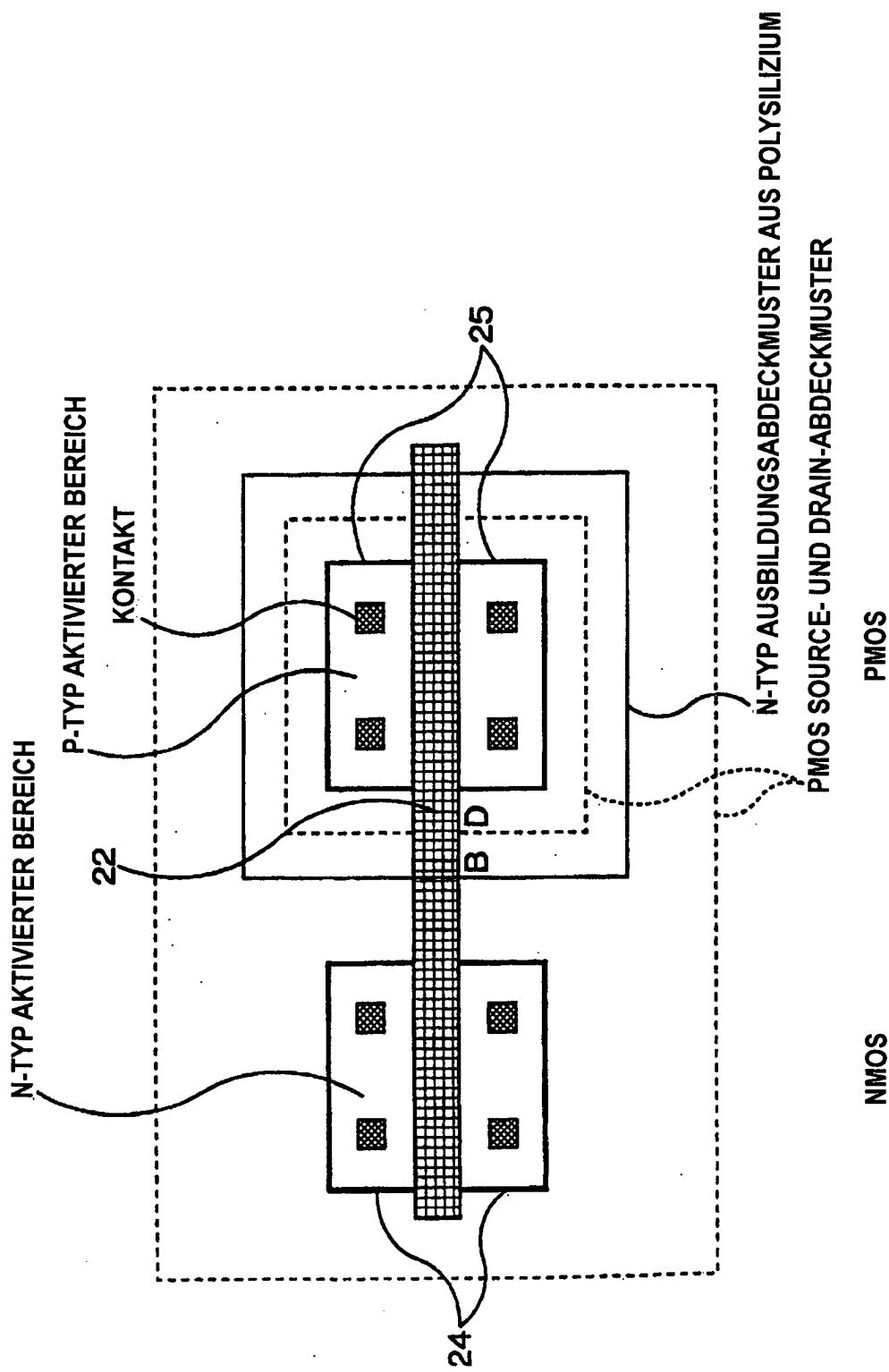

**[0076]** Dann wird die vierte Abdeckmaske **9** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

**[0077]** Als Nächstes, wie in [Fig. 2B](#) gezeigt, um Source- und Drain-Bereiche im PMOS-Ausbildungsbereich auszubilden, wird ein n-Typ-Ausbildungsbereich **4a1**, der einen Bereich angrenzend an den nicht-dotierten Bereich **4b1** ausschließt, mit einer fünften Abdeckmaske **10** als eine dritte Maskenschicht abgedeckt.

**[0078]** Genauer gesagt ist ein Ende C der fünften Abdeckmaske **10** auf dem PMOS-Ausbildungsbereich angeordnet, um zwischen dem n-Typ-Ausbildungsfenster (das Ende B der ersten Abdeckmaske **5** auf der Seite des NMOS-Ausbildungsbereichs) der Gateelektrode und der NMOS-Gateelektrode (ein Ende der Polysiliciumschicht **4**, die auf der Gate-Iso-

lierschicht **3a** auf der Seite des PMOS-Ausbildungsbereichs positioniert ist) positioniert zu werden, in einer ähnlichen Weise zu dem Fall der oben beschriebenen NMOSLDD-Ionenimplantation.

**[0079]** Dann wird ein Borion ( $B^+$ ) als eine dritte Störstelle von oben injiziert, beispielsweise mit der Bedingung 7 keV,  $2 \times 10^{15} \text{ cm}^{-2}$ . Durch diesen Prozess wird ein nicht-dotierter Bereich **4b1** in einem p-Typ ausgebildet (nachfolgend genannt, um den nicht-dotierten Bereich vom p-Typ als einen p-Typ-Ausbildungsbereich auszudrücken), und zur gleichen Zeit werden ein Source-Bereich und ein Drain-Bereich mit hoher Konzentration (PMOS LDD Source und Drain **14** in [Fig. 3](#)) im PMOS-Ausbildungsbereich des Halbleitersubstrats ausgebildet.

**[0080]** Es sollte beachtet werden, dass die Implantation des Bor ( $B^+$ ) mit einer Ionenimplantationsmenge durchgeführt wird, die geringer ist als die Arsenion-Implantationsmenge ( $4 \times 10^{15} \text{ cm}^{-2}$ ) zum Ausbilden des NMOS-Ausbildungsbereichs **4a**, der in [Fig. 1A](#) gezeigt ist. Dies ist so, da der n-Typ-Ausbildungsbereich, der nicht mit der fünften Abdeckmaske **10** abgedeckt ist, nicht in einen p-Typ umgewandelt werden soll.

**[0081]** Die Differenz zwischen der Ionenkonzentration  $N1^+$  in einem Bereich, der mit der fünften Abdeckmaske **10** abgedeckt ist, und der Ionenkonzentration  $N2^+$  in einem Bereich, der nicht damit abgedeckt ist, beträgt in dem Bereich, der mit der vierten Abdeckmaske **9** abgedeckt ist, die in [Fig. 2A](#) gezeigt ist, ungefähr  $1 \times 10^{20} \text{ cm}^{-3}$ .

**[0082]** Es sollte beachtet werden, dass die PMOS-Source- und -Drain ausbildenden Implantationsfensterdaten (das PMOS-Source- und -Drain-Abdeckmuster in [Fig. 3](#)), um die Source- und Drain-Bereiche im oben beschriebenen PMOS-Ausbildungsbereich auszubilden, automatisch erzeugt werden können, durch Verschieben der n-Typ-Musterdaten der oben beschriebenen Gateelektrode (das n-Typ-Ausbildungsabdeckmuster aus Polysilicium in [Fig. 3](#)), ähnlich zu den oben beschriebenen LDD-Implantationsfensterdaten.

**[0083]** Als Nächstes, wie in [Fig. 2C](#) gezeigt, wird eine Ionen-injizierte Störstelle durch Erhitzen eines Elements aktiviert, welches einen Bereich **1** des Halbleitersubstrats bildet. Dann wird Silicid **11** in der Gateelektrode ausgebildet, und die Source- und Drain-Bereiche, indem ein Metall mit einem hohen Schmelzpunkt verwendet wird.

**[0084]** Zu diesem Zeitpunkt, da Carbid in die Oberfläche der Polysiliciumschicht getrieben wird, die an einem Ende A der dritten und der vierten Abdeckmasken **7** und **9** positioniert ist, durch Implantation eines Arsenions ( $As^+$ ), was in den [Fig. 1C](#) und [Fig. 2A](#)

gezeigt ist, wird kein Silicid **11** auf diesem Abschnitt ausgebildet.

**[0085]** Jedoch, wenn ein Halbleiterbauelement mit einer Doppelgatestruktur durch das Verfahren gemäß dem vorliegenden Ausführungsbeispiel ausgebildet wird, wird ein Bereich **12**, der kein Silicid bildet, wo das oben beschriebene Silicid nicht ausgebildet wird, in der Nähe des mittleren Abschnitts des n-Typ-Bereichs **4a1** der Ausbildungsschichten **4a1** und **4b1** einer Gateelektrode ausgebildet.

**[0086]** Dementsprechend kann der Bereich **12**, der kein Silicid bildet, so angeordnet werden, um einen pn-Übergang der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode nicht zu überlappen, und ein Abschnitt, wo der oben beschriebene Abschnitt, der kein Silicid bildet, mit einem Polysilicium-Widerstand bei einer Konzentration von  $1 \times 10^{20} \text{ cm}^{-3}$  verbunden werden kann.

**[0087]** Somit wird in dem vorliegenden Ausführungsbeispiel, da der Bereich **12**, der kein Silicid bildet, auf dem n-Typ-Ausbildungsbereich **4a1** der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode ausgebildet ist, so dass der Bereich **12**, der kein Silicid bildet, nicht mit dem pn-Übergang der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode überlappt, und die Silicidschicht **11** am pn-Übergang ausgebildet ist, keine parasitäre Diode, die aus dem pn-Übergang besteht, an der Gateelektrode ausgebildet, was den Bereich **12**, der kein Silicid bildet, daran hindert, dass sein Widerstand ansteigt.

**[0088]** Infolge dieser Struktur ist solch ein Prozess wie im Stand der Technik, um eine Siliciumoxidschicht auf der Polysiliciumschicht auszubilden, nicht erforderlich, und ein Halbleiterbauelement mit einer Doppelgatestruktur kann mit geringeren Kosten produziert werden als den Kosten, die im Stand der Technik erforderlich sind.

**[0089]** Außerdem, da die Notwendigkeit des Ausbildens der Siliciumoxidschicht verschwunden ist, muss die Ionenimplantationsenergie nicht groß sein. Dementsprechend kann das Halbleiterbauelement der vorliegenden Erfindung dünner hergestellt werden als das Halbleiterbauelement mit der vorherigen Doppelstruktur.

– Zweites Ausführungsbeispiel –

**[0090]** Ein zweites Ausführungsbeispiel des Halbleiterbauelements und des Verfahrens zum Herstellen davon gemäß der vorliegenden Erfindung wird als Nächstes beschrieben werden.

**[0091]** [Fig. 4A](#), [Fig. 4B](#) und [Fig. 4C](#) und [Fig. 5A](#), [Fig. 5B](#) und [Fig. 5C](#) sind schematische Schnittsichten, welche ein Herstellungsverfahren eines

Halbleiterbauelemente gemäß dem vorliegenden Ausführungsbeispiel zeigen, in der Reihenfolge seiner Prozesse. [Fig. 6](#) und [Fig. 7](#) sind schematische Draufsichten, welche das Halbleiterbauelement zeigen, das durch die Prozesse hergestellt wird, die in den [Fig. 4A](#), [Fig. 4B](#) und [Fig. 4C](#) und in den [Fig. 5A](#), [Fig. 5B](#) und [Fig. 5C](#) gezeigt sind, in der Prozessreihenfolge, die aus dem Obigen ersichtlich ist.

**[0092]** Da sich das Verfahren zum Herstellen des Halbleiterbauelements des vorliegenden Ausführungsbeispiels in einem Abschnitt zum Ausbilden einer fünften Abdeckmaske **10** von dem Verfahren zum Herstellen des Halbleiterbauelements in dem oben beschriebenen ersten Ausführungsbeispiel unterscheidet, sind die gleichen Abschnitte wie jene im ersten Ausführungsbeispiel mit den gleichen Symbolen und Nummern versehen, und eine detaillierte Erklärung davon wird ausgelassen werden.

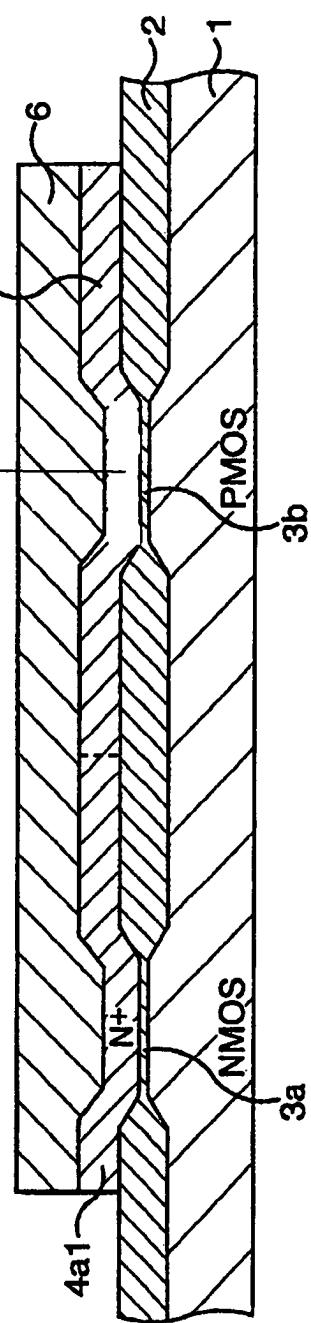

**[0093]** Zuerst, wie in [Fig. 4A](#) gezeigt, nachdem eine Gate-Isolierschicht auf einem Elementausbildungsbereich **1** eines Halbleitersubstrats ausgebildet ist, wird eine Feldisolierschicht **2** ausgebildet, um eine Gate-Isolierschicht **3a** eines NMOS-Ausbildungsbereichs von einer Gate-Isolierschicht **3b** eines PMOS-Ausbildungsbereichs zu trennen.

**[0094]** Dann, nachdem eine Polysiliciumschicht **4** auf die Gate-Isolierschichten **3a** und **3b** und die Feldisolierschicht **2** geschichtet ist, wird ein n-Typ-Ausbildungsfenster der Gateelektrode ausgebildet, indem ein PMOS-Ausbildungsbereich **4b** der Polysiliciumschicht **4** mit einer ersten Abdeckmaske **5** abgedeckt wird.

**[0095]** Dann wird ein Phosphorion ( $P^+$ ) injiziert, beispielsweise mit der Bedingung  $20 \text{ keV}$ ,  $4 \times 10^{15} \text{ cm}^{-2}$ , von oben, um den NMOS-Ausbildungsbereich **4a** der Polysilicium-Gateschicht **4** in einen n-Typ umzuwandeln. Dann wird die erste Abdeckmaske **5** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

**[0096]** Es sollte beachtet werden, dass n-Typ-Ausbildungsmusterdaten (ein n-Typ-Ausbildungsbereich aus Polysilicium in [Fig. 6](#)), um die Polysiliciumschicht **4** in einen n-Typ umzuwandeln, während die erste Abdeckmaske **5** abgedeckt wird, nur erzeugt werden können, indem n-Wannen-Daten verschoben werden, und somit die automatische Erzeugung leicht erreicht werden kann.

**[0097]** Als Nächstes, wie in [Fig. 4B](#) gezeigt, wird ein Gate-Ausbildungsbereich der Polysiliciumschicht **4** mit einer zweiten Abdeckmaske **6** abgedeckt, und die Polysiliciumschicht **4** wird gemustert, um die Ausbildungsschichten **4a1** und **4b1** der Gateelektrode auszubilden. Dann wird die zweite Abdeckmaske **6** abgeblättert und gewaschen.

**[0098]** Als Nächstes, wie in [Fig. 4C](#) gezeigt, um einen LDD im NMOS-Ausbildungsbereich auszubilden, werden ein nicht-dotierter Bereich **4b1** und ein Teilbereich des n-Typ-Ausbildungsbereichs **4a1** mit einer dritten Abdeckmaske **7** abgedeckt, um den nicht-dotierten Bereich der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode und einen Grenzabschnitt zwischen einem nicht-dotierten Bereich **4b1** und einem n-Typ-Ausbildungsbereich **4a1** zu umfassen.

**[0099]** Genauer gesagt ist ein NMOSLDD-Ionenimplantationsfenster, um einen LDD in dem NMOS-Ausbildungsbereich auszubilden (ein Ende A der dritten Abdeckmaske **7** auf der Seite des NMOS-Ausbildungsbereichs) angeordnet, um zwischen einem n-Typ-Ausbildungsfenster der Gateelektrode (ein Ende B der ersten Abdeckmaske **5** auf der Seite des NMOS-Ausbildungsbereichs) und der NMOS-Gateelektrode (ein Ende der Polysiliciumschicht **4**, die auf der Gate-Isolierschicht **3a** auf der Seite des PMOS-Ausbildungsbereichs positioniert ist) positioniert zu werden.

**[0100]** Dann wird ein Arsenion ( $As^+$ ) von oben injiziert, beispielsweise mit der Bedingung  $10 \text{ keV}$ ,  $3 \times 10^{14} \text{ cm}^{-2}$ , um eine Ionenimplantation für den LDD eines NMOS-Transistors durchzuführen.

**[0101]** Die LDD-Implantationsfensterdaten (das NMOSLDD-Abdeckmuster in [Fig. 6](#)), um das oben beschriebene NMOSLDD-Ionenimplantationsfenster auszubilden, können automatisch erzeugt werden, durch Verschieben der n-Typ-Musterdaten der Gateelektrode (das n-Typ-Ausbildungsbereich aus Polysilicium in [Fig. 6](#)).

**[0102]** Dann wird die dritte Abdeckmaske **7** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

**[0103]** Als Nächstes, wie in [Fig. 5A](#) gezeigt, nach einem Ausbilden von seitlichen Wandabstandshaltern **8a** und **8b** an den Seitenwänden der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode, um Source- und Drain-Bereiche im NMOS-Ausbildungsbereich auszubilden, werden ein nicht-dotierter Bereich **4b1** und ein Teilbereich eines n-Typ-Ausbildungsbereichs **4a1** mit einer vierten Abdeckmaske **9** als vierte Abdeckschicht abgedeckt, um einen Grenzbereich zwischen dem nicht-dotierten Bereich **4b1** der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode und dem n-Typ-Ausbildungsbereich **4a1** zu umfassen.

**[0104]** Genauer gesagt wird ein Ende A einer vierten Abdeckmaske **9** auf der Seite des NMOS-Ausbildungsbereichs so gehandhabt, um zwischen einem Ende des n-Typ-Ausbildungsfensters der Gateelektrode (das Ende B der ersten Abdeckmaske **5** auf der Seite des NMOS-Ausbildungsbereichs) und der

NMOS-Gateelektrode (ein Ende der Polysiliciumschicht **4**, die auf der Gate-Isolierschicht **3a** auf der Seite des PMOS-Ausbildungsbereichs positioniert ist) positioniert zu werden, in einer ähnlichen Weise zu dem oben beschriebenen Fall einer NMOS-LDD-Ionenimplantation.

**[0105]** Dann wird ein Arsenion ( $\text{As}^+$ ) als eine vierte Störstelle von oben injiziert, beispielsweise mit der Bedingung  $40 \text{ keV}, 2 \times 10^{15} \text{ cm}^{-2}$ , um einen Source-Bereich und einen Drain-Bereich mit hoher Konzentration (einen NMOS LDD S/D24 in [Fig. 6](#) und [Fig. 7](#)) im NMOS-Ausbildungsbereich des Halbleitersubstrats auszubilden.

**[0106]** Die Differenz zwischen der Ionenkonzentration  $\text{N}^+$  in einem Bereich, der mit der vierten Abdeckmaske **9** abgedeckt ist, und der Ionenkonzentration  $\text{N}^{++}$  in einem Bereich, der nicht damit abgedeckt ist, beträgt im n-Typ-Bereich **4a1** der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode ungefähr  $1,5 \times 10^{20} \text{ cm}^{-3}$ .

**[0107]** Die NMOS-Source- und -Drain ausbildenden Implantationsfensterdaten (das NMOS S/D-Abdeckmuster in [Fig. 6](#)), um Source- und Drain-Bereiche im NMOS-Ausbildungsbereich auszubilden, sind die gleichen wie die LDD-Implantationsfensterdaten (das NMOSLDD-Abdeckmuster in [Fig. 6](#)), um das NMOS-LDD-Ionenimplantationsfenster auszubilden.

**[0108]** Dann wird die vierte Abdeckmaske **9** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

**[0109]** Als Nächstes, wie in [Fig. 5B](#) gezeigt, werden der nicht-dotierte Bereich **4b1**, außer einem Bereich **E**, um die PMOS-Gateelektrode auszubilden, und der n-Typ-Ausbildungsbereich **4a1** mit einer sechsten Abdeckmaske **21** als eine dritte Abdeckschicht abgedeckt.

**[0110]** Genauer gesagt wird ein Ende **D** der sechsten Abdeckmaske **21** auf der Seite des PMOS-Ausbildungsbereichs angeordnet, um zwischen einem Ende **B** des n-Typ-Ausbildungsfensters der Gateelektrode und einer PMOS-Gateelektrode positioniert zu werden (ein Ende der Polysiliciumschicht **4**, die auf der Gate-Isolierschicht **3b** auf der Seite des NMOS-Ausbildungsbereichs positioniert ist).

**[0111]** Zu diesem Zeitpunkt ist der Abstand zwischen dem n-Typ-Ausbildungsfenster und der Gateelektrode (das Ende **B** der ersten Abdeckmaske) und dem PMOS-Source- und -Drain-Ionenimplantationsfenster (das Ende **D** der sechsten Abdeckmaske **21**) vorzugsweise ungefähr  $0,3 \mu\text{m}$ , beispielsweise in dem Fall eines  $0,25 \mu\text{m}$  Bauelements.

**[0112]** Dann wird ein Borion ( $\text{B}^+$ ) als eine dritte Stör-

stelle von oben injiziert, beispielsweise mit der Bedingung  $7 \text{ keV}, 2 \times 10^{15} \text{ cm}^{-2}$ . Durch diesen Prozess wird ein Bereich **E**, um die PMOS-Gateelektrode auszubilden, in einen p-Typ umgewandelt (nachfolgend wird in p-Typ-ausgebildeter, nicht-dotierter Bereich als ein p-Typ-Ausbildungsbereich bezeichnet), und zur gleichen Zeit werden ein Source-Bereich und ein Drain-Bereich mit hoher Konzentration (PMOS LDD Source und Drain **21** in [Fig. 6](#) und [Fig. 7](#)) im PMOS-Ausbildungsbereich des Halbleitersubstrats ausgebildet.

**[0113]** Es sollte beachtet werden, dass die PMOS-Source- und -Drain ausbildenden Implantationsfensterdaten (das PMOS-Source- und -Drain-Abdeckmuster in [Fig. 7](#)), um die Source- und Drain-Bereiche im oben beschriebenen PMOS-Ausbildungsbereich auszubilden, automatisch erzeugt werden können, durch Verschieben der n-Typ-Ausbildungsmusterdaten der Gateelektrode (das n-Typ-Ausbildungsabdeckmuster aus Polysilicium in [Fig. 7](#)), ähnlich zu den oben beschriebenen LDD-Implantationsfensterdaten.

**[0114]** Als Nächstes, wie in [Fig. 5C](#) gezeigt, wird eine Ionen-injizierte Störstelle durch Erwärmen eines Elements aktiviert, welches den Bereich **1** des Halbleitersubstrats bildet. Dann wird Silicid **22** in der Gateelektrode ausgebildet, und die Source- und Drain-Bereiche, indem ein Metall mit einem hohem Schmelzpunkt verwendet wird.

**[0115]** Zu diesem Zeitpunkt, da Carbid in die Oberfläche der Polysiliciumschicht getrieben wird, die an einem Ende **A** der vierten Abdeckmaske **9** positioniert ist, durch Implantation eines Arsenions ( $\text{As}^+$ ), was in [Fig. 5A](#) gezeigt ist, wird in diesem Abschnitt kein Silicid **22** ausgebildet.

**[0116]** Jedoch wird auch in dem Verfahren gemäß dem vorliegenden Ausführungsbeispiel ein Bereich **23**, in dem kein Silicid ausgebildet wird, wo das Silicid **22** nicht ausgebildet wird, in der Nähe des mittleren Abschnitts des n-Typ-Ausbildungsbereichs **4a1** der Ausbildungsbereiche **4a1** und **4b1** der Gateelektrode ausgebildet.

**[0117]** Dementsprechend kann ein Bereich **23**, in dem kein Silicid ausgebildet wird, so angeordnet werden, um nicht mit einem pn-Übergang der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode zu überlappen, so dass ein Abschnitt, wo das oben beschriebene Silicid nicht ausgebildet wird, mit einem Polysilicium-Widerstand einer Konzentration von  $10^{20} \text{ cm}^{-3}$  verbunden werden kann.

**[0118]** Somit wird auch in dem vorliegenden Ausführungsbeispiel, da der Bereich **23**, in dem kein Silicid ausgebildet wird, in dem n-Typ-Ausbildungsbereich **4a1** der Ausbildungsschichten **4a1** und **4b1** der

Gateelektrode ausgebildet wird, so dass der Bereich **23**, in dem kein Silicid ausgebildet wird, nicht mit dem pn-Übergang der Ausbildungsschichten **4a1** und **4b1** der Gateelektrode überlappt, und die Silicidschicht **22** an dem pn-Übergang ausgebildet wird, keine parasitäre Diode, die aus dem pn-Übergang besteht, an der Gateelektrode ausgebildet, was den Bereich **23**, in dem kein Silicid ausgebildet ist, daran hindert, dass sein Widerstand ansteigt.

**[0119]** Infolge dieser Struktur ist solch ein Prozess wie im Stand der Technik, um eine Siliciumoxidschicht auf der Polysiliciumschicht auszubilden, nicht erforderlich, und ein Halbleiterbauelement mit einer Doppelgatestruktur kann mit geringeren Kosten als den Kosten hergestellt werden, die im Stand der Technik erforderlich sind.

**[0120]** Außerdem, da die Notwendigkeit des Ausbildens der Siliciumoxidschicht verschwindet, muss die Ionenimplantationsenergie nicht groß sein. Dementsprechend kann das Halbleiterbauelement des vorliegenden Ausführungsbeispiels dünner hergestellt werden als das Halbleiterbauelement in der früheren Doppelstruktur.

**[0121]** Des Weiteren, in dem Halbleiterbauelement gemäß dem vorliegenden Ausführungsbeispiel, wenn die Ausbildungsschichten **4a1** und **4b1** der Gateelektrode in einen p-Typ umgewandelt werden, da das sechste Abdeckmuster **21** so ausgebildet ist, um einen Abschnitt des nicht-dotierten Bereichs **4b** abzudecken, kann der PMOS-Ausbildungsbereich in einen p-Typ umgewandelt werden, ohne dass ein Borion ( $B^+$ ) in den n-Typ-Ausbildungsbereich **4a** injiziert wird.

**[0122]** Dementsprechend, in dem Verfahren zum Herstellen des Halbleiterbauelements gemäß dem vorliegenden Ausführungsbeispiel, wie in dem ersten Ausführungsbeispiel, hat es auch insofern einen vorteilhaften Effekt, als dass die Implantationskonzentration des Borions ( $B^+$ ) nicht geringer sein muss als die Konzentration des Arsenions ( $As^+$ ), das injiziert wird, um einen n-Typ-Ausbildungsbereich **4a1** auszubilden.

**[0123]** Es sollte beachtet werden, dass, obwohl in den oben beschriebenen ersten und zweiten Ausführungsbeispielen ein Phosphorion als die erste Störstelle verwendet wird, und Arsenionen als die zweite und vierte Störstelle verwendet werden, die erste Störstelle und die zweite Störstelle nicht darauf beschränkt sind. Jede Substanz wird akzeptabel sein, vorausgesetzt, dass die Masse des Elements, welches die erste Störstelle bildet, geringer ist als die Masse des Elements, welches die zweite Störstelle bildet.

### – Drittes Ausführungsbeispiel –

**[0124]** Ein drittes Ausführungsbeispiel des Halbleiterbauelements der vorliegenden Erfindung und eines Herstellungsverfahrens davon wird als nächstes erklärt werden.

**[0125]** Die ersten und zweiten Ausführungsbeispiele sind die Technologie, um die nachteiligen Einflüsse aufgrund des Bereichs, in dem kein Silicid ausgebildet wird, zu entfernen, begleitet von einer Herstellung des NMOS-Transistors unter den CMOS-Transistoren in einer Doppelgatestruktur. Jedoch wird in dem vorliegenden Ausführungsbeispiel eine Technologie, um nachteilige Einflüsse aufgrund des Bereichs, in dem kein Silicid ausgebildet wird, zu entfernen, begleitet von der Herstellung des PMOS-Transistors, erklärt werden.

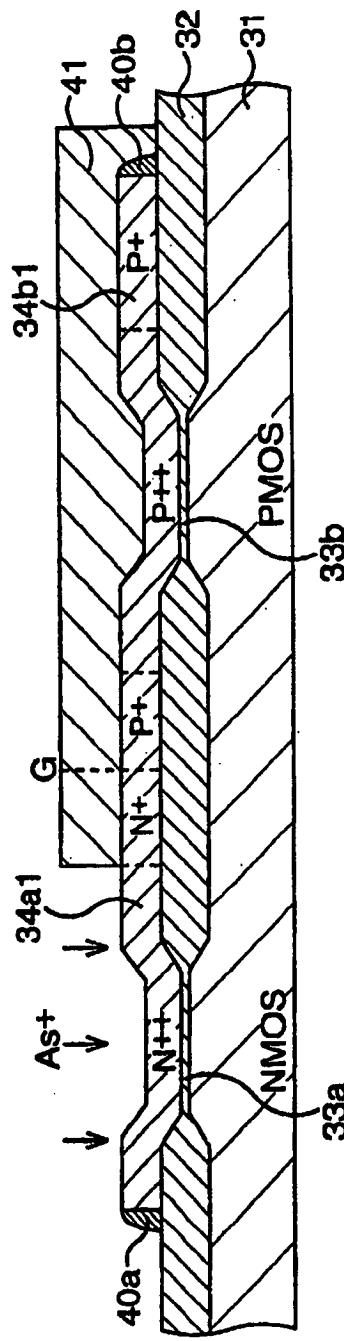

**[0126]** [Fig. 8A](#) bis [Fig. 10B](#) sind schematische Schnittansichten, welche ein Herstellungsverfahren eines Halbleiterbauelements gemäß dem vorliegenden Ausführungsbeispiel zeigen, in der Reihenfolge seiner Prozesse.

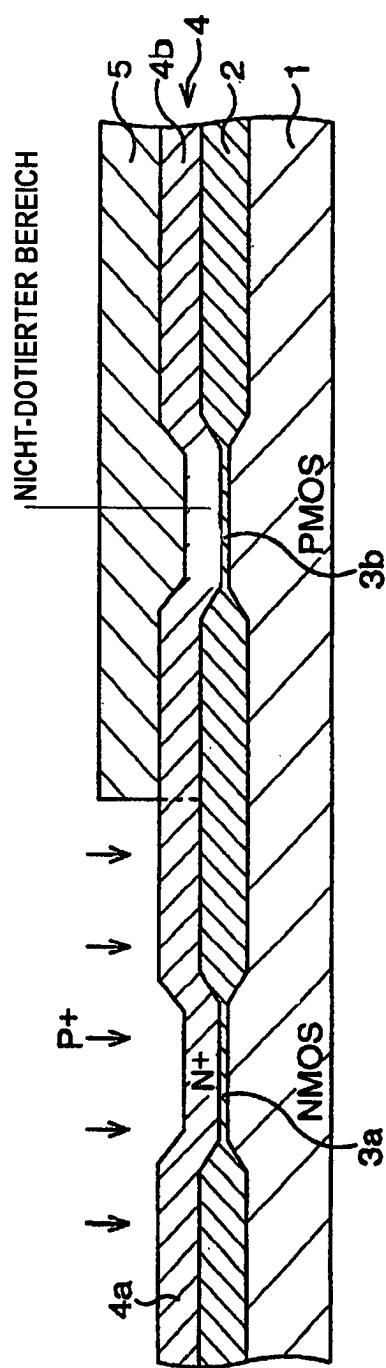

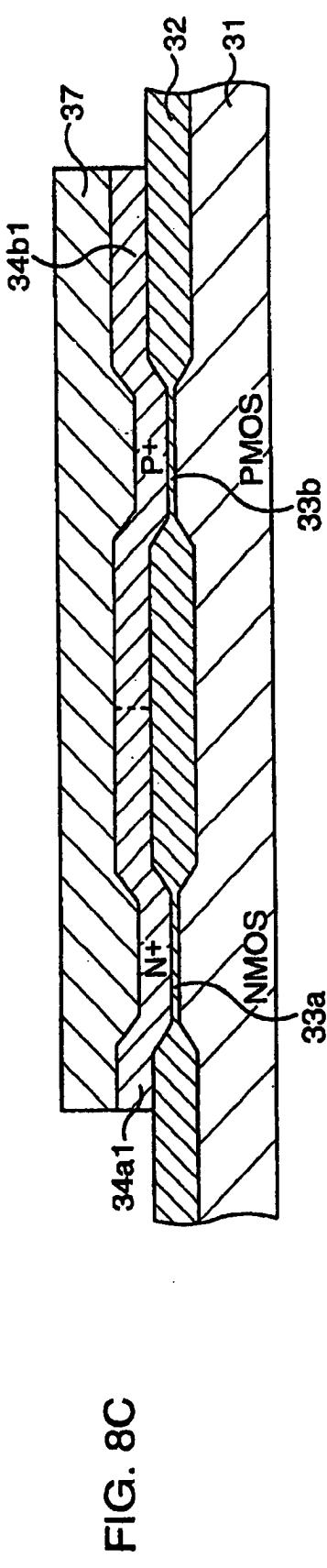

**[0127]** Wie in [Fig. 8A](#) gezeigt, nach einem Ausbilden einer Gate-Isolierschicht, die beispielsweise aus einer  $SiO_2$ -Schicht hergestellt ist, indem ein Wärme-oxidationsverfahren oder Ähnliches verwendet wird, auf einem Elementausbildungsbereich **31** eines Halbleitersubstrats, wird eine Feldisolierschicht **32** in einem Elementtrennungsbereich ausgebildet, indem ein LOCOS-Verfahren oder Ähnliches verwendet wird. Durch den Prozess werden eine Gate-Isolierschicht **33a** in einem NMOS-Ausbildungsbereich und eine Gate-Isolierschicht **33b** in einem PMOS-Ausbildungsbereich ausgebildet, welche durch die Feldisolierschicht **32** getrennt sind.

**[0128]** Dann wird eine Polysiliciumschicht **34** auf die Gate-Isolierschichten **33a** und **33b** und die Feldisolierschicht **32** geschichtet, durch ein Verfahren, wie z. B. eine Pyrolyse von  $SiH_4$ -Gas in einer Stickstoff-gas-Atmosphäre.

**[0129]** Dann wird ein n-Typ-Ausbildungsfenster der Gateelektrode durch Abdecken eines PMOS-Ausbildungsbereichs **34b** der Polysiliciumschicht **34** mit einer siebten Abdeckmaske **35** als eine erste Abdeckschicht ausgebildet, und ein Phosphorion ( $P^+$ ) wird als eine erste Störstelle injiziert, beispielsweise mit der Bedingung  $15\text{ keV}$ ,  $4 \times 10^{15} \text{ cm}^{-2}$ , von oben.

**[0130]** Durch diesen Prozess wird der NMOS-Ausbildungsbereich **34a** der Polysilicium-Gateschicht **34** in einen n-Typ umgewandelt, mit einer Konzentration von ungefähr  $3,5 \times 10^{20} \text{ cm}^{-3}$ . Dann wird die siebte Abdeckmaske **35** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

[0131] Es sollte beachtet werden, dass n-Typ-Ausbildungsmusterdaten, um die Polysiliciumschicht **34** in einen n-Typ umzuwandeln, durch Abdecken der siebten Abdeckmaske **35**, nur durch Verschieben von n-Wannen-Daten erzeugt werden können, so dass sie mit Leichtigkeit automatisch erzeugt werden können.

[0132] Als Nächstes, wie in [Fig. 8B](#) gezeigt, wird ein NMOS-Ausbildungsbereich **34a** einer n-Typ-ausgebildeten Polysiliciumschicht **34** mit einer achten Abdeckmaske **36** als eine fünfte Maskenschicht abgedeckt, und ein Borion ( $B^+$ ) wird als eine fünfte Störstelle injiziert, beispielsweise mit der Bedingung 5 keV,  $4 \times 10^{15} \text{ cm}^{-2}$ , von oben.

[0133] Durch diesen Prozess wird der PMOS-Ausbildungsbereich **34b** der Polysiliciumschicht **34** in einen p-Typ umgewandelt, mit einer Konzentration von ungefähr  $3,5 \times 10^{20} \text{ cm}^{-3}$ . Dann wird die achte Abdeckmaske **36** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

[0134] Es sollte beachtet werden, dass p-Typ-Ausbildungsmusterdaten, um die Polysiliciumschicht **34** in einen p-Typ umzuwandeln, durch Abdecken der achten Abdeckmaske **36**, nur durch Verschieben von p-Wannen-Daten erzeugt werden können, so dass sie mit Leichtigkeit automatisch erzeugt werden können.

[0135] Als Nächstes, wie in [Fig. 8C](#) gezeigt, wird ein Gate-Ausbildungsbereich der Polysiliciumschicht **34**, welche den NMOS-Ausbildungsbereich **34a** der Polysilicium-Gateschicht **34** umfasst, und der PMOS-Ausbildungsbereich **34b** der Polysilicium-Gateschicht **34** mit einer neunten Abdeckmaske **37** abgedeckt, und die Polysiliciumschicht **34** wird gemustert, indem beispielsweise Photolithographie oder Trockenätzung verwendet wird, um Ausbildungsschichten **34a1** und **34b1** einer Gateelektrode auszubilden. Dann wird die neunte Abdeckmaske **37** abgeblättert und gewaschen.

[0136] Als Nächstes, wie in [Fig. 9A](#) gezeigt, um einen LDD im NMOS-Ausbildungsbereich auszubilden, werden der p-Typ-Ausbildungsbereich **34b1** und ein Teilbereich des n-Typ-Ausbildungsbereichs **34a1**, der einen Grenzbereich zwischen **34a1** und **34b1** umfasst, mit einer zehnten Abdeckmaske **38** als eine zweite Maskenschicht abgedeckt.

[0137] Genauer gesagt ist ein NMOSLDD-Ionenimplantationsfenster, um einen LDD im NMOS-Ausbildungsbereich auszubilden (ein Ende F der zehnten Abdeckmaske **38** auf der Seite des NMOS-Ausbildungsbereichs) angeordnet, um zwischen einem n-Typ-Ausbildungsfenster der Gateelektrode (ein Ende G der siebten Abdeckmaske **35** auf der Seite des NMOS-Ausbildungsbereichs) und der

NMOS-Gateelektrode (ein Ende der Polysiliciumschicht **34**, die auf der Gate-Isolierschicht **33a** auf der Seite des PMOS-Ausbildungsbereichs positioniert ist) positioniert zu werden.

[0138] Dann wird ein Arsenion ( $As^+$ ) als eine zweite Störstelle von oben injiziert, beispielsweise mit der Bedingung 5 keV,  $3 \times 10^{14} \text{ cm}^{-2}$ , um eine Ionenimplantation für ein LDD eines NMOS-Transistors durchzuführen.

[0139] Der Grund, das Arsenion ( $As^+$ ) zum Ausbilden des LDD wie oben zu verwenden, liegt darin, dass es notwendig ist, einen flachen Übergang im Halbleitersubstrat **1** auszubilden. Außerdem bringt die Verwendung des Arsenions ( $As^+$ ) einen Vorteil, dass nicht nur die Ionenimplantationsenergie gering gehalten wird, sondern dass auch das Element mit einem geringen Widerstand versehen wird, so dass die Ansteuerungskapazität verbessert werden kann.

[0140] Es sollte beachtet werden, dass Implantationsfensterdaten für den LDD, um das oben beschriebene NMOSLDD-Ionenimplantationsfenster auszubilden, automatisch erzeugt werden können durch Verschieben der n-Typ-Ausbildungsmusterdaten der Gateelektrode.

[0141] Dann wird die zehnte Abdeckmaske **38** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

[0142] Als Nächstes, wie in [Fig. 9B](#) gezeigt, um einen LDD im PMOS-Ausbildungsbereich auszubilden, werden ein p-Typ-Ausbildungsbereich **34b1**, außer ein Bereich H zum Ausbilden einer PMOS-Gateelektrode, und ein n-Typ-Ausbildungsbereich **34a1** mit einer elften Abdeckmaske **39** als eine sechste Maskenschicht abgedeckt.

[0143] Genauer gesagt ist ein PMOSLDD-Ionenimplantationsfenster (ein Ende I der elften Abdeckmaske **39** der Seite des NMOS-Ausbildungsbereichs) auf der Seite des PMOS-Ausbildungsbereichs angeordnet, um zwischen einem p-Typ-Ausbildungsfenster der Gateelektrode (ein Ende G der achten Abdeckmaske **36** auf der Seite des PMOS-Ausbildungsbereichs) und der PMOS-Gateelektrode (ein Ende der Polysiliciumschicht **34**, die auf der Gate-Isolierschicht **33b** auf der Seite des NMOS-Ausbildungsbereichs positioniert ist) positioniert zu werden.

[0144] Dann wird ein Indiumion ( $In^+$ ) als eine sechste Störstelle von oben injiziert, beispielsweise mit der Bedingung 5 keV,  $3 \times 10^{14} \text{ cm}^{-2}$ , um eine Ionenimplantation für ein LDD des PMOS-Transistors durchzuführen.

[0145] Der Grund, das Indiumion ( $In^+$ ) zum Ausbilden des LDD wie oben zu verwenden, liegt darin,

dass es notwendig ist, einen flachen Übergang im Halbleitersubstrat **1** auszubilden. Außerdem bringt die Verwendung des Indiumions ( $\text{In}^+$ ) den Vorteil, dass nicht nur die Ionenimplantationsenergie gering gehalten wird, sondern auch das Element mit einem geringen Widerstand versehen wird, so dass die Ansteuerungskapazität verbessert werden kann.

**[0146]** Es sollte beachtet werden, dass LDD-Implantationsfensterdaten, um das oben beschriebene PMOSLDD-Ionenimplantationsfenster auszubilden, automatisch erzeugt werden können, durch verschieben der p-Typ-Ausbildungsmusterdaten der Gateelektrode.

**[0147]** Dann wird die elfte Abdeckmaske **39** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

**[0148]** Als Nächstes, wie in [Fig. 9C](#) gezeigt, nach einem Abdecken der obersten Flächen und Seitenflächen der Ausbildungsschichten **34a1** und **34b1** der Gateelektrode, um eine Isolierschicht auszubilden, werden anisotropes Ätzen und Ähnliches angewendet, um seitliche Wandabstandshalter **40a** und **40b** an Seitenwänden der Ausbildungsschicht **34a1** und **34b1** der Gateelektrode auszubilden.

**[0149]** Dann werden der p-Typ-Ausbildungsbereich **34b1** der Ausbildungsschichten **34a1** und **34b1** der Gateelektrode, ein Teilbereich eines n-Typ-Ausbildungsbereichs **34a1**, der einen Grenzbereich zwischen **34a1** und **34b1** umfasst, und der seitliche Wandabstandshalter **40b** mit der zwölften Abdeckmaske **41** als eine vierte Maskenschicht abgedeckt.

**[0150]** Genauer gesagt wird ein Ende E der zwölften Abdeckmaske **41** auf der Seite des NMOS-Ausbildungsbereichs so gehandhabt, um zwischen einem n-Typ-Ausbildungsfenster der Gateelektrode (ein Ende F der siebten Abdeckungsmaske **35** auf der Seite des NMOS-Ausbildungsbereichs) und der NMOS-Gateelektrode (ein Ende der Polysiliciumschicht **34**, die auf der Gate-Isolierschicht **33b** auf der Seite des NMOS-Ausbildungsabschnitts positioniert ist) positioniert zu werden, in einer ähnlichen Weise zu dem Fall einer NMOSLDD-Ionenimplantation, die oben beschrieben wird.

**[0151]** Zu diesem Zeitpunkt ist der Abstand zwischen dem n-Typ-Ausbildungsfenster der Gateelektrode (das Ende F der siebten Abdeckmaske **5**) und dem NMOS-Source- und -Drain ausbildenden Ionenimplantationsfenster (das Ende E der zwölften Abdeckmaske **41**) vorzugsweise ungefähr  $0,3 \mu\text{m}$ , beispielsweise in dem Fall eines  $0,25 \mu\text{m}$  Bauelements.

**[0152]** Dann wird ein Arsenion ( $\text{As}^+$ ) von oben injiziert, beispielsweise mit der Bedingung  $15 \text{ keV}$ ,  $2 \times 10^{15} \text{ cm}^{-2}$ , um einen Source-Bereich und einen

Drain-Bereich mit hoher Konzentration im NMOS-Ausbildungsbereich des Halbleitersubstrats (nicht gezeigt) auszubilden.

**[0153]** Der Grund der Verwendung eines Arsenions ( $\text{As}^+$ ), um den Source-Bereich und den Drain-Bereich wie oben auszubilden, liegt darin, dass die erforderliche Ionenimplantationsenergie gering sein kann, und das Element mit einem geringen Widerstand versehen werden kann, so dass die Ansteuerungskapazität verbessert werden kann.

**[0154]** Somit beträgt die Differenz zwischen der Ionenkonzentration  $\text{N}^+$  in einem Bereich, der mit der zwölften Abdeckmaske **41** abgedeckt ist, und der Ionenkonzentration  $\text{N}^{++}$  in einem Bereich, der nicht damit abgedeckt ist, im n-Typ-Ausbildungsbereich **34a1** der Ausbildungsschichten **34a1** und **34b1** der Gateelektrode ungefähr  $2 \times 10^{20} \text{ cm}^{-3}$ .

**[0155]** Die NMOS-Source- und -Drain ausbildenden Implantationsfensterdaten, um Source- und Drain-Bereiche im NMOS-Ausbildungsbereich auszubilden, sind die gleichen wie die LDD-Implantationsfensterdaten, um das oben beschriebene NMOS-LDD-Ionenimplantationsfenster auszubilden.

**[0156]** Dann wird die zwölfte Abdeckmaske **41** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

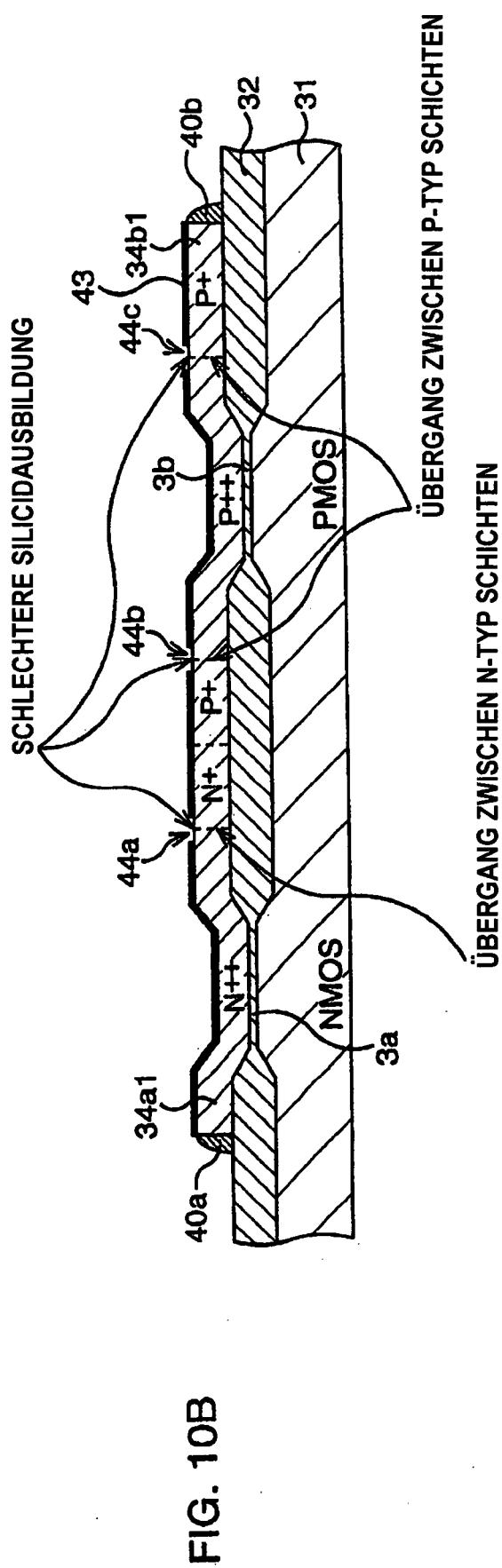

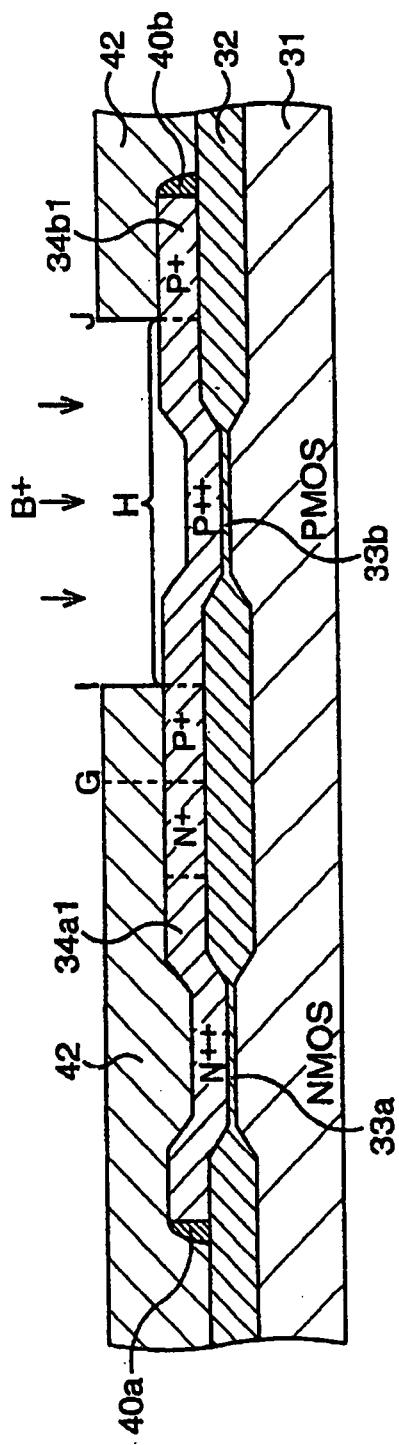

**[0157]** Als Nächstes, wie in [Fig. 10A](#) gezeigt, werden ein p-Typ-Ausbildungsbereich **34b1**, außer einem Bereich G, um eine PMOS-Gateelektrode auszubilden, und ein n-Typ-Ausbildungsbereich **34a1** mit einer dreizehnten Abdeckmaske **42** als eine dritte Maskenschicht abgedeckt.

**[0158]** Genauer gesagt wird ein Ende I der dreizehnten Abdeckmaske **42** der NMOS-Ausbildungsbereichsseite auf der Seite des PMOS-Ausbildungsbereichs so gehandhabt, um zwischen einem p-Typ-Ausbildungsfenster der Gateelektrode (ein Ende G der achten Abdeckmaske **36** auf der Seite des PMOS-Ausbildungsbereichs) und der PMOS-Gateelektrode (ein Ende der Polysiliciumschicht **34**, die auf der Gate-Isolierschicht **33b** auf der Seite des NMOS-Ausbildungsbereichs positioniert ist, positioniert zu werden.

**[0159]** Dann wird ein Borion ( $\text{B}^+$ ) als eine dritte Störstelle von oben injiziert, beispielsweise mit der Bedingung  $5 \text{ keV}$ ,  $2 \times 10^{15} \text{ cm}^{-2}$ . Durch diesen Prozess wird ein Bereich G zum Ausbilden einer PMOS-Gateelektrode in einen p-Typ umgewandelt, und zur gleichen Zeit werden ein Source-Bereich und ein Drain-Bereich mit hoher Konzentration im PMOS-Ausbildungsbereich des Halbleitersubstrats (nicht gezeigt) ausgebildet.

[0160] Somit beträgt die Differenz zwischen der Ionenkonzentration  $P^+$  in einem Bereich, der mit der dreizehnten Abdeckmaske **42** abgedeckt ist, und der Ionenkonzentration  $P^{++}$  in einem Bereich, der nicht damit abgedeckt ist, im p-Typ-Ausbildungsbereich **34b1** der Ausbildungsschichten **34a1** und **34b1** der Gateelektrode ungefähr  $2 \times 10^{20} \text{ cm}^{-3}$ .

[0161] Es sollte beachtet werden, dass Implantationsfensterdaten zur PMOS-Source- und -Drain-Ausbildung, um Source- und Drain-Bereiche im PMOS-Ausbildungsbereich auszubilden, auch automatisch erzeugt werden können, durch Verschieben der p-Typ-Ausbildungsmusterdaten der Gateelektrode.

[0162] Als Nächstes, wie in [Fig. 10B](#) gezeigt, wird eine Ionen-injizierte Störstelle durch Erwärmen eines Elementausbildungsbereichs **31** des Halbleitersubstrats aktiviert. Dann wird Silicid **43** in der Gateelektrode ausgebildet, und die Source- und Drain-Bereiche, indem ein Metall mit einem hohem Schmelzpunkt verwendet wird.

[0163] Zu dieser Zeit, da Carbid in die Oberfläche der Polysiliciumschicht **34** getrieben wird, die an einem Ende E der zehnten Abdeckmaske **38** und der zwölften Abdeckmaske **41** positioniert ist, durch Implantation eines Arsenions ( $\text{As}^+$ ), das in [Fig. 9A](#) und [Fig. 9C](#) gezeigt ist, wird kein Silicid **43** in diesem Abschnitt ausgebildet.

[0164] Da Carbid auch in die Oberfläche der Polysiliciumschicht **34** getrieben wird, die an Enden H und J der elften Abdeckmaske **39** positioniert ist, durch Implantation eines Indiumions ( $\text{In}^+$ ), das in [Fig. 9B](#) gezeigt ist, wird kein Silicid **43** in diesem Abschnitt ausgebildet.

[0165] Jedoch, gemäß dem Herstellungsverfahren im vorliegenden Ausführungsbeispiel, werden Bereiche **44A** bis **44C**, in denen kein Silicid ausgebildet ist, wo das Silicid **43** nicht ausgebildet ist, in der Nähe des zentralen Abschnitts des n-Typ-Ausbildungsbereichs **34a1** oder in der Nähe des zentralen Abschnitts des p-Typ-Ausbildungsbereichs **34b1** der Ausbildungsschichten **34a1** und **34b1** der Gateelektrode ausgebildet.

[0166] Dementsprechend kann ein Bereich **43**, in dem kein Silicid ausgebildet ist, angeordnet werden, um nicht mit einem pn-Übergang der Ausbildungsschichten **34a1** und **34b1** der Gateelektrode zu überlappen, so dass ein Abschnitt, wo der Bereich **43**, in dem kein Silicid ausgebildet ist, ausgebildet ist, mit einem Polysilicium-Widerstand mit einer Konzentration von  $10^{20} \text{ cm}^{-3}$  verbunden werden kann.

[0167] Somit wird im vorliegenden Ausführungsbeispiel, da die Bereiche **44A** bis **44C**, in denen kein Si-

licid ausgebildet wird, nicht mit einem pn-Übergang der Ausbildungsbereiche **34a1** und **34b1** der Gateelektrode überlappen, so dass eine Silicidschicht **43** am pn-Übergang ausgebildet wird, keine parasitäre Diode, die aus dem pn-Übergang besteht, an der Gateelektrode im PMOS-Transistor mit einer Doppelgatestuktur ausgebildet, was einen Widerstand im Bereich **44**, in dem kein Silicid ausgebildet ist, daran hindert, anzusteigen.

[0168] Es sollte beachtet werden, dass, obwohl in dem vorliegenden Ausführungsbeispiel ein Phosphorion als eine erste Störstelle verwendet wird, und Arsenionen als zweite und vierte Störstellen verwendet werden, die erste Störstelle und die zweiten und vierten Störstellen nicht darauf beschränkt sind. Jede Substanz wird akzeptabel sein, vorausgesetzt, dass die Masse des Elements, das die erste Störstelle bildet, geringer ist als die Masse des Elements, das die zweite und vierte Störstelle bildet.

[0169] Obwohl Borionen als die dritten und fünften Störstellen verwendet werden, und ein Indiumion als die sechste Störstelle verwendet wird, sind die dritten und fünften Störstellen und die sechste Störstelle nicht darauf beschränkt. Jede Substanz wird akzeptabel sein, vorausgesetzt, dass die Masse des Elements das die dritten und fünften Störstellen bildet, geringer ist als die Masse des Elements, das die sechste Störstelle bildet.

#### – Viertes Ausführungsbeispiel –

[0170] Ein vierter Ausführungsbeispiel des Halbleiterbauelements der vorliegenden Erfindung und eines Herstellungsverfahrens davon wird als Nächstes erklärt werden.

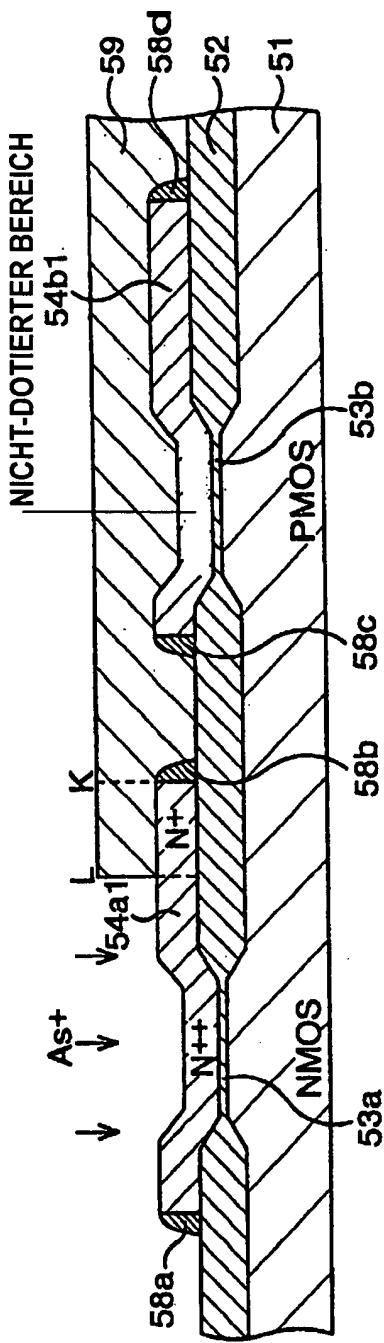

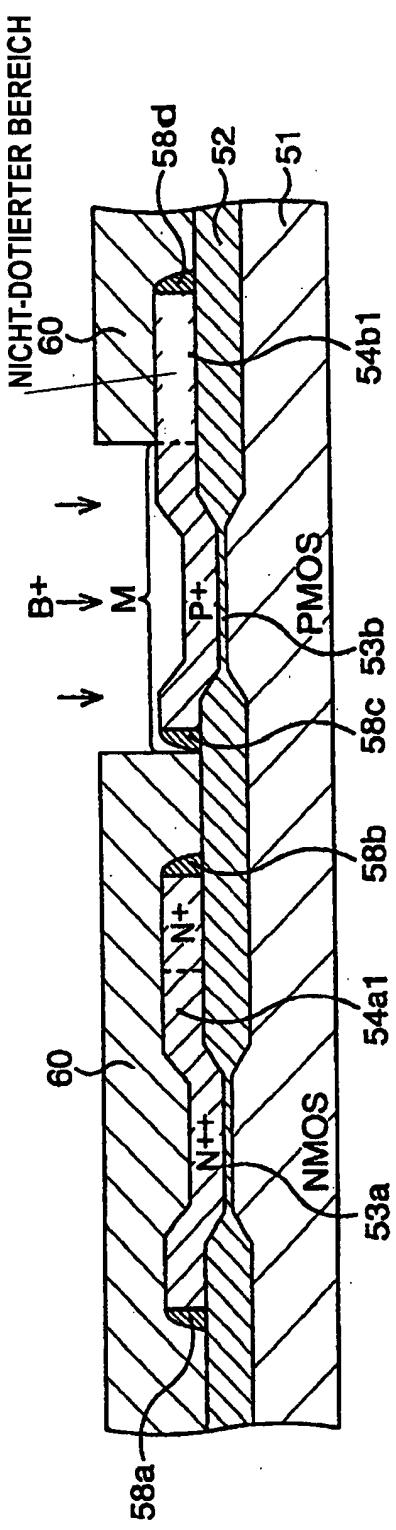

[0171] [Fig. 11A](#), [Fig. 11B](#) und [Fig. 11C](#) und [Fig. 12A](#), [Fig. 12B](#) und [Fig. 12C](#) sind schematische Schnittansichten, welche ein Herstellungsverfahren eines Halbleiterbauelements gemäß dem vorliegenden Ausführungsbeispiel zeigen, in der Reihenfolge seiner Prozesse.

[0172] Wie in [Fig. 11A](#) gezeigt, nach einem Ausbilden einer Gate-Isolierschicht auf einem Elementausbildungsbereich **51** eines Halbleitersubstrats, wird eine Feldisolierschicht **52** ausgebildet, so dass eine Gate-Isolierschicht **53a** eines NMOS-Ausbildungsbereichs und eine Gate-Isolierschicht **53b** eines PMOS-Ausbildungsbereichs voneinander getrennt werden.

[0173] Dann, nachdem eine Polysiliciumschicht **54** auf die Gate-Isolierschichten **53a** und **53b** und die Feldisolierschicht **52** geschichtet wurde, wird ein PMOS-Ausbildungsabschnitt **54b** der Polysiliciumschicht **54** mit einer vierzehnten Abdeckmaske **55** als eine erste Abdeckschicht abgedeckt, um ein

n-Typ-Ausbildungsfenster der Gateelektrode auszubilden.

**[0174]** Dann wird ein Phosphorion ( $P^+$ ) als eine erste Störstelle injiziert, beispielsweise mit der Bedingung 20 keV,  $4 \times 10^{15} \text{ cm}^{-2}$ , von oben, um einen NMOS-Ausbildungsbereich **54a** der Polysilicium-Gateschicht **54** in einen n-Typ umzuwandeln. Dann wird die vierzehnte Abdeckmaske **55** abgeblättert, und der abgeblätterte Abschnitt wird gewaschen.

**[0175]** Als Nächstes, wie in [Fig. 11B](#) gezeigt, wird ein Gate-Ausbildungsbereich der Polysiliciumschicht **54** mit einer Abdeckmaske **56** abgedeckt, und die Polysiliciumschicht **54** ist gemustert, um eine NMOS-Gateelektroden-ausbildende Schicht **54a1** und eine PMOS-Gateelektroden-ausbildende Schicht **54b1** auszubilden. Dann wird die fünfzehnte Abdeckmaske **56** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

**[0176]** Als Nächstes, wie in [Fig. 11C](#) gezeigt, um einen LDD im NMOS-Ausbildungsbereich auszubilden, wird eine PMOS-Gateelektroden-ausbildende Schicht **54b1** und ein Bereich einer NMOS-Gateelektroden-ausbildenden Schicht **54a1** auf der Seite der PMOS-Gateelektroden-ausbildenden Schicht **54b1** mit einer sechzehnten Abdeckmaske **57** als eine zweite Maskenschicht abgedeckt.

**[0177]** Genauer gesagt ist ein NMOSLDD-Ionenimplantationsfenster (ein Ende L der sechzehnten Abdeckmaske **57** auf der Seite des NMOS-Ausbildungsbereichs), um den LDD im NMOS-Ausbildungsbereich auszubilden, angeordnet, um zwischen dem n-Typ-Ausbildungsfenster der Gateelektrode (ein Ende K der vierzehnten Abdeckmaske **55** auf der Seite des NMOS-Ausbildungsbereichs) und der NMOS-Gateelektrode (ein Ende der Polysiliciumschicht **54**, die auf der Gate-Isolierschicht **53a** auf der Seite des PMOS-Ausbildungsbereichs positioniert ist) positioniert zu werden.

**[0178]** Dann wird ein Arsenion ( $As^+$ ) als eine zweite Störstelle injiziert, beispielsweise mit der Bedingung 10 keV,  $3 \times 10^{14} \text{ cm}^{-2}$ , von oben, um eine Ionenimplantation für einen LDD des NMOS-Transistors durchzuführen.

**[0179]** Dann wird die sechzehnte Abdeckmaske **57** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

**[0180]** Als Nächstes, wie in [Fig. 12A](#) gezeigt, nachdem seitliche Wandabstandshalter **58a** bis **58d** an Seitenwänden einer NMOS-Gateelektroden-ausbildenden Schicht **54a** und einer PMOS-Gateelektroden-ausbildenden Schicht **54b** ausgebildet werden, wird eine siebzehnte Abdeckungsmaske **59** als eine vierte Maskenschicht ausgebildet, um die PMOS-Ga-

teelektroden-ausbildende Schicht **54b1** und einen Teilbereich der NMOS-Gateelektroden-ausbildenden Schicht **54a1** auf der Seite des PMOS-Ausbildungsbereichs von oben abzudecken.

**[0181]** Genauer gesagt ist ein Ende L der siebzehnten Abdeckmaske **59** auf der Seite des NMOS-Ausbildungsbereichs angeordnet, um zwischen einem n-Typ-Ausbildungsfenster der Gateelektrode (ein Ende K der vierzehnten Abdeckmaske **55** auf der Seite des NMOS-Ausbildungsbereichs) und einer NMOS-Gateelektrode (ein Ende der Polysiliciumschicht **54**, welche auf der Gate-Isolierschicht **53a** auf der Seite des PMOS-Ausbildungsbereichs positioniert ist) positioniert zu werden, in einer ähnlichen Weise zu dem Fall der oben beschriebenen NMOS-LDD-Ionenimplantation.

**[0182]** Dann wird ein Arsenion ( $As^+$ ) als eine vierte Störstelle von oben injiziert, beispielsweise mit der Bedingung 40 keV,  $20 \times 10^{15} \text{ cm}^{-2}$ . Um einen Source-Bereich und einen Drain-Bereich mit hoher Konzentration im NMOS-Ausbildungsbereich des Halbleitersubstrats (nicht gezeigt) auszubilden.

**[0183]** Somit beträgt die Differenz zwischen der Ionenkonzentration  $N^+$  in einem Bereich, der mit der siebzehnten Abdeckmaske **59** abgedeckt ist, und der Ionenkonzentration  $N^{++}$  in einem Bereich, der nicht damit abgedeckt ist, in der NMOS-Gateelektroden-ausbildenden Schicht **54a1** ungefähr  $1,5 \times 10^{20} \text{ cm}^{-3}$ .

**[0184]** Dann wird die siebzehnte Abdeckmaske **59** abgeblättert und der abgeblätterte Abschnitt wird gewaschen.

**[0185]** Als Nächstes, wie in [Fig. 12B](#) gezeigt, wird ein Bereich, außer einem Bereich M zum Ausbilden der PMOS-Gateelektrode, mit einer achtzehnten Abdeckmaske **60** als eine dritte Maskenschicht abgedeckt.

**[0186]** Dann wird ein Borion ( $B^+$ ) als eine dritte Störstelle von oben injiziert, beispielsweise mit der Bedingung 7 keV,  $2 \times 10^{15} \text{ cm}^{-2}$ . Durch diesen Prozess wird eine PMOS-Gateelektroden-ausbildende Schicht **54b1** zum Ausbilden der PMOS-Gateelektrode in einen p-Typ umgewandelt, und zur gleichen Zeit werden ein Source-Bereich und ein Drain-Bereich mit hoher Konzentration im PMOS-Ausbildungsbereich des Halbleitersubstrats (nicht gezeigt) ausgebildet.

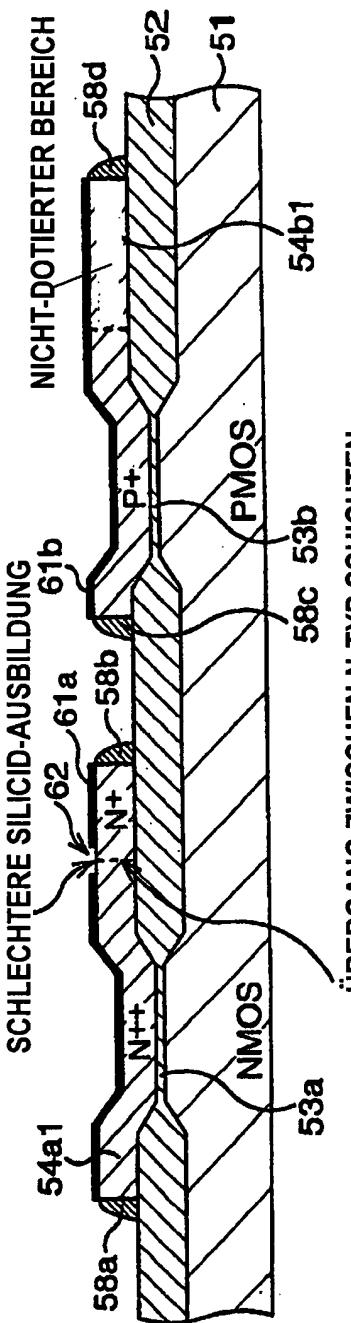

**[0187]** Als Nächstes, wie in [Fig. 12C](#) gezeigt, wird eine Ionen-injizierte Störstelle durch Erwärmen eines Elementausbildungsbereichs **51** des Halbleitersubstrats aktiviert. Dann werden Silicide **61a** und **61b** in der Gateelektrode ausgebildet, und die Source- und Drain-Bereiche, indem ein Metall mit einem hohem Schmelzpunkt verwendet wird.

**[0188]** Zu diesem Zeitpunkt, da Carbid in die Oberfläche der Polysiliciumschicht getrieben wird, die an dem Ende M der siebzehnten Abdeckmaske **57** positioniert ist, durch die Arsenion-(As<sup>+</sup>)-Injektion, die in **Fig. 12A** gezeigt ist, wird das Silicid **61a** in diesem Abschnitt nicht ausgebildet.

**[0189]** Jedoch wird gemäß dem Verfahren des vorliegenden Ausführungsbeispiels ein Bereich **62**, in dem kein Silicid ausgebildet ist, wo das Silicid **61a** nicht ausgebildet ist, auf der NMOS-Gateelektroden-ausbildenden Schicht **54a1** ausgebildet.

**[0190]** Dementsprechend kann ein Bereich **62**, in dem kein Silicid ausgebildet ist, angeordnet werden, um nicht mit einem pn-Übergang der Ausbildungsschichten **54a1** und **54b1** der Gateelektrode zu überlappen, und ein Abschnitt, in dem der Bereich **62**, in dem kein Silicid ausgebildet ist, ausgebildet ist, kann mit einem Polysilicium-Widerstand mit einer Konzentration von  $10^{20} \text{ cm}^{-3}$  verbunden werden.

**[0191]** Somit kann selbst in einem Halbleiterbauelement, in welchem ein NMOS-Transistor und ein PMOS-Transistor nicht mit dem gleichen Polysilicium ausgebildet sind, ein Bereich **62**, in dem kein Silicid ausgebildet ist, auf einem n-Typ-Ausbildungsbereich ausgebildet werden (Ausbildungsschicht **54a1** der NMOS-Gateelektrode), ähnlich zu dem Fall des CMOS-Transistors in den ersten und dritten Ausführungsbeispielen des vorliegenden Ausführungsbeispiels, und der Bereich **62**, in dem kein Silicid ausgebildet ist, ist nicht auf dem pn-Übergang positioniert.

**[0192]** Die Ausbildung einer parasitären Diode, die aus dem pn-Übergang besteht, an der Gateelektrode kann verhindert werden, und ein Widerstand im Bereich **62**, in dem kein Silicid ausgebildet ist, kann daran gehindert werden, anzusteigen.

**[0193]** Außerdem kann im PMOS-Transistor im vorliegenden Ausführungsbeispiel das Silicid **61b** perfekt auf der Ausbildungsschicht **54b1** der PMOS-Gateelektrode ausgebildet werden. Dementsprechend kann ein nachteiliger Einfluss auf den Betrieb des Halbleiterbauelements aufgrund der Silicid-Ausbildung komplett eliminiert werden.

**[0194]** Es sollte beachtet werden, dass selbst in dem vorliegenden Ausführungsbeispiel, obwohl ein Phosphorion als die erste Störstelle und ein Arsenion als die zweite und vierte Störstelle verwendet werden, ähnlich zu den ersten und zweiten Ausführungsbeispielen, die erste Störstelle und die zweite Störstelle nicht auf diese beschränkt sind, und jede Substanz akzeptabel sein wird, vorausgesetzt, dass die Masse des Elements, das die erste Störstelle bildet, kleiner ist als die Masse des Elements, das die zweite Störstelle bildet.

**[0195]** Des Weiteren ist in den oben beschriebenen ersten und vierten Ausführungsbeispielen, obwohl eine Polysiliciumschicht als ein Material für die Gateelektrode verwendet wird, das Material für die Gateelektrode nicht auf die Polysiliciumschicht beschränkt, und jedes Material wird akzeptabel sein, vorausgesetzt, dass es eine Halbleiterschicht ist.