(19)中華民國智慧財產局

(12)發明說明書公告本 (11)證書號數：TW 1657539 B

(45)公告日：中華民國 108 (2019) 年 04 月 21 日

(21)申請案號：106137190

(22)申請日：中華民國 102 (2013) 年 08 月 06 日

(51)Int. Cl. : H01L21/77 (2017.01)

H01L27/12 (2006.01)

G02F1/136 (2006.01)

(30)優先權：2012/08/31 日本

2012-192214

2013/03/15 日本

2013-054021

(71)申請人：日商半導體能源研究所股份有限公司 (日本) SEMICONDUCTOR ENERGY

LABORATORY CO., LTD. (JP)

日本

(72)發明人：山崎舜平 YAMAZAKI, SHUNPEI (JP) ; 片山雅博 KATAYAMA, MASAHIRO

(JP) ; 佐藤亞美 SATO, AMI (JP) ; 島行徳 SHIMA, YUKINORI (JP)

(74)代理人：林志剛

(56)參考文獻：

US 2007215945A1

US 2009141203A1

US 2012062813A1

審查人員：吳松屏

申請專利範圍項數：10 項 圖式數：32 共 153 頁

(54)名稱

半導體裝置

SEMICONDUCTOR DEVICE

(57)摘要

本發明的一個方式是提供一種不降低孔徑比且具有增大了電荷容量的電容元件的半導體裝置。半導體裝置包括：包括具有透光性的半導體膜的電晶體；在一對電極之間設置有介電膜的電容元件；以及電連接於電晶體的像素電極，其中在電容元件中，與電晶體的具有透光性的半導體膜形成在同一表面上的具有導電性的膜用作一個電極，像素電極用作另一個電極，設置在具有透光性的半導體膜與像素電極之間的氮化絕緣膜及第二氧化絕緣膜用作介電體。

A semiconductor device including a capacitor having an increased charge capacity without decreasing an aperture ratio is provided. The semiconductor device includes a transistor including a light-transmitting semiconductor film, a capacitor in which a dielectric film is provided between a pair of electrodes, and a pixel electrode electrically connected to the transistor. In the capacitor, a conductive film formed on the same surface as the light-transmitting semiconductor film in the transistor serves as one electrode, the pixel electrode serves as the other electrode, and a nitride insulating film and a second oxide insulating film which are provided between the light-transmitting semiconductor film and the pixel electrode serve as the a dielectric film.

指定代表圖：

## 符號簡單說明：

圖 3

- 102 · · · 基板

- 103 · · · 電晶體

- 105 · · · 電容元件

- 107 · · · 掃描線

- 109 · · · 信號線

- 111 · · · 半導體膜

- 113 · · · 導電膜

- 115 · · · 電容線

- 119 · · · 半導體膜

- 121 · · · 像素電極

- 123 · · · 開口

- 125 · · · 導電膜

- 127 · · · 閘極絕緣膜

- 129 · · · 絝緣膜

- 131 · · · 絝緣膜

- 132 · · · 絝緣膜

- 137 · · · 絝緣膜

- 623 · · · 電晶體

- 627 · · · 閘極電極

- 629 · · · 源極電極

- 631 · · · 半導體膜

- 633 · · · 汲極電極

- 641 · · · 導電膜

# 發明專利說明書

(本說明書格式、順序，請勿任意更動)

## 【發明名稱】(中文/英文)

半導體裝置

Semiconductor device

## 【技術領域】

本說明書等所公開的發明係關於一種半導體裝置。

## 【先前技術】

近年來，液晶顯示器（LCD）等的平板顯示器得到廣泛普及。在平板顯示器等的顯示裝置中，行方向及列方向配置的像素內設置有：作為切換元件的電晶體；與該電晶體電連接的液晶元件；以及與該液晶元件並聯連接的電容元件。

作為構成該電晶體的半導體膜的半導體材料，通常使用非晶矽或多晶矽等的矽半導體。

另外，呈現半導體特性的金屬氧化物（以下也稱為氧化物半導體）也是能夠用作電晶體的半導體膜的半導體材料。例如，已公開有一種使用氧化鋅或 In-Ga-Zn 類氧化物半導體製造電晶體的技術（參照專利文獻 1 及專利文獻 2）。

[專利文獻 1]日本專利申請公開第 2007-123861 號公報

[專利文獻 2]日本專利申請公開第 2007-96055 號公報

一般地，在電容元件中，在一對電極之間設置有介電膜，一對電極中的至少一個電極是由構成電晶體的閘極電極、源極電極或汲極電極等具有遮光性的導電膜形成的。

另外，電容元件的電容值越大，在施加電場的情況下，能夠將液晶元件的液晶分子的配向保持為固定的期間越長。在顯示靜態影像的顯示裝置中，能夠延長該期間意味著可以減少重寫影像資料的次數，從而可以降低耗電量。

為了增大電容元件的電荷容量，可以增大電容元件的佔有面積，具體地可以增大一對電極彼此重疊的面積。但是，在上述顯示裝置中，當為了增大一對電極彼此重疊的面積而增大具有遮光性的導電膜的面積時，像素的孔徑比降低，影像顯示品質下降。

### 【發明內容】

於是，鑒於上述課題，本發明的一個方式的課題之一是提供孔徑比高且包括能夠增大電荷容量的電容元件的半導體裝置。

本發明的一個方式是一種設置有電晶體及具有透光性的電容元件的半導體裝置。明確而言，在該電容元件中，具有透光性的半導體膜用作一個電極，像素電極等的具有透光性的導電膜用作該電容元件的另一個電極，具有透光性的絕緣膜用作介電膜。該具有透光性的絕緣膜是依次層疊有第一氧化絕緣膜、氮化絕緣膜及第二氧化絕緣膜的絕

緣膜。

本發明的一個方式是一種半導體裝置，包括：包括具有透光性的半導體膜的電晶體；在一對電極之間設置有介電膜的電容元件；以及電連接於電晶體的像素電極，其中，在電容元件中，與電晶體的具有透光性的半導體膜形成在同一表面上的具有透光性的半導體膜用作一個電極，像素電極用作另一個電極，設置在具有透光性的半導體膜上的具有透光性的絕緣膜用作介電膜，該具有透光性的絕緣膜是依次層疊有第一氧化絕緣膜、氮化絕緣膜及第二氧化絕緣膜的絕緣膜。

第一氧化絕緣膜是藉由使用含矽的沉積氣體及氧化氣體的化學氣相沉積法形成的氧化絕緣膜。氮化絕緣膜是藉由化學氣相沉積法或物理氣相沉積法形成的氮化絕緣膜。第二氧化絕緣膜是藉由使用有機矽烷氣體的化學氣相沉積法形成的氧化絕緣膜。

藉由在氮化絕緣膜上利用使用有機矽烷氣體的化學氣相沉積法形成氧化絕緣膜，可以提高設置有電晶體及電容元件的元件部的表面的平坦性。此外，藉由在電晶體與利用使用有機矽烷氣體的化學氣相沉積法形成的氧化絕緣膜之間設置氮化絕緣膜，可以防止包含在該氧化絕緣膜中的碳等雜質移動到電晶體，可以減少電晶體的偏差。

此外，具有透光性的半導體膜可以使用氧化物半導體形成。這是因為氧化物半導體的能隙大，即  $3.0\text{eV}$  以上，對於可見光的穿透率大的緣故。

具有透光性的電容元件可以利用電晶體的製程製造。電容元件的一個電極可以利用形成電晶體的具有透光性的半導體膜的製程，電容元件的介電膜可以利用形成設置在電晶體的具有透光性的半導體膜上的絕緣膜的製程，電容元件的另一個電極可以利用形成電連接於電晶體的像素電極的製程。由此，包括在電晶體中的具有透光性的半導體膜及電容元件的一個電極由同一金屬元素構成。

當作為電容元件的一個電極使用在形成電晶體的具有透光性的半導體膜的製程中形成的半導體膜時，也可以增大該半導體膜的導電率。例如，較佳的是在半導體膜中添加選自硼、氮、氟、鋁、磷、砷、銦、錫及稀有氣體元素中的一種以上。此外，作為在該半導體膜中添加上述元素的方法，有離子植入法或離子摻雜法等，藉由將該半導體膜暴露於包含上述元素的電漿也可以添加上述元素。此時，電容元件的一個電極為  $n$  型的半導體膜，其導電率為  $10S/cm$  以上且  $1000S/cm$  以下，較佳為  $100S/cm$  以上且  $1000S/cm$  以下。

藉由採用上述結構，由於電容元件具有透光性，所以可以在像素內的形成有電晶體的區域以外的區域大面積地形成電容元件。因此，可以獲得提高了孔徑比且增大了電荷容量的半導體裝置。其結果是，可以獲得顯示品質優良的半導體裝置。

在電容元件中，由於介電膜使用設置在電晶體的具有透光性的半導體膜上的絕緣膜，所以可以採用與該絕緣膜

相同的疊層結構。例如，當作為設置在電晶體的具有透光性的半導體膜上的絕緣膜使用依次層疊有第一氧化絕緣膜、氮化絕緣膜及第二氧化絕緣膜的絕緣膜時，作為電容元件的介電膜可以使用依次層疊有第一氧化絕緣膜、氮化絕緣膜及第二氧化絕緣膜的絕緣膜。

在電容元件中，當作為設置在電晶體的具有透光性的半導體膜上的絕緣膜使用依次層疊有第一氧化絕緣膜、氮化絕緣膜及第二氧化絕緣膜的絕緣膜時，在形成該氧化絕緣膜之後只在形成有電容元件的區域去除該第一氧化絕緣膜，可以作為電容元件的介電膜使用氮化絕緣膜及第二氧化絕緣膜。換言之，該氮化絕緣膜接觸於用作電容元件的一對電極的半導體膜。由於半導體膜使用氧化物半導體形成，所以藉由氮化絕緣膜與半導體膜接觸，在該氮化絕緣膜與該半導體膜之間的界面形成缺陷能階（界面能階）。或者/加上藉由利用電漿 CVD 法或濺射法形成氮化絕緣膜，該半導體膜暴露於電漿，生成氧缺陷。再者，包含在該氮化絕緣膜中的氮或/及氫移動到該半導體膜。在缺陷能階或氧缺陷中進入包含在氮化絕緣膜中的氫，生成作為載子的電子。其結果是，該半導體膜的導電率增大，成為  $n$  型，並成為具有導電性的膜。即，可以形成具有作為導體的特性的金屬氧化物膜。此外，由於可以使介電膜的厚度減薄，所以可以增大電容元件的電荷容量。

如上所述，在電容元件中，藉由採用氮化絕緣膜接觸於上述半導體膜的結構，可以省略將增大導電率的元素添

加到上述半導體膜的製程諸如離子植入法或離子摻雜法等，提高半導體裝置的良率，從而可以降低製造成本。

此外，當使用氧化物半導體形成電晶體的具有透光性的半導體膜，依次層疊有第一氧化絕緣膜、氮化絕緣膜及第二氧化絕緣膜的絕緣膜是設置在該具有透光性的半導體膜上的絕緣膜時，該氧化絕緣膜較佳的是不容易透過氮及氬，即阻擋氮。

藉由採用上述結構，可以抑制氮及氬中的一者或兩者擴散到電晶體的具有透光性的半導體膜，可以抑制電晶體的電特性變動。

在上述結構中，本發明的一個方式的半導體裝置設置有包括電晶體的閘極電極的掃描線、在平行於掃描線的方向上延伸且與掃描線設置於同一表面上的電容線。電容元件的一個電極（半導體膜）藉由當形成電晶體的源極電極或汲極電極時可以形成的導電膜電連接於電容線。或者，使用包括在電容元件中的半導體膜形成電容線。

此外，電容線不侷限於在平行於掃描線的方向上延伸且與掃描線設置於同一表面上，也可以在平行於包括電晶體的源極電極或汲極電極的信號線的方向上延伸且與信號線設置於同一表面上，並電連接於電容元件的一個電極（半導體膜）。

此外，電容線也可以分別連接於包括在相鄰的像素中的電容元件。此時，也可以在相鄰的像素之間設置有電容線。

此外，當作為電容元件的一個電極使用與電晶體的具有透光性的半導體膜一起形成的半導體膜時，連接於該半導體膜及電容線的導電膜也可以以接觸於該半導體膜的端部的方式設置，例如也可以沿著該半導體膜的外周接觸的方式設置。藉由採用上述結構，可以增大該半導體膜的導電性。

另外，本發明的一個方式的半導體裝置的製造方法也屬於本發明的一個方式。

根據本發明的一個方式，可以提供一種孔徑比高且具有增大了電荷容量的電容元件的半導體裝置。

### 【圖式簡單說明】

在圖式中：

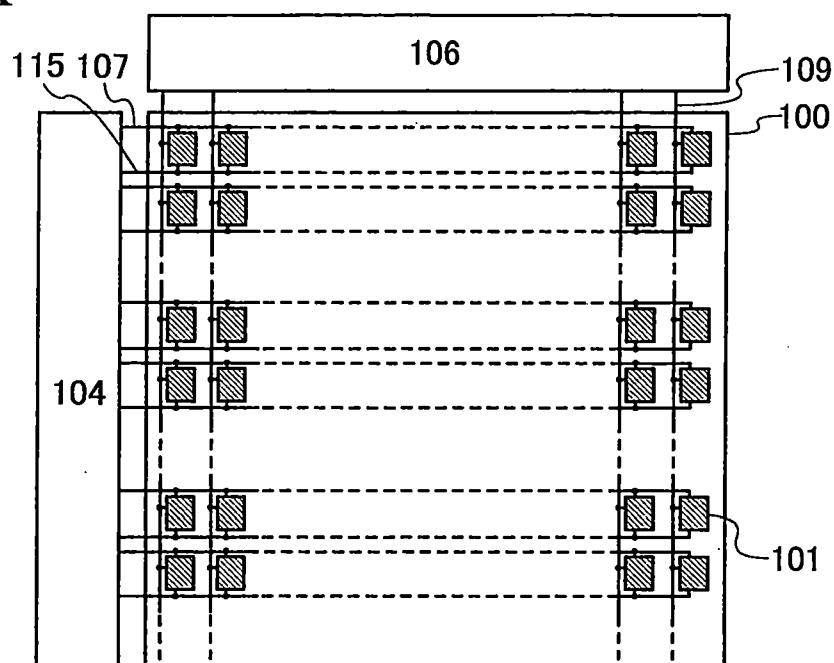

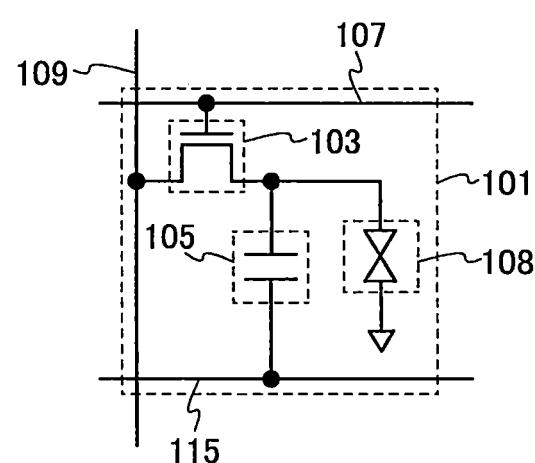

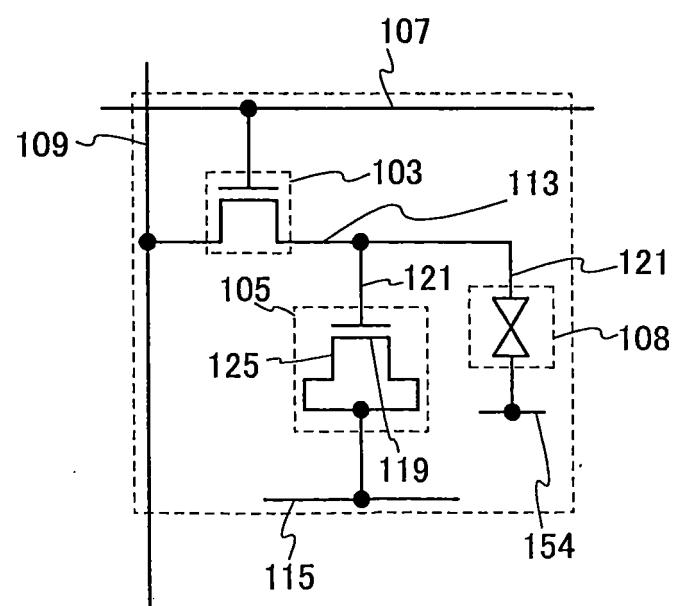

圖 1A 至圖 1C 是說明本發明的一個方式的半導體裝置的圖及像素的電路圖；

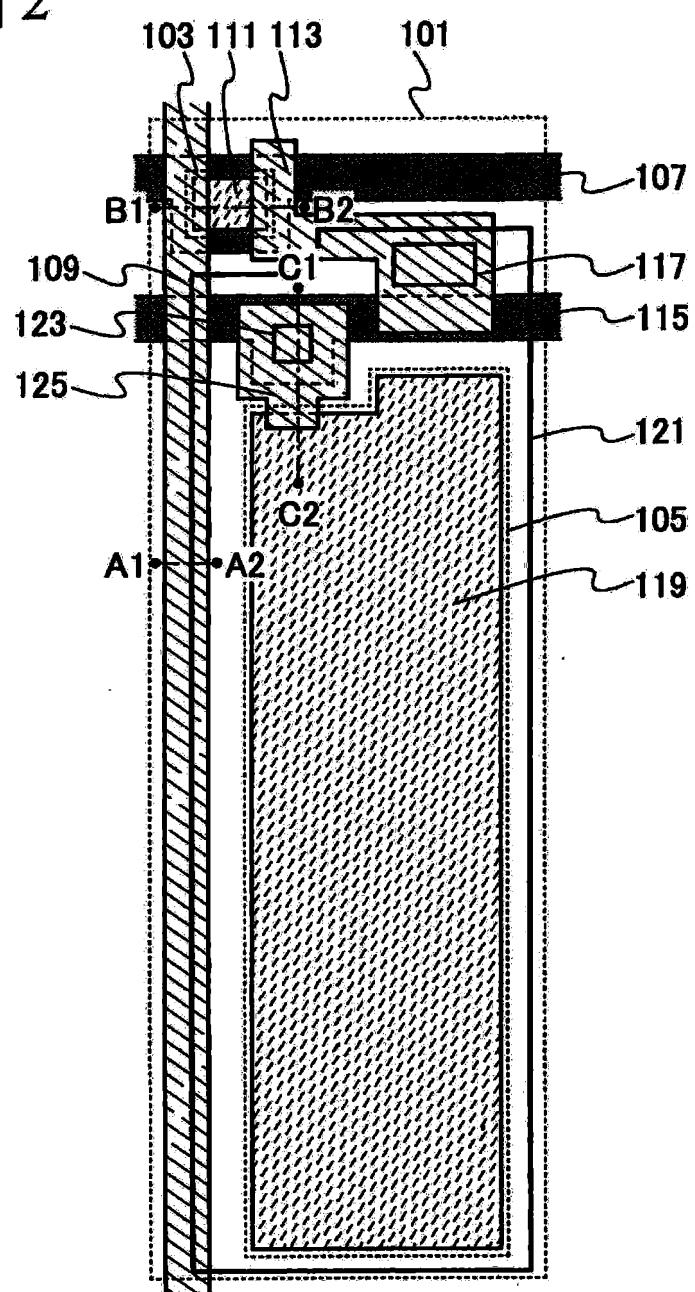

圖 2 是說明本發明的一個方式的半導體裝置的俯視圖；

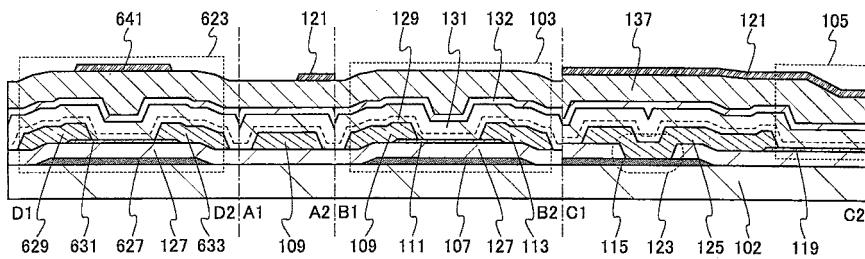

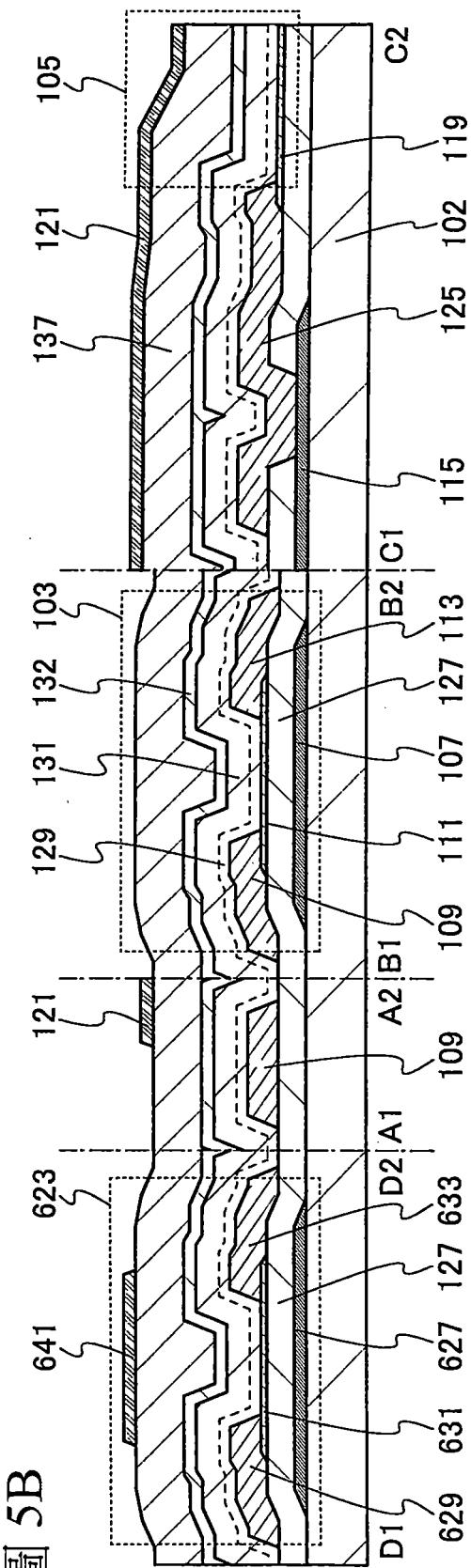

圖 3 是說明本發明的一個方式的半導體裝置的剖面圖；

圖 4A 和圖 4B 是說明本發明的一個方式的半導體裝置的製造方法的剖面圖；

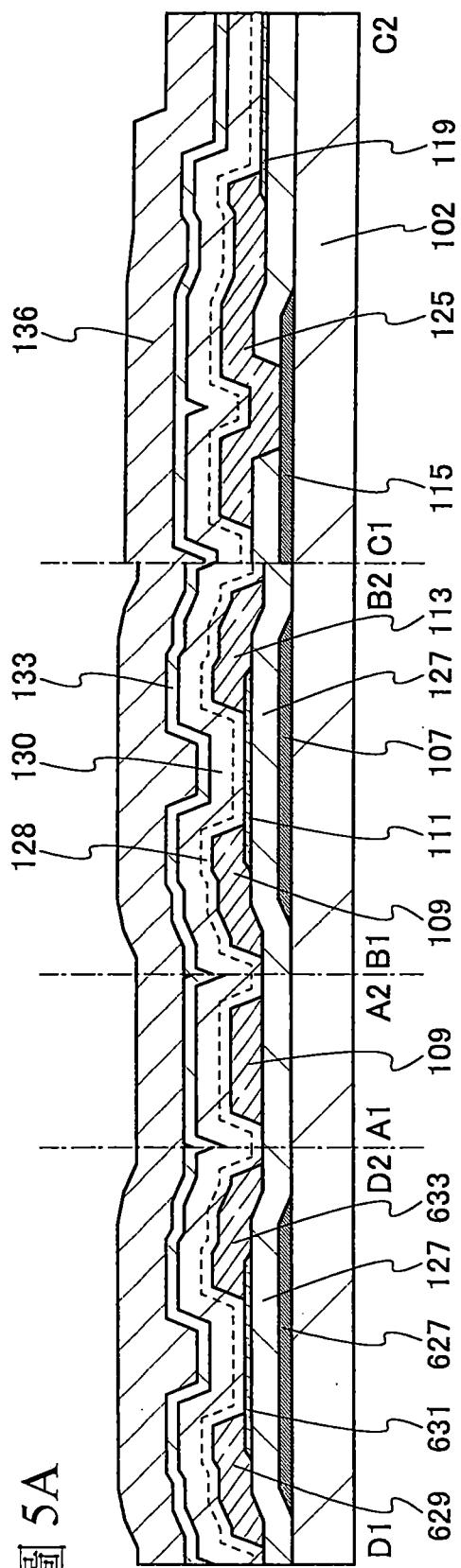

圖 5A 和圖 5B 是說明本發明的一個方式的半導體裝置的製造方法的剖面圖；

圖 6 是說明本發明的一個方式的半導體裝置的俯視

圖；

圖 7 是說明本發明的一個方式的半導體裝置的俯視圖；

圖 8 是說明本發明的一個方式的半導體裝置的俯視圖；

圖 9 是說明本發明的一個方式的半導體裝置的俯視圖；

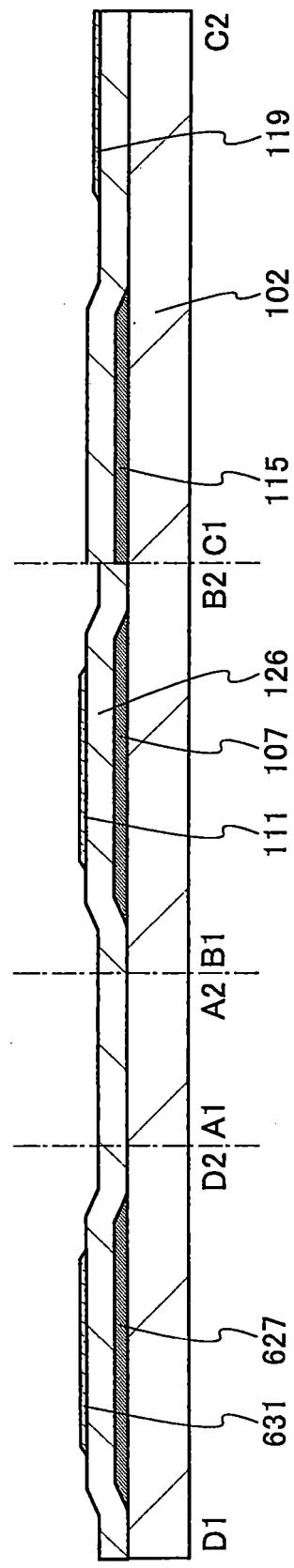

圖 10 是說明本發明的一個方式的半導體裝置的剖面圖；

圖 11A 和圖 11B 是說明本發明的一個方式的半導體裝置的製造方法的剖面圖；

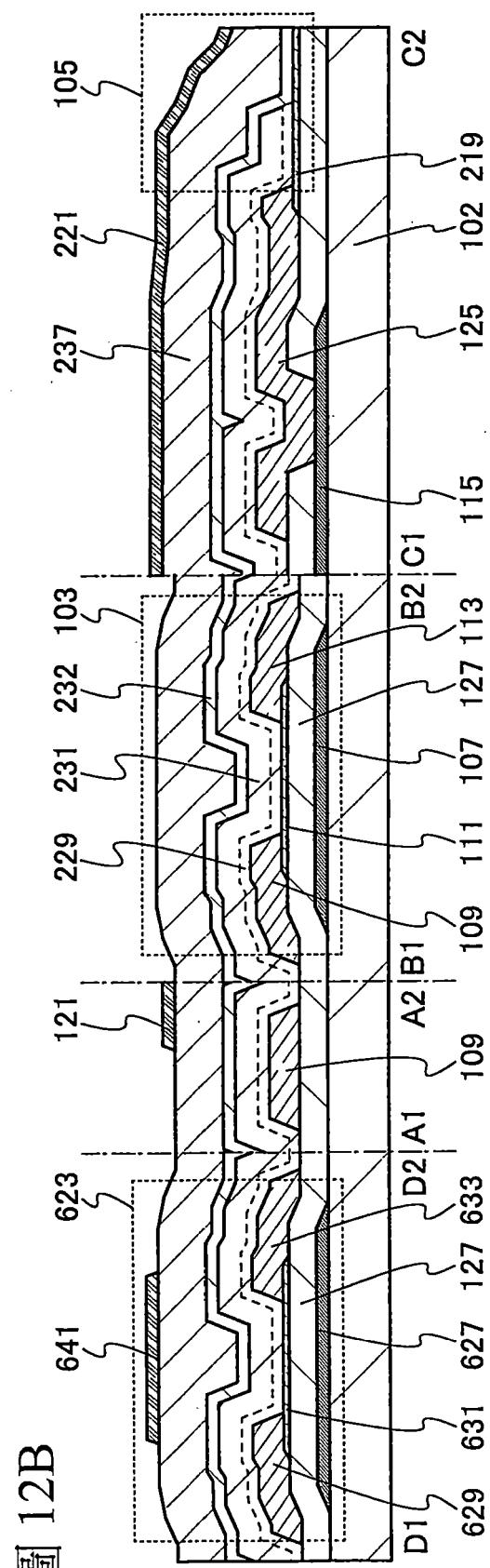

圖 12A 和圖 12B 是說明本發明的一個方式的半導體裝置的製造方法的剖面圖；

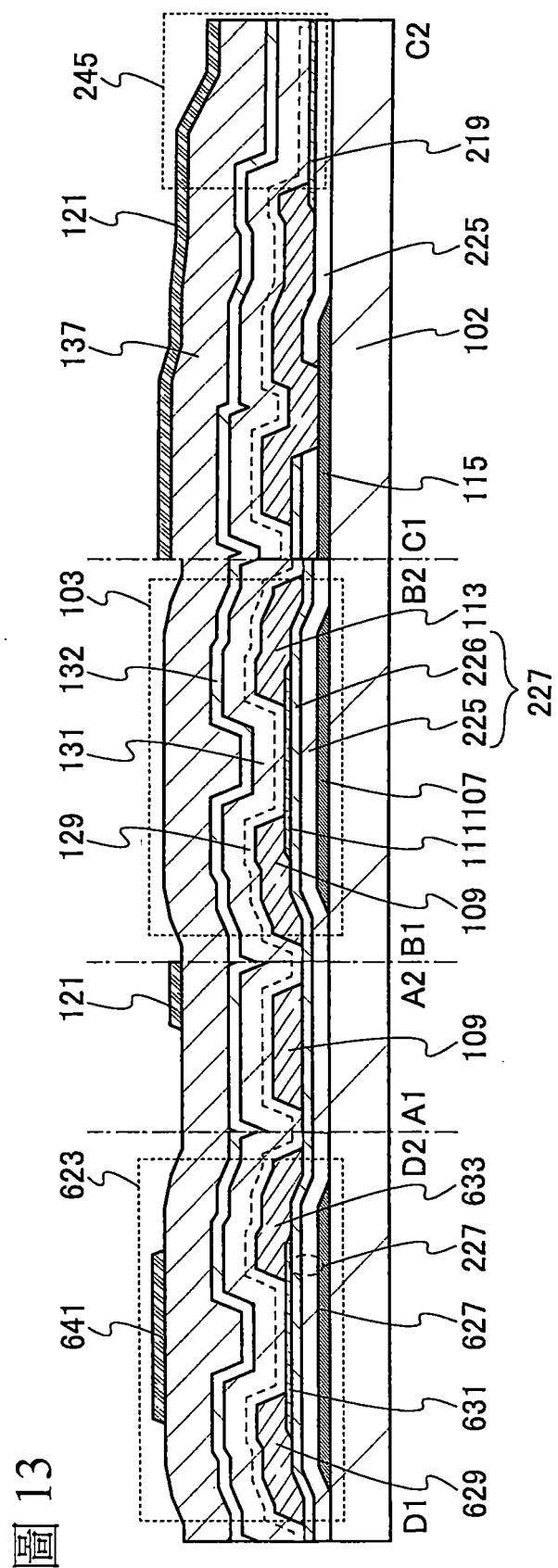

圖 13 是說明本發明的一個方式的半導體裝置的製造方法的剖面圖；

圖 14 是說明本發明的一個方式的半導體裝置的俯視圖；

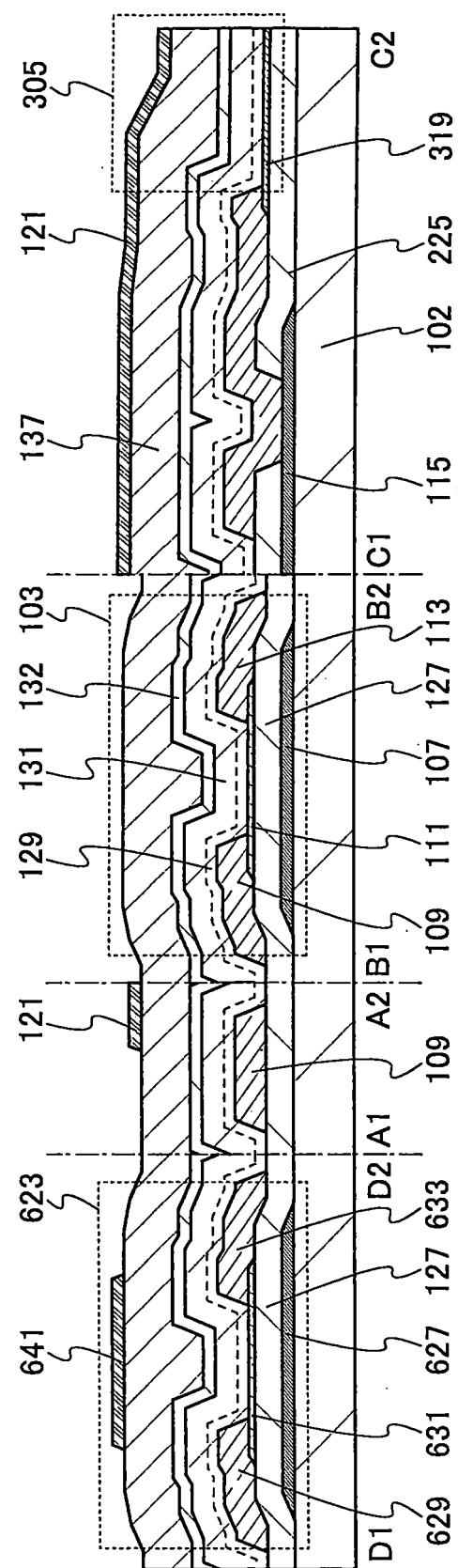

圖 15 是說明本發明的一個方式的半導體裝置的剖面圖；

圖 16A 和圖 16B 是說明本發明的一個方式的半導體裝置的製造方法的剖面圖；

圖 17A 和圖 17B 是說明本發明的一個方式的半導體裝置的製造方法的剖面圖；

圖 18 是說明本發明的一個方式的半導體裝置的剖面

圖；

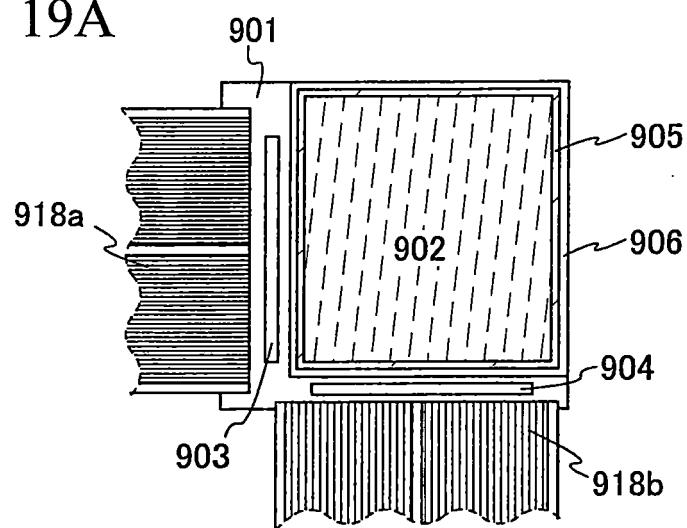

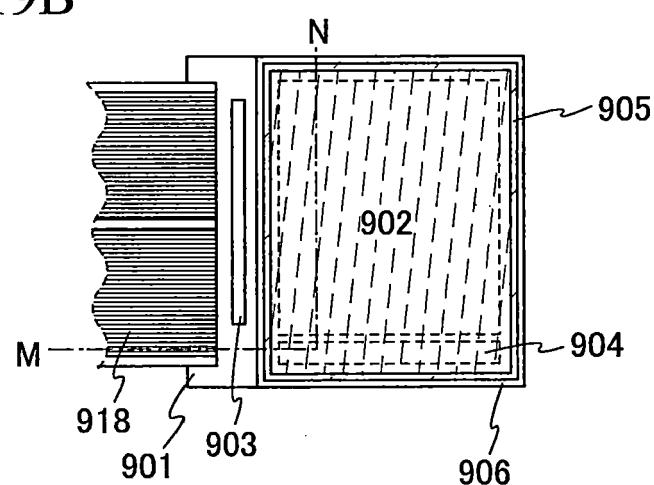

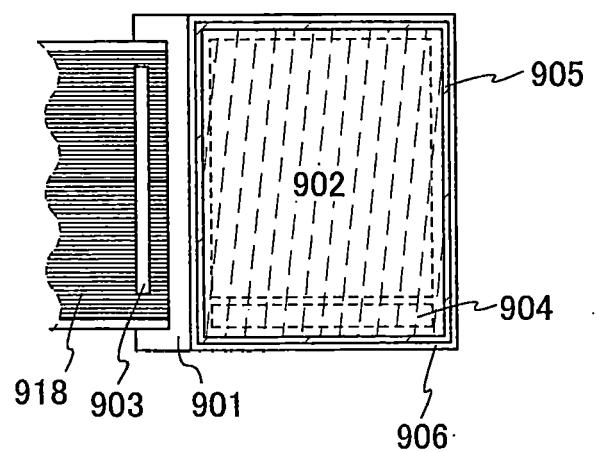

圖 19A 至圖 19C 是說明本發明的一個方式的半導體裝置的俯視圖；

圖 20 是說明本發明的一個方式的半導體裝置的剖面圖；

圖 21A 至圖 21C 是說明本發明的一個方式的半導體裝置的剖面圖及俯視圖；

圖 22A 至圖 22C 是說明使用本發明的一個方式的半導體裝置的電子裝置的圖；

圖 23A 至圖 23C 是說明使用本發明的一個方式的半導體裝置的電子裝置的圖；

圖 24A 至圖 24D 是說明樣本結構的圖；

圖 25 是說明薄層電阻的圖；

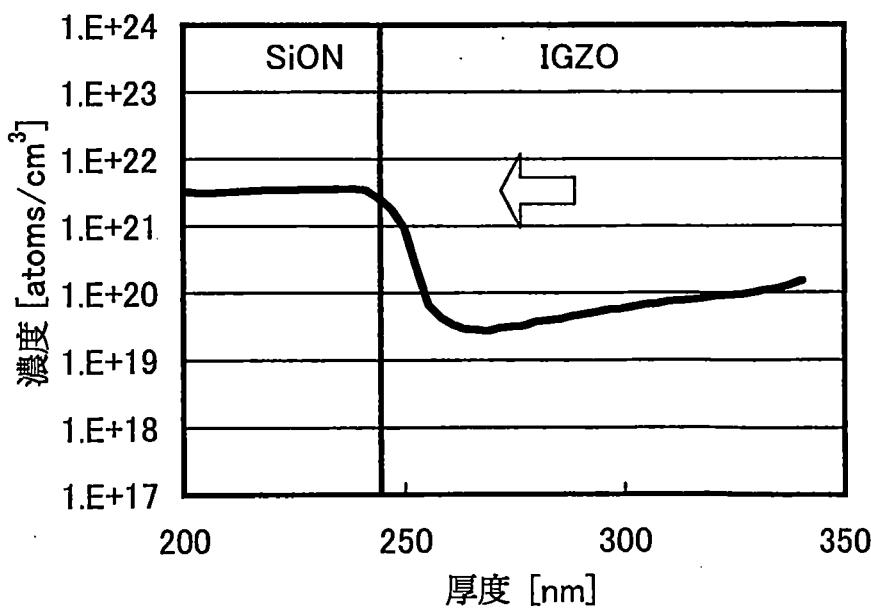

圖 26A 和圖 26B 是說明 SIMS 的測量結果的圖；

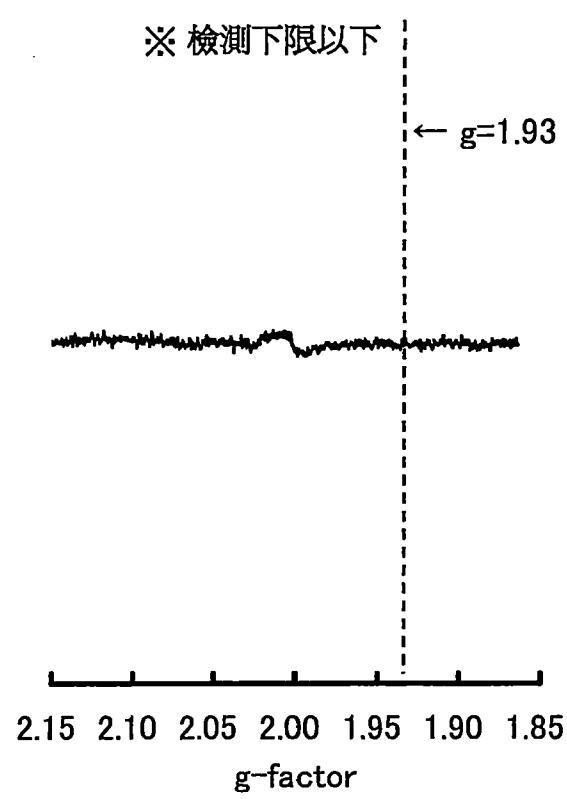

圖 27A 至圖 27C 是說明 ESR 的測量結果的圖；

圖 28 是說明 ESR 的測量結果的圖；

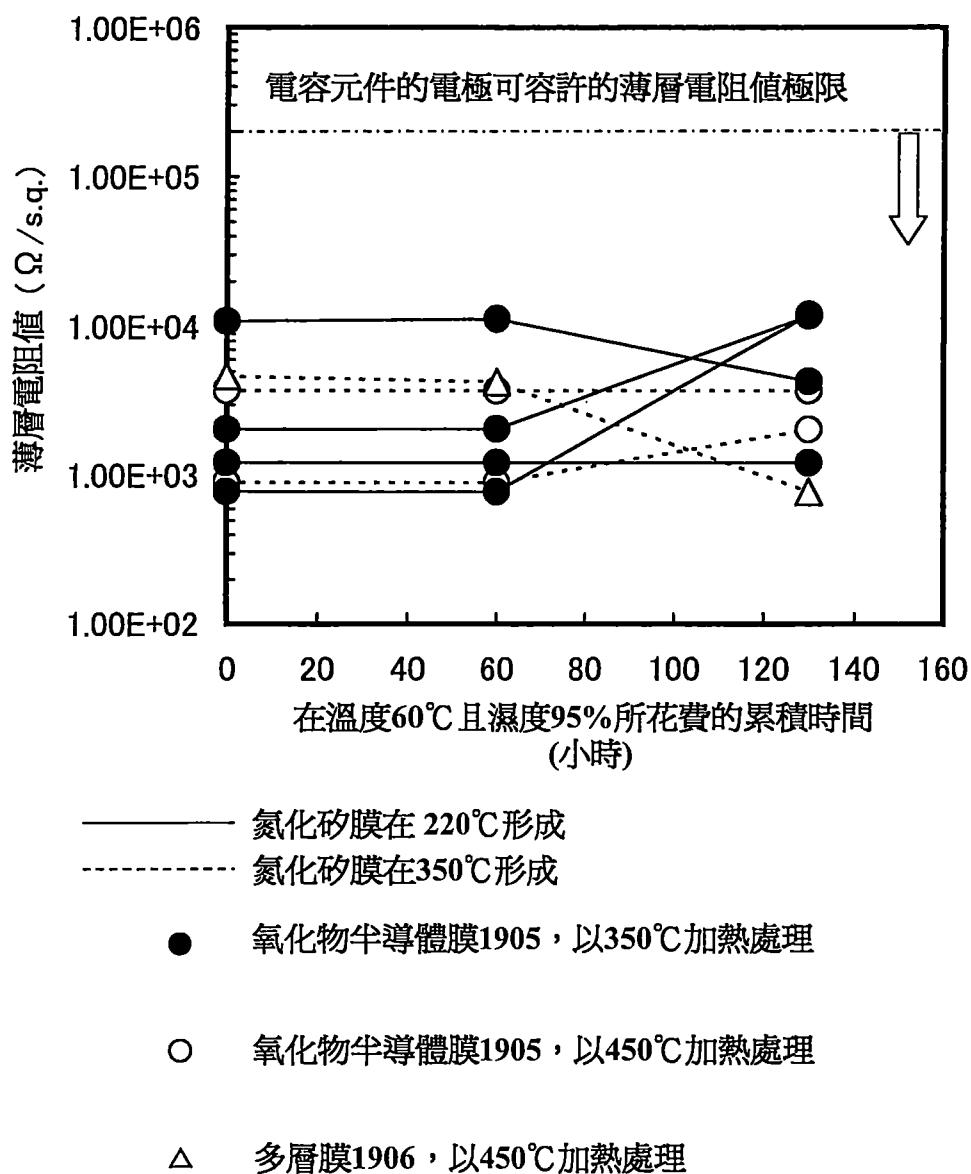

圖 29 是說明薄層電阻的圖；

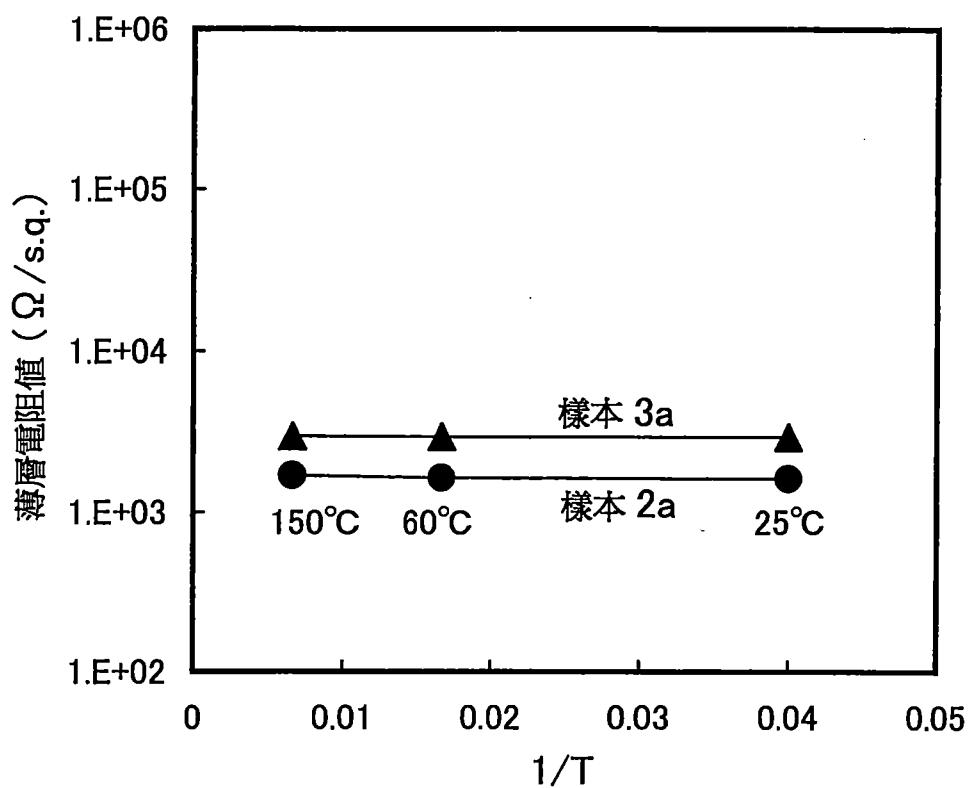

圖 30 是說明薄層電阻的圖；

圖 31A 至圖 31D 是說明  $\text{InGaZnO}_4$  的塊體模型的圖；

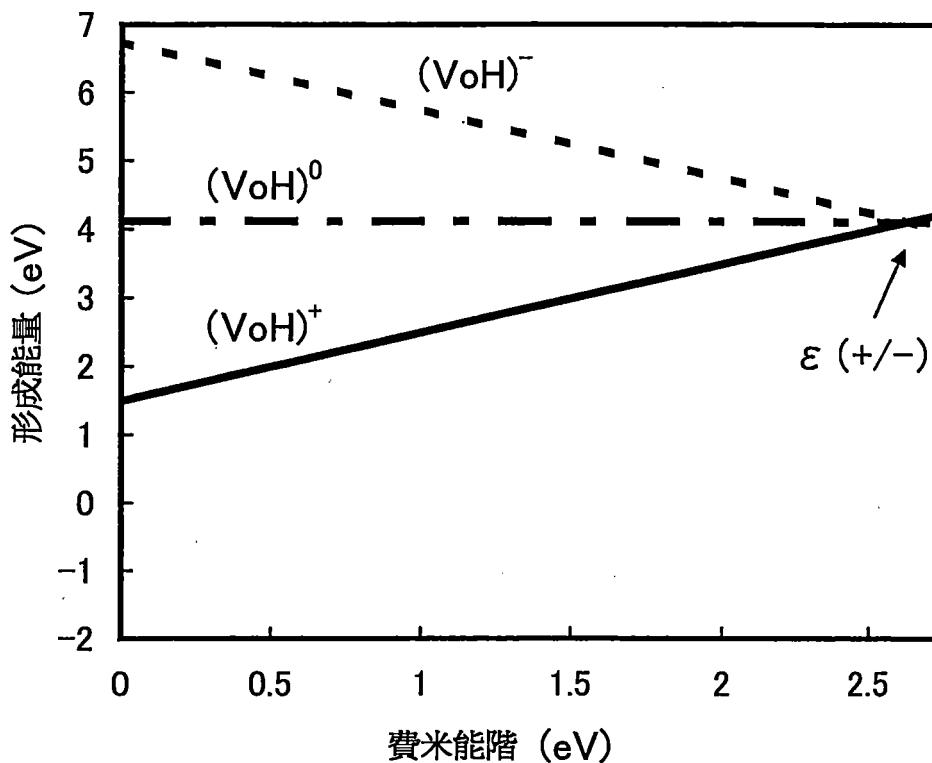

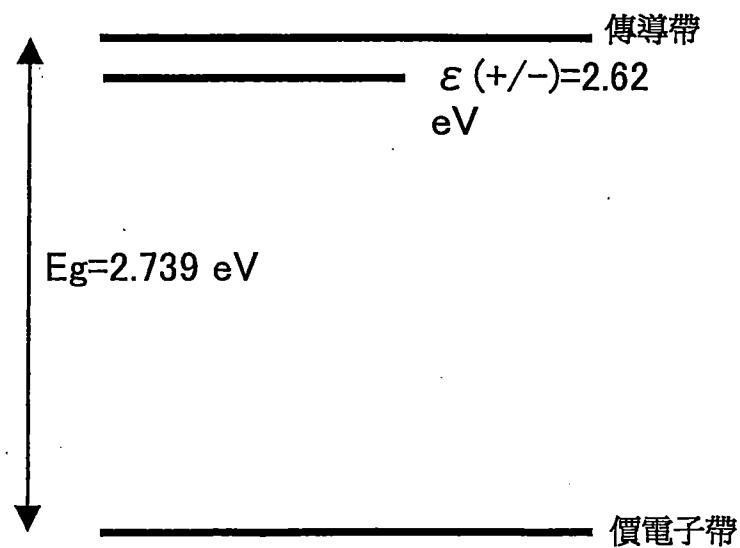

圖 32A 和圖 32B 是說明  $\text{V}_{\text{OH}}$  的形成能量及熱力學遷移能階的圖。

## 【實施方式】

下面，參照圖式對本發明的實施方式進行詳細說明。

但是，本發明不侷限於以下說明，所屬技術領域的普通技術人員可以很容易地理解一個事實，就是本發明的方式和詳細內容可以被變換為各種各樣的形成。此外，本發明不應該被解釋為僅限定在以下所示的實施方式所記載的內容中。

在以下說明的本發明的結構中，在不同圖式之間共同使用同一符號表示同一部分或具有同樣功能的部分而省略其重複說明。另外，當表示具有相同功能的部分時有時使用相同的陰影線，而不特別附加元件符號。

在本說明書所說明的各圖式中，各結構的大小、膜的厚度或區域有時為了明確起見而被誇大。因此，本發明並不一定限定於圖式中的比例。

在本說明書等中，為了方便起見，附加了第一、第二等序數詞，而其並不表示製程順序或疊層順序。此外，本說明書等中，這些序數詞不表示用來特定發明的事項的固有名稱。

另外，電壓是指兩個點之間的電位差，電位是指某一點的靜電場中的單位電荷具有的靜電能(電位能量)。但是，一般來說，將某一點的電位與標準的電位(例如接地電位)之間的電位差簡單地稱為電位或電壓，通常，電位和電壓是同義詞。因此，在本說明書中，除了特別指定的情況以外，既可將“電位”稱為“電壓”，又可將“電壓”稱為“電位”。

在本說明書中，當在進行光微影處理之後進行蝕刻處

理時，光微影處理中形成的遮罩被去除。

## 實施方式 1

在本實施方式中，參照圖式對本發明的一個方式的半導體裝置進行說明。此外，在本實施方式中，以液晶顯示裝置為例子說明本發明的一個方式的半導體裝置。

### 〈半導體裝置的結構〉

圖 1A 示出半導體裝置的一個例子。圖 1A 所示的半導體裝置包括：像素部 100；掃描線驅動電路 104；信號線驅動電路 106；分別以平行或大致平行的方式配置的、電位由掃描線驅動電路 104 控制的  $m$  個掃描線 107；分別以平行或大致平行的方式配置的、電位由信號線驅動電路 106 控制的  $n$  個信號線 109。並且，像素部 100 包括以矩陣狀配置的多個像素 101。另外，還包括沿著掃描線 107 分別以平行或大致平行的方式配置的電容線 115。另外，電容線 115 還可以沿著信號線 109 以分別平行或大致平行的方式配置。

各掃描線 107 電連接到在像素部 100 中配置為  $m$  行  $n$  列的像素 101 中的配置在任一行的  $n$  個像素 101。另外，各信號線 109 電連接到配置為  $m$  行  $n$  列的像素 101 中的配置在任一列的  $m$  個像素 101。 $m$ 、 $n$  都是 1 以上的整數。另外，各電容線 115 電連接到配置為  $m$  行  $n$  列的像素 101 中的配置在任一行的  $n$  個像素 101。另外，當電容

線 115 沿著信號線 109 以分別平行或大致平行的方式配置時，電連接到配置為  $m$  行  $n$  列的像素 101 中的配置在任一列的  $m$  個像素 101。

圖 1B 是示出圖 1A 所示的半導體裝置所具有的像素 101 的電路圖的一個例子。圖 1B 所示的像素 101 包括：與掃描線 107 及信號線 109 電連接的電晶體 103；電容元件 105，該電容元件 105 的一個電極與電晶體 103 的汲極電極電連接，另一個電極與供應固定電位的電容線 115 電連接；液晶元件 108，該液晶元件 108 的像素電極與電晶體 103 的汲極電極及電容元件 105 的一個電極電連接，以與像素電極對置的方式設置的電極（反電極）與供應反電位（counter potential）的佈線電連接。

液晶元件 108 是如下元件：利用以形成有電晶體 103 及像素電極的基板及形成有反電極的基板夾持的液晶的光學調變作用，來控制使光透過或不透過的元件。注意，液晶的光學調變作用由施加到液晶的電場（包括縱向電場或斜向電場）控制。此外，當在形成像素電極的基板中形成反電極（也稱為共用電極）時，施加到液晶的電場成為橫向電場。

接著，說明液晶顯示裝置的像素 101 的具體例子。圖 2 是示出像素 101 的俯視圖。注意，在圖 2 中，省略反電極及液晶元件。

在圖 2 中，掃描線 107 在大致垂直於信號線 109 的方向（圖中左右方向）上延伸地設置。信號線 109 在大致垂

直於掃描線 107 的方向（圖中上下方向）上延伸地設置。電容線 115 在平行於掃描線 107 的方向上延伸地設置。另外，掃描線 107 及電容線 115 與掃描線驅動電路 104（參照圖 1A）電連接，信號線 109 與信號線驅動電路 106（參照圖 1A）電連接。

電晶體 103 設置於掃描線 107 及信號線 109 彼此交叉的區域中。電晶體 103 至少包括具有通道形成區的半導體膜 111、閘極電極、閘極絕緣膜（圖 2 中未圖示）、源極電極及汲極電極。此外，掃描線 107 中的與半導體膜 111 重疊的區域用作電晶體 103 的閘極電極。信號線 109 中的與半導體膜 111 重疊的區域用作電晶體 103 的源極電極。導電膜 113 中的與半導體膜 111 重疊的區域用作電晶體 103 的汲極電極。由此，閘極電極、源極電極及汲極電極有時分別表示為掃描線 107、信號線 109 及導電膜 113。此外，在圖 2 中，從上方看時掃描線 107 的端部位於半導體膜的端部的外側。由此，掃描線 107 用作遮擋來自背光等的光源的光的遮光膜。其結果是，光不照射到包括在電晶體中的半導體膜 111，由此可以抑制電晶體的電特性的變動。

此外，由於藉由使用適當的條件對氧化物半導體進行處理可以使電晶體的關態電流（off-state current）降至極低，在本發明的一個方式中作為半導體膜 111 使用氧化物半導體。因此，可以減少半導體裝置的耗電量。

此外，導電膜 113 藉由開口 117 與由具有透光性的導

電膜形成的像素電極 121 電連接。此外，在圖 2 中，省略像素電極 121 的陰影進行圖示。

電容元件 105 設置於像素 101 內的由電容線 115 及信號線 109 圍繞的區域中。電容元件 105 藉由設置於開口 123 中的導電膜 125 與電容線 115 電連接。電容元件 105 包括由氧化物半導體形成的半導體膜 119、像素電極 121 以及作為介電膜形成在電晶體 103 上的絕緣膜（圖 2 中未圖示）。由於半導體膜 119、像素電極 121 及介電膜都具有透光性，所以電容元件 105 具有透光性。

像這樣，由於半導體膜 119 具有透光性，所以可以在像素 101 內大面積地形成電容元件 105。由此，可以獲得提高孔徑比，典型地是 55% 以上，較佳為 60% 以上，並增大了電荷容量的半導體裝置。例如，在解析度高的半導體裝置諸如液晶顯示裝置中，像素的面積小，電容元件的面積也小。由此，在解析度高的半導體裝置中，儲存在電容元件中的電荷容量變小。但是，由於本實施方式所示的電容元件 105 具有透光性，所以藉由在像素中設置該電容元件，可以在各像素中獲得充分的電荷容量，並提高孔徑比。典型的是，適當地用於像素密度為 200ppi 以上較佳為 300ppi 以上的高解析度的半導體裝置。另外，本發明的一個方式在高解析度的顯示裝置中也可以提高孔徑比，因此可以有效地利用背光等光源的光，由此可以降低顯示裝置的耗電量。

在此，對使用氧化物半導體的電晶體特性進行說明。

使用氧化物半導體的電晶體是  $n$  通道型電晶體。另外，氧化物半導體中的氧缺陷有時生成載子，而有可能導致電晶體的電特性及可靠性降低。例如，有可能使電晶體的臨界電壓移到負方向而導致閘極電壓為  $0V$  時流過汲極電流。將這種當閘極電壓為  $0V$  時流過汲極電流的電晶體稱為常開啓型電晶體。另外，將閘極電壓為  $0V$  時被視為沒有流過汲極電流的電晶體稱為常閉型電晶體。

因此，當作為半導體膜 111 使用氧化物半導體時，較佳的是盡可能地減少以氧缺陷為代表的半導體膜 111 中的缺陷。例如，較佳的是將利用對膜表面施加平行方向的磁場的電子自旋共振法得到的  $g$  值 = 1.93 的自旋密度（相當於半導體膜 111 所含的缺陷密度）降低到測量器的檢測下限以下。藉由盡可能地減少以氧缺陷為代表的半導體膜 111 中的缺陷，可以抑制電晶體 103 的常開啓特性，由此可以提高半導體裝置的電特性及可靠性。

除了氧缺陷之外，氧化物半導體中的氫（包括水等氫化合物）也使電晶體的臨界電壓向負方向移動。氧化物半導體中的氫與接合於金屬原子的氧發生反應生成水，與此同時發生氧脫離的晶格（或氧脫離的部分）形成缺陷（也稱為氧缺陷）。另外，氫的一部分與氧發生反應生成作為載子的電子。因此，使用含有氫的氧化物半導體的電晶體容易具有常開啓特性。

因此，當作為半導體膜 111 使用氧化物半導體時，較佳的是儘量降低半導體膜 111 中的氫。明確而言，在半導

體膜 111 中，使利用二次離子質譜分析法 (SIMS : Secondary Ion Mass Spectrometry) 得到的氫濃度低於  $5 \times 10^{18} \text{ atoms/cm}^3$ ，較佳為  $1 \times 10^{18} \text{ atoms/cm}^3$  以下，更佳為  $5 \times 10^{17} \text{ atoms/cm}^3$  以下，進一步佳為  $1 \times 10^{16} \text{ atoms/cm}^3$  以下。

另外，在半導體膜 111 中，使利用二次離子質譜分析法得到的鹼金屬或鹼土金屬的濃度為  $1 \times 10^{18} \text{ atoms/cm}^3$  以下，較佳為  $2 \times 10^{16} \text{ atoms/cm}^3$  以下。有時當鹼金屬及鹼土金屬與氧化物半導體接合時生成載子而使電晶體 103 的關態電流增大。

另外，當半導體膜 111 中含有氮時生成作為載子的電子，載子密度增加而容易 n 型化。其結果，使用含有氮的氧化物半導體的電晶體容易變為常開啓特性。因此，在該半導體膜 111 中，較佳的是盡可能地減少氮，例如，較佳的是使氮濃度為  $5 \times 10^{18} \text{ atoms/cm}^3$  以下。

像這樣，藉由使用儘量地減少了雜質（氫、氮、鹼金屬或鹼土金屬等）而被高度純化的氧化物半導體膜形成半導體膜 111，可以抑制電晶體 103 變為常開啓特性，由此可以使電晶體 103 的關態電流降至極低。由此，可以製造具有良好電特性的半導體裝置。此外，可以製造可靠性得到提高的半導體裝置。

注意，可以利用各種試驗證明使用被高度純化的氧化物半導體膜的電晶體的關態電流低的事實。例如，即便是通道寬度 W 為  $1 \times 10^6 \mu\text{m}$  通道長度 L 為  $10 \mu\text{m}$  的元件，當源極電極與汲極電極間的電壓（汲極電壓）為 1V 至 10V

的範圍內，關態電流可以為半導體參數分析儀的測量極限以下，即  $1 \times 10^{-13} \text{ A}$  以下。在此情況下，可知：相當於關態電流除以電晶體的通道寬度的數值的關態電流為  $100 \text{ zA}/\mu\text{m}$  以下。另外，利用如下電路測量關態電流，該電路中電容元件與電晶體連接並且該電晶體控制流入電容元件或從電容元件流出的電荷。在該測量時，將被高度純化的氧化物半導體膜用於上述電晶體的通道形成區，且根據電容元件的單位時間的電荷量推移測量該電晶體的關態電流。其結果是，可知：當電晶體的源極電極與汲極電極之間的電壓為  $3 \text{ V}$  時，可以獲得幾十  $\text{yA}/\mu\text{m}$  的更低的關態電流。由此，使用被高度純化的氧化物半導體膜的電晶體的關態電流顯著低。

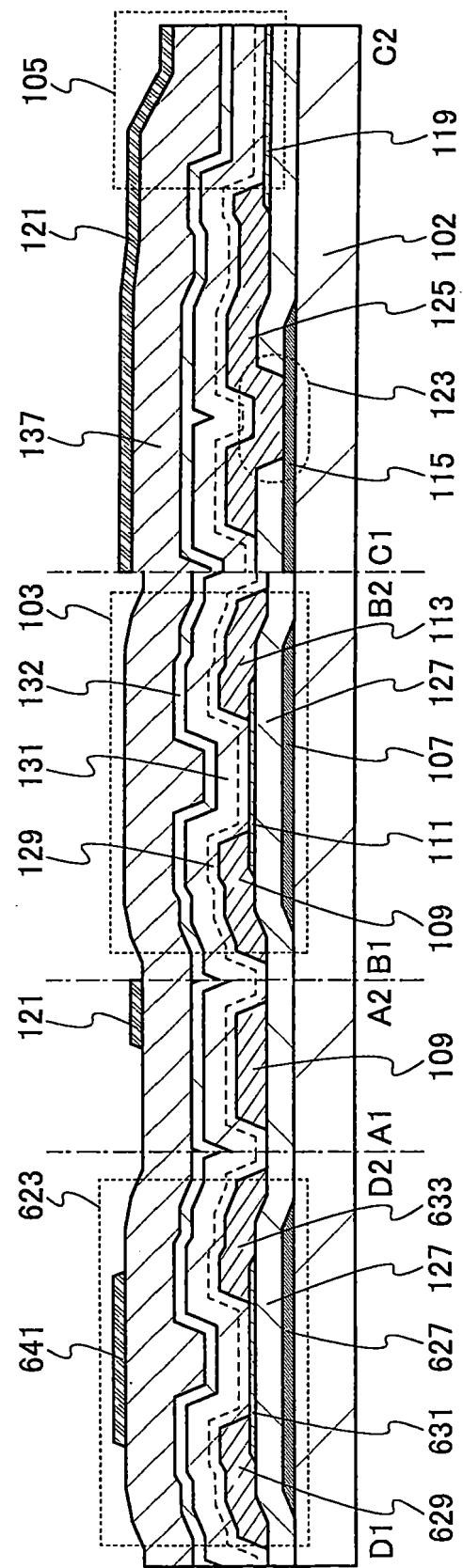

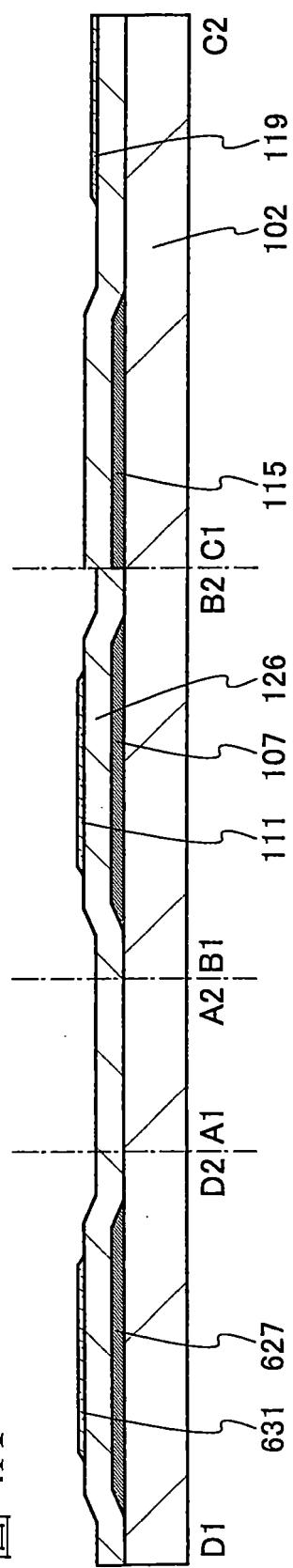

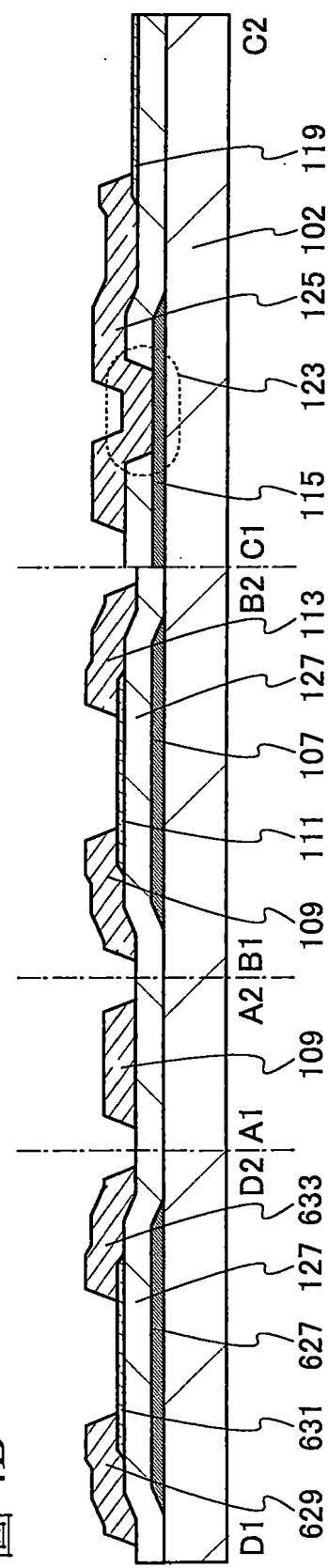

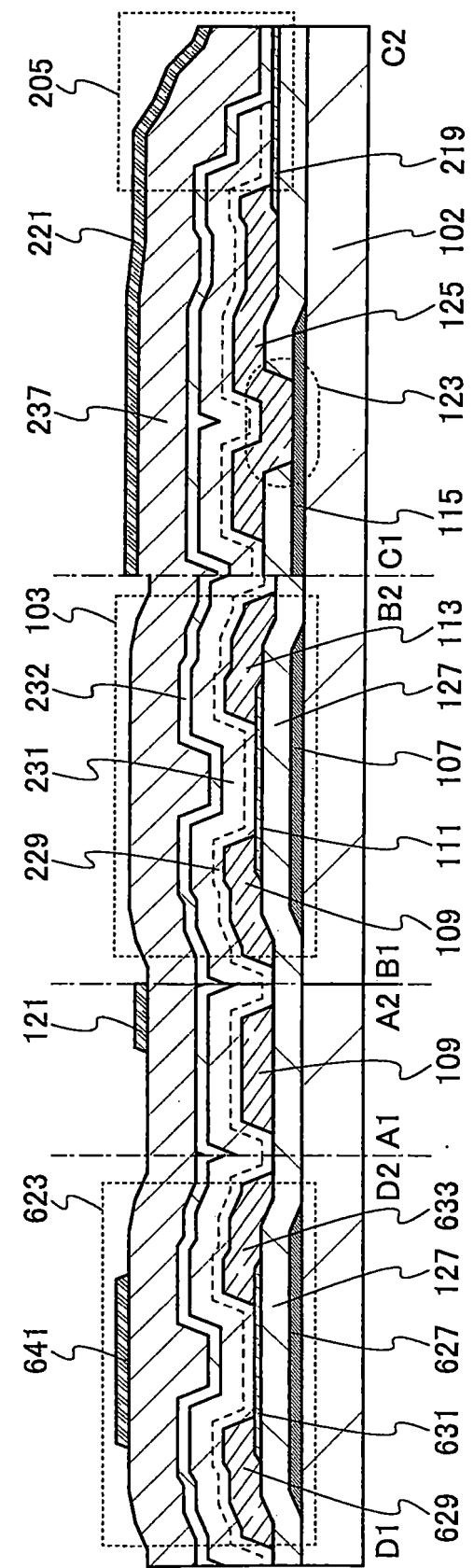

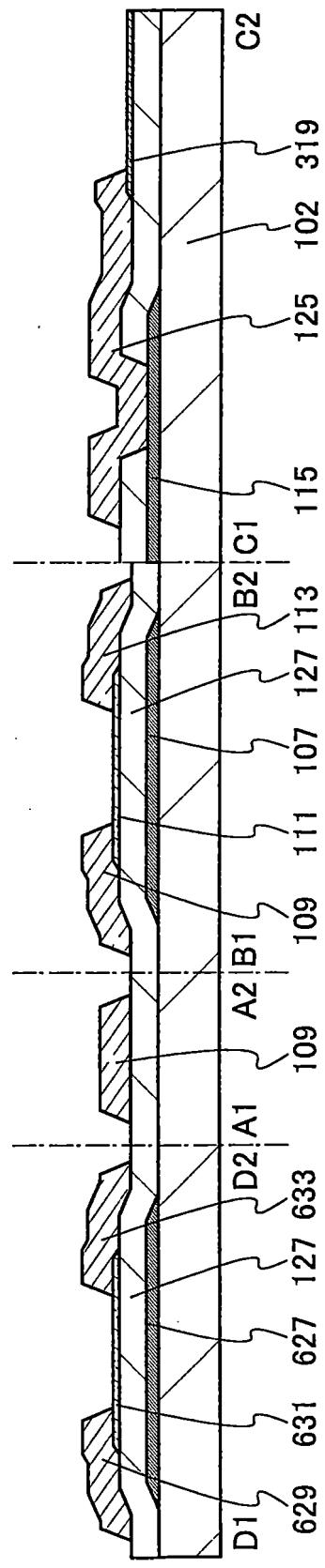

接著，圖 3 是示出圖 2 的點劃線 A1-A2 間、點劃線 B1-B2 間、點劃線 C1-C2 間的剖面圖。此外，省略掃描線驅動電路 104 的俯視圖，與此同時 D1-D2 示出掃描線驅動電路 104 的剖面圖。另外，這裡示出設置在掃描線驅動電路 104 中的電晶體的剖面圖，但是該電晶體可以設置在信號線驅動電路 106 中。

首先，說明像素 101 的 A1-A2 間、點劃線 B1-B2 間及點劃線 C1-C2 間的結構。在基板 102 上設置有包括電晶體 103 的閘極電極的掃描線 107、與掃描線 107 設置於同一表面上的電容線 115。在掃描線 107 及電容線 115 上設置有閘極絕緣膜 127。在閘極絕緣膜 127 的與掃描線 107 重疊的區域上設置有半導體膜 111，在閘極絕緣膜 127 上

設置有半導體膜 119。在半導體膜 111 及閘極絕緣膜 127 上設置有包括電晶體 103 的源極電極的信號線 109、包括電晶體 103 的汲極電極的導電膜 113。在閘極絕緣膜 127 中設置有到達電容線 115 的開口 123，在開口 123 中及其上、閘極絕緣膜 127 及半導體膜 119 上設置有導電膜 125。在閘極絕緣膜 127、信號線 109、半導體膜 111、導電膜 113、導電膜 125、半導體膜 119 上設置有用作電晶體 103 的保護絕緣膜的絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137。在絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137 中設置有到達導電膜 113 的開口 117（參照圖 2），在開口 117（參照圖 2）中以及絕緣膜 137 上設置有像素電極 121。

本實施方式所示的電容元件 105 的一對電極中的一個電極是在與半導體膜 111 相同的製程中形成的半導體膜 119，一對電極中的另一個電極是像素電極 121，設置在一對電極之間的介電膜是絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137。

接著，說明設置在掃描線驅動電路 104 中的電晶體的結構。在基板 102 上設置有電晶體 623 的閘極電極 627。在閘極電極 627 上設置有閘極絕緣膜 127。在閘極絕緣膜 127 的與閘極電極 627 重疊的區域上設置有半導體膜 631。在半導體膜 631 及閘極絕緣膜 127 上設置有電晶體 623 的源極電極 629 及汲極電極 633。在閘極絕緣膜 127、源極電極 629、半導體膜 631、汲極電極 633 上設置

有用作電晶體 623 的保護絕緣膜的絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137。在絕緣膜 137 上設置有導電膜 641。

此外，也可以在基板 102 與掃描線 107、電容線 115、閘極電極 627 及閘極絕緣膜 127 之間設置有基底絕緣膜。

藉由在電晶體 623 中設置隔著半導體膜 631 重疊於閘極電極 627 的導電膜 641，可以在不同的汲極電壓中降低通態電流的上升閘極電壓的偏差。此外，在與導電膜 641 對置的半導體膜 631 的表面上可以控制在源極電極 629 與汲極電極 633 之間流過的電流，可以降低不同的電晶體之間的電特性的偏差。此外，藉由設置導電膜 641，可以減少周圍的電場的變化給半導體膜 631 帶來的負面影響，由此可以提高電晶體的可靠性。並且，當將導電膜 641 的電位設定為與驅動電路的最低電位 ( $V_{ss}$ ，例如當以源極電極 629 的電位為基準時源極電極 629 的電位) 同一的電位或與其大致同一的電位，可以減少電晶體的臨界電壓的變動，由此可以提高電晶體的可靠性。

絕緣膜 129 及絕緣膜 131 例如可以使用氧化矽、氮氧化矽、氧化鋁、氧化鉻、氧化鎵或 Ga-Zn 類金屬氧化物等氧化絕緣材料以單層結構或疊層結構設置。

可以將絕緣膜 129 的厚度設定為 5nm 以上且 150nm 以下，較佳為 5nm 以上且 50nm 以下，更佳為 10nm 以上且 30nm 以下。可以將絕緣膜 131 的厚度設定為 30nm 以

上且 500nm 以下，較佳為 150nm 以上且 400nm 以下。

此外，絕緣膜 132 例如可以使用氮氧化矽、氮化矽、氮化鋁、氮氧化鋁等氮化絕緣材料以單層結構或疊層結構設置。

作為絕緣膜 132，也可以設置氫含量少的氮化絕緣膜。該氮化絕緣膜是如下氮化絕緣膜，例如利用 TDS 分析測量的氫分子的釋放量小於  $5.0 \times 10^{21} \text{ atoms/cm}^3$ ，較佳為小於  $3.0 \times 10^{21} \text{ atoms/cm}^3$ ，更佳為小於  $1.0 \times 10^{21} \text{ atoms/cm}^3$ 。

將絕緣膜 132 的厚度設定為能夠發揮抑制氫和水等雜質從外部侵入的效果的厚度。例如，可以設定為 50nm 以上且 200nm 以下，較佳為 50nm 以上且 150nm 以下，更佳為 50nm 以上且 100nm 以下。

此外，作為絕緣膜 137，可以使用藉由使用有機矽烷氣體的 CVD 法（化學氣相沉積法）形成的氧化絕緣膜，典型地是氧化矽膜。

作為絕緣膜 137，設置藉由使用有機矽烷氣體的 CVD 法形成的氧化矽膜。該氧化矽膜設置為 300nm 以上且 600nm 以下。作為有機矽烷氣體，可以使用正矽酸乙酯（TEOS：化學式為  $\text{Si}(\text{OC}_2\text{H}_5)_4$ ）、四甲基矽烷（TMS：化學式為  $\text{Si}(\text{CH}_3)_4$ ）、四甲基環四矽氧烷（TMCTS）、八甲基環四矽氧烷（OMCTS）、六甲基二矽氮烷（HMDS）、三乙氧基矽烷（ $\text{SiH}(\text{OC}_2\text{H}_5)_3$ ）、三（二甲氨基）矽烷（ $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ ）等含有矽的化合物。

藉由使用利用使用有機矽烷氣體的 CVD 法形成的氧

化矽膜形成絕緣膜 137，可以提高形成在基板 102 上的元件部表面的平坦性。其結果是，即使不設置由有機樹脂形成的平坦化膜，也可以減少液晶的配向無序，可以減少漏光，並可以提高對比。這裡，元件部包括：形成在基板 102 上的電晶體；設置在電晶體上的保護絕緣膜（絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137）、電容元件、形成在保護絕緣膜上的導電膜。此外，也可以不設置絕緣膜 129。

此外，由於藉由在電晶體 103 及電晶體 623 與絕緣膜 137 之間設置氮化絕緣膜的絕緣膜 132，由絕緣膜 132 阻擋包含在該氧化絕緣膜中的碳等雜質，抑制雜質移動到電晶體 103 及電晶體 623 的半導體膜 111 及半導體膜 631，由此可以減少電晶體的電特性的偏差。

再者，絕緣膜 129 及絕緣膜 131 中的一者或兩者較佳的是含有比滿足化學計量組成的氧多的氧的氧化絕緣膜。由此，可以防止從該半導體膜 111、631 脫離氧，並可以使包含在氧過剩區中的氧移動到半導體膜 111、631。移動到半導體膜 111、631 的氧可以減少包含在形成半導體膜 111、631 的氧化物半導體中的氧缺陷。例如，藉由使用利用熱脫附譜分析法（以下稱為 TDS 分析）測量的氧分子的釋放量為  $1.0 \times 10^{18}$  分子/ $\text{cm}^3$  以上的氧化絕緣膜，可以減少包含在該半導體膜 111、631 中的氧缺陷。此外，絕緣膜 129 及絕緣膜 131 中的一者或兩者也可以是包含超過化學計量組成的氧的區域（氧過剩區）部分地存在的氧

化絕緣膜，至少在與半導體膜 111、631 重疊的區域存在有氧過剩區，可以防止從該半導體膜 111、631 脫離氧，並將包含在氧過剩區的這些氧移動到半導體膜 111、631，可以減少氧缺陷。

當絕緣膜 131 是包含比滿足化學計量組成的氧多的氧的氧化絕緣膜時，絕緣膜 129 較佳的是使氧透過的氧化絕緣膜。此外，從外部進入到絕緣膜 129 中的氧並不是都透過絕緣膜 129 並且移動，也有停留在絕緣膜 129 的氧。此外，也有預先就包含在絕緣膜 129 中並且從絕緣膜 129 向外部移動的氧。因此，絕緣膜 129 較佳為氧的擴散係數大的氧化絕緣膜。

此外，絕緣膜 129 由於接觸於使用氧化物半導體形成的半導體膜 111 及半導體膜 631，所以較佳為不僅使氧透過而且在半導體膜 111 與半導體膜 631 之間的介面能階低的氧化絕緣膜。例如，絕緣膜 129 較佳為比絕緣膜 131 的膜中的缺陷密度低的氧化絕緣膜。明確地說，絕緣膜 129 較佳為藉由電子自旋共振法測量的在  $g$  值 = 2.001 (E'-center) 處的自旋密度為  $3.0 \times 10^{17}$  spins/cm<sup>3</sup> 以下，更佳為  $5.0 \times 10^{16}$  spins/cm<sup>3</sup> 以下的氧化絕緣膜。另外，藉由電子自旋共振法測量的在  $g$  值 = 2.001 處的自旋密度對應於絕緣膜 129 所包含的懸空鍵的量。

此外，絕緣膜 129 及絕緣膜 131 中的一者或兩者較佳為具有對氮的阻擋性的絕緣膜。例如，藉由形成為緻密的氧化絕緣膜可以使其具有對氮的阻擋性，明確地說，在以

25°C 使用 0.5wt%的氟酸時的蝕刻速度較佳為 10nm/分以下。

另外，當作為絕緣膜 129 及絕緣膜 131 中的一者或兩者使用氮化矽或氮氧化矽等含有氮的氧化絕緣膜時，藉由 SIMS 測量出的氮濃度為 SIMS 檢測下限以上且小於  $3 \times 10^{20}$  atoms/cm<sup>3</sup>，較佳為  $1 \times 10^{18}$  atoms/cm<sup>3</sup> 以上且  $1 \times 10^{20}$  atoms/cm<sup>3</sup> 以下。由此，可以減少向電晶體 103 所包括的半導體膜 111 及半導體膜 631 的氮移動量。另外，這樣可以減少含有氮的氧化絕緣膜本身的缺陷量。

此外，藉由在像素中的信號線 109 與像素電極 121 之間設置絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137，可以擴大信號線 109 與像素電極 121 之間的間隔，所以可以減少寄生電容，並可以降低因施加到信號線 109 的信號電壓的遲延所引起的顯示不均勻或耗電量的增加。另外，在掃描線驅動電路中的電晶體 623 中，由於擴大半導體膜 631 與導電膜 641 之間的間隔，所以可以緩和導電膜 641 影響到半導體膜 631 的電場，並可以減少電晶體 623 的電特性的偏差。其結果是，可以獲得顯示品質優良的半導體裝置。

以下示出上述結構的構成要素的詳細內容。

雖然對基板 102 的材質等沒有大的限制，但是至少需要具有能夠承受半導體裝置的製程中的加熱處理的耐熱性。例如，有玻璃基板、陶瓷基板、塑膠基板等，作為玻璃基板使用鋇硼矽酸鹽玻璃、鋁硼矽酸鹽玻璃或鋁矽酸鹽

玻璃等無鹼玻璃基板，即可。另外，作為基板 102 也可以使用不鏽鋼合金等沒有透光性的基板。此時，較佳的是在基板表面上設置絕緣膜。另外，作為基板 102，也可以使用石英基板、藍寶石基板、單晶半導體基板、多晶半導體基板、化合物半導體基板、SOI (Silicon On Insulator：絕緣體上矽晶片) 基板等。

由於在掃描線 107、電容線 115 及閘極電極 627 中大電流流過，所以較佳為使用金屬膜形成，典型地採用以鉬 (Mo)、鈦 (Ti)、鎢 (W)、鉭 (Ta)、鋁 (Al)、銅 (Cu)、鉻 (Cr)、釔 (Nd)、钪 (Sc) 等金屬材料或以這些金屬材料為主要成分的合金材料的單層或疊層的結構來設置。

作為掃描線 107、電容線 115 及閘極電極 627 的一個例子，可以舉出：使用包含矽的鋁的單層結構；在鋁上層疊鈦的兩層結構；在氮化鈦上層疊鈦的兩層結構；在氮化鈦上層疊鎢的兩層結構；在氮化鉭上層疊鎢的兩層結構；在銅-鎂-鋁合金上層疊銅的兩層結構；以及依次層疊氮化鈦、銅和鎢的三層結構等。

另外，作為掃描線 107、電容線 115 及閘極電極 627 的材料，可以使用能夠應用於像素電極 121 的具有透光性的導電材料。

另外，作為掃描線 107、電容線 115 及閘極電極 627 的材料，可以使用含有氮的金屬氧化物，明確地說，含有氮的 In-Ga-Zn 類氧化物、含有氮的 In-Sn 類氧化物、含有

氮的 In-Ga 類氧化物、含有氮的 In-Zn 類氧化物、含有氮的 Sn 類氧化物、含有氮的 In 類氧化物以及金屬氮化膜 (InN、SnN 等)。這些材料具有 5eV (電子伏特) 以上的功函數。當使用氧化物半導體形成電晶體 103 的半導體膜 111 時，藉由作為掃描線 107 (電晶體 103 的閘極電極) 使用含有氮的金屬氧化物，可以使電晶體 103 的臨界電壓向正方向變動，可以實現具有所謂常閉特性的電晶體。例如，當使用含有氮的 In-Ga-Zn 類氧化物時，可以使用其氮濃度至少高於半導體膜 111 的 In-Ga-Zn 類氧化物，明確而言，可以使用氮濃度為 7 原子%以上的 In-Ga-Zn 類氧化物。

掃描線 107、電容線 115 及閘極電極 627 較佳為使用低電阻材料的鋁或銅。藉由使用鋁或銅，可以減少信號延遲，從而提高顯示品質。另外，由於鋁的耐熱性低，因此容易產生小丘、晶鬚或遷移所導致的不良。為了防止鋁的遷移，較佳的是在鋁上層疊其熔點比鋁高的金屬材料如鉬、鈦、鎢等。此外，在使用銅時，為了防止遷移所導致的不良或銅元素的擴散，較佳的是在銅上層疊其熔點比銅高的金屬材料如鉬、鈦、鎢等。

閘極絕緣膜 127 使用如氧化矽、氮氧化矽、氮化矽、氮化矽、氧化鋁、氧化鎗、氧化鎵或 Ga-Zn 類金屬氧化物等絕緣材料，並且以單層結構或疊層結構設置。另外，為了提高與半導體膜 111 的介面特性，閘極絕緣膜 127 較佳的是至少接觸於半導體膜 111 的區域以氧化絕緣

膜形成。

另外，藉由在閘極絕緣膜 127 上設置具有對氧、氫、水等的阻擋性的絕緣膜，可以防止氧從半導體膜 111 向外部擴散，還可以防止氫、水等從外部侵入到該半導體膜 111 中。作為具有對氧、氫、水等的阻擋性的絕緣膜，可以舉出氧化鋁膜、氧化鎵膜、氧化鎗膜、氧化鈦膜、氧化鈷膜、氧化鉻膜、氧化鎳膜、氮化矽膜等。

此外，藉由作為閘極絕緣膜 127 使用矽酸鉿 ( $\text{HfSiO}_x$ )、含有氮的矽酸鉿 ( $\text{HfSi}_x\text{O}_y\text{N}_z$ )、含有氮的鋁酸鉿 ( $\text{HfAl}_x\text{O}_y\text{N}_z$ )、氧化鉬、氧化鈷等 high-k 材料，可以降低電晶體 103 的閘極漏電流。

此外，閘極絕緣膜 127 較佳為採用如下結構：作為第一氮化矽膜，設置缺陷量少的氮化矽膜，作為第二氮化矽膜，在第一氮化矽膜上設置氫脫離量及氮脫離量少的氮化矽膜，在第二氮化矽膜上較佳為設置上述閘極絕緣膜 127 中舉出的氧化絕緣膜中的任一個。

作為第二氮化矽膜，當利用熱脫附譜分析法分析時，較佳為使用以下的氮化絕緣膜：氫分子的脫離量小於  $5 \times 10^{21}$  分子/ $\text{cm}^3$ ，較佳為  $3 \times 10^{21}$  分子/ $\text{cm}^3$  以下，更佳為  $1 \times 10^{21}$  分子/ $\text{cm}^3$  以下，氮分子的脫離量小於  $1 \times 10^{22}$  分子/ $\text{cm}^3$ ，較佳為  $5 \times 10^{21}$  分子/ $\text{cm}^3$  以下，更佳為  $1 \times 10^{21}$  分子/ $\text{cm}^3$  以下。藉由使用上述第一氮化矽膜及第二氮化矽膜作為閘極絕緣膜 127 的一部分，可以形成缺陷量少，並且氫

和氮的脫離量少的閘極絕緣膜作為閘極絕緣膜 127。其結果，可以減少閘極絕緣膜 127 所含有的氫和氮的向半導體膜 111 的移動量。

在使用氧化物半導體的電晶體中，當使用氧化物半導體形成的半導體膜 111 與閘極絕緣膜的界面或閘極絕緣膜中存在陷阱能階（也稱為界面能階）時，有可能成為電晶體的臨界電壓變動，典型為臨界電壓的負方向變動，以及次臨界擺幅值（S 值）增大的原因，該次臨界擺幅值是指當使電晶體導通時為了使汲極電流變化一位數而所需的閘極電壓。其結果，有每個電晶體的電特性產生偏差的問題。因此，藉由作為閘極絕緣膜使用缺陷量少的氮化矽膜，並且在與半導體膜 111 接觸的區域設置氧化絕緣膜，可以減少臨界電壓的負向漂移，並且可以抑制 S 值的增大。

可以將閘極絕緣膜 127 的厚度設定為 5nm 以上且 400nm 以下，較佳為 10nm 以上且 300nm 以下，更佳為 50nm 以上且 250nm 以下。

半導體膜 111、半導體膜 119 及半導體膜 631 使用氧化物半導體形成。該氧化物半導體可以為非晶結構、單晶結構或多晶結構。此外，半導體膜 111、半導體膜 119 及半導體膜 631 由同一金屬元素構成。此外，半導體膜 111、半導體膜 119 及半導體膜 631 的厚度為 1nm 以上且 100nm 以下，較佳為 1nm 以上且 50nm 以下，更佳為 1nm 以上且 30nm 以下，進一步較佳為 3nm 以上且 20nm 以

下。

作為可以應用於半導體膜 111、半導體膜 119 及半導體膜 631 的氧化物半導體，能隙為  $2\text{eV}$  以上，較佳為  $2.5\text{eV}$  以上，更佳為  $3\text{eV}$  以上。像這樣，藉由使用能隙寬的氧化物半導體，可以減少電晶體 103 的關態電流。

可以應用於半導體膜 111、半導體膜 119 及半導體膜 631 的氧化物半導體較佳為至少包含銦 (In) 或鋅 (Zn) 的金屬氧化物。或者，較佳為包含 In 及 Zn 的兩者的金屬氧化物。此外，為了減少使用該氧化物半導體的電晶體的電特性的偏差，除了上述元素以外，較佳的是還具有一種或多種穩定劑 (stabilizer)。

作為穩定劑，可以舉出鎵 (Ga)、錫 (Sn)、鉿 (Hf)、鋁 (Al) 或鎔 (Zr) 等。另外，作為其他穩定劑，還可以舉出鑭系元素的鑭 (La)、鈦 (Ce)、鑑 (Pr)、釔 (Nd)、釤 (Sm)、铕 (Eu)、釔 (Gd)、铽 (Tb)、鏑 (Dy)、鈥 (Ho)、鈔 (Er)、銩 (Tm)、镱 (Yb)、鑑 (Lu) 等。

作為可以應用於半導體膜 111、半導體膜 119 及半導體膜 631 的氧化物半導體，例如，可以使用氧化銦、氧化錫、氧化鋅；含有兩種金屬的氧化物的 In-Zn 類氧化物、Sn-Zn 類氧化物、Al-Zn 類氧化物、Zn-Mg 類氧化物、Sn-Mg 類氧化物、In-Mg 類氧化物、In-Ga 類氧化物；含有三種金屬的氧化物的 In-Ga-Zn 類氧化物（也稱為 IGZO）、In-Al-Zn 類氧化物、In-Sn-Zn 類氧化物、Sn-Ga-Zn 類氧化

物、Al-Ga-Zn 類氧化物、Sn-Al-Zn 類氧化物、In-Hf-Zn 類氧化物、In-Zr-Zn 類氧化物、In-Ti-Zn 類氧化物、In-Sc-Zn 類氧化物、In-Y-Zn 類氧化物、In-La-Zn 類氧化物、In-Ce-Zn 類氧化物、In-Pr-Zn 類氧化物、In-Nd-Zn 類氧化物、In-Sm-Zn 類氧化物、In-Eu-Zn 類氧化物、In-Gd-Zn 類氧化物、In-Tb-Zn 類氧化物、In-Dy-Zn 類氧化物、In-Ho-Zn 類氧化物、In-Er-Zn 類氧化物、In-Tm-Zn 類氧化物、In-Yb-Zn 類氧化物、In-Lu-Zn 類氧化物；含有四種金屬的氧化物的 In-Sn-Ga-Zn 類氧化物、In-Hf-Ga-Zn 類氧化物、In-Al-Ga-Zn 類氧化物、In-Sn-Al-Zn 類氧化物、In-Sn-Hf-Zn 類氧化物、In-Hf-Al-Zn 類氧化物。

在此，“In-Ga-Zn 類氧化物”是指以 In、Ga 以及 Zn 為主要成分的氧化物，對 In、Ga 以及 Zn 的比例沒有限制。此外，也可以包含 In、Ga、Zn 以外的金屬元素。

另外，可以作爲氧化物半導體使用以  $InMO_3(ZnO)_m$  ( $m > 0$ ) 表示的材料。另外，M 表示選自 Ga、Fe、Mn 及 Co 中的一種或多種金屬元素或者用作上述穩定劑的元素。

例如，可以使用  $In:Ga:Zn=1:1:1$  ( $=1/3:1/3:1/3$ )、 $In:Ga:Zn=2:2:1$  ( $=2/5:2/5:1/5$ ) 或  $In:Ga:Zn=3:1:2$  ( $=1/2:1/6:1/3$ ) 的原子數比的 In-Ga-Zn 類金屬氧化物。或者，可以使用  $In:Sn:Zn=1:1:1$  ( $=1/3:1/3:1/3$ )、 $In:Sn:Zn=2:1:3$  ( $=1/3:1/6:1/2$ ) 或  $In:Sn:Zn=2:1:5$  ( $=1/4:1/8:5/8$ ) 的原子數比的 In-Sn-Zn 類金屬氧化物。

另外，包含在金屬氧化物中的金屬元素的原子數比作為誤差包括上述原子數比的±20%的變動。

但是，本發明不侷限於此，可以根據所需要的半導體特性及電特性（場效移動率、臨界電壓等）而使用具有適當的原子數比的材料。另外，較佳為採用適當的載子密度、雜質濃度、缺陷密度、金屬元素及氧的原子數比、原子間距離、密度等，以得到所需要的半導體特性。例如，使用 In-Sn-Zn 類金屬氧化物的電晶體可以較容易獲得較高的場效移動率。但是，In-Ga-Zn 類金屬氧化物也可以藉由減小塊體內缺陷密度提高場效移動率。

包括電晶體 103 的源極電極的信號線 109、包括電晶體 103 的汲極電極的導電膜 113、電連接電容元件 105 的半導體膜 119 與電容線 115 的導電膜 125 以及源極電極 629 及汲極電極 633 使用可應用於掃描線 107、電容線 115 及閘極電極 627 的材料並以單層結構或疊層結構設置。

像素電極 121 及導電膜 641 使用銻錫氧化物、含有氧化錫的銻氧化物、含有氧化錫的銻鋅氧化物、含有氧化鈦的銻氧化物、含有氧化鈦的銻錫氧化物、銻鋅氧化物、添加有氧化矽的銻錫氧化物等具有透光性的導電材料來形成。

這裡，參照圖 1C 所示的電路圖及圖 3 所示的剖面圖對本實施方式所示的像素 101 所包括的各構成要素的連接結構進行說明。

圖 1C 是示出圖 1A 所示的半導體裝置所包括的像素 101 的詳細的電路圖的一個例子。如圖 1C 及圖 3 所示，電晶體 103 包括：包括閘極電極的掃描線 107；包括源極電極的信號線 109；以及包括汲極電極的導電膜 113。

在電容元件 105 中，藉由導電膜 125 與電容線 115 電連接的半導體膜 119 用作一個電極。此外，與包括汲極電極的導電膜 113 電連接的像素電極 121 用作另一個電極。另外，設置於半導體膜 119 與像素電極 121 之間的絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137 用作介電膜。

液晶元件 108 包括：像素電極 121；反電極 154；以及設置於像素電極 121 與反電極 154 之間的液晶層。

在電容元件 105 中，半導體膜 119 即使與半導體膜 111 結構相同，也用作電容元件 105 的電極。這是因為像素電極 121 可以用作閘極電極，絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137 可以用作閘極絕緣膜，電容線 115 可以用作源極電極或汲極電極，其結果，可以使電容元件 105 與電晶體同樣地工作，而使半導體膜 119 成為導通狀態。也就是說，可以使電容元件 105 成為 MOS (Metal Oxide Semiconductor：金屬氧化物半導體) 電容器。MOS 電容器當比臨界電壓 ( $V_{th}$ ) 高的電壓施加到構成 MOS 電容器的電極的一個 (電容元件 105 中的像素電極 121) 時進行充電。此外，藉由控制對電容線 115 施加的電位可以使半導體膜 119 成為導通狀態，並可以使半導

體膜 119 用作電容元件 105 的一個電極。此時，將施加於電容線 115 的電位設定為如下。為了使液晶元件 108 (參照圖 1C) 工作，以視訊訊號的中心電位為基準將像素電極 121 的電位向正方向及負方向變動。為了使電容元件 105 (MOS 電容器) 成為始終導通的狀態，需要始終將電容線 115 的電位設定為比施加於像素電極 121 的電位高出電容元件 105 (MOS 電容器) 的臨界電壓的電位以上。也就是說，由於半導體膜 119 與半導體膜 111 結構相同，因此將電容線 115 的電位設定為高出電晶體 103 的臨界電壓以上即可。由此，可以使半導體膜 119 始終成為導通狀態，並使電容元件 105 (MOS 電容器) 成為始終導通的狀態。

另外，藉由使氧透過設置在半導體膜 111 及半導體膜 631 上的絕緣膜 129，使其成為與半導體膜 111 及半導體膜 631 的界面能階變低的氧化絕緣膜，並且使絕緣膜 131 成為包括氧過剩區的氧化絕緣膜或含有比滿足化學計量組成的氧多的氧的氧化絕緣膜，可以容易地向用氧化物半導體形成的半導體膜 111 及半導體膜 631 供應氧，並且在防止氧從該半導體膜 111 及半導體膜 631 脫離的同時，將絕緣膜 131 所包含的該氧移動到半導體膜 111 及半導體膜 631 中，減少形成半導體膜 111 及半導體膜 631 的氧化物半導體所包含的氧缺陷。其結果，可以抑制電晶體 103 成為常開啓，並且能夠控制施加於電容線 115 的電位而使電容元件 105 (MOS 電容器) 為始終導通的狀態，從而可以

提高半導體裝置的電特性及可靠性。

另外，藉由作為設置在絕緣膜 131 上的絕緣膜 132 使用氮化絕緣膜，可以抑制氫、水等雜質從外部侵入半導體膜 111 及半導體膜 119 中。並且，藉由作為絕緣膜 132 設置氫的含量少的氮化絕緣膜，可以抑制電晶體及電容元件 105 (MOS 電容器) 的電特性變動。

另外，可以在像素 101 內大面積地形成電容元件 105。因此，可以獲得提高了孔徑比且增大了電荷容量的半導體裝置。其結果是，可以獲得顯示品質優良的半導體裝置。

#### 〈半導體裝置的製造方法〉

接著，參照圖 4A、圖 4B、圖 5A 及圖 5B 說明上述半導體裝置所示的設置在基板 102 上的元件部的製造方法。

首先，在基板 102 上形成掃描線 107、電容線 115 及閘極電極 627，以覆蓋掃描線 107、電容線 115 及閘極電極 627 的方式形成後面加工為閘極絕緣膜 127 的絕緣膜 126，在絕緣膜 126 的重疊於掃描線 107 的區域形成半導體膜 111，以重疊於後面形成像素電極 121 的區域的方式形成半導體膜 119。此外，在重疊於閘極電極 627 的區域形成半導體膜 631 (參照圖 4A)。

掃描線 107、電容線 115 及閘極電極 627 可以使用上述材料形成導電膜，在該導電膜上形成遮罩，使用該遮罩進行加工來形成。該導電膜可以使用蒸鍍法、CVD 法、

濺射法、旋塗法等各種成膜方法。另外，對上述導電膜的厚度沒有特別的限制，可以根據形成時間及所希望的電阻率等而決定。該遮罩例如可以為利用光微影製程形成的光阻遮罩。此外，該導電膜的加工可以使用乾蝕刻和濕蝕刻中的一者或兩者來進行。

絕緣膜 126 可以使用能夠應用於閘極絕緣膜 127 的材料並利用 CVD 法或濺射法等各種成膜方法形成。

此外，當作為閘極絕緣膜 127 應用氧化鎵時，可以利用 MOCVD (Metal Organic Chemical Vapor Deposition：有機金屬氣相沉積) 法形成絕緣膜 126。

半導體膜 111、半導體膜 119 及半導體膜 631 可以使用上述氧化物半導體形成氧化物半導體膜，在該氧化物半導體膜上形成遮罩，使用該遮罩進行加工來形成。由此，半導體膜 111、半導體膜 119 及半導體膜 631 由同一金屬元素構成。可以利用濺射法、塗敷法、脈衝雷射蒸鍍法、雷射燒蝕法等形成該氧化物半導體膜。藉由使用印刷法，可以將元件分離的半導體膜 111 及半導體膜 119 直接形成在絕緣膜 126 上。在藉由濺射法形成該氧化物半導體膜的情況下，作為用來產生電漿的電源裝置，可以適當地使用 RF 電源裝置、AC 電源裝置或 DC 電源裝置等。另外，作為濺射氣體，適當地使用稀有氣體（典型的是氬）、氧氣體、稀有氣體和氧的混合氣體。此外，當採用稀有氣體和氧的混合氣體時，較佳為增高氧氣體對稀有氣體的比例。另外，根據所形成的氧化物半導體膜的組成而適當地選擇

靶材，即可。該遮罩例如可以爲利用光微影製程形成的光阻遮罩。此外，該氧化物半導體膜的加工可以使用乾蝕刻和濕蝕刻中的一者或兩者來進行。根據材料適當地設定蝕刻條件（蝕刻氣體、蝕刻劑、蝕刻時間、溫度等），來將其蝕刻成所希望的形狀。

在形成半導體膜 111、半導體膜 119 及半導體膜 631 之後進行加熱處理，較佳爲進行由氧化物半導體形成的半導體膜 111、半導體膜 119 及半導體膜 631 的脫氫化或脫水化。將該加熱處理的溫度典型地設定爲 150°C 以上且低於基板的應變點，較佳爲 200°C 以上且 450°C 以下，更佳爲 300°C 以上且 450°C 以下。此外，該加熱處理也可以對在加工成半導體膜 111 及半導體膜 119 之前的氧化物半導體膜進行。

在上述加熱處理中，加熱處理裝置不侷限於電爐，也可以利用被加熱的氣體等媒體所產生的熱傳導或熱輻射對被處理物進行加熱的裝置。例如，可以使用 GRTA ( Gas Rapid Thermal Anneal : 氣體快速熱退火 ) 裝置、LRTA ( Lamp Rapid Thermal Anneal : 燈快速熱退火 ) 裝置等的 RTA ( Rapid Thermal Anneal : 快速熱退火 ) 裝置。LRTA 裝置是利用從燈如鹵素燈、金屬鹵化物燈、氙弧燈、碳弧燈、高壓鈉燈或高壓汞燈等發射的光（電磁波）的輻射加熱被處理物的裝置。GRTA 裝置是使用高溫的氣體進行加熱處理的裝置。

上述加熱處理可以在氮、氧、超乾燥空氣（含水量爲

20ppm 以下，較佳為 1ppm 以下，更佳為 10ppb 以下的空氣）或稀有氣體（氬、氮等）的氛圍下進行。另外，上述氮、氧、超乾燥空氣或稀有氣體較佳的是不含有氫或水等。或者，也可以在惰性氣體氛圍中進行加熱之後在氧氛圍中進行加熱。此外，處理時間為 3 分鐘至 24 小時。

此外，當在基板 102 與掃描線 107、電容線 115 及閘極絕緣膜 127 之間設置基底絕緣膜時，該基底絕緣膜可以使用氧化矽、氮氧化矽、氮化矽、氮氧化矽、氧化鎵、氧化鋁、氧化釔、氧化鋁、氮氧化鋁等形成。此外，藉由作為基底絕緣膜使用氮化矽、氧化鎵、氧化鋁、氧化釔、氧化鋁等形成，可以抑制來自基板 102 的雜質典型地是鹼金屬、水、氫等擴散到半導體膜 111、半導體膜 119 及半導體膜 631。基底絕緣膜可以利用濺射法或 CVD 法形成。

接著，在絕緣膜 126 中形成到達電容線 115 的開口 123 形成閘極絕緣膜 127 之後，包括電晶體 103 的源極電極的信號線 109、包括電晶體 103 的汲極電極的導電膜 113、電連接半導體膜 119 與電容線 115 的導電膜 125。此外，形成源極電極 629 及汲極電極 633（參照圖 4B）。

開口 123 可以以露出絕緣膜 126 的重疊於電容線 115 的區域的一部分的方式形成遮罩，使用該遮罩進行加工來形成。此外，該遮罩的形成及該加工可以與掃描線 107、電容線 115 及閘極電極 627 同樣地進行。

信號線 109、導電膜 113、導電膜 125、源極電極 629 及汲極電極 633 可以使用能夠應用於信號線 109、導電膜

113、導電膜 125 及閘極電極 627 的材料形成導電膜，在該導電膜上形成遮罩，使用該遮罩進行加工來形成。該遮罩的形成及該加工可以與掃描線 107、電容線 115 及閘極電極 627 同樣地進行。

接著，在半導體膜 111、半導體膜 119、半導體膜 631、信號線 109、導電膜 113、導電膜 125、源極電極 629、汲極電極 633 及閘極絕緣膜 127 上形成絕緣膜 128，在絕緣膜 128 上形成絕緣膜 130，在絕緣膜 130 上形成絕緣膜 133。此外，在絕緣膜 133 上形成絕緣膜 136（參照圖 5A）。此外，較佳的是連續形成絕緣膜 128、絕緣膜 130 及絕緣膜 133。由此，可以抑制雜質混入到絕緣膜 128、絕緣膜 130 及絕緣膜 133 的每一個的介面。

絕緣膜 128 可以使用能夠應用於絕緣膜 129 的材料並利用 CVD 法或濺射法等各種成膜方法形成。絕緣膜 130 可以使用能夠應用於絕緣膜 131 的材料並利用 CVD 法或濺射法等各種成膜方法形成。絕緣膜 133 可以使用能夠應用於絕緣膜 132 的材料並利用 CVD 法或濺射法等各種成膜方法形成。絕緣膜 136 可以使用能夠應用於絕緣膜 137 的材料並利用 CVD 法形成。

當作為絕緣膜 129 應用與半導體膜 111 的介面能階變低的氧化絕緣膜時，絕緣膜 128 可以使用如下形成條件形成。此外，這裡示出作為該氧化絕緣膜形成氧化矽膜或氮化矽膜的情況。該形成條件是如下條件：將安裝在電漿 CVD 設備的進行了真空排氣的處理室內的基板的溫度保

持爲 180°C 以上且 400°C 以下，較佳爲 200°C 以上且 370°C 以下，將原料氣體的含有矽的沉積氣體及氧化氣體導入處理室將處理室內的壓力設定爲 20Pa 以上且 250Pa 以下，較佳爲 40Pa 以上且 200Pa 以下，並對設置在處理室內的電極供應高頻功率。

含有矽的沉積氣體的典型例子爲矽烷、乙矽烷、丙矽烷、氟化矽烷等。作爲氧化氣體，可以舉出氧、臭氧、一氧化二氮、二氧化氮等。

另外，藉由將相對於含有矽的沉積氣體的氧化氣體量設定爲 100 倍以上，可以減少包含在絕緣膜 128（絕緣膜 129）中的氫含量，並可以減少包含在絕緣膜 128（絕緣膜 129）中的懸空鍵。由於從絕緣膜 130（絕緣膜 131）移動的氧有時被包含在絕緣膜 128（絕緣膜 129）中的懸空鍵俘獲，所以當減少包含在絕緣膜 128（絕緣膜 129）中的懸空鍵時，可以使包含在絕緣膜 130（絕緣膜 131）中的氧效率好地移動到半導體膜 111 及半導體膜 119，由此減少包含在形成半導體膜 111 及半導體膜 119 的氧化物半導體中的氧缺陷。其結果是，可以減少混入在半導體膜 111 及半導體膜 119 的氫量，並可以減少包含在半導體膜 111 及半導體膜 119 中的氧缺陷。

當作爲絕緣膜 131 使用包括上述氧過剩區的氧化絕緣膜或包含比滿足化學計量組成的氧多的氧的氧化絕緣膜時，絕緣膜 130 可以使用如下形成條件形成。此外，這裡示出作爲該氧化絕緣膜形成氧化矽膜或氧氮化矽膜的情

況。該形成條件是如下條件：將安裝在電漿 CVD 設備的進行了真空排氣的處理室內的基板的溫度保持為 180°C 以上且 260°C 以下，較佳為 180°C 以上且 230°C 以下，將原料氣體導入處理室將處理室內的壓力設定為 100Pa 以上且 250Pa 以下，較佳為 100Pa 以上且 200Pa 以下，並對設置在處理室內的電極供應  $0.17\text{W}/\text{cm}^2$  以上且  $0.5\text{W}/\text{cm}^2$  以下較佳為  $0.25\text{W}/\text{cm}^2$  以上且  $0.35\text{W}/\text{cm}^2$  以下的高頻功率。

作為絕緣膜 130 的原料氣體可以使用能夠應用於絕緣膜 128 的原料氣體。

由於作為絕緣膜 130 的形成條件，在上述壓力的處理室中供應具有上述功率密度的高頻功率，因此電漿中的原料氣體的分解效率提高，氧自由基增加，且原料氣體的氧化進展，所以絕緣膜 130 中的氧含量多於化學計量組成。此外，由於在以上述基板溫度形成的膜中矽與氧的接合力弱。因此，藉由在後面的製程中進行的加熱處理可以使膜中的氧的一部分脫離。其結果是，可以形成包含比滿足化學計量組成的氧多的氧且藉由加熱氧的一部分發生脫離的氧化絕緣膜。此外，在半導體膜 111 上設置有絕緣膜 128。由此，在絕緣膜 130 的形成製程中絕緣膜 128 用作半導體膜 111 的保護膜。其結果是，即使使用功率密度好的高頻功率形成絕緣膜 130，也可以抑制對於半導體膜 111 及半導體膜 631 的損傷。

此外，由於藉由加厚絕緣膜 130 的膜厚可以利用加熱增加脫離的氧的量，所以絕緣膜 130 的厚度比絕緣膜 128

的厚度厚較佳。藉由設置絕緣膜 128 即使使絕緣膜 130 的厚度厚也可以獲得良好的覆蓋性。

絕緣膜 132 可以利用濺射法或 CVD 法等形成。當作為絕緣膜 132 設置含氫量少的氮化絕緣膜時，絕緣膜 133 可以使用如下條件下形成。此外，這裡示出作為該氧化絕緣膜形成氧化矽膜的情況。該形成條件是如下條件：將安裝在電漿 CVD 設備的進行了真空排氣的處理室內的基板的溫度保持為 80°C 以上且 400°C 以下，較佳為 200°C 以上且 370°C 以下，將原料氣體導入處理室將處理室內的壓力設定為 100Pa 以上且 250Pa 以下，較佳為 100Pa 以上且 200Pa 以下，並對設置在處理室內的電極供應高頻功率。

作為絕緣膜 132 的原料氣體，較佳為使用含有矽的沉積氣體、氮及氨。含有矽的沉積氣體的典型例子為矽烷、乙矽烷、丙矽烷、氟化矽烷等。此外，氮的流量為相對於氨的流量的 5 倍以上且 50 倍以下，較佳為 10 倍以上且 50 倍以下。此外，藉由作為原料氣體使用氨，可以促進含有矽的沉積氣體及氮的分解。這是因為如下緣故：氨因電漿能或熱能而離解，離解時產生的能量有助於含有矽的沉積氣體分子的接合及氮分子的接合的分解。由此，可以形成含氫量少且能夠抑制來自外部的氫或水等雜質的侵入的氮化矽膜。

絕緣膜 136 使用有機矽烷氣體及氧並利用將基板溫度設定為 200°C 以上且 550°C 以下，較佳為 300°C 以上且 450 °C 以下的 CVD 法形成。

較佳的是至少在形成絕緣膜 130 之後進行加熱處理，將包含在絕緣膜 128 或絕緣膜 130 中的過剩氧移動到半導體膜 111 及半導體膜 631，減少包含在形成半導體膜 111 及半導體膜 631 的氧化物半導體中的氧缺陷。此外，該加熱處理可以參照進行半導體膜 111 及半導體膜 119 的脫氫化或脫水化的加熱處理的詳細內容適當地進行。

接著，在絕緣膜 128、絕緣膜 130、絕緣膜 133 及絕緣膜 136 的重疊於導電膜 113 的區域形成到達導電膜 113 的開口 117（參照圖 2），並形成絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137。開口 117（參照圖 2）可以與開口 123 同樣地形成。

最後，藉由形成像素電極 121 及導電膜 641，可以製造設置在基板 102 上的元件部（參照圖 5B）。像素電極 121 可以使用上述材料形成藉由開口 117 接觸於導電膜 113 的導電膜，在該導電膜上形成遮罩，使用該遮罩進行加工來形成。此外，該遮罩的形成及該加工可以與掃描線 107 及電容線 115 同樣地進行。

### <變形例 1>

在本發明的一個方式的半導體裝置中，可以適當地改變作為構成電容元件的一個電極的半導體膜 119 與電容線 115 的連接。例如，為了進一步提高孔徑比，可以不隔著導電膜 125 而採用電容線直接接觸半導體膜的結構。由於不形成成為遮光膜的導電膜 125，所以進一步提高像素的

孔徑比。

<變形例 2>

在本發明的一個方式的半導體裝置中，可以適當地改變將作為構成電容元件 105 的一個電極的半導體膜 119 與電容線 115 電連接的導電膜 125 的俯視形狀。例如，為了降低該半導體膜 119 與導電膜 125 的接觸電阻，可以沿著該半導體膜 119 的外周以與其接觸的方式設置該導電膜 125。另外，導電膜由於在與包括電晶體 103 的源極電極的信號線 109 及包括電晶體 103 的汲極電極的導電膜 113 相同的形成製程中形成所以有時具有遮光性，由此較佳為形成為閉環狀。

<變形例 3>

此外，在本發明的一個方式的半導體裝置中，可以適當地改變包括在電容元件中的半導體膜及電容線的結構。參照圖 6 說明本結構的具體例子。圖 6 是像素 172 的俯視圖，如像素 172，與平行於信號線 109 的邊相比平行於掃描線 107 的邊長，且電容線 176 也可以以平行於信號線 109 的方向延伸的方式設置。此外，信號線 109 及電容線 176 電連接於信號線驅動電路 106（參照圖 1A）。

電容元件 174 連接於以平行於信號線 109 的方向延伸的方式設置的電容線 176。電容元件 174 包括在與半導體膜 111 相同的製程中形成的由氧化物半導體形成的半導體

膜 178、像素電極 121 以及作為介電膜形成在電晶體 103 上的絕緣膜（圖 6 中未圖示）。由於半導體膜 111、像素電極 121 及介電膜都具有透光性，所以電容元件 174 具有透光性。

此外，在電容元件 174 中，設置在一對電極之間的介電膜與圖 3 所示的電容元件 105 同樣是絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137。

電容線 176 可以在與信號線 109 及導電膜 113 相同的製程中形成。藉由以接觸於半導體膜 178 的方式設置電容線 176，可以增大半導體膜 178 及電容線 176 的接觸面積。另外，在像素 172 中，由於與平行於掃描線 107 的邊相比平行於信號線 109 的邊短，所以可以縮小像素電極 121 與電容線 176 重疊的面積，由此可以提高孔徑比。

#### <變形例 4>

在本發明的一個方式的半導體裝置中，作為構成電容元件的一個電極及電容線可以採用半導體膜。參照圖 7 對具體例子進行說明。注意，這裡僅對與圖 2 中說明的半導體膜 119 及電容線 115 不同的半導體膜 198 進行說明。圖 7 是像素 196 的俯視圖，在像素 196 中，設置有兼用作電容元件 197 的一個電極及電容線的半導體膜 198。半導體膜 198 具有在與信號線 109 平行的方向上延伸的區域，該區域用作電容線。半導體膜 198 中的與像素電極 121 重疊的區域用作電容元件 197 的一個電極。此外，半導體膜

198 可以與設置在像素 196 中的電晶體 103 的半導體膜 111 同時形成。

另外，當作為半導體膜 198 在 1 行中的所有的像素 196 中沒有間隔地形成連續的半導體膜時，半導體膜 198 與掃描線 107 重疊，由於掃描線 107 的電位變化的影響半導體膜 198 有可能不能充分地發揮作為電容線及電容元件 197 的一個電極的功能。因此，如圖 7 所示，較佳的是在各像素 196 中相離地設置半導體膜 198，使用與信號線 109 及導電膜 113 同時形成的導電膜 199 來將間隔地設置的半導體膜 198 彼此電連接。此時，藉由半導體膜 198 中的不連接於導電膜 199 的區域重疊於像素電極 121，可以降低該區域中的半導體膜 198 的電阻，所以半導體膜 198 用作電容線及電容元件 197 中的一個電極。

此外，雖然未圖示，但是當半導體膜 198 中的重疊於掃描線 107 的區域不受到掃描線 107 的電位變化影響時，可以在像素 196 的每一個中重疊於掃描線 107 的方式設置半導體膜 198 作為一個半導體膜。即，可以將半導體膜 198 在 1 行的所有像素 196 中沒有間隔地設置為連續的半導體膜。

在圖 7 中，雖然用作半導體膜 198 的電容線的區域在與信號線 109 平行的方向上延伸，但是用作電容線的區域可以在與掃描線 107 平行的方向上延伸。注意，當採用用作半導體膜 198 的電容線的區域在與掃描線 107 平行的方向上延伸的結構時，在電晶體 103 及電容元件 197 中，需

要在半導體膜 111 與半導體膜 198 之間以及信號線 109 與導電膜 113 之間設置絕緣膜而使其電分離。

如上所述，如像素 196，藉由作為設置在像素中的電容元件的一個電極及電容線設置氧化物半導體膜，氧化物半導體膜具有透光性，因此可以提高像素的孔徑比。

#### <變形例 5>

另外，在本發明的一個方式的半導體裝置中，可以適當地改變電容線的結構。參照圖 8 對本結構進行說明。注意，這裡，與圖 2 中說明的電容線 115 相比，其不同之處在於彼此鄰接的兩個像素之間的電容線的位置。

圖 8 示出在信號線 409 的延伸方向上在相鄰的像素之間設置有電容線的結構。此外，可以適當地應用在掃描線 437 的延伸方向上在相鄰的像素之間設置有電容線的結構代替圖 8 的結構。

圖 8 是鄰接於信號線 409 的延伸方向的像素 401\_1 及像素 401\_2 的俯視圖。

掃描線 407\_1 及掃描線 407\_2 互相平行並且在大致垂直於信號線 409 的方向上延伸。掃描線 407\_1 與掃描線 407\_2 之間以與掃描線 407\_1 及掃描線 407\_2 平行的方式設置有電容線 415。另外，電容線 415 與設置於像素 401\_1 中的電容元件 405\_1 以及設置於像素 401\_2 中的電容元件 405\_2 電連接。像素 401\_1 及像素 401\_2 的上表面形狀以及構成要素的配置位置與電容線 415 對稱。

像素 401\_1 中設置有與電晶體 403\_1 及該電晶體 403\_1 電連接的像素電極 421\_1 及電容元件 405\_1。

電晶體 403\_1 設置於掃描線 407\_1 及信號線 409 交叉的區域中。電晶體 403\_1 至少包括具有通道形成區的半導體膜 411\_1、閘極電極、閘極絕緣膜（圖 8 中未圖示）、源極電極及汲極電極。另外，掃描線 407\_1 的與半導體膜 411\_1 重疊的區域用作電晶體 403\_1 的閘極電極。信號線 409 的與半導體膜 411\_1 重疊的區域用作電晶體 403\_1 的源極電極。導電膜 413\_1 的與半導體膜 411\_1 重疊的區域用作電晶體 403\_1 的汲極電極。導電膜 413\_1 及像素電極 421\_1 在開口 417\_1 中連接。

電容元件 405\_1 藉由設置在開口 423 中的導電膜 425 與電容線 415 電連接。電容元件 405\_1 包括：由氧化物半導體形成的半導體膜 419\_1；像素電極 421\_1；作為介電膜的形成於電晶體 403\_1 上的絕緣膜（圖 8 中未圖示）。由於半導體膜 419\_1、像素電極 421\_1 及介電膜都具有透光性，所以電容元件 405\_1 具有透光性。

像素 401\_2 中設置有電晶體 403\_2、與該電晶體 403\_2 電連接的像素電極 421\_2 及電容元件 405\_2。

電晶體 403\_2 設置於掃描線 407\_2 及信號線 409 交叉的區域中。電晶體 403\_2 至少包括：具有通道形成區的半導體膜 411\_2、閘極電極、閘極絕緣膜（圖 8 中未圖示）、源極電極及汲極電極。另外，掃描線 407\_2 的與半導體膜 411\_2 重疊的區域用作電晶體 403\_2 的閘極電極。

信號線 409 的與半導體膜 411\_2 重疊的區域用作電晶體 403\_2 的源極電極。導電膜 413\_2 的與半導體膜 411\_2 重疊的區域用作電晶體 403\_2 的汲極電極。導電膜 413\_2 及像素電極 421\_2 在開口 417\_2 中連接。

電容元件 405\_2 與電容元件 405\_1 同樣，藉由設置於開口 423 中的導電膜 425 與電容線 415 電連接。電容元件 405\_2 包括：由氧化物半導體形成的半導體膜 419\_2；像素電極 421\_2；作為介電膜的形成於電晶體 403\_2 上的絕緣膜（圖 8 中未圖示）。由於半導體膜 419\_2、像素電極 421\_2 及介電膜都具有透光性，所以電容元件 405\_2 具有透光性。

另外，電晶體 403\_1 及電晶體 403\_2 以及電容元件 405\_1 及電容元件 405\_2 的剖面結構分別與圖 3 所示的電晶體 103 及電容元件 105 相同，因此在此對其進行省略。

在上面形狀看，鄰接的兩個像素之間設置有電容線，藉由使包含於各像素中的電容元件及該電容線連接，可以減少電容線的個數。由此，與在各像素中設置電容線的結構相比，可以進一步提高像素的孔徑比。

#### 〈變形例 6〉

在本發明的一個方式的半導體裝置中，設置在像素內的電晶體的形狀不侷限於圖 2 及圖 3 所示的電晶體的形狀，能夠適當地改變形狀。例如，在電晶體中，包括在信號線 109 中的源極電極形成爲 U 字型（C 字型、方格型或

馬蹄型），也可以爲圍繞包括汲極電極的導電膜的形狀。藉由採用這種形狀，即使電晶體的面積小，也可以確保充分寬的通道寬度，可以增加電晶體的開啓時流過的汲極電流（也稱爲通態電流）量。

#### 〈變形例 7〉

此外，在上述所示的像素 101、172、196 中，使用了半導體膜位於閘極絕緣膜與包括源極電極的信號線 109 及包括汲極電極的導電膜 113 之間的電晶體，但是也可以使用半導體膜位於包括源極電極的信號線及包括汲極電極的導電膜與絕緣膜 129 之間的電晶體。

#### 〈變形例 8〉

此外，在上述所示的像素 101、172、196 中，作爲電晶體示出通道蝕刻型電晶體，也可以使用通道保護型電晶體代替通道蝕刻型電晶體。藉由設置通道保護膜，半導體膜 111 的表面不暴露於在形成信號線及導電膜的製程中使用的蝕刻劑及蝕刻氣體，可以減少半導體膜 111 與通道保護膜之間的雜質。其結果是，可以降低在電晶體的源極電極與汲極電極之間流過的洩漏電流。

#### 〈變形例 9〉

此外，在上述所示的像素 101、172、196、401\_1、401\_2 中，作爲電晶體示出具有一個閘極電極的電晶體，

但是可以使用具有夾著半導體膜 111 對置的兩個閘極電極的電晶體代替上述電晶體。

電晶體在本實施方式所說明的電晶體 103 的絕緣膜 137 上具有導電膜。導電膜至少重疊於半導體膜 111 的通道形成區。較佳的是藉由將導電膜設置在重疊於半導體膜 111 的通道形成區的位置，來將導電膜的電位設為輸入到信號線 109 的視訊訊號的最低電位。其結果是，在對置於導電膜的半導體膜 111 的表面上可以控制在源極電極與汲極電極之間流過的電流，可以減少電晶體的電特性的偏差。此外，藉由設置導電膜，減輕周圍的電場的變化給半導體膜 111 帶來的影響，由此可以提高電晶體的可靠性。

導電膜可以使用與掃描線 107、信號線 109、像素電極 121 等同樣的材料及方法而形成。

如上所述，作為電容元件的一個電極，藉由使用在與包括在電晶體中的半導體膜相同的形成製程中形成的半導體膜，可以製造具有在提高孔徑比的同時能夠增大電荷容量的電容元件的半導體裝置。由此，可以得到顯示品質優良的半導體裝置。

另外，由於包括在電晶體中的使用氧化物半導體形成的半導體膜的氧缺陷得到減少並且氫等雜質被減少，因此本發明的一個方式的半導體裝置成為具有良好的電特性的半導體裝置。

另外，本實施方式所述的結構等可以適當地與其它實施方式所述的結構等組合使用。

## 實施方式 2

在本實施方式中，參照圖式對本發明的一個方式的半導體裝置進行說明，該半導體裝置具有與上述實施方式不同的結構。在本實施方式中，以液晶顯示裝置為例子而說明本發明的一個方式的半導體裝置。此外，本實施方式所說明的半導體裝置的電容元件的結構與上述實施方式不同。此外，在本實施方式所說明的半導體裝置中，與上述實施方式所說明的半導體裝置同樣的結構可以參照上述實施方式。

### 〈半導體裝置的結構〉

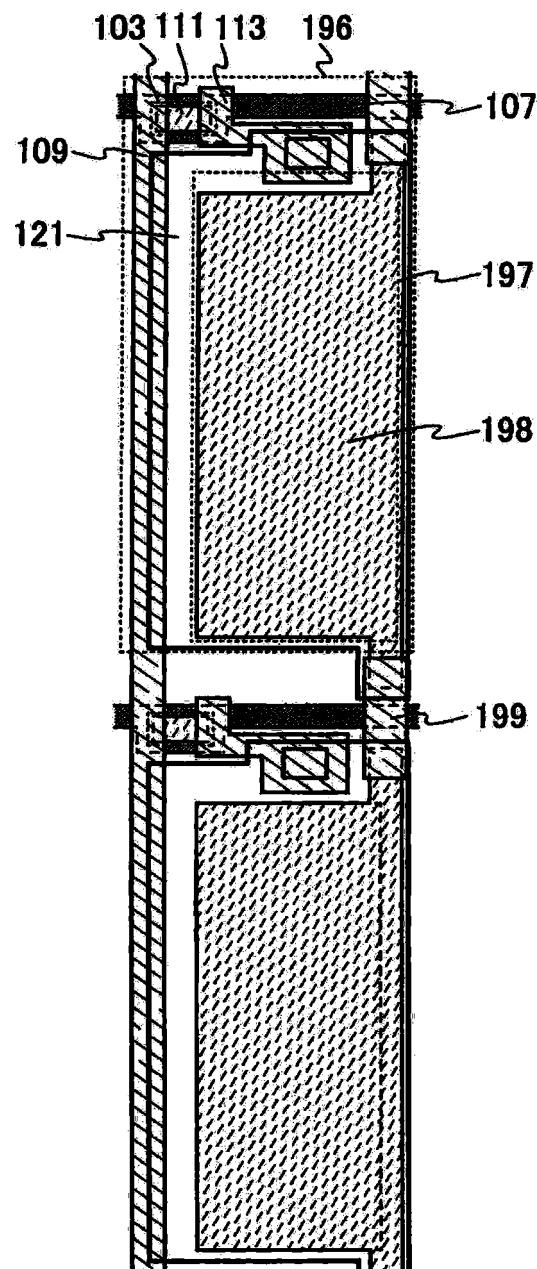

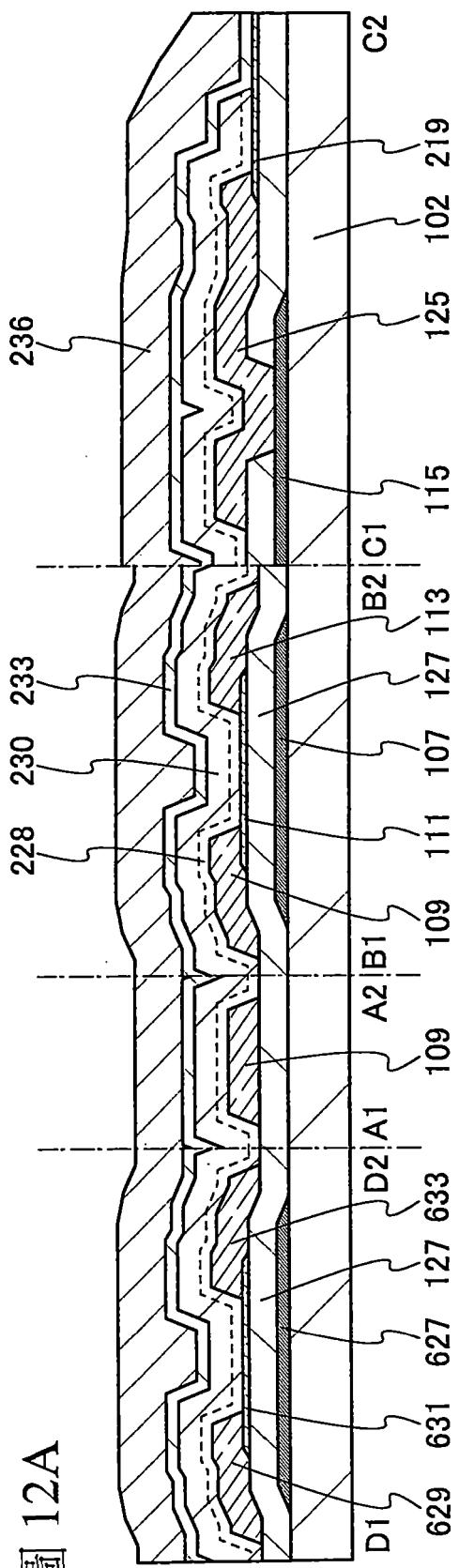

圖 9 示出本實施方式所說明的像素 101 的俯視圖。圖 9 所示的像素 201 在點劃線內的區域中不設置絕緣膜 229（未圖示）及絕緣膜 231（未圖示）。此外，在半導體膜 119 上位於絕緣膜 229（未圖示）及絕緣膜 231 的端部。因此，圖 9 所示的像素 201 的電容元件 205 包括作為一個電極的半導體膜 119、作為另一個電極的像素電極 221 及作為介電膜的絕緣膜 232 及絕緣膜 237（未圖示）。

接著，圖 10 是示出圖 9 的點劃線 A1-A2 間、點劃線 B1-B2 間、點劃線 C1-C2 間及設置在掃描線驅動電路 104（參照圖 1A）中的電晶體的剖面圖。這裡，省略掃描線驅動電路 104 的俯視圖，與此同時 D1-D2 示出掃描線驅動電路 104 的剖面圖。另外，這裡示出設置在掃描線驅動

電路 104 中的電晶體的剖面圖，但是該電晶體可以設置在信號線驅動電路 106 中。

以下示出本實施方式中的像素 201 的剖面結構。在基板 102 上設置有包括電晶體 103 的閘極電極的掃描線 107、與掃描線 107 設置於同一表面上的電容線 115。在掃描線 107 及電容線 115 上設置有閘極絕緣膜 127。在閘極絕緣膜 127 的與掃描線 107 重疊的區域上設置有半導體膜 111，在閘極絕緣膜 127 上設置有半導體膜 219。在半導體膜 111 及閘極絕緣膜 127 上設置有包括電晶體 103 的源極電極的信號線 109、包括電晶體 103 的汲極電極的導電膜 113。在閘極絕緣膜 127 中設置有到達電容線 115 的開口 123，在開口 123 中及其上、閘極絕緣膜 127 及半導體膜 219 上設置有導電膜 125。在閘極絕緣膜 127、信號線 109、半導體膜 111、導電膜 113、導電膜 125、半導體膜 219 上設置有用作電晶體 103 的保護絕緣膜的絕緣膜 229、絕緣膜 231、絕緣膜 232 及絕緣膜 237。此外，至少在成為電容元件 205 的區域中，在半導體膜 219 上設置有絕緣膜 232。在絕緣膜 229、絕緣膜 231、絕緣膜 232 及絕緣膜 237 中設置有到達導電膜 113 的開口 117（參照圖 9），在開口 117（參照圖 9）中及其上以及絕緣膜 232 上設置有像素電極 221。此外，也可以在基板 102 與掃描線 107、電容線 115 及閘極絕緣膜 127 之間設置有基底絕緣膜。

絕緣膜 229 是與實施方式 1 所說明的絕緣膜 129 同樣

的絕緣膜。絕緣膜 231 是與實施方式 1 所說明的絕緣膜 131 同樣的絕緣膜。絕緣膜 232 是與實施方式 1 所說明的絕緣膜 132 同樣的絕緣膜。絕緣膜 237 是與實施方式 1 所說明的絕緣膜 137 同樣的絕緣膜。像素電極 221 是與實施方式 1 所說明的像素電極 121 同樣的像素電極。

如本實施方式中的電容元件 205，藉由作為設置在用作一個電極的半導體膜 219 與用作另一個電極的像素電極 221 之間的介電膜使用絕緣膜 232 及絕緣膜 237，可以使介電膜的厚度比實施方式 1 中的電容元件 105 的介電膜的厚度薄。因此，本實施方式中的電容元件 205 與實施方式 1 中的電容元件 105 相比可以增大電荷容量。

此外，絕緣膜 232 及絕緣膜 237 用作電容元件 205 的介電膜。絕緣膜 232 由氮化絕緣膜形成，氮化絕緣膜具有與氧化矽等氧化絕緣膜相比相對介電常數高且內部應力大的傾向。由此，當作為電容元件 205 的介電膜只使用絕緣膜 232 而不使用絕緣膜 237 時，若絕緣膜 232 的厚度薄則電容元件 205 的電容值過大，不容易在低耗電量的情況下提高對像素寫入影像信號的速度。與此相反，若絕緣膜 232 的厚度厚，則內部應力過大，這引起電晶體的臨界電壓變動等電特性的惡化。此外，若絕緣膜 232 的內部應力大，則絕緣膜 232 容易從基板 102 剝離，由此良率降低。但是，藉由使用其相對介電常數比絕緣膜 232 低的氧化矽等的氧化絕緣物形成的絕緣膜 237 與絕緣膜 232 一起用作像素的電容元件的介電膜，可以將介電膜的介電常數調整

爲所希望的值而不增加絕緣膜 232 的厚度。

此外，由於絕緣膜 232 是與實施方式 1 的絕緣膜 132 同樣的氮化絕緣膜，所以半導體膜 219 的導電率高，成爲 n 型。此外，半導體膜 219 是由具有導體特性的金屬氧化物構成的具有透光性的導電膜。另外，半導體膜 219 的導電率比半導體膜 111 高。

此外，半導體膜 219 具有其導電率比半導體膜 111 高的區域。在本結構中，半導體膜 219 的至少接觸於絕緣膜 232 的區域是 n 型，其導電率比半導體膜 111 的接觸於絕緣膜 229 的區域高。

此外，較佳的是半導體膜 219 的氫濃度比半導體膜 111 高。在半導體膜 219 中，藉由二次離子質譜分析法 (SIMS : Secondary Ion Mass Spectrometry) 得到的氫濃度爲  $8 \times 10^{19} \text{ atoms/cm}^3$  以上，較佳爲  $1 \times 10^{20} \text{ atoms/cm}^3$  以上，更佳爲  $5 \times 10^{20} \text{ atoms/cm}^3$  以上。在半導體膜 111 中，藉由二次離子質譜分析法得到的氫濃度小於  $5 \times 10^{19} \text{ atoms/cm}^3$ ，較佳爲小於  $5 \times 10^{18} \text{ atoms/cm}^3$ ，較佳爲  $1 \times 10^{18} \text{ atoms/cm}^3$  以下，更佳爲  $5 \times 10^{17} \text{ atoms/cm}^3$  以下，進一步佳爲  $1 \times 10^{16} \text{ atoms/cm}^3$  以下。

此外，半導體膜 219 的電阻率比半導體膜 111 低。半導體膜 219 的電阻率較佳爲半導體膜 111 的電阻率的  $1 \times 10^{-8}$  倍以上且  $1 \times 10^{-1}$  倍以下，典型地爲  $1 \times 10^{-3} \Omega \text{cm}$  以上且小於  $1 \times 10^4 \Omega \text{cm}$ ，更佳爲  $1 \times 10^{-3} \Omega \text{cm}$  以上且小於  $1 \times 10^{-1} \Omega \text{cm}$ 。

在本實施方式的半導體裝置中，使電容元件 205 工作的方法與使實施方式 1 所記載的電容元件 105 工作的方法同樣，在使電容元件 205 工作的期間，將半導體膜 219 的電位（換言之，電容線 115 的電位）始終設定為比像素電極 121 的電位低電容元件 205 (MOS 電容器) 的臨界電壓 ( $V_{th}$ ) 以上。注意，在電容元件 205 中，用作一個電極的半導體膜 219 為  $n$  型，由於導電率高，所以臨界電壓向負方向漂移。半導體膜 219 的電位（換言之，電容線 115 的電位）根據電容元件 205 的臨界電壓的向負方向的漂移量，從像素電極 121 的能夠達到的最低電位升高。因此，當電容元件 205 的臨界電壓示出較大的負值時，可以使電容線 115 的電位比像素電極 121 的電位高。

如本實施方式那樣，作為電容元件 205 的一個電極的半導體膜 219 為  $n$  型，藉由增大導電率，可以使臨界電壓向負方向漂移，所以與實施方式 1 的電容元件 105 相比，可以擴大使電容元件 205 工作時需要的電位的選擇寬度。因此，本實施方式在使電容元件 205 工作的期間始終可以穩定地使電容元件 205 工作，所以是較佳的。

此外，由於包括在電容元件 205 中的半導體膜 219 為  $n$  型，導電率高，所以即使縮小電容元件 205 的平面面積也可以獲得充分的電荷容量。由於構成半導體膜 219 的氧化物半導體的可見光的穿透率為 80% 至 90%，所以縮小半導體膜 219 的面積，在像素中設置不形成半導體膜 219 的區域，由此可以提高從背光等光源發射的光的穿透率。

〈半導體裝置的製造方法〉

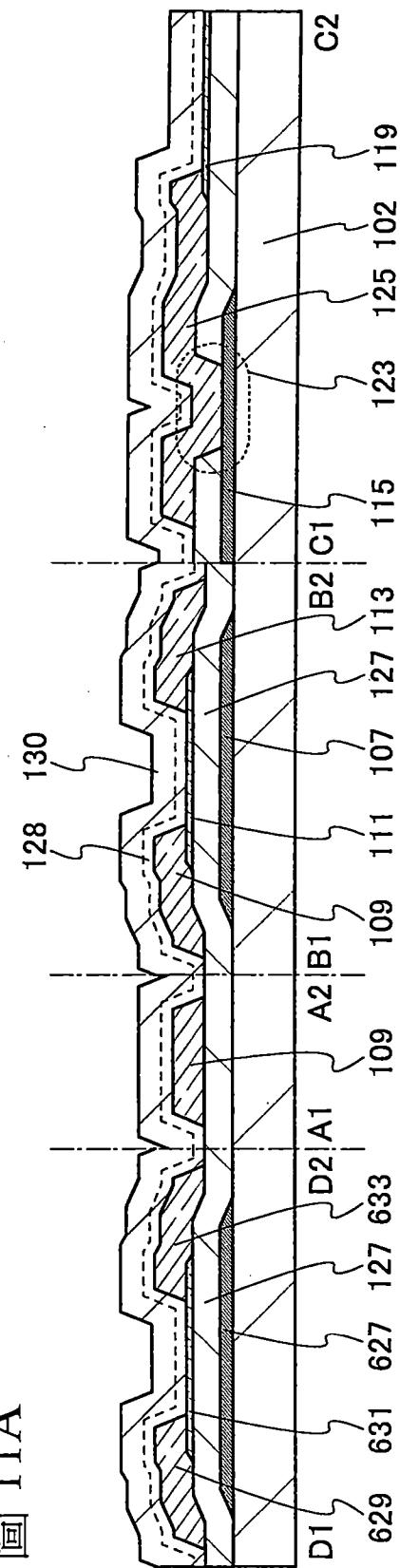

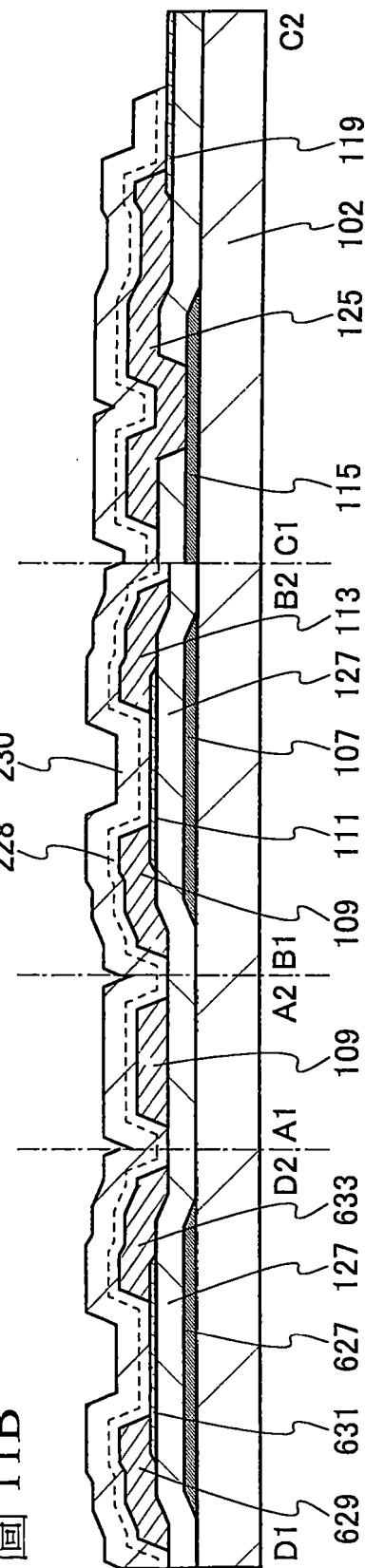

接著，參照圖 11A、圖 11B、圖 12A 及圖 12B 說明本實施方式所示的設置在基板 102 上的元件部的製造方法。

首先，在基板 102 上形成掃描線 107、電容線 115 及閘極電極 627，在基板 102、掃描線 107、電容線 115 及閘極電極 627 上形成加工為閘極絕緣膜 127 的絕緣膜，在該絕緣膜上形成半導體膜 111、半導體膜 119 及半導體膜 631，在該絕緣膜中形成到達電容線 115 的開口 123 來形成閘極絕緣膜 127 之後，形成信號線 109、導電膜 113、導電膜 125、源極電極 629 及汲極電極 633。接著，在閘極絕緣膜 127、半導體膜 111、半導體膜 119、半導體膜 631、信號線 109、導電膜 113、導電膜 125、源極電極 629 及汲極電極 633 上形成絕緣膜 128，在絕緣膜 128 上形成絕緣膜 130（參照圖 11A）。注意，到此為止的製程可以參照實施方式 1 進行。

接著，在至少重疊於半導體膜 119 的絕緣膜 130 的區域上形成遮罩，使用該遮罩進行加工來形成絕緣膜 228 及絕緣膜 230，並露出半導體膜 119（參照圖 11B）。作為該遮罩可以使用藉由光微影製程形成的光阻遮罩，該加工可以利用乾蝕刻和濕蝕刻中的一者或兩者來進行。

接著，在露出半導體膜 119 的區域及絕緣膜 230 上形成絕緣膜 233，在絕緣膜 233 上形成絕緣膜 236（參照圖 12A）。絕緣膜 233 是與實施方式 1 所說明的絕緣膜 133

同樣的絕緣膜。絕緣膜 236 是與實施方式 1 所說明的絕緣膜 136 同樣的絕緣膜。此外，在形成絕緣膜 233 及絕緣膜 236 之後等，也可以以絕緣膜 233 接觸於半導體膜 119 的狀態下進行加熱處理。注意，到此為止的製程也可以參照實施方式 1 進行。

藉由電漿 CVD 法或濺射法形成使用氮化絕緣膜形成的絕緣膜 233，半導體膜 119 暴露於電漿，在半導體膜 119 中生成氧缺陷。此外，藉由半導體膜 119 與由氮化絕緣膜形成的絕緣膜 233 接觸，氮或/及氬從絕緣膜 233 移動到半導體膜 119。包含在絕緣膜 233 中的氬進入氧缺陷中，生成作為載子的電子。或者，以絕緣膜 232 為氮化絕緣膜，藉由以絕緣膜 232 接觸於半導體膜 119 的狀態下進行加熱處理，可以使包含在該氮化絕緣膜中的氮或/及氬移動到半導體膜 119。包含在絕緣膜 233 中的氬進入氧缺陷中，生成作為載子的電子。其結果是，半導體膜 119 的導電率增大，而成為 n 型的半導體膜 219。此外，半導體膜 219 是由具有導體特性的金屬氧化物構成的具有透光性的導電膜。半導體膜 219 的導電率比半導體膜 111 高。

接著，在絕緣膜 228、絕緣膜 230、絕緣膜 233 及絕緣膜 236 中形成到達導電膜 113 的開口 117（參照圖 9），形成絕緣膜 229、絕緣膜 231、絕緣膜 232 及絕緣膜 237，形成藉由開口 117 接觸於導電膜 113 的像素電極 221（參照圖 12B）。注意，到此為止的製程也可以參照實施方式 1 進行。

藉由上述製程，可以製造本實施方式中的半導體裝置。

〈變形例〉

在本發明的一個方式的半導體裝置中可以適當地改變電容元件的結構。參照圖 13 說明本結構的具體例子。此外，這裡，只說明與圖 9 及圖 10 所說明的電容元件 105 不同的電容元件 245。

半導體膜 219 為 n 型，為了增大導電率，作為閘極絕緣膜 227 採用氮化絕緣膜的絕緣膜 225、氧化絕緣膜的絕緣膜 226 的疊層結構，在至少設置有半導體膜 219 的區域只設置氮化絕緣膜的絕緣膜 225。藉由採用這種結構，絕緣膜 225 的氮化絕緣膜接觸於半導體膜 219 的下表面，半導體膜 219 為 n 型，可以增大導電率。此時，電容元件 245 的介電膜是絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137。此外，絕緣膜 225 及絕緣膜 226 可以適當地使用可應用於閘極絕緣膜 127 的絕緣膜，絕緣膜 225 可以是與絕緣膜 132 同樣的絕緣膜。此外，為了實現本結構，可以參照實施方式 1 適當地加工絕緣膜 226。藉由採用圖 13 所示的結構，由於不進行絕緣膜 129 及絕緣膜 131 的蝕刻，所以可以防止減少半導體膜 219 的厚度，由此與圖 9 及圖 10 所示的半導體裝置相比可以提高良率。

此外，在圖 13 所示的結構中，也可以採用半導體膜 219 的上表面接觸於絕緣膜 132 的結構。換言之，在圖 13

所示的絕緣膜 129 及絕緣膜 131 中，也可以去除接觸於半導體膜 219 的區域。此時，電容元件 245 的介電膜是絕緣膜 132 及絕緣膜 137。藉由採用半導體膜 219 的上表面及下表面接觸於氮化絕緣膜的結構，與只有一個表面接觸於氮化絕緣膜的情況相比，效率好地充分使半導體膜 219 成為 n 型，可以增大導電率。

如上所述，藉由作為電容元件的一個電極使用在與包括在電晶體中的半導體膜相同的形成製程中形成的半導體膜，可以製造包括電容元件的半導體裝置，該電容元件的孔徑比典型地提高到 55% 以上，較佳為 60% 以上，並增大電荷容量。其結果是，可以獲得顯示品質優良的半導體裝置。

另外，由於包括在電晶體中的使用氧化物半導體形成的半導體膜的氧缺陷得到減少並且氫等雜質被減少，因此本發明的一個方式的半導體裝置成為具有良好的電特性的半導體裝置。

注意，本實施方式所示的結構等可以與其他實施方式所示的結構及其變形例適當地組合而使用。

### 實施方式 3

在本實施方式中，參照圖式對本發明的一個方式的半導體裝置進行說明，該半導體裝置具有與上述實施方式不同的結構。在本實施方式中，以液晶顯示裝置為例子而說明本發明的一個方式的半導體裝置。此外，在本實施方式

所說明的半導體裝置中，包括在電容元件中的半導體膜與上述實施方式不同。此外，在本實施方式所說明的半導體裝置中，與上述實施方式所說明的半導體裝置同樣的結構可以參照上述實施方式。

#### 〈半導體裝置的結構〉

以下說明設置在本實施方式所說明的液晶顯示裝置的像素部中的像素 301 的具體結構例子。圖 14 示出像素 301 的俯視圖。圖 14 所示的像素 301 包括電容元件 305，電容元件 305 設置在由像素 301 內的電容線 115 及信號線 109 圍繞的區域。電容元件 305 藉由設置在開口 123 中的導電膜 125 電連接於電容線 115。電容元件 305 包括由氧化物半導體形成且其導電率比半導體膜 111 高的半導體膜 319、像素電極 121 以及作為介電膜形成在電晶體 103 上的絕緣膜（圖 14 中未圖示）。由於半導體膜 319、像素電極 121 及介電膜都具有透光性，所以電容元件 305 具有透光性。

半導體膜 319 的導電率為  $10S/cm$  以上且  $1000S/cm$  以下，較佳為  $100S/cm$  以上且  $1000S/cm$  以下。

像這樣，半導體膜 319 具有透光性。換言之，可以在像素 101 內大面積地形成電容元件 305。由此，可以獲得提高孔徑比，典型地是 55% 以上，較佳為 60% 以上，並增大了電荷容量的半導體裝置。其結果是，可以獲得顯示品質優良的半導體裝置。此外，由於包括在電容元件 305 中

的半導體膜 319 為 n 型，導電率高，所以也可以說半導體膜 319 是具有導電性的膜。由於包括在電容元件 305 中的半導體膜 319 的導電率高，所以即使縮小電容元件 305 的平面面積也可以獲得充分的電荷容量。由於構成半導體膜 319 的氧化物半導體的光穿透率為 80% 至 90%，所以縮小半導體膜 319 的面積，在像素中設置不形成半導體膜 319 的區域，由此可以提高從背光等光源發射的光的穿透率。

接著，圖 15 是示出圖 14 的點劃線 A1-A2 間、點劃線 B1-B2 間、點劃線 C1-C2 間及設置在掃描線驅動電路 104（參照圖 1A）中的電晶體的剖面圖。這裡，省略掃描線驅動電路 104 的俯視圖，與此同時 D1-D2 示出掃描線驅動電路 104 的剖面圖。另外，這裡示出設置在掃描線驅動電路 104 中的電晶體的剖面圖，但是該電晶體可以設置在信號線驅動電路 106 中。

以下示出像素 301 的剖面結構。在基板 102 上設置有包括電晶體 103 的閘極電極的掃描線 107。在掃描線 107 上設置有閘極絕緣膜 127。在閘極絕緣膜 127 的與掃描線 107 重疊的區域上設置有半導體膜 111，在閘極絕緣膜 127 上設置有半導體膜 319。在半導體膜 111 及閘極絕緣膜 127 上設置有包括電晶體 103 的源極電極的信號線 109 及包括電晶體 103 的汲極電極的導電膜 113。此外，在閘極絕緣膜 127 及半導體膜 319 上設置有電容線 115。在閘極絕緣膜 127、信號線 109、半導體膜 111、導電膜 113、半導體膜 319 及電容線 115 上設置有用作電晶體 103 的保

護絕緣膜的絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137。在絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137 中設置有到達導電膜 113 的開口 117，在開口 117 中及絕緣膜 137 上設置有像素電極 121。

在本結構中的電容元件 305 中，一對電極中的一個電極是 n 型，是其導電率比半導體膜 111 高的半導體膜 319，一對電極中的另一個電極是像素電極 121，設置在一對電極之間的介電膜是絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137。

半導體膜 319 可以使用可應用於半導體膜 111 的半導體。由於在形成半導體膜 111 的同時形成半導體膜 319，所以半導體膜 319 包含構成半導體膜 111 的氧化物半導體的金屬元素。並且，由於半導體膜 319 的導電率比半導體膜 111 高較佳，所以較佳為包含增大導電率的元素（摻雜劑）。明確而言，在半導體膜 319 中作為摻雜劑包含硼、氮、氟、鋁、磷、砷、銦、錫、鎘和稀有氣體元素中的一種以上。半導體膜 319 所包含的摻雜濃度較佳為  $1 \times 10^{19} \text{ atoms/cm}^3$  以上且  $1 \times 10^{22} \text{ atoms/cm}^3$  以下。由此，半導體膜 319 的導電率可以為  $10 \text{ S/cm}$  以上且  $1000 \text{ S/cm}$  以下，較佳為  $100 \text{ S/cm}$  以上且  $1000 \text{ S/cm}$  以下，可以使半導體膜 319 充分用作電容元件 305 的一方的電極。另外，半導體膜 319 具有其導電率比半導體膜 111 高的區域。在本結構中，半導體膜 319 的至少接觸於絕緣膜 132 的區域的導電率比半導體膜 111 的接觸於絕緣膜 129 的區域高。此外，

半導體膜 319 由於包含上述元素（摻雜劑）所以是 n 型，且導電率高，由此也可說是具有導電性的膜。

〈半導體裝置的製造方法〉

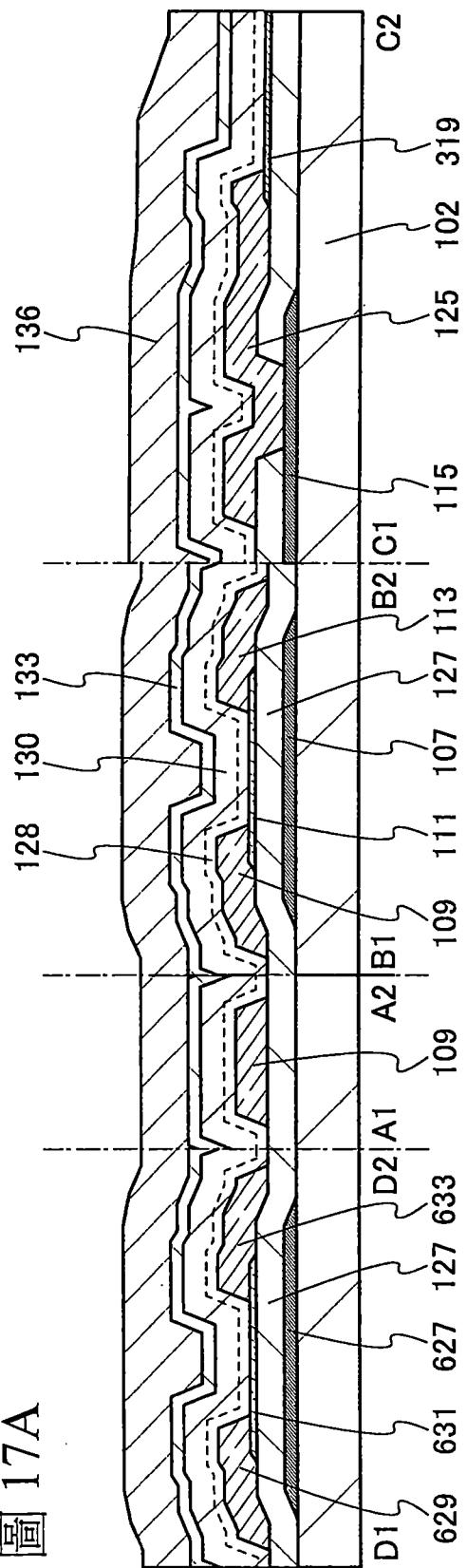

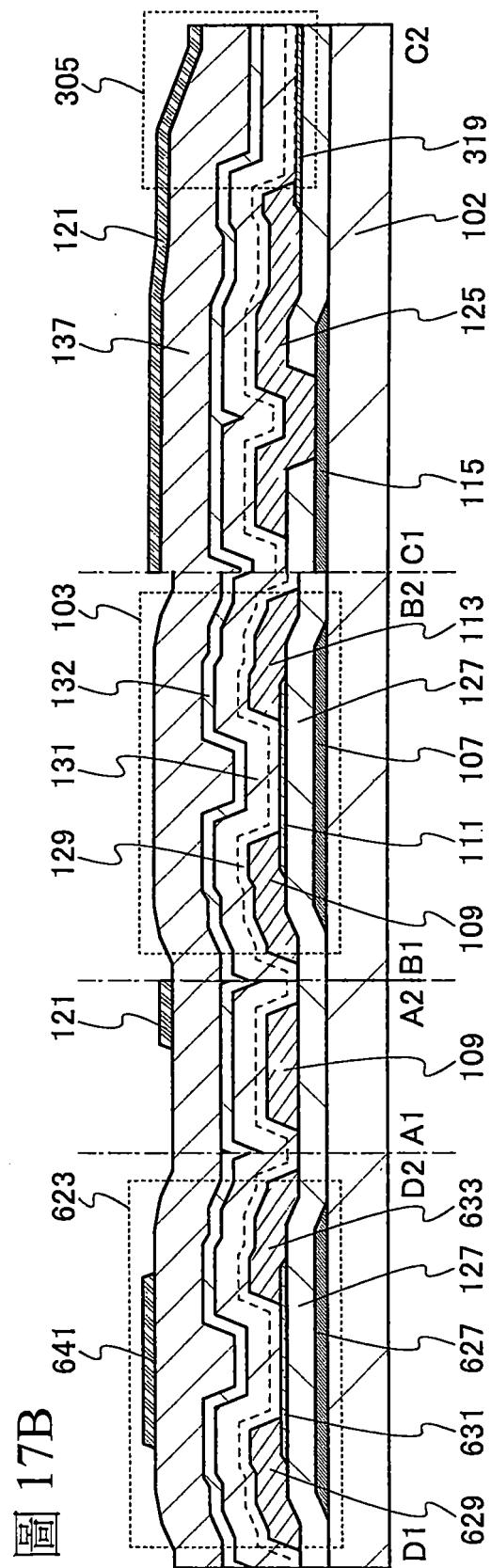

接著，參照圖 16A、圖 16B、圖 17A 及圖 17B 說明本實施方式所示的設置在基板 102 上的元件部的製造方法。

首先，在基板 102 上形成掃描線 107、電容線 115 及閘極電極 627，在基板 102、掃描線 107、電容線 115 及閘極電極 627 上形成加工為閘極絕緣膜 127 的絕緣膜 126，在該絕緣膜 126 上形成半導體膜 111 及半導體膜 119。此外，在重疊於閘極電極 627 的區域形成半導體膜 631（參照圖 16A）。注意，到此為止的製程可以參照實施方式 1 進行。

接著，在對半導體膜 119 添加摻雜劑形成半導體膜 319 之後，在絕緣膜 126 中形成到達電容線 115 的開口 123 形成閘極絕緣膜 127 之後，形成包括電晶體 103 的源極電極的信號線 109、包括電晶體 103 的汲極電極的導電膜 113、電連接半導體膜 319 與電容線 115 的導電膜 125。此外，形成源極電極 629 及汲極電極 633（參照圖 16B）。

作為對半導體膜 119 添加摻雜劑的方法有如下方法：在半導體膜 119 以外的區域設置遮罩，使用該遮罩，藉由離子植入法或離子摻雜法等添加選自硼、氮、氟、鋁、磷、砷、銦、錫、鎢和稀有氣體元素中的一種以上的摻雜

劑。此外，也可以將半導體膜 119 暴露於包含該摻雜劑的電漿來添加該摻雜劑，代替離子植入法或離子摻雜法。此外，也可以在添加摻雜劑之後進行加熱處理。該加熱處理可以參照進行半導體膜 111 及半導體膜 119 的脫氫化或脫水化的加熱處理的詳細內容適當地進行。

此外，添加摻雜劑的製程也可以在形成信號線 109、導電膜 113、導電膜 125、源極電極 629 及汲極電極 633 之後進行。此時，摻雜劑不添加到半導體膜 319 中的接觸於信號線 109、導電膜 113 及導電膜 125 的區域。

接著，在半導體膜 111、半導體膜 319、半導體膜 631、信號線 109、導電膜 113、導電膜 125、源極電極 629、汲極電極 633 及閘極絕緣膜 127 上形成絕緣膜 128，在絕緣膜 128 上形成絕緣膜 130，在絕緣膜 130 上形成絕緣膜 133。此外，在絕緣膜 133 上形成絕緣膜 136（參照圖 17A）。注意，該製程可以參照實施方式 1 進行。

接著，在絕緣膜 128、絕緣膜 130、絕緣膜 133 及絕緣膜 136 的重疊於導電膜 113 的區域形成到達導電膜 113 的開口 117（參照圖 14），並形成絕緣膜 129、絕緣膜 131、絕緣膜 132 及絕緣膜 137。接著，形成藉由開口 117 接觸於導電膜 113 的像素電極 121（參照圖 17B）。注意，該製程也可以參照實施方式 1 進行。

藉由上述製程，可以製造本實施方式中的半導體裝置。

如上所述，作為電容元件的一個電極，藉由使用在與包括在電晶體中的半導體膜相同的形成製程中形成的半導體膜，可以製造具有在提高孔徑比的同時能夠增大電荷容量的電容元件的半導體裝置。由此，可以得到顯示品質優良的半導體裝置。

另外，由於包括在電晶體中的使用氧化物半導體形成的半導體膜的氧缺陷得到減少並且氫等雜質被減少，因此本發明的一個方式的半導體裝置成為具有良好的電特性的半導體裝置。

注意，本實施方式所示的結構等可以與其他實施方式所示的結構及其變形例適當地組合而使用。

#### 實施方式 4

在本實施方式中，說明在上述實施方式所說明的包括在半導體裝置中的電晶體及電容元件中，可以應用於形成半導體膜的氧化物半導體的一個方式。

上述氧化物半導體較佳的是由如下半導體構成：非晶氧化物半導體、單晶氧化物半導體、多晶氧化物半導體以及包括結晶部的氧化物半導體（C Axis Aligned Crystalline Oxide Semiconductor：CAAC-OS）。CAAC-OS 膜是包含多個結晶部的氧化物半導體膜之一，大部分的結晶部為能夠容納在一邊短於 100nm 的立方體的尺寸。因此，有時包括在 CAAC-OS 膜中的結晶部為能夠容納在一邊短於 10nm、短於 5nm 或短於 3nm 的立方體的尺寸。

寸。CAAC-OS 膜的缺陷能階密度低於微晶氧化物半導體膜。下面，詳細說明 CAAC-OS 膜。

在 CAAC-OS 膜的穿透式電子顯微鏡 (TEM : Transmission Electron Microscope) 影像中，觀察不到結晶部與結晶部之間的明確的邊界，即晶界 (grain boundary)。因此，在 CAAC-OS 膜中，不容易發生起因於晶界的電子遷移率的降低。

由利用 TEM 所得到的大致平行於樣本面的方向上的 CAAC-OS 膜的影像 (剖面 TEM 影像) 可知，在結晶部中金屬原子排列為層狀。各金屬原子層具有反映被形成 CAAC-OS 膜的面 (也稱為被形成面) 或 CAAC-OS 膜的頂面的凸凹的形狀並以平行於 CAAC-OS 膜的被形成面或頂面的方式排列。

另一方面，根據從大致垂直於樣本面的方向觀察的 CAAC-OS 膜的 TEM 影像 (平面 TEM 影像) 可知，在結晶部中金屬原子排列為三角形狀或六角形狀。但是，在不同的結晶部之間，金屬原子的排列沒有規律性。

由剖面 TEM 影像以及平面 TEM 影像可知，CAAC-OS 膜的結晶部具有配向性。

使用 X 射線繞射 (XRD:X-Ray Diffraction) 裝置對 CAAC-OS 膜進行結構分析。例如，在利用 out-of-plane 法來分析具有  $\text{InGaZnO}_4$  的結晶的 CAAC-OS 膜時，在繞射角度 ( $2\theta$ ) 為  $31^\circ$  附近時會出現峰值。由於該峰值源自  $\text{InGaZnO}_4$  結晶的 (009) 面，由此可知 CAAC-OS 膜的結晶

具有 c 軸配向性，並且 c 軸朝向大致垂直於 CAAC-OS 膜的被形成面或頂面的方向。

另一方面，當利用從大致垂直於 c 軸的方向使 X 線入射的 *in-plane* 法分析 CAAC-OS 膜時，在  $2\theta$  為  $56^\circ$  附近時會出現峰值。該峰值來源於  $\text{InGaZnO}_4$  結晶的 (110) 面。在此，在將  $2\theta$  固定為  $56^\circ$  附近並在以樣本面的法線向量為軸 ( $\phi$  軸) 旋轉樣本的條件下進行分析 ( $\phi$  掃描)。在該樣本是  $\text{InGaZnO}_4$  的單晶氧化物半導體膜時，出現六個峰值。該六個峰值來源於相等於 (110) 面的結晶面。另一方面，當該樣本是 CAAC-OS 膜時，即使在將  $2\theta$  固定為  $56^\circ$  附近的狀態下進行  $\phi$  掃描也不能觀察到明確的峰值。

由上述結果可知，在具有 c 軸配向的 CAAC-OS 膜中，雖然 a 軸及 b 軸的方向在結晶部之間不同，但是 c 軸都朝向平行於被形成面或頂面的法線向量的方向。因此，在上述剖面 TEM 影像中觀察到的排列為層狀的各金屬原子層相當於與結晶的 ab 面平行的面。

注意，結晶部在形成 CAAC-OS 膜或進行加熱處理等晶化處理時形成。如上所述，結晶的 c 軸朝向平行於 CAAC-OS 膜的被形成面或頂面的法線向量的方向。由此，例如，當 CAAC-OS 膜的形狀因蝕刻等而發生改變時，結晶的 c 軸不一定平行於 CAAC-OS 膜的被形成面或頂面的法線向量。

此外，CAAC-OS 膜中的晶化度不一定均勻。例如，當 CAAC-OS 膜的結晶部是由 CAAC-OS 膜的頂面附近的

結晶成長而形成時，有時頂面附近的晶化度高於被形成面附近的晶化度。另外，當對 CAAC-OS 膜添加雜質時，被添加了雜質的區域的晶化度改變，所以有時 CAAC-OS 膜中的晶化度根據區域而不同。

注意，在藉由 out-of-plane 法分析包含  $\text{InGaZnO}_4$  結晶的 CAAC-OS 膜的情況下，除了  $2\theta$  為  $31^\circ$  附近的峰值之外，有時還觀察到  $2\theta$  為  $36^\circ$  附近的峰值。 $2\theta$  為  $36^\circ$  附近的峰值示出不具有 c 軸配向性的結晶包含在 CAAC-OS 膜的一部分中。較佳的是，在 CAAC-OS 膜中出現  $2\theta$  為  $31^\circ$  附近的峰值而不出現  $2\theta$  為  $36^\circ$  附近的峰值。

作為形成 CAAC-OS 膜的方法可以舉出如下三個方法。

第一個方法是：藉由在  $100^\circ\text{C}$  以上且  $450^\circ\text{C}$  以下的成膜溫度下形成氧化物半導體膜，形成包括在氧化物半導體膜中的結晶部的 c 軸在平行於被形成面的法線向量或表面的法線向量的方向上一致的結晶部。

第二個方法是：藉由在以薄厚度形成氧化物半導體膜之後進行  $200^\circ\text{C}$  以上且  $700^\circ\text{C}$  以下的加熱處理，形成包括在氧化物半導體膜中的結晶部的 c 軸在平行於被形成面的法線向量或表面的法線向量的方向上一致的結晶部。

第三個方法是：藉由在以薄厚度形成第一層氧化物半導體膜之後進行  $200^\circ\text{C}$  以上且  $700^\circ\text{C}$  以下的加熱處理，並形成第二層氧化物半導體膜，來形成包括在氧化物半導體膜中的結晶部的 c 軸在平行於被形成面的法線向量或表面

的法線向量的方向上一致的結晶部。

對於將 CAAC-OS 應用於氧化物半導體膜而形成的電晶體，起因於可見光或紫外光的照射的電特性的變動小。因此，將 CAAC-OS 應用於氧化物半導體膜的電晶體具有高可靠性。

此外，CAAC-OS 較佳為使用多晶的氧化物半導體濺射靶材且利用濺射法形成。當離子碰撞到該濺射靶材時，有時包含在濺射靶材中的結晶區域沿著 a-b 面劈開，即具有平行於 a-b 面的面的平板狀或顆粒狀的濺射粒子有時剝離。此時，藉由使該平板狀或顆粒狀的濺射粒子在保持結晶狀態的情況下到達被形成面，可以形成 CAAC-OS。

另外，為了形成 CAAC-OS，較佳為採用如下條件。

藉由降低成膜時的雜質的混入，可以抑制因雜質導致的結晶狀態的破壞。例如，可以降低存在於成膜室內的雜質（氫、水、二氧化碳及氮等）的濃度即可。另外，可以降低成膜氣體中的雜質濃度即可。明確而言，使用露點為 -80°C 以下，較佳為 -100°C 以下的成膜氣體。

另外，藉由增高成膜時的被形成面加熱溫度（例如，基板加熱溫度），在濺射粒子到達被形成面之後發生濺射粒子的遷移。明確而言，在將被形成面加熱溫度設定為 100°C 以上且 740°C 以下，較佳為 150°C 以上且 500°C 以下的狀態下進行成膜。藉由增高成膜時的被形成面的溫度，當平板狀或顆粒狀的濺射粒子到達被形成面時，在該被形成面上發生遷移，濺射粒子的平坦的面附著到被形成面。

另外，較佳的是，藉由增高成膜氣體中的氧比例並對電力進行最優化，減輕成膜時的電漿損傷。將成膜氣體中的氧比例設定為 30 體積%以上，較佳為 100 體積%。

以下，作為濺射靶材的一個例子示出 In-Ga-Zn-O 化合物靶材。

藉由將  $InO_x$  粉末、 $GaO_y$  粉末及  $ZnO_z$  粉末以規定的莫耳數混合，並進行加壓處理，然後在  $1000^{\circ}C$  以上且  $1500^{\circ}C$  以下的溫度下進行加熱處理，由此得到多晶的 In-Ga-Zn-O 化合物靶材。此外，也可以在冷卻（放冷）或加熱的同時進行該加壓處理。另外，X、Y 及 Z 為任意正數。在此， $InO_x$  粉末、 $GaO_y$  粉末及  $ZnO_z$  粉末的規定的莫耳數比例如為  $2:2:1$ 、 $8:4:3$ 、 $3:1:1$ 、 $1:1:1$ 、 $1:4:2:3$  或  $3:1:2$ 。另外，粉末的種類及混合粉末時的莫耳數比可以根據所製造的濺射靶材適當地改變即可。

另外，氧化物半導體膜也可以採用層疊有多個氧化物半導體膜的結構。例如，也可以作為氧化物半導體膜採用第一氧化物半導體膜和第二氧化物半導體膜的疊層，並且第一氧化物半導體膜和第二氧化物半導體膜分別使用不同的原子數比的金屬氧化物。例如，可以作為第一氧化物半導體膜使用包含兩種金屬的氧化物、包含三種金屬的氧化物或者包含四種金屬的氧化物，作為第二氧化物半導體膜使用包含與第一氧化物半導體膜不同的兩種金屬的氧化物、包含三種金屬的氧化物或者包含四種金屬的氧化物。

作為氧化物半導體膜採用兩層結構，也可以使第一氧

化物半導體膜與第二氧化物半導體膜的構成元素相同，並使兩者的原子數比不同。例如，也可以將第一氧化物半導體膜的原子數比設定為  $In : Ga : Zn = 3 : 1 : 2$ ，將第二氧化物半導體膜的原子數比設定為  $In : Ga : Zn = 1 : 1 : 1$ 。此外，也可以將第一氧化物半導體膜的原子數比設定為  $In : Ga : Zn = 2 : 1 : 3$ ，將第二氧化物半導體膜的原子數比設定為  $In : Ga : Zn = 1 : 3 : 2$ 。另外，各氧化物半導體膜的原子數比作為誤差包括上述原子數比的  $\pm 20\%$  的變動。

此時，較佳的是將第一氧化物半導體膜與第二氧化物半導體膜中的離閘極電極近的一側（通道一側）的氧化物半導體膜的 In 與 Ga 的原子數比設定為  $In \geq Ga$ 。另外，較佳的是將離閘極電極遠的一側（背通道一側）的氧化物半導體膜的 In 與 Ga 的原子數比設定為  $In < Ga$ 。藉由採用這些疊層結構，可以製造場效移動率高的電晶體。另一方面，藉由將離閘極電極近的一側（通道一側）的氧化物半導體膜的 In 與 Ga 的原子數比設定為  $In < Ga$ ，將背通道一側的氧化物半導體膜的 In 與 Ga 的原子數比設定為  $In \geq Ga$ ，可以減少電晶體的隨時間的變化或因可靠性測試導致的臨界電壓的變動量。

原子數比為  $In : Ga : Zn = 1 : 3 : 2$  的第一氧化物半導體膜可以藉由使用原子數比為  $In : Ga : Zn = 1 : 3 : 2$  的氧化物靶材的濺射法來形成。可以將基板溫度設定為室溫，作為濺射氣體使用氬或氬及氧的混合氣體來形成。原子數比為  $In : Ga : Zn = 3 : 1 : 2$  的第二氧化物半導體膜可以使

用原子數比爲  $In : Ga : Zn = 3 : 1 : 2$  的氧化物靶材並使用第一氧化物半導體膜同樣的方法形成。

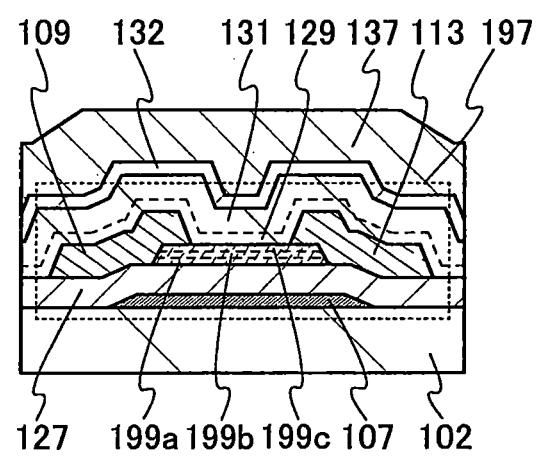

此外，作爲氧化物半導體膜採用三層結構，也可以使第一氧化物半導體膜至第三氧化物半導體膜的構成元素相同，並使它們的原子數比不同。參照圖 18 說明作爲氧化物半導體膜採用三層結構。

圖 18 所示的電晶體從閘極絕緣膜 127 一側依次層疊有第一氧化物半導體膜 199a、第二氧化物半導體膜 199b 及第三氧化物半導體膜 199c。作爲構成第一氧化物半導體膜 199a 及第三氧化物半導體膜 199c 的材料使用可以以  $InM1_xZn_yO_z$  ( $x \geq 1$ ,  $y > 1$ ,  $z > 0$ ,  $M1 = Ga, Hf$  等) 表示的材料。注意，當使構成第一氧化物半導體膜 199a 及第三氧化物半導體膜 199c 的材料中包含 Ga 時，當所包含的 Ga 的比例多時，明確而言，當在可以以  $InM1_xZn_yO_z$  表示的材料中超過  $x=10$  時，在成膜時有可能發生粉末，所以不適合的。

此外，構成第二氧化物半導體膜 199b 的材料使用可以以  $InM2_xZn_yO_z$  ( $x \geq 1$ ,  $y \geq x$ ,  $z > 0$ ,  $M2 = Ga, Sn$  等) 表示的材料。

以構成如下結構的方式適當地選擇第一氧化物半導體膜 199a、第二氧化物半導體膜 199b 及第三氧化物半導體膜 199c 的材料，該結構是與第一氧化物半導體膜 199a 的傳導帶及第三氧化物半導體膜 199c 的傳導帶相比第二氧化物半導體膜 199b 的傳導帶離真空能階更深的阱結構。

此外，在氧化物半導體膜中第 14 族元素之一的矽或碳成爲施體的供應源。由此，當矽或碳包含在氧化物半導體膜中時，氧化物半導體膜有可能成爲 n 型化。由此，包含在各氧化物半導體膜中的矽的濃度及碳的濃度分別爲  $3 \times 10^{18}/\text{cm}^3$  以下，較佳爲  $3 \times 10^{17}/\text{cm}^3$  以下。尤其是，爲了不在第二氧化物半導體膜 199b 中混入多量的第 14 族元素，較佳爲用第一氧化物半導體膜 199a 及第三氧化物半導體膜 199c 夾住成爲載子路徑的第二氧化物半導體膜 199b 或圍繞第二氧化物半導體膜 199b。即，第一氧化物半導體膜 199a 及第三氧化物半導體膜 199c 也可以稱爲障壁膜，該障壁膜防止在第二氧化物半導體膜 199b 中混入矽、碳等的第 14 族元素。

例如，也可以將第一氧化物半導體膜 199a 的原子數比設定爲  $\text{In} : \text{Ga} : \text{Zn} = 1 : 3 : 2$ ，將第二氧化物半導體膜 199b 的原子數比設定爲  $\text{In} : \text{Ga} : \text{Zn} = 3 : 1 : 2$ ，將第三氧化物半導體膜 199c 的原子數比設定爲  $\text{In} : \text{Ga} : \text{Zn} = 1 : 1 : 1$ 。此外，第三氧化物半導體膜 199c 可以藉由使用原子數比設定爲  $\text{In} : \text{Ga} : \text{Zn} = 1 : 1 : 1$  的氧化物靶材的濺射法來形成。

或者，也可以採用層疊如下膜的三層結構：作爲第一氧化物半導體膜 199a 使用將原子數比設定爲  $\text{In} : \text{Ga} : \text{Zn} = 1 : 3 : 2$  的氧化物半導體膜；作爲第二氧化物半導體膜 199b 使用將原子數比設定爲  $\text{In} : \text{Ga} : \text{Zn} = 1 : 1 : 1$  或  $\text{In} : \text{Ga} : \text{Zn} = 1 : 3 : 2$  的氧化物半導體膜；以及作爲第三

氧化物半導體膜 199c 使用將原子數比設定為  $In : Ga : Zn = 1 : 3 : 2$  的氧化物半導體膜。

由於第一氧化物半導體膜 199a 至第三氧化物半導體膜 199c 的構成元素相同，所以第二氧化物半導體膜 199b 與第一氧化物半導體膜 199a 之間的介面的缺陷能階（陷阱能階密度）很低。詳細地說，該缺陷能階（陷阱能階）比閘極絕緣膜 127 與第一氧化物半導體膜 199a 之間的介面的缺陷能階密度低。由此，如上所述藉由層疊氧化物半導體膜，可以減少電晶體的隨時間的變化或因可靠性測試導致的臨界電壓的變動量。

此外，藉由以構成如下阱結構的方式適當地選擇第一氧化物半導體膜 199a、第二氧化物半導體膜 199b 及第三氧化物半導體膜 199c 的材料，該阱結構是與第一氧化物半導體膜 199a 的傳導帶及第三氧化物半導體膜 199c 的傳導帶相比第二氧化物半導體膜 199b 的傳導帶離真空能階更深的阱結構，可以提高電晶體的場效移動率，並可以減少電晶體的隨時間的變化或因可靠性測試導致的臨界電壓的變動量。

另外，也可以作為第一氧化物半導體膜 199a 至第三氧化物半導體膜 199c 應用結晶性不同的氧化物半導體。就是說，也可以採用適當地組合單晶氧化物半導體、多晶氧化物半導體、非晶氧化物半導體及 CAAC-OS 的結構。此外，當第一氧化物半導體膜 199a 至第三氧化物半導體膜 199c 中的任一個使用非晶氧化物半導體時，可以緩和

氧化物半導體膜的內部應力或外部應力，而降低電晶體的特性偏差。此外，可以減少電晶體的隨時間的變化或因可靠性測試導致的臨界電壓的變動量。

此外，較佳的是至少成為通道形成區的第二氧化物半導體膜 199b 為 CAAC-OS。另外，背通道一側的氧化物半導體膜，即本實施方式中的第三氧化物半導體膜 199c 較佳為非晶或 CAAC-OS。藉由採用上述那樣的結構，可以減少電晶體的隨時間的變化或因可靠性測試導致的臨界電壓的變動量。

本實施方式所示的結構等可以與其他實施方式所示的結構適當地組合而使用。

### 實施方式 5

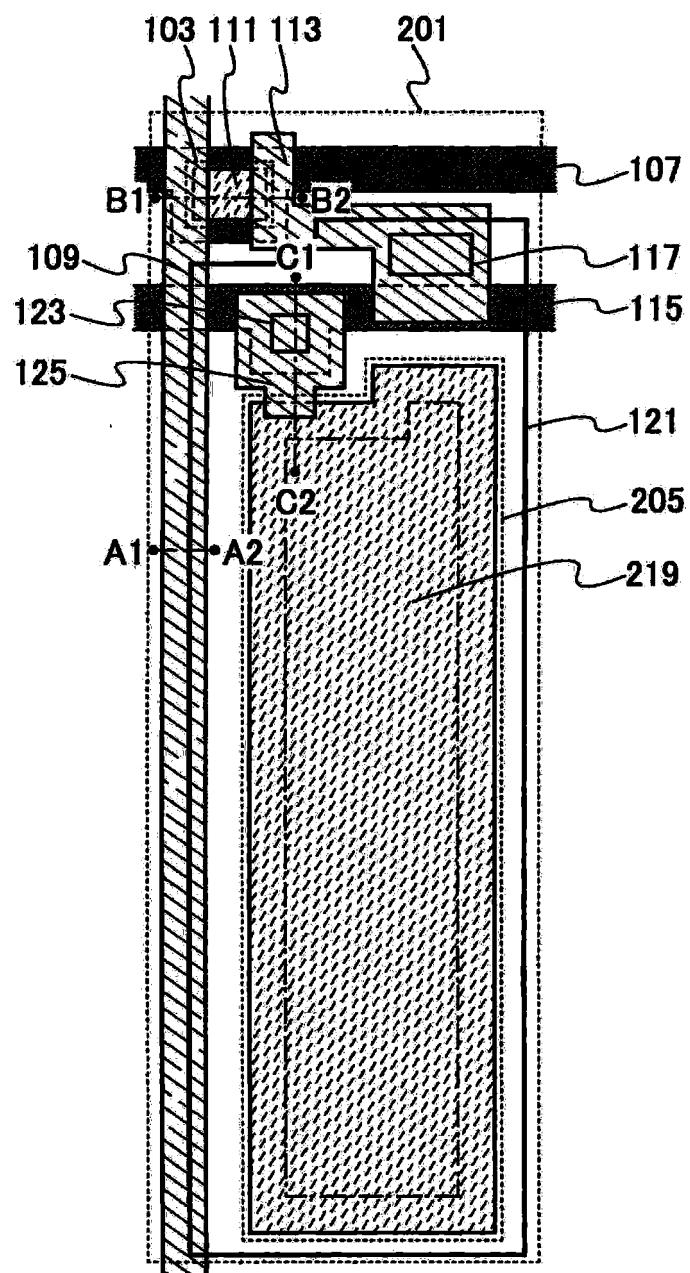

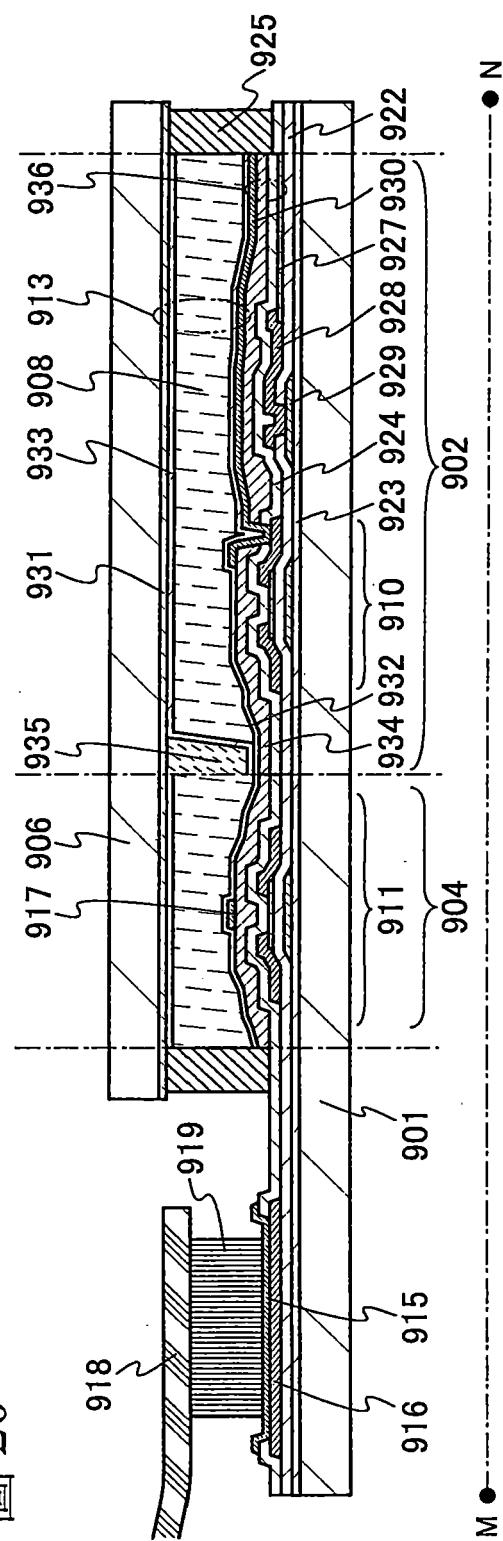

藉由使用上述實施方式所例示的電晶體及電容元件可以製造具有顯示功能的半導體裝置（也稱為顯示裝置）。此外，藉由將包括電晶體的驅動電路的一部分或全部與像素部一起形成在同一個基板上，可以形成系統整合型面板（system-on-panel）。在本實施方式中，參照圖 19A 至圖 21C 說明使用上述實施方式所例示的電晶體的顯示裝置的例子。此外，圖 20 是示出沿圖 19B 中的 M-N 點劃線的剖面結構的剖面圖。此外，在圖 20 中關於像素部的結構只記載其一部分。

在圖 19A 中，以圍繞設置在第一基板 901 上的像素部 902 的方式設置有密封材料 905，並且使用第二基板 906

進行密封。在圖 19A 中，在第一基板 901 上的與由密封材料 905 圍繞的區域不同的區域中安裝有使用單晶半導體或多晶半導體形成在另行準備的基板上的信號線驅動電路 903 及掃描線驅動電路 904。此外，供應到信號線驅動電路 903、掃描線驅動電路 904 或者像素部 902 的各種信號及電位藉由 FPC (Flexible printed circuit：撓性印刷電路) 918a、FPC918b 供應。

在圖 19B 和圖 19C 中，以圍繞設置在第一基板 901 上的像素部 902 和掃描線驅動電路 904 的方式設置有密封材料 905。此外，在像素部 902 和掃描線驅動電路 904 上設置有第二基板 906。因此，像素部 902 及掃描線驅動電路 904 與顯示元件一起由第一基板 901、密封材料 905 以及第二基板 906 密封。在圖 19B 和圖 19C 中，在第一基板 901 上的與由密封材料 905 圍繞的區域不同的區域中安裝有使用單晶半導體或多晶半導體形成在另行準備的基板上的信號線驅動電路 903。在圖 19B 和圖 19C 中，供應到信號線驅動電路 903、掃描線驅動電路 904 或者像素部 902 的各種信號及電位由 FPC918 供應。

此外，圖 19B 和圖 19C 示出另行形成信號線驅動電路 903 並且將其安裝到第一基板 901 的例子，但是不侷限於該結構。既可以另行形成掃描線驅動電路並進行安裝，又可以僅另行形成信號線驅動電路的一部分或者掃描線驅動電路的一部分並進行安裝。

另外，對另行形成的驅動電路的連接方法沒有特別的

限制，而可以採用 COG (Chip On Glass：晶粒玻璃接合) 方法、打線接合方法或者 TAB (Tape Automated Bonding：捲帶式自動接合) 方法等。圖 19A 是藉由 COG 方法安裝信號線驅動電路 903、掃描線驅動電路 904 的例子，圖 19B 是藉由 COG 方法安裝信號線驅動電路 903 的例子，而圖 19C 是藉由 TAB 方法安裝信號線驅動電路 903 的例子。

此外，顯示裝置包括顯示元件為密封狀態的面板和在該面板中安裝有包含控制器的 IC 等的模組。

注意，本說明書中的顯示裝置是指影像顯示裝置或顯示裝置。此外，也可以用作光源（包括照明設備）代替顯示裝置。另外，顯示裝置還包括：安裝有諸如 FPC 或 TCP 的連接器的模組；在 TCP 的端部設置有印刷線路板的模組；或者藉由 COG 方式將 IC（積體電路）直接安裝到顯示元件的模組。

此外，設置在第一基板上的像素部及掃描線驅動電路具有多個電晶體，可以應用上述實施方式所示的電晶體。

作為設置在顯示裝置中的顯示元件，可以使用液晶元件（也稱為液晶顯示元件）、發光元件（也稱為發光顯示元件）。發光元件將由電流或電壓控制亮度的元件包括在其範疇內，明確而言，包括無機 EL (Electro Luminescence：電致發光) 元件、有機 EL 元件等。此外，也可以應用電子墨水等由於電作用而改變對比度的顯示媒介。圖 20 示出作為顯示元件使用液晶元件的液晶顯

示裝置的例子。

圖 20 所示的液晶顯示裝置是垂直電場方式的液晶顯示裝置。液晶顯示裝置包括連接端子電極 915 及端子電極 916，連接端子電極 915 及端子電極 916 藉由各向異性導電劑 919 電連接到 FPC918 所具有的端子。

連接端子電極 915 由與第一電極 930 相同的導電膜形成，並且，端子電極 916 由與電晶體 910、電晶體 911 的源極電極及汲極電極相同的導電膜形成。

此外，設置在第一基板 901 上的像素部 902、掃描線驅動電路 904 包括多個電晶體，在圖 20 中示出像素部 902 所包括的電晶體 910、掃描線驅動電路 904 所包括的電晶體 911。在電晶體 910 及電晶體 911 上設置有相當於實施方式 1 所示的絕緣膜 129、絕緣膜 131 及絕緣膜 132 的絕緣膜 924。此外，在絕緣膜 924 上設置有相當於實施方式 1 所示的絕緣膜 137 的絕緣膜 934。此外，絕緣膜 923 用作基底膜。

在本實施方式中，作為電晶體 910 可以應用上述實施方式 1 至實施方式 3 所示的設置在像素中的電晶體。作為電晶體 911 可以應用上述實施方式 1 至實施方式 3 所示的設置在掃描線驅動電路中的電晶體。另外，使用氧化物半導體膜 927、絕緣膜 924、絕緣膜 934 及第一電極 930 構成電容元件 936。此外，氧化物半導體膜 927 藉由電極 928 電連接於電容佈線 929。電極 928 使用與電晶體 910、電晶體 911 的源極電極及汲極電極相同的材料及相

同的製程形成。電容佈線 929 使用與電晶體 910、電晶體 911 的閘極電極相同的材料及相同的製程形成。注意，這裡作為電容元件 936 示出實施方式 1 所示的電容元件，但是，也可以適當地使用其他實施方式所示的電容元件。

設置在像素部 902 中的電晶體 910 與顯示元件電連接，而構成顯示面板。顯示元件只要能夠進行顯示就沒有特別的限制，而可以使用各種各樣的顯示元件。

作為顯示元件的液晶元件 913 包括第一電極 930、第二電極 931 以及液晶層 908。另外，以夾持液晶層 908 的方式設置有用作配向膜的絕緣膜 932、絕緣膜 933。此外，第二電極 931 設置在第二基板 906 一側，並且，第一電極 930 和第二電極 931 隔著液晶層 908 重疊。

關於對顯示元件施加電壓的第一電極及第二電極（也稱為像素電極、共用電極、反電極等），可以根據取出光的方向、設置電極的位置以及電極的圖案結構選擇透光性或反射性。

第一電極 930 及第二電極 931 可以適當地使用與實施方式 1 所示的像素電極 121 相同的材料。

此外，間隔物 935 是藉由對絕緣膜選擇性地進行蝕刻而得到的柱狀間隔物，並且它是為控制第一電極 930 與第二電極 931 之間的間隔（單元間隙）而設置的。此外，也可以使用球狀間隔物。

當作為顯示元件使用液晶元件時，可以使用熱致液晶、低分子液晶、高分子液晶、高分子分散型液晶、鐵電

液晶、反鐵電液晶等。上述液晶材料根據條件而呈現膽固醇相、近晶相、立方相、手性向列相、均質相等。

另外，也可以使用不使用配向膜的呈現藍相的液晶。藍相是液晶相中之一種，當使膽固醇相液晶的溫度升高時，在即將由膽固醇相轉變成均質相之前呈現。由於藍相只出現在較窄的溫度範圍內，所以為了改善溫度範圍而將混合手性試劑的液晶組成物用於液晶層。此外，配向膜由有機樹脂構成，由於有機樹脂包含氫或水等，所以有可能降低本發明的一個方式的半導體裝置的電晶體的電特性。於是，藉由作為液晶層使用藍相，可以製造本發明的一個方式的半導體裝置而不使用有機樹脂，可以獲得可靠性高的半導體裝置。

第一基板 901 和第二基板 906 由密封材料 925 固定。作為密封材料 925，可以使用熱固性樹脂或光硬化性樹脂等有機樹脂。另外，密封材料 925 接觸於絕緣膜 924。此外，密封材料 925 相當於圖 19A 至圖 19C 所示的密封材料 905。

密封材料 925 設置在絕緣膜 924 上。此外，絕緣膜 934 設置在密封材料 925 的內側。絕緣膜 924 的最上層是氮化絕緣膜，可以抑制從外部侵入氫或水等雜質。另一方面，絕緣膜 934 具有高透濕性。因此，將絕緣膜 934 設置在密封材料 925 的內側，在絕緣膜 924 上設置密封材料 925，可以抑制從外部侵入氫或水等雜質，並可抑制電晶體 910 及電晶體 911 的電特性的變動。

此外，在液晶顯示裝置中，適當地設置黑矩陣（遮光膜）、偏振構件、相位差構件、抗反射構件等的光學構件（光學基板）等。例如，也可以使用利用偏振基板以及相位差基板的圓偏振光。此外，作為光源，也可以使用背光、側光燈等。

此外，由於電晶體容易被靜電等損壞，所以較佳為設置用來保護驅動電路的保護電路。保護電路較佳為使用非線性元件構成。

圖 21A 至圖 21C 示出在圖 20 所示的液晶顯示裝置中與將設置在基板 906 上的第二電極 931 電連接的公共連接部（焊盤部）形成在基板 901 上的例子。

公共連接部配置於與用來黏結基板 901 和基板 906 的密封材料重疊的位置，並且藉由密封材料所包含的導電粒子與第二電極 931 電連接。或者，在不與密封材料重疊的位置（注意，像素部以外的位置）設置公共連接部，並且，以與公共連接部重疊的方式將包含導電粒子的膏劑與密封材料另行設置，而與第二電極 931 電連接。

圖 21A 是公共連接部的剖面圖，並相當於圖 21B 所示的俯視圖的 I-J。

共用電位線 975 設置在閘極絕緣膜 922 上並利用與圖 21A 和圖 21B 所示的電晶體 910 的源極電極 971 或汲極電極 973 相同的材料及製程製造。

此外，共用電位線 975 由絕緣膜 924 及絕緣膜 934 覆蓋，絕緣膜 924 及絕緣膜 934 在重疊於共用電位線 975 的

位置上具有多個開口。該開口在與使電晶體 910 的源極電極 971 或汲極電極 973 與第一電極 930 連接的接觸孔相同的製程中製造。

此外，共用電位線 975 及共用電極 977 在開口中連接。共用電極 977 設置在絕緣膜 934 上，並使用與連接端子電極 915、像素部的第一電極 930 相同的材料及製程製造。

如此，與像素部 902 的切換元件的製程共同地製造公共連接部。

共用電極 977 是與包括在密封材料中的導電粒子接觸的電極，並與基板 906 的第二電極 931 電連接。

此外，如圖 21C 所示，共用電位線 985 也可以使用與電晶體 910 的閘極電極相同的材料及製程製造。

在圖 21C 所示的公共連接部中，共用電位線 985 設置在閘極絕緣膜 922、絕緣膜 924 及絕緣膜 934 的下層，閘極絕緣膜 922、絕緣膜 924 及絕緣膜 934 在重疊於共用電位線 985 的位置上具有多個開口。該開口在與使電晶體 910 的源極電極 971 或汲極電極 973 與第一電極 930 連接的接觸孔相同的製程中對絕緣膜 924 及絕緣膜 934 進行蝕刻之後，還對閘極絕緣膜 922 選擇性地進行蝕刻形成。

此外，共用電位線 985 及共用電極 987 在開口中連接。共用電極 987 設置在絕緣膜 924 上，並使用與連接端子電極 915、像素部的第一電極 930 相同的材料及製程製造。

如上所述，藉由應用上述實施方式所示的電晶體及電容元件，可以提供提高了孔徑比且具有增大了電荷容量的電容元件的半導體裝置。其結果是，可以獲得顯示品質優良的半導體裝置。

另外，由於包括在電晶體中的使用氧化物半導體形成的半導體膜的氧缺陷得到減少並且氫等雜質被減少，因此本發明的一個方式的半導體裝置成為具有良好的電特性的半導體裝置。

另外，本實施方式所述的結構等可以適當地與其它實施方式所述的結構等組合使用。

## 實施方式 6

本發明的一個方式的半導體裝置可以應用於各種電子裝置（也包括遊戲機）。作為電子裝置，可以舉出電視機（也稱為電視或電視接收機）、用於電腦等的顯示器、數位相機、數位攝影機、數位相框、行動電話機、可攜式遊戲機、可攜式資訊終端、音頻再生裝置、遊戲機（彈珠機（pachinko machine）或投幣機（slot machine）等）、外殼遊戲機。圖 22A 至圖 22C 示出上述電子裝置的一個例子。

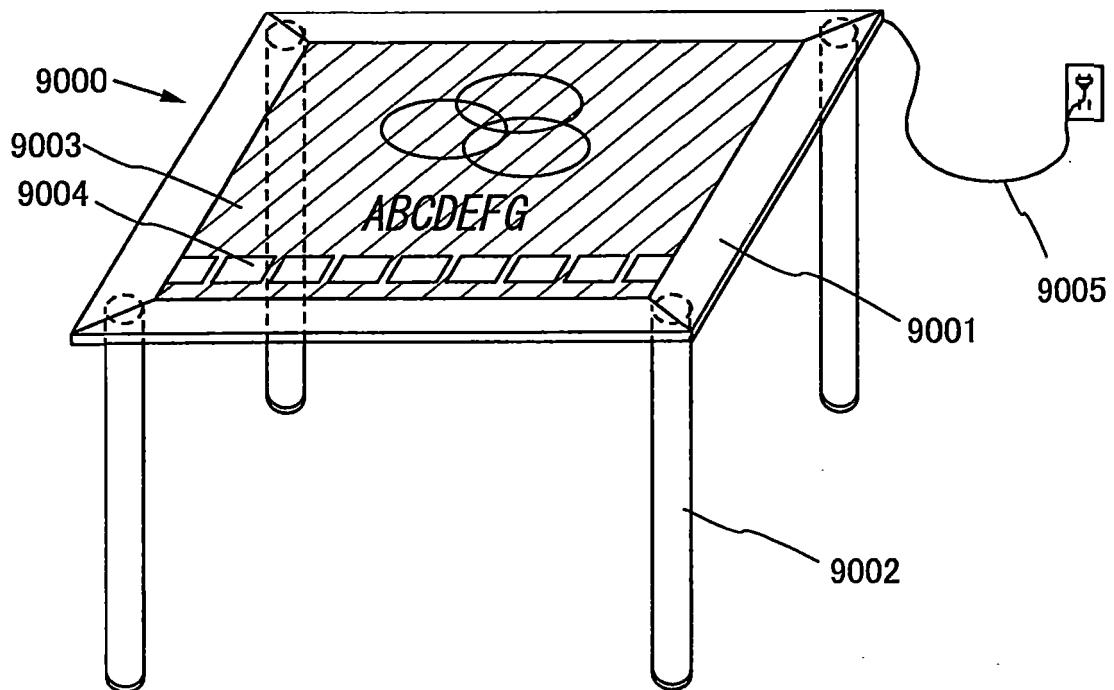

圖 22A 示出具有顯示部的桌子 9000。在桌子 9000 中，外殼 9001 組裝有顯示部 9003，利用顯示部 9003 可以顯示影像。另外，示出利用四個桌腿 9002 支撐外殼 9001 的結構。另外，外殼 9001 具有用於供應電力的電源

供應線 9005。

可以將上述實施方式中任一個所示的半導體裝置用於顯示部 9003。由此可以提高顯示部 9003 的顯示品質。

顯示部 9003 具有觸屏輸入功能，藉由用手指等按觸顯示於桌子 9000 的顯示部 9003 中的顯示按鈕 9004 來可以進行屏面操作或資訊輸入，並且桌子 9000 也可以用作如下控制裝置，即藉由使其具有能夠與其他家電產品進行通信的功能或能夠控制其他家電產品的功能，而藉由屏面操作控制其他家電產品。例如，藉由使用具有影像感測器功能的半導體裝置，可以使顯示部 9003 具有觸屏輸入功能。

另外，利用設置於外殼 9001 的鉸鏈也可以將顯示部 9003 的屏面以垂直於地板的方式立起來，從而也可以將桌子用作電視機。雖然當在小房間裡設置大屏面的電視機時自由使用的空間變小，但是若在桌子內安裝有顯示部則可以有效地利用房間的空間。

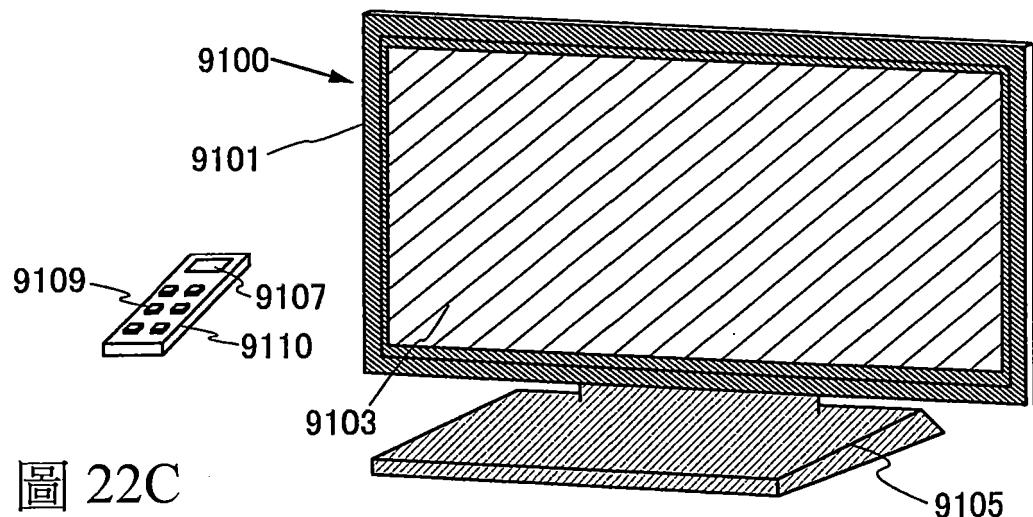

圖 22B 示出電視機 9100。在電視機 9100 中，外殼 9101 組裝有顯示部 9103，並且利用顯示部 9103 可以顯示影像。此外，在此示出利用支架 9105 支撐外殼 9101 的結構。

藉由利用外殼 9101 所具備的操作開關、另外提供的遙控器 9110，可以進行電視機 9100 的操作。藉由利用遙控器 9110 所具備的操作鍵 9109，可以進行頻道及音量的操作，並可以對在顯示部 9103 上顯示的影像進行操作。

此外，也可以採用在遙控器 9110 中設置顯示從該遙控器 9110 輸出的資訊的顯示部 9107 的結構。

圖 22B 所示的電視機 9100 具備接收機及數據機等。電視機 9100 可以利用接收機接收一般的電視廣播。再者，電視機 9100 藉由數據機連接到有線或無線方式的通信網路，也可以進行單向（從發送者到接收者）或雙向（發送者和接收者之間或接收者之間等）的資訊通信。

可以將上述實施方式中任一個所示的半導體裝置用於顯示部 9103、9107。由此可以提高電視機的顯示品質。

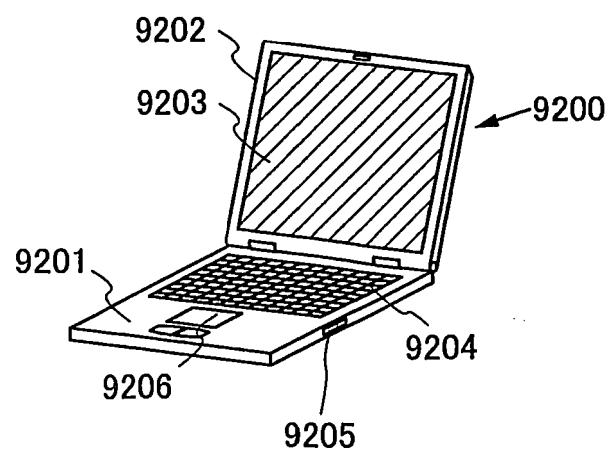

圖 22C 示出電腦 9200，該電腦包括主體 9201、外殼 9202、顯示部 9203、鍵盤 9204、外部連接埠 9205、指向裝置 9206 等。

可以將上述實施方式中任一個所示的半導體裝置用於顯示部 9203。由此可以提高電腦 9200 的顯示品質。

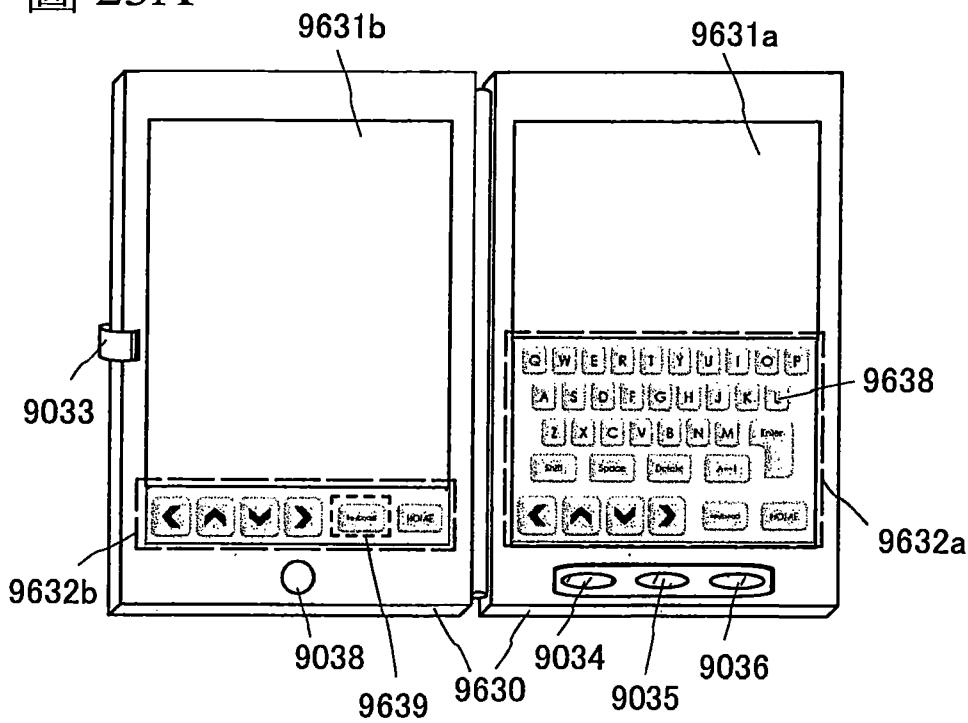

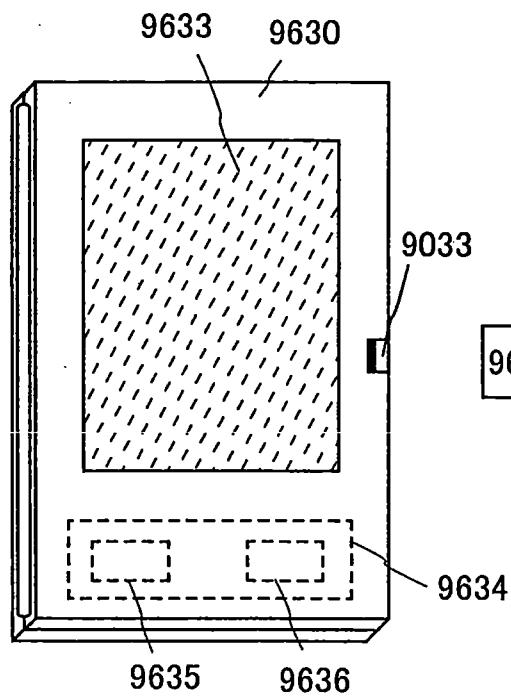

圖 23A 和圖 23B 是能夠折疊的平板終端。圖 23A 是打開的狀態，並且平板終端包括外殼 9630、顯示部 9631a、顯示部 9631b、顯示模式切換開關 9034、電源開關 9035、省電模式切換開關 9036、卡子 9033 以及操作開關 9038。

可以將上述實施方式中任一個所示的半導體裝置用於顯示部 9631a、9631b。由此可以提高平板終端的顯示品質。

在顯示部 9631a 中，可以將其一部分用作觸控式螢幕的區域 9632a，並且可以藉由按觸所顯示的操作鍵 9638

來輸入資料。此外，作為一個例子在此示出：顯示部 9631a 的一半只具有顯示的功能，並且另一半具有觸控式螢幕的功能，但是不侷限於該結構。也可以採用顯示部 9631a 的全部區域具有觸控式螢幕的功能的結構。例如，可以使顯示部 9631a 的整個面顯示鍵盤按鈕來將其用作觸控式螢幕，並且將顯示部 9631b 用作顯示幕面。

此外，顯示部 9631b 也與顯示部 9631a 同樣，可以將其一部分用作觸控式螢幕的區域 9632b。此外，藉由使用手指或觸控筆等按觸觸控式螢幕的顯示鍵盤顯示切換按鈕 9639 的位置，可以在顯示部 9631b 顯示鍵盤按鈕。

此外，也可以對觸控式螢幕的區域 9632a 和觸控式螢幕的區域 9632b 同時進行按觸輸入。

另外，顯示模式切換開關 9034 能夠進行豎屏顯示和橫屏顯示等顯示的方向的切換以及黑白顯示或彩色顯示等的切換等。根據內置於平板終端中的光感測器所檢測的使用時的外光的光量，省電模式切換開關 9036 可以將顯示的亮度設定為最適合的亮度。平板終端除了光感測器以外還可以內置陀螺儀和加速度感測器等檢測傾斜度的感測器等的其他檢測裝置。

此外，圖 23A 示出顯示部 9631b 的顯示面積與顯示部 9631a 的顯示面積相同的例子，但是不侷限於此，一方的尺寸和另一方的尺寸可以不同，並且它們的顯示品質也可以不同。例如顯示部 9631a 和顯示部 9631b 中的一方可以進行比另一方更高精細的顯示。

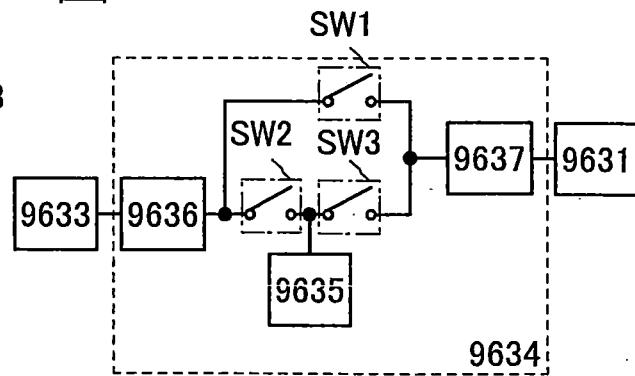

圖 23B 是合上的狀態，並且平板終端包括外殼 9630、太陽能電池 9633、充放電控制電路 9634。此外，在圖 23B 中，作為充放電控制電路 9634 的一個例子示出具有電池 9635 和 DCDC 轉換器 9636 的結構。

此外，平板終端可以折疊，因此不使用時可以合上外殼 9630。因此，可以保護顯示部 9631a 和顯示部 9631b，而可以提供一種具有良好的耐久性且從長期使用的觀點來看具有良好的可靠性的平板終端。

此外，圖 23A 和圖 23B 所示的平板終端還可以具有如下功能：顯示各種各樣的資訊（靜態影像、動態影像、文字影像等）；將日曆、日期或時刻等顯示在顯示部上；對顯示在顯示部上的資訊進行操作或編輯的觸摸輸入；藉由各種各樣的軟體（程式）控制處理等。

藉由利用安裝在平板終端的表面上的太陽能電池 9633，可以將電力供應到觸控式螢幕、顯示部或影像信號處理部等。注意，太陽能電池 9633 可以設置在外殼 9630 的一面或兩面，因此可以進行高效的電池 9635 的充電。另外，當作為電池 9635 使用鋰離子電池時，有可以實現小型化等的優點。

另外，參照圖 23C 所示的方塊圖對圖 23B 所示的充放電控制電路 9634 的結構和工作進行說明。圖 23C 示出太陽能電池 9633、電池 9635、DCDC 轉換器 9636、轉換器 9637、開關 SW1 至 SW3 以及顯示部 9631，電池 9635、DCDC 轉換器 9636、轉換器 9637、開關 SW1 至

SW3 對應於圖 23B 所示的充放電控制電路 9634。

首先，說明在利用外光使太陽能電池 9633 發電時的工作的例子。使用 DCDC 轉換器 9636 對太陽能電池 9633 所產生的電力進行升壓或降壓以使它成為用來對電池 9635 進行充電的電壓。並且，當利用來自太陽能電池的電力使顯示部 9631 工作時使開關 SW1 導通，並且，利用轉換器 9637 將其升壓或降壓到顯示部 9631 所需要的電壓。另外，當不進行顯示部 9631 中的顯示時，可以採用使 SW1 截止且使 SW2 導通來對電池 9635 進行充電的結構。

注意，作為發電單元的一個例子示出太陽能電池 9633，但是不侷限於此，也可以使用壓電元件 (piezoelectric element) 或熱電轉換元件 (珀耳帖元件 (Peltier element)) 等其他發電單元進行電池 9635 的充電。例如，也可以使用以無線 (不接觸) 的方式能夠收發電力來進行充電的無線電力傳輸模組或組合其他充電方法進行充電。

本實施方式所示的結構等可以與其他實施方式所示的結構適當地組合而實施。

### 實施例 1

在本實施例中，參照圖 24A 至圖 24D 及圖 25 說明氧化物半導體膜及多層膜的電阻。

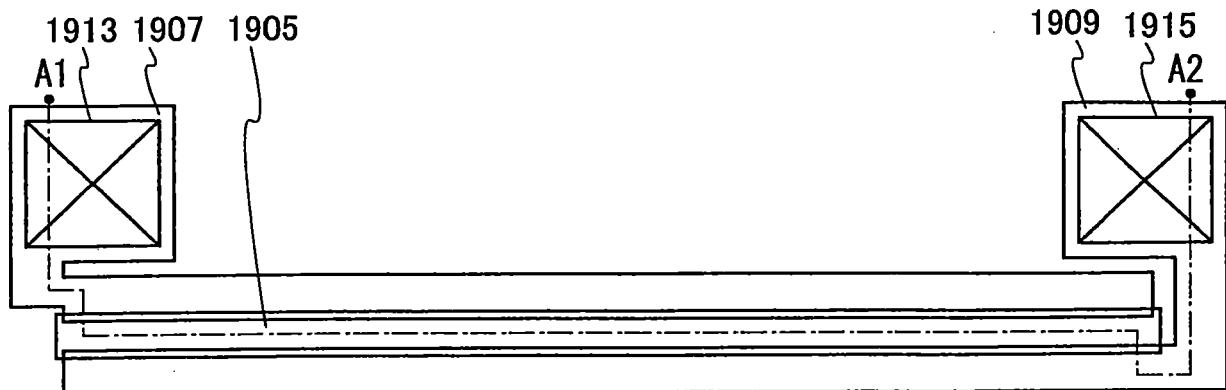

首先，參照圖 24A 至圖 24D 說明樣本的結構。

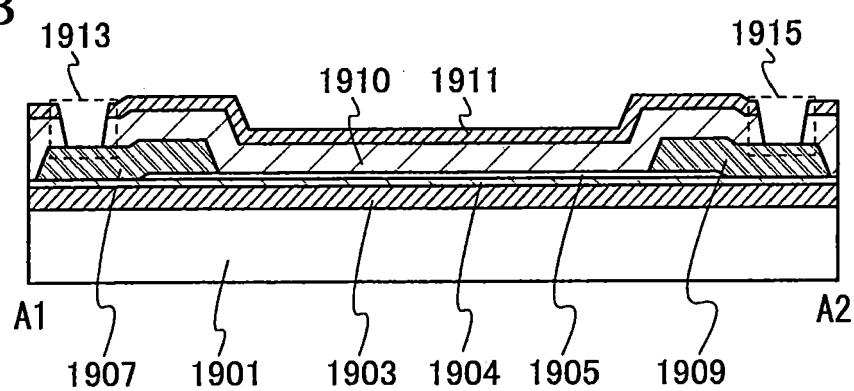

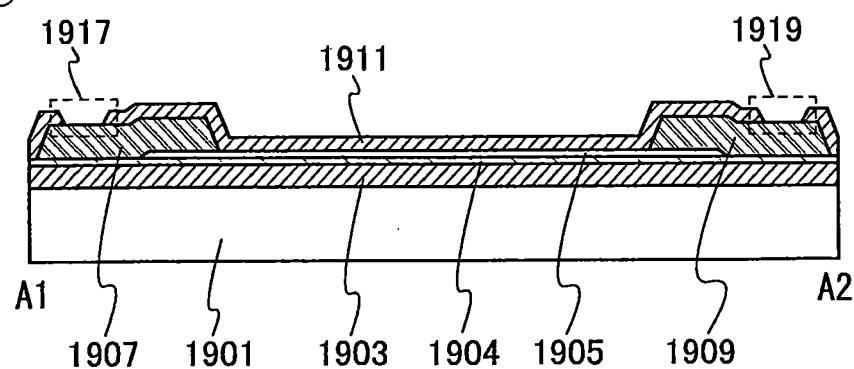

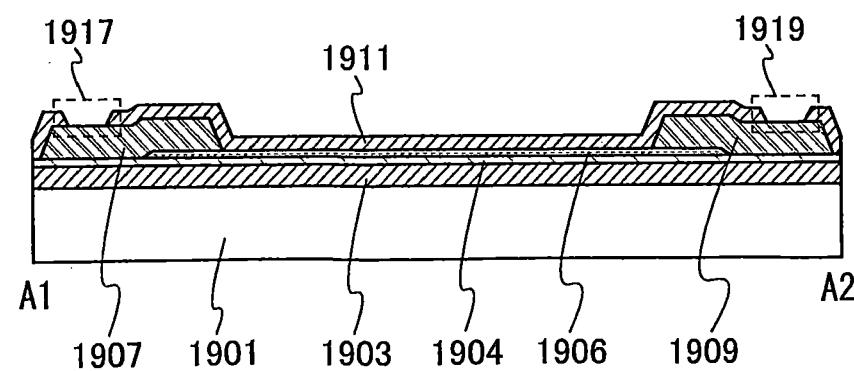

圖 24A 是樣本 1 至樣本 4 的俯視圖，圖 24B、圖 24C 及圖 24D 示出點劃線 A1-A2 的剖面圖。此外，由於樣本 1 至樣本 4 的俯視圖相同但剖面的疊層結構不同，所以剖面圖不同。圖 24B 示出樣本 1 的剖面圖，圖 24C 示出樣本 2 的剖面圖，圖 24D 示出樣本 3 及樣本 4 的剖面圖。

在樣本 1 中，在玻璃基板 1901 上形成絕緣膜 1903，在絕緣膜 1903 上形成絕緣膜 1904，在絕緣膜 1904 上形成氧化物半導體膜 1905。此外，由用作電極的導電膜 1907、1909 覆蓋氧化物半導體膜 1905 的兩端，由絕緣膜 1910、1911 覆蓋氧化物半導體膜 1905 及導電膜 1907、1909。另外，在絕緣膜 1910、1911 中設置有開口部 1913、1915，在該開口部露出導電膜 1907、1909。

在樣本 2 中，在玻璃基板 1901 上形成絕緣膜 1903，在絕緣膜 1903 上形成絕緣膜 1904，在絕緣膜 1904 上形成氧化物半導體膜 1905。此外，由用作電極的導電膜 1907、1909 覆蓋氧化物半導體膜 1905 的兩端，由絕緣膜 1911 覆蓋氧化物半導體膜 1905 及導電膜 1907、1909。另外，在絕緣膜 1911 中設置有開口部 1917、1919，在該開口部露出導電膜 1907、1909。

在樣本 3 及樣本 4 中，在玻璃基板 1901 上形成絕緣膜 1903，在絕緣膜 1903 上形成絕緣膜 1904，在絕緣膜 1904 上形成多層膜 1906。此外，由用作電極的導電膜 1907、1909 覆蓋多層膜 1906 的兩端，由絕緣膜 1911 覆蓋多層膜 1906 及導電膜 1907、1909。另外，在絕緣膜

1911 中設置有開口部 1917、1919，在該開口部露出導電膜 1907、1909。

像這樣，樣本 1 至樣本 4 的不同之處是接觸於氧化物半導體膜 1905 或多層膜 1906 上的絕緣膜的結構。在樣本 1 中，氧化物半導體膜 1905 與絕緣膜 1910 接觸，在樣本 2 中，氧化物半導體膜 1905 與絕緣膜 1911 接觸，在樣本 3 及樣本 4 中，多層膜 1906 與絕緣膜 1911 接觸。

接著，說明各樣本的製造方法。

首先，說明樣本 1 的製造方法。

作為絕緣膜 1903，藉由電漿 CVD 法在玻璃基板 1901 上形成厚度為 400nm 的氮化矽膜。

接著，作為絕緣膜 1904，藉由電漿 CVD 法在絕緣膜 1903 上形成厚度為 50nm 的氧氮化矽膜。

接著，作為氧化物半導體膜 1905，藉由濺射法使用金屬氧化物靶材 (In : Ga : Zn=1 : 1 : 1) 在絕緣膜 1904 上形成厚度為 35nm 的 IGZO 膜。然後，使用藉由光微影製程形成的遮罩進行蝕刻處理來形成氧化物半導體膜 1905。

接著，藉由濺射法在絕緣膜 1903 及氧化物半導體膜 1905 上依次層疊厚度為 50nm 的鎢膜、厚度為 400nm 的鋁膜及厚度為 100nm 的鈦膜，然後使用藉由光微影製程形成的遮罩進行蝕刻處理，來形成導電膜 1907 及導電膜 1909。

接著，作為絕緣膜 1910，藉由電漿 CVD 法在絕緣膜

1904、氧化物半導體膜 1905、導電膜 1907 及導電膜 1909 上形成厚度為 450nm 的氮化矽膜，然後在氮及氧的混合氛圍下以 350°C 進行 1 小時的加熱處理。

接著，作為絕緣膜 1911，藉由電漿 CVD 法在絕緣膜 1910 上形成厚度為 50nm 的氮化矽膜。

接著，在絕緣膜 1911 上設置藉由光微影製程形成的遮罩，然後進行蝕刻處理，來形成絕緣膜 1910、絕緣膜 1911 中的開口部 1913、1915。

藉由上述製程製造樣本 1。

接著，說明樣本 2 的製造方法。

作為絕緣膜 1910，藉由電漿 CVD 法在樣本 1 的絕緣膜 1903、氧化物半導體膜 1905、導電膜 1907 及導電膜 1909 上形成厚度為 450nm 的氮化矽膜，然後在氮及氧的混合氛圍下以 350°C 進行 1 小時的加熱處理。然後去除絕緣膜 1910。

接著，作為絕緣膜 1911，藉由電漿 CVD 法在絕緣膜 1904、氧化物半導體膜 1905、導電膜 1907 及導電膜 1909 上形成厚度為 50nm 的氮化矽膜。

接著，在絕緣膜 1911 上設置藉由光微影製程形成的遮罩，然後進行蝕刻處理，來在絕緣膜 1911 中形成開口部 1917、1919。

藉由上述製程製造樣本 2。

接著，說明樣本 3 的製造方法。

樣本 3 使用多層膜 1906 代替樣本 2 的氧化物半導體

膜 1905。作為多層膜 1906，在絕緣膜 1904 上使用金屬氧化物靶材 (In : Ga : Zn=1 : 3 : 2) 藉由濺射法形成厚度為 10nm 的 IGZO 膜，接著使用金屬氧化物靶材 (In : Ga : Zn=1 : 1 : 1) 藉由濺射法形成厚度為 10nm 的 IGZO 膜，使用金屬氧化物靶材 (In : Ga : Zn=1 : 3 : 2) 藉由濺射法形成厚度為 10nm 的 IGZO 膜。然後，使用藉由光微影製程形成的遮罩進行蝕刻處理，來形成多層膜 1906。

藉由上述製程製造樣本 3。

接著，說明樣本 4 的製造方法。

樣本 4 使用多層膜 1906 代替樣本 2 的氧化物半導體膜 1905。此外，對樣本 4 與樣本 3 進行比較時構成多層膜 1906 的 IGZO 膜的厚度彼此不同。作為多層膜 1906，在絕緣膜 1904 上使用金屬氧化物靶材 (In : Ga : Zn=1 : 3 : 2) 藉由濺射法形成厚度為 20nm 的 IGZO 膜，接著使用金屬氧化物靶材 (In : Ga : Zn=1 : 1 : 1) 藉由濺射法形成厚度為 15nm 的 IGZO 膜，使用金屬氧化物靶材 (In : Ga : Zn=1 : 3 : 2) 藉由濺射法形成厚度為 10nm 的 IGZO 膜。然後，使用藉由光微影製程形成的遮罩進行蝕刻處理，來形成多層膜 1906。

藉由上述製程製造樣本 4。

接著，對設置在樣本 1 至樣本 4 中的氧化物半導體膜 1905 及多層膜 1906 的薄層電阻進行測量。在樣本 1 中，將探針接觸於開口部 1913 及開口部 1915，對氧化物半導體膜 1905 的薄層電阻進行測量。此外，在樣本 2 至樣本

4 中，將探針接觸於開口部 1917 及開口部 1919，對氧化物半導體膜 1905 及多層膜 1906 的薄層電阻進行測量。此外，在樣本 1 至樣本 4 的氧化物半導體膜 1905 及多層膜 1906 中，導電膜 1907 與導電膜 1909 對置的寬度為 1mm，導電膜 1907 與導電膜 1909 之間的距離為  $10\mu\text{m}$ 。此外，在樣本 1 至樣本 4 中，導電膜 1907 為接地電位，對導電膜 1909 施加 1V。

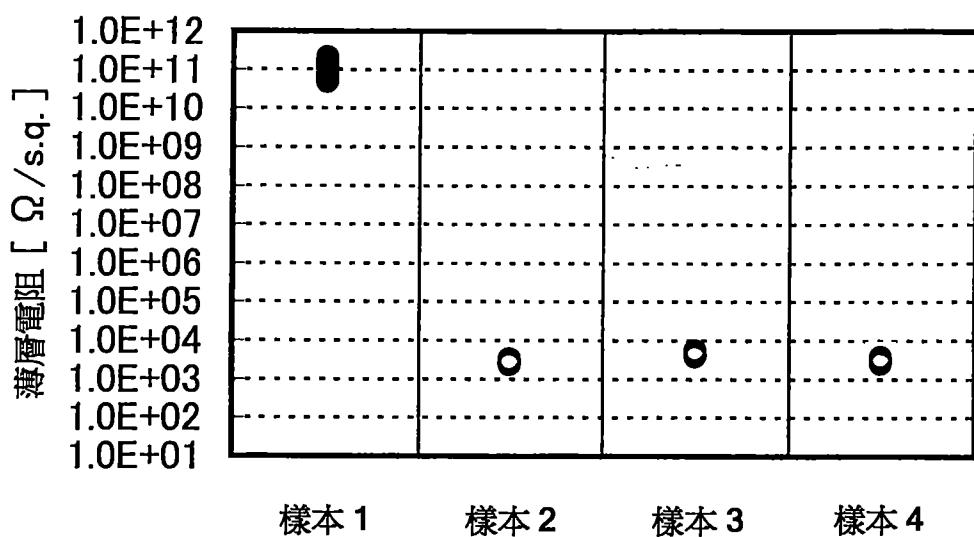

圖 25 示出樣本 1 至樣本 4 的薄層電阻。

樣本 1 的薄層電阻大約為  $1 \times 10^{11}\Omega/\text{s.q.}$ 。樣本 2 的薄層電阻為  $2620\Omega/\text{s.q.}$ 。樣本 3 的薄層電阻為  $4410\Omega/\text{s.q.}$ 。另外，樣本 4 的薄層電阻為  $2930\Omega/\text{s.q.}$ 。

像這樣，接觸於氧化物半導體膜 1905 及多層膜 1906 的絕緣膜的不同，氧化物半導體膜 1905 及多層膜 1906 的薄層電阻不同。

另外，當將上述樣本 1 至樣本 4 的薄層電阻換算為電阻率時，樣本 1 為  $3.9 \times 10^5\Omega\text{cm}$ ，樣本 2 為  $9.3 \times 10^{-3}\Omega\text{cm}$ ，樣本 3 為  $1.3 \times 10^{-2}\Omega\text{cm}$ ，樣本 4 為  $1.3 \times 10^{-2}\Omega\text{cm}$ 。

在樣本 1 中，在氧化物半導體膜 1905 上且與其接觸地形成有用於絕緣膜 1910 的氮化矽膜，與用於絕緣膜 1911 的氮化矽膜離開地形成。另一方面，在樣本 2 至樣本 4 中，在氧化物半導體膜 1905 及多層膜 1906 上且與其接觸地形成有用於絕緣膜 1911 的氮化矽膜。像這樣，藉由氧化物半導體膜 1905 及多層膜 1906 與用於絕緣膜 1911 的氮化矽膜接觸地設置，在氧化物半導體膜 1905 及

多層膜 1906 中形成缺陷，典型地形成氧缺陷，並且包含在該氮化矽膜中的氫移動或擴散到氧化物半導體膜 1905 及多層膜 1906。其結果是提高氧化物半導體膜 1905 及多層膜 1906 的導電性。

例如，當作為電晶體的通道形成區使用氧化物半導體膜時，如樣本 1 所示與氧化物半導體膜接觸地設置氮化矽膜較佳。此外，作為用於電容元件的電極的具有透光性的導電膜，如樣本 2 至樣本 4 所示，較佳的是與氧化物半導體膜或多層膜接觸地設置氮化矽膜。藉由使用這種結構，即使在同一製程中形成用於電晶體的通道形成區的氧化物半導體膜或多層膜以及用於電容元件的電極的氧化物半導體膜或多層膜，也可以改變氧化物半導體膜及多層膜的電阻率。

接著，在樣本 2 及樣本 3 中，對保存在高溫度且高濕度的環境下的樣本的薄層電阻值進行測量。以下說明這裡所使用的各樣本的條件。此外，這裡，在一部分的條件中，使用與樣本 2 及樣本 3 不同的條件。由此，將樣本 2 與樣本 3 的結構相同但製造條件不同的樣本分別稱為樣本 2a 及樣本 3a。

首先，說明樣本 2a 的製造方法。

在玻璃基板 1901 上形成絕緣膜 1903 及絕緣膜 1904。

作為氧化物半導體膜 1905，藉由濺射法使用金屬氧化物靶材 (In : Ga : Zn = 1 : 1 : 1) 在絕緣膜 1904 上形成

厚度爲 35nm 的 IGZO 膜。然後，在使用藉由光微影製程形成的遮罩進行蝕刻處理之後，以 350°C 或 450°C 進行加熱處理，來形成氧化物半導體膜 1905。

藉由濺射法在絕緣膜 1903 及氧化物半導體膜 1905 上依次層疊厚度爲 50nm 的鈦膜及厚度爲 400nm 的銅膜，然後使用藉由光微影製程形成的遮罩進行蝕刻處理，來形成導電膜 1907 及導電膜 1909。

接著，作爲絕緣膜 1910，藉由電漿 CVD 法在絕緣膜 1904、氧化物半導體膜 1905、導電膜 1907 及導電膜 1909 上形成厚度爲 450nm 的氮化矽膜，然後在氮及氧的混合氛圍下以 350°C 進行 1 小時的加熱處理。

接著，作爲絕緣膜 1911，藉由電漿 CVD 法在絕緣膜 1904、氧化物半導體膜 1905、導電膜 1907 及導電膜 1909 上形成厚度爲 50nm 的氮化矽膜。此外，將氮化矽膜的成膜溫度設定爲 220°C 或 350°C。

接著，在絕緣膜 1911 上設置藉由光微影製程形成的遮罩，然後進行蝕刻處理，來在絕緣膜 1910 及絕緣膜 1911 中形成開口部 1913、1915。

藉由上述製程製造樣本 2a。

接著，說明樣本 3a 的製造方法。

在樣本 3a 中使用多層膜 1906 代替樣本 2a 的氧化物半導體膜 1905。作爲多層膜 1906，在絕緣膜 1904 上使用金屬氧化物靶材 (In : Ga : Zn=1 : 1 : 1) 藉由濺射法形成厚度爲 10nm 的 IGZO 膜，接著使用金屬氧化物靶材

(In : Ga : Zn=1 : 3 : 2) 藉由濺射法形成厚度為 10nm 的 IGZO 膜。然後，在使用藉由光微影製程形成的遮罩進行蝕刻處理之後，以 350°C 或 450°C 進行加熱處理，來形成多層膜 1906。

藉由上述製程製造樣本 3a。

接著，對設置在樣本 2a 及樣本 3a 中的氧化物半導體膜 1905 及多層膜 1906 的薄層電阻進行測量。在樣本 2a 及樣本 3a 中，將探針接觸於開口部 1917 及開口部 1919，測量氧化物半導體膜 1905 及多層膜 1906 的薄層電阻。此外，在樣本 2a 及樣本 3a 的氧化物半導體膜 1905 及多層膜 1906 中，導電膜 1907 與導電膜 1909 對置的寬度為 1.5mm，導電膜 1907 與導電膜 1909 之間的距離為 10μm。此外，在樣本 2a 及樣本 3a 中，導電膜 1907 為接地電位，對導電膜 1909 施加 1V。此外，在溫度為 60°C 且濕度為 95% 的氛圍下，在保存樣本 2a 及樣本 3a 60 個小時及 130 個小時之後，測量各樣本的薄層電阻值。

圖 29 示出樣本 2a 及樣本 3a 的薄層電阻值。此外，在圖 29 中，實線示出在各樣本中作為絕緣膜 1910 形成的氮化矽膜的成膜溫度為 220°C，虛線示出成膜溫度為 350°C。另外，黑標記示出在各樣本中在形成氧化物半導體膜 1905 或多層膜 1906 之後以 350°C 進行加熱處理，白標記示出在形成氧化物半導體膜 1905 或多層膜 1906 之後以 450°C 進行加熱處理。圓形標記示出各樣本具有氧化物半導體膜 1905，即樣本 2a。三角標記示出各樣本具有多層

膜 1906，即樣本 3a。此外，在圖 29 中不示出在形成多層膜 1906 之後以 350°C 進行加熱的樣本 3a 的測量結果，即黑三角標記。

從圖 29 可知樣本 2a 及樣本 3a 的薄層電阻值低，作為電容元件的電極滿足較佳的薄層電阻值，即  $0.2\Omega/\text{s.q.}$  以下。此外，可知樣本 2a 及樣本 3a 的薄層電阻值的時間變動量少。如上所述，由於在高溫度且高濕度的環境下接觸於氮化矽膜的氧化物半導體膜或多層膜的薄層電阻值的變動量少，所以可以用於用作電容元件的電極的具有透光性的導電膜。

接著，圖 30 示出在樣本 2a 及樣本 3a 中將基板溫度設定為 25°C、60°C 及 150°C，測量各個薄層電阻值的結果。此外，這裡，作為樣本 2a 及樣本 3a 使用如下方法形成的樣本，作為絕緣膜 1910 形成的氮化矽膜的成膜溫度為 220°C，在形成氧化物半導體膜 1905 或多層膜 1906 之後，以 350°C 進行加熱處理。黑圓形標記示出樣本 2a 的測量結果，黑三角標記示出樣本 3a 的測量結果。

從圖 30 可知，即使使基板溫度升高氧化物半導體膜 1905 及多層膜 1906 的薄層電阻值也不變動。即，接觸於氮化矽膜的氧化物半導體膜或多層膜也可以稱為簡並半導體。由於接觸於氮化矽膜的氧化物半導體膜或多層膜即使基板溫度變化薄層電阻值的變動也少，所以可以用於用作電容元件的電極的具有透光性的導電膜。

本實施例所示的結構可以與其他實施方式或實施例所

示的結構適當地組合而實施。

## 實施例 2

在本實施例中，參照圖 26A 及圖 26B 說明氧化物半導體膜及形成在氧化物半導體膜上的絕緣膜的雜質分析。

在本實施例中，作為用於雜質分析的樣本，製造兩種樣本（以下稱為樣本 5 及樣本 6）。

首先，以下示出樣本 5 的製造方法。

在樣本 5 中，在玻璃基板上形成 IGZO 膜，然後形成氮化矽膜。然後，在氮氛圍下以  $450^{\circ}\text{C}$  進行 1 個小時的熱處理，接著在氮及氧的混合氣體氛圍（氮 = 80%，氧 = 20%）下以  $450^{\circ}\text{C}$  進行 1 個小時的熱處理。

此外，作為 IGZO 膜的成膜條件採用如下條件來形成厚度為  $100\text{nm}$  的 IGZO 膜：藉由濺射法使用金屬氧化物靶材（In : Ga : Zn = 1 : 1 : 1）； $\text{Ar}/\text{O}_2 = 100/100\text{sccm}$  ( $\text{O}_2 = 50\%$ )；壓力 =  $0.6\text{Pa}$ ；成膜功率 =  $5000\text{W}$ ；基板溫度 =  $170^{\circ}\text{C}$ 。

此外，作為氮化矽膜的成膜條件藉由電漿 CVD 法採用如下條件來形成厚度為  $100\text{nm}$  的氮化矽膜： $\text{SiH}_4/\text{N}_2/\text{NH}_3 = 50/5000/100\text{sccm}$ ；壓力 =  $100\text{Pa}$ ；成膜功率 =  $1000\text{W}$ ；基板溫度 =  $220^{\circ}\text{C}$ 。

下面，以下示出樣本 6 的製造方法。

在玻璃基板上形成 IGZO 膜，然後層疊形成氧氮化矽膜及氮化矽膜。然後，在氮氛圍下以  $450^{\circ}\text{C}$  進行 1 個小時

的熱處理，接著在氮及氧的混合氣體氛圍（氮=80%，氧=20%）下以450°C進行1個小時的熱處理。

此外，作為IGZO膜的成膜條件及氮化矽膜的成膜條件使用與樣本5相同的條件。此外，作為氧氮化矽膜的成膜條件藉由電漿CVD法採用如下條件來形成厚度為50nm的氧氮化矽膜： $\text{SiH}_4/\text{N}_2\text{O}=30/4000\text{sccm}$ ；壓力=40Pa；成膜功率=150W；基板溫度=220°C，然後藉由電漿CVD法採用如下條件來形成厚度為400nm的氧氮化矽膜： $\text{SiH}_4/\text{N}_2\text{O}=160/4000\text{sccm}$ ；壓力=200Pa；成膜功率=1500W；基板溫度=220°C。

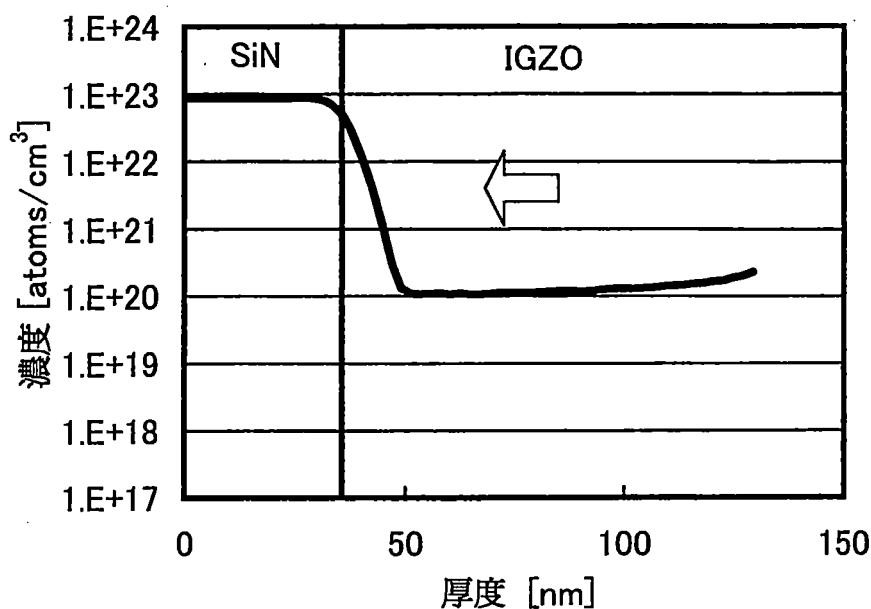

圖26A及圖26B示出樣本5及樣本6的雜質分析結果。

另外，作為雜質分析，使用二次離子質譜分析法(SIMS: Secondary Ion Mass Spectrometry)，從圖26A及圖26B所示的箭頭的方向進行分析。即，從玻璃基板一側進行測量。

此外，圖26A是藉由樣本5的測量獲得的氫(H)的濃度分佈。圖26B是藉由樣本6的測量獲得的氫(H)的濃度分佈。

從圖26A可知IGZO膜中的氫(H)濃度為 $1.0 \times 10^{20}\text{atoms}/\text{cm}^3$ 。此外，可知氮化矽膜中的氫(H)濃度為 $1.0 \times 10^{23}\text{atoms}/\text{cm}^3$ 。另外，從圖26B可知IGZO膜中的氫(H)濃度為 $5.0 \times 10^{19}\text{atoms}/\text{cm}^3$ 。此外，可知氧氮化矽膜中的氫(H)濃度為 $3.0 \times 10^{21}\text{atoms}/\text{cm}^3$ 。

另外，已知：在 SIMS 分析中，由於其測量原理而難以獲得樣本表面附近或與材質不同的膜之間的疊層介面附近的準確資料。因此，當使用 SIMS 來分析膜中的厚度方向上的氫（H）的分佈時，採用在目標的膜所存在的範圍中沒有值的極端變動且可以獲得大致恆定的強度的區域中的平均值。

像這樣，藉由改變接觸於 IGZO 膜的絕緣膜的結構，可確認到 IGZO 膜中的氫（H）濃度的差異。

例如，當作為電晶體的通道形成區使用上述 IGZO 膜時，如樣本 6 所示與 IGZO 膜接觸地設置氧化矽膜較佳。此外，作為用於電容元件的電極的具有透光性的導電膜，如樣本 5 所示，與 IGZO 膜接觸地設置氮化矽膜較佳。藉由使用這種結構，即使在同一製程中形成用於電晶體的通道形成區的 IGZO 膜以及用於電容元件的電極的 IGZO 膜，也可以改變 IGZO 膜中的氫濃度。

### 實施例 3

在本實施例中，參照圖 27A 至圖 27C 及圖 28 說明氧化物半導體膜及多層膜的缺陷量。

首先，說明樣本的結構。

樣本 7 包括形成在石英基板上的厚度為 35nm 的氧化物半導體膜及形成在氧化物半導體膜上的厚度為 100nm 的氮化絕緣膜。

樣本 8 及樣本 9 包括形成在石英基板上的厚度為

30nm 的多層膜及形成在多層膜上的厚度為 100nm 的氮化絕緣膜。此外，樣本 8 的多層膜依次層疊有厚度為 10nm 的第一 IGZO 膜、厚度為 10nm 的第二 IGZO 膜及厚度為 10nm 的第三 IGZO 膜。此外，樣本 9 依次層疊有厚度為 20nm 的第一 IGZO 膜、厚度為 15nm 的第二 IGZO 膜及厚度為 10nm 的第三 IGZO 膜。樣本 8 及樣本 9 與樣本 7 的不同之處在於包括多層膜代替氧化物半導體膜。

樣本 10 包括形成在石英基板上的厚度為 100nm 的氧化物半導體膜、形成在氧化物半導體膜上的厚度為 250nm 的氧化絕緣膜及形成在氧化絕緣膜上的厚度為 100nm 的氮化絕緣膜。樣本 10 與樣本 7 至樣本 9 的不同之處在於氧化物半導體膜不接觸於氮化絕緣膜而接觸於氧化絕緣膜。

下面，說明各樣本的製造方法。

首先，說明樣本 7 的製造方法。

作為氧化物半導體膜，在石英基板上形成厚度為 35nm 的 IGZO 膜。作為 IGZO 膜的成膜條件藉由濺射法採用如下條件：金屬氧化物靶材 (In : Ga : Zn=1 : 1 : 1) ；  $Ar/O_2=100\text{sccm}/100\text{sccm}$  (O<sub>2</sub>=50%) ；壓力=0.6Pa；成膜功率=5000W；基板溫度=170°C。

接著，作為第一加熱處理在氮氛圍下以 450°C 進行 1 個小時的加熱處理，然後在氮及氧的混合氣體氛圍 (氮=80%，氧=20%) 以 450°C 進行 1 個小時的加熱處理。

接著，在氧化物半導體膜上作為氮化絕緣膜形成厚度

爲 100nm 的氮化矽膜。作爲氮化矽膜的成膜條件，藉由電漿 CVD 法採用如下條件： $\text{SiH}_4/\text{N}_2/\text{NH}_3=50/5000/100\text{sccm}$ ；壓力 = 100Pa；成膜功率 = 1000W；基板溫度 = 350 °C。

接著，作爲第二加熱處理在氮氣圍下以 250°C 進行 1 小時的加熱處理。

藉由上述製程製造樣本 7。

下面，說明樣本 8 的製造方法。

在樣本 8 中形成多層膜代替樣本 7 的氧化物半導體膜。作爲多層膜，藉由濺射法在石英基板上採用如下條件來形成厚度爲 10nm 的第一 IGZO 膜：使用金屬氧化物靶材 (In : Ga : Zn = 1 : 3 : 2)； $\text{Ar}/\text{O}_2=180/20\text{sccm}$  ( $\text{O}_2=10\%$ )；壓力 = 0.6Pa；成膜功率 = 5000W；基板溫度 = 25 °C。接著，藉由濺射法採用如下條件來形成厚度爲 10nm 的第二 IGZO 膜：使用金屬氧化物靶材 (In : Ga : Zn = 1 : 1 : 1)； $\text{Ar}/\text{O}_2=100/100\text{sccm}$  ( $\text{O}_2=50\%$ )；壓力 = 0.6Pa；成膜功率 = 5000W；基板溫度 = 170 °C。接著，藉由濺射法採用如下條件來形成厚度爲 10nm 的第三 IGZO 膜：使用金屬氧化物靶材 (In : Ga : Zn = 1 : 3 : 2)； $\text{Ar}/\text{O}_2=180/20\text{sccm}$  ( $\text{O}_2=10\%$ )；壓力 = 0.6Pa；成膜功率 = 5000W；基板溫度 = 25 °C。

其他製程與樣本 7 相同。藉由上述製程形成樣本 8。

下面，說明樣本 9 的製造方法。

在樣本 9 中形成多層膜代替樣本 7 的氧化物半導體

膜。作為多層膜，在石英基板上使用與樣本 8 所示的第一 IGZO 膜相同的條件形成厚度為 20nm 的第一 IGZO 膜。接著，藉由濺射法使用與樣本 8 所示的第二 IGZO 膜相同的條件形成厚度為 15nm 的第二 IGZO 膜。接著，使用樣本 8 所示的第三 IGZO 膜相同的條件形成厚度為 10nm 的第二 IGZO 膜。

其他製程與樣本 7 相同。藉由上述製程形成樣本 9。

下面，說明樣本 10 的製造方法。

樣本 10 使用與樣本 7 相同的條件在石英基板上形成厚度為 100nm 的氧化物半導體膜。

接著，使用與樣本 7 相同的條件進行第一加熱處理。

接著，在氧化物半導體膜上作為氧化絕緣膜形成厚度為 50nm 的第一氮化矽膜及厚度為 200nm 的第二氮化矽膜。這裡，藉由電漿 CVD 法採用如下條件來形成厚度為 50nm 的第一氮化矽膜： $\text{SiH}_4/\text{N}_2\text{O}=30/4000\text{sccm}$ ；壓力 = 40Pa；成膜功率 = 150W；基板溫度 = 220°C，然後藉由電漿 CVD 法採用如下條件來形成厚度為 200nm 的第二氮化矽膜： $\text{SiH}_4/\text{N}_2\text{O}=160/4000\text{sccm}$ ；壓力 = 200Pa；成膜功率 = 1500W；基板溫度 = 220°C。另外，第二氮化矽膜是包含比滿足化學計量組成的氧多的氧的膜。

接著，使用與樣本 7 相同的條件在氧化絕緣膜上形成厚度為 100nm 的氮化矽膜。

接著，使用與樣本 7 相同的條件進行第二加熱處理。

藉由上述製程形成樣本 10。

下面，對樣本 7 至樣本 10 進行 ESR 測量。藉由 ESR 測量，可以在規定的溫度下，從產生微波的吸收的磁場的值 ( $H_0$ ) 用算式  $g=h\nu/\beta H_0$  來算出參數  $g$  值。注意， $\nu$  是微波的頻率。 $h$  是普朗克常數， $\beta$  是玻爾磁子 (Bohr magneton)，都是常數。

在此，以下述條件進行 ESR 測量。將測量溫度設定為室溫 (25°C)，將 8.92GHz 的高頻功率 (微波功率) 設定為 20mW，並且將磁場的方向設定為與所製造的樣本的膜表面平行的方向。

圖 27A 至圖 27C 示出藉由對樣本 7 至樣本 9 所包括的氧化物半導體膜及多層膜進行 ESR 測量而得到的一次微分曲線。圖 27A 示出樣本 7 的測量結果，圖 27B 示出樣本 8 的測量結果，圖 27C 示出樣本 9 的測量結果。

圖 28 示出藉由對樣本 10 所包括的氧化物半導體膜進行 ESR 測量而得到的一次微分曲線。

在圖 27A 至圖 27C 中，當樣本 7 的  $g$  值為 1.93 時檢測出起因於氧化物半導體膜中的缺陷的具有對稱性的信號。當樣本 8 及樣本 9 的  $g$  值為 1.95 時檢測出起因於多層膜中的缺陷的具有對稱性的信號。樣本 7 的  $g$  值為 1.93 時的自旋密度為  $2.5 \times 10^{19} \text{ spins/cm}^3$ ，樣本 8 的  $g$  值為 1.93 及 1.95 時的自旋密度的總和為  $1.6 \times 10^{19} \text{ spins/cm}^3$ ，樣本 9 的  $g$  值為 1.93 及 1.95 時的自旋密度的總和為  $2.3 \times 10^{19} \text{ spins/cm}^3$ 。即，可知氧化物半導體膜及多層膜包括缺陷。此外，作為氧化物半導體膜及多層膜的缺陷的一個例子有

氧缺陷。

在圖 28 中，樣本 10 與樣本 7 的氧化物半導體膜、樣本 8 及樣本 9 的多層膜相比，即使氧化物半導體膜的厚度厚，也沒有檢測出起因於缺陷的具有對稱性的信號，換言之，檢測下限以下（在此，檢測下限為  $3.7 \times 10^{16}$  spins/cm<sup>3</sup>）。由此，不能檢測出氧化物半導體膜所包括的缺陷量。

當氧化物半導體膜或多層膜接觸於氮化絕緣膜、這裡是藉由電漿 CVD 法形成的氮化矽膜時，在氧化物半導體膜或多層膜中形成缺陷，典型地形成氧缺陷。另一方面，當在氧化物半導體膜中設置氧化絕緣膜、這裡是設置氧氮化矽膜時，包含在氧氮化矽膜中的過剩氧，即包含比滿足化學計量組成的氧多的氧擴散到氧化物半導體膜，由此不增加氧化物半導體膜中的缺陷。

如上所述，如樣本 7 至樣本 9 所示，接觸於氮化絕緣膜的氧化物半導體膜或多層膜的缺陷多，典型的是氧缺陷多，而導電性高，所以可以用作電容元件的電極。另一方面，如樣本 10 所示，接觸於氧化絕緣膜的氧化物半導體膜或多層膜的氧缺陷量少，而導電性低，所以可以用作電晶體的通道形成區。

這裡，以下說明接觸於氮化物絕緣膜的氧化物半導體膜及多層膜的電阻率降低的原因。

〈H 的存在形態間的能量及穩定性〉

首先，說明存在於氧化物半導體膜中的 H 的形態的能量差及穩定性的計算結果。這裡，作為氧化物半導體膜使用  $\text{InGaZnO}_4$ 。

在用於計算的結構中，以  $\text{InGaZnO}_4$  的六方晶的單位晶格在 a 軸及 b 軸方向上放大至兩倍的 84 原子塊體模型為基礎。

作為塊體模型，準備將與三個 In 原子及一個 Zn 原子接合的一個 O 原子置換為 H 原子的模型（參照圖 31A）。此外，圖 31B 示出在圖 31A 中從 c 軸看  $\text{InO}$  層中的 ab 面時的圖。將去除與三個 In 原子及一個 Zn 原子接合的一個 O 原子的區域稱為氧缺陷  $\text{V}_\text{O}$ ，在圖 31A 及圖 31B 中用虛線示出氧缺陷  $\text{V}_\text{O}$ 。此外，將位於氧缺陷  $\text{V}_\text{O}$  中的 H 原子表示為  $\text{V}_\text{O}^\text{H}$ 。

此外，在塊體模型中，去除與三個 In 原子及一個 Zn 原子接合的一個 O 原子，形成氧缺陷（ $\text{V}_\text{O}$ ）。準備在該  $\text{V}_\text{O}$  附近對於 ab 面與一個 Ga 原子及兩個 Zn 原子接合的 O 原子接合於 H 原子的模型（參照圖 31C）。此外，圖 31D 示出在圖 31C 中從 c 軸看  $\text{InO}$  層中的 ab 面的圖。在圖 31C 及圖 31D 中，以虛線示出氧缺陷  $\text{V}_\text{O}$ 。另外，將包括氧缺陷  $\text{V}_\text{O}$  且包括在氧缺陷  $\text{V}_\text{O}$  附近對於 ab 面與一個 Ga 原子及兩個 Zn 原子接合的 O 原子接合於 H 原子的模型表示為  $\text{V}_\text{O}^\text{H}$ 。

對上述兩個模型在固定晶格常數的情況下進行最優化計算來算出總能量。注意，可說總能量值越小，其結構越

穩定。

在計算中使用第一原理計算軟體 VASP (The Vienna Ab initio simulation package)。表 1 示出計算條件。

[表 1]

|      |         |

|------|---------|

| 軟體   | VASP    |

| 殼勢   | PAW     |

| 泛函   | GGA/PBE |

| 截止能量 | 500 eV  |

| K 點  | 4×4×1   |

作為電子狀態殼勢使用利用 Projector Augmented Wave (PAW) 法生成的位勢，作為泛函使用 GGA/PBE (Generalized-Gradient-Approximation/Perdew-Burke-Ernzerhof)。

此外，表 2 示出藉由計算算出的兩個模型的總能量。

[表 2]

|      |             |

|------|-------------|

| 模型   | 總能量         |

| VoH  | -456.084 eV |

| Vo+H | -455.304 eV |

從表 2 可知 VoH 的總能量比 Vo+H 的總能量小 0.78 eV。因此，可說 VoH 與 Vo+H 相比穩定。由此，當 H 原子接近於氧缺陷 (Vo) 時，與接合於 O 原子相比，H 原子容易被引入到氧缺陷 (Vo) 中。

〈VoH 的熱力學狀態〉

下面，說明 H 原子被引入到氧缺陷 (Vo) 中的 VoH 的形成能量及帶電狀態的計算結果。VoH 根據帶電狀態的不同其形成能量不同，並且還依賴於費米能量。因此，VoH 依賴於費米能階而穩定的帶電狀態不同。這裡，VoH 釋放一個電子的狀態表示為  $(\text{VoH})^+$ ，俘獲一個電子的狀態表示為  $(\text{VoH})^-$ ，電子不移動的狀態表示為  $(\text{VoH})^0$ 。下面計算  $(\text{VoH})^+$ 、 $(\text{VoH})^-$ 、 $(\text{VoH})^0$  的形成能量。

在計算中使用第一原理計算軟體 VASP。表 3 示出計算條件。

[表 3]

|        |                                |

|--------|--------------------------------|

| 軟體     | VASP                           |

| 屢勢     | PAW                            |

| 泛函     | HSE06                          |

| 截止能量   | 800 eV                         |

| k 點取樣數 | $2 \times 2 \times 1$ (opt.)   |

|        | $4 \times 4 \times 1$ (single) |

| 自旋分極   | setup                          |

| 遮蔽參數   | 0.2                            |

| 交換項混合比 | 0.25                           |

| 原子數    | 84                             |

作為電子狀態屢勢計算使用利用 Projector Augmented Wave (PAW) 法生成的位勢，作為泛函使用 Heyd-Scuseria-Ernzerhof (HSE) DFT 混合泛函 (HSE06)。

另外，在計算氧缺陷的形成能量時假設氧缺陷濃度的稀薄極限，校正電子及電洞過剩地擴展到導帶、價電子

帶而算出能量。另外，以完全的結晶的價電子帶上端為能量原點，來源於缺陷結構的價電子帶的偏差用平均靜電位勢校正。

圖 32A 示出  $(\text{VoH})^+$ 、 $(\text{VoH})^-$ 、 $(\text{VoH})^0$  的形成能量。橫軸示出費米能階，縱軸示出形成能量。實線示出  $(\text{VoH})^+$  的形成能量，點劃線示出  $(\text{VoH})^0$  的形成能量，虛線示出  $(\text{VoH})^-$  的形成能量。此外， $\text{VoH}$  的電荷從  $(\text{VoH})^+$  經過  $(\text{VoH})^0$  變為  $(\text{VoH})^-$  的遷移能階表示為  $\varepsilon (+/-)$ 。

圖 32B 示出  $\text{VoH}$  的熱力學遷移能階。從計算結果可知  $\text{InGaZnO}_4$  的能隙為  $2.739\text{eV}$ 。此外，當價電子帶的能量為  $0\text{eV}$  時，遷移能階 ( $\varepsilon (+/-)$ ) 為  $2.62\text{eV}$ ，存在於導帶的正下方。由此可知，藉由  $\text{H}$  原子被引入到氧缺陷 ( $\text{Vo}$ ) 中， $\text{InGaZnO}_4$  成為  $n$  型。

當氧化物半導體膜暴露於電漿時，氧化物半導體膜受到損傷，而在氧化物半導體膜中生成缺陷，典型地生成氧缺陷。此外，當氧化物半導體膜接觸於氮化絕緣膜時，包含在氮化絕緣膜中的氫移動到氧化物半導體膜。其結果是，氫進入到包括在氧化物半導體膜中的氧缺陷，由此在氧化物半導體膜中形成  $\text{VoH}$ ，氧化物半導體膜成為  $n$  型，從而電阻率降低。如上所述，可以將接觸於氮化絕緣膜的氧化物半導體膜用作電容元件的電極。

### 【符號說明】

- 100 : 像素部

- 101 : 像素

- 102 : 基板

- 103 : 電晶體

- 104 : 掃描線驅動電路

- 105 : 電容元件

- 106 : 信號線驅動電路

- 107 : 掃描線

- 108 : 液晶元件

- 109 : 信號線

- 111 : 半導體膜

- 113 : 導電膜

- 115 : 電容線

- 117 : 開口

- 119 : 半導體膜

- 121 : 像素電極

- 123 : 開口

- 125 : 導電膜

- 126 : 絝緣膜

- 127 : 閘極絝緣膜

- 128 : 絝緣膜

- 129 : 絝緣膜

- 130 : 絝緣膜

- 131 : 絝緣膜

- 132 : 絶緣膜

- 133 : 絶緣膜

- 136 : 絶緣膜

- 137 : 絶緣膜

- 154 : 反電極

- 172 : 像素

- 174 : 電容元件

- 176 : 電容線

- 178 : 半導體膜

- 196 : 像素

- 197 : 電容元件

- 198 : 半導體膜

- 199 : 導電膜

- 199a : 氧化物半導體膜

- 199b : 氧化物半導體膜

- 199c : 氧化物半導體膜

- 201 : 像素

- 205 : 電容元件

- 219 : 半導體膜

- 221 : 像素電極

- 225 : 絶緣膜

- 226 : 絶緣膜

- 227 : 閘極絕緣膜

- 228 : 絶緣膜

229 : 絶緣膜

230 : 絶緣膜

231 : 絶緣膜

232 : 絶緣膜

233 : 絶緣膜

236 : 絶緣膜

237 : 絶緣膜

245 : 電容元件

301 : 像素

305 : 電容元件

315 : 電容線

319 : 半導體膜

401\_1 : 像素

401\_2 : 像素

403\_1 : 電晶體

403\_2 : 電晶體

405\_1 : 電容元件

405\_2 : 電容元件

407\_1 : 掃描線

407\_2 : 掃描線

409 : 信號線

411\_1 : 半導體膜

411\_2 : 半導體膜

413\_1 : 導電膜

- 413\_2 : 導電膜

415 : 電容線

417\_1 : 開口

417\_2 : 開口

419\_1 : 半導體膜

419\_2 : 半導體膜

421\_1 : 像素電極

421\_2 : 像素電極

423 : 開口

425 : 導電膜

437 : 掃描線

623 : 電晶體

627 : 閘極電極

629 : 源極電極

631 : 半導體膜

633 : 沖極電極

641 : 導電膜

901 : 基板

902 : 像素部

903 : 信號線驅動電路

904 : 掃描線驅動電路

905 : 密封材料

906 : 基板

908 : 液晶層

- 910 : 電晶體

- 911 : 電晶體

- 913 : 液晶元件

- 915 : 連接端子電極

- 916 : 端子電極