(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3645387号

(P3645387)

(45) 発行日 平成17年5月11日(2005.5.11)

(24) 登録日 平成17年2月10日(2005.2.10)

(51) Int.CI.<sup>7</sup>

F 1

|              |            |      |

|--------------|------------|------|

| H01L 29/786  | H01L 29/78 | 613A |

| H01L 21/20   | H01L 21/20 |      |

| H01L 21/336  | H01L 27/08 | 331E |

| H01L 21/8238 | H01L 29/78 | 627G |

| H01L 27/08   | H01L 27/08 | 321B |

請求項の数 8 (全 20 頁) 最終頁に続く

|           |                         |

|-----------|-------------------------|

| (21) 出願番号 | 特願平8-358953             |

| (22) 出願日  | 平成8年12月30日(1996.12.30)  |

| (65) 公開番号 | 特開平10-200112            |

| (43) 公開日  | 平成10年7月31日(1998.7.31)   |

| 審査請求日     | 平成15年12月25日(2003.12.25) |

|           |                     |

|-----------|---------------------|

| (73) 特許権者 | 000153878           |

|           | 株式会社半導体エネルギー研究所     |

|           | 神奈川県厚木市長谷398番地      |

| (72) 発明者  | 大谷 久                |

|           | 神奈川県厚木市長谷398番地 株式会社 |

|           | 半導体エネルギー研究所内        |

| (72) 発明者  | 小山 潤                |

|           | 神奈川県厚木市長谷398番地 株式会社 |

|           | 半導体エネルギー研究所内        |

| (72) 発明者  | 尾形 靖                |

|           | 神奈川県厚木市長谷398番地 株式会社 |

|           | 半導体エネルギー研究所内        |

| (72) 発明者  | 山崎 舜平               |

|           | 神奈川県厚木市長谷398番地 株式会社 |

|           | 半導体エネルギー研究所内        |

最終頁に続く

(54) 【発明の名称】半導体回路

## (57) 【特許請求の範囲】

## 【請求項 1】

Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを相補型に組み合わせた半導体回路であって、

各薄膜トランジスタを構成する活性層は、絶縁表面を有する基板上に形成された結晶性珪素膜を用いて構成されており、

前記活性層を構成する結晶性珪素膜は、結晶化を助長する金属元素の添加領域から前記基板に平行な方向に結晶成長した結晶構造を有し、

前記Pチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記添加領域の端部との距離をL<sub>1</sub>とし、前記Nチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記添加領域の端部との距離をL<sub>2</sub>とした場合、L<sub>1</sub> < L<sub>2</sub>であることを特徴とする半導体回路。

## 【請求項 2】

Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを有する第1のアナログスイッチと、

Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを有する第2のアナログスイッチとを有し、

各薄膜トランジスタを構成する活性層は、絶縁表面を有する基板上に形成された結晶性珪素膜を用いて構成されており、

前記活性層を構成する結晶性珪素膜は、結晶化を助長する金属元素の添加領域から前記基

10

20

板に平行な方向に結晶成長した結晶構造を有し、

前記第1のアナログスイッチおよび前記第2のアナログスイッチは2つの前記添加領域の間に位置し、

前記第1のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と当該Pチャネル型の薄膜トランジスタと最も近い添加領域の端部との距離と、前記第2のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と当該Pチャネル型の薄膜トランジスタと最も近い添加領域の端部との距離が等しく、

前記第1のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と当該Nチャネル型の薄膜トランジスタと最も近い添加領域の端部との距離と、前記第2のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と当該Nチャネル型の薄膜トランジスタと最も近い添加領域の端部との距離が等しいことを特徴とする半導体回路。

### 【請求項3】

Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを有する第1のアナログスイッチと、

Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを有する第2のアナログスイッチとを有し、

各薄膜トランジスタを構成する活性層は、絶縁表面を有する基板上に形成された結晶性珪素膜を用いて構成されており、

前記活性層を構成する結晶性珪素膜は、結晶化を助長する金属元素の添加領域から前記基板に平行な方向に結晶成長した結晶構造を有し、

前記第1のアナログスイッチおよび前記第2のアナログスイッチは2つの前記添加領域の間に位置し、

前記第1のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と当該Pチャネル型の薄膜トランジスタと最も近い添加領域の端部との距離は、前記第2のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と当該Pチャネル型の薄膜トランジスタと最も近い添加領域の端部との距離の±10%以内であり、

前記第1のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と当該Nチャネル型の薄膜トランジスタと最も近い添加領域の端部との距離は、前記第2のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と当該Nチャネル型の薄膜トランジスタと最も近い添加領域の端部との距離の±10%以内であることを特徴とする半導体回路。

### 【請求項4】

Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを有する第1のアナログスイッチと、

Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを有する第2のアナログスイッチとを有し、

各薄膜トランジスタを構成する活性層は、絶縁表面を有する基板上に形成された結晶性珪素膜を用いて構成されており、

前記第1のアナログスイッチの各薄膜トランジスタの活性層を構成する結晶性珪素膜は、結晶化を助長する金属元素の第1の添加領域から前記基板に平行な方向に結晶成長した結晶構造を有し、

前記第2のアナログスイッチの各薄膜トランジスタの活性層を構成する結晶性珪素膜は、結晶化を助長する金属元素の第2の添加領域から前記基板に平行な方向に結晶成長した結晶構造を有し、

前記第1のアナログスイッチおよび前記第2のアナログスイッチは前記第1の添加領域と前記第2の添加領域の間に位置し、

前記第1のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成

10

20

30

40

50

領域の中心と前記第1の添加領域の端部との距離と、前記第2のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第2の添加領域の端部との距離が等しく、

前記第1のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部との距離と、前記第2のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第2の添加領域の端部との距離が等しいことを特徴とする半導体回路。

**【請求項5】**

Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを有する第1のアナログスイッチと、

10

Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを有する第2のアナログスイッチとを有し、

各薄膜トランジスタを構成する活性層は、絶縁表面を有する基板上に形成された結晶性珪素膜を用いて構成されており、

前記第1のアナログスイッチの各薄膜トランジスタの活性層を構成する結晶性珪素膜は、結晶化を助長する金属元素の第1の添加領域から前記基板に平行な方向に結晶成長した結晶構造を有し、

前記第2のアナログスイッチの各薄膜トランジスタの活性層を構成する結晶性珪素膜は、結晶化を助長する金属元素の第2の添加領域から前記基板に平行な方向に結晶成長した結晶構造を有し、

20

前記第1のアナログスイッチおよび前記第2のアナログスイッチは前記第1の添加領域と前記第2の添加領域の間に位置し、

前記第1のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部との距離は、前記第2のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第2の添加領域の端部との距離の±10%以内であり、

前記第1のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部との距離は、前記第2のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第2の添加領域の端部との距離の±10%以内であることを特徴とする半導体回路。

30

**【請求項6】**

第1の入力信号が入力され、Nチャネル型の薄膜トランジスタとPチャネル型の薄膜トランジスタとを有する第1のインバータ回路と、

前記第1のインバータ回路の出力信号がゲイトに入力される薄膜トランジスタと前記第1の入力信号がゲイトに入力される薄膜トランジスタとを有する第1のアナログスイッチ回路と、

第2の入力信号が入力され、Nチャネル型の薄膜トランジスタとPチャネル型の薄膜トランジスタとを有する第2のインバータ回路と、

前記第2のインバータ回路の出力信号がゲイトに入力される薄膜トランジスタと前記第2の入力信号がゲイトに入力される薄膜トランジスタとを有する第2のアナログスイッチ回路とを有し、

40

前記第1及び第2のインバータ回路の薄膜トランジスタの活性層と前記第1のアナログスイッチ回路の薄膜トランジスタの活性層とを構成する結晶性珪素膜は、結晶化を助長する金属元素の第1の添加領域から基板に平行な方向に結晶成長した結晶構造を有し、

前記第2のアナログスイッチ回路の薄膜トランジスタの活性層を構成する結晶性珪素膜は、結晶化を助長する金属元素の第2の添加領域から基板に平行な方向に結晶成長した結晶構造を有し、

前記第1のインバータ回路のNチャネル型の薄膜トランジスタのチャネル形成領域の中心と前記第1の添加領域の端部との距離をL<sub>1</sub>とし、前記第2のインバータ回路のNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部

50

との距離を  $L_2$ とした場合、 $L_1 < L_2$ であり、

前記第1のインバータ回路のPチャネル型の薄膜トランジスタのチャネル形成領域の中心と前記第1の添加領域の端部との距離を  $L_3$ とし、前記第2のインバータ回路のPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部との距離を  $L_4$ とした場合、 $L_3 < L_4$ であり、

前記第1のアナログスイッチおよび前記第2のアナログスイッチは前記第1の添加領域と前記第2の添加領域の間に位置し、

前記第1のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部との距離と、前記第2のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第2の添加領域の端部との距離が等しく、

前記第1のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部との距離と、前記第2のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第2の添加領域の端部との距離が等しいことを特徴とする半導体回路。

#### 【請求項7】

第1の入力信号が入力され、Nチャネル型の薄膜トランジスタとPチャネル型の薄膜トランジスタとを有する第1のインバータ回路と、

前記第1のインバータ回路の出力信号がゲイトに入力される薄膜トランジスタと前記第1の入力信号がゲイトに入力される薄膜トランジスタとを有する第1のアナログスイッチ回路と、

第2の入力信号が入力され、Nチャネル型の薄膜トランジスタとPチャネル型の薄膜トランジスタとを有する第2のインバータ回路と、

前記第2のインバータ回路の出力信号がゲイトに入力される薄膜トランジスタと前記第2の入力信号がゲイトに入力される薄膜トランジスタとを有する第2のアナログスイッチ回路とを有し、

前記第1のインバータ回路のNチャネル型の薄膜トランジスタの活性層と前記第2のインバータ回路のNチャネル型の薄膜トランジスタの活性層は同一の活性層からなり、前記第1のインバータ回路のPチャネル型の薄膜トランジスタの活性層と前記第2のインバータ回路のPチャネル型の薄膜トランジスタの活性層は同一の活性層からなり、

前記第1及び第2のインバータ回路の薄膜トランジスタの活性層と、前記第1のアナログスイッチ回路の薄膜トランジスタの活性層とを構成する結晶性珪素膜は、結晶化を助長する金属元素の第1の添加領域から基板に平行な方向に結晶成長した結晶構造を有し、

前記第2のアナログスイッチ回路の薄膜トランジスタの活性層を構成する結晶性珪素膜は、結晶化を助長する金属元素の第2の添加領域から基板に平行な方向に結晶成長した結晶構造を有し、

前記第1のインバータ回路のNチャネル型の薄膜トランジスタのチャネル形成領域の中心と前記第1の添加領域の端部との距離を  $L_1$ とし、前記第2のインバータ回路のNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部との距離を  $L_2$ とした場合、 $L_1 < L_2$ であり、

前記第1のインバータ回路のPチャネル型の薄膜トランジスタのチャネル形成領域の中心と前記第1の添加領域の端部との距離を  $L_3$ とし、前記第2のインバータ回路のPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部との距離を  $L_4$ とした場合、 $L_3 < L_4$ であり、

前記第1のアナログスイッチおよび前記第2のアナログスイッチは前記第1の添加領域と前記第2の添加領域の間に位置し、

前記第1のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部との距離と、前記第2のアナログスイッチのNチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第2の添加領域の端部との距離が等しく、

10

20

30

40

50

前記第1のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第1の添加領域の端部との距離と、前記第2のアナログスイッチのPチャネル型の薄膜トランジスタの活性層のチャネル形成領域の中心と前記第2の添加領域の端部との距離が等しいことを特徴とする半導体回路。

【請求項8】

請求項1乃至請求項7のいずれか一において、前記薄膜トランジスタのキャリアの移動方向は、前記結晶構造の成長方向と平行であることを特徴とする半導体回路。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】10

本明細書で開示する発明は、結晶性を有する薄膜半導体装置を用いた回路に関する。

【0002】

【従来技術】

ガラス基板や石英基板の上に薄膜珪素膜を形成し、その珪素膜を用いる半導体装置が知られている。近年、この珪素膜を熱或いはレーザーにより結晶化することにより、結晶性を持たせ高速動作を可能にさせる技術が開発されている。

【0003】

熱により結晶化する多結晶珪素半導体装置は、800 や 900 以上というような比較的高温の加熱処理を利用する。そのため、基板として、上記高温に耐えうる石英基板を用いている。20

【0004】

レーザーを用いて結晶化を行う技術は、基板に対して、熱的ダメージがほとんど生じないためガラス基板を用いることが出来る。

【0005】

【発明が解決しようとする課題】

現状においてTFTは、アクティブマトリクス型の液晶表示装置のアクティブマトリクス回路と周辺駆動回路とを同一基板上に集積化するために利用されている。即ちアクティブマトリクス回路と周辺駆動回路とを同一の基板上にTFTを用いて形成することが行われている。

【0006】

また、周辺駆動回路（シフトレジスタ回路やバッファー回路で構成される）以外に発振回路やD/AコンバータやA/Dコンバータ、更に各種画像処理を行うデジタル回路を、更に同一基板上に集積化することが考えられている。30

【0007】

このような各種回路を構成する場合、差動回路のようにペアとなる薄膜トランジスタの特性が厳密に一致する必要のある回路構成が必要とされる。

【0008】

また、上述した回路の基本となるCMOS回路（Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタを相補型に構成した回路）では、Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとの特性が極力一致していることが好ましい。40

【0009】

しかし、同一の構造と寸法でもってPチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを作製した場合、Nチャネル型の薄膜トランジスタに方が30%~50%程度移動度が大きなものとなってしまう。

【0010】

従った、動作周波数を高くしてCMOS回路を動作させた場合、Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタにおいて、その動作のバランスが崩れてしまう事態が生じる。

【0011】

本明細書で開示する発明は、上記のような回路によって必要とされる薄膜トランジスタの50

特性差を是正するような技術を提供することを課題とする。

**【0012】**

**【課題を解決するための手段】**

本明細書で開示する発明の一つは、絶縁表面を有する基板上に形成された結晶性珪素膜を活性層とした複数の半導体装置を有する半導体回路であって、前記活性層を構成する結晶性珪素膜は、所定の領域から基板に平行な方向に結晶成長した結晶構造を有し、各半導体装置を構成する活性層のチャネル形成領域の中心と前記所定の領域の端部との距離が同一または概略同一であることを特徴。

**【0013】**

他の発明の構成は、Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを相補型に組み合わせた半導体回路であって、各薄膜トランジスタを構成する活性層は、絶縁表面を有する基板上に形成された結晶性珪素膜を用いて構成されており、前記活性層を構成する結晶性珪素膜は、所定の領域から基板に平行な方向に結晶成長した結晶構造を有し、Pチャネル型の薄膜トランジスタを構成する活性層のチャネル形成領域の中心と前記所定の領域の端部との距離をL<sub>1</sub>とし、Nチャネル型の薄膜トランジスタを構成する活性層のチャネル形成領域の中心と前記所定の領域の端部との距離をL<sub>2</sub>とした場合、L<sub>1</sub>とL<sub>2</sub>とは異なることを特徴とする。

**【0014】**

上記構成において、Pチャネル型の薄膜トランジスタの特性とNチャネル型の薄膜トランジスタの特性を合わせるのであれば、L<sub>1</sub> < L<sub>2</sub>とする。

**【0015】**

他の発明の構成は、Pチャネル型の薄膜トランジスタとNチャネル型の薄膜トランジスタとを相補型に組み合わせた半導体回路であって、各薄膜トランジスタを構成する活性層は、絶縁表面を有する基板上に形成された結晶性珪素膜を用いて構成されており、前記活性層を構成する結晶性珪素膜は、所定の領域から基板に平行な方向に結晶成長した結晶構造を有し、Pチャネル型の薄膜トランジスタを構成する活性層のチャネル形成領域の中心と前記所定の領域の端部との距離をL<sub>1</sub>とし、Nチャネル型の薄膜トランジスタを構成する活性層のチャネル形成領域の中心と前記所定の領域の端部との距離をL<sub>2</sub>とした場合、L<sub>1</sub>とL<sub>2</sub>とを異ならせることにより、両薄膜トランジスタの特性差を是正していることを特徴とする。

**【0016】**

他の発明の構成は、同一の特性を要求される少なくとも2つの薄膜トランジスタを有した半導体回路であって、各薄膜トランジスタを構成する活性層は、絶縁表面を有する基板上に形成された結晶性珪素膜を用いて構成されており、前記活性層を構成する結晶性珪素膜は、所定の領域から基板に平行な方向に結晶成長した結晶構造を有し、各薄膜トランジスタにおいて、活性層のチャネル形成領域の中心と前記所定の領域の端部との距離を同じにすることにより各薄膜トランジスタの特性の違いを是正していることを特徴とする。

**【0017】**

上記構成において、活性層と所定の領域との距離は、各半導体装置または薄膜トランジスタにおいて、所定の領域の端部から活性層内に形成されるチャネル形成領域の中心までの距離が±10%以内、より好ましくは±5%以内である。

**【0018】**

本明細書で開示する発明で用いる薄膜トランジスタ(TFT)は、結晶化を助長する元素によって、基板と平行に結晶が横成長した半導体を用いる。そして、TFTの動作時において、半導体層中のソース領域から、チャネル領域を経て、ドレイン領域へと流れる電流の流れが、結晶の成長方向に沿って形成されたTFTを用いる。

**【0019】**

このようなTFTを用いることにより、上記のような高速動作を処理することを要求される回路を構成することが可能となる。

**【0020】**

10

20

30

40

50

本明細書中で結晶化を助長する金属元素とは、Fe、Co、Ni、Ru、Rh、Pd、Os、Ir、Pt、Cu、Auから選ばれた一種または複種類のものを指す。

#### 【0021】

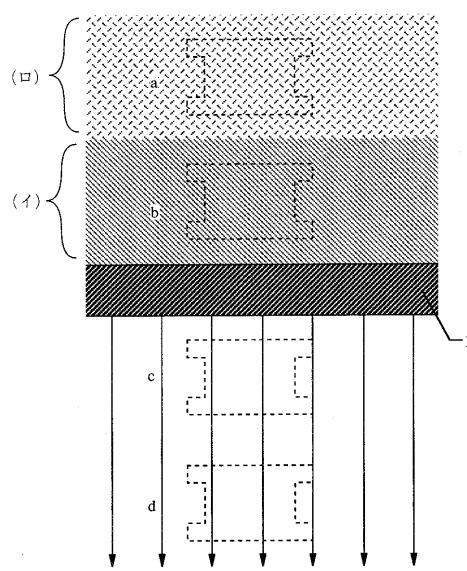

図1に結晶化を助長する金属元素による結晶化の模式的な上面図を示す。図1において、1は金属元素添加領域である。このように帯状に金属元素を添加することにより、結晶化の成長方向を矢印で示すように揃えることができる。

#### 【0022】

しかし、このように金属元素添加領域1の端部から結晶成長した半導体を用いて、複数のTFTを得ようとする場合、添加領域1の端部から近い領域(イ)では、結晶粒は密に成長し、添加領域の端部から遠い領域(ロ)では、結晶の成長限界点に近いため、その結晶粒は疎となっている。

#### 【0023】

そのため、近い領域(イ)に形成される半導体層b、cと、遠い領域(ロ)で形成される半導体層a、dとでは、得られるTFTの特性が異なる。一般的には、金属元素に近い領域(イ)に形成される半導体層b、cの方が、遠い領域(ロ)で形成される半導体層a、dよりも良い特性を得ることが出来る。

#### 【0024】

しかし、金属元素に近すぎる領域では、逆に金属元素が高濃度存在するため、特性が悪くなることも考えられる。また、金属元素の添加濃度を変えたり、結晶化の時間、温度等の条件を変えることにより、その成長限界点は変化する。

#### 【0025】

ここでいう、成長限界点とは、図1のように成長領域に障害が存在しない時の金属元素による結晶化の終点を指す。尚、成長限界点は、他の成長領域よりも金属元素が高濃度に存在する。そのため、一般的にはパターニング時に一緒に除去するよう設計する。

#### 【0026】

図1において、半導体a、dと半導体b、cとでは最も近くに存在する金属元素添加領域1の端部までの離間が異なる。このようにして形成された半導体a、b、c、dを一つの回路に用いるには、その特性の違いを考慮して設計する必要がある。

#### 【0027】

半導体aとb、cとdを組み合わせて用いるには、その特性の差を問題としない回路、例えばインバータ回路等に用いることが考えられる。

#### 【0028】

また、その特性の違いを利用して、優れた特性を得られる半導体b、cに移動度の小さいP型不純物を添加し、特性の劣っている半導体a、dに移動度の大きいN型不純物を添加する。

#### 【0029】

そして、半導体aとb、cとdを組み合わせてCMOS回路を形成する。こうすることで、CMOS回路を構成するPチャネル型の薄膜トランジスタとNチャネルチャネル型の薄膜トランジスタとの特性の違いを是正することができる。

#### 【0030】

ただし、CMOS回路の設計において、その金属元素の濃度、添加領域又結晶化の温度等の諸条件によって、半導体a、dと半導体b、cの特性の違いは大きく異なることを考慮して条件決めをする必要がある。

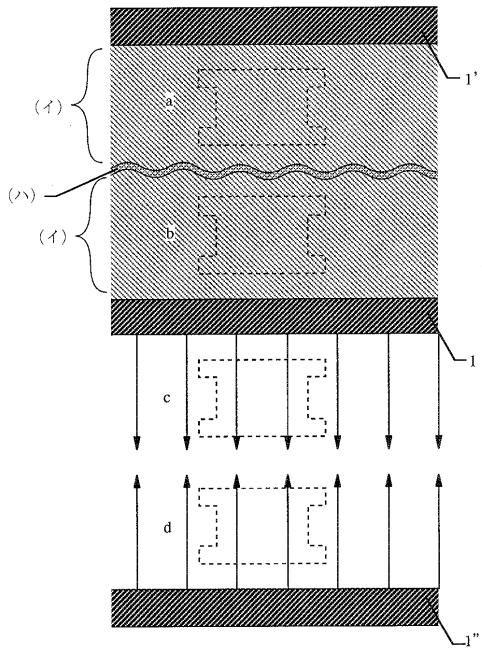

#### 【0031】

また、半導体a、b、c、dに均一なTFT特性を要求する場合は、図2に示すように、金属元素を添加する領域を1、1'、1''のように添加する。ここで、添加領域1'は、添加領域1'の端部と半導体aの活性層のチャネル形成領域の中心との離間が、半導体b、cの活性層のチャネル形成領域の中心と添加領域1の端部との離間と等しくなるように配置する。同様に、添加領域1''は、添加領域1''の端部と半導体dの活性層のチャネル形成領域の中心との離間が、半導体b、cの活性層のチャネル形成領域の中心と添加領域1の端部との離間と等しくなるように配置する。

10

20

30

40

50

域 1 の端部との離間と等しくなるよう配置する。

**【0032】**

つまり、図 2において半導体 a の活性層のチャネル形成領域の中心とその最も近くに存在する金属元素添加領域 1' の端部との離間、半導体 b 及び c の活性層のチャネル形成領域の中心とその最も近くに存在する金属元素添加領域 1 の端部との離間及び半導体 d の活性層のチャネル形成領域の中心とその最も近くに存在する金属元素添加領域 1" の端部との離間とを等しくする。

**【0033】**

このように配置することによって、図中矢印で示すように結晶は成長し、半導体 a、b、c、d は、等しい TFT 特性を有することになる。 10

**【0034】**

このような配置は、対となる薄膜トランジスタの特性を一致させる必要がある差動增幅回路等に利用すると効果がある。

**【0035】**

ここで、注意するべき要素として、図中(ハ)で示される領域は、添加領域 1 からの結晶成長と、添加領域 1' からの結晶成長とがぶつかり形成される粒界である。この粒界(ハ)は、結晶の成長方向が乱れているため、また、金属元素の濃度も比較的高濃度になっているため、TFT の半導体として用いることは極力避けるべきである。なお図中では省略しているが、半導体 c と d の間に粒界は形成されている。 20

**【0036】**

このようにして形成された半導体 a、b、c、d を用いて回路を作製すると、全ての半導体の特性が揃った回路を構成することができる。つまり、同一の入力波形に対して、同一の出力波形を出力することが可能となる。 20

**【0037】**

**【発明の実施の形態】**

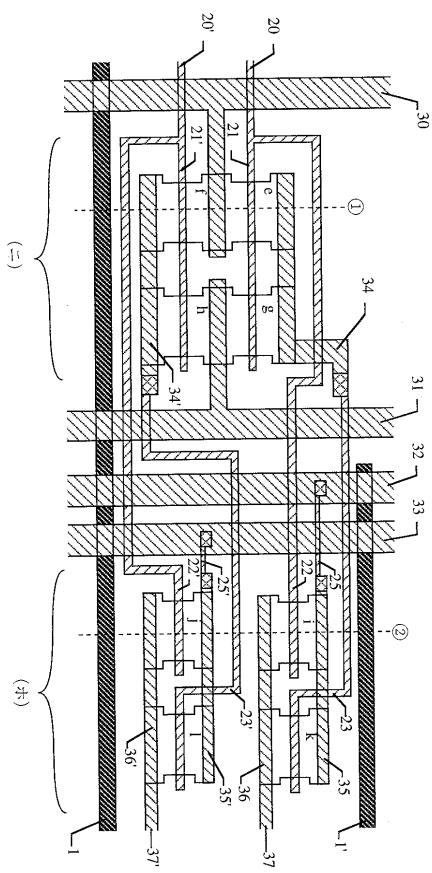

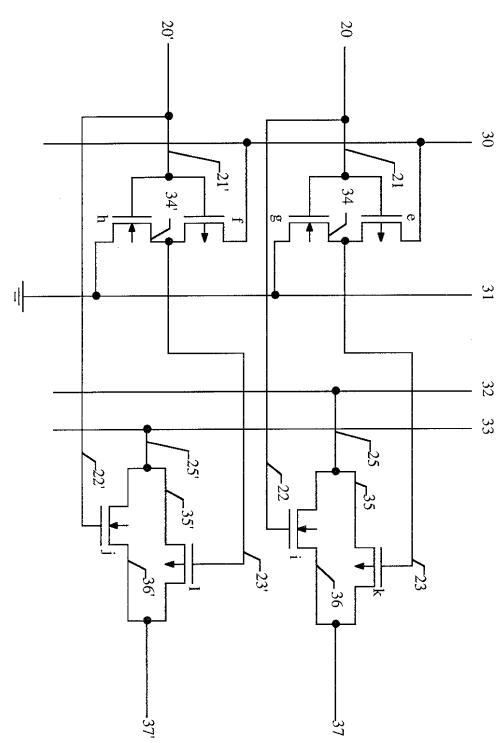

本発明の望ましい実施の形態として、図 3 にそのマスクパターンを示す。ここで、アクティブマトリクス型の表示装置のソースドライバー回路の一部を構成する(ニ)で示されるインバータ回路と、(ホ)で示されるアナログスイッチ回路とを同時に形成する。その等価回路図を図 4 に示す。 30

**【0038】**

図 3、4 に示すようにインバータ回路(ニ)は、P 型半導体 e と N 型半導体 g、P 型半導体 f と N 型半導体 h で構成される二つの組み合わせが形成されている。また、アナログスイッチ回路も同様に、N 型半導体 i と P 型半導体 k、N 型半導体 j と P 型半導体 l の二つの組み合わせが構成されている。 30

**【0039】**

そして、インバータ回路(ニ)の e と g で構成される回路とアナログスイッチ回路(ホ)の i と k で構成される回路は連結している。

**【0040】**

同様に、インバータ回路(ニ)の f と h で構成される回路とアナログスイッチ回路(ホ)の j と l で構成される回路は連結している。 40

**【0041】**

図 3 で、1、1' は金属元素の添加領域を示している。半導体 e、f、g、h は、添加領域 1 から、添加領域 1 に対して垂直の方向に結晶成長した結晶構造を有している。

**【0042】**

そのため、図 1 にも示したように、結晶性半導体 e と f 又 g と h の特性は異なり、半導体 f、h の方が半導体 e、g よりも優れた特性を有している。

**【0043】**

しかし、e と g で形成されるインバータ回路と、f と h で形成されるインバータ回路とは、TFT 特性の相互均一性を殊更必要とするものではないので、添加領域は 1 だけで十分である。 50

**【0044】**

しかし、アナログスイッチ回路（ホ）では、結晶性半導体iとj、kとlのTFT特性に均一性を要求される。そのため、半導体i、kに近接して、金属元素添加領域1'を形成する。金属元素添加領域1の端部と半導体jの活性層のチャネル形成領域の中心との距離は、金属元素添加領域1'の端部と半導体iの活性層のチャネル形成領域の中心との距離に等しくする。また、金属元素添加領域1の端部と半導体lの活性層のチャネル形成領域の中心との距離は、金属元素添加領域1'の端部と半導体kの活性層のチャネル形成領域の中心との距離に等しくする。このように添加領域1および1'を形成することにより半導体iとj、kとlのTFT特性を等しくすることができる。

**【0045】**

金属元素添加領域と半導体との距離は、金属元素添加領域の端部と最終的にチャネル形成領域となる領域の中心との距離を基準とする。そして、そろった特性が要求される複数の半導体装置においては、各半導体装置におけるこの距離が±10%以内、より好ましくは±5%以内となるようにすることが望ましい。もちろん、要求される特性の許容誤差が大きければ、この限りではない。

**【0046】**

次に、図4で示す回路は、20、20'から入ってくる入力信号を、インバータ回路（二）で反転させる。そして、その信号を23、23'を通じて珪素膜k、lのゲイトに入力する。また、配線20、20'から入ってくる入力信号を、配線22、22'を通じ珪素膜i、jのゲイトに入力する。

**【0047】**

こうして、入力信号が高電位の時、アナログスイッチ回路（ホ）はオン状態になり、ビデオ信号線32の信号を配線25、35、36を通じて配線37からソース線へと出力する。また、ビデオ信号線33の信号を配線25'、35'、36'を通じて配線37'がらソース線へと出力する。

以下に、実施例としてこの回路の作製工程を説明する。

**【0048】**

なお、金属元素の添加領域は、回路の完成状態においては、存在していない。しかしながらこの領域は下記のような理由によりその位置を判別することができる。

**【0049】**

即ち、金属元素を添加した領域の半導体は、アロイ化しており、エッティングの際に他の領域に比較して速いレートでエッティングされる。このため、下地の基板表面が一部削られた状態となる。従って、この下地が一部エッティングされた状態の領域（凹状になっている）が金属元素を導入した領域であると判別することができる。

**【0050】****【実施例】****〔実施例1〕**

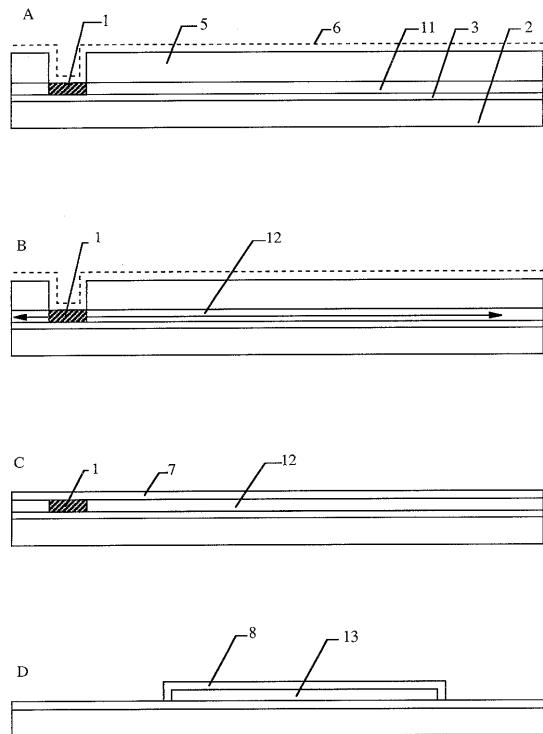

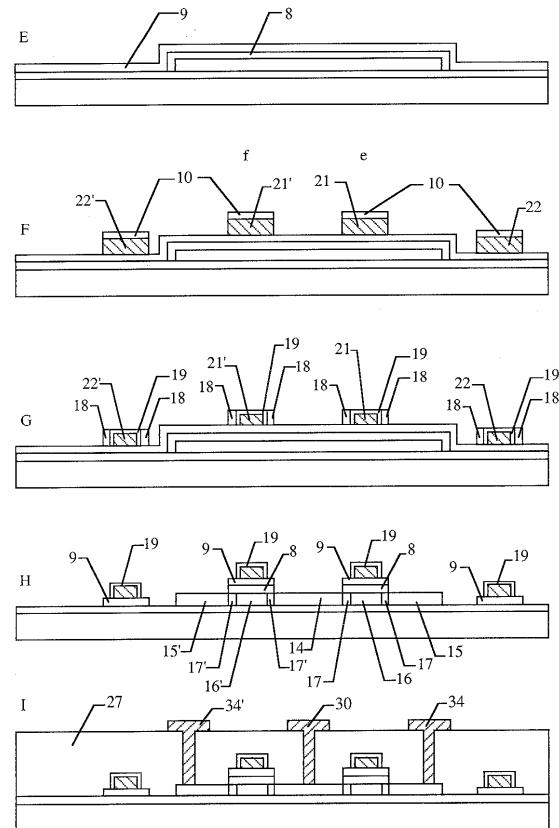

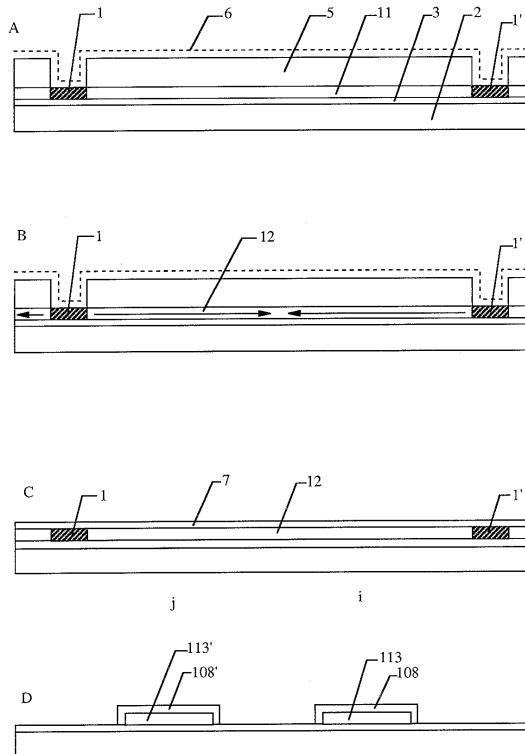

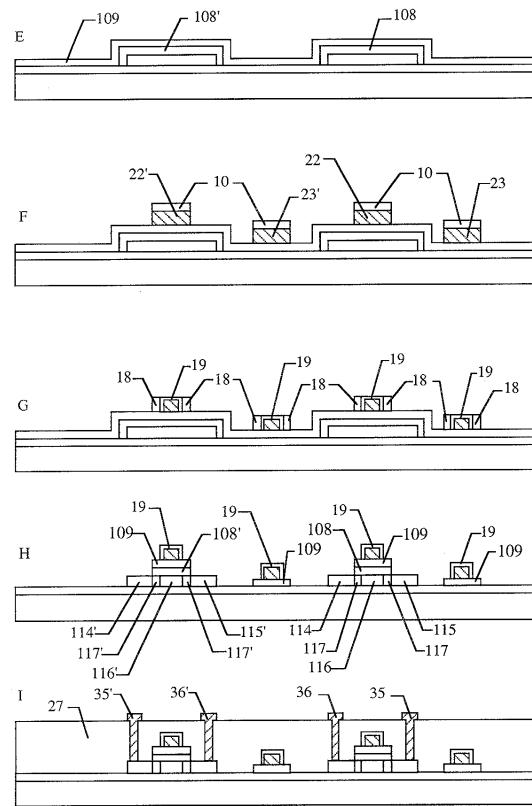

本実施例は、図3に示す構成の作製工程の一つを示す。図5、6に、図3の直線1の断面の作製工程図を示す。また、図7、8に、図3の直線2の断面の作製工程図を示す。

**【0051】**

まず、図5A及び図7Aの2で示す石英基板上に、下地膜3として酸化珪素膜を3000厚さに成膜する。なお、石英基板の表面の平滑性が良く、また洗浄を十分にするのであれば、この下地膜3は特に必要ない。

**【0052】**

なお、基板としては石英基板を利用することが現状においては好ましい選択となるが、加熱処理温度に耐える基板であれば、石英に限定されるものではない。

**【0053】**

次に結晶性珪素膜の出発膜となる非晶質珪素膜11を減圧熱CVD法でもって、500の厚さに成膜する。

**【0054】**

次に図示しない酸化珪素膜を1500の厚さに成膜し、それをパターニングすることにより、5で示されるマスクを形成する。このマスクは図5Aでは、1で示される、図7Aでは、1、1'で示される金属元素添加領域に開口が形成されている。この開口が形成されている領域においては、非晶質珪素膜11が露呈する。

**【0055】**

金属元素添加領域1、1'は、図面の奥行及び手前方向に長手方向を有する細長い長方形を有している。この金属元素添加領域1、1'の幅は20μm以上とするのが適当である。またその長手方向の長さは必要とする長さでもって形成すればよい。

**【0056】**

また、図7Aに示す金属元素添加領域1、1'の離間は、その間にTFTを作製することとそのマージンを考慮して設計する。一般的には、結晶の成長距離は50~200μmであるので、その離間は、80~300μmの範囲で選択される。本実施例では、その離間は100μmとする。

**【0057】**

そして、重量換算で10ppmのニッケル元素を含んだ酢酸ニッケル溶液を塗布する。そして図示しないスピナーを用いてスピンドライを行い余分な溶液を除去する。ニッケル元素の導入量は、上記溶液中におけるニッケル元素の含有濃度で制御することができる。

**【0058】**

こうして、ニッケル元素が図5A及び図7Aの点線6で示されるような状態で存在した状態が得られる。この状態では、ニッケル元素が金属元素添加領域1、1'において、非晶質珪素膜の一部に選択的に接して保持された状態が得られる。

**【0059】**

なお、ニッケル元素の導入をイオン注入法を用いて行ってもよい。この場合、ニッケル元素の溶液を塗布する場合に比較して、ニッケル元素の導入位置をより精度よく制御することができる。したがって、ニッケル元素の導入領域の幅が数μmあるいはそれ以下の極めて狭い場合や、導入領域の形状が複雑な場合に特に有効である。

**【0060】**

次に水素を3%含有した極力酸素を含まない窒素雰囲気中（または窒素雰囲気中）において、500~630、例えば600、8時間の加熱処理を行う。すると、図5B及び図7Bの矢印で示すように、基板2と平行な方向への結晶成長が進行する。

**【0061】**

この結晶成長は、ニッケル元素が導入された金属元素添加領域1、1'の領域から周囲に向かって進行する。この基板に平行な方向への結晶成長を横成長またはラテラル成長と称する。

**【0062】**

この結晶成長により得られる横成長した結晶性珪素膜の表面は、従来の低温ポリシリコンや高温ポリシリコンに比較して非常に平滑性の良いものが得られる。これは、結晶粒界の延在する方向が概略そろっていることに起因すると考えられる。

**【0063】**

一般の多結晶珪素やポリシリコンと呼ばれる珪素膜は、その表面の凹凸は±100以上ある。しかし、本実施例で示すような横成長をさせた場合は、その表面の凹凸は±30以下であることが観察されている。この凹凸は、ゲイト絶縁膜との間の界面特性を悪化させるものであり、極力小さいものであることが好ましい。

**【0064】**

上記の結晶化のために加熱処理条件においては、この横成長を100μm以上にわたって行わすことができる。こうして横成長した領域を有する珪素膜12、12'を得る。

**【0065】**

この結晶成長のための加熱処理は、450~1100（上限は基板の耐熱性で規制される）で行うことができる。ある程度の横成長距離を確保するのであれば、加熱処理の温

10

20

30

40

50

度を 600 以上とすることが好ましい。しかし、それ以上に温度を上げることによる結晶成長距離や結晶性の向上はそれ程大きくなない。（従って、経済性や工程の簡略化を考慮した場合、600 ~ 650 程度の加熱処理で十分である）

【0066】

そしてニッケル元素を選択的に導入するための酸化珪素膜でなるマスク 5 を除去する。

【0067】

この状態においては、ニッケル元素が膜中に偏在している。特に、金属元素添加領域 1、1' とその近辺及び結晶成長の先端部分においては、ニッケル元素が比較的高濃度に存在している。

【0068】

従って、活性層の形成においては、それらの領域を避けることが重要となる。即ち、活性層中に上記ニッケル元素が偏在した領域が存在しないようにすることが重要である。そのため、活性層と金属元素添加領域とは、少なくとも 10 μm 以上離れている必要がある。

【0069】

また、図 7B の結晶性珪素膜 12' においては、結晶のぶつかりによって形成される粒界が、その中心付近に形成されているため、後に半導体 i、j をパターニングする際に、その間に少なくとも 10 μm 以上のマージンを必要とする。

【0070】

結晶化の後にさらに、レーザー光の照射を行なってもよい。即ち、レーザー光の照射により、さらに結晶化を助長させてもよい。このレーザー光の照射は、膜中に存在するニッケル元素の固まりを分散させ、後にニッケル元素を除去し易くする効果を有している。なお、この段階でレーザー光の照射を行っても、さらに横成長が進行することはない。

【0071】

レーザー光としては、紫外領域の波長を有するエキシマレーザーを利用することができます。例えば、KrF エキシマレーザー（波長 248 nm）や XeCl エキシマレーザー（波長 308 nm）を利用することができます。

【0072】

次にハロゲン元素を含有した酸素雰囲気、例えば HCl を 3 体積 % 含んだ酸素雰囲気中において、950 の加熱処理を行い、熱酸化膜 7 を 200 の厚さに成膜する。（図 5C、図 7C）

【0073】

上記の工程においては、熱酸化膜の形成に従い、膜中の不安定な結合状態を有する珪素元素が熱酸化膜の形成に利用される。そして、膜中の欠陥が減少し、より高い結晶性を得ることができる。

【0074】

また同時に熱酸化膜 7 の形成および塩素の作用により膜中よりニッケル元素のゲッタリングが行われる。この工程で、珪素膜 12、12' 中にも若干の塩素が添加される。

【0075】

当然、熱酸化膜中には、比較的高濃度にニッケル元素が取り込まれることになる。そして相対的に珪素膜 12、12' 中のニッケル元素は減少する。こうして図 5C、図 7C に示す状態を得る。

【0076】

熱酸化膜 7 を形成したら、この熱酸化膜 7 を除去する。こうして、ニッケル元素の含有濃度を減少させた結晶性珪素膜 12、12' を得る。

【0077】

図 5C で得られた結晶性珪素膜 12 は、図 1 に示すように一方向に結晶構造が延在した（この方向は結晶成長方向に一致する）構造を有している。即ち、細長い円柱状の結晶体が複数の一方向に延在した結晶粒界を介して、複数平行に並んでいるような構造を有している。そして、金属元素添加領域に近い領域では結晶が密に、遠い領域では比較的疎に形成されている。

## 【0078】

また、図7Cで得られた結晶性珪素膜12'は、図2に示すように二つの結晶成長がぶつかりことにより、大部分において、結晶が密な領域を均一に有する構造を得ている。即ち、金属元素添加領域1、1'の極近辺と、結晶成長がぶつかることにより形成される粒界とを除く領域で結晶の均一性を有している。

## 【0079】

次にパターニングを行うことにより、横成長領域でなるパターンを形成する。図5Dの島状の領域13が後に半導体e及びfの活性層となる。また、図7Dの島状の領域113が後に半導体iの、113'が半導体jの活性層となる。

## 【0080】

ここでは、ソース領域とドレイン領域とを結ぶ方向と結晶成長方向とが一致または概略一致するようにパターンの位置取りを行う。こうすることで、キャリアの移動する方向と結晶格子が連続して延在する方向とを合わせることができ、結果として高い特性のTFTを得ることができる。

## 【0081】

そして、13、113、113'でなるパターンを形成後に熱酸化膜8、108、108'を300の厚さに成膜する。この熱酸化膜は、HClを0.1~10体積%、例えば3体積%含有した酸素雰囲気中において、950の加熱処理を行うことによって得る。

## 【0082】

この工程においても熱酸化膜7を成膜する場合と同様の効果を得ることができる。なお、この熱酸化膜8、108、108'は、TFTのゲイト絶縁膜の一部となる。

## 【0083】

この後、熱酸化膜8、108、108'と共にゲイト絶縁膜を構成する酸化珪素膜9、109、109'を1000の厚さにプラズマCVD法により成膜する。(図6E、図8E)

## 【0084】

ここでは、熱酸化膜8、108、108'を先に形成したが、パターン13、113、113'を形成後、プラズマCVD法で酸化珪素膜を形成してから、加熱処理を行い熱酸化膜を酸化珪素膜と珪素膜の間に形成する方法も選択できる。この方法を選択すると、ゲイト絶縁膜と珪素膜との界面における界面準位を下げることができる。

## 【0085】

最終的に珪素膜中に残留するニッケルの濃度は、現状では $1 \times 10^{14}$ 原子個/cm<sup>3</sup>~ $5 \times 10^{18}$ 原子個/cm<sup>3</sup>程度となるが、低いほど好ましい。熱酸化膜のゲッタリング条件を詰めれば、この濃度の上限は $5 \times 10^{17}$ 原子個/cm<sup>3</sup>程度まで低減できる。この濃度の計測は、SIMS(2次イオン分析方法)を利用して計測できる。

## 【0086】

次にゲイト電極を形成するためのアルミニウム膜をスパッタ法で4000の厚さに成膜する。このアルミニウム膜中には、スカンジウムを0.2重量%含有させる。

## 【0087】

アルミニウム膜中に入れるスカンジウムを含有させるのは、後の工程において、ヒロックやウィスカーやが発生することを抑制するためである。ヒロックやウィスカーやというものは、加熱の際のアルミニウムの異常成長に起因する針状あるいは刺状の突起部のことである。

## 【0088】

ゲイト電極を形成するための材料として、アルミニウム以外にタンタル(Ta)、多量にリン(P)がドープされた多結晶シリコン、タングステンのシリサイド(WSi)、またはリンドープされた多結晶シリコンとタングステンのシリサイドの積層または混成した構造としてもよい。

## 【0089】

アルミニウム膜を成膜したら、図示しない緻密な陽極酸化膜を形成する。この陽極酸化膜は、3%の酒石酸を含んだエチレングルコール溶液を電解溶液とし、アルミニウム膜を陽

10

20

30

40

50

極、白金を陰極として行う。この工程においては、アルミニウム膜上に緻密な膜質を有する陽極酸化膜を 100 の厚さに成膜する。

**【0090】**

この図示しない陽極酸化膜は、後に形成されるレジストマスクとの密着性を向上させる役割を有している。

**【0091】**

この陽極酸化膜の膜厚は、陽極酸化時の印加電圧によって制御することができる。

**【0092】**

次にレジストマスク 10 を形成する。そしてこのレジストマスクを利用して、図 6 F 及び図 8 F に示すように、アルミニウム膜を 21、21'、22、22'、23、23' で示されるパターンにパターニングする。

10

**【0093】**

ここで再度の陽極酸化を行う。ここでは、3 % のシュウ酸水溶液を電解溶液として用いる。この電解溶液中において、アルミニウムのパターン 21、21'、22、22'、23、23' を陽極とした陽極酸化を行うことにより、18 で示される多孔質状の陽極酸化膜が形成される。

**【0094】**

この工程においては、上部に密着性の高いレジストマスク 10 が存在する関係で、アルミニウムパターンの側面に選択的に陽極酸化膜 18 が形成される。

**【0095】**

この陽極酸化膜は、その膜厚を数  $\mu\text{m}$  まで成長させることができる。ここでは、その膜厚を 6000 とする。なお、その成長距離は、陽極酸化時間によって制御することができる。

20

**【0096】**

そしてレジストマスク 10 を除去する。次に再度の緻密な陽極酸化膜の形成を行う。即ち、前述した 3 % の酒石酸を含んだエチレングルコール溶液を電解溶液とした陽極酸化を再び行う。

**【0097】**

この工程においては、多孔質状の陽極酸化膜 18 中に電解溶液が進入する関係から、19 で示されるように緻密な膜質を有する陽極酸化膜が形成される。

30

**【0098】**

この緻密な陽極酸化膜 19 の膜厚は 1000 とする。この膜厚の制御は印加電圧によって行う。(図 6 G、図 8 G)

**【0099】**

ここで、露呈した酸化珪素膜 9、109、109' をエッティングする。また同時に熱酸化膜 8、108、108' をエッティングする。このエッティングはドライエッティングを利用する。そして酢酸と硝酸とリン酸とを混合した混酸を用いて多孔質状の陽極酸化膜 18 を除去する。

**【0100】**

次に、不純物イオンの注入を行う。ここでは、図 8 の半導体 i、j から N チャネル型の薄膜トランジスタを、図 6 の半導体 e、f から P チャネル型の薄膜トランジスタを作製する。

40

**【0101】**

そのため、まず、図示しないレジストマスクを図 6 の半導体 e、f 上に形成し、P(リン)イオンの添加を防止する。この状態で、全面に P イオンの注入をプラズマドーピング法でもって行う。

**【0102】**

この工程において、半導体 i、j には、ヘビードープがされる 114、114'、115、115' の領域とライトドープがされる 117、117' の領域が形成される。これは、残存した酸化珪素膜 109 が半透過なマスクとして機能し、注入されたイオンの一部が

50

そこで遮蔽されるからである。

**【0103】**

次に、半導体e、f上に形成されたレジストマスクを除去する。そして、半導体i、jの上にレジストマスクを形成する。そして、Pチャネル型の薄膜トランジスタを作製するためにB(ボロン)イオンの注入をプラズマドーピング法でもって行う。

**【0104】**

ここで、半導体i、jの上にはレジストマスクが形成されているため、Bイオンの注入を防ぐことができる。

**【0105】**

この工程においては、ヘビードープがされる14、15、15'の領域とライトドープがされる17、17'の領域が形成される。これは、残存した酸化珪素膜9が半透過なマスクとして機能し、注入されたイオンの一部がそこで遮蔽されるからである。

**【0106】**

そしてレーザー光(またはランプを用いた強光)の照射を行うことにより、不純物イオンが注入された領域の活性化を行う。

**【0107】**

こうして、半導体eにチャネル形成領域16とP型のドレイン領域15、低濃度不純物領域17及び半導体fと共にソース領域14が自己整合的に形成される。また、半導体fには、チャネル形成領域16'、P型のドレイン領域15'、低濃度不純物領域17'及び半導体eと共にソース領域14'が自己整合的に形成される。(図6H)

**【0108】**

同様に、半導体iにチャネル形成領域116とN型のソース領域114、ドレイン領域115、低濃度不純物領域117が自己整合的に形成される。また、半導体jには、チャネル形成領域116'、N型のソース領域114'、ドレイン領域115'、低濃度不純物領域117'が自己整合的に形成される。(図8H)

**【0109】**

なお、緻密な陽極酸化膜19の膜厚を2000以上というように厚くした場合、その膜厚でもってチャネル形成領域16、16'、116、116'の外側にオフセットゲート領域を形成することができる。

**【0110】**

本実施例においてもオフセットゲート領域は形成されているが、その寸法が小さいのでその存在による寄与が小さく、また図面が煩雑になるので図中には記載していない。

**【0111】**

なお、緻密な膜質を有する陽極酸化膜を2000以上というように厚く形成するには、200V以上の印加電圧が必要とされるので、再現性や安全性に関して、注意が必要である。

**【0112】**

次に層間絶縁膜27として酸化珪素膜、または窒化珪素膜、またはその積層膜を形成する。層間絶縁膜としては、酸化珪素膜または窒化珪素膜上に樹脂材料でなる層を用いてよい。

**【0113】**

そしてコンタクトホールの形成を行い、半導体eのドレイン電極34と半導体fと共にソース電極30と半導体fのドレイン電極34'の形成を行う。こうして図6Iに示す薄膜トランジスタが完成する。

**【0114】**

同様に、図8Iにおいては、半導体iのドレイン電極35とソース電極36及び、半導体jのドレイン電極35'、ソース電極36'の形成を行う。

**【0115】**

本実施例に示すTFTは、その特性として従来には得られなかつた極めて高いものを得ることができる。

10

20

30

40

50

## 【0116】

例えば、N TFT (Nチャネル型のTFT)で、移動度が $200 \sim 300 (\text{cm}^2/\text{Vs})$ 、S値が $75 \sim 90 (\text{mV}/\text{dec}) (V_D = 1 \text{V})$ という高性能なものが得られる。P TFT (Pチャネル型のTFT)で $120 \sim 180 (\text{cm}^2/\text{Vs})$ 、S値が $75 \sim 100 (\text{mV}/\text{dec}) (V_D = 1 \text{V})$ という高性能なものを得ることができる。なおこの場合のチャネル長(活性層上のゲート電極幅)Lは $0.6 \mu\text{m}$ である。

## 【0117】

そしてこれらのTFTは、駆動信号の電圧が $3.3 \sim 5 \text{V}$ において、リングオシレータレベルで $1 \text{GHz}$ 、シフトレジスタレベルで $100 \text{MHz}$ の動作を行わすことができる。

## 【0118】

また、上述したような特異な結晶構造を有する結晶性珪素膜を利用した薄膜トランジスタは、その結晶構造に起因して短チャネル効果が現れにくいという特徴がある。また基板として絶縁体を利用するので基板の容量の問題がなく、高速動作に適するという特徴もある。

## 【0119】

従来の単結晶シリコンウェハーを利用したMOS型トランジスタにおいては、スケーリング則というものがあった。これは、所定に法則に従ってトランジスタに寸法を小さくすれば、これまた所定の法則に従ってトランジスタの性能が高くなるというものである。

## 【0120】

しかし、近年の微細化大きく進行した状態においては、このスケーリング則に従って、トランジスタの性能を高めることが困難になってきている。

## 【0121】

その一つに短チャネル効果を抑制するためにチャネル長を短くすればするほど、チャネルの横に不純物のドーピングをしたりする細かな工夫が必要になり、作製工程上の困難性が増大するという点を挙げることができる。

## 【0122】

しかし、上述した特異な結晶構造を有した結晶性珪素膜を用いた場合には、必要とする特性を上記のスケーリング則に従わない寸法で得ることができる。

## 【0123】

これは、以下のような事項が要因であると考えられる。

(1) チャネルにおいてキャリアの移動する方向に柱状の結晶体の延在方向を合わせることにより、短チャネル効果が抑制される。

(2) 基板に絶縁体を利用してすることで、容量の問題が大きく抑制される。

(3) ゲート電極にアルミニウムを利用できるので、高速動作に有利である。

## 【0124】

(1)については、以下のように考えることができる。即ち、一つ一つに柱状の結晶構造体は、不活性な結晶粒界により仕切られているが、この結晶粒界部分では、エネルギーにレベルが高いので、キャリアは結晶体の延在方向にその移動が寄生される。また同様な考え方により、ソース及びドレイン領域からのチャネル内部への空乏層の広がりも抑制される。このことが、短チャネル効果の抑制になっていると考えられる。

## 【0125】

上述したスケーリング則に従わない具体的な例としては、以下のような例を挙げることができる。

## 【0126】

例えば、従来にスケーリング則に従えば、ゲート絶縁膜の厚さが $100 \text{ nm}$ でなければならないところ、本明細書で開示するような結晶性珪素膜を用いた場合、ゲート絶縁膜の厚さを $300 \text{ nm}$ として、同じ特性を得ることができる。その結果耐静電気特性を高くできる。

## 【0127】

これは、上述した(1)～(3)に示すような要因であると理解される。

## 【0128】

10

30

40

50

また、ゲイト絶縁膜の膜厚のみではなく、チャネル長に関しても従来のスケーリング則よりも緩い条件（1ランク下の条件）でもって、所定の特性を得ることができる。

【0129】

これは、高速動作が可能な半導体回路を大面積にわたって低コストで作製する場合に有用なことである。

【0130】

なお、本実施例で示したTFTにおいて、チャネル長 $L = 0.35 \mu m$ とすると、駆動できる最高周波数（カットオフ周波数）は、上記のチャネル長 $L = 0.6 \mu m$ のものより約4倍、 $L = 2 \mu m$ のものより、約50倍の高速駆動が期待できる。

【0131】

尚、本実施例は、本発明の一例に過ぎず、この作製方法に限定されるものではない。また、図3、4に示す回路も本発明の一例に過ぎず、本明細書で開示した内容に従うならば特定の回路に限定されるものではない。

【0132】

〔実施例2〕

本実施例は、金属元素による結晶成長にレーザー光の照射を組み合わせた場合の例を示す。

【0133】

本実施例に示す作製工程においては、図5（B）に示す加熱処理の条件を600、8時間として、その後に得られた結晶性珪素膜に対してレーザー光の照射を行う。

【0134】

そして、その後の高温での加熱処理による熱酸化膜の形成は行わない。この場合、最高プロセス温度を600とすることができるので、基板としてガラス基板を利用することができる。

【0135】

〔実施例3〕

本実施例は、図1に示すような位置取りで活性層a～dを形成する場合において、aをNチャネル型の薄膜トランジスタの活性層とし、bをPチャネル型の薄膜トランジスタの活性層とする。そして、2つの薄膜トランジスタを相補型に構成する。

【0136】

こうすることで、Nチャネル型の薄膜トランジスタに移動度を抑える構成とし、Pチャネル型の薄膜トランジスタに移動度を高くする構成とすることができます、結果として、2つの薄膜トランジスタ間の特性差を抑制することができる。

【0137】

〔実施例4〕

本実施例は、実施例1～3で示した構成を逆スタガ型の薄膜トランジスタで構成する。実施例1で示したプレナー型の薄膜トランジスタに変えて、逆スタガ型の薄膜トランジスタとしても、同様の効果を得ることができる。

【0138】

なお、逆スタガ型の薄膜トランジスタのゲート電極として、ゲート電極に耐熱性の高い材料、例えばリンが多量にドープされた多結晶シリコンを利用することは、高性能な薄膜トランジスタを得るために有効である。

【0139】

〔発明の効果〕

以上のように、本明細書に記載の半導体を用いることによって、従来の薄膜トランジスタでは成しえなかつた高性能の回路を作製することが可能になる。

【0140】

また、金属元素を添加した領域からの距離の違いによって、結晶性が異なることを利用することにより、異なった導電性を有する薄膜トランジスタの特性を均一化することが可能となる。

## 【0141】

本明細書で開示した発明は、透過型、反射型のアクティブマトリクス型の液晶表示装置の、アクティブマトリクス回路と同一基板に形成される周辺回路を構成するのみでなく、他にEL(エレクトロルミネセンス)素子を用いた表示装置、その他薄膜トランジスタを用いた種々の回路にて利用することが可能である。

## 【図面の簡単な説明】

- 【図1】 金属元素による結晶化の成長を示す上面図。

- 【図2】 金属元素による結晶化の成長を示す上面図。

- 【図3】 本発明の構成の一つを示すマスクパターン。

- 【図4】 図3の等価回路図。 10

- 【図5】 図3の 1 断面の作製工程図。

- 【図6】 図3の 1 断面の作製工程図。

- 【図7】 図3の 2 断面の作製工程図。

- 【図8】 図3の 2 断面の作製工程図。

## 【符号の説明】

|         |                |    |

|---------|----------------|----|

| 1、1'、1" | 金属元素添加領域       |    |

| 2       | 基板             |    |

| 3       | 下地膜            |    |

| 5       | マスク酸化珪素膜       |    |

| 6       | ニッケル           | 20 |

| 7       | 熱酸化珪素膜         |    |

| 8、9     | ゲイト絶縁膜         |    |

| 10      | レジストマスク        |    |

| 11      | 珪素膜            |    |

| 12、12'  | 結晶性珪素膜         |    |

| 13      | 島状珪素膜          |    |

| 14      | ソース領域          |    |

| 15、15'  | ドレイン領域         |    |

| 16、16'  | チャネル領域         |    |

| 17、17'  | 低濃度不純物領域       | 30 |

| 18      | 多孔質状の陽極酸化膜     |    |

| 19      | 緻密な膜質を有する陽極酸化膜 |    |

| 20      | ゲイト配線          |    |

| 21、21'  | ゲイト配線          |    |

| 22、22'  | ゲイト配線          |    |

| 23、23'  | ゲイト配線          |    |

| 25、25'  | ゲイト配線          |    |

| 27      | 層間絶縁膜          |    |

| 30      | ソース配線          |    |

| 31      | ソース配線          | 40 |

| 32      | ビデオ信号線         |    |

| 33      | ビデオ信号線         |    |

| 34、34'  | 配線             |    |

| 35、35'  | 配線             |    |

| 36、36'  | 配線             |    |

| 37、37'  | 配線             |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【 図 7 】

【 四 8 】

---

フロントページの続き

(51) Int.Cl.<sup>7</sup> F I

H 01 L 27/092

審査官 緋引 隆

(56) 参考文献 特開平06-349735(JP,A)

特開平08-213634(JP,A)

特開平07-297125(JP,A)

(58) 調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 21/20

H01L 21/336

H01L 21/8234

H01L 27/08

H01L 29/786