(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6698369号

(P6698369)

(45) 発行日 令和2年5月27日(2020.5.27)

(24) 登録日 令和2年5月1日(2020.5.1)

(51) Int.Cl.

G09G 3/36 (2006.01)

G09G 3/20 (2006.01)

F 1

G09G 3/36

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

請求項の数 12 (全 26 頁)

(21) 出願番号 特願2016-23425 (P2016-23425)

(22) 出願日 平成28年2月10日 (2016.2.10)

(65) 公開番号 特開2017-142359 (P2017-142359A)

(43) 公開日 平成29年8月17日 (2017.8.17)

審査請求日 平成31年2月6日 (2019.2.6)

(73) 特許権者 308017571

シナプティクス・ジャパン合同会社

東京都中野区中野四丁目10番2号

(74) 代理人 100205350

弁理士 狩野 芳正

(74) 代理人 100117617

弁理士 中尾 圭策

(72) 発明者 坂巻 五郎

東京都中野区中野四丁目10番2号 シナ

プティクス・ディスプレイ・デバイス合同

会社内

(72) 発明者 宮澤 敏

東京都中野区中野四丁目10番2号 シナ

プティクス・ディスプレイ・デバイス合同

会社内

最終頁に続く

(54) 【発明の名称】表示ドライバ及び表示パネルモジュール

## (57) 【特許請求の範囲】

## 【請求項 1】

長尺状の半導体集積回路として形成された表示ドライバであって、

前記表示ドライバの長手方向に沿って規則的に配置された複数の外部出力端子と、

所要の外部出力端子から表示パネルに供給するための表示駆動信号を生成する出力回路

と、

出力モードデータが書換え可能に設定される出力モードレジスタと、

前記出力モードデータに従って、前記表示駆動信号を出力するために前記出力回路が用

いる外部出力端子の配列を、配置ピッチが異なる複数種類の配列の中から選択する制御を行なう制御回路と、

を含み、

前記複数種類の配列は、

前記複数の外部出力端子の全てを前記表示駆動信号の出力に用いる使用端子とする第1配列と、

前記複数の外部出力端子のうちの一部を前記表示駆動信号の出力に用いる使用端子として残りを前記表示駆動信号の出力に用いない不使用端子とする第2配列と

を含み、

前記第1配列において隣接する2つの使用端子の間の前記長手方向のピッチである第1ピッチは、前記第2配列において隣接する2つの使用端子の間の前記長手方向のピッチのうちの最小ピッチである第2ピッチより小さく、

前記第2配列において前記長手方向に隣接する2つの使用端子の間には少なくとも1つの不使用端子が配置されている、

表示ドライバ。

**【請求項2】**

前記出力回路は、画素データを保持するデータレジスタが複数個並列されたラインラッチ回路と、前記ラインラッチ回路が出力する画素データから画素データ単位で前記表示駆動信号を生成して外部出力端子に与える駆動回路と、を含み、

前記制御回路は、前記出力モードデータに従って前記ラインラッチ回路に画素データを逐次書き込む書き込みアドレスの制御と共に、画素データが書き込まれた前記複数のデータレジスタの出力を並列的に駆動回路に出力する出力制御を行なう、

請求項1に記載の表示ドライバ。

**【請求項3】**

前記データレジスタは複数個の画素の画素データを一単位として保持し、

前記駆動回路は、前記データレジスタが出力する複数個の画素の画素データに対して画素データ単位で対応する駆動信号を時分割で出力する、

請求項2に記載の表示ドライバ。

**【請求項4】**

前記制御回路は、前記出力モードデータを解読して、前記書き込みアドレスの制御及び前記出力制御のための制御信号を生成するプログラムシーケンス制御ロジックを有する、

請求項2又は3に記載の表示ドライバ。

**【請求項5】**

前記第2配列において隣接する2つの使用端子の間のピッチは、前記第2ピッチと、前記第2ピッチより大きい第3ピッチとを含む

請求項1乃至4のいずれか1項に記載の表示ドライバ。

**【請求項6】**

前記第2配列において隣接する2つの使用端子の間のピッチは、前記第2ピッチより大きく前記第3ピッチより小さい第4ピッチをさらに含む

請求項5に記載の表示ドライバ。

**【請求項7】**

前記第2配列の使用端子は、

前記第2配列の長手方向両端の少なくとも一方に配置され、前記第2ピッチを挟んで隣接する2つの使用端子と、

前記第2配列の中央部に配置され、前記第3ピッチを挟んで隣接する2つの使用端子とを含む、

請求項5又は6に記載の表示ドライバ。

**【請求項8】**

表示素子がマトリクス配置された表示パネルと、

長尺状の半導体集積回路として形成された表示ドライバと、を有する表示パネルモジュールであつて、

前記表示ドライバは、当該表示ドライバの長手方向に沿って規則的に配置された複数の外部出力端子と、

所要の外部出力端子から前記表示パネルに供給するための表示駆動信号を生成する出力回路と、

出力モードデータが書換え可能に設定される出力モードレジスタと、

前記出力モードレジスタに設定された前記出力モードデータに従って、前記表示駆動信号を出力するために前記出力回路が用いる外部出力端子の配列を、配置ピッチが異なる複数種類の配列の中から選択する制御を行なう制御回路と、を含み、

前記複数種類の配列は、

前記複数の外部出力端子の全てを前記表示駆動信号の出力に用いる使用端子とする第1配列と、

10

20

30

40

50

前記複数の外部出力端子のうちの一部を前記表示駆動信号の出力に用いる使用端子として残りを前記表示駆動信号の出力に用いない不使用の端子とする第2配列とを含み、

前記第1配列において隣接する2つの使用端子の間の前記長手方向のピッチである第1ピッチは、前記第2配列において隣接する2つの使用端子の間の前記長手方向のピッチのうちの最小ピッチである第2ピッチより小さく、

前記第2配列において前記長手方向に隣接する2つの使用端子の間には少なくとも1つの不使用端子が配置されている、

表示パネルモジュール。

【請求項9】

10

前記第2配列において隣接する2つの使用端子の間のピッチは、前記第2ピッチと、前記第2ピッチより大きい第3ピッチとを含む

請求項8に記載の表示パネルモジュール。

【請求項10】

前記第2配列において隣接する2つの使用端子の間のピッチは、前記第2ピッチより大きく前記第3ピッチより小さい第4ピッチをさらに含む

請求項9に記載の表示パネルモジュール。

【請求項11】

前記第2配列の使用端子は、

前記第2配列の長手方向両端の少なくとも一方に配置され、前記第2ピッチを挟んで隣接する2つの使用端子と、

前記第2配列の中央部に配置され、前記第3ピッチを挟んで隣接する2つの使用端子とを含む、

請求項9又は10に記載の表示パネルモジュール。

【請求項12】

20

前記複数の外部出力端子を前記表示パネルに接続する配線パターンをさらに具備し、

前記配線パターンの配列ピッチは、前記表示駆動信号を出力するために前記出力回路が用いる外部出力端子のピッチに対して整数倍以外のピッチである、

請求項8乃至11のいずれか一項に記載の表示パネルモジュール。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示ドライバ及び表示パネルモジュールに関し、COG (Chip On Glass) 実装及びCOF (Chip On Film) 実装の何れにも適用可能とする技術に関し、例えば液晶表示パネルを表示駆動する表示ドライバに適用して有効な技術に関する。

【背景技術】

【0002】

液晶表示パネル等の表示パネルはガラス基板上に表示素子が形成されると共に、表示素子に駆動信号を供給する信号配線が形成される。ガラス基板に高精度で形成可能な信号配線ピッチはフレキシブルプリント配線基板 (FPC) などのフィルム上に形成される配線ピッチに比べて狭ピッチ化が可能である。

【0003】

液晶表示パネル等の表示パネルの表示駆動に用いる表示ドライバの実装形態としてCOG実装とCOF実装がある。

【0004】

COG実装は表示素子や透明電極が形成されるガラス基板上に直接ベアチップ (半導体チップ状) の表示ドライバを実装する形態である。この実装形態では表示ドライバにとって配線負荷が小さくなるので高速動作に適する。例えば特許文献1に例示されたCOG実

40

50

装に好適な表示駆動用の半導体チップでは、チップの長手方向に2列で駆動信号の外部出力端子列が配置され、列間で外部出力端子を大凡半ピッチずらすことにより、後列の外部出力端は前列の外部出力端子間を通って表示パネルの信号回線に接続される。このようなく、COG実装される表示ドライバの出力端子の配列、換言すれば、ドライバの出力端子が接続されるガラス基板上の配線パターンの配線ピッチは、狭ピッチ化される傾向にある。

#### 【0005】

COF実装は例えばポリイミドから成るフィルム上の配線回路基板上の配線パターンに半導体チップ状の表示ドライバを実装する形態である。フィルム上に形成される配線パターンの配線ピッチはガラス基板上に形成される配線パターンの配線ピッチに比べて大きくならざるを得ない。COF実施される表示駆動用の半導体チップが特許文献2に例示される。

10

#### 【0006】

したがって、FHD(Full High Definition)のような高解像度の表示パネルの表示ドライバにはCOG実装が適用され、表示パネルの電極配線パターンのピッチが比較的広くされたVGA(Video Graphics Array)などの低解像度表示パネルの表示ドライバにはCOF実装が適用されることが多い。

#### 【先行技術文献】

##### 【特許文献】

##### 【0007】

【特許文献1】特開2008-145477号公報

20

【特許文献2】特開2006-13421号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

従来の技術によれば、表示パネルの電極配線パターンのピッチが比較的狭くされた高解像度の表示パネルに最適化された表示ドライバは、電極配線パターンのピッチが比較的広くされた低解像度の表示パネルには適用し難い。逆の場合も同様である。COF実装に適用する表示ドライバの外部出力端子である実装用バンプのピッチは例えば20ミクロン以上必要とされるのに対し、COG実装に適用する表示ドライバの実装用バンプのピッチは例えば18ミクロン以下になっているからである。今日、液晶表示パネル等の表示パネルはスマートフォンなどに利用される小型化且つ高精細化されたFHDサイズから、時計や自動車のインパネ(instrument panel)に設けられる計器盤の盤面などに利用される低解像度のサイズまで多岐に亘り、夫々に専用の表示ドライバを用いるのは表示パネルモジュールのコスト低減に寄与しない。

30

#### 【0009】

本発明の目的は、駆動信号を受ける信号配線のピッチが相違する表示パネルに対しても、また、COF実装とCOG実装の何れに対しても、共用可能な表示ドライバを提供することにある。更には、表示パネルモジュールのコスト低減に寄与することを目的とする。

#### 【0010】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

40

#### 【課題を解決するための手段】

#### 【0011】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。尚、本項において括弧内に記載した図面内参照符号などは理解を容易化するための一例である。

#### 【0012】

[1] <表示パネルの電極パッド列の配置ピッチに応じて外部出力端子の配列が選択可能>

長尺状の半導体集積回路として形成された表示ドライバ(1)は、前記表示ドライバの

50

長手方向に沿って規則的に配置された複数の外部出力端子 ( S<sub>1</sub> ~ S<sub>n</sub> ) と、所要の外部出力端子から表示パネル ( 6 , 7 ) に供給するための表示駆動信号を生成する出力回路 ( 46 ) と、出力モードデータ ( M d a t a ) が書換え可能に設定される出力モードレジスタ ( 60 ) と、前記出力モードレジスタに設定された前記出力モードデータに従って、前記表示駆動信号を出力するために前記出力回路が用いる外部出力端子の配列を、配置ピッチが異なる複数種類の配列の中から選択する制御を行なう制御回路 ( 43 ) と、を含む。見方を変えれば前記制御回路は外部出力端子の配列方向に従って前記出力回路による表示データの出力位置 ( 或いは書き込み位置及び出力位置 ) を可変とすることによって、出力に用いる外部出力端子の配列を配置ピッチが異なる複数種類の配列の中から選択可能にする。

10

#### 【 0 0 1 3 】

これによれば、表示パネルを駆動するとき表示駆動信号の出力に用いる外部出力端子の配列として配置ピッチが異なる複数種類の配列の中から一つの配列を選択可能であるから、この表示ドライバを実装するパッドのピッチに合うように表示駆動信号の出力に用いる外部出力端子の配列を配置ピッチの異なる複数種類の配列の中から選択すればよい。したがって、上記表示ドライバは、表示ドライバから駆動信号を受ける信号配線のピッチが相違する表示パネルに対しても、また、実装されるバンプのピッチが相違される C O F 実装と C O G 実装の何れに対しても、共用可能である。

#### 【 0 0 1 4 】

##### 〔 2 〕 < ラインラッチ回路と駆動回路 >

20

項 1において、前記出力回路は、画素データを保持するデータレジスタ ( R E G ) が複数個並列されたラインラッチ回路 ( 44 ) と、前記ラインラッチ回路が出力する画素データから画素データ単位で表示駆動信号を生成して外部出力端子に与える駆動回路 ( 45 ) と、を含む。前記制御回路は、前記出力モードデータに従って前記ラインラッチ回路に画素データを逐次書き込む書き込みアドレスの制御と共に、画素データが書き込まれた複数のデータレジスタの出力を並列的に駆動回路に出力する出力制御を行なう。

#### 【 0 0 1 5 】

これによれば、制御回路による前記アドレス制御と出力制御によって、外部出力端子の配列を配置ピッチの異なる複数種類の配列の中から選択する制御を容易に実現することができる。

30

#### 【 0 0 1 6 】

##### 〔 3 〕 < 1 個の外部出力端子を複数画素の駆動に共用 >

項 2において、前記データレジスタは複数個の画素の画素データ ( Di\_Pn\_r, Di\_Pn\_g, Di\_Pn\_b, Di\_Pn+1\_r, Pn+1\_g, Pn+1\_b, ) を一単位として保持する。前記駆動回路は、前記データレジスタが出力する複数個の画素の画素データに対して画素データ単位で対応する駆動信号を時分割で出力する。

#### 【 0 0 1 7 】

これによれば、例えば 1 個のデータレジスタが n 個の画素の画素データを保持する場合に 1 個の外部出力端子が n 個の画素に時分割で表示駆動信号を供給するのに共用される。これは、高解像度の表示パネルに配置された表示素子の信号線を複数本単位でセレクタを介して 1 本の配線パターンに引き出して表示ドライバの外部出力端子に接続する構成を可能にするものであり、表示パネルの高解像度化に対して表示ドライバの外部出力端子の配列ピッチを実装可能なピッチに留めておくことを可能にする。

40

#### 【 0 0 1 8 】

##### 〔 4 〕 < シーケンス制御ロジック >

項 2において、前記制御回路は、前記出力モードレジスタに設定された出力モードデータを解読して、前記書き込みアドレスの制御及び前記出力制御のための制御信号を生成するプログラムシーケンス制御ロジック ( 61 , 62 ) を有する。

#### 【 0 0 1 9 】

これにより、ハードワイヤードロジックに比べて制御回路の回路規模を縮小でき、また

50

、制御機能の設定・変更も容易になる。

**【0020】**

〔5〕<複数の配列形態は出力に用いられる外部出力端子の隣接する端子間ピッチが相違>

項1において、前記制御回路が選択可能な前記複数種類の配列は、前記複数の外部出力端子の配列中で駆動信号の出力に用いられる複数の外部出力端子の隣接する端子間に割り当てられるピッチの状態が相違され、駆動信号の出力に用いられる複数の外部出力端子の配置がその配列の長手方向両端を基点に中央部に向って配置される配列を有する。

**【0021】**

これによれば、上記選択可能な配列間で、外部出力端子の隣接する端子間に割り当てられるピッチの状態に相違があるということは、表示ドライバを実装する実装相手の配線パターンの配列ピッチが外部出力端子の物理的配置のピッチに対して整数倍以外のピッチであっても選択可能な配列とすることができる意味し、上記選択可能な配列のバリエーションが増える。また、外部出力端子配列の両端から必要個数の外部出力端子を用いることは、表示ドライバを実装する実装相手の配線パターンの傾きが外部出力端子の配列方向に対して大きくなるように作用し、前記配線パターンの配線ピッチが極端に小さくならないようとする。

**【0022】**

〔6〕<複数の配列形態は駆動信号の出力に用いられる複数の外部出力端子の数が相違>

項5において、前記制御回路が選択可能な前記複数種類の配列は、前記複数の外部出力端子の配列中で駆動信号の出力に用いられる複数の外部出力端子の数が相違され、駆動信号の出力に用いられる複数の外部出力端子の配置がその配列の長手方向両端を基点に中央部に向って配置される配列を有する。

**【0023】**

これによれば、上記選択可能な配列のバリエーションが更に増える。

**【0024】**

〔7〕<表示パネルの電極パッド列の配置ピッチに応じて外部出力端子の配列が選択可能>

長尺状の半導体集積回路として形成され表示パネルの表示素子に表示駆動信号を出力するための表示ドライバ(1)は、前記表示ドライバの長手方向に沿って規則的に配置された複数の外部出力端子(S1～Sn)と、所要の外部出力端子から表示パネルに供給するための表示駆動信号を生成する出力回路(46)と、ホストインターフェース回路(40)と、前記ホストインターフェース回路から制御データが入力されるレジスタ回路(41)と、前記レジスタ回路にセットされた制御データに基づいて制御信号を生成する制御回路‘43)と、を含む。前記レジスタ回路は、出力モードデータ(Mdata)が書換え可能に設定される出力モードレジスタ(60)を有する。前記制御回路は、前記出力モードレジスタに設定された前記出力モードデータに従って、前記表示駆動信号を出力するために前記出力回路が用いる外部出力端子の配列を、配置ピッチが異なる複数種類配列の中から選択する制御を行なう。前記制御回路が選択可能な前記複数種類の配列として、前記複数の外部出力端子の配列中で駆動信号の出力に用いられる複数の外部出力端子の隣接する端子間に割り当てられるピッチの状態が相違される配列を有する。

**【0025】**

これによれば、表示パネルを駆動するとき表示駆動信号の出力に用いる外部出力端子の配列として配置ピッチが異なる複数種類の配列の中から一つの配列を選択可能であるから、この表示ドライバを実装するパッドのピッチに合うように表示駆動信号の出力に用いる外部出力端子の配列を配置ピッチの異なる複数種類の配列の中から選択すればよい。したがって、上記表示ドライバは、表示ドライバから駆動信号を受ける信号配線のピッチが相違する表示パネルに対しても、また、実装されるバンプのピッチが相違されるCOF実装とCOG実装の何れに対しても、共用可能である。更に、上記選択可能な配列間で、外部

10

20

30

40

50

出力端子の隣接する端子間に割り当てられるピッチの状態に相違があるということは、表示ドライバを実装する実装相手の配線パターンの配列ピッチが外部出力端子の物理的配置のピッチに対して整数倍以外のピッチであっても選択可能な配列とすることができる意味し、上記選択可能な配列のバリエーションが増える。

**【0026】**

〔8〕<複数の配列形態は駆動信号の出力に用いられる複数の外部出力端子の数が相違>

項7において、前記制御回路が選択可能な前記複数種類の配列として、前記複数の外部出力端子の配列中で駆動信号の出力に用いられる複数の外部出力端子の数が相違される配列を更に有する。 10

**【0027】**

これによれば、上記選択可能な配列のバリエーションが更に増える。

**【0028】**

〔9〕<外部出力端子配列の両端から必要個数の外部出力端子を使用>

項7において、前記制御回路が選択可能な前記複数種類の配列は、前記駆動信号の出力に用いられる複数の外部出力端子の配置がその配列の長手方向両端を基点に中央部に向って配置される配列を有する。 20

**【0029】**

これによれば、外部出力端子配列の両端から必要個数の外部出力端子を用いることは、表示ドライバを実装する実装相手の配線パターンの傾きが外部出力端子の配列方向に対して大きくなるように作用し、前記配線パターンの配線ピッチが極端に小さくならないよう 20

**【0030】**

〔10〕<ラインラッチ回路と駆動回路>

項7において、前記出力回路は、画素データを保持するデータレジスタが複数個並列されたラインラッチ回路(44)と、前記ラインラッチ回路が出力する画素データから画素データ単位で表示駆動信号を生成して外部出力端子に与える駆動回路(45)と、を含む。前記制御回路は、前記出力モードデータに従って前記ラインラッチ回路に画素データを逐次書き込む書き込みアドレスの制御と共に、画素データが書き込まれた複数のデータレジスタの出力を並列的に駆動回路に出力する出力制御を行なう。 30

**【0031】**

これによれば、制御回路による前記アドレス制御と出力制御によって、外部出力端子の配列を配置ピッチの異なる複数種類の配列の中から選択する制御を容易に実現することができる。

**【0032】**

〔11〕<1個の外部出力端子を複数画素の駆動に共用>

項10において、前記データレジスタは複数個の画素の画素データを一単位として保持する。前記駆動回路は、前記データレジスタが出力する複数個の画素の画素データに対して画素データ単位で対応する駆動信号を時分割で出力する。 40

**【0033】**

これによれば、例えば1個のデータレジスタがn個の画素の画素データを保持する場合に1個の外部出力端子がn個の画素に時分割で表示駆動信号を供給するのに共用される。これは、高解像度の表示パネルに配置された表示素子の信号線を複数本単位でセレクタを介して1本の配線パターンに引き出して表示ドライバの外部出力端子に接続する構成を可能にするものであり、表示パネルの高解像度化に対して表示ドライバの外部出力端子の配列ピッチを実装可能なピッチに留めておくことを可能にする。

**【0034】**

〔12〕<表示パネルの電極パッド列の配置ピッチに応じて外部出力端子の配列が選択可能>

表示パネルモジュール(2,3)は、表示素子がマトリクス配置された表示パネル(6) 50

, 7)と、長尺状の半導体集積回路として形成され、前記表示パネルに表示駆動信号を供給する表示ドライバ(1)と、を有する。前記表示ドライバは、当該表示ドライバの長手方向に沿って規則的に配置された複数の外部出力端子(S1~S<sub>n</sub>)と、所要の外部出力端子から表示パネルに供給するための表示駆動信号を生成する出力回路(46)と、出力モードデータ(M data)が書換え可能に設定される出力モードレジスタ(60)と、前記出力モードレジスタに設定された前記出力モードデータに従って、前記表示駆動信号を出力するために前記出力回路が用いる外部出力端子の配列を、配置ピッチが異なる複数種類の配列の中から選択する制御を行なう制御回路(43)と、を含む。前記制御回路が選択可能な前記複数種類の配列として、前記複数の外部出力端子の配列中で駆動信号の出力に用いられる複数の外部出力端子の隣接する端子間に割り当てられるピッチの状態が相違される配列を有する。

#### 【0035】

これによれば、表示パネルモジュールは、表示ドライバから駆動信号を受ける信号配線のピッチが相違する表示パネルに対しても、また、実装されるバンプのピッチが相違されるCOF実装とCOG実装の何れに対しても、共用可能な上記表示ドライバを用いて構成されるから、表示パネルモジュールのコスト低減を実現することができる。

#### 【0036】

[13] <複数の配列形態は駆動信号の出力に用いられる複数の外部出力端子の数が相違>

項12において、前記制御回路が選択可能な前記複数種類の配列として、前記複数の外部出力端子の配列中で駆動信号の出力に用いられる複数の外部出力端子の数が相違される配列を更に有する。

#### 【0037】

これによれば、上記表示ドライバに共用範囲が更に広がり、コスト低減可能な表示パネルモジュールの種類を更に拡げることができる。

#### 【0038】

[14] <外部出力端子配列の両端から必要個数の外部出力端子を使用>

項12において、前記制御回路が選択可能な前記複数種類の配列は、前記駆動信号の出力に用いられる複数の外部出力端子の配置がその配列の長手方向両端を基点に中央部に向って配置される配列を有する。

#### 【0039】

これによれば、外部出力端子配列の両端から必要個数の外部出力端子を用いることは、表示ドライバを実装する実装相手の配線パターンの傾きが外部出力端子の配列方向に対して大きくなるように作用し、前記配線パターンの配線ピッチが極端に小さくならないようになる。

#### 【0040】

[15] <COG形態による表示ドライバの実装>

項12において、前記表示ドライバは前記表示パネル(6)のガラス基板(9)にチップ・オン・グラス(COG)形態で実装されて、前記外部出力端子が前記表示パネルの前記ガラス基板上の配線パターン(12)に直結される。

#### 【0041】

これによれば、高解像度の表示パネルにCOG形態で表示ドライバを実装して高解像度の表示パネルモジュールを構成することができる。

#### 【0042】

[16] <COF形態による表示ドライバの実装>

項12において、前記表示ドライバは表示パネル(7)に接続されたフレキシブル配線基板(5)にチップ・オン・フィルム(COF)形態で実装され、前記外部出力端子が前記フレキシブル配線基板の配線(13)に直結されて前記表示パネルの前記ガラス基板上の配線パターンに接続される。

#### 【0043】

10

20

30

40

50

これによれば、低解像度の表示パネルに接続するフレキシブル配線基板にC O F形態で表示ドライバを実装して低解像度の表示パネルモジュールを構成することができる。

#### 【0044】

##### 〔17〕<ラインラッチ回路と駆動回路>

項12において、前記出力回路は、画素データを保持するデータレジスタが複数個並列されたラインラッチ回路(44)と、前記ラインラッチ回路が出力する画素データから画素データ単位で表示駆動信号を生成して外部出力端子に与える駆動回路(45)と、を含む。前記制御回路は、前記出力モードデータに従って前記ラインラッチ回路に画素データを逐次書き込む書き込みアドレスの制御と共に、画素データが書き込まれた複数のデータレジスタの出力を並列的に駆動回路に出力する出力制御を行なう。

10

#### 【0045】

これによれば、制御回路による前記アドレス制御と出力制御によって、外部出力端子の配列を配置ピッチの異なる複数種類の配列の中から選択する制御を容易に実現することができる。

#### 【0046】

##### 〔18〕<1個の外部出力端子を複数画素の駆動に共用>

項17において、前記データレジスタは複数個の画素の画素データ(Di\_Pn\_r, Di\_Pn\_g, Di\_Pn\_b, Di\_Pn+1\_r, Pn+1\_g, Pn+1\_b,)を一単位として保持する。前記駆動回路は、前記データレジスタが出力する複数個の画素の画素データに対して画素データ単位で対応する駆動信号を時分割で出力する。前記表示パネルは、前記駆動回路が時分割で順次出力する駆動信号を対応する複数個の画素の画素データ単位で対応する表示素子の信号線に供給する選択回路(72)を有する。前記制御回路は、前記駆動回路による駆動信号の時分割出力に同期して、当該時分割出力される駆動信号に応ずる表示素子の信号線を前記選択回路に選択させる選択制御を行なう。

20

#### 【0047】

これによれば、表示パネルの表示素子の信号線ピッチを表示ドライバの外部出力端子の最小配列ピッチよりも格段に小さくすることができ、スマートフォンなどの小型の機器に搭載する表示パネルの高解像度化の促進に寄与することができる。

#### 【発明の効果】

#### 【0048】

30

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

#### 【0049】

すなわち、駆動信号の外部信号電極のピッチが相違する表示パネルに対しても、また、C O F実装とC O G実装の何れに対しても、共用可能な表示ドライバを提供することができる。更には、表示パネルモジュールのコストを低減することができる。

#### 【図面の簡単な説明】

#### 【0050】

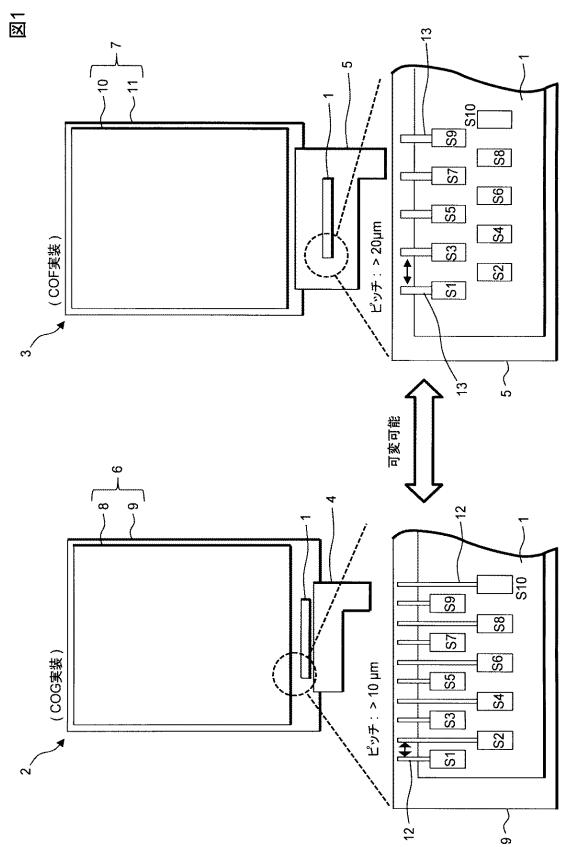

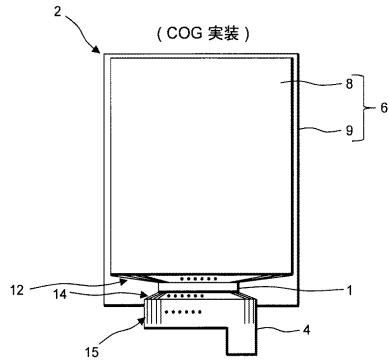

【図1】図1は同じ表示ドライバをC O G実装形態とC O F実装形態の何れにも可変可能に適用した適用例を示す説明図である。

40

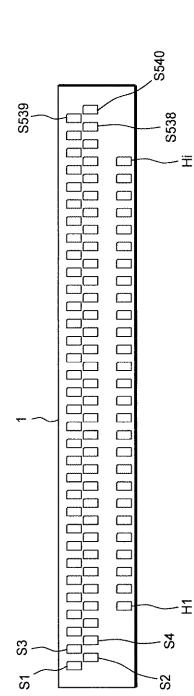

【図2】図2は本発明の一実施の形態に係る表示ドライバの外観を例示する平面図である。

【図3】図3は表示ドライバを適用したスマートフォンを示す説明図である。

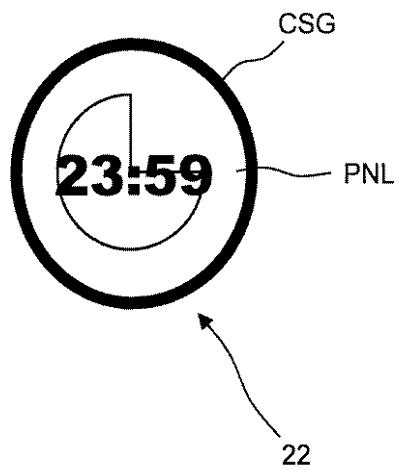

【図4】図4は表示ドライバを適用したスマートウォッチを示す説明図である。

【図5】図5は表示ドライバを適用したフリーフォームディスプレイを示す説明図である。

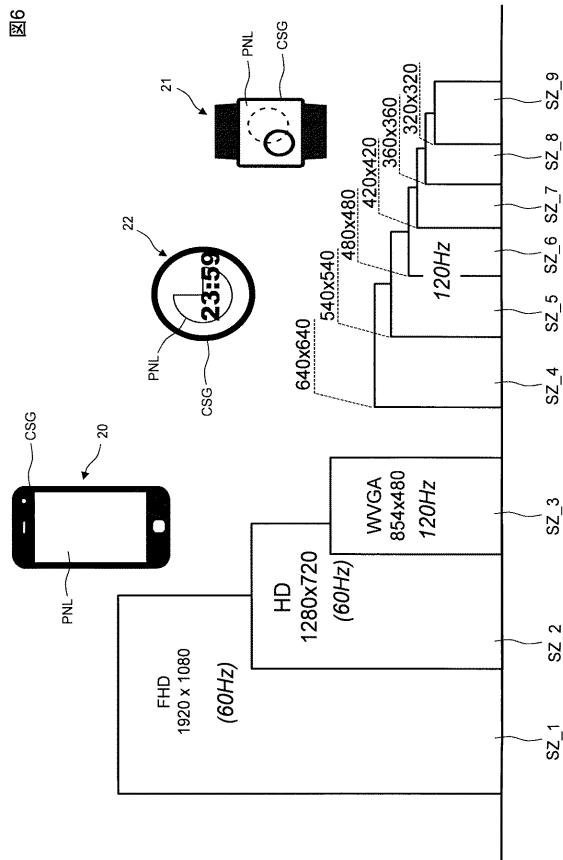

【図6】図6はスマートフォン、スマートウォッチ及びフリーフォームディスプレイ等に用いる表示パネルの代表的な解像度を例示する説明図である。

【図7】図7はC O G実装に適用される表示パネルを用いた表示パネルモジュールを例示する平面図である。

50

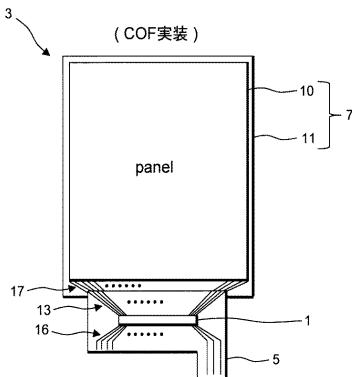

【図8】図8はC O F実装に適用される表示パネルを用いた表示パネルモジュールを例示する平面図である。

【図9】図9は図7及び図8に用いる表示パネルの構成を回路的に例示した回路図である。

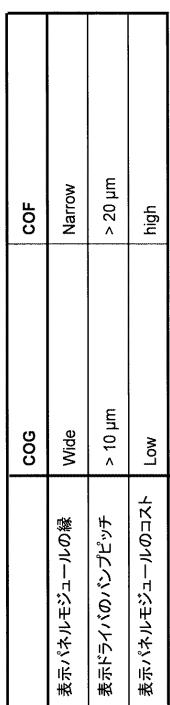

【図10】図10はC O G実装とC O F実装の主な相違点を対比して例示した説明図である。

【図11】図11は各種解像度の表示パネルに対する外部出力端子の利用形態をC O G実装とC O F実装に大別して例示した説明図である。

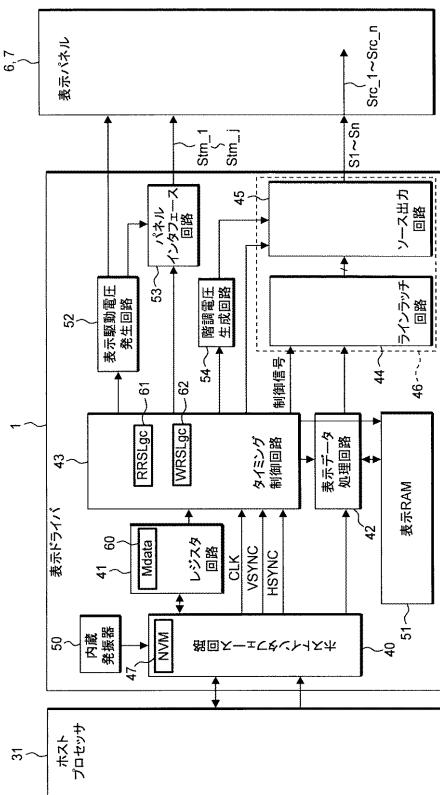

【図12】図12は表示ドライバの構成が例示するブロック図である。

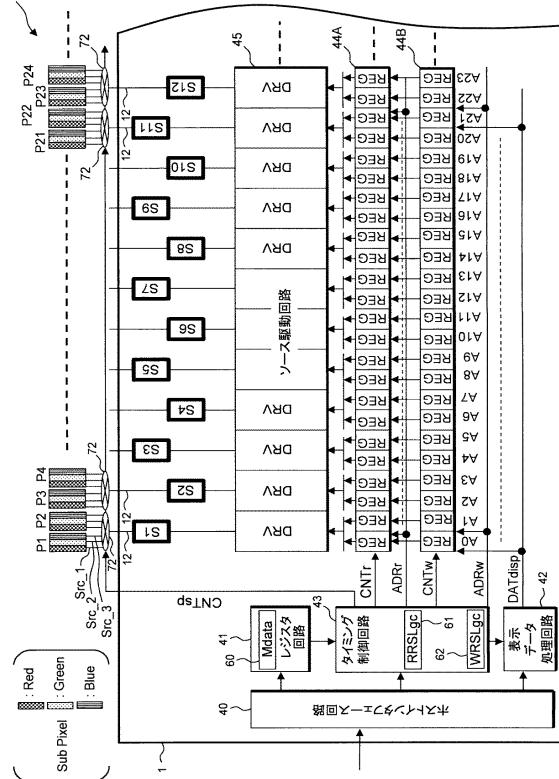

【図13】図13は解像度がF H Dの表示パネルに表示ドライバをC O G実装した状態における出力回路の詳細を例示するブロック図である。10

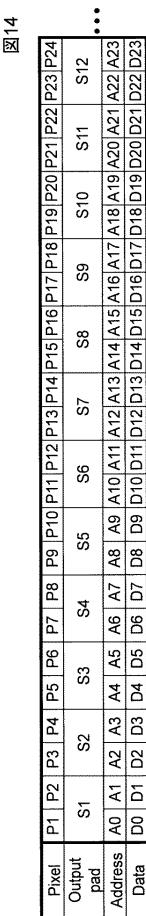

【図14】図14は図13における画素と、その出力に用いる外部出力端子と、画素データとそれを保持するレジスタR E Gのアドレスとの関係を示す説明図である。

【図15】図15は3 2ビット単位の表示データのデータ列として各データが対応する1画素分の3個のR G Bの単位表示データから成るデータ構造を例示する説明図である。

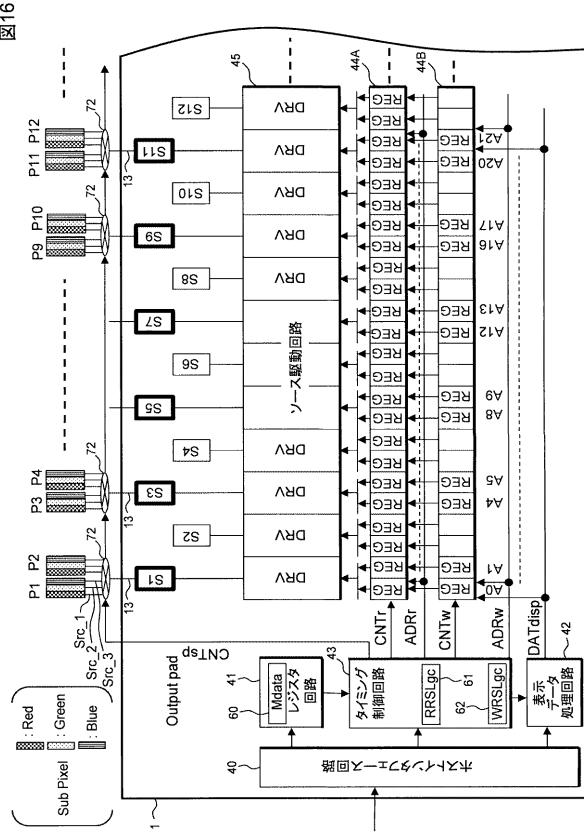

【図16】図16はモードデータによってC O F実装のW V G Aが指定された場合に応ずる外部出力端子の接続形態を例示するブロック図である。

【図17】図17は図16における画素と、その出力に用いる外部出力端子と、画素データとそれを保持するレジスタR E Gのアドレスとの関係を示す説明図である。

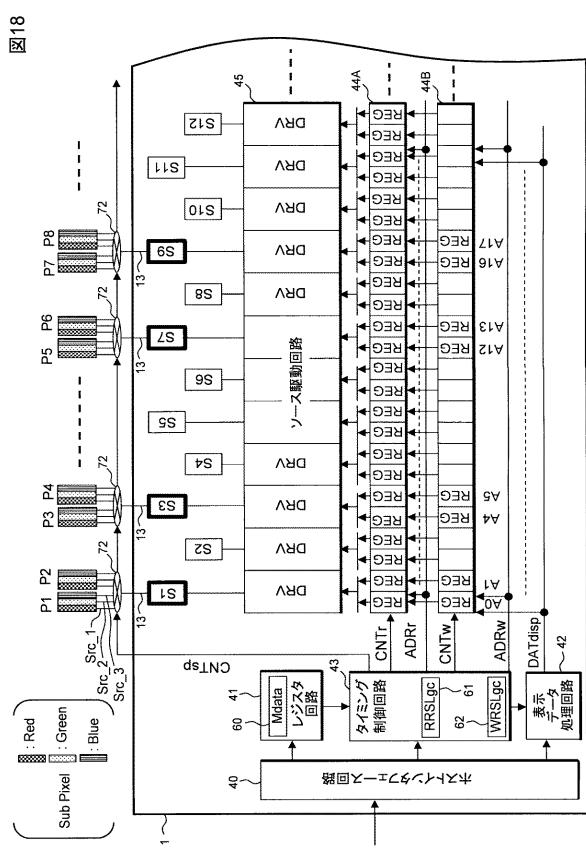

【図18】図18はパネルインターフェース用F P C配線のピッチが上段の端子配列ピッチから僅かにずれているフレキシブル配線基板を使用する場合に所定個数に1個の割合で外部出力端子を不使用にして接続することによってピッチの誤差を吸収する実装形態における外部出力端子の接続形態を例示するブロック図である。20

【図19】図19は図18における画素と、その出力に用いる外部出力端子と、画素データとそれを保持するレジスタR E Gのアドレスとの関係を示す説明図である。

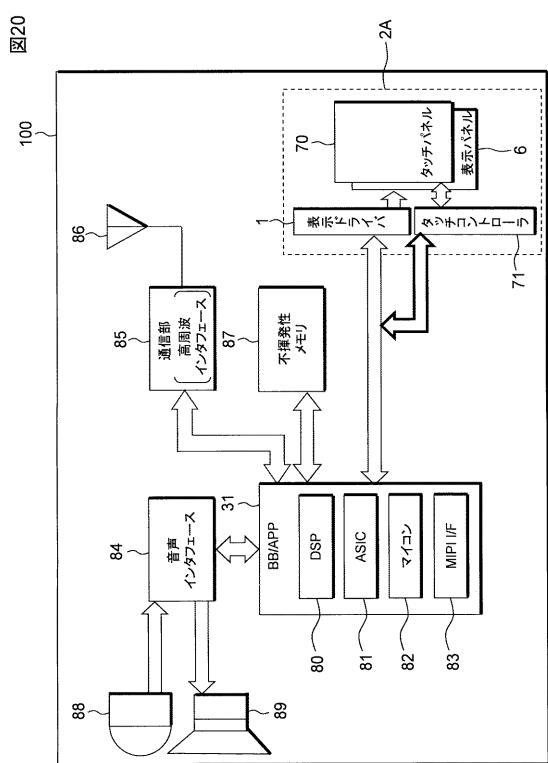

【図20】図20は表示パネルモジュールを用いた電子機器が例示するブロック図である。

#### 【発明を実施するための形態】

##### 【0 0 5 1】

図2には本発明の一実施の形態に係る表示ドライバの外観が例示される。同図に示される表示ドライバ1は長尺状の半導体集積回路として形成され、例えば単結晶シリコン基板に公知のC M O S集積回路製造技術によって形成される。この表示ドライバ1は、所謂ベアチップ又はペレットと称される形態を有し、前記表示ドライバ1の表面には一方の長手辺側にその長手方向に沿って複数の外部出力端子S 1 ~ S nが規則的に配置され、他方の長手辺側にその長手方向に沿って複数のホストインターフェース端子H 1 ~ H iが配置される。図ではn = 5 4 0を一例とする。外部出力端子S 1 ~ S nは表示パネルを駆動する駆動信号の出力端子である。表示ドライバ1は表示パネルにタイミング信号などその他の信号も出力するが、その他の信号を出力する外部出力端子について、ここでは図示を省略する。30

##### 【0 0 5 2】

表示ドライバ1は図3のスマートフォン2 0、図4のスマートウォッチ2 1、及び図5のフリーフォームディスプレイ2 2等における表示パネルP N Lの駆動に兼用される。表示パネルP N Lと表示ドライバ1はその他電子機器と共にケーシングC S Gに収容されている。表示パネルP N Lのサイズはスマートフォン2 0やスマートウォッチ2 1などの適用製品の大きさと、表示に必要な解像度に応じて異なる。

##### 【0 0 5 3】

スマートフォン2 0、スマートウォッチ2 1、及びフリーフォームディスプレイ2 2等に用いる表示パネルの代表的な解像度として図6に示される解像度がある。例えばスマートフォン2 0に必要とされる解像度は図6のR S L\_1で示される1 9 2 0 × 1 0 8 0画素のF H Dサイズ、R S L\_2で示される1 2 8 0 × 7 2 0画素のH Dサイズ、又はR S

10

20

30

40

50

L\_3で示される854×480画素のW V G Aサイズである。スマートウォッチ21やフリーフォームディスプレイ22には、例えばR S L\_4で示される640×640画素のサイズ、R S L\_5で示される540×540画素のサイズ、R S L\_6で示される480×480画素のサイズ、R S L\_7で示される420×420画素のサイズ、R S L\_8で示される360×360画素のサイズ、R S L\_9で示される320×320画素のサイズ等が適用される。

#### 【0054】

各種解像度の表示パネルに対する表示ドライバ1の搭載形態は図7のC O G実装と図8のC O F実装に大別される。特に制限されないが、各図は液晶を用いた表示パネルを一例とする。

10

#### 【0055】

図7にはC O G実装に適用される表示パネル6（表示パネルP N Lの一例）が例示される。表示パネル6は夫々ガラス基板であるアレイ基板9とフィルタ基板8の間には複数本の透明電極が直交方向に配置され、交差位置に液晶を挟んで表示素子が形成される。透明電極の材料にはインジウムとスズの酸化物であるI T O（Indium-Tin-oxide）などが用いられる。この例ではアレイ基板上9の配線パターンは全てI T Oを用いた透明配線若しくは透明電極とされる。フィルタ基板8には表示素子の列毎に順次R G Bのカラーフィルタが形成され、R G B 3個の表示素子で1個の画素（ピクセル）を構成し、R G B夫々の表示素子はサブ画素（ピクセル）を構成する。夫々図示はしないが、表示素子の選択端子に行単位で接続する透明電極はゲート電極、表示素子のデータ入力端子に列単位で接続する透明電極はソース電極である。アレイ基板9には表示ドライバ1を実装するための配線パターンが形成される。この配線パターンは表示パネルの解像度に応じてそのソース電極を表示ドライバ1の外部出力端子S 1～S nの全部又は一部に接続する配線パターン（以下単に駆動用I T O配線とも記す）12と、表示ドライバ1のホストインタフェース端子H 1～H iに接続する配線パターン（以下単にホストインタフェース用I T O配線とも記す）14を有する。表示ドライバ1は外部出力端子S 1～S nとホストインタフェース端子H 1～H iを下に向けて対応する駆動用I T O配線12の基端部の上と、ホストインタフェース用I T O配線14の一端部の上に載置して例えば異方性導電膜を用いた圧着で固定することによって実装される。ホストインタフェース用I T O配線14の他端部はF P Cで構成されたインタフェースコネクタ4のF P C配線15に例えば異方性導電膜を用いて圧着で結合され、表示ドライバ1はインタフェースコネクタ4を介してホスト装置に接続可能にされる。駆動用I T O配線12はソース電極と一対一対応であっても良いが、ソース電極の数が多くなる高解像度の表示パネルの場合には複数本のソース電極をセレクタを介して駆動用I T O配線12に接続可能とすることが得策であり、それによって表示ドライバ1が長くなり過ぎないようにすることができる。

20

#### 【0056】

図8にはC O F実装に適用される表示パネル7（表示パネルP N Lの別の例）が例示される。表示パネル7も同様であって夫々ガラス基板であるアレイ基板11とフィルタ基板10の間には複数本の透明電極が直交方向に配置され、交差位置に液晶を挟んで表示素子が形成される。フィルタ基板10には表示素子の列毎に順次R G Bのカラーフィルタが形成され、R G B 3個の表示素子で1個の画素（ピクセル）を構成し、R G B夫々の表示素子はサブ画素（ピクセル）を構成する。夫々図示はしないが、表示素子の選択端子に行単位で接続する透明電極はゲート電極、表示素子のデータ入力端子に列単位で接続する透明電極はソース電極である。図8のC O F実装の場合には表示ドライバ1がフレキシブル配線基板5に搭載される。フレキシブル配線基板5は表示ドライバ1の外部出力端子S 1～S nの全部又は一部に接続する配線（以下単にパネルインタフェース用F P C配線とも記す）13と、表示ドライバ1のホストインタフェース端子H 1～H iに接続する配線（以下単にホストインタフェース用F P C配線とも記す）16を有する。フレキシブル配線基板5はポリイミドなどの薄膜樹脂にアルミニウム箔や銅箔を張り合わせて前記パネルインタフェース用F P C配線13やホストインタフェース用F P C配線16が形成されている

30

40

50

。表示ドライバ1は外部出力端子S1～Snとホストインターフェース端子H1～Hiを下に向けて対応するパネルインターフェース用FPC配線13の基端部の上と、ホストインターフェース用FPC配線16の一端部の上に載置して例えば異方性導電膜を用いた圧着で固定することによって実装される。表示ドライバ1はホストインターフェース用FPC配線16を介してホスト装置に接続可能にされる。フレキシブル配線基板5のパネルインターフェース用FPC配線13はアレイ基板11に形成された駆動用ITO配線17に例えば異方性導電膜を用いて圧着で接続される。この駆動用ITO配線17は表示パネルの解像度に応じてそのソース電極を表示ドライバ1の外部出力端子S1～Snの全部又は一部に接続するための配線である。駆動用ITO配線17はソース電極と一対一対応であっても良いが、ソース電極の数が多くなる高解像度の表示パネルの場合には複数本のソース電極をセレクタを介して駆動用ITO配線17に接続可能とすることが得策であり、それによって表示ドライバ1が長くなり過ぎない様にすることができる。

10

#### 【0057】

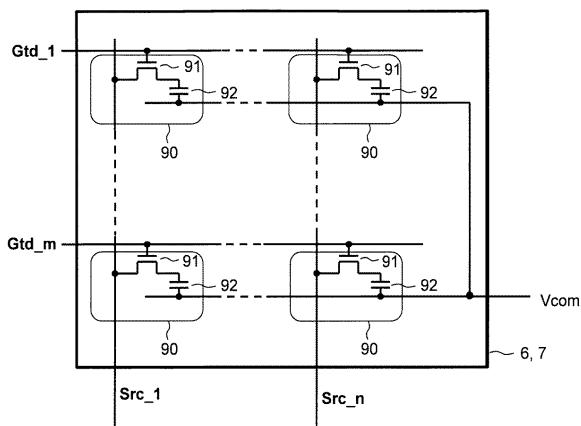

上記表示パネル6、7の構成を回路的に示せば、図9のように、X方向に配置された透明電極であるゲート電極Gt<sub>d</sub>\_1～Gt<sub>d</sub>\_mと、Y方向に配置された透明電極であるソース電極Sr<sub>c</sub>\_1～Sr<sub>c</sub>\_nが形成され、各交差位置に表示素子90が形成される。表示素子90はアレイ基板9，11に形成された薄膜スイッチトランジスタ91とこれに直列接続された容量成分92から成る。薄膜スイッチトランジスタ91の選択端子はゲート電極Gt<sub>d</sub>\_1～Gt<sub>d</sub>\_m内の対応する一つに結合され、薄膜スイッチトランジスタ91のデータ入力端子はソース電極Sr<sub>c</sub>\_1～Sr<sub>c</sub>\_n内の対応する一つに結合される。容量成分92は各表示素子の液晶及び蓄積容量の容量成分を意味し、一方に容量電極は対応する薄膜スイッチトランジスタ91に直列され、他方の容量電極は共通電圧信号線Vcomに結合される。表示素子90はゲート電極を共有する表示ライン単位でゲート電極によって選択され、選択された表示素子90にはソース電極Sr<sub>c</sub>\_1～Sr<sub>c</sub>\_nから並列的に駆動信号が供給されて容量成分92に蓄積され、蓄積された駆動信号の電圧に応じて液晶のニードル傾斜度が制御され、各画素はそれに従った階調で表示を行う。ソース電極Sr<sub>c</sub>\_1～Sr<sub>c</sub>\_nのピッチは表示パネル6、7の解像度やパネルのサイズに応じて相違する。ソース電極Sr<sub>c</sub>\_1～Sr<sub>c</sub>\_n及びゲート電極Gt<sub>d</sub>\_1～Gt<sub>d</sub>\_mは共にITO配線とされる。前述のようにソース電極Sr<sub>c</sub>\_1～Sr<sub>c</sub>\_nは駆動用ITO配線と一対一対応にされ、或いは複数本のソース電極を単位にスイッチを介して1本の駆動用ITO配線に接続される。ちなみに、当該スイッチの選択は表示ドライバ1からソース電極への表示駆動信号の供給タイミングに同期しなければならないからそのスイッチ選択信号は例えば表示ドライバ1が供給する。

20

#### 【0058】

図1にはCOG実装形態において表示ドライバ1の外部出力端子S1～Snに直接結合される駆動用ITO配線12と、COF実装形態において表示ドライバ1の外部出力端子S1～Snに直接結合されるパネルインターフェース用FPC配線13が例示される。COG実装のためにアレイ基板9に形成される駆動用ITO配線12はフォトリソグラフィなどを用いて高精度に、即ち狭ピッチで形成可能である。図1では駆動用ITO配線12のパターンピッチとして10μmが例示される。これに対し、COG実装のためにパネル配線基板5に形成されるパネルインターフェース用FPC配線13やホストインターフェース用FPC配線はフィルム基板に銅箔やアルミ箔を接着して形成するから加工精度はガラス基板9に形成される駆動用ITO配線12などに比べて低くなり、COGの場合に比べて狭ピッチを実現することはできず、図1ではパネルインターフェース用FPC配線13の配線ピッチは例えば20μmにされる。

30

#### 【0059】

COG実装とCOF実装の主な相違点を対比すると、図10に例示されるように、COG実装の場合にはガラス基板上に実装領域を必要とするから表示パネルモジュールの縁はCOG実装の方が広くなり、搭載される配線のピッチ、即ち、搭載に用いる外部出力端子のピッチ（出力バンプピッチ）はCOG実装の方が狭くすることができる。また、表示パ

40

ネルモジュールのコストと言う点ではCOFの方がCOG実装のためのフレキシブル配線基板5を用意しなければならないという点でコスト高になる。

#### 【0060】

図1ではCOG実装とCOF実装の何れにも同じ表示ドライバ1を用いている。例えば上下2段で配置された外部出力端子S1～S540の各段のピッチは20μmで上段と下段の間では相互にピッチを5μmずらして配置してある。即ち、奇数番の端子番号を有する上段の外部出力端子S1～S539の隣接ピッチは20μm、同じく偶数番の端子番号を有する下段の外部出力端子S2～S540の隣接ピッチは20μmとされ、上下段を併せた全体では外部出力端子S1～S540の隣り合う端子番号の隣接ピッチは10μmとされる。表示ドライバ1は図1のCOG実装に対応する場合にはピッチが10μmの駆動用ITO配線12に対して外部出力端子S1～S540の内の上下両段で必要な数の外部出力端子を表示駆動信号の出力に用いる動作モードで動作される。一方、表示ドライバ1は図1のCOF実装に対応する場合にはピッチが10μmのインターフェース用FPC配線13に対して外部出力端子S1～S540の内の上段の必要な数の外部出力端子を表示駆動信号の出力に用いる動作モードで動作される。10

#### 【0061】

表示ドライバ1を使用する表示パネルの解像度に応じた外部出力端子S1～S540の利用形態は、図11に示されるようにCOG実装の場合とCOF実装の場合で相違させることができる。即ち、解像度がFHDの場合はCOG実装により外部出力端子S1～S540の全てを用いる。特に制限されないが、ここでは、2個の画素(6個のサブ画素に応ずる6個の表示素子)の6本に1本のソース電極をセレクタ若しくはスイッチで選択して1本の駆動用ITO配線に接続される。したがって540個の外部出力端子で1080画素のFHDの表示駆動を行う。COFのFHDへの対応は現実的ではないのでサポートしていない。20

#### 【0062】

解像度がHDの場合はCOG実装により外部出力端子S1～S540の配列の左端のS1～S180と右端のS360～S540を用いる。外部出力端子S1～S540の一部を用いる場合には端子配列の両端から中央に向って必要個数用いるようにする。このように、外部出力端子配列の両端から必要個数の外部出力端子を用いることにより、表示ドライバ1を実装する実装相手の配線12, 13の傾きが外部出力端子の配列方向に対して大きくなり、前記配線12, 13の配線ピッチが極端に小さくならないようになる。30

#### 【0063】

解像度がWVGA以下の場合にCOG実装する場合は解像度HDの場合に比べて使用する外部出力端子の数が相違する。

#### 【0064】

表示ドライバ1をCOF実装する場合はパネルインターフェース用FPC配線13のピッチがCOG実装の場合に2倍の20μmであるから、外部出力端子S1～S540の内の端子番号奇数番の上段の冗外部出力端子S1, S3...S537, S539を用いる。例えばWVGAの場合、外部端子配列の左端から端子番号Siが*i* = 2n + 1となる外部端子を用い(但し、*n* = 0 ~ 119)、外部端子配列の右端から端子番号Siが*i* = 539 - 2nとなる外部端子を用いる(但し、*n* = 119 ~ 0)。以下同様であり、540 × 540の解像度の場合は使用する外部出力端子の端子番号Siは*i* = 2n + 1(但し、*n* = 0 ~ 269)の範囲とされる。420 × 420の解像度の場合は左端から使用する外部出力端子の端子番号Siは*i* = 2n + 1(但し、*n* = 0 ~ 104)の範囲とされ、右端から使用する外部出力端子の端子番号Siは*i* = 2n + 1(但し、*n* = 104 ~ 0)の範囲とされる。360 × 360の解像度の場合は左端から使用する外部出力端子の端子番号Siは*i* = 2n + 1(但し、*n* = 0 ~ 89)の範囲とされ、右端から使用する外部出力端子の端子番号Siは*i* = 2n + 1(但し、*n* = 89 ~ 0)の範囲とされる。40

#### 【0065】

図11では外部出力端子S1～S540の隣り合う端子ピッチ(10μm)に対して上50

段と下段の各々の配列の端子ピッチ ( $20 \mu m$ ) が 2 倍にされた表示ドライバ 1 を一例とした場合に、それに合わせて COF 実装の場合の配線ピッチを便宜上 COG 実装の場合の配線ピッチの 2 倍として説明した。実際はそれに限られるものではなく、COF 実装の場合の配線ピッチが COG 実装の場合の配線ピッチの整数倍にならない場合や、配線ピッチそれ自体が  $10 \mu m$  や  $20 \mu m$  でない場合が想定される。その場合に表示ドライバ 1 を実装するときは、実装相手となる配線の上に乗る位置の外部出力端子を利用して実装すればよい。例えば外部出力端子配列中で  $m$  個に 1 個の割合で外部出力端子を不使用とするように実装すればよい。

#### 【0066】

上述の COG 実装や COF 実装の双方に対応し、更に、実装可能な配線ピッチに柔軟に対応するために、表示ドライバ 1 はその実装形態に応じてどの外部出力端子からどの駆動信号を出力するかを可変に制御する機能を備える。以下ではその機能を実現する表示ドライバ 1 の構成について説明する。

#### 【0067】

図 12 には表示ドライバ 1 の構成が例示される。

#### 【0068】

表示ドライバ 1 はホストプロセッサ 31 から表示動作を指示するコマンド及び表示データを受け取る。表示ドライバ 1 は受け取ったコマンドに従った動作を行って、表示データに基づいて表示パネル 6 又は 7 に画像を表示する制御などを行なう。表示ドライバ 1 は、ホストプロセッサ 2 から画像データを入力し、表示タイミングに同期しながら、複数本のゲート電極線 Gt d\_1 ~ Gt d\_m によって画素を表示ライン単位で順次走査するためのタイミング信号を出力すると共に、走査駆動された表示ラインの画素には表示データに応する階調信号としての駆動信号を複数本のソース電極線 Src\_1 ~ Src\_n に並列的に供給する制御を行う。特に図示はしないがゲート電極線 Gt d\_1 ~ Gt d\_m を駆動するゲートドライバは表示ドライバ 1 とは別に表示パネルに搭載され、表示ドライバはゲート電極線の駆動タイミング信号をゲートドライバに出力する。駆動タイミング信号はタイミング信号 Stm\_1 ~ Stm\_j の一部とされる。

#### 【0069】

表示ドライバ 1 は、特に制限されないが、ホストインターフェース回路 40、レジスタ回路 41、表示データ処理回路 42、タイミング制御回路 43、ラインラッチ回路 44、ソース出力回路 45、内蔵発振器 50、表示 RAM 51、表示駆動電圧発生回路 52、パネルインターフェース回路 53、及び階調電圧生成回路 54 を有する。

#### 【0070】

ホストインターフェース回路 40 はホストプロセッサ 31 から表示データ、コマンド、制御データ及び各種外部タイミング信号を受け取る。受け取った外部タイミング信号に基づいて内部タイミング信号としてのクロック信号 CLK、垂直同期信号 VSYNC 及び水平同期信号 HSYNC を生成してタイミング制御回路 43 に与える。ホストインターフェース回路 40 はホストプロセッサ 31 から受け取ったコマンド及び制御データをレジスタ回路 41 に格納する。初期設定データ等の一部の制御データはホストインターフェース回路 40 内の不揮発性記憶回路 (NVM) 47 からロードされる。タイミング制御回路 43 は、ホストインターフェース回路 40 から与えられるタイミング信号、レジスタ回路 41 から転送されたコマンド及び制御データに基づいて表示制御を行う。クロック信号 CLK はドットクロックに一致されるドットクロック信号である。

#### 【0071】

表示データはビデオストリームデータとして供給される場合もあれば、ワード単位でバスアクセスサイクルに従って供給される場合もある。供給されたデータは必要に応じて表示データ処理部 42 でフィルタ演算などが行われる。バスアクセスサイクルに従って供給された表示データは例えば表示フレーム単位で表示 RAM 51 に格納され、表示 RAM 51 に格納された表示データは表示タイミングに同期して読み出され、読み出された表示データは表示ライン毎に直列的にラインラッチ回路 44 にラッチされる。ビデオストリームデ

10

20

30

40

50

ータで供給された表示データは表示タイミングに同期して直列的にラインラッチ回路44にラッチされる。ラインラッチ回路41に対するラッチアドレス制御はタイミング制御回路43が行う。ソース出力回路45はラインラッチ回路44にラッチされた表示データを並列的に入力し、表示データに応ずる階調電圧の駆動信号を表示パネル6又は7に出力する。表示ドライバ1がCOG実装されていれば駆動用ITO配線12に出力され、COF実装されていればパネルインターフェース用FPC配線13に出力される。階調電圧は階調電圧生成回路54が生成してソース出力回路45に与える。ラインラッチ回路44とソース出力回路45は外部出力端子S1～S540の内の所要の端子から表示パネル6,7に供給するための表示駆動信号を生成する出力回路46の一例を成すものである。

## 【0072】

10

内蔵発信回路50は表示ドライバ1の内部タイミングを規定するためのクロック信号を出力する。表示駆動電圧発生回路52は表示パネルで必要するゲート駆動電圧や共通電圧信号線の電圧を出力する。パネルインターフェース回路はタイミング信号STM\_1～STM\_jを出力する。

## 【0073】

図13には解像度がFHDの表示パネル6に表示ドライバ1をCOG実装した状態で出力回路46の詳細を例示する。P1, P2…は表示パネル6の画素であり、各画素はR(赤)、G(緑)、B(青)の表示素子90から成るサブ画素を持つ。特に制限されないが、この例ではソース電極SRC\_1～SRC\_nは6本一組、すなわち2画素一組でセレクタ72を介して1本の駆動用ITO配線12に接続される。各セレクタ72はタイミング制御回路43から出力される選択信号CNTspによって順次1本ずつソース電極をRGBRGBの順に選択していく。選択信号CNTspは前記タイミング信号STM\_1～STM\_jに含まれる信号である。

20

## 【0074】

解像度がFHDの表示パネル6にCOG実装される場合、図11の接続形態で説明したように外部出力端子S1～S540は夫々対応する駆動用ITO配線12に接続されてCOG実装されることになる。

## 【0075】

ソース駆動回路45は外部出力端子S1～S540の夫々に一体一対応でドライバDRVを有する。各ドライバDRVは、特に図示はしないが、階調に対応する8ビットのような複数ビットの単位表示データを受け取ってこれに対応する階調電圧を出力バッファから出力する回路である。

30

## 【0076】

ラインラッチ回路44は入力段ラインラッチ回路44Bと出力段ラインラッチ回路44Aの2段構成になっている。入力段ラインラッチ回路44Bと出力段ラインラッチ回路44Aは夫々画素単位、すなわち3個のサブ画素単位で、RGB3個の単位表示データを保持する32ビットのレジスタREGを540個有する。レジスタREG毎にアドレスA0～A539が割り当てられている。

## 【0077】

入力段ラインラッチ回路44Bの各レジスタREGのデータ入力端子には、特に制限されないが、32ビットの内部バスから32ビット単位で表示データDATdispが供給される。内部バスに供給された表示データDATdispは書き込みアドレスADRwで指定されたレジスタREGに書き込まれる。書き込みタイミングは書き込みイネーブル信号CNTwによって制御される。32ビット単位の表示データDATdispは図15に例示するように、順次D0、D1、D2、…とされ、各データは対応する1画素分の3個のRGBの単位表示データを有する。例えばデータD0は、画素P1のRデータD0\_P1r、GデータD0\_P1g及びBデータD0\_P1bを有し、データD1は、画素P2のRデータD1\_P2r、GデータD1\_P2g及びBデータD1\_P2bを有する。

40

## 【0078】

出力段ラインラッチ回路44Aの各レジスタREGは対応する入力段ラインラッチ回路

50

44Bのレジスタ REG から 32 ビット単位で表示データ DAT disp が転送される。出力段ラインラッチ回路 44A は読み出しアドレス ADDRr で指定されたレジスタ REG が読み出し対象にされる。読み出しは単位表示データ毎の 8 ビット単位で行われ、読み出しタイミングは読み出しイネーブル信号 CNTr によって制御される。

#### 【0079】

出力段ラインラッチ回路 44A の隣り合う 2 個のレジスタ REG の出力はワイヤードオア又はセレクタを介して次段のドライバDRV の入力端子に接続される。

#### 【0080】

上記入力段ラインラッチ回路 44B のレジスタ REG に対する 1 表示ライン分の表示データ DAT disp の書き込み動作は水平同期期間で行われ、出力段ラインラッチ回路 44A のレジスタ REG に対する 1 表示ライン分の読み出しは次の水平同期期間で行われる。

出力段ラインラッチ回路 44A のレジスタ REG に対する読み出し動作では、特に制限されないが、1 表示期間中に出力段ラインラッチ回路 44A のレジスタ REG を順次選択し、選択したレジスタ REG の RGB 3 個の単位表示データを順次読み出すようにすればよい。

この場合に出力段ラインラッチ回路 44A のレジスタ REG の選択サイクルに対して 3 倍の速度でセレクタ 72 によるソース電極の選択を順次行えばよい。或いは、1 表示期間の前半期間中に奇数番目のレジスタ REG の RGB 3 個の単位表示データを順次選択し、1 表示期間の後半期間中に偶数番目のレジスタ REG の RGB 3 個の単位表示データを順次選択して、読み出しを行うことも可能である。但し表示品質は低くなる。

#### 【0081】

タイミング制御回路 43 は、入力段ラインラッチ回路 44B のレジスタ REG に対してどのレジスタ REG に表示データを書き込むか、そしてそれに応じて出力段ラインラッチ回路 44A のどのレジスタ REG から表示データを読み出すかを可変に選択する制御ロジックを有する。即ち、レジスタ回路 41 の出力モードレジスタ 60 に設定された出力モードデータ Mdata に従って、入力段ラインラッチ回路 44B に対する表示データの書き込み位置を制御する書き込みレジスタアドレス生成ロジック (WRSLgc) 62 と出力段ラインラッチ回路 44A に対する表示データに読み出し位置を制御する読み出しレジスタアドレス生成ロジック (RRSLgc) 61 を有する。書き込みレジスタアドレス生成ロジック 62 はモードデータ Mdata に応じた書き込みアドレス ADDRw を生成し、読み出しレジスタアドレス生成ロジック 61 はモードデータ Mdata に応じた読み出しアドレスを生成する。双方のレジスタアドレス生成ロジック 61, 62 は特に制限されないが、プログラムシーケンス制御ロジックで構成されるが、ハードワイヤードロジックで構成する子とは妨げられない。

#### 【0082】

レジスタアドレス生成ロジック 61, 62 による制御は、出力モードレジスタ 60 に設定された出力モードデータ Mdata に従って、表示駆動信号を出力するために出力回路 46 が用いる外部出力端子 S1 ~ S540 の配列を、配置ピッチが異なる複数種類の配列の中から選択するよう、書き込みアドレス ADDRw と読み出しアドレス ADDRr を生成する制御を行なう。即ち、レジスタアドレス生成ロジック 61, 62 は外部出力端子 S1 ~ S540 の配列方向に従って入力段ラインラッチ回路 44B へ表示データを書き込むレジスタ位置（入力位置）、そして、出力段ラインラッチ回路 44A から表示データを読み出すレジスタ位置（出力位置）をモードデータ Mdata に従って可変に制御することによって、表示データの出力に用いる外部出力端子 S1 ~ S540 の配列を配置ピッチが異なる複数種類の配列の中から選択可能にするものである。

#### 【0083】

モードデータ Mdata に従ってレジスタアドレス生成ロジック 61, 62 が選択可能な外部出力端子 S1 ~ S540 の配列形態として、例えば図 11 の配列形態を備える。COG 実装の FHD、COG 実装の HD、COG 実装の WVGA、COF 実装の WVGA などに対して夫々固有のモード番号が割り当てられ、このモード番号をモードレジスタ 60 に設定することにより、レジスタアドレス生成ロジック 61, 62 が其のモード番号をコ

10

20

30

40

50

マンドとして解読することによって対応する書き込みアドレス A D R w 及び読み出しアドレス A D R rなどを生成する。レジスタ書き込み及び読み出しに必要な動作イネーブル信号や選択信号など、その他のタイミング信号はタイミング制御回路 4 3 内の図示を省略する制御ロジックがモードデータ M d a t a に基づいて生成する。

#### 【 0 0 8 4 】

C O G 実装の F H D が指定された場合の外部出力端子 S 1 ~ S 5 4 0 の接続形態は図 1 3 に示される通りであり、上下 2 段夫々の外部出力端子 S 1 ~ S 5 4 0 が駆動用 I T O 配線 1 2 に接続される。このときの画素と、その出力に用いる外部出力端子と、画素データとそれを保持するレジスタ R E G のアドレスとの関係は図 1 4 に例示される通りである。C O G 実装の H D 、 C O G 実装の W V G A 、 C O G 実装の 5 4 0 × 5 4 0 解像度、 C O G 実装の 4 2 0 × 4 2 0 解像度、 C O G 実装の 3 6 0 × 3 6 0 解像度についても同様であり、レジスタ R E G の配列に対して端から順次必要個数だけ利用するようにされる。10

#### 【 0 0 8 5 】

C O F 実装の W V G A が指定された場合の外部出力端子 S 1 ~ S 5 4 0 の接続形態は図 1 6 に示される通りであり、端子番号が奇数番とされる上段に位置する一列の所要個数の外部出力端子 S 1 、 S 3 、 S 5 、 ... が駆動用 I T O 配線 1 2 に接続される。このときの画素と、その出力に用いる外部出力端子と、画素データとそれを保持するレジスタ R E G のアドレスとの関係は図 1 7 に例示される通りであり、画素 P 1 、 P 2 の出力には外部出力端子 S 1 を用い、そこから出力する画素データ D 0 , D 1 の書き込み及び読み出しレジスタアドレスとして A 0 、 A 1 を用い、画素 P 3 、 P 4 の出力には外部出力端子 S 3 を用い、そこから出力する画素データ D 2 , D 3 の書き込み及び読み出しレジスタアドレスとして A 4 、 A 5 を用い、其の間に位置する外部出力端子 S 2 及びアドレス A 2 、 A 3 のレジスタは不使用とされる。他の画素に対しても同じである。C O F 実装の W V G A 、 C O F 実装の 5 4 0 × 5 4 0 解像度、 C O F 実装の 4 2 0 × 4 2 0 解像度、 C O F 実装の 3 6 0 × 3 6 0 解像度についても同様であり、レジスタ R E G の配列に対して端から同様に必要個数だけ利用するようにされる。20

#### 【 0 0 8 6 】

図 1 8 にはその他の動作モードに対応する接続形態が例示される。以上の説明では図 1 に示されるようにパネルインタフェース用 F P C 配線 1 3 のピッチが上段の端子配列ピッチに等しい場合としたが、この例ではパネルインタフェース用 F P C 配線 1 3 のピッチが上段の端子配列ピッチから僅かにずれているフレキシブル配線基板 5 を使用する場合を想定する。この場合には所定個数に 1 個の割合で外部出力端子を不使用にして接続することによって、ピッチの誤差を吸収することができる。図 1 8 では上段の外部出力端子配列の 2 個に 1 個の割合で不使用とする。外部出力端子の配列ピッチに対するパネルインタフェース用 F P C 配線 1 3 のピッチずれ量が解れば幾つ置きに外部出力端子を不使用にすればよいのかは事前に知ることができるので、その関係に従って動作モードを事前に決定し、それに応じた制御シーケンスを制御回路 4 3 に組み込んでおけばよい。このときの画素と、その出力に用いる外部出力端子と、画素データとそれを保持するレジスタ R E G のアドレスとの関係は図 1 9 に例示される通りであり、画素 P 1 、 P 2 の出力には外部出力端子 S 1 を用い、そこから出力する画素データ D 0 , D 1 の書き込み及び読み出しレジスタアドレスとして A 0 、 A 1 を用い、画素 P 3 、 P 4 の出力には外部出力端子 S 3 を用い、そこから出力する画素データ D 2 , D 3 の書き込み及び読み出しレジスタアドレスとして A 4 、 A 5 を用い、その間に位置する外部出力端子 S 2 及びアドレス A 2 、 A 3 のレジスタは不使用とされる。次の画素 P 5 、 P 6 の出力には外部出力端子 S 7 を用い、そこから出力する画素データ D 4 , D 5 の書き込み及び読み出しレジスタアドレスとしてアドレス A 1 2 、 A 1 3 を用い、その間に位置する外部出力端子 S 4 ~ S 6 及びアドレス A 6 ~ A 1 1 のレジスタは不使用とされる。40

#### 【 0 0 8 7 】

以上説明した表示ドライバ 1 によれば、表示パネルを駆動するとき表示駆動信号の出力に用いる外部出力端子 S 1 ~ S 5 4 0 の配列として配置ピッチが異なる複数種類の配列の50

中から一つの配列をモードデータ M d a t a に基づいて選択可能である。換言すれば、制御回路 4 3 は外部出力端子 S 1 ~ S 5 4 0 の配列方向に対するラインラッチ回路 4 4 B への画素データの書き込みレジスタ位置、そしてラインラッチ回路 4 4 A から画素データを読み出す読み出しレジスタ位置が可変とされる。したがって、表示ドライバ 1 を実装する駆動用 I T O 配線 1 2 やパネルインタフェース用 F P C 配線 1 3 のピッチに合うようにモードデータ M d a t a をモードレジスタ 6 0 に設定して、表示駆動信号の出力に用いる外部出力端子の配列を配置ピッチの異なる複数種類の配列の中から選択すればよい。したがって、表示ドライバ 1 は、表示ドライバ 1 から駆動信号を受ける信号配線のピッチが相違する表示パネルに対しても、また、実装される駆動用 I T O 配線 1 2 やパネルインタフェース用 F P C 配線 1 3 のような配線のピッチが相違される C O F 実装と C O G 実装の何れに対しても、共用可能となる。これは、図 7 や図 8 に示す表示パネルモジュールのコスト低減に寄与するものである。10

#### 【 0 0 8 8 】

また、モードデータ M d a t a に従って制御回路 4 3 が選択可能な複数種類の配列として、複数の外部出力端子 S 1 ~ S 5 4 0 の配列中で駆動信号の出力に用いられる複数の外部出力端子の隣接する端子間に割り当てられるピッチの状態が相違されていて、駆動信号の出力に用いられる複数の外部出力端子の配置がその配列の長手方向両端を基点に中央部に向って配置される配列を有する。図 1 8 及び図 1 9 で説明した配列などである。このように選択可能な配列間で、外部出力端子 S 1 ~ S 5 4 0 の隣接する端子間に割り当てられるピッチの状態に相違があるということは、表示ドライバ 1 を実装する実装相手の配線パターンの配列ピッチが外部出力端子 S 1 ~ S 5 4 0 の物理的配置のピッチに対して整数倍以外のピッチであっても選択可能な配列とすることができる意味し、選択可能な配列のバリエーションが増える。外部出力端子 S 1 ~ S 5 4 0 の配列の両端から必要個数の外部出力端子を用いることは、表示ドライバ 1 を実装する実装相手の配線パターン（図 7 の駆動用 I T O 配線 1 2 、図 8 のパネルインタフェース用 F P C 配線 1 3 ）の傾きが外部出力端子 S 1 ~ S 5 4 0 の配列方向に対して大きくなるように作用し、配線パターンの配線ピッチが極端に小さくならないようにするのに好適である。20

#### 【 0 0 8 9 】

更に、図 1 1 で説明したようにモードデータ M d a t a に基づいて制御回路 4 3 が選択可能な複数種類の配列として、外部出力端子 S 1 ~ S 5 4 0 の配列中で駆動信号の出力に用いられる複数の外部出力端子の数が相違され、駆動信号の出力に用いられる複数の外部出力端子の配置がその配列の長手方向両端を基点に中央部に向って配置される配列を有するので、選択可能な配列のバリエーションは格段に増える。30

#### 【 0 0 9 0 】

また、図 1 3 などに基づいて説明したように、1 個の外部出力端子を複数画素の駆動に共用すること、例えば1 個のデータレジスタが n 個の画素の画素データを保持する場合に1 個の外部出力端子が n 個の画素に時分割で表示駆動信号を供給するのに共用することにより、高解像度の表示パネル 6 に配置された表示素子 9 0 の信号線 S r c \_ 1 ~ S r c \_ n を複数本単位でセレクタ 7 2 を介して1 本の配線 1 2 又は 1 7 に引き出して表示ドライバ 1 の外部出力端子に接続する構成を可能にする。これは、表示パネル 6 の高解像度化に対しても表示ドライバ 1 の外部出力端子の配列ピッチが極端に狭くならないようにすることができ、実装可能なピッチに留めておくことを可能にする。40

#### 【 0 0 9 1 】

図 2 0 には表示パネルモジュールを用いた電子機器 1 0 0 が例示される。この例では携帯端末を電子機器 1 0 0 の一例としている。ここでは表示パネルモジュール 2 A には表示パネル 6 と表示ドライバ 1 の外に、タッチパネル 7 0 とタッチコントローラ 7 1 が搭載される。特に制限されないが、タッチパネル 7 0 は表示パネル 6 の表面に形成され、タッチコントローラ 7 1 は表示ドライバ 1 にオンチップされる。

#### 【 0 0 9 2 】

ホストプロセッサ 3 1 は、特に制限されないが、通信プロトコル処理とその他のアプリ50

ケーション処理を制御するベースバンド・アプリケーションプロセッサ（B B / A P P）として構成される。B B / A P P 3 1は、特に制限されないが、音声信号や送受信信号に係る信号処理を行なうD S P（Digital Signal Processor）8 0、カスタム機能（ユーザ論理）を提供するA S I C（Application Specific Integrated Circuits）8 1、装置全体の制御を行なうデータ処理装置としてのマイクロプロセッサ若しくはマイクロコンピュータ（以下、マイコンと略す）8 2、及び表示ドライバ1等とインタフェースを行なうM I P I インタフェース回路8 3を有する。ホストプロセッサ3 1には、特に制限されないが、表示パネルモジュール2 Aの他に、スピーカ8 9やマイクロホン8 8の信号入出力を行なう音声インタフェース8 4、アンテナ8 6との間の信号の入出力を行なう高周波インタフェースのような通信部8 5、及び不揮発性ファイルメモリ8 7が接続される。

10

#### 【0093】

以上本発明者によってなされた発明を実施の形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

#### 【0094】

例えは、表示ドライバの外部出力端子配列に対する実装配線との接続形態、表示ドライバの外部出力端子を実装配線に接続する方法、表示パネルのガラス基板上における電極の配線構造や材質、そしてF P C基板の配線構造や材質は、上記実施の形態に限定されず、適宜変更可能である。駆動対象とする表示パネルの解像度は図1 1に限定されず、他の解像度であってもよいことは言うまでもない。表示ドライバの外部出力端子の配列は図2のように列間でピッチをずらした2列配置に限定されず、3列以上であってもよく、また、1列であってもよい。

20

#### 【0095】

また、表示ドライバがセレクタ7 2を利用しない場合には表示ドライバは表示パネルのゲート電極線G t d \_ 1 ~ G t d \_ mに直接ゲート駆動信号を出力すればよい。また、表示ドライバはタッチパネルコントローラを搭載しても良い。

#### 【0096】

また、入力段ラインラッチ回路4 4 BのレジスタR E G列に対する単位表示データの書き込み順序、出力段ラインラッチ回路4 4 AのレジスタR E G列に対する単位表示データの読み出し順序は上記実施形態に制限されず、必要な表示機能を阻害しない範囲で適宜変更可能である。

30

#### 【符号の説明】

#### 【0097】

- 1 表示ドライバ

- 2 表示ドライバをC O G実装した表示パネルモジュール

- 2 A 表示パネルモジュール

- 3 表示ドライバをC O F実装した表示パネルモジュール

- 4 インタフェースコネクタ

- 5 フレキシブル配線基板

- 6 , 7 表示パネル

- 8 フィルタ基板

- 9 アレイ基板

- 10 フィルタ基板

- 11 アレイ基板

- S 1 ~ S n 外部出力端子

- H 1 ~ H i ホストインタフェース端子

- 12 駆動用I T O配線

- 13 パネルインタフェース用F P C配線

- 14 ホストインタフェース用I T O配線

- 15 F P C配線

40

50

|                       |                                    |    |

|-----------------------|------------------------------------|----|

| 1 6                   | ホストインターフェース用 F P C 配線              |    |

| 1 7                   | 駆動用 I T O 配線                       |    |

| G t d _ 1 ~ G t d _ m | ゲート電極                              |    |

| S r c _ 1 ~ S R C _ n | ソース電極                              |    |

| 2 0                   | スマートフォン                            |    |

| 2 1                   | スマートウォッチ                           |    |

| 2 2                   | フリーフォームディスプレイ                      |    |

| 3 1                   | ホストプロセッサ                           |    |

| 4 0                   | ホストインターフェース回路                      |    |

| 4 1                   | レジスタ回路                             | 10 |

| 4 2                   | 表示データ処理回路                          |    |

| 4 3                   | タイミング制御回路                          |    |

| 4 4                   | ラインラッチ回路                           |    |

| 4 4 B                 | 入力段ラインラッチ回路                        |    |

| 4 4 A                 | 出力段ラインラッチ回路                        |    |

| 4 5                   | ソース出力回路                            |    |

| 4 6                   | 出力回路                               |    |

| 5 0                   | 内蔵発振器                              |    |

| 5 1                   | 表示 R A M                           |    |

| 5 2                   | 表示駆動電圧発生回路                         | 20 |

| 5 3                   | パネルインターフェース回路                      |    |

| 5 4                   | 階調電圧生成回路                           |    |

| 7 0                   | タッチパネル                             |    |

| 7 1                   | タッチコントローラ                          |    |

| 7 2                   | セレクタ                               |    |

| C N T s p             | 選択信号                               |    |

| S t m _ 1 ~ S t m _ j | タイミング信号                            |    |

| R E R G               | レジスタ                               |    |

| D A T d i s p         | 表示データ                              |    |

| A D R w               | 書き込みアドレス                           | 30 |

| C N T w               | 書き込みイネーブル信号                        |    |

| A D R r               | 読み出しアドレス                           |    |

| C N T r               | 読み出しイネーブル信号                        |    |

| D A T d i s p         | 表示データ                              |    |

| 6 0                   | 出力モードレジスタ                          |    |

| 6 1                   | 読み出しレジスタアドレス生成ロジック ( R R S L g c ) |    |

| 6 2                   | 書き込みレジスタアドレス生成ロジック ( W R S L g c ) |    |

| 9 0                   | 表示素子                               |    |

| 9 1                   | 薄膜スイッチトランジスタ                       |    |

| 9 2                   | 容量成分                               | 40 |

| V c o m               | 共通電圧信号線                            |    |

| 1 0 0                 | 電子機                                |    |

【図1】

【図2】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

【 図 1 2 】

【 図 1 1 】

|           |        | Pad assignment for COF      | Pad assignment for COF                        |

|-----------|--------|-----------------------------|-----------------------------------------------|

| FID       | 540 ch | S1 to S540                  | --                                            |

| HD        | 360 ch | S1 to S180<br>S360 to S540  | --                                            |

| WVGA      | 240 ch | S1 to S120,<br>S421 to S540 | S(2n+1) n=0 to 119,<br>S(539 - 2n) n=119 to 0 |

| 540 x 540 | 270 ch | S1 to S135,<br>S406 to S540 | S(2n+1) n=0 to 269                            |

| 420 x 420 | 210 ch | S1 to S105,<br>S436 to S540 | S(2n+1) n=0 to 104,<br>S(539 - 2n) n=104 to 0 |

| 360 x 360 | 180 ch | S1 to S90,<br>S451 to S540  | S(2n+1) n=0 to 89,<br>S(539 - 2n) n=89 to 0   |

【 図 1 3 】

【図 1 4】

【図 1 5】

|    |         |         |         |

|----|---------|---------|---------|

| D0 | D0_P1 r | D0_P1 g | D0_P1 b |

| D1 | D1_P2 r | D1_P2 g | D1_P2 b |

| D2 | D2_P3 r | D2_P3 g | D2_P3 b |

| D3 | D3_P4 r | D3_P4 g | D3_P4 b |

| D4 | D4_P5 r | D4_P5 g | D4_P5 b |

| D5 | D5_P6 r | D5_P6 g | D5_P6 b |

... (ellipsis)

【図 1 6】

【図 1 7】

| Pixel      | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | P9 | P10 | P11 | P12 |

|------------|----|----|----|----|----|----|----|----|----|-----|-----|-----|

| Output pad | S1 |    | S3 |    | S5 |    | S7 |    | S9 |     | S11 |     |

| Address    | A0 | A1 | A2 | A3 | A4 | A5 | A6 | A7 | A8 | A9  | A10 | A11 |

| Data       | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9  | D10 | D11 |

【図18】

【図19】

| Pixel      | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | S9      | ...   |

|------------|----|----|----|----|----|----|----|----|---------|-------|

| Output pad | S1 |    |    | S3 |    |    |    |    |         |       |

| Address    | A0 | A1 |    | A4 | A5 |    |    |    | A16/A17 |       |

| Data       | D0 | D1 |    | D2 | D3 |    |    |    | D4 D5   | D6 D7 |

【図20】

---

フロントページの続き

審査官 西島 篤宏

- (56)参考文献 特開2002-278492(JP,A)

特開2005-182010(JP,A)

特開2008-065295(JP,A)

国際公開第2011/129400(WO,A1)

特開2007-183542(JP,A)

特開2005-257899(JP,A)

国際公開第2007/145522(WO,A1)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 0 0 - 3 / 3 8