ことを特徴とする光電変換装置。

【請求項 2】

第1面および第2面を有する半導体層に配置された第1導電型の複数の第1領域と、前記第2面と前記第1領域との間に配置され、前記複数の第1領域のうち対応する1つの第1領域とともに各々がアバランシェフォトダイオードのアバランシェ増倍領域を構成する第2導電型の複数の第2領域と、

前記第1面に対する正射影において、前記複数の第2領域を取り囲むように前記第1面と前記第2面との間に配置された前記第2導電型の分離領域と、

前記分離領域に接するように配置された前記第2導電型のコンタクト領域と、

前記複数の前記第1領域にそれぞれ接続された複数の第1コンタクトプラグと、

前記コンタクト領域に接続された第2コンタクトプラグと、が複数の画素を構成するように設けられ、

第1の方向に前記複数の画素のうちの第1の画素、第2の画素が配され、

前記第1の方向に交差する第2の方向に前記第2の画素、第3の画素が配され、

前記第1面に対する正射影において、前記第1の画素の前記第2コンタクトプラグの中心と前記第1の画素の前記第1コンタクトプラグの中心との距離をL1、前記第1の画素の前記第2コンタクトプラグの中心と前記第1の画素の前記第1コンタクトプラグの中心とを通る直線上において、前記第1の画素の前記第1領域と前記第3の画素の前記第1領域との距離をL2としたときに、L1 > 0.5L2であり、

前記第1面に対する正射影において、前記第1の画素の前記第1領域と前記第3の画素の前記第1領域との間に前記第2コンタクトプラグは配されていない、

ことを特徴とする光電変換装置。

【請求項 3】

第1面および第2面を有する半導体層に配置された第1導電型の第1領域と、

前記第2面と前記第1領域との間に配置され、前記第1領域とともにアバランシェフォトダイオードのアバランシェ増倍領域を構成する第2導電型の第2領域と、

前記第1面に対する正射影において前記第2領域を取り囲むように、前記第1面と前記第2面との間に配置された前記第2導電型の分離領域と、

前記分離領域に接するように配置された前記第2導電型のコンタクト領域と、

前記第1領域に接続された第1コンタクトプラグと、

前記コンタクト領域に接続された第2コンタクトプラグと、が複数の画素を構成するように設けられ、

第1の方向に前記複数の画素のうちの第1の画素、第2の画素が配され、

前記第1の方向に交差する第2の方向に前記第2の画素、第3の画素が配され、

前記第1面に対する正射影において、前記分離領域の第1部分に接するように配置された前記コンタクト領域と前記分離領域の第2部分との間に位置するように前記第1領域が配置され、

前記第1面に対する正射影において、前記第1部分、前記コンタクト領域、前記第1領域、および前記第2部分を通る直線において、前記コンタクト領域と前記第1領域との距離は、前記第2部分と前記第1領域との距離よりも大きく、

前記第1面に対する正射影において、前記第1の画素の前記第1領域と前記第3の画素の前記第1領域との間に前記第2コンタクトプラグは配されていない、

ことを特徴とする光電変換装置。

【請求項 4】

前記第2領域は、矩形の形状を有し、前記第2コンタクトプラグは、前記矩形の対角方向に配置されている、

ことを特徴とする請求項1乃至3のいずれか1項に記載の光電変換装置。

【請求項 5】

前記第2コンタクトプラグの個数が前記第1コンタクトプラグの個数より少ない、

ことを特徴とする請求項1乃至4のいずれか1項に記載の光電変換装置。

10

20

30

40

50

**【請求項 6】**

1つの画素が1つの前記アバランシェフォトダイオードを含むように前記複数の画素が前記半導体層に配置され、

前記複数の画素の少なくとも2つの画素によって前記第2コンタクトプラグが共有されている、

ことを特徴とする請求項1乃至5のいずれか1項に記載の光電変換装置。

**【請求項 7】**

前記第2コンタクトプラグを共有する前記少なくとも2つの画素が前記第2コンタクトプラグに関して対称性を有するように配置されている、

ことを特徴とする請求項6に記載の光電変換装置。

10

**【請求項 8】**

マイクロレンズを更に含み、

前記正射影において、前記マイクロレンズの中心は、前記第2領域の中心と一致している、ことを特徴とする請求項6又は7に記載の光電変換装置。

**【請求項 9】**

1つの画素が1つの前記アバランシェフォトダイオードを含むように前記複数の画素が前記半導体層に配置され、

前記第2コンタクトプラグは、前記複数の画素のうち4つの画素によって取り囲まれ、かつ前記4つの画素によって共有されている、

ことを特徴とする請求項1乃至5のいずれか1項に記載の光電変換装置。

20

**【請求項 10】**

1つの画素が1つの前記アバランシェフォトダイオードを含むように前記複数の画素が前記半導体層に配置され、

前記複数の画素は、矩形の画素アレイを構成するように配置され、

前記第2コンタクトプラグは、前記画素アレイの対角方向の各位置に配置されている、ことを特徴とする請求項1乃至5のいずれか1項に記載の光電変換装置。

**【請求項 11】**

1つの画素が1つの前記アバランシェフォトダイオードを含むように前記複数の画素が前記半導体層に配置され、

前記複数の画素は、矩形の画素アレイを構成するように配置され、

2つの前記第2コンタクトプラグによって前記複数の画素のうち少なくとも2つの画素が挟まれている、

ことを特徴とする請求項1乃至5のいずれか1項に記載の光電変換装置。

30

**【請求項 12】**

前記第2領域は、前記第1領域から離隔して配置されている、

ことを特徴とする請求項1乃至11のいずれか1項に記載の光電変換装置。

**【請求項 13】**

前記第1領域の側面を覆うように配置され、前記第1領域の前記第1導電型の不純物濃度より低い前記第1導電型の不純物濃度のリング状領域を更に含む、

ことを特徴とする請求項12に記載の光電変換装置。

40

**【請求項 14】**

前記第2領域は、前記リング状領域から離隔して配置されている、

ことを特徴とする請求項13に記載の光電変換装置。

**【請求項 15】**

前記分離領域は、前記リング状領域から離隔して配置されている、

ことを特徴とする請求項13又は14に記載の光電変換装置。

**【請求項 16】**

1つの画素の前記リング状領域が他の画素の前記リング状領域と結合している、

ことを特徴とする請求項13乃至15のいずれか1項に記載の光電変換装置。

**【請求項 17】**

50

前記第1領域と前記第2領域との間、および、前記リング状領域と前記第2領域との間に前記第1導電型の第3領域を有し、

前記第3領域の前記第1導電型の不純物濃度は、前記リング状領域の前記第1導電型の不純物濃度より低い、

ことを特徴とする請求項13乃至16のいずれか1項に記載の光電変換装置。

【請求項18】

前記第1領域と前記第2領域との間、および、前記リング状領域と前記第2領域との間に前記第2導電型の第3領域を有し、

前記第3領域の前記第2導電型の不純物濃度は、前記第2領域および前記分離領域の前記第2導電型の不純物濃度より低い、

ことを特徴とする請求項13乃至16のいずれか1項に記載の光電変換装置。

【請求項19】

請求項1乃至18のいずれか1項に記載の光電変換装置と、

前記光電変換装置が出力する信号を処理する信号処理部と、

を備えることを特徴とする光電変換システム。

【請求項20】

請求項1乃至18のいずれか1項に記載の光電変換装置と、

前記光電変換装置からの信号に基づく測距情報から、対象物までの距離情報を取得する距離情報取得手段と、を有する移動体であって、

前記距離情報に基づいて前記移動体を制御する制御手段をさらに有することを特徴とする移動体。

10

20

30

40

50

【発明の詳細な説明】

【技術分野】

【0001】

光電変換装置、光電変換システムおよび移動体に関する。

【背景技術】

【0002】

アバランシェ（電子なだれ）増倍を利用し、単一光子レベルの微弱光を検出可能な光検出装置が知られている。特許文献1では、光電変換部を構成する半導体領域のP N接合領域において、単一光子に起因する光電荷がアバランシェ増倍を起こすS P A D（S i n g l e P h o t o n A v a l a n c h e D i o d e）を開示している。

【先行技術文献】

【特許文献】

【0003】

【文献】特開2018-201005号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明は、アバランシェフォトダイオード（以下、A P D）における高電界に起因するダークカウントレート（D a r k C o u n t R a t e（以下、D C R））の増加を抑制するために有利な技術を提供することを目的とする。

【課題を解決するための手段】

【0005】

本発明の1つの側面は、光電変換装置に係り、前記光電変換装置は、第1面および第2面を有する半導体層に配置された第1導電型の第1領域と、前記第2面と前記第1領域との間に配置され、前記第1領域とともにアバランシェフォトダイオードのアバランシェ増倍領域を構成する第2導電型の第2領域と、前記第1面に対する正射影において前記第2領域を取り囲むように、前記第1面と前記第2面との間に配置された前記第2導電型の分離領域と、前記分離領域に接するように配置された前記第2導電型のコンタクト領域と、前記第1領域に接続された第1コンタクトプラグと、前記コンタクト領域に接続された第

2 コンタクトプラグと、が複数の画素を構成するように設けられ、第1の方向に前記複数の画素のうちの第1の画素、第2の画素が配され、前記第1の方向に交差する第2の方向に前記第2の画素、第3の画素が配され、前記第1面に対する正射影において、前記第1の画素の前記第1コンタクトプラグの中心と前記第1の画素の前記第2コンタクトプラグの中心とは前記第1の画素の対角方向に配され、前記第1の画素の前記第1コンタクトプラグの中心と前記第1の画素の前記第2コンタクトプラグの中心との距離は、前記第1の画素の前記第2領域の中心と前記第2コンタクトプラグの中心との距離より大きく、前記第1面に対する正射影において、前記第1の画素の前記第1領域と前記第3の画素の前記第1領域との間に前記第2コンタクトプラグは配されていない。

【0006】

10

本発明の他の側面は、光電変換装置に係り、前記光電変換装置は、第1面および第2面を有する半導体層に配置された第1導電型の複数の第1領域と、前記第2面と前記第1領域との間に配置され、前記複数の第1領域のうち対応する1つの第1領域とともに各々がアバランシェフォトダイオードのアバランシェ増倍領域を構成する第2導電型の複数の第2領域と、前記第1面に対する正射影において、前記複数の第2領域を取り囲むように前記第1面と前記第2面との間に配置された前記第2導電型の分離領域と、前記分離領域に接するように配置された前記第2導電型のコンタクト領域と、前記複数の前記第1領域にそれぞれ接続された複数の第1コンタクトプラグと、前記コンタクト領域に接続された第2コンタクトプラグと、が複数の画素を構成するように設けられ、第1の方向に前記複数の画素のうちの第1の画素、第2の画素が配され、前記第1の方向に交差する第2の方向に前記第2の画素、第3の画素が配され、前記第1面に対する正射影において、前記第1の画素の前記第2コンタクトプラグの中心と前記第1の画素の前記第1コンタクトプラグの中心との距離をL1、前記第1の画素の前記第2コンタクトプラグの中心と前記第1の画素の前記第1コンタクトプラグの中心とを通る直線上において、前記第1の画素の前記第1領域と前記第3の画素の前記第1領域との距離をL2としたときに、 $L1 > 0.5L2$  であり、前記第1面に対する正射影において、前記第1の画素の前記第1領域と前記第3の画素の前記第1領域との間に前記第2コンタクトプラグは配されていない。

20

【発明の効果】

【0007】

本発明によれば、APDにおける高電界に起因するDCRの増加を抑制するために有利な技術が提供される。

30

【図面の簡単な説明】

【0008】

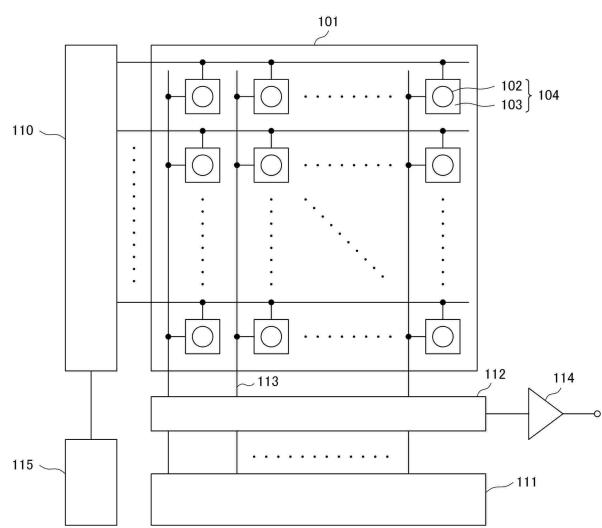

【図1】一実施形態の光電変換装置の構成を例示する図。

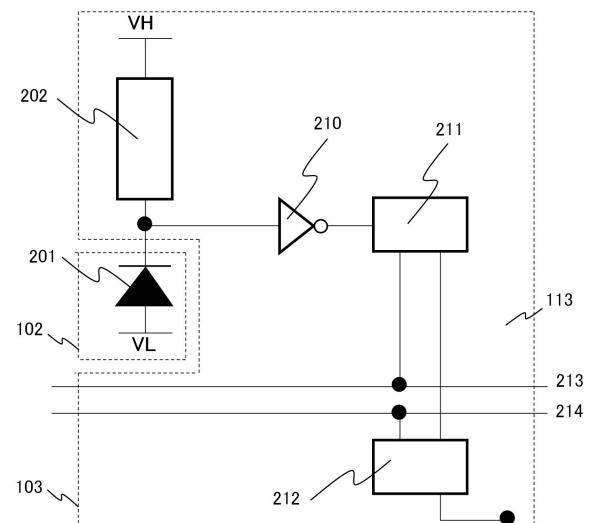

【図2】図1の1つの画素の構成を例示する図。

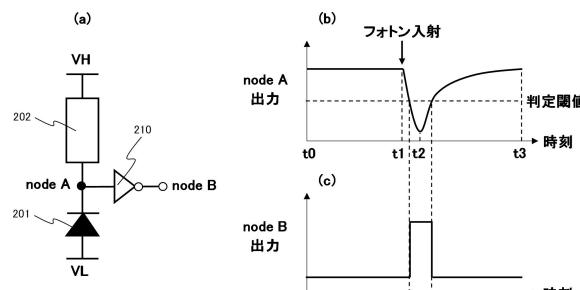

【図3】APDを用いた光子の検出を例示する図。

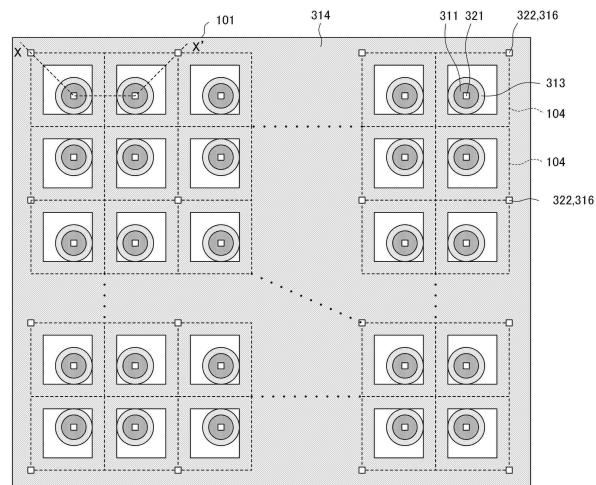

【図4】画素アレイの第1実施形態の平面図。

【図5】図4の一部分の拡大図。

【図6】図4の一部分の拡大図。

【図7】図4のX-X'の断面図。

40

【図8】画素アレイの第2実施形態の平面図。

【図9】画素アレイの第3実施形態の平面図。

【図10】画素アレイの第4実施形態の平面図。

【図11】画素アレイの第5実施形態の平面図。

【図12】画素アレイの第6実施形態の平面図。

【図13】画素アレイの第7実施形態の平面図。

【図14】一実施形態の光電変換システムの構成を示す図。

【図15】一実施形態の車両システムとこれに搭載される撮像を行う光電変換システムの構成を示す図。

【図16】図15の光電変換システムの動作を示す図。

50

【発明を実施するための形態】

【0009】

以下、添付図面を参照して実施形態を詳しく説明する。なお、以下の実施形態は特許請求の範囲に係る発明を限定するものではない。実施形態には複数の特徴が記載されているが、これらの複数の特徴の全てが発明に必須のものとは限らず、また、複数の特徴は任意に組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参照番号を付し、重複した説明は省略する。

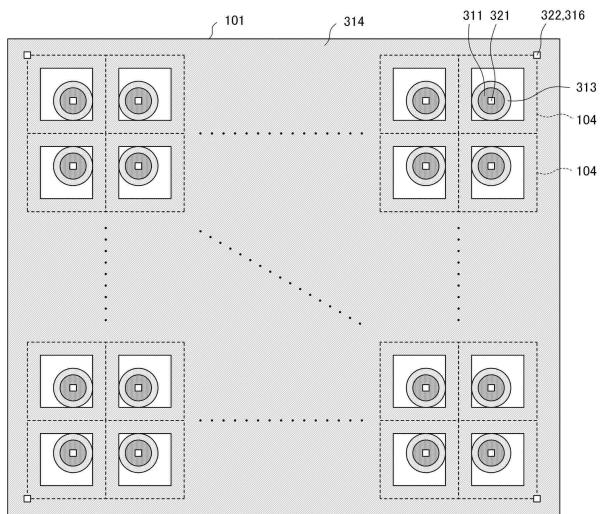

【0010】

図1には、一実施形態の光電変換装置100の構成が例示されている。図1は、光電変換装置100は、画素アレイ101、制御部115、水平走査回路111、読み出し回路112、複数の信号線113、垂直走査回路110を備えうる。画素アレイ101は、複数の画素104が複数の行および複数の列を構成するように配置されうる。各画素104は、APD(アバランシェフォトダイオード)を含む光電変換部102と、信号処理部103とを含みうる。光電変換部102は、光を電気信号へ変換する。信号処理部103は、光電変換部102から出力される電気信号を処理して得られた信号を読み出し回路112に出力するように構成されうる。信号処理部103は、例えば、カウンタおよびメモリ等を含みうる。該メモリにはデジタル値が格納されうる。

10

【0011】

垂直走査回路110は、制御部115から供給される制御信号を受けて、各画素104に制御パルスを供給するように構成されうる。垂直走査回路110は、例えば、シフトレジスタおよびアドレスデコーダ等を含みうる。垂直走査回路110は、画素アレイ101の複数の画素104を行単位で選択するように構成されうる。垂直走査回路110によって選択された行に属する複数の画素104の信号処理部103は、複数の信号線113のうち対応する信号線113に信号を出力する。

20

【0012】

水平走査回路111は、複数の信号線113のうち読み出し回路112によって信号を読み出すべき信号線113を選択するように複数の信号線113を走査するように構成されうる。読み出し回路112は、水平走査回路111によって選択された信号線113の信号を出力回路114に供給しうる。出力回路114は、読み出し回路112から供給された信号を光電変換装置100の外部または内部に備えられたデバイス、例えば、記録部またはプロセッサに出力しうる。

30

【0013】

図1には、複数の画素104が2次元状に配置された例が示されているが、複数の画素104は1次元状に配置されてもよい。また、画素アレイ101は、単一の画素104で置き換えられてもよい。信号処理部103の機能は、必ずしも全ての画素104に個別に設けられる必要はない。例えば、少なくとも2つの画素104によって1つの信号処理部103が共有され、該少なくとも2つの画素104の光電変換部102から出力される信号がその共有された信号処理部103によって順次に処理されてもよい。

30

【0014】

図2には、1つの画素104の構成が例示されている。光電変換部102は、APD201を含む。APD201は、入射した光を光電変換して電荷対を生成する。APD201のアノードには、電圧VLが供給されうる。また、APD201のカソードには、アノードに供給される電圧VLよりも高い電圧VHが供給されうる。アノードおよびカソードには、APD201がアバランシェ増倍動作をするような逆バイアス電圧が供給される。このような電圧が供給された状態において、APD201に光が入射すると、これによって生じた電荷がアバランシェ増倍を起こして、アバランシェ電流が発生する。逆バイアス電圧が供給される場合において、アノードとカソードとの電位差が降伏電圧より大きい状態で動作するガイガーモードと、アノードとカソードとの電位差が降伏電圧の近傍またはそれより小さい状態で動作するリニアモードとがある。ガイガーモードで動作させるAPDをSPADと呼ぶ。例えば、電圧VLは-30V、電圧VHは1Vである。

40

50

## 【0015】

クエンチ素子202は、電圧VHを供給する電源ラインとAPD201のカソードとを接続するように配置されうる。クエンチ素子202は、APD201で生じたアバランシェ電流の変化を電圧に変換する機能を有する。クエンチ素子202は、アバランシェ増倍による信号増倍時に負荷回路（クエンチ回路）として機能し、APD201に供給される電圧を低下させることによってアバランシェ増倍を抑制する動作をする（クエンチ動作）。

## 【0016】

信号処理部103は、例えば、波形整形部210、カウンタ回路211および選択回路212を含みうる。波形整形部210は、光子検出時に得られるAPD201のカソードの電位変化波形を整形することによってパルス信号を出力する。波形整形部210は、例えば、インバータ回路を含みうる。図2では、波形整形部210として1つのインバータで構成された例が示されているが、波形整形部210は、複数のインバータを直列に接続して構成されてもよいし、波形整形効果がある他の回路で構成されてもよい。カウンタ回路211は、波形整形部210から出力されたパルス信号をカウントし、それによって得られたカウント値を保持しうる。また、カウンタ回路211は、垂直走査回路110から駆動線213（図1では不図示）を介して制御パルスpRESが供給されると、保持された信号をリセットする。選択回路212には、垂直走査回路110から駆動線214（図1では不図示）を介して制御パルスpSELが供給されると、カウンタ回路211と信号線113とを電気的に接続する。選択回路212は、例えば、信号線113を駆動するバッファ回路などを含んでもよい。クエンチ素子202と光電変換部102（APD201）との間、および／または、光電変換部102と信号処理部103との間にトランジスタ等のスイッチを配してもよい。光電変換部102に対する電圧VHまたは電圧VLの供給経路にトランジスタ等のスイッチを配してもよい。

10

20

30

## 【0017】

本実施形態では、カウンタ回路211を用いる構成が示されているが、カウンタ回路211の代わりに、時間・デジタル変換回路（Time to Digital Converter：以下、TDC）およびメモリが用いられてもよい。この場合は、光電変換装置100は、パルス検出タイミングを取得する光電変換装置として機能しうる。この場合、波形整形部210から出力されるパルス信号の発生タイミングがTDCによってデジタル信号に変換される。TDCには、パルス信号のタイミングの測定のために、垂直走査回路110から駆動線を介して制御パルスpREF（参照信号）が供給されうる。TDCは、制御パルスpREFを基準として、波形整形部210から出力される信号の入力タイミングを示すデジタル信号を生成する。

## 【0018】

図2の構成例では、APD201のアノードが電圧VLの供給ラインに接続され、APD201のカソードと電圧VHの供給ラインとの間にクエンチ素子202が接続され、該カソードが波形整形部210の入力端子に接続されている。この場合、信号電荷は電子である。このような構成に代えて、APD201のカソードが電圧VHの供給ラインに接続され、APD201のアノードと電圧VLの供給ラインとの間にクエンチ素子202が接続され、該アノードが波形整形部210の入力端子に接続されてもよい。この場合、信号電荷は正孔である。

40

## 【0019】

図3(a)、(b)、(c)を参照しながらAPD201を用いた光子の検出を説明する。図3(a)には、画素104の一部を構成するAPD201、クエンチ素子202および波形整形部210が示されている。波形整形部210の入力側をnodeA、出力側をnodeBとする。図3(b)には、図3(a)のnodeAの電圧波形が示され、図3(c)には、図3(a)のnodeBの電圧波形が示されている。

## 【0020】

時刻t0からt1までの間において、図3(a)のAPD201には、VH-VLの電

50

位差が印加されている。時刻  $t_1$  において光子が入射すると、クエンチ素子 202 にアバランシェ増倍電流が流れ、node A の電圧が降下する。電圧降下量がさらに大きくなり、APD 201 に印加される電位差が小さくなると、APD 201 のアバランシェ増倍が停止し、node A の電圧レベルはある一定値以上降下しなくなる。その後、node A には電圧降下分を補う電流が流れ、時刻  $t_3$  において node A は元の電位レベルに整定する。node A の電圧波形は、波形整形部 210 で整形される。具体的には、node A の電圧が閾値を越えた部分においてアクティブルレベルとなる信号が波形整形部 210 から出力される。

### 【0021】

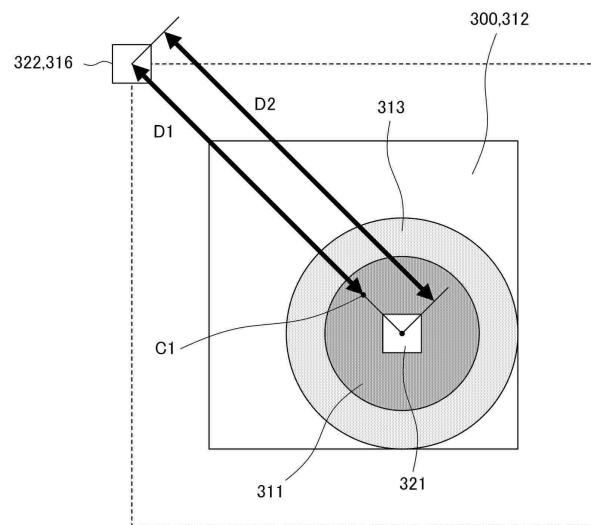

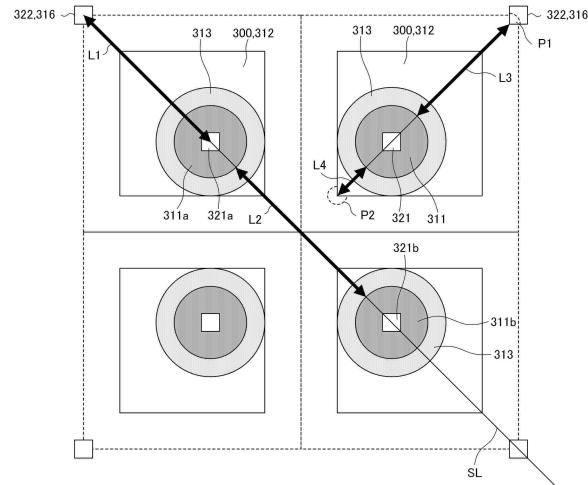

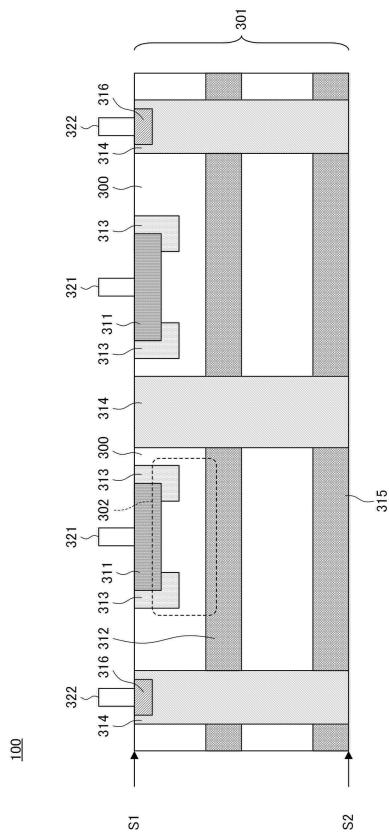

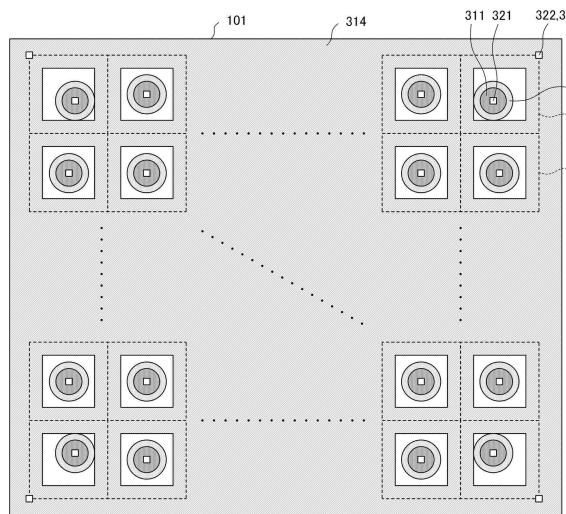

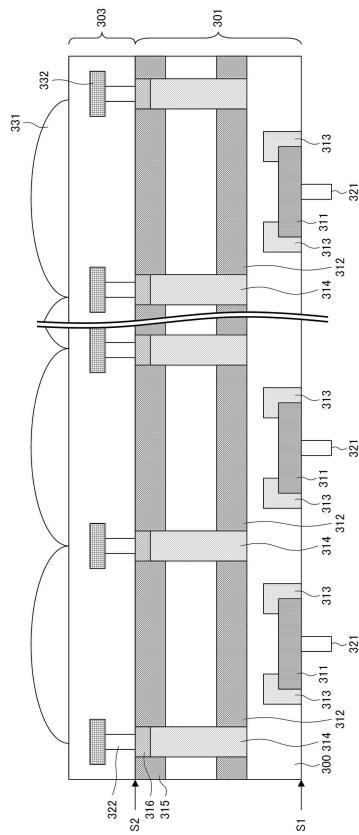

図 4 には、画素アレイ 101 の第 1 実施形態の平面図あるいは平面図が示されている。

図 5、図 6 には、図 4 の一部分の拡大図が示されている。図 7 には、図 4 の X-X' の断面図が示されている。光電変換装置 100 は、第 1 面 S1 および第 2 面 S2 を有する半導体層 301 を含む。図 4 および図 5 は、第 1 面 S1 に対する正射影として理解されてもよいし、第 2 面 S2 に対する正射影として理解されてもよい。以下の説明において、第 1 導電型と第 2 導電型とは、互いに異なる導電型である。第 1 導電型が n 型である場合には第 2 導電型は p 型であり、第 1 導電型が p 型である場合には第 2 導電型は n 型である。なお、図 4、図 5、図 6、図 7 において、説明の簡略化のために信号処理部 103 は省略されている。以降で参照される他の図面についても同様である。第 1 導電型を有する領域および第 2 導電型を有する領域は、いずれも半導体領域であり、換言すれば不純物半導体領域である。以後の説明において、第 1 導電型の領域の不純物濃度は、該領域が第 1 導電型不純物の他に第 2 導電型不純物を含む場合には、第 1 導電型不純物の濃度から第 2 導電型不純物の濃度を差し引いた正味の不純物濃度を意味する。同様に、第 2 導電型の領域の不純物濃度は、該領域が第 2 導電型不純物の他に第 1 導電型不純物を含む場合には、第 2 導電型不純物の濃度から第 1 導電型不純物の濃度を差し引いた正味の不純物濃度を意味する。

### 【0022】

画素 104 は、第 1 導電型の第 1 領域 311 と、第 2 導電型の第 2 領域 312 と、第 2 導電型の分離領域 314 と、第 2 導電型のコンタクト領域 316 とを含みうる。第 1 領域 311 は、半導体層 301 の第 1 面 S1 と第 2 面 S2 との間に配置される。第 2 領域 312 は、半導体層 301 の第 2 面 S2 と第 1 領域 311 との間に配置されうる。第 2 領域 312 は、第 1 領域 311 から離隔して配置されうる。なお、第 1 領域 311 と第 2 領域 312 とは接しててもよい。第 2 領域 312 は、第 1 領域 311 とともに APD 201 を構成しうる。第 1 領域 311 は、APD 201 のカソードであり、第 2 領域 312 は、APD 201 のアノードでありうる。あるいは、第 1 領域 311 は、APD 201 のアノードであり、第 2 領域 312 は、APD 201 のカソードでありうる。

### 【0023】

平面図あるいは平面図（第 1 面 S1 に対する正射影）において、分離領域 314 は、第 2 領域 312 を取り囲むように第 1 面 S1 と第 2 面 S2 との間に配置されうる。また、分離領域 314 は、第 1 領域 311 を取り囲むように第 1 面 S1 と第 2 面 S2 との間に配置されうる。分離領域 314 の境界は、第 1 面 S1 を含んでもよいし、第 1 面 S1 を含まなくててもよい。分離領域 314 の境界は、第 2 面 S2 を含んでもよいし、第 2 面 S2 を含まなくててもよい。コンタクト領域 316 は、分離領域 314 に接するように配置されうる。コンタクト領域 316 の第 2 導電型の不純物濃度は、分離領域 314 の第 2 導電型の不純物濃度よりも高くてよい。コンタクト領域 316 は、その側面が分離領域 314 によって取り囲まれるように配置されてもよいし、分離領域 314 と接するように配置されてもよい。コンタクト領域 316 は、分離領域 314 の第 1 面 S1 側の端面の全域を覆うように配置されてもよい。コンタクト領域 316 は、少なくともその一部が、分離領域 314 と接することが好ましい。これにより、後述する第 2 コンタクトプラグ 322 からコンタクト領域 316 を介して分離領域 314 に電位を供給することができる。また、分離領域 314 と第 2 領域 312 とが接する場合には、分離領域 314 を介して第 2 領域 312 に電位を供給することができる。

10

20

30

40

50

## 【0024】

画素104は、第1領域311に電気的に接続された第1コンタクトプラグ321を含みうる。また、画素104は、コンタクト領域316に電気的に接続された第2コンタクトプラグ322を含みうる。画素104は、第1導電型の313のリング状領域313を更に含んでもよい。リング状領域313の第1導電型の不純物濃度は、第1領域311の第1導電型の不純物濃度よりも低くてよい。リング状領域313は、第1領域311と分離領域314および/またはコンタクト領域316との間の領域における電界の局所的な集中を緩和するように機能しうる。リング状領域313は、第1領域311の側面を覆うように配置されうる。リング状領域313は、第1領域311の面のうち第2領域312に対向する対向面のうち中央部を覆わず、該中央部の外側の周辺部の全部または一部を覆うように配置されうる。第2領域312は、リング状領域313から離隔して配置されうる。分離領域314は、リング状領域313から離隔して配置されうる。図4乃至図6では、リング状領域313は円形であるが、リング状領域313は矩形や多角形であってもよい。

10

## 【0025】

画素104は、第3領域300を含んでもよい。第3領域300は、第1導電型の第1領域311と第2導電型の第2領域312との間、および、第1導電型のリング状領域313と第2導電型の第2領域312との間に配置された第1導電型の領域でありうる。この場合、第3領域300の第1導電型の不純物濃度は、リング状領域313の第1導電型の不純物濃度より低い。あるいは、第3領域300は、第1導電型の第1領域311と第2の導電型の第2領域312との間、および、第1導電型のリング状領域313と第2導電型の第2領域312との間に配置された第2導電型の領域でありうる。この場合、第3領域300の第2導電型の不純物濃度は、第2領域312および分離領域314の第2導電型の不純物濃度より低い。

20

## 【0026】

画素104は、第2導電型の第4領域315を更に含んでもよい。第4領域315は、第2領域312と第2面S2との間に配置されうる。第4領域315の境界は、第2面S2を含んでもよいし、含まなくてよい。第2導電型の第2領域312と第2導電型の第4領域315との間には、第2領域312および第4領域315の第2不純物濃度よりも低い不純物濃度を有する第2導電型の領域が配置されうる。あるいは、第2導電型の第2領域312と第2導電型の第4領域315との間には、第1導電型の領域が配置されうる。第2領域312と第4領域315との間の領域において生成された電荷は、第1領域311と第2領域312とにより形成される強電界領域へと収集される。そして、生成された電荷により強電界領域でアバランシェ増倍が生じる。第4領域315と分離領域314とは接することが好ましい。これにより、第2領域312と第4領域315との間の領域を、第2領域312、分離領域314、第4領域315で取り囲み、生成された電荷を強電界領域へと収集しやすくなる。

30

## 【0027】

第2コンタクトプラグ322および第2導電型のコンタクト領域316は、少なくとも2つの画素104、例えば4つの画素104によって共有されうる。例えば、第2コンタクトプラグ322は、4つの画素104によって取り囲まれ、かつ該4つの画素によって共有されうる。他の観点において、第2コンタクトプラグ322の個数は、第1コンタクトプラグ321の個数より少ない。第2コンタクトプラグ322を共有する4つの画素104は、第2コンタクトプラグ322に関して対称性（点対称性）を有するように配置されうる。他の観点において、任意に抽出されうる隣り合う4つの画素104は、それらの中心に関して対称性（点対称性）を有するように配置されうる。他の観点において、第2領域312は、矩形の形状を有し、第2領域312に割り当てられた第2コンタクトプラグ322は、第2領域312の4つの対角方向のうちの1つの対角方向に配置されうる。あるいは、第3領域300は、矩形の形状を有し、第3領域300に割り当てられた第2コンタクトプラグ322は、第3領域300の4つの対角方向のうちの1つの対角方向に

40

50

配置されうる。

【0028】

カソードを構成する第1領域311に電気的に接続された第1コンタクトプラグ321には、クエンチ素子202を介して電圧VHが供給されうる。アノードを構成する第2領域312に分離領域314を介して電気的に接続された第2コンタクトプラグ322には、カソードに供給される電圧VHよりも低い電圧VLが供給されうる。アノードとカソードには、APD201がアバランシェ増倍動作をするように逆バイアス電圧が供給されうる。このような逆バイアス電圧によって、第1領域311と第2領域312との間のアバランシェ倍増領域302において、入射光の光電変換によって生じる電荷がアバランシェ増倍を引き起こし、アバランシェ電流が流れる。

10

【0029】

画素104のサイズの縮小に伴って、第1導電型の第1領域311と第2導電型のコンタクト領域316との間の距離が小さくなると、第1領域311とコンタクト領域316との間に局所的な高電界領域が形成されうる。そこで、第1導電型の第1領域311と第2導電型のコンタクト領域316との距離は、可能な限り大きくされるべきである。

【0030】

図5に示されるように、平面図あるいは平面視（第1面S1に対する正射影）において、D2 > D1を満たすことが好ましい。ここで、D1は、第2領域312（第3領域300）の中心C1と第2コンタクトプラグ322の中心との距離D1である。D2は、第1コンタクトプラグ321の中心と第2コンタクトプラグ322の中心との距離である。

20

【0031】

他の観点において、図6に示されるように、平面図あるいは平面視（第1面S1に対する正射影）において、L1 > 0.5L2を満たすことが好ましい。ここで、L1は、第2コンタクトプラグ322の中心と複数の第1コンタクトプラグ321のうち第2コンタクトプラグ322に最も近い第1コンタクトプラグ（これを「最近第1コンタクトプラグ」という。）321aの中心との距離である。L2は、第2コンタクトプラグ322の中心と最近第1コンタクトプラグ321aの中心とを通る直線上（直線SL上）において、複数の第1領域311のうち最近第1コンタクトプラグ321aが接続された第1領域（これを「最近第1領域」という。）311aと複数の第1領域311のうち最近第1領域311aに最も近い第1領域（これを「隣接第1領域」という。）311bとの距離である。

30

【0032】

また、他の観点において、図6に示されるように、平面図あるいは平面視（第1面S1に対する正射影）において、L3 > L4を満たすことが好ましい。ここで、L3とL4は、コンタクト領域316、コンタクト領域316に接する分離領域314の第1部分P1、第1領域311、分離領域314の第2部分P2とを通る直線上に位置する。第1領域312は、コンタクト領域316と分離領域314の第2部分P2との間に位置する。L3は、コンタクト領域316と第1領域311との距離である。また、L4は、分離領域314の第2部分P2と第1領域311との距離である。第2部分P2はコンタクト領域316が配されていない分離領域314である。

【0033】

このような構成によれば、第1導電型の第1領域311と第2導電型のコンタクト領域316との間の電界は、画素104のサイズの縮小による影響を受けにくくなる。つまり、画素104のサイズの縮小によるDCRの増加を抑制することができる。

40

【0034】

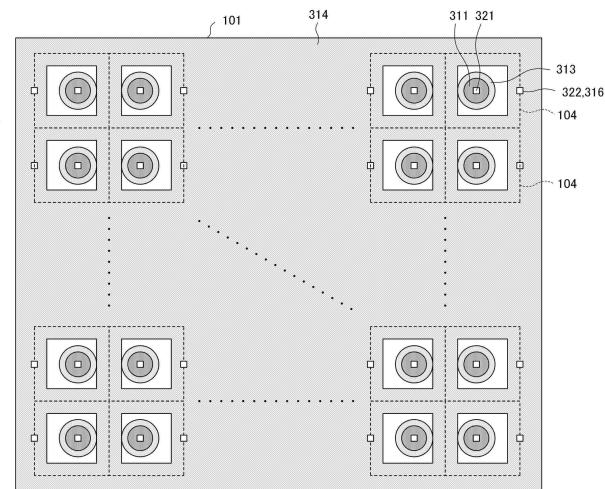

図8には、画素アレイ101の第2実施形態の平面図あるいは平面視が示されている。第2実施形態では、第1実施形態として例示された構成と同様に、半導体層301に配置された複数の画素104によって矩形の画素アレイ101が構成される。各画素104は、APD201を含む光電変換部102を含む。複数の画素104は、半導体層301に配置される。また、第2コンタクトプラグ322は、画素アレイ101の対角方向の各位置に配置され、第2コンタクトプラグ322の総数は4である。第2実施形態では、第2

50

コンタクトプラグ 322 が電気的に接続されたコンタクト領域 316 からの暗電子を減らすために有利であり、これは DCR を低減するために効果的である。第 2 実施形態においても、図 5、図 6 を参照して説明した構成を採用することができ、これにより DCR の増加を抑制することができる。

#### 【0035】

図 9 には、画素アレイ 101 の第 3 実施形態の平面図あるいは平面図が示されている。第 3 実施形態の構成は、第 2 実施形態の変形例であり、第 3 実施形態として言及しない事項は、第 1 および / または第 2 実施形態に従う。第 3 実施形態では、画素アレイ 101 の 4 隅の画素 104 については、図 5、図 6 を参照して説明した構成が採用される。他の画素 104 については、第 1 コンタクトプラグ 321 は、第 2 領域 312 および / または第 4 領域 315 の中心に配置されうるが、該中心からずれた位置に配置されてもよい。他の観点において、4 隅の画素 104 以外の画素 104 は、等間隔で配置されてよく、このような構成は、複数の画素 104 において、光電変換された電荷が信号として検出されるまでの時間ばらつきを低減することができる。

#### 【0036】

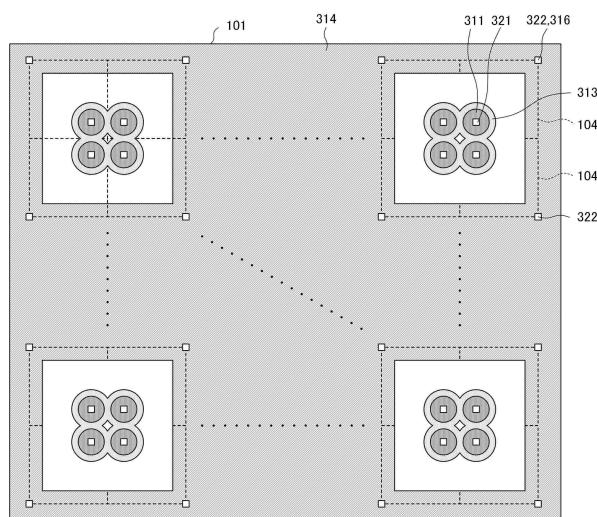

図 10 には、画素アレイ 101 の第 4 実施形態の平面図あるいは平面図が示されている。第 4 実施形態の構成は、第 1 実施形態の変形例であり、第 4 実施形態として言及しない事項は、第 1 実施形態に従う。第 4 実施形態では、第 1 実施形態として例示された構成と同様に、半導体層 301 に配置された複数の画素 104 によって矩形の画素アレイ 101 が構成される。各画素 104 は、APD 201 を含む光電変換部 102 を含む。第 4 実施形態の光電変換装置 100 は、複数の第 2 コンタクトプラグ 322 を有し、複数の第 2 コンタクトプラグ 322 は、2 つの第 2 コンタクトプラグ 322 によって少なくとも 2 つの画素 104 が挟まれるように配置されうる。一例において、複数の第 2 コンタクトプラグ 322 は、2 つの第 2 コンタクトプラグ 322 によって、行方向（信号線 113 に直交する方向）に並んだ少なくとも 2 つの画素 104 が挟まれるように配置されうる。他の例において、第 2 コンタクトプラグ 322 によって少なくとも 2 つの画素 104 が挟まれるように配置されうる。一例において、複数の第 2 コンタクトプラグ 322 は、2 つの第 2 コンタクトプラグ 322 によって、列方向（信号線 113 に平行な方向）に並んだ少なくとも 2 つの画素 104 が挟まれるように配置されうる。第 4 実施形態においても、図 5、図 6 を参照して説明した構成を採用することができ、これにより DCR の増加を抑制することができる。

#### 【0037】

第 4 実施形態は、一例において、2 つの第 2 コンタクトプラグ 322 によって 2 つの画素 104 が挟まれるように配置されるように実施することができる。このような構成では、第 1 実施形態として例示されたように 4 つの画素 104 で 1 つの第 2 コンタクトプラグ 322 が共有される構成よりも第 2 コンタクトプラグ 322 の個数が多い。APD の動作時の電圧降下量を抑制するために有利である。

#### 【0038】

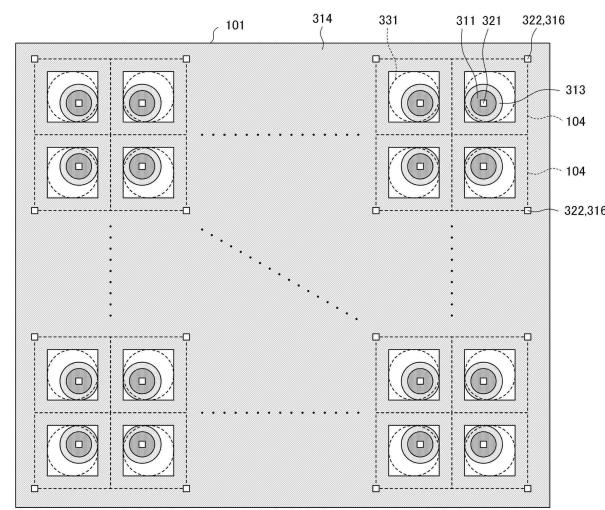

図 11 には、画素アレイ 101 の第 5 実施形態の平面図あるいは平面図が示されている。第 5 実施形態の構成は、第 1 実施形態の変形例であり、第 5 実施形態として言及しない事項は、第 1 実施形態に従う。第 5 実施形態では、第 1 実施形態として例示された構成と同様に、半導体層 301 に配置された複数の画素 104 によって矩形の画素アレイ 101 が構成される。各画素 104 は、APD 201 を含む光電変換部 102 を含む。

#### 【0039】

第 5 実施形態では、仮想矩形の頂点に配置された 4 つの第 2 コンタクトプラグ 322 によって囲まれる 4 つの画素 104 のグループにおいて、4 つのリング状領域 313 が結合して配置されている。このような構成は、画素 104 のサイズがより縮小された場合においても図 6 を参照して説明した条件を満たすために有利である。

#### 【0040】

図 12 には、画素アレイ 101 の第 6 実施形態の平面図あるいは平面図が示されている

10

20

30

40

50

。第6実施形態の構成は、第1乃至第5実施形態の変形例あるいは応用例であり、第6実施形態として言及しない事項は、第1実施形態に従う。第6実施形態では、第1実施形態として例示された構成と同様に、半導体層301に配置された複数の画素104によって矩形の画素アレイ101が構成される。各画素104は、APD201を含む光電変換部102を含む。第6実施形態の光電変換装置100は、各画素104にマイクロレンズ331が設けられている。マイクロレンズ331は、例えば、第1面S1の側に設けられるが、第2面S2の側に設けられてもよい。マイクロレンズ331が第1面S1の側に設けられる場合、マイクロレンズ331と第2面S2との間に第1面S1が位置する。マイクロレンズ331が第2面S2の側に設けられる場合、マイクロレンズ331と第1面S1との間に第2面S2が位置する。

10

#### 【0041】

第1面S1に対する正射影において、マイクロレンズ331は、マイクロレンズ331の中心が第2領域312の中心と一致するように配置されうる。あるいは、第1面S1に対する正射影において、マイクロレンズ331は、マイクロレンズ331の中心が第3領域300の中心と一致するように配置されうる。

#### 【0042】

一例において、第1コントラクトプラグ321は、第1コントラクトプラグ321の中心が第2領域312の中心からずれるように配置され、マイクロレンズ331は、マイクロレンズ331の中心が第2領域312の中心と一致するように配置されうる。一例において、第1コントラクトプラグ321は、第1コントラクトプラグ321の中心が第3領域300の中心からずれるように配置され、マイクロレンズ331は、マイクロレンズ331の中心が第3領域300の中心と一致するように配置されうる。このような構成は、マイクロレンズ331が第1面S1の側に設けられる場合において、光あるいは光子をAPD201が効率的に受けるために有利である。

20

#### 【0043】

図13には、画素アレイ101の第7実施形態の平面図あるいは平面図が示されている。第7実施形態の構成は、第1乃至第6実施形態の変形例あるいは応用例であり、第7実施形態として言及しない事項は、第1実施形態に従う。第7実施形態では、第1実施形態として例示された構成と同様に、半導体層301に配置された複数の画素104によって矩形の画素アレイ101が構成される。第7実施形態は、裏面照射型として構成された光電変換装置100の例を提供する。コントラクト領域316は、第2面S2の側に配され、第2コントラクトプラグ322も第2面S2の側に配置される。第2コントラクトプラグ322には、例えば、電圧VLを供給する電圧ライン332が電気的に接続されうる。このような構成によれば、第1導電型の第1領域311と第2導電型のコントラクト領域316との間の電界は、画素104のサイズの縮小とは無関係になる。よって、画素104のサイズの縮小によるDCRの増加を抑制することができる。

30

#### 【0044】

コントラクト領域316は、分離領域314と接するように配置されうる。また、コントラクト領域316は、第4領域315と接するように配置されうる。一例において、コントラクト領域316の側面は、第4領域315と接触し、第4領域315によって取り囲まれる。他の例において、コントラクト領域316の側面は、分離領域314と接触し、分離領域314によって取り囲まれる。

40

#### 【0045】

分離領域314の第1面S1側の端面は、第1面S1と第2面S2との間に配置されうる。他の観点において、分離領域314の第1面S1側の端面は、第1面S1から離隔して配置されうる。このような構成によれば、第1導電型の第1領域311と第2導電型の分離領域314との間の電界は、画素104のサイズの縮小による影響を受けにくくなる。つまり、画素104のサイズの縮小によるDCRの増加を抑制することができる。

#### 【0046】

他の例において、分離領域314の第1面S1側の端面は、第1面S1に一致してもよ

50

い。このような構成は、画素 104 間の分離特性の改善に有利である。

【0047】

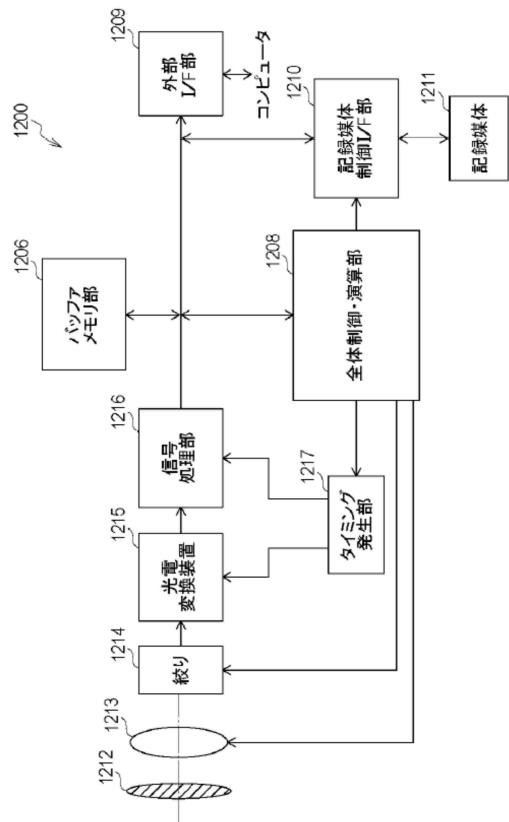

以下、上記の各実施形態の光電変換装置を用いた光電変換システムの一例を説明する。

【0048】

図14は、本実施形態に係る光電変換システム1200の構成を示すブロック図である。本実施形態の光電変換システム1200は、光電変換装置1215を含む。ここで、光電変換装置1215は、上述の実施形態で述べた光電変換装置のいずれかを適用することができる。光電変換システム1200は例えば、撮像システムとして用いることができる。撮像システムの具体例としては、デジタルスチルカメラ、デジタルカムコーダー、監視カメラ等が挙げられる。図14では、光電変換システム1200としてデジタルスチルカメラの例を示している。

10

【0049】

図14に示す光電変換システム1200は、光電変換装置1215、被写体の光学像を光電変換装置1215に結像させるレンズ1213、レンズ1213を通過する光量を可変にするための絞り1214、レンズ1213の保護のためのバリア1212を有する。レンズ1213および絞り1214は、光電変換装置1215に光を集光する光学系である。

【0050】

光電変換システム1200は、光電変換装置1215から出力される出力信号の処理を行う信号処理部1216を有する。信号処理部1216は、必要に応じて入力信号に対して各種の補正、圧縮を行って出力する信号処理の動作を行う。光電変換システム1200は、更に、画像データを一時的に記憶するためのバッファメモリ部1206、外部コンピュータ等と通信するための外部インターフェース部（外部I/F部）1209を有する。更に光電変換システム1200は、撮像データの記録または読み出しを行うための記録媒体制御インターフェース部（記録媒体制御I/F部）1210を有する。記録媒体1211は、光電変換システム1200に内蔵されていてもよく、着脱可能であってもよい。また、記録媒体制御I/F部1210から記録媒体1211との通信や外部I/F部1209からの通信は無線によってなされてもよい。

20

【0051】

更に光電変換システム1200は、各種演算を行うとともにデジタルスチルカメラ全体を制御する全体制御・演算部1208、光電変換装置1215と信号処理部1216に各種タイミング信号を出力するタイミング発生部1217を有する。ここで、タイミング信号などは外部から入力されてもよく、光電変換システム1200は、少なくとも光電変換装置1215と、光電変換装置1215から出力された出力信号を処理する信号処理部1216とを有すればよい。第4の実施形態にて説明したようにタイミング発生部1217は光電変換装置に搭載されていてもよい。全体制御・演算部1208およびタイミング発生部1217は、光電変換装置1215の制御機能の一部または全部を実施するように構成してもよい。

30

【0052】

光電変換装置1215は、画像用信号を信号処理部1216に出力する。信号処理部1216は、光電変換装置1215から出力される画像用信号に対して所定の信号処理を実施し、画像データを出力する。また、信号処理部1216は、画像用信号を用いて、画像を生成する。また、信号処理部1216は、光電変換装置1215から出力される信号に対して測距演算を行ってもよい。なお、信号処理部1216やタイミング発生部1217は、光電変換装置に搭載されていてもよい。つまり、信号処理部1216やタイミング発生部1217は、画素が配された基板に設けられていてもよいし、別の基板に設けられている構成であってもよい。上述した各実施形態の光電変換装置を用いて撮像システムを構成することにより、より良質の画像が取得可能な撮像システムを実現することができる。

40

【0053】

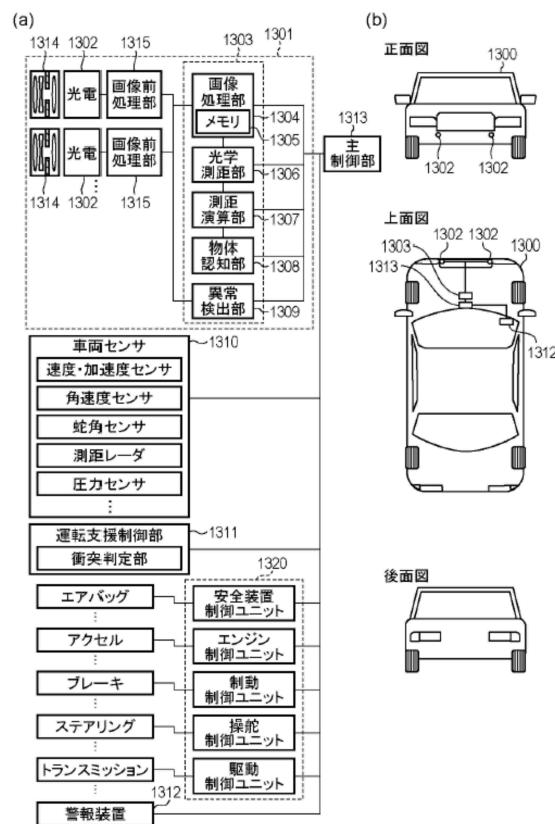

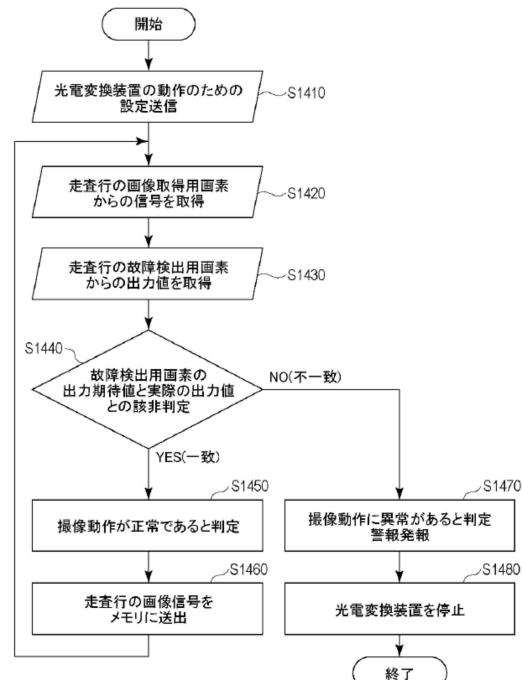

50

本実施形態の光電変換システムおよび移動体について、図15及び図16を用いて説明する。図15は、本実施形態による光電変換システムおよび移動体の構成例を示す概略図である。図16は、本実施形態による光電変換システムの動作を示すフロー図である。本実施形態では、光電変換システムとして、車載カメラの一例を示す。

#### 【0054】

図15は、車両システムとこれに搭載される撮像を行う光電変換システムの一例を示したものである。光電変換システム1301は、光電変換装置1302、画像前処理部1315、集積回路1303、光学系1314を含む。光学系1314は、光電変換装置1302に被写体の光学像を結像する。光電変換装置1302は、光学系1314により結像された被写体の光学像を電気信号に変換する。光電変換装置1302は、上述の各実施形態のいずれかの光電変換装置である。画像前処理部1315は、光電変換装置1302から出力された信号に対して所定の信号処理を行う。画像前処理部1315の機能は、光電変換装置1302内に組み込まれていてもよい。光電変換システム1301には、光学系1314、光電変換装置1302および画像前処理部1315が、少なくとも2組設けられており、各組の画像前処理部1315からの出力が集積回路1303に入力されるようになっている。

#### 【0055】

集積回路1303は、撮像システム用途向けの集積回路であり、メモリ1305を含む画像処理部1304、光学測距部1306、測距演算部1307、物体認知部1308、異常検出部1309を含む。画像処理部1304は、画像前処理部1315の出力信号に対して、現像処理や欠陥補正等の画像処理を行う。メモリ1305は、撮像画像の一次記憶、撮像画素の欠陥位置を格納する。光学測距部1306は、被写体の合焦や、測距を行う。測距演算部1307は、複数の光電変換装置1302により取得された複数の画像データから測距情報の算出を行う。物体認知部1308は、車、道、標識、人等の被写体の認知を行う。異常検出部1309は、光電変換装置1302の異常を検出すると、主制御部1313に異常を発報する。

#### 【0056】

集積回路1303は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよいし、これらの組合せによって実現されてもよい。また、FPGA(Field Programmable Gate Array)やASIC(Application Specific Integrated Circuit)等によって実現されてもよいし、これらの組合せによって実現されてもよい。

#### 【0057】

主制御部1313は、光電変換システム1301、車両センサ1310、制御ユニット1320等の動作を統括・制御する。主制御部1313を持たず、光電変換システム1301、車両センサ1310、制御ユニット1320が個別に通信インターフェースを有して、それぞれが通信ネットワークを介して制御信号の送受を行う(例えばCAN規格)方法も取り得る。

#### 【0058】

集積回路1303は、主制御部1313からの制御信号を受け或いは自身の制御部によって、光電変換装置1302へ制御信号や設定値を送信する機能を有する。

#### 【0059】

光電変換システム1301は、車両センサ1310に接続されており、車速、ヨーレート、舵角などの自車両走行状態および自車外環境や他車・障害物の状態を検出することができる。車両センサ1310は、対象物までの距離情報を取得する距離情報取得手段でもある。また、光電変換システム1301は、自動操舵、自動巡航、衝突防止機能等の種々の運転支援を行う運転支援制御部1311に接続されている。特に、衝突判定機能に関しては、光電変換システム1301や車両センサ1310の検出結果を基に他車・障害物との衝突推定・衝突有無を判定する。これにより、衝突が推定される場合の回避制御、衝突時の安全装置起動を行う。

**【 0 0 6 0 】**

また、光電変換システム 1301 は、衝突判定部での判定結果に基づいて、ドライバーに警報を発する警報装置 1312 にも接続されている。例えば、衝突判定部の判定結果として衝突可能性が高い場合、主制御部 1313 は、ブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして、衝突を回避、被害を軽減する車両制御を行う。警報装置 1312 は、音等の警報を鳴らす、カーナビゲーションシステムやメーターパネルなどの表示部画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

**【 0 0 6 1 】**

発明は上記実施形態に制限されるものではなく、発明の精神及び範囲から離脱することなく、様々な変更及び変形が可能である。従って、発明の範囲を公にするために請求項を添付する。

10

**【 符号の説明 】****【 0 0 6 2 】**

104：画素、300：第3領域、301：半導体層、311：第1領域、312：第2領域、313：リング状領域、314：分離領域、315：リング状領域、316：コンタクト領域、321：第1コンタクトプラグ、322：第2コンタクトプラグ、S1：第1面、S2：第2面

20

30

40

50

【図面】

【図 1】

100

【図 2】

10

【図 3】

【図 4】

20

30

40

50

【 义 5 】

【 囮 6 】

【 义 7 】

【 四 8 】

【図9】

【図10】

10

【図11】

【図12】

20

30

40

50

【図13】

【図14】

10

20

【図15】

【図16】

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開2018-157387 (JP, A)

特開2019-033136 (JP, A)

特開2018-201005 (JP, A)

特開2020-057651 (JP, A)

特開2020-017943 (JP, A)

特開2018-064086 (JP, A)

米国特許出願公開第2019/0319154 (US, A1)

特開2019-102618 (JP, A)

特開2020-174149 (JP, A)

国際公開第2019/087783 (WO, A1)

特表2019-530215 (JP, A)

国際公開第2019/098035 (WO, A1)

国際公開第2020/203222 (WO, A1)

米国特許出願公開第2018/0019268 (US, A1)

- (58)調査した分野 (Int.Cl., DB名)

- H10F 39/18

H10F 30/225

H10F 30/20