(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5631058号

(P5631058)

(45) 発行日 平成26年11月26日(2014.11.26)

(24) 登録日 平成26年10月17日(2014.10.17)

(51) Int.Cl.

H04N 5/374 (2011.01)

F 1

H04N 5/335 740

請求項の数 14 (全 24 頁)

(21) 出願番号 特願2010-116398 (P2010-116398)

(22) 出願日 平成22年5月20日 (2010.5.20)

(65) 公開番号 特開2011-244329 (P2011-244329A)

(43) 公開日 平成23年12月1日 (2011.12.1)

審査請求日 平成25年5月16日 (2013.5.16)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 竹中 真太郎

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 林 英俊

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】撮像装置、撮像システムおよび撮像装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が光電変換部を含む画素が複数行列状に配列された画素アレイと、

前記画素アレイの行を選択する行選択部と、を有し、

前記行選択部は

前記画素アレイの行のアドレスに対応するアドレス信号を時分割多重方式により生成するアドレス生成部と、

前記アドレス生成部で生成された前記アドレス信号をデコードして、対応するデコード値を出力するデコーダと、

信号を読み出す前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第1記憶部と、

初期化を行う前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第2記憶部と、

を含む撮像装置と、タイミング生成部と、を有し、

前記行選択部はさらに、前記光電変換部の電位を固定する前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第3記憶部を含み、

前記タイミング生成部は、同一の行に係る前記第2記憶部と前記第3記憶部について、前記第2記憶部に前記デコード値を記憶する動作と、

前記第3記憶部を初期化する動作と、を同時に行うこと

を特徴とする撮像システム。

10

20

## 【請求項 2】

前記画素の各々はさらに、

前記光電変換部で生成された電荷に基づく信号を出力する増幅トランジスタと、

前記光電変換部に保持された電荷を前記増幅トランジスタのゲートのノードに転送する転送トランジスタと、前記増幅トランジスタのゲートのノードをリセットするリセットトランジスタと、を含み、

前記第3記憶部に記憶された前記デコード値に基づいて、前記転送トランジスタと前記リセットトランジスタとを制御すること

を特徴とする請求項1に記載の撮像システム。

## 【請求項 3】

10

前記増幅トランジスタと、前記リセットトランジスタとで、それぞれのドレイン端子が共通に接続されること

を特徴とする請求項2に記載の撮像システム。

## 【請求項 4】

前記増幅トランジスタと、前記リセットトランジスタとで、それぞれのドレイン端子が異なる電源に接続されること

を特徴とする請求項2に記載の撮像システム。

## 【請求項 5】

前記画素の各々はさらに、前記画素を選択状態あるいは非選択状態にする選択トランジスタを含むこと

20

を特徴とする請求項2ないし4のいずれかに記載の撮像システム。

## 【請求項 6】

複数の前記画素で、前記増幅トランジスタおよび前記リセットトランジスタとを共有することを特徴とする請求項2ないし5のいずれかに記載の撮像システム。

## 【請求項 7】

前記タイミング生成部は、さらに、1行の前記画素に係る信号の読み出しを行う水平同期期間を規定する水平同期信号を出力することを特徴とする請求項1ないし6のいずれかに記載の撮像システム。

## 【請求項 8】

前記撮像装置は、同一の前記水平同期期間において、前記第1記憶部に基づいて信号を読み出す前記画素の初期化と並行して、前記第2記憶部に基づいて選択する画素の初期化を行うこと

30

を特徴とする請求項1ないし7のいずれかに記載の撮像システム。

## 【請求項 9】

前記撮像装置の画素部に像を形成する光学系と、

前記撮像装置から出力された信号を処理して画像データを生成する映像信号処理部と、をさらに備えたこと

を特徴とする請求項1ないし8のいずれかに記載の撮像システム。

## 【請求項 10】

各々が光電変換部を含む画素が複数行列状に配列された画素アレイと、

40

前記画素アレイの行を選択する行選択部と、を有し、

前記行選択部は

前記画素アレイの行のアドレスに対応するアドレス信号を時分割多重方式により生成するアドレス生成部と、

前記アドレス生成部で生成された前記アドレス信号をデコードして、対応するデコード値を出力するデコーダと、

信号を読み出す前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第1記憶部と、

初期化を行う前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第2記憶部と、

50

を含む撮像装置の駆動方法であって、

前記行選択部はさらに、前記光電変換部の電位を固定する前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第3記憶部を含み、

前記第3記憶部で記憶された行の電位を固定している期間に、前記第2記憶部で記憶された行のシャッタ走査を行い、

さらに、同一の行に係る前記第2記憶部と前記第3記憶部について、

前記第2記憶部に前記デコード値を記憶する動作と、前記第3記憶部を初期化する動作と、を同時に行うことの特徴とする撮像装置の駆動方法。

【請求項11】

同一の水平同期期間において、前記第1記憶部に基づいて信号を読み出す前記画素の初期化と並行して、前記第2記憶部に基づいて選択する画素の初期化を行うことを特徴とする請求項10に記載の撮像装置の駆動方法。 10

【請求項12】

前記画素アレイの一部を切り出して信号を読み出す切り出し動作において、

前記第1記憶部に基づく、前記画素アレイからの信号を読み出す読み出し走査は第1の方向に走査を行い、

前記読み出し走査の開始行から前記第1の方向とは異なる側にある非読み出し行は、前記第3記憶部に基づく前記光電変換部の電位を固定する走査を、前記第1の方向とは異なる第2の方向に行うこと

を特徴とする請求項10または11に記載の撮像装置の駆動方法。 20

【請求項13】

前記画素アレイの一部を切り出して信号を読み出す切り出し動作において、

前記第1記憶部に基づく、前記画素アレイからの信号を読み出す読み出し走査は第1の方向に走査を行い、

前記読み出し走査の終了行から前記第1の方向と同じ側にある非読み出し行は、前記第3記憶部に基づく前記光電変換部の電位を固定する走査を、前記第1の方向に行うこと

を特徴とする請求項10ないし12のいずれかに記載の撮像装置の駆動方法。

【請求項14】

前記画素の各々はさらに、

前記光電変換部で生成された電荷に基づく信号を出力する増幅トランジスタと、 30

前記光電変換部に保持された電荷を前記増幅トランジスタのゲートのノードに転送する転送トランジスタと、

前記増幅トランジスタのゲートのノードをリセットするリセットトランジスタと、を含み、

複数の前記画素で、前記増幅トランジスタおよび前記リセットトランジスタとを共有し、

前記第1記憶部に基づいて信号が読み出される前記画素と前記増幅トランジスタと前記リセットトランジスタとを共有する前記画素は、前記第2記憶部に基づいてシャッタ走査を行い、前記第3記憶部に基づいて光電変換部の電位を固定しないこと

を特徴とする請求項10ないし13のいずれかに記載の撮像装置の駆動方法。 40

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像装置、撮像システムおよび撮像装置の駆動方法に関する。

【背景技術】

【0002】

電子ビデオカメラや電子スチルカメラに用いられる撮像装置として、X-Yアドレス型センサとも呼ばれるものが知られている。X-Yアドレス型センサは、アドレスを指定することによって特定の位置の画素から信号を得ることができる。この特徴によって、X-Yアドレス型センサでは、全ての画素から信号を得る全画素読み出しモードや、一部の行

や列をスキップして他の画素から信号を得る間引き読み出しモードなどを実現することができる。

#### 【0003】

特許文献1には、間引き読み出しを行った際に、信号を読み出さない、すなわち間引く行の画素に対して、光電変換素子を常にリセット状態に固定することが記載されている。

#### 【0004】

特許文献2には、例えば間引き読み出しモードにおける複雑なシャッタ動作を行うために、シャッタ走査を行う行のアドレスを記憶する第1の記憶手段と、読み出し走査を行う行のアドレスを記憶する第2の記憶手段とを設けることが記載されている。また、画素を構成するトランジスタの一部であって、各画素に蓄積された電荷を一時的に保持するフローティングディフュージョンが複数の画素で共有される、画素共有技術についても記載されているとともに、その際に画素を選択するための回路が記載されている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0005】

【特許文献1】特開2000-350103号公報

【特許文献2】特開2008-288903号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

特許文献1では、間引く行が固定して使われるように構成されているため、自由に間引く行を変更することが困難である。

#### 【0007】

特許文献2の技術によれば、デコーダを用いているために間引く行を自由に設定することができる。しかしながら、特許文献2は、シャッタ走査を行う行のアドレスを記憶する第1の記憶手段と、読み出し走査を行う行のアドレスを記憶する第2の記憶手段しか持たないため、間引く行を常にリセット状態に保持することができない。

#### 【0008】

本発明は、上述の問題を鑑みて、間引く行の光電変換部をリセット状態に固定しながら、信号を読み出す行とシャッタ行とを設定することが可能な撮像装置、撮像システム、および撮像装置の駆動方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0009】

上記課題を解決する本発明の一の側面は、各々が光電変換部を含む画素が複数行列状に配列された画素アレイと、前記画素アレイの行を選択する行選択部と、を有し、前記行選択部は前記画素アレイの行のアドレスに対応するアドレス信号を時分割多重方式により生成するアドレス生成部と、前記アドレス生成部で生成された前記アドレス信号をデコードして、対応するデコード値を出力するデコーダと、信号を読み出す前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第1記憶部と、初期化を行う前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第2記憶部と、を含む撮像装置と、タイミング生成部と、を有し、前記行選択部はさらに、前記光電変換部の電位を固定する前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第3記憶部を含み、前記タイミング生成部は、同一の行に係る前記第2記憶部と前記第3記憶部について、前記第2記憶部に前記デコード値を記憶する動作と、前記第3記憶部を初期化する動作と、を同時に行うことを特徴とする撮像システムである。

#### 【0010】

上記課題を解決する本発明の別の側面は、各々が光電変換部を含む画素が複数行列状に配列された画素アレイと、前記画素アレイの行を選択する行選択部と、を有し、前記行選択部は前記画素アレイの行のアドレスに対応するアドレス信号を時分割多重方式により生成するアドレス生成部と、前記アドレス生成部で生成された前記アドレス信号をデコード

10

20

30

40

50

して、対応するデコード値を出力するデコーダと、信号を読み出す前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第1記憶部と、初期化を行う前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第2記憶部と、を含む撮像装置の駆動方法であって、前記行選択部はさらに、前記光電変換部の電位を固定する前記画素アレイの行のアドレスに対応する前記デコード値を記憶する第3記憶部を含み、前記第3記憶部で記憶された行の電位を固定している期間に、前記第2記憶部で記憶された行のシャッタ走査を行い、さらに、同一の行に係る前記第2記憶部と前記第3記憶部について、前記第2記憶部に前記デコード値を記憶する動作と、前記第3記憶部を初期化する動作と、を同時に行うことの特徴とする撮像装置の駆動方法である。

## 【発明の効果】

10

## 【0011】

本発明によれば、間引く行の光電変換部をリセット状態に固定しながら、信号を読み出す行とシャッタ行とを設定することが可能となる。

## 【図面の簡単な説明】

## 【0012】

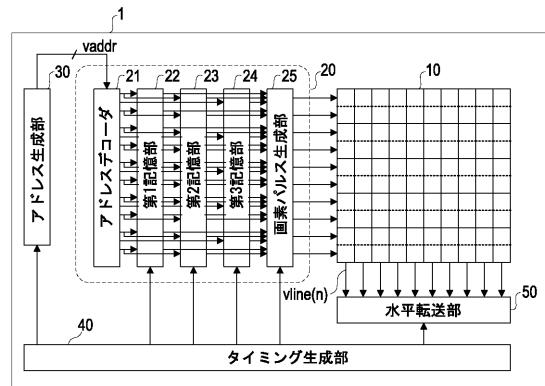

## 【図1】本発明に係る撮像装置の概略を示すブロック図

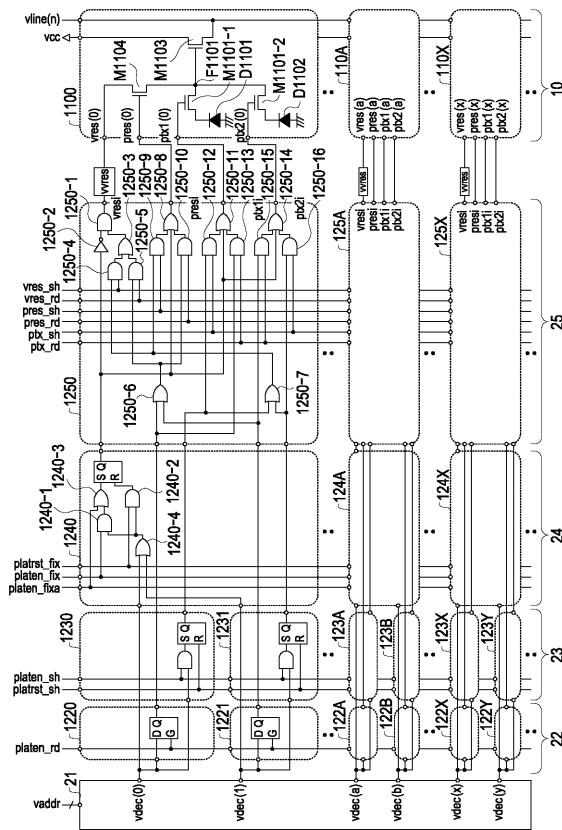

## 【図2】実施例1に係る撮像装置の構成例を示す回路図

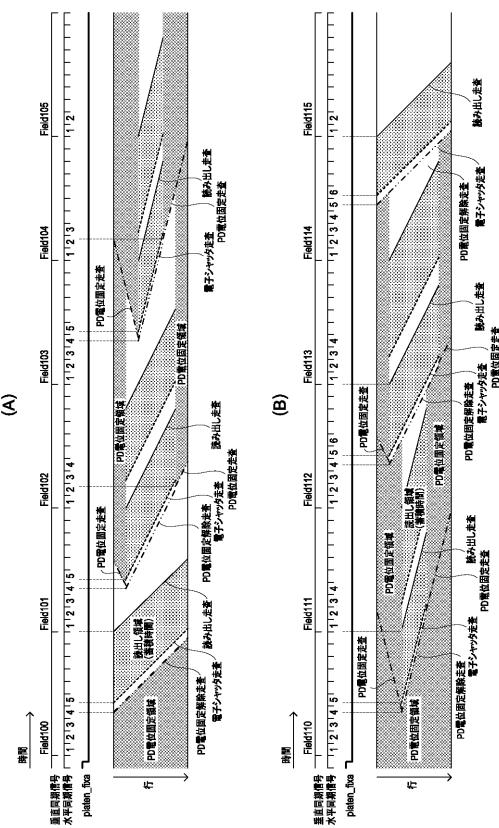

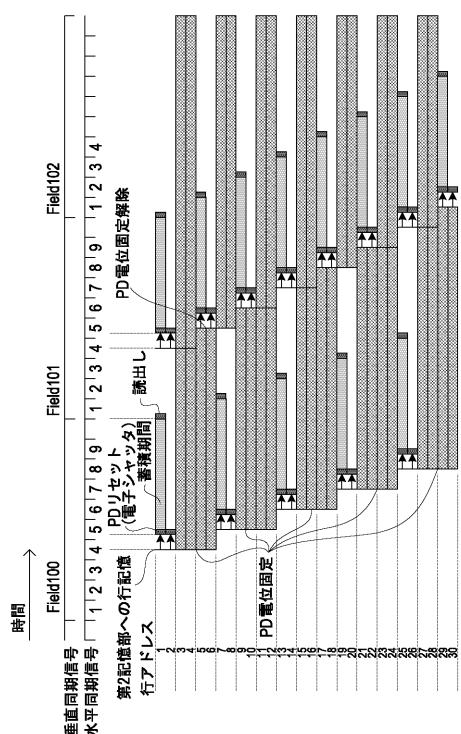

## 【図3】実施例1に係る撮像装置の動作の概略を示すタイミング図

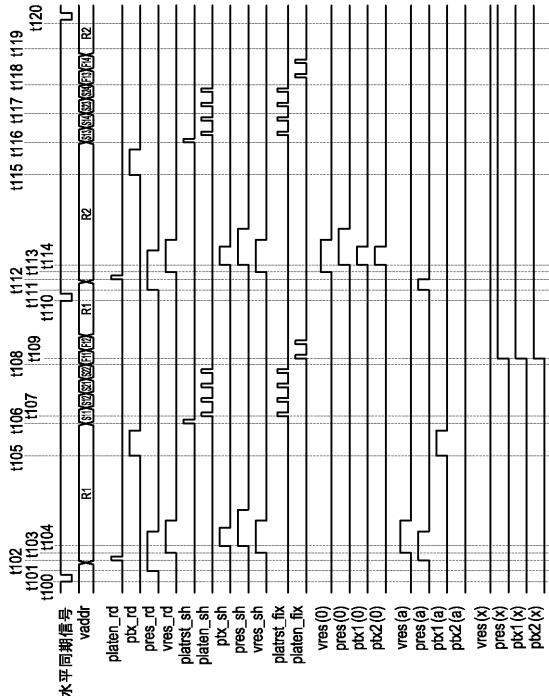

## 【図4】実施例1に係る撮像装置の動作を示すタイミング図

## 【図5】実施例2に係る撮像装置の構成例を示す回路図

20

## 【図6】実施例2に係る撮像装置の動作を示すタイミング図

## 【図7】実施例3に係る撮像装置の構成例を示す回路図

## 【図8】実施例3に係る撮像装置の動作を示すタイミング図

## 【図9】実施例4に係る撮像装置の動作を示すタイミング図

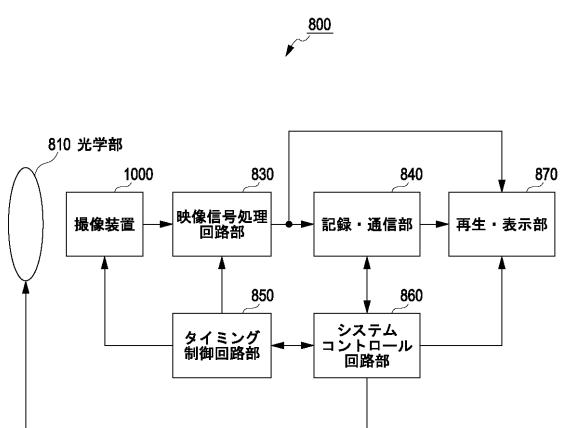

## 【図10】実施例5に係る撮像システムの概略を示すブロック図

## 【発明を実施するための形態】

## 【0013】

## (実施例1)

図面を参照しながら、本発明に係る第1の実施形態を説明する。

## 【0014】

30

図1は、本発明に係る撮像装置の概略構成を示すブロック図である。撮像装置1は、画素アレイ10、行選択部20、アドレス生成部30、タイミング生成部40、および水平転送部50を含む。これらの構成は全て同一半導体基板上に形成しても良いし、その一部を異なる半導体基板上に形成しても良い。

## 【0015】

画素アレイ10は、画素が複数行列状に配列されており、隣接する行の画素間で回路を共有する構成である。以下では、互いに回路を共有する複数の画素を画素ブロックと呼ぶ。つまり、画素アレイ10は、複数の画素ブロックが行列状に配列されたものであると言い換えることができる。

## 【0016】

40

行選択部20は画素アレイ10に隣接して配置されており、画素アレイ10の画素を行単位で選択する。

## 【0017】

行選択部20はさらにアドレスデコーダ21、第1記憶部22、第2記憶部23、第3記憶部24、および画素パルス生成部25を含む。アドレスデコーダ21は、アドレス生成部30で生成されたアドレス値をデコードしたデコード値を出力し、アドレス値に対応するアドレスを選択する。

## 【0018】

第1記憶部22は、アドレスデコーダ21から出力されたデコード値を記憶するもので、その出力は画素アレイ10において画素から信号を読み出す行のアドレスとして用いら

50

れる。

【0019】

第2記憶部23は、アドレスデコーダ21から出力されたデコード値を記憶するもので、その出力は画素アレイ10において画素が持つ光電変換部をリセットする行のアドレスとして用いられる。

【0020】

第3記憶部24は、アドレスデコーダ21から出力されたデコード値を記憶するもので、その出力は画素アレイ10において画素ブロックにおいて複数の画素間で共有される素子を制御するために用いられる。

【0021】

アドレス生成部30は、タイミング生成部40から供給される信号に基づいてアドレス値を生成し、行選択部20に供給する。アドレス生成部30は時分割多重方式によってアドレス信号vaddrを出力することで、1個のアドレスデコーダが複数のアドレスを選択できるように構成されている。より具体的には、アドレス生成部はアドレス値を生成する回路を複数有し、タイミング生成部40からの信号に基づいてそのいずれかの回路からの出力を選択してアドレス信号vaddrとして出力する構成が考えられる。

【0022】

タイミング生成部40は、アドレス生成部30がアドレス値を生成するタイミングを制御する信号を供給するほか、行選択部20および水平転送部50の動作タイミングを制御する信号を供給する。

【0023】

水平転送部50は、画素アレイ10から垂直信号線vline(n)を介して読み出された信号を、出力端子outから出力させるための回路である。具体的には、垂直信号線vline(n)毎に設けられた増幅器やAD変換器、CDS回路、ラインメモリ回路などを含み、水平走査回路によって出力端子outに順次出力させる。ラインメモリ回路は、アナログメモリでも良いし、SRAMやラッチ回路からなるデジタルメモリでも良い。

【0024】

水平走査回路をデコーダで構成することによって、任意の列にアクセスできるようにしてもよい。これにより、行選択部20との組合せでランダムアクセスが実現できる。行選択部および水平走査回路がデコーダであっても、アドレスの順に従って順次走査を行っても良いことは無論である。

【0025】

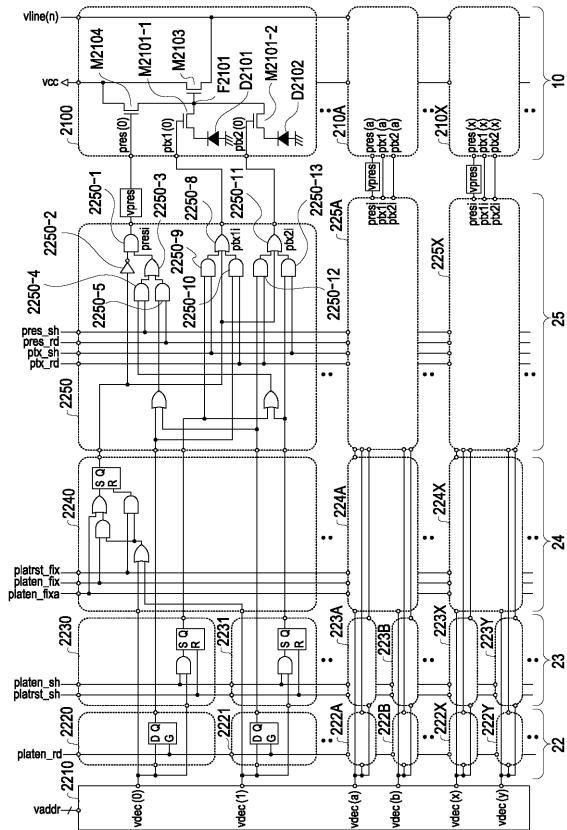

図2は、図1に示した構成のうち、タイミング生成部40と水平転送部50を除く部分を抜き出し、より詳細に示した回路図である。

【0026】

画素アレイ10は、複数の画素ブロック1100、…110A、…110Xが配列されており、図2ではそのうちの6行×1列の画素ブロックを抜き出している。画素ブロック1100は、2個の画素を含む。1行目の画素は、光電変換部であるフォトダイオードD1101、転送トランジスタM1101-1、増幅トランジスタM1103、およびリセット部であるリセットトランジスタM1104を含む。転送トランジスタM1101-1が導通すると、フォトダイオードD1101に保持された電荷が増幅トランジスタM1103のゲートのノードに転送される。図示はしていないが、増幅トランジスタM1103のゲートは半導体基板上にあっては転送トランジスタM1101-1の一方の主電極を兼ねる浮遊拡散部(Floating Diffusion)と接続され、フォトダイオードからの電荷は浮遊拡散部に転送される。以下では浮遊拡散部のことをFD部と称する。増幅トランジスタM1103は、一方の主電極が電源電圧Vccの供給を受けるとともに、他方の主電極が選択トランジスタM1105を介して垂直信号線vline(n)に接続される。増幅トランジスタM1103は、そのゲートのノードをリセットトランジスタM1104によって動作電位に設定されると、垂直信号線vline(n)に接続された不図示の定電流源とでソースフォロワ回路を形成し、FD部の電位に応じた信号

10

20

30

40

50

を出力する。リセットトランジスタM1104は、一方の主電極がFD部と接続され、導通すると、その他の主電極に供給される電位に応じてFD部をリセットする。2行目の画素は、フォトダイオードD1102、転送トランジスタM1101-2、画素出力部である増幅トランジスタM1103、リセット部であるリセットトランジスタM1104、および選択トランジスタM1105を含む。これらの2個の画素は、増幅トランジスタM1103とリセットトランジスタM1104とを共有する。画素ブロック1101、1102、・・・は画素ブロック1100と同じく、隣接する2行の画素で増幅トランジスタM1103とリセットトランジスタM1104とを共有する。

#### 【0027】

アドレスデコーダ21には、タイミング生成部40からの制御信号に基づいてアドレス生成部30が出力したアドレス信号vaddrが入力される。アドレス信号vaddrは画素の行数に対応した信号で、本実施例では0～Xに対応する。アドレス信号vaddrとして「0」がアドレス生成部から与えられると、アドレスデコーダはデコード値vdec(0)のみ論理的Highレベルを出力し、その他は論理的Lowレベルを出力する。アドレス信号vaddrが1、2、・・・、A、・・・、Xであっても同様である。

#### 【0028】

第1記憶部22を構成する複数の第1記憶回路1220、1221、・・・は、それぞれ1ビットデータを記憶するDラッチを含む。第1記憶回路1220に含まれるDラッチはD端子がアドレスデコーダ21の出力vdec(0)と接続され、G端子は信号platent\_rdを伝達する配線と接続される。第1記憶回路1221、1222、・・・は第1記憶回路1220と同じくDラッチを含むが、D端子が接続されるアドレスデコーダ21の出力が異なる。信号platent\_rdを伝達する配線は、第1記憶部の他の記憶回路1221、1222、・・・にも共通に接続される。

#### 【0029】

第2記憶部23を構成する第2記憶回路1230、1231、・・・はそれぞれAND回路と、当該AND回路の出力がS端子に接続されたSRラッチとを含む。AND回路の一方の入力端子はアドレスデコーダ21の出力vdec(0)と接続され、他方の入力端子は、信号platent\_shを伝達する配線と接続される。SRラッチのR端子は信号platrst\_shを伝達する配線と接続される。信号platrst\_shを伝達する配線は、第2記憶部の他の第2記憶回路1231、1232、・・・にも共通に接続される。

#### 【0030】

第3記憶部24を構成する第3記憶回路1240、1241、・・・はそれぞれSRラッチと、AND回路とOR回路とを含む。AND回路1240-1は、その一方の入力端子が信号platent\_fixを伝達する配線と接続され、他方の入力端子はOR回路1240-4の出力端子と接続される。AND回路1240-2は、その一方の入力端子が信号platrst\_fixを伝達する配線と接続され、他方の入力端子はOR回路1240-4の出力端子と接続される。さらに、AND回路1240-2の出力端子はSRラッチのR端子と接続される。OR回路1240-3は、その一方の入力端子が信号platent\_fixaを伝達する配線と接続され、他方の入力端子はAND回路1240-1の出力端子と接続される。さらに、OR回路1240-3の出力端子は、SRラッチのS端子と接続される。OR回路1240-4は、その一方の入力端子がアドレスデコーダ21の出力端子vdec(0)と接続され、他方の入力端子はアドレスデコーダ21の出力端子vdec(1)と接続される。

#### 【0031】

画素パルス生成部25を構成する画素パルス生成回路1250、1251、・・・をAND回路とOR回路とNOT回路とを用いて構成した例を示しているが、回路の構成は本例の構成に限定されない。画素パルス生成回路1250は、信号vresi、presi、ptx1i、ptx2iを出力し、それぞれ画素ブロック1100のvres(0)、pres(0)、ptx1(0)、ptx2(0)として画素ブロック1100に供給さ

10

20

30

40

50

れる。

【0032】

信号 *vresi* は、AND 回路 1250-1 の出力として現れる。AND 回路 1250-1 の一方の入力端子は、SR ラッチ 1240-3 の出力を NOT 回路 1250-2 で反転された信号を受け、他方の入力端子は OR 回路 1250-3 からの出力を受ける。OR 回路 1250-3 の一方の入力端子は AND 回路 1250-4 の出力端子と接続され、他方の入力端子は AND 回路 1250-5 の出力端子と接続される。AND 回路 1250-4 の一方の入力端子は、第 2 記憶回路 1230 と 1231 との出力の論理和を出力する OR 回路 1250-7 の出力端子と接続され、他方の入力端子は信号 *vres\_sh* を伝達する配線と接続される。AND 回路 1250-5 の一方の入力端子は、第 1 記憶回路 1220 と 1221 との出力の論理和を出力する OR 回路 1250-6 の出力端子と接続され、他方の入力端子は信号 *vres\_rd* を伝達する配線と接続される。信号 *vresi* は、画素ブロック 1100 のリセットトランジスタ M1104 のドレイン端子に電圧信号を供給する電源供給部 *vvres* に入力される。電源供給部 *vvres* は、信号 *vresi* の High および Low レベルに対応した電圧信号を出力するように構成されている。電源供給部 *vvres* が output する電圧信号は、信号 *vresi* の論理レベルが示す電位と同じである必要はなく、信号 *vresi* の論理レベルの電位とは異なる電位に設定しうる。ここでは電源供給部 *vvres* を設ける例を示したが、信号 *vresi* を直接リセットトランジスタ M1104 のドレイン端子に与えるような構成でも良い。電源供給部 *vvres* を設けることの利点は、AND 回路 1250-1 の High あるいは Low レベルとは異なる電圧値に *vres(0)* を設定できる点である。

【0033】

信号 *presi* は、3 入力からなる OR 回路 1250-8 の出力として現れる。OR 回路 1250-8 は、AND 回路 1250-9 の出力、第 3 記憶回路 1240 の出力、および AND 回路 1250-10 の出力の論理和を出力する。AND 回路 1250-9 は、OR 回路 1250-7 の出力と信号 *pres\_sh* との論理積を出力する。AND 回路 1250-10 は、OR 回路 1250-6 の出力と信号 *pres\_rd* との論理積を出力する。

【0034】

信号 *ptx1i* は、3 入力からなる OR 回路 1250-11 の出力として現れる。OR 回路 1250-11 は、AND 回路 1250-12 の出力、第 3 記憶回路 1240 の出力、および AND 回路 1250-13 の出力の論理和を出力する。AND 回路 1250-12 は、第 2 記憶回路 1230 の出力と信号 *ptx\_sh* との論理積を出力する。AND 回路 1250-13 は、第 1 記憶回路 1220 の出力と信号 *ptx\_rd* との論理積を出力する。

【0035】

信号 *ptx2i* は、3 入力からなる OR 回路 1250-14 の出力として現れる。OR 回路 1250-14 は、AND 回路 1250-15 の出力、第 3 記憶回路 1240 の出力、および AND 回路 1250-16 の出力の論理和を出力する。AND 回路 1250-15 は、第 1 記憶回路 1221 の出力と信号 *ptx\_rd* との論理積を出力する。また、AND 回路 1250-16 は第 2 記憶回路 1231 の出力と信号 *ptx\_sh* との論理積を出力する。

【0036】

なお、信号 *platent\_rd*、*plaen\_sh*、*platrst\_sh*、*platrst\_fix*、*platent\_fix*、*platent\_fixa*、*vres\_sh*、*vres\_rd*、*ptx\_rd*、*ptx\_sh*、*pres\_rd*、および *pres\_sh* はタイミング生成部 40 で生成される。

【0037】

次に、図 3 を参照しながら、本発明を適用しうる動作の概略を説明する。図 3 (A) は、フィールドの進行とともに、信号を読み出す領域を狭める、ズームイン動作を示してい

10

20

30

40

50

る。不図示の外部からタイミング生成部 40 に垂直同期信号が入力されると、各フィールドにおける動作が開始され、不図示の外部からタイミング生成部 40 に水平同期信号が入力されると、各行に係る動作が行われるものである。また、図中「読み出し領域」については当該領域の画素から信号を読み出すことを、「PD 電位固定領域」については当該領域の画素が持つフォトダイオードの電位を一定電位に保つことを示している。

#### 【0038】

ここでは Field 100 に先だって全画素の PD の電位が固定されており、Field 100 に、電位が固定された状態を解除する走査が行われる。その後、読み出し行に係る電子シャッタ走査が行われ、蓄積時間が開始する。予め設定された蓄積時間の経過の後に読み出し走査が行われる。全画素の PD 電位を固定する際には、図 2 において信号 p1 10 a\_t\_e\_n\_f\_i\_x\_a を High レベルとする。

#### 【0039】

Field 101 からは、Field 100 よりも狭い領域を読み出し領域として設定し、信号を読み出さない領域は PD 電位固定領域として制御される。

#### 【0040】

その後、Field 103 からはさらに狭い領域を読み出し領域として設定することで、ズームイン動作を実現している。

#### 【0041】

一方、図 3 (B) は、フィールドの進行とともに、信号を読み出す領域を広げる、ズームアウト動作を示している。ズームアウト動作においても読み出し領域以外は PD 電位固定領域に設定される。 20

#### 【0042】

このように、信号を読み出さない行の PD の電位を固定することで、電子シャッタ行のように駆動させることができなくなるため、シャッタ走査に起因するノイズや消費電力を低減することが可能となる。

#### 【0043】

さらに、図 3 に示す動作によれば、電子シャッタ走査に同調して PD 電位固定解除走査と PD 電位固定走査を行うため、ズームインやズームアウト動作に伴う読み出し領域の変更を継ぎ目なく連続して行うことが可能となる。

#### 【0044】

一般に画素アレイには、PD が遮光された OB (Optical Black) 画素が設けられ、図 1 を例に取れば、画素アレイ 10 の上から数行を OB 画素とすることがある。図 3 は、説明の簡単のために OB 画素に関する動作は図示していないが、OB 画素が画素アレイ 10 に設けられている場合には、OB 画素の読み出し走査の終了時刻の直後に、読み出し領域の読み出し走査の開始時刻がくるように動作を行う。 30

#### 【0045】

このような条件では PD 電位固定走査を、電子シャッタ走査や読み出し走査の走査方向とは逆方向に進めることが有効である。これは、PD 電位固定領域に隣接する OB 画素と読み出し領域の画素とで、隣接する PD 電位固定領域の画素の蓄積時間を近づけることが可能となるためで、PD 電位固定領域の画素からの影響を OB 画素と読み出し領域の画素とで近づけられるためである。この動作を別の言い方をすれば、切り出し動作において、第 1 記憶部に記憶されたアドレスに基づいて行われる読み出し走査を第 1 の方向 (図中上から下) に行う。そして、読み出し走査の開始行よりも上側、すなわち、第 1 の方向とは異なる側にある非読み出し行は、第 3 記憶部に記憶されたアドレスに基づく PD の電位を固定する走査を、第 1 の方向とは異なる第 2 の方向に行う。また、読み出し走査の終了行よりも下側、すなわち、第 1 の方向と同じ側にある非読み出し行は、第 3 記憶部に記憶されたアドレスに基づく PD の電位を固定する走査を、第 1 の方向に行うものである。 40

#### 【0046】

ところで、図 3 の Field 102 中の 4 回目の水平同期信号が入力されるタイミングでは、Field 101 で蓄積を開始した読み出し領域の読み出し走査に加えて、PD 電 50

位固定領域のフォトダイオードを一定電位に保つ制御と、Field 102に係る電子シャッタ走査とが行われる。このように、撮像装置が有する複数の画素に対して3通りの制御が必要になる状況が考えられる。しかしながら、従来の技術では読み出し行のアドレスを記憶する記憶部と、電子シャッタ行のアドレスを記憶する記憶部のみしか備えなかつたために、複数通りのリセット動作を実現することができなかつた。

#### 【0047】

これに対して本発明は、PDの電位を固定する行のアドレスを記憶する第3記憶部を備えることで、電子シャッタ行の動作とは異なる動作を実現している。

#### 【0048】

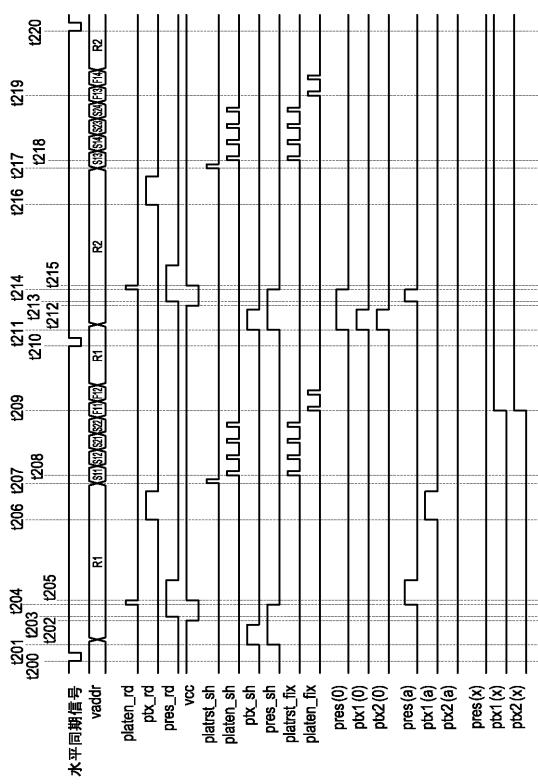

次に、図4に示したタイミング図を参照しながら図1および2に示す撮像装置1のより具体的な動作を説明する。

#### 【0049】

ここでは、画素アレイ10のうちのA行の画素から信号を読み出した後、XおよびY行の画素のフォトダイオードの電位を固定し、さらに、0行および1行を含む合計4行の画素に係るシャッタ動作を行う場合を例にとって説明する。シャッタ動作とはすなわちフォトダイオードをリセットすることで、画素の初期化とも称する。図4の時刻t100においては、第1記憶部22のDラッチ、第2記憶部23および第3記憶部24のSRラッチはいずれもLowレベルを保持しているものとする。

#### 【0050】

まず、時刻t100に不図示の外部から水平同期信号がタイミング生成部40に入力されると、タイミング生成部40は時刻t101に信号pres\_rdをHighレベルにする。このとき、信号vres\_rdがLowレベルにあるため、時刻t100から始まる水平同期期間の前の水平同期期間で信号を読み出された行の画素が非選択状態になる。なお、水平同期信号とは、1行の前記画素に係る信号の読み出しを行う水平同期期間を規定する信号である。

#### 【0051】

時刻t102におけるアドレス信号vaddrはR1='a'であるので、アドレスデコーダ21の出力のうちvdec(a)のみがHighレベルとなる。時刻t102から信号plate\_n\_rdが一時的にHighレベルになると、a行目の第1記憶回路122AのDラッチの出力のみがHighレベルとなる。また時刻t102では、信号pres\_rdもHighレベルであるため、画素パルス生成部125AのOR回路1250-10がHighレベルとなり、信号pres(a)がHighレベルとなって、画素プロック110AのリセットトランジスタM1104が導通する。

#### 【0052】

時刻t103に信号vres\_rdがHighレベルになると、AND回路1250-1の出力がHighレベルになる。これにより、a行目の画素が含まれる画素プロック110AのFD部F1101が高い電位にリセットされて、当該画素プロックが選択状態になる。選択状態とは、増幅トランジスタM1103が垂直信号線vline(n)に設けられた不図示の定電流源とともにソースフォロワを構成し、増幅トランジスタFD部F1101の電位に対応する信号が垂直信号線vline(n)に現れる状態を意味する。時刻t103に垂直信号線vline(n)に現れる信号は、画素プロック110AのFD部F1101をリセットしたことに対応する信号で、この信号にはリセットトランジスタM1104、増幅トランジスタM1103、FD部F1101に起因するノイズ成分が含まれている。水平転送部50にCDS回路を備える構成であれば、この後、信号pres\_rdがLowレベルに変化した後に、この期間に垂直信号線vline(n)に現れる出力をサンプリングする。

#### 【0053】

時刻t104に、信号ptx\_shおよびpres\_shがHighレベルとなるが、ここでは第2記憶部23および第3記憶部24のSRラッチはいずれもLowレベルを保持しているので、AND回路1250-12および1250-9はいずれもLowレベル

10

20

30

40

50

のままである。

【0054】

時刻  $t_{105}$  に信号  $p_{tx\_rd}$  が  $HIGH$  レベルになると、第1記憶回路  $122A$  の SR ラッチの出力との論理積により AND 回路  $1250-13$  が  $HIGH$  レベルとなり、信号  $p_{tx1(a)}$  のみが  $HIGH$  レベルとなる。これにより  $a$  行目の PD に保持された電荷が、転送トランジスタ  $M_{1101-1}$  を介して FD 部  $F_{1101}$  に転送されると、転送された電荷量に応じて FD 部  $F_{1101}$  の電位が変化し、垂直信号線  $vline(n)$  に現れる信号も合わせて変化する。この時の信号は、FD 部  $F_{1101}$  をリセットした直後のレベルに対して、光電変換によって生じた電荷量に応じた分だけ変化しているので、CDS 回路に保持されたノイズ成分との差分を取ることで、ノイズ成分を低減することができる。以上によって 1 行目の画素から信号を読み出す動作が終了する。 10

【0055】

時刻  $t_{106} \sim t_{108}$  の期間では、0 行目および 1 行目の画素を含む、合計 4 行のシャッタ行アドレスを第2記憶回路に記憶させる動作が行われるとともに、これらの行に係る第3記憶回路がリセットされる。 20

【0056】

時刻  $t_{106}$  に、アドレス信号  $v_{addr}$  が  $S_{11}$  に変化するとともに、信号  $p_{platr\_st\_sh}$  が一時的に  $HIGH$  レベルになる。これにより、第2記憶部の各記憶回路の SR ラッチがリセットされる。この時の  $S_{11}$  は「0」を示す。 20

【0057】

時刻  $t_{107}$  に信号  $p_{platensh}$  が  $HIGH$  レベルになると、 $S_{11}$  で示される 0 行目の画素に係る第2記憶回路の SR ラッチがセットされ、その出力が  $HIGH$  レベルに遷移する。また、時刻  $t_{107}$  には信号  $p_{platrst\_fix}$  が  $HIGH$  レベルになるので、0 行目の画素に係る第3記憶回路の SR ラッチがリセットされる。つまり、同一行について、第2記憶部にアドレスを書き込む動作と、第3記憶部をリセットする動作とが同時に行われるものである。 20

【0058】

この後、アドレス信号が  $S_{12}$ 、 $S_{21}$ 、 $S_{22}$  と変化して、 $S_{11}$  の時と同様の操作が行われる。ここで  $S_{12}$  は「1」に、 $S_{21}$  と  $S_{22}$  は別の 2 行のアドレスに対応する値である。 30

【0059】

時刻  $t_{108}$  からは、PD の電位を固定する行に係る第3記憶回路の SR ラッチを設定する動作が行われる。時刻  $t_{108}$  にアドレス信号  $v_{addr}$  が  $F_{11}$  に変化する。ここでは  $F_{11}$  は「x」を示す。 20

【0060】

時刻  $t_{109}$  に信号  $p_{platen\_fix}$  が  $HIGH$  レベルになると、第3記憶回路  $124X$  の SR ラッチがセットされ、その出力が  $HIGH$  レベルに遷移する。第3記憶回路  $124X$  の SR ラッチが  $HIGH$  レベルを出力すると、対応する画素パルス生成部  $125X$  の出力のうち信号  $p_{resi}$ 、 $p_{tx1i}$ 、および  $p_{tx2i}$  が  $HIGH$  レベルになる。これにより、画素ブロック  $110X$  内のリセットトランジスタ  $M_{1104}$  並びに転送トランジスタ  $M_{1101-1}$ 、 $M_{1101-2}$  が導通する。ここで、リセットトランジスタ  $M_{1104}$  のドレイン端子に与えられる電圧は  $Low$  レベルであるため、画素ブロック  $110X$  のフォトダイオード  $D_{1101}$  および  $D_{1102}$  はともに低い電位に保たれる。 40

【0061】

同様に、アドレス信号  $v_{addr}$  が  $F_{12}$  に遷移し、対応する行の第3記憶回路  $124X$  の SR ラッチがセットされる。ここでは  $F_{12}$  は「y」であるため、 $F_{11}$  の時と同じで、第3の記憶回路  $124X$  の SR ラッチがセットされることになる。そのため、信号  $p_{res(x)}$ 、 $p_{tx1(x)}$ 、および  $p_{tx2(x)}$  の状態は時刻  $t_{109}$  から変わらない。 50

【0062】

時刻  $t_{110}$  に水平同期信号  $H\bar{D}$  が入力されて、次の行に係る動作が行われる。

【0063】

時刻  $t_{111}$  に信号  $pres\_rd$  が  $High$  レベルになると、時刻  $t_{103}$  に読み出し行としてセットされた  $a$  行に係る画素パルス生成部  $125A$  から、  $High$  レベルの信号  $pres_i$  が出力される。つまり、画素ブロック  $110A$  のリセットトランジスタ  $M_{1104}$  に与えられる信号  $pres(a)$  が  $High$  レベルになり、画素ブロック  $110A$  の  $FD$  部  $F_{1101}$  が低い電位にリセットされ、非選択状態になる。

【0064】

その後、アドレス信号  $addr$  が  $R_2$  に遷移すると、アドレスデコーダ  $21$  の出力のうち  $vdec(b)$  のみが  $High$  レベルとなる。ここでは  $R_2$  は「 $b$ 」を示す。時刻  $t_{112}$  に信号  $platenn_rd$  が一時的に  $High$  レベルになると、 $a+1$  行目の第 1 記憶回路  $122A$  の  $D$  ラッチの出力のみが  $High$  レベルとなる。また、時刻  $t_{112}$  では、信号  $pres_rd$  も  $High$  レベルであるため、信号  $pres(a)$  が  $High$  レベルとなって、画素ブロック  $110A$  のリセットトランジスタ  $M_{1104}$  が導通する。

【0065】

時刻  $t_{113}$  に信号  $pres_rd$  が  $High$  レベルになると、 $AND$  回路  $1250-1$  の出力が  $High$  レベルになる。これにより、 $b$  行目の画素が含まれる画素ブロック  $110A$  の  $FD$  部  $F_{1101}$  が高い電位にリセットされ、当該画素ブロックが選択状態になる。時刻  $t_{113}$  に垂直信号線  $vine(n)$  に現れる信号は、画素ブロック  $110A$  の  $FD$  部  $F_{1101}$  をリセットしたことに対応する信号である。この信号にはリセットトランジスタ  $M_{1104}$ 、増幅トランジスタ  $M_{1003}$ 、 $FD$  部  $F_{1101}$  に起因するノイズ成分が含まれている。水平転送部  $50$  に  $CDS$  回路を備える構成であれば、この後、信号  $pres_rd$  が  $Low$  レベルに変化した後に、この期間に垂直信号線  $vine(n)$  に現れる出力をサンプリングする。

【0066】

時刻  $t_{114}$  に、信号  $ptx_sh$  および  $pres_sh$  が  $High$  レベルとなる。ここでは第 2 記憶部  $23$  の  $SR$  ラッチのうち  $S_{11}$ 、 $S_{12}$ 、 $S_{21}$ 、 $S_{22}$  に係る行、すなわち、 $0$  行目と  $1$  行目を含む計  $4$  行分の第 2 記憶部  $23$  のみが  $High$  レベルを出力する。これにより、これらの行に対応する信号  $pres(0)$ 、 $ptx1(0)$ 、 $ptx2(0)$ 、などが  $High$  レベルになる。信号  $pres_sh$  が  $High$  レベルである期間に  $4$  行のフォトダイオードが高い電位にリセットされ、その後、信号  $pres_sh$  が  $Low$  レベルに遷移した後に信号  $pres_sh$  が  $Low$  レベルに遷移する。これにより、フォトダイオードがリセットされた  $4$  行の画素が含まれる画素ブロックが非選択状態になる。このように、時刻  $t_{114}$  から始まる期間では、信号  $pres_rd$ 、 $pres_r$ 、 $ptx_sh$ 、 $pres_sh$ 、および  $pres_sh$  が同時に  $High$  レベルとなる。これによって、第 1 記憶部に基づいて信号を読み出す画素の  $FD$  部の初期化と、第 2 記憶部に基づいて選択する画素の初期化とが同時に行われる。

【0067】

時刻  $t_{115}$  以降は、アドレス信号  $addr$  の値を除いては先に説明した時刻  $t_{105}$  以降の動作と同じであるので、説明を省略する。

【0068】

アドレス信号  $addr$  が  $F_{12}$  に設定された後、次の行に係る動作が開始されるまでの期間に  $R_1$  に設定する例を示したが、この期間のアドレス信号  $addr$  はいずれの記憶回路にも保持されないので、 $R_1$  以外の値に設定しても良い。

【0069】

以上で説明したように、本実施例によれば、信号が画素から読み出されない行におけるフォトダイオードのリセット方法を複数設定することができる。これにより、時刻  $t_{107}$  から時刻  $t_{109}$  までの期間に第 2 記憶回路がセットされる行は、次の水平同期期間に一時的に  $PD$  がリセットされる一方で、時刻  $t_{109}$  からの期間で第 3 記憶回路がセットされる行は、 $PD$  がリセットされ続ける。

10

20

30

40

50

## 【0070】

## (実施例2)

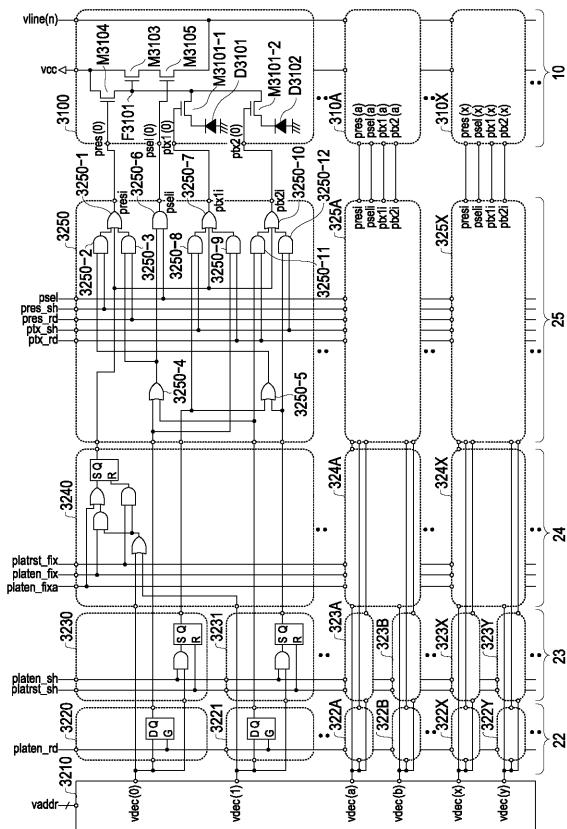

図面を参照しながら、本発明に係る第2の実施例を説明する。図5は、図1に示した構成のうち、タイミング生成部40と水平転送部50とを除く部分を抜き出し、より詳細に示した回路図である。以下では、実施例1との相違点を中心に説明する。

## 【0071】

実施例1においては、各画素ブロックにおけるリセットトランジスタのドレイン端子と増幅トランジスタのドレイン端子とは、互いに異なる電源が供給される構成になっていた。これに対して図5に示す本実施例に係る構成では、各画素ブロックにおけるリセットトランジスタと増幅トランジスタとで、両者のドレイン端子が共通に接続され、共通の電源が与えられる。この構成によれば、画素の制御に必要な信号線の数が実施例1の構成と比べて減少するので、撮像装置の縮小化に有利なものとなる。

10

## 【0072】

画素ブロックの構成の変更に伴い、画素パルス生成部25の構成も実施例1のものとは異なっている。図5では、画素パルス生成回路2250、2251、…をAND回路、OR回路、およびNOT回路を用いて構成する例を示した。画素パルス生成回路2250は、信号presi、ptx1i、ptx2iを出力し、それぞれ画素ブロック2100の、pres(0)、ptx1(0)、ptx2(0)として画素ブロック2100に供給される。

## 【0073】

20

信号presiは、AND回路2250-1の出力として現れる。AND回路2250-1は、NOT回路2250-2の出力とOR回路2250-3との論理積を出力する。NOT回路2250-2は、第3記憶回路2240の出力の反転信号を出力する。OR回路2250-3は、AND回路2250-4の出力とAND回路2250-5の出力との論理和を出力する。AND回路2250-4は、信号pres\_shとOR回路2250-7の出力との論理積を出力する。AND回路2250-5は、信号pres\_rdとOR回路2250-6の出力との論理積を出力する。また、OR回路2250-6は、第1記憶回路2220および2221の出力の論理和を出力し、OR回路2250-7は、第2記憶回路2230および2231の出力の論理和を出力する。信号presiは、リセットゲート制御部v\_presに供給される。リセットゲート制御部v\_presは、信号presiの論理レベルに応じた信号をpres(n)(nは任意の行)として画素ブロックに与えるものである。リセットゲート制御部を省略し、信号presiを直接信号pres(n)として画素ブロックに供給しても良い。

30

## 【0074】

信号ptx1iは、3入力からなるOR回路2250-8の出力として現れる。OR回路2250-8は、AND回路2250-9の出力、第3記憶回路2240の出力、およびAND回路2250-10の出力の論理和を出力する。AND回路2250-9は、第2記憶回路2230の出力と信号ptx\_shとの論理積を出力する。AND回路2250-10は、第1記憶回路2220の出力と信号ptx\_rdとの論理積を出力する。

40

## 【0075】

信号ptx2iは、3入力からなるOR回路2250-11の出力として現れる。OR回路2250-11は、AND回路2250-12の出力、第3記憶回路2240の出力、およびAND回路2250-13の出力の論理和を出力する。AND回路2250-12は、第1記憶回路2221の出力と信号ptx\_rdとの論理積を出力する。また、AND回路2250-13は、第2記憶回路2231の出力と信号ptx\_shとの論理積を出力する。

## 【0076】

なお、信号plat\_en\_rd、plat\_en\_sh、plat\_rst\_sh、plat\_rst\_fix、plat\_en\_fix、plat\_en\_fixa、ptx\_rd、ptx\_sh、pres\_rd、及びpres\_shはタイミング生成部40で生成される

50

。

## 【0077】

なお、画素パルス生成部の構成は図示したものに限られない。また、第1から第3記憶部の構成は実施例1と共通なので説明を省略する。

## 【0078】

次に、図6に示したタイミング図を参照しながら図1および5に示す撮像装置の動作を説明する。

## 【0079】

ここでは、画素アレイ10のうちのA行の画素から信号を読み出した後、XおよびY行の画素のフォトダイオードの電位を固定し、さらに、0行および1行を含む合計4行の画素に係るシャッタ動作を行う場合を例にとって説明する。繰り返しになるが、シャッタ動作とはすなわちフォトダイオードをリセットすることで、画素の初期化とも称する。図6の時刻t200においては、第1記憶部22のDラッチ、第2記憶部23および第3記憶部24のSRラッチはいずれもLowレベルを保持しているものとする。また、増幅トランジスタおよびリセットトランジスタのドレイン端子に与えられる電圧vccはHighレベルにあるものとする。

10

## 【0080】

実施例1の動作と大きく異なるのは、画素を選択あるいは非選択状態にするための制御方法である。ここでは実施例1で説明した動作との相違点を中心に説明する。

## 【0081】

20

図6の時刻t200に不図示の外部から水平同期信号がタイミング生成部40に入力されると、タイミング生成部40は時刻t201に信号ptx\_shおよびpres\_shをHighレベルにする。ここでは第2および第3記憶回路のSRラッチのいずれもがLowレベルを保持しているので、画素ブロックに供給される信号に変化はない。

## 【0082】

時刻t202に信号vccがLowレベルに遷移し、時刻t203に信号pres\_rdがHighレベルになる。この時点では第1記憶回路のDラッチのいずれもがLowレベルを保持しているので、画素ブロックに供給される信号に変化はない。

## 【0083】

時刻t204に信号plate\_rdがHighレベルになると、アドレス信号R1で示されるa行目の第1記憶回路222AのDラッチがHighレベルの信号を出力するようになる。これにより、画素パルス生成部225Aから出力される信号presiがHighレベルとなり、結果、画素ブロック210Aに与えられる信号pres(a)がHighレベルとなる。これにより、画素ブロック210AのリセットトランジスタM2104が導通する。この時点では、信号vccがLowレベルなので、画素ブロック210AのFD部F2101は低い電位にリセットされ、非選択状態になる。

30

## 【0084】

時刻t205に信号vccがHighレベルになる。この時、信号pres\_rd、ひいては信号pres(a)がHighレベルであるので、画素ブロック210AのFD部F2101が高い電位にリセットされて、当該画素ブロックが選択状態になる。この後、信号pres\_rdがLowレベルになると、画素ブロック210Aを選択状態にする動作が終了する。これ以降の期間で垂直信号線vline(n)に現れる信号は、画素ブロック210AのFD部をリセットしたことに対応する信号である。この信号にはリセットトランジスタM2104、増幅トランジスタM2103、FD部F2101に起因するノイズ成分が含まれている。水平転送部50にCDS回路を備える構成であれば、信号pres\_rdがLowレベルに変化した後に、垂直信号線vline(n)に現れる出力をサンプリングする。

40

## 【0085】

時刻t206に信号ptx\_rdがHighレベルになると、第1記憶回路222AのDラッチの出力との論理積によりAND回路2250-5の出力がHighレベルとなり

50

、信号  $p_t \times 1 (a)$  のみが  $H_i g h$  レベルになる。これにより  $a$  行目の  $P D$  に保持された電荷が、転送トランジスタ  $M_{2101-1}$  を介して  $FD$  部  $F_{2101}$  に転送されると、転送された電荷量に応じて  $FD$  部  $F_{2101}$  の電位が変化し、垂直信号線  $v_{line}(n)$  に現れる信号も合わせて変化する。このときの信号は、 $FD$  部  $F_{2101}$  をリセットした直後のレベルに対して、光電変換によって生じた電荷量に応じた分だけ変化しているので、 $CDS$  回路に保持されたノイズ成分との差分を取ることで、ノイズ成分を低減することができる。以上によって 1 行目の画素から信号を読み出す動作が終了する。

#### 【0086】

時刻  $t_{207} \sim t_{210}$  の期間では、0 行目および 1 行目の画素を含む、合計 4 行のシャッタ行アドレスを第 2 記憶回路に記憶させる動作が行われるとともに、これらの行に係る第 3 記憶回路がリセットされる。この期間の動作は図 4 に示した時刻  $t_{106} \sim t_{111}$  の動作と同じなので、説明を省略する。

10

#### 【0087】

時刻  $t_{210}$  に水平同期信号  $HD$  が入力されて、次の行に係る動作が行われる。

#### 【0088】

時刻  $t_{211}$  に信号  $p_t \times sh$  および  $pres_sh$  が  $H_i g h$  レベルになると、時刻  $t_{207} \sim t_{210}$  の期間で第 2 記憶回路がセットされた行の画素の転送トランジスタおよびリセットトランジスタが導通する。これにより、4 行の画素のシャッタ動作が行われる。

20

#### 【0089】

時刻  $t_{212}$  に信号  $vcc$  が  $L_o w$  レベルになった後、時刻  $t_{213}$  に信号  $pres_rd$  が  $H_i g h$  レベルになると、信号  $pres_rd$  が  $H_i g h$  レベルになることで、 $a$  行目の第 1 記憶回路の D ラッチとの論理積により信号  $pres(a)$  が  $H_i g h$  レベルになる。

20

#### 【0090】

時刻  $t_{214}$  から信号  $plate_n_rd$  が一時的に  $H_i g h$  レベルになる。これにより、アドレス信号  $vaddr$  は  $R_2$  が表す行の第 1 ラッチ回路の D ラッチのみが  $H_i g h$  レベルを出力することになるので、信号  $pres(a)$  は  $L_o w$  レベルになる。このタイミングで信号  $vcc$  は  $L_o w$  レベルであるため、 $a$  行目の画素の  $FD$  部  $F_{2101}$  の電位は低い電位にあり、非選択状態となる。

30

#### 【0091】

時刻  $t_{215}$  に信号  $vcc$  が再び  $H_i g h$  レベルとなった後に信号  $pres_rd$  が  $L_o w$  レベルとなることで、 $R_2$  のアドレス信号で示される行の画素の  $FD$  部  $F_{2101}$  の電位が高い電位となり、この行が選択状態となる。

#### 【0092】

これ以降の動作は既に説明した動作が繰り返されるものなので、説明を省略する。

#### 【0093】

以上説明した本実施例においても、信号が画素から読み出されない行におけるフォトダイオードのリセット方法を複数設定することができる。これにより、時刻  $t_{208}$  から時刻  $t_{209}$  までの期間に第 2 記憶回路がセットされる行は、次の水平同期期間に一時的に  $PD$  がリセットされる一方で、時刻  $t_{209}$  からの期間で第 3 記憶回路がセットされる行は、 $PD$  がリセットされ続ける。特に本実施例によれば、各画素ブロックにおけるリセットトランジスタと増幅トランジスタとで、両者のドレイン端子が共通に接続され、共通の電源が与えられるので、撮像装置の縮小化に有利なものとなる。

40

#### 【0094】

##### （実施例 3）

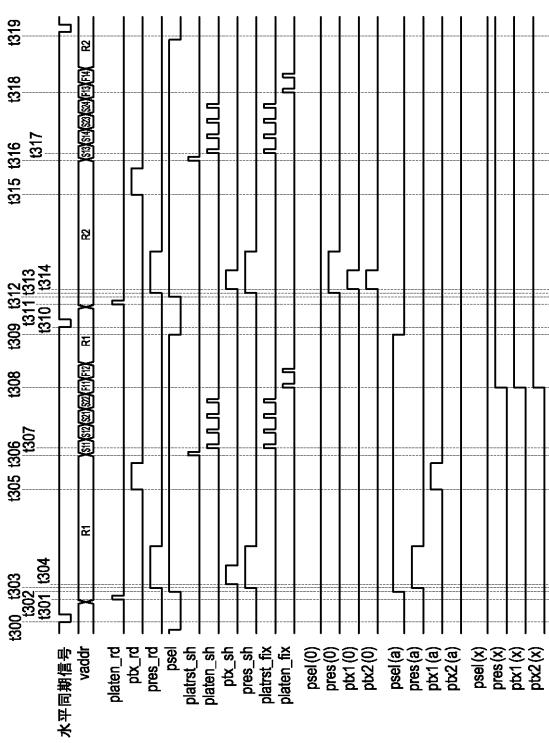

図面を参照しながら、本発明に係る第 2 の実施例を説明する。図 7 は、図 1 に示した構成のうち、タイミング生成部 40 と水平転送部 50 とを除く部分を抜き出し、より詳細に示した回路図である。以下では、実施例 1 との相違点を中心に説明する。

#### 【0095】

実施例 1 および 2 では、画素が選択トランジスタを含まないものを例示して説明したが、選択トランジスタを有する場合でも本発明は適用可能である。画素ブロック 3100 は、選択トランジスタ M3105 が追加された点を除いて、図 5 と同じ構成である。

#### 【0096】

画素ブロックの変更に伴い、画素パルス生成部 25 の構成も実施例 2 のものとは異なっている。図 7 では、画素パルス生成回路 3250、3251、…を AND 回路および OR 回路を用いて構成する例を示した。画素パルス生成回路 3250 は、信号 pres\_i、pse1\_i、ptx1\_i、ptx2\_i を出力し、それぞれ画素ブロック 3100 の、pres(0)、pse1(0)、ptx1(0)、ptx2(0) として画素ブロック 3100 に供給される。

10

#### 【0097】

信号 pres\_i は、AND 回路 3250-2 の出力と、第 3 記憶回路 3240 の出力と、AND 回路 3250-3 の出力との論理和を出力する OR 回路 3250-1 の出力として現れる。AND 回路 3250-2 は、第 2 記憶回路 3230 と 3231 の出力との論理和を出力する OR 回路 3250-5 の出力と、信号 pres\_sh との論理積を出力する。AND 回路 3250-3 は、第 1 記憶回路 3220 と 3221 の出力との論理和を出力する OR 回路 3250-4 の出力と、信号 pres\_rd との論理積を出力する。

#### 【0098】

信号 pse1\_i は、OR 回路 3250-4 の出力と信号 pse1 の論理積として現れる。

20

#### 【0099】

信号 ptx1\_i は、OR 回路 3250-7 の出力として現れる。OR 回路 3250-7 は、AND 回路 3250-8 の出力、第 3 記憶回路 2240 の出力、および AND 回路 3250-9 の出力の論理和を出力する。AND 回路 3250-8 は、第 2 記憶回路 2230 の出力と信号 ptx\_sh との論理積を出力する。AND 回路 3250-9 は、第 1 記憶回路 3220 の出力と信号 ptx\_rd との論理積を出力する。

#### 【0100】

信号 ptx2\_i は、OR 回路 3250-10 の出力として現れる。OR 回路 3250-10 は、AND 回路 3250-11 の出力、第 3 記憶回路 3240 の出力、および AND 回路 3250-12 の出力の論理和を出力する。AND 回路 3250-11 第 1 記憶回路 3221 の出力と信号 ptx\_rd との論理積を出力する。また、AND 回路 3250-12 は、第 2 記憶回路 3231 の出力と信号 ptx\_sh との論理積を出力する。

30

#### 【0101】

なお、信号 platen\_rd、platen\_sh、platrst\_sh、platrst\_fix、platen\_fix、platen\_fixa、pse1、ptx\_rd、ptx\_sh、pres\_rd、および pres\_sh はタイミング生成部 40 で生成される。

#### 【0102】

なお、画素パルス生成部の構成は図示したものに限られない。また、第 1 から第 3 記憶部の構成は実施例 1 と共通なので説明を省略する。

40

#### 【0103】

次に、図 8 に示したタイミング図を参照しながら図 1 および 7 に示す撮像装置の動作を説明する。

#### 【0104】

ここでは、画素アレイ 10 のうちの A 行の画素から信号を読み出した後、X および Y 行の画素のフォトダイオードの電位を固定し、さらに、0 行および 1 行を含む合計 4 行の画素に係るシャッタ動作を行う場合を例にとって説明する。繰り返しになるが、シャッタ動作とはすなわちフォトダイオードをリセットすることで、画素の初期化とも称する。図 8 の時刻 t300 においては、第 1 記憶部 22 の D ラッチ、第 2 記憶部 23 および第 3 記憶部 24 の S R ラッチはいずれも Low レベルを保持しているものとする。

50

## 【0105】

実施例1および2と大きく異なるのは、画素を選択あるいは非選択状態にするための制御方法である。実施例1および2ではFD部を高い電位にリセットすることで画素を選択状態にし、FD部を低い電位にリセットすることで画素を非選択状態にしていた。これに對して、本実施例では、増幅トランジスタM3103と垂直信号線vline(n)との間に設けられた選択トランジスタをオンすることで画素を選択状態にし、選択トランジスタをオフすることで画素を非選択状態にする。ここでは先の実施例で説明した動作との相違点を中心に説明する。

## 【0106】

図8の時刻t300に、不図示の外部から水平同期信号がタイミング生成部40に入力されると、タイミング生成部40は時刻t201に信号plate\_n\_rdをHighレベルにする。このときアドレス信号vaddrはR1=A行目を指しているので、アドレスデコーダ3210の出力のうちvdec(a)のみがHighレベルであり、第1記憶回路322AのDラッチのみがHighレベルを出力する。

10

## 【0107】

時刻t302に信号pse1がHighレベルになると、画素パルス生成部325AのAND回路325A-6の出力がHighレベルになり、画素ブロック310Aに含まれる選択トランジスタが導通する。これにより、画素ブロック310Aが選択状態になる。

## 【0108】

時刻t303に信号pres\_rdがHighレベルになると、画素パルス生成部325AのOR回路325A-1がHighレベルになり、画素ブロック310Aに含まれるリセットトランジスタM3104が導通する。これにより、画素ブロック310AのFD部F3101がリセットされる。一定時間経過後に信号pres\_rdがLowレベルになるとFD部のリセットが終了する。これ以降の期間で垂直信号線vline(n)に現れる信号は、画素ブロック310AのFD部をリセットしたことに対応する信号である。この信号にはリセットトランジスタM3104、増幅トランジスタM3103、FD部F3101に起因するノイズ成分が含まれている。水平転送部50にCDS回路を備える構成であれば、信号pres\_rdがLowレベルに変化した後に、垂直信号線vline(n)に現れる出力をサンプリングする。

20

## 【0109】

時刻t303には信号pres\_shが、そして時刻t304には信号ptx\_shがそれぞれHighレベルになるが、ここでは第2および第3記憶回路のSRラッチのいずれもがLowレベルを保持しているので、画素ブロックに供給される信号に変化はない。

30

## 【0110】

時刻t305に信号ptx\_rdがHighレベルになると、OR回路325A-9の出力がHighレベルになり、信号ptx1(a)のみがHighレベルになる。これによりa行目のPDに保持された電荷が、転送トランジスタM3101-1を介してFD部F3101に転送されると、てんそうされ多電荷量に応じてF3101の電位が変化し、垂直信号線vline(n)に現れる信号も合わせて変化する。このときの信号は、FD部F3101をリセットした直後のレベルに対して、光電変換によって生じた電荷量に応じた分だけ変化しているので、CDS回路に保持されたノイズ成分との差分を取ることで、ノイズ成分を低減することができる。以上によって1行目の画素から信号を読み出す動作が終了する。

40

## 【0111】

時刻t306からt309までの期間の動作は実施例1、2と同様なので説明を省略する。

## 【0112】

時刻t309に信号pse1がLowレベルに変化すると、画素ブロック310Aの選択状態が解除される。

## 【0113】

50

時刻 t 310 に水平同期信号 H D が入力されて、次の行に係る動作が行われる。

【0114】

時刻 t 311 に信号 p l a t e n \_ r d が H i g h レベルになると、このときのアドレス信号 v a d d r は R 2 = b であるので、 b 行の第 1 記憶回路 322A の D ラッチが H i g h レベルを出力するようになる。

【0115】

時刻 t 313 に信号 p r e s \_ s h が、時刻 t 314 に信号 p t x \_ s h がそれぞれ H i g h レベルになると、時刻 t 307 から第 2 記憶回路がセットされた行の画素のリセットトランジスタおよび転送トランジスタが導通する。これにより、4 行の画素のシャッタ動作が行われる。

10

【0116】

以上で説明したように、時刻 t 307 から時刻 t 308 までの期間に第 2 記憶回路がセットされる行は、次の水平同期期間に一時的に P D がリセットされる一方で、時刻 t 308 からの期間で第 3 記憶回路がセットされる行は、 P D がリセットされ続ける。つまり、本実施例のように選択トランジスタを備える画素の構成であっても、異なるリセット動作を実現することができる。

【0117】

(実施例 4)

図 9 を参照しながら、本発明に係る第 4 の実施例を説明する。

【0118】

第 1 から第 3 の実施例では、電子ズーム動作による、切り出し動作を行う場合を説明したが、本発明は、間引き動作を行う場合にも適用できる。

20

【0119】

図 9 は、連続するフィールドで、間引く、すなわち画素から信号を読み出さずにスキップする行が変更される動作を示すタイミング図である。具体的には、 F i e l d 101 では 6 行につき 1 行のみから信号を読み出し、残る 5 行は間引く、 1 / 6 間引き動作で、続く F i e l d 102 では 5 行につき 1 行のみから信号を読み出し、残る 3 行は間引く、 1 / 4 間引き動作を行う場合を例示する。画素は、実施例 1 ~ 3 で例示したように、隣接する 2 行で 1 つの画素ブロックを構成するものであるとする。

【0120】

30

実施例 1 ~ 3 で示したように複数の画素で 1 つの画素ブロックを構成する場合、 P D の電位を固定する動作と、読み出しあるいは電子シャッタ走査と、同じ画素ブロックに設定することはできない。そのため、 F i e l d 101 で 1 行目の画素から信号が読み出されるとすると、 2 行目の画素の P D の電位を固定することはできない。したがって、 1 行目および 2 行目の画素については、同時に電子シャッタ走査を行う。

【0121】

F i e l d 100 の水平同期信号 4 の期間には、電子シャッタ走査あるいは P D 電位を固定する行を第 2 あるいは第 3 記憶部に記憶させる動作が開始される。この動作は、例えば図 4 の時刻 t 107 ~ t 110 の期間に行われる動作に対応する。ここでは、次のフィールドに信号が読み出される 1 行目と、 1 行目の画素と 1 つの画素ブロックを構成する 2 行目のアドレスが、第 2 記憶部に記憶されるとともに、 3 ~ 6 行目のアドレスが、第 3 記憶部に記憶される。

40

【0122】

F i e l d 100 の水平同期信号 5 の期間になると、水平同期信号 4 の期間に第 2 記憶部に記憶させた行の P D リセット動作が行われる。この後、 F i e l d 101 に信号を読み出すまでが 1 行目の画素の蓄積期間となる。また、水平同期期間 5 においても 7 ~ 12 行目までの画素について、水平同期期間 4 と同様の動作が行われる。

【0123】

以下、 F i e l d 100 の間、同様の動作が繰り返される。

【0124】

50

続く Field 101 では、1、7、13、・・・と 5 行おきに信号を読み出す 1 / 6 間引き動作を行う。

Field 101 では、Field 102 の読み出し走査に対応する電子シャッタ走査と、PD 電位の固定も行う。Field 102 では 1、5、9、・・・と 3 行おきに信号を読み出す 1 / 4 間引き動作になるので、Field 101 では、1、2、5、6、9、10、・・・の行について電子シャッタ走査を行い、それ以外の行は PD の電位を固定する。

Field 102 になると、Field 101 から蓄積期間が開始した 1、5、9、・・・行について読み出し走査が行われる。

#### 【0125】

10

図 9 に示すタイミング図から明らかなように、間引き動作を行った場合には、読み出し行と画素ブロックを構成しない画素については PD の電位を固定し、間引く行に変更が生じた時にのみ、電子シャッタ走査に同調して PD の電位の固定状態を解除する動作を行う。したがって、以上で説明した本実施例の駆動方法によれば、間引き動作時における PD 電位を固定する行の変更を継ぎ目なく連続して行うことが可能となる。

#### 【0126】

また、上記で説明した実施例どうしを組み合わせることも可能である。同様にして、複数の画素で共有される素子を制御するための第 3 の記憶部を 3 個以上設けても良い。

#### 【0127】

20

なお、上述の各実施例で用いた、第 1 乃至第 3 記憶部に含まれるラッチは例示したものに限られない。例えば、第 1 乃至第 3 記憶部の全てで SR ラッチを用いても良い。図示の通り、画素の列に対して 1 本の垂直信号線が設けられている構成においては、つねに 1 行の画素からしか信号を読み出すことができない。このため、信号を読み出す画素の行に係るアドレスを記憶する第 1 記憶部には D ラッチを用いることで、セットとリセットを同時に可能としている。また、第 2 および第 3 記憶部に対しては SR ラッチを用いることで、デコーダからの出力が High レベルであるときに、ラッチをセットし、Low レベルであるときには値を保持するように構成されている。また、複数ある SR ラッチに対して共通のリセット信号を与えることで、一括してラッチの状態をリセットできる。

#### 【0128】

##### (実施例 5)

30

次に、本実施形態に係る撮像システムの概略を、図 10 を用いて説明する。

#### 【0129】

撮像システム 800 は、例えば、光学部 810、撮像装置 1000、映像信号処理回路部 830、記録・通信部 840、タイミング制御回路部 850、システムコントロール回路部 860、及び再生・表示部 870 を含む。撮像装置 1000 は、先述の各実施例で説明した撮像装置が用いられる。ここでは、図 1 に示したタイミング生成部 40 が、撮像装置ではなく、タイミング制御回路部 850 に含まれる場合を例示している。

#### 【0130】

レンズなどの光学系である光学部は 810、被写体からの光を撮像装置 1000 の、複数の画素が 2 次元状に配列された画素アレイに結像させ、被写体の像を形成する。撮像装置 1000 は、タイミング制御回路部 850 からの信号に基づくタイミングで、画素部に結像された光に応じた信号を出力する。

#### 【0131】

撮像装置 1000 から出力された信号は、映像信号処理部である映像信号処理回路部 830 に入力され、映像信号処理回路部 830 が、プログラムなどによって定められた方法に従って、入力された電気信号に対して A/D 変換などの処理を行う。映像信号処理回路部での処理によって得られた信号は画像データとして記録・通信部 840 に送られる。記録・通信部 840 は、画像を形成するための信号を再生・表示部 870 に送り、再生・表示部 870 に動画や静止画像が再生・表示させる。記録通信部は、また、映像信号処理回路部 830 からの信号を受けて、システムコントロール回路部 860 とも通信を行うほか、

40

50

不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。

【0132】

システムコントロール回路部860は、撮像システムの動作を統括的に制御するものであり、光学部810、タイミング制御回路部850、記録・通信部840、及び再生・表示部870の駆動を制御する。また、システムコントロール回路部860は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラムなどが記録される。また、システムコントロール回路部860は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内で供給する。具体的な例としては、読み出す行やりセットする行の変更、電子ズームに伴う画角の変更や、電子防振に伴う画角のずらしなどである。

10

【0133】

タイミング制御回路部850は、制御部であるシステムコントロール回路部860による制御に基づいて撮像装置1000及び映像信号処理回路部830の駆動タイミングを制御する。

【0134】

以上で説明した各実施例は、本発明を実施するための例示的なものであって、本発明の技術的思想を逸脱しない範囲で様々なに変更あるいは組み合わせることが可能である。

【符号の説明】

【0135】

1 撮像装置

20

10 画素アレイ

20 行選択部

21 アドレスデコーダ

22 第1記憶部

23 第2記憶部

24 第3記憶部

25 画素パルス生成部

30 アドレス生成部

40 タイミング生成部

50 水平転送部

30

【 义 1 】

【 四 2 】

【 义 3 】

【 図 4 】

【 四 5 】

〔 四 6 〕

【圖 7】

【 义 8 】

【図9】

【図10】

---

フロントページの続き

(56)参考文献 特開2009-065585(JP,A)

特開2006-229797(JP,A)

特開2010-103667(JP,A)

特開2005-184358(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/374