(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6133280号

(P6133280)

(45) 発行日 平成29年5月24日(2017.5.24)

(24) 登録日 平成29年4月28日(2017.4.28)

(51) Int.Cl.

F 1

H05B 37/02 (2006.01)

H05B 37/02

J

H02M 7/12 (2006.01)

H02M 7/12

Q

H02M 3/155 (2006.01)

H02M 3/155

H

請求項の数 12 (全 17 頁)

(21) 出願番号 特願2014-515319 (P2014-515319)

(86) (22) 出願日 平成24年6月11日 (2012.6.11)

(65) 公表番号 特表2014-520366 (P2014-520366A)

(43) 公表日 平成26年8月21日 (2014.8.21)

(86) 國際出願番号 PCT/IB2012/052936

(87) 國際公開番号 WO2012/172472

(87) 國際公開日 平成24年12月20日 (2012.12.20)

審査請求日 平成27年6月9日 (2015.6.9)

(31) 優先権主張番号 11170268.4

(32) 優先日 平成23年6月17日 (2011.6.17)

(33) 優先権主張国 歐州特許庁 (EP)

(73) 特許権者 516043960

フィリップス ライティング ホールディング ビー ヴィ

オランダ国 5656 アーエー アイン

トホーフェン ハイ テク キャンパス

45

(74) 代理人 110001690

特許業務法人M&Sパートナーズ

(72) 発明者 ロペズ トニ

オランダ国 5656 アーエー アイン

トホーフェン ハイ テク キャンパス

ビルディング 44

最終頁に続く

(54) 【発明の名称】負荷、特にLEDユニットを駆動するための、LCフィルタを有する单一のスイッチドライバ装置

## (57) 【特許請求の範囲】

## 【請求項1】

負荷用のドライバ装置であって、

第1電力入力端子及び第2電力入力端子を含み、外部電源から整流電源電圧を受ける電力入力端子と、

前記第1電力入力端子及び前記第2電力入力端子のいずれとも直接接続されていない第1電力出力端子及び第2電力出力端子を含み、負荷を駆動するための駆動電圧及び/又は電流を供給する電力出力端子と、

いずれもスイッチノードに結合された单一のスイッチング要素及びエネルギー保持要素を含む、前記電力入力端子に結合された单段式電力変換ユニットであって、前記電力出力端子は单段式電力変換ユニットの出力部によって表される、前記单段式電力変換ユニットと、

前記スイッチノードと前記第1電力入力端子及び前記第2電力入力端子のいずれか一方との間に結合された第1インダクタと、

前記スイッチノードと前記第1電力出力端子との間に結合された、フィルタインダクタ及びフィルタコンデンサを含むフィルタユニットと、

前記スイッチング要素を制御する制御ユニットと

を有し、

前記エネルギー保持要素は、前記スイッチノードと中間ノードとの間に結合され、

前記中間ノードと前記第1電力出力端子及び前記第2電力出力端子のいずれか一方との

間に第2インダクタが結合され、

前記中間ノードと前記第1電力出力端子及び前記第2電力出力端子のいずれか他方との間にダイオードが結合される、

ドライバ装置。

**【請求項2】**

前記単段式電力変換ユニットは、Cuk型、SEPIC型、又はZeta型コンバータを含む、請求項1に記載のドライバ装置。

**【請求項3】**

前記単段式電力変換ユニットはCuk型コンバータを含み、

前記スイッチング要素は、前記スイッチノードと前記第2電力出力端子との間に結合され、10

前記第2インダクタは、前記中間ノードと前記第1電力出力端子との間に結合され、

前記ダイオードは、前記中間ノードと前記第2電力出力端子との間に結合される、請求項1に記載のドライバ装置。

**【請求項4】**

前記単段式電力変換ユニットはSEPIC型コンバータを含み、

前記スイッチング要素は、前記スイッチノードと前記第2電力出力端子との間に結合され、

前記第2インダクタは、前記中間ノードと前記第2電力出力端子との間に結合され、

前記ダイオードは、前記中間ノードと前記第1電力出力端子との間に結合される、請求項1に記載のドライバ装置。20

**【請求項5】**

前記スイッチング要素は、前記スイッチノードと前記第2電力入力端子との間に結合される、請求項3又は4に記載のドライバ装置。

**【請求項6】**

前記単段式電力変換ユニットはZeta型コンバータを含み、

前記スイッチング要素は、前記第1電力入力端子と前記スイッチノードとの間に結合され、

前記第1インダクタに直列に他のダイオードが結合され、

前記第2インダクタは、前記中間ノードと前記第1電力出力端子との間に結合され、30

前記ダイオードは、前記中間ノードと前記第2電力出力端子との間に結合される、請求項1に記載のドライバ装置。

**【請求項7】**

前記電力入力端子間に結合された入力バイパスコンデンサをさらに有する、請求項1に記載のドライバ装置。

**【請求項8】**

前記電力出力端子間に結合された出力バイパスコンデンサをさらに有する、請求項1に記載のドライバ装置。

**【請求項9】**

前記第2電力入力端子、及び前記第2電力出力端子が基準電位に接続される、請求項1に記載のドライバ装置。40

**【請求項10】**

A C電源電圧を前記整流電源電圧に整流する整流ユニットをさらに有する、請求項1に記載のドライバ装置。

**【請求項11】**

前記制御ユニットは、前記エネルギー保持要素の両端の電圧を所定の閾値未満に保つ、及び/又は入力電流を変調して、出力電流を一定に保つ、請求項1に記載のドライバ装置。

**【請求項12】**

一つ以上の照明ユニットを含む照明アセンブリと、50

前記照明アセンブリを駆動する、請求項 1 乃至 1\_1 の何れか一項に記載のドライバ装置と

を有する、照明装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、負荷、特に一つ又は複数の LED を備える LED ユニットを駆動するためのドライバ装置に関する。また、本発明は照明装置に関する。

**【背景技術】**

**【0002】**

レトロフィットランプ等のオフラインアプリケーション用の LED ドライバの分野において、高効率性、高電力密度、長寿命、高力率、及び低コスト等の特徴に対応するソリューションが求められている。既存のソリューションのほぼ全てがこれらの要件のいずれかを満たしているが、提案されるドライバ回路は、現在及び将来のコンセント（電源）規格に適合しつつ、コンセント電力の形式を LED に適した形式に適切に調整しなければならない。力率を所定の下限以上に維持するとともに、最大光知覚フリッカーを保証する（好ましくはゼロ）ことは極めて重要である。

**【0003】**

また、オフラインコンバータにおいて高力率及び低高調波歪を実現するためには、コンセントからのエネルギーを、供給される電圧波形に比例して同期的に引き出さなければならない場合が多い。このタスクを、負荷に送られるエネルギーの形式を不適切に損なうことなく最適に達成するために、従来、独立した前処理（事前調整）段階を有する電力コンバータアーキテクチャが用いられてきた。

**【0004】**

典型的には、電源サイクル（又は供給サイクル、すなわち、電源電圧又は供給電圧のサイクル）を通して出力電力を一定に保ちつつ高力率を得るために、二段階の直列電力段が用いられる。これらのアーキテクチャにおいて、第一段階は電源電流を適合（変調）させ、第二段階は負荷への電力変換を行う。

**【0005】**

しかし、複雑さ及びコストに関する理由から、二段階のうちの一つが本質的には必要ではない、従来「単段式」として知られる単純化されたパワートレイン（伝動機構）ソリューションが採用されている。このような単純化の結果、上記要求事項が大きく損なわれる可能性があり、且つ / 又は、コンバータの性能が、特にサイズ、信頼性、及び寿命に関して、大きく低下する可能性がある。後者については、通常、一定の出力電力供給を保証する場合、負荷に並列な大きな低周波保持容量を用いなければならないことに主に起因する。

**【0006】**

単段式のソリューションに関する文献は一般的である。一例は、Robert Eri ckson, Michael Madigan著、「フライバックコンバータに基づく単純な高力率整流器の設計」、応用パワーエレクトロニクス会議及び展示会 IEEE 議事録、1990、pp. 792 - 801 である。

**【0007】**

二段式アプローチと単段式アプローチとの間にある中間ソリューションは、組み込まれた前処理段階を有する単段式コンバータである。このようなソリューションは、負荷及び電源（コンセント）の要求事項を満たしつつ、部品数の削減及び高電力密度を提供する。単一の電力変換段階を有する他の実施形態は、不連続導通モードで動作する昇圧コンバータを組み込むことで高力率（high power factors (HPF)）を実現する。これらのコンバータは、実際には前述の二つの電力変換段階を組み合わせる。

**【0008】**

「一定 DC リンク電圧を有する高力率電子安定器」、Ricardo de Oliv

10

20

30

40

50

eira Brioschi、Jose Luiz F. Vieira著、パワーエレクトロニクス IEEE 議事録、vol. 13、no. 6、1998 には、コンパクトな蛍光ランプ用の HPF コンバータが記載されている。この例では、ハーフブリッジが、昇圧コンバータと LC 並列共振コンバータとによって共有され、LC 並列共振コンバータは、ゼロ電圧スイッチング (zero voltage switching (ZVS)) を得るために共振以上で動作する。ZVS をさらにサポートするために、バス電圧は一定に制御される。しかし、このような HPF コンバータは、通常大きなバス容量及び出力整流器を必要とし、電源電圧幅及び負荷 (駆動) 電圧幅が狭い。

#### 【0009】

R. Venkataraman、A. K. S. Bhat、Mark Edmunds 著、

「高調波歪が低減されたソフトスイッチング単段式 AC - DC コンバータ」、エアロスペース及びエレクトロニクスシステム IEEE 議事録、vol. 36、no. 4、2000 年 10 月は、統合電力段階の他の例を示す。この文献は、一定電源負荷のために、高周波変圧器が分離した、ゼロ電圧スイッチング (ZVS)、高効率及び低高調波歪を有する単段式 AC - DC コンバータを提示し、考察する。

10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

本発明の目的は、負荷、特に一つ以上の LED を有する LED ユニットを駆動するためのドライバ装置を提供することであり、とりわけ高効率、実質的に一定負荷、小サイズ、高効率性、長寿命、及び低成本を提供するドライバ装置を提供することである。また、本発明の他の目的は、対応する照明装置を提供することである。

20

#### 【課題を解決するための手段】

#### 【0011】

本発明の一側面によれば、

負荷、特に一つ以上の LED を含む LED ユニット用のドライバ装置であって、

外部電源から整流電源電圧を受ける電力入力端子と、

負荷を駆動するための駆動電圧及び / 又は電流を供給する電力出力端子と、

いずれもスイッチノードに結合された単一のスイッチング要素とエネルギー保持要素とを含む、前記電力入力端子に結合された単段式電力変換ユニットであって、前記電力出力端子は単段式電力変換ユニットの出力部によって表される、前記単段式電力変換ユニットと、

30

前記スイッチノードに結合された、フィルタインダクタとフィルタコンデンサとを含むフィルタユニットと、

前記スイッチング要素を制御する制御ユニットと

を有する、ドライバ装置が提供される。

#### 【0012】

本発明の他の側面によれば、一つ以上の照明ユニットを含む照明アセンブリ、特に一つ以上の LED を含む LED ユニットと、前記照明アセンブリを駆動する本発明が提供するドライバ装置とを有する照明装置が提供される。

40

#### 【0013】

本発明の実施形態は、従属請求項において定義される。上記照明装置は、上記装置の従属請求項において定義される実施形態と同様及び / 又は同一の好適な実施形態を有する。

#### 【0014】

本発明は、一定な出力電力を負荷に送達する一方で高効率を達成する、前処理ユニットが組み込まれた単段式電力コンバータ (電力変換ユニット) を提供するという着想に基づく。これは、フィルタユニットの要素によって表されるローパスフィルタが組み込まれた電力コンバータを適切に制御することによって実現される。通常、変換機能を実施するには単一のスイッチしか必要とされない。提案されるドライバ装置は、特に電力出力端子に結合された高電圧 LED ストリングを使用するオフライン LED ドライバを対象とする。

50

## 【0015】

L E D用の二段式オフラインドライバと比較して、高コスト、複雑性、及び大きな部品数という、電源及び負荷の両方の要求事項を満たすための課題が解決される。これは、提案されるドライバ装置及び方法が、慣用的な部品を好適に用いながら、単純性及び少部品数を備えることによる。

## 【0016】

L E D用の単段式オフラインドライバと比較して、下記の問題が解決される。出力電力を一定に保ちながら、電源サイクル又はコンセントサイクル間の低周波保持容量電圧変動を小さくする（例えば、20～80%）ことによって、大きな低周波コンデンサを省くことができる。これは、サイズの小型化、並びに特に高温動作における長寿命及び高信頼性につながる。また、電源及び負荷のいずれの要求事項も損なうことなく部品数を削減することが必要である。これは、電力段（パワーステージ）及び電力段に組み込まれた前処理機能の動作によって本質的に達成される。また、大きな低周波保持容量を用いたとしても、単段式では知覚フリッカを完全に排除できないおそれがある。提案されるソリューションは、一定出力電流を可能にし、知覚フリッカを最小化できる。

10

## 【0017】

本発明によれば、多様な負荷及び入力電圧範囲に対応する多様な実施形態として、電力変換ユニットの多様な基本構成が提供される。全ての構成において、デューティサイクル若しくはスイッチング周波数の操作、又はバーストモード動作によって、実質的にゼロ負荷電流までの全負荷範囲にかけて制御することができる。

20

## 【0018】

電源（供給）電圧は、電源によって供給される整流周期供給電圧でもよい。例えば、コンセント電圧電源から電源（又は電力入力端子）への入力電圧としてA Cコンセント電圧が供給される場合、供給されたA C入力電圧、例えばコンセント電圧を（整流周期）供給電圧に整流する整流器ユニットが（ドライバ装置の一部として又は電力入力端子に結合される外部ユニットとして）用いられる。このような整流器ユニットは、例えばよく知られている半波又は全波整流器である。したがって、供給電圧は、A C入力電圧のいずれの極性に関しても同じ極性を有する。

## 【0019】

あるいは、例えば他の箇所に設けられた整流器（前記外部電力電源を表す）から整流周期電圧電圧がすでに電力入力端子に供給されている場合、電力入力端子には、供給される電源電圧を変調するための一般的な要素（增幅器等）が付加的に結合されないか、又は、一般的な要素しか結合されない。

30

## 【0020】

提案のドライバ装置には多様な実施形態が存在し、それらはドライバ装置の多様な要素の結合（方法）によって主に区別される。

## 【0021】

一実施形態においては、前記フィルタインダクタと前記フィルタコンデンサとが直列に結合され、前記フィルタユニットの高電圧端子が前記スイッチノードに結合される。

## 【0022】

一実施形態においては、前記フィルタユニットの低電圧端子が基準電位、特にグランド電位に結合され、且つ／又は電力出力端子に結合された電力入力端子に結合される。他の実施形態においては、前記フィルタユニットの低電圧端子が、電力入力端子に接続されていない電力出力端子に結合される。装置内のコンバータからの電圧及び電流ストレスは異なり得る。最良のオプションは、各場合における利用可能な部品の種類に依存し得る。

40

## 【0023】

前記単段式電力変換ユニットは、C u k型、S E P I C型、又はZ e t a型コンバータを含み得る。C h i K . T s e著、「ゼロ次スイッチングネットワーク及びスイッチングコンバータにおける力率補正への適用」、回路及びシステムI：基礎的原理と応用I E E E議事録、v o l . 4 4 、n o . 8 、1 9 9 7年8月は、基本的なC u k、S E P I C

50

、Zetaトポロジーの基礎的な説明を提供する。

**【0024】**

前記単段式電力変換ユニットはCuk型コンバータを含み、当該Cuk型コンバータは、第一電力入力端子と前記スイッチノードとの間に結合された第1インダクタと、前記スイッチノードと中間ノードとの間に結合された前記エネルギー保持要素と、前記中間ノードと第1電力出力端子との間に結合された第2インダクタと、前記中間ノードと第2電力出力端子との間に結合されたダイオードとを有する。

**【0025】**

前記単段式電力変換ユニットはSEPIC型コンバータを含み、当該SEPIC型コンバータは、第1電力入力端子と前記スイッチノードとの間に結合された第1インダクタと、前記スイッチノードと中間ノードとの間に結合された前記エネルギー保持要素、特に中間コンデンサと、前記中間ノードと第1電力出力端子との間に結合されたダイオードと、前記中間ノードと第2電力出力端子との間に結合された第2インダクタとを有する。10

**【0026】**

これらの実施形態において、好ましくは、前記スイッチング要素は、前記スイッチノードと第2電力入力端子との間に結合される。

**【0027】**

他の実施形態においては、前記単段式電力変換ユニットはZeta型コンバータを含み、当該Zeta型コンバータは、第1電力入力端子と前記スイッチノードとの間に結合された前記スイッチング要素と、前記スイッチノードと第2電力入力端子との間に結合された第1インダクタと、前記第1インダクタに直列に結合された第1ダイオードと、前記スイッチノードと中間ノードとの間に結合された前記エネルギー保持要素、特に中間コンデンサと、前記中間ノードと第1電力出力端子との間に結合された第2インダクタと、前記中間ノードと第2電力出力端子との間に結合された第2ダイオードとを有する。20

**【0028】**

多様な実施形態は、様々な用途及び様々な電圧での使用のために提供され、所定の目的を果たすよう設計されている。多くの場合、最適な実施形態の選択はトレードオフを伴う。

**【0029】**

好適には、高周波分離（デカップリング）のために、電力入力端子間に結合される入力バイパス（デカップリング）コンデンサ、及び／又は電力出力端子間に結合される出力バイパスコンデンサがさらに設けられる。30

**【0030】**

広義には、スイッチング要素は、トランジスタ（例えばMOSFET）及び他の被制御スイッチング手段を含む多様な方法で実現され得る。

**【0031】**

制御ユニットは、エネルギー保持要素の両端の電圧を所定の閾値未満に保つ、且つ／又は入力電流を変調して、出力電流を一定に保つ。スイッチング要素のゼロ電圧スイッチングは提案のドライバ装置の設計（部品）によって提供される。制御のタスクは、出力電流を（場合によっては基準電流（セットポイント）に基づいて）一定に保ち、バス電圧（エネルギー保持要素の両端の電圧）をプリセット限界以下に保つ、且つ／又は入力電流を変調する。40

**【図面の簡単な説明】**

**【0032】**

本発明の上記及び他の側面は、下記において説明される実施形態を参照して説明されることによって明瞭になるであろう。

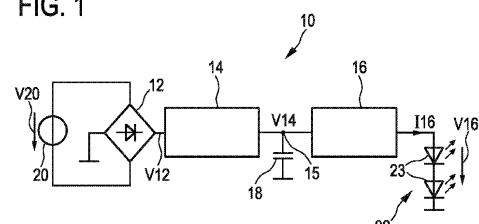

**【図1】**図1は、既知の二段式ドライバ装置の概略的なブロック図を示す。

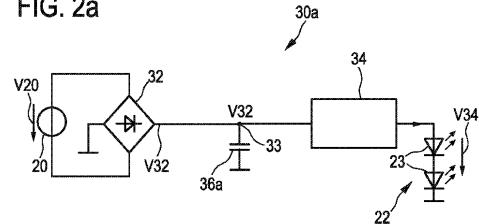

**【図2a】**図2aは、入力保持容量を有する既知の単段式ドライバ装置の概略的なブロック図を示す。

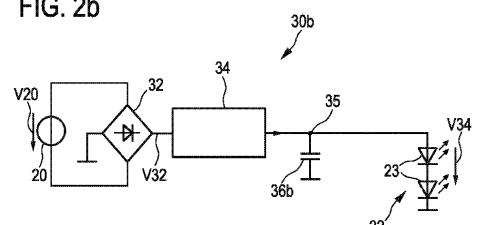

**【図2b】**図2bは、出力保持容量を有する既知の単段式ドライバ装置の概略的なブロック図を示す。50

ク図を示す。

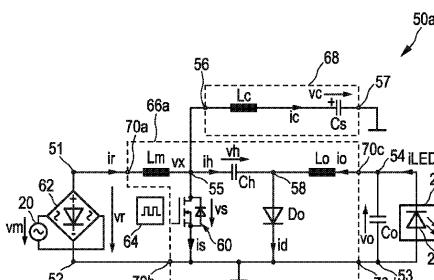

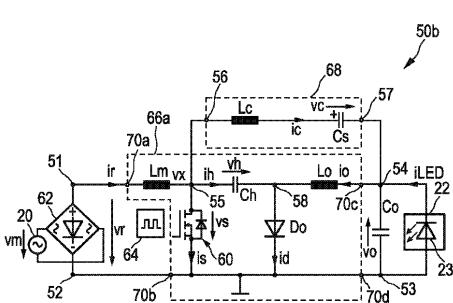

【図3】図3は、本発明に係るドライバ装置の第1構成の二つの実施形態の概略的なプロック図を示す。

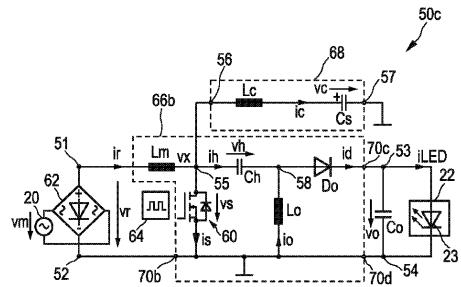

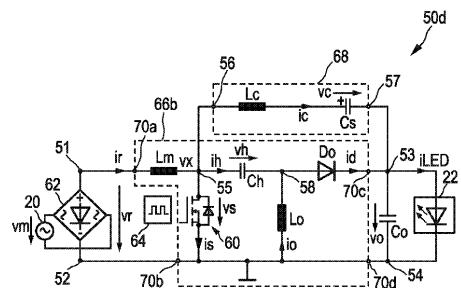

【図4】図4は、本発明に係るドライバ装置の第2構成の二つの実施形態の概略的なプロック図を示す。

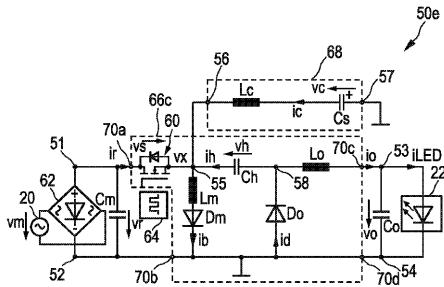

【図5】図5は、本発明に係るドライバ装置の第3構成の二つの実施形態の概略的なプロック図を示す。

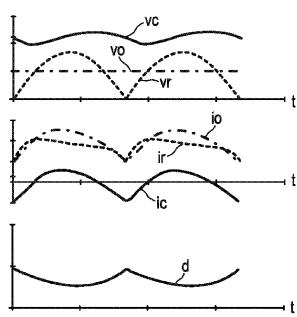

【図6】図6は、提案されるドライバ装置の第1構成の実施形態における一つの低周波サイクル間の電圧及び電流のダイアグラムを示す。

【図7】図7は、提案されるドライバ装置の第1構成の実施形態における一つの高周波サイクル間の電圧及び電流のダイアグラムを示す。 10

【図8】図8は、提案されるドライバ装置の第2構成の実施形態における一つの低周波サイクル間の電圧及び電流のダイアグラムを示す。

【図9】図9は、提案されるドライバ装置の第3構成の実施形態における一つの低周波サイクル間の電圧及び電流のダイアグラムを示す。

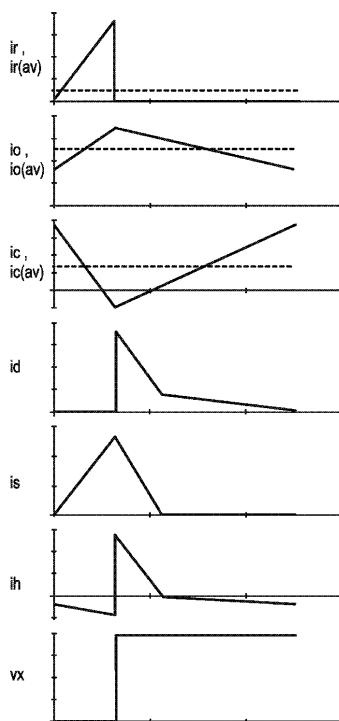

【図10】図10は、提案されるドライバ装置の第3構成の実施形態における一つの高周波サイクル間の電圧及び電流のダイアグラムを示す。 20

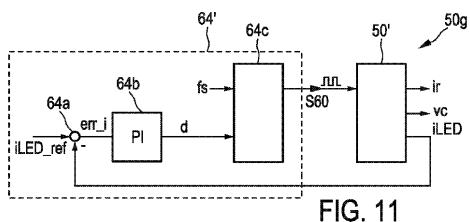

【図11】図11は、提案されるドライバ装置の制御ユニットの第1実施形態を示す。

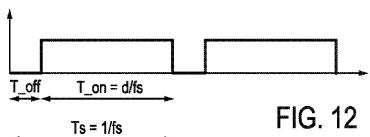

【図12】図12は、ドライバ装置の単一のスイッチング要素のスイッチング信号を示す。 20

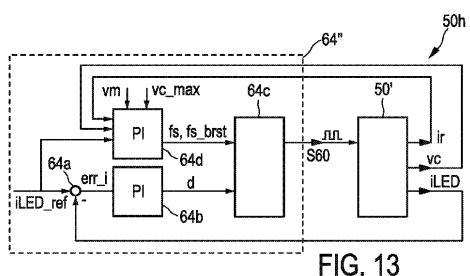

【図13】図13は、提案されるドライバ装置の制御ユニットの第2実施形態を示す。

#### 【発明を実施するための形態】

##### 【0033】

図1は、既知の二段式ドライバ装置10の一実施形態を概略的に示す。ドライバ装置10は、整流器ユニット12、整流器ユニット12の出力に結合された第1段前処理ユニット14、第1段前処理ユニット14の出力に結合された第2段変換ユニット16、及び第1段前処理ユニット14と第2段変換ユニット16との間のノード15に結合された充電コンデンサ18を有する。整流器ユニット12は、好ましくは、例えば外部コンセント電圧電源20から供給されるAC入力電圧V20を整流電圧V12に整流する全波又は半波整流器等の既知の整流器ユニットを備える。本実施形態において、負荷22は二つのLED23を有するLEDユニットであり、第2段変換ユニット16の出力に結合される。第2段変換ユニット16の出力信号、具体的には駆動電圧V16及び駆動電流I16は、負荷22を駆動するために用いられる。 30

##### 【0034】

第1段前処理ユニット14は、整流電圧V12を中間DC電圧V14に前処理（予備調整）し、第2段変換ユニット16は中間DC電圧V14を所望のDC駆動電圧V16に変換する。充電コンデンサ18は電荷を蓄電するために、すなわち、中間DC電圧V14によって充電され、これによって整流電圧V12の低周波信号をフィルタリングし、第二段変換ユニット16の実質的に一定な出力信号、特に負荷22を流れる一定の駆動電流I16を保証する。このようなドライバ装置内の上記要素14、16、18は広く使用されているため、本明細書でこれ以上詳しく説明しない。 40

##### 【0035】

通常、ドライバ装置10は、広いスペースやコストの代償に前述の高効率及び低フリッカー（明滅、ゆらぎ）という要求を満たすが、特にレトロフィット用途においては、これらは大幅に限定される可能性がある。第1段前処理ユニット14のサイズは、特に低又は中程度のスイッチング周波数で動作する昇圧コンバータ等のスイッチモード電源（switched mode power supply (SMPSS)）を備える場合、関連する受動部品によって主に決定される。これらのフィルタ部品のサイズを小さくするためにスイッチング周波数を上げると、ハードスイッチングSMPSS内で急激なエネルギー損失が起こるおそれがあり、より大きなヒートシンクが必要になる。 50

## 【0036】

図2a及び図2bは、既知のドライバ装置30a、30bの実施形態を概略的に示す。ドライバ装置30は、整流器ユニット32（図1に示す二段式ドライバ装置10の整流器ユニット12と同一のものでもよい）と、整流器ユニット32の出力に結合される変換ユニット34（例えば、図2bに示す実施形態ではフライバックコンバータ、又は図2aに示す実施形態では降圧コンバータ）とを備える。また、図2aの実施形態においては、整流器ユニット32と変換ユニット34との間のノード33に充電コンデンサ36a（低周波入力保持容量）が結合されている。図2bの実施形態においては、変換ユニット34と負荷22との間のノード35に充電コンデンサ36b（低周波出力保持容量）が結合されている。整流器ユニットは、例えば外部コンセント電圧電源（電源とも呼ぶ）20から供給されるAC入力電圧V20を整流電圧V32に整流する。整流電圧V32は、負荷22を駆動するための所望のDC駆動電圧V34に変換される。

10

## 【0037】

保持容量18（図1）及び36a、36b（図2a、2b）は、主に、整流電圧V12の低周波成分をフィルタリング除去して、負荷への定電流を実現するために設けられる。したがって、このような容量（コンデンサ）は、特に負荷に対して並列に配置され、LEDが負荷である場合には大きなサイズを有する。

## 【0038】

図1及び2のドライバ装置は、例えばRobert Erickson、Michael Madigan著、「フライバックコンバータに基づく単純な高効率整流器の設計」応用パワーエレクトロニクス会議及び展示会IEEE予稿集、1990、pp. 792-801に記載されている。

20

## 【0039】

これら单段式ドライバ装置30a、bのほとんどは、図1に例示されるような二段式ドライバ装置に比べてハードウェア部品の個数が少ないが、AC入力電圧の低周波成分をフィルタリング除去する充電コンデンサのサイズの制限のため、通常、高効率及び低知覚フリッカーを提供することができない。また、知覚フリッカーを低減するための大きな保持容量の使用のため、单段式ドライバ装置は負荷（例えばランプ）のサイズ、寿命、及び最高動作温度を著しく損なうおそれがある。

## 【0040】

30

図3～5は、本発明に係るドライバ装置の三つの基本的構成のいくつかの実施形態を示す。各構成（図3は構成1の実施形態を、図4は構成2の実施形態を、図5は構成3の実施形態を示す）は、单段式電力変換ユニット及びフィルタユニットを含む提案ドライバ装置の二つの実施形態によって示される。各提案構成に対して、フィルタコンデンサ（低周波数保持容量とも呼ぶ）Csをグランド又は負荷に接続する二つの異なる実施形態を説明する。

## 【0041】

三つの構成は全て自己安定挙動を示し、これは、（低周波）保持容量Csの両端で所定の電圧リップルで出力電流を一定に制御することを可能にする。一実施形態においては、電力変換ユニットの昇圧インダクタLmは、非連続導通モード用に設計され、このために追加ダイオード（Dm）が昇圧インダクタに直列に結合される。また、全ての構成が高電圧負荷、例えば複数の高電圧LEDストリングに適しているが、低電圧も可能である。負荷が変わる可能性があるので、スイッチング周波数を変えることによってコンデンサ電圧を一定に制御することができる。出力電流が減少するにつれ、スイッチング周波数が上がる。したがって、各構成のタイプ1の実施形態（図3a、4a、5aの実施形態）とタイプ2の実施形態（図3b、4b、5bの実施形態）とは大部分において同等であるが、パフォーマンス、コンデンサの両端の電圧ストレス、及びスイッチに関して異なる。両タイプは似ているため、主にタイプ2の実施形態を以下に説明する。

40

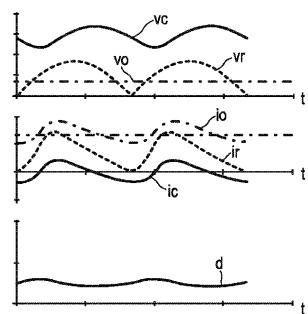

## 【0042】

図6～10に示すダイアグラムは、図3、4、及び5に示す三つの構成に関する。図6

50

～11は図3a、4a、5aに示す第1、第3、及び第5実施形態の低周波定常状態波形(図6、8、9)及び高周波スイッチング波形(図7、10)を示す。実施系チア50b及び50dのスイッチング波形は同等であるため、実施形態50dのスイッチング波形は別々に繰り返して示されない。全ての場合において、直列接続LEDユニットを含むLED負荷が10W定電力で動作するよう選択され、これは出力電力が一定でなければならないことを意味する。整流AC入力信号は、ヨーロッパコンセントに言及する。他の種類の負荷及び電源も使用可能である。ここに示される全ての実施形態において、最終的な力率(power factor(PF))は90%以上であり、全高調波歪(total harmonic distortion(THD))は40%未満である。

## 【0043】

10

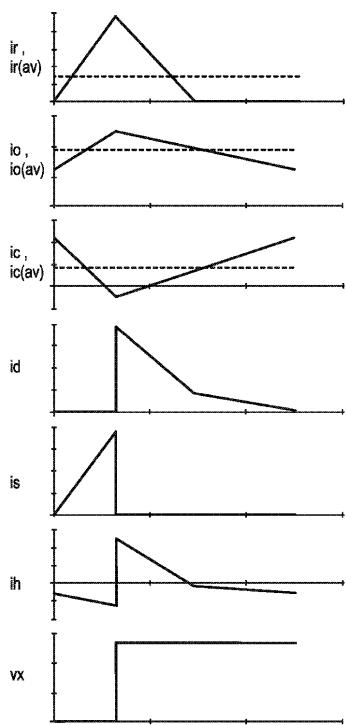

デューティサイクルはスイッチ動作に言及することに留意されたい。例えば、100%デューティサイクルは、スイッチング要素60が常にオン(閉)であることを示す。切り替えられたノードの電圧は、 $v_x$ で表される。

## 【0044】

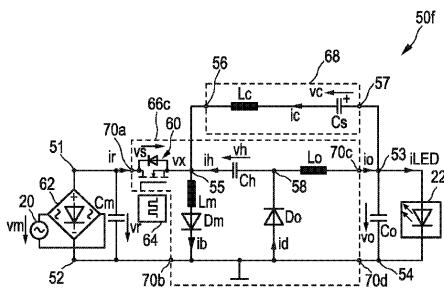

図3aは、本発明に係るドライバ装置50aの第1実施形態を概略的に示す。ドライバ装置50aは、整流器62によって整流される、外部電源20(例えば電源電圧 $v_m$ を供給するコンセント電圧電源)からの整流電源電圧 $v_r$ を受ける電源入力端子51、52を備える。ドライバ装置50aは、負荷22を駆動するための駆動電圧 $v_o$ 及び/又は電流 $i_o$ を供給するための電力出力端子53、54をさらに備える。この文脈において、本実施形態における電流 $i_o$ は負荷22を流れる電流であることに留意されたい(以下で説明される、図4a、5aに示す実施形態でも同様)。これは全ての実施形態には当てはまらない。

20

## 【0045】

また、ドライバ装置50aは、単段式電力変換ユニット66aを有し、当該ユニットの入力端子70a、70bは電力入力端子51、52に結合され、出力端子70c、70dは電力出力端子53、54に結合される。電力変換ユニット66aは一つのスイッチング要素60とエネルギー保持要素Ch、具体的には一つのコンデンサを有し、両方ともにスイッチノード55に結合される。

## 【0046】

30

また、ドライバ装置50aはフィルタインダクタLcとフィルタコンデンサCsとを有するフィルタユニット68を有する。フィルタユニット68の(フィルタインダクタLcに接続される)高電圧端子56はスイッチノード55に結合され、一方、フィルタユニット68の(フィルタコンデンサCsに接続される)低電圧端子57は、グランドに結合されている。

## 【0047】

スイッチング要素60を制御するために、制御ユニット64(例えば、適切に設計又はプログラムされたコントローラ、プロセッサ、又はコンピュータ)が提供される。

## 【0048】

該当する実施形態においては、高周波バイパス(デカップリング)のために、電力入力端子51、52の間に結合される(任意の)入力バイパスコンデンサCm(図5参照(図3及び4には示されていない))と、電力出力端子53、54の間に結合される(任意の)出力バイパスコンデンサCoが追加される。低電力入力端子52及び高電力出力端子53はともにグランドに結合される。

40

## 【0049】

Cuk型電力変換ユニット66aは、高電力入力端子51とスイッチノード55との間に結合された第1インダクタLmを有する。エネルギー保持要素Ch、具体的には中間コンデンサは、スイッチノード55と中間ノード58との間に結合される。第2インダクタLoは、中間ノード58と第1電力出力端子54との間に結合される。最後に、ダイオードDoが中間ノード58と低電力出力端子54との間に結合される。スイッチング要素60は、スイッチノード55と低電力入力端子52との間に結合される。

50

## 【0050】

図3bは、本発明に係るドライバ装置50bの第2実施形態を概略的に示す。ドライバ装置50aの第1実施形態と比較すると、フィルタユニット68の低電圧端子57はグラウンドではなく低電力出力端子54に結合される。他の要素及び結合部はドライバ装置50aの第1実施形態と同様である。

## 【0051】

したがって、ドライバ装置50a、50bの第1及び第2実施形態においては、回路はCuk型電力コンバータを、直列接続された高周波フィルタインダクタLcと低周波（コンセント周波数）保持容量Csとを含み、スイッチノード55と負荷との間（第2実施形態の場合）、又はスイッチノード55とグラウンドとの間（第1実施形態の場合）に接続される、ローパスフィルタと組み合わせる。パフォーマンス（性能）並びにコンデンサ及びスイッチの両端でのストレス電圧は、両実施形態で関連し得る。10

## 【0052】

また、第2実施形態の場合、出力インダクタ電流ioは出力負荷電流及び保持容量電流の両方を運ぶ。スイッチ要素60の両端の最大ストレス電圧はコンデンサChの両端の電圧であり、Vo/dである（dはデューティサイクル）。通常、保持容量電圧vcはコンセント整流器電圧vr及び出力負荷電圧voより高い。

## 【0053】

図6に示すように、平均入力電流ir(av)は、整流コンセント電圧vrのゼロ交差にてゼロになる。デューティサイクルdは出力負荷電圧voに比例し、保持容量電圧vcに反比例する。図7は、電源（コンセント）サイクル電圧のゼロ交差から3ms後の高スイッチング周波波形を示す。図7は、入力電流irの不連続導通動作モードを示す。スイッチ60がオフの間は常にダイオード電流idが存在するため、出力での連続導通モードが保証される。ただし、これは必須ではなく、出力での非連続導通モードが許容されてもよい。20

## 【0054】

この例において、保持容量Csは1μF(100nF/W)程度に低くてもよく、一方、一定な出力電力及び高効率が保証される。ステップダウン変換により、負荷電圧voを電源ピーク電圧（例えば、USコンセント電源の場合は70V）より著しく低くすることができます。Cukコンバータのローパスフィルタは良好な高周波フィルタリングを提供し、負荷22における低電流リップルを維持する。30

## 【0055】

図6に例示される定常状態波形、及び図7に例示される電源サイクルから位相角0.18における高周波波形において（両図ともにドライバ装置50bの第2実施形態の場合を示す）、Vm=120Veff、60Hz、スイッチング周波数200kHz、Lm=400μH、Lc=L0=2mH、Po=10W、vo=70V、Cs=1μF、PF=95%、THD=23%、スイッチ両端の最大電圧ストレス=337Vである。「av」は、スイッチングサイクルにかけての平均成分を示し、「d」はデューティサイクルを示す。

## 【0056】

図4a及び4bは本発明に係るドライバ装置50c、50dの第3及び第4実施形態を概略的に示す。これらの実施形態はドライバ装置50a、50bと実質的に同一であるが、これらの実施形態では、Cuk型電力変換ユニット65aがSEPIC型電力変換ユニット65bに置き換えられている。また、電力出力端子53、54及び負荷22の極性が逆転されている。40

## 【0057】

SEPIC型電力変換ユニット65bは、高電力入力端子51とスイッチノード55との間に結合された第1インダクタLmを有する。エネルギー保持要素Ch、具体的には中間コンデンサは、スイッチノード55と中間ノード58との間に結合される。ダイオードDoが中間ノード58と高電力出力端子53との間に結合される。最後に、第2インダク50

タ  $L_o$  が中間ノード 5 8 と低電力入力端子 5 2との間に結合される。スイッチング要素 6 0 は、スイッチノード 5 5 と低電力入力端子 5 2との間に結合される。

#### 【 0 0 5 8 】

したがって、ドライバ装置 5 0 c、5 0 d の第 3 及び第 4 実施形態においては、回路は S E P I C 型電力コンバータを、直列接続された高周波フィルタインダクタ  $L_c$  と低周波（コンセント周波数）保持容量  $C_s$  とを含み、スイッチノード 5 5 と負荷との間（第 4 実施形態の場合）、又はスイッチノード 5 5 とグランドとの間（第 3 実施形態の場合）に接続される、ローパスフィルタと組み合わせる。パフォーマンス、並びにコンデンサ両端及びスイッチ両端のストレス電圧は両実施形態間で関連し得る。また、第 4 実施形態の場合において、出力インダクタ電流  $i_o$  は、平均で出力負荷電流  $i_d$  マイナス保持容量電流  $i_h$  を運ぶ。スイッチ 6 0 両端の最大ストレス電圧は、コンデンサ  $C_h$  両端の電圧  $v_h$  プラス出力電圧  $v_o$  に等しい。通常、保持容量電圧  $v_h$  は出力電圧  $v_o$  より高く、実質的にピーク電圧の 30 % より大きく振動できる。

10

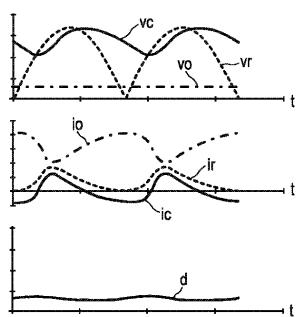

#### 【 0 0 5 9 】

図 8 に示すように、平均入力電流  $i_r$  ( $a_v$ ) は、整流コンセント電圧  $v_r$  のゼロ交差においてゼロになる。デューティサイクル  $d$  は出力負荷電圧  $v_o$  に比例し、保持容量電圧  $v_h$  プラス出力負荷電圧  $v_o$  の 2 倍に反比例する。高スイッチング周波数波形は図に示す第 2 実施形態のものと同等である。

#### 【 0 0 6 0 】

この例において、保持容量  $C_h$  は  $4 \mu F$  程度に低くでもよく、一定な出力電力及び高効率を保証する。ステップダウン変換により、負荷電圧  $v_o$  は電源ピーク電圧（例えば、U S コンセント電源の場合 30 V）より著しく低くなり得る。

20

#### 【 0 0 6 1 】

図 8 に例示の定常状態波形（ドライバ装置 5 0 d の第 4 実施形態に対応）において、 $v_m = 120 V_{eff}$ 、60 Hz、スイッチング周波数 200 kHz、 $L_m = 300 \mu H$ 、 $L_c = L_o = 2 mH$ 、 $P_o = 10 W$ 、 $v_o = 30 V$ 、 $C_s = 4 \mu F$ 、PF = 92 %、THD = 35 %、スイッチ間の最大電圧ストレス = 228 V である。

#### 【 0 0 6 2 】

図 5 a 及び 5 b は、本発明に係るドライバ装置 5 0 e、5 0 f の第 5 および第 6 実施形態を概略的に示す。これらの実施形態はドライバ装置 5 0 c、5 0 d の実施形態と実質的に同一であるが、これらの実施形態では S E P I C 型電力変換ユニット 6 5 b が Zeta 型電力変換ユニット 6 5 c によって置き換えられている。また、コンデンサ  $C_s$  及び  $C_h$  の極性が逆転されている。

30

#### 【 0 0 6 3 】

Zeta 型電力変換ユニット 6 5 c は、高電力入力端子 5 1 とスイッチノード 5 5 の間に結合されたスイッチング要素 6 0 を有する。第 1 インダクタ  $L_m$  がスイッチノード 5 5 と低電力入力端子 5 2 の間に結合されている。第 1 ダイオード  $D_m$  が第 1 インダクタ  $L_m$  と直列に結合されている。エネルギー保持要素  $C_h$ 、具体的には中間コンデンサは、スイッチノード 5 5 と中間ノード 5 8 の間に結合されている。第 2 インダクタ  $L_o$  が中間ノード 5 8 と高電力出力端子 5 3 の間に結合されている。最後に、第 2 ダイオード  $D_o$  が中間ノード 5 8 と低電力出力端子 5 4 の間に結合されている。

40

#### 【 0 0 6 4 】

よって、ドライバ装置 5 0 e、5 0 f の第 5 および第 6 実施形態において、回路は Zeta 型の電力コンバータを、直列接続された高周波フィルタインダクタ  $L_c$  と低周波（コンセント周波数）保持容量  $C_s$  とを有し、スイッチノード 5 5 と負荷との間（第 6 実施形態の場合）、又はスイッチノード 5 5 とグランドとの間（第 5 実施形態の場合）に接続される、ローパスフィルタを組み合わせる。パフォーマンス並びにコンデンサ両端及びスイッチ両端のストレス電圧における違いは両実施形態間で関連し得る。また、第 6 実施形態の場合、出力インダクタ電流  $i_o$  は出力負荷電流  $i_d$  及び保持容量電流  $i_h$  の両方を運ぶ。スイッチ 6 0 両端の最大ストレス電圧はコンデンサ  $C_h$  両端の電圧  $v_h$  プラス整流コン

50

セント電圧  $v_r$  に等しい。通常、保持容量電圧  $v_h$  はコンセント整流電圧  $v_r$  及び出力負荷電圧  $v_o$  より高い。

#### 【0065】

図9に示すように、この実施形態においては（他の構成と異なり）、平均入力電流  $i_r$  ( $a_v$ ) は整流コンセント電圧  $v_r$  のゼロ交差においてゼロにならない。デューティサイクル  $d$  は出力負荷電圧  $v_o$  に比例し、整流コンセント電圧  $v_r$  マイナス保持容量電圧  $v_h$  に反比例する。

#### 【0066】

図10は、電源（コンセント）サイクル電圧のゼロ交差から3ms後の高スイッチング周波数波形を示す。図10は、昇圧インダクタ  $L_m$  の非連続動作モードを示す。スイッチ 10 60がオフの間はダイオード電流  $i_d$  が常に存在するため、出力では連続導通モードが保証される。ただし、これは必須ではなく、出力での非連続導通モードが許容され得る。

#### 【0067】

この例において、保持容量は  $2 \mu F$  ( $200nF/W$ ) 程度に低くてもよく、それでも一定な出力電力及び高効率を保証する。ステップダウン変換により、負荷電圧  $v_o$  は電源ピーク電圧（例えば、USコンセント電源の場合は100V）より著しく低くなり得る。 $Zeta$  型段階のローパスフィルタは良好な高周波フィルタリングを提供し、LED負荷における低電流リップルを維持する。いくつかの動作条件においては整流入力電流  $i_r$  が負になり得るため、好ましくは、入力にて高周波デカップリング（バイパス）コンデンサ 20  $C_m$  が用いられる。

#### 【0068】

図9に示す定常状態波形、及び図10に示す電源（コンセント）サイクルから位相角0.18°の高周波波形（ともにドライバ装置50fの第6実施形態の場合）において、 $v_m = 120Veff$ 、60Hz、スイッチング周波数200kHz、 $L_m = 400\mu H$ 、 $L_c = L_o = 4mH$ 、 $P_o = 10W$ 、 $v_o = 100V$ 、 $C_s = 2\mu F$ 、PF = 94%、THD = 36%、スイッチ間最大電圧ストレス = 398Vである。

#### 【0069】

次に、本発明に係る制御方法及び制御装置が説明される。図11は、制御ユニット64'の第1実施形態を含むドライバ装置50gの他の実施形態を示す（ドライバ装置の他の部品は単一のブロック50'で概略的に示す）。LED電流  $i_{LED}$  が比較要素64aにおいて測定され、（プリセット又は可変の）基準電流  $i_{LED\_ref}$  と比較される。制御誤差  $e_{rr\_i}$  はコントローラブロック64b（PI）内で処理され、操作変数としてのデューティサイクル  $d$  となる。（ゲート）ドライバブロック64cにおいて、プリセットスイッチング周波数  $f_s$  と合わせて、スイッチング要素60の制御信号  $S_{60}$  を表すゲート駆動信号が形成される。

#### 【0070】

図12は、スイッチング要素60（のゲートの）タイミングダイアグラムを示す。

#### 【0071】

典型的には降圧コンバータで行われるように、デューティサイクルは基本的には制御誤差に関連付けられる。ドライバ装置50gの実施形態に関しては、正の制御誤差  $e_{rr\_i}$ （小さすぎる電流）は  $d$  の増加を引き起こし、その逆も同様である。

#### 【0072】

自己安定挙動は、 $C_s$ 両端の電圧ストレスの限界を超えることなく適切な電力バランスを保証する。これは提案の回路配置及び採用の制御スキームによって得られる。例えば、出力から取り出される平均電力より入力から引き込まれる平均電力が大きい場合、バス電圧  $v_c$  が高くなり、 $d$  が減少するように制御され、入力電力が減らされる。他の実施形態も同様に動作可能である。ドライバ装置50a、50c、50eの実施形態に対して、ドライバ装置50b、50d、50fの実施形態ではデューティサイクルの意味が切り替える、すなわち、 $d$  が  $1 - d$  に置き換えられる。バス電圧及びコンセント電流（PF）等の他の動作特性は、通常明確には制御されない。これらの特性は、設計及び動作選択及 50

び許容範囲による。

**【0073】**

他の実施形態においては、最大バス電圧も上記制御によって明確に制御され、特に、スイッチング周波数も操作することによって明確に制御される。出力電流を制御するために  $d$  を操作する一方、バス電圧の増加（例えば、高コンセント電圧又は高出力電圧に由来する）に対応して  $f_s$  が上昇される。代わりに、 $T_{on}$  及び  $T_{off}$  を別々に制御してもよいが、この場合もスイッチングパターンは同様になる。

**【0074】**

基準信号  $i_{LED\_ref}$  が可変で定格最大値よりはるかに低い場合、バス電圧が過度に高くなるのを防ぐため（すなわち、過度の昇圧を防ぐため）、他の実施形態においては上記制御はバーストモードに入る、すなわち、 $f_s$  より低い（例えば、10 ~ 1000 分の1）バースト頻度にてコンバータのスイッチをオフにする。PFを改善するために、又は所定の種類の壁コンセントディマーへの適合を高めるために、バス電圧制御のための周波数変調に加えて、又はその代わりに、入力電流の変調に  $f_s$  を用いてもよい。

10

**【0075】**

図13は、制御ユニット64”の第2実施形態を含むドライバ装置50hの他の実施形態を示す。図11の実施形態に対して、制御ユニット64”は、さらに第2コントローラブロック64d（PI）を有し、操作変数としてのスイッチング周波数  $f_s$ 、 $f_s_{brst}$  が（ゲート）ドライバブロック64cに供給される。第2コントローラブロック64dは、入力基準電流  $i_{LED\_ref}$  としてバス電圧  $v_c$ 、入力電流  $i_r$ 、入力電圧  $v_m$ 、及び最大バス電圧  $v_{c\_max}$  を受ける。

20

**【0076】**

本発明によれば、前処理ユニットが組み込まれ、且つ、高効率を備える一方で負荷に一定な出力電流を供給する単段式電力コンバータトポロジーを備えるドライバ装置が提案される。少数の部品しか必要なく、ハーフ／フルスイッチブリッジや大きな電界コンデンサは不要ない。これは、ローパスフィルタが一体化された（組み込まれた）電力コンバータを適切に制御することで達成される。上記変換機能の実行には、通常一つのスイッチ（例えば、MOSFETトランジスタ）しか要求されない。ドライバ装置は、高電圧LEDストリングを使用するオフラインLEDドライバに好適に適用可能である。

30

**【0077】**

本発明の実施形態によれば、一つの昇圧インダクタが非連続導通モードで動作する。これを強化するために、ダイオードが好適に直列に結合される（入力整流器ブリッジのものか、又は専用のもの）。高スイッチング周波数電流成分をフィルタリング除去するために、好ましくは二つのインダクタが用いられる。好ましくは、一つの高周波バイパスコンデンサが出力に結合され、またいくつかの場合においては、二つ目が入力（整流ブリッジの出力）に結合される。

**【0078】**

スイッチノードは、さらに第3インダクタ、具体的には高周波インダクタに接続され、高周波インダクタは、小さな低周波保持容量に直列接続されることによってフィルタを形成する。スイッチノードはさらに中間保持要素として用いられる高周波コンデンサに接続され、スイッチングサイクル内で出力にエネルギーを運ぶ。整流器コンセントは昇圧インダクタ又はスイッチのいずれかに接続されてもよい。

40

**【0079】**

低周波保持容量の一方の端子はグランド又は負荷のいずれに結合されてもよい。また、負荷（例えばLED）電流のみが一定に制御されてもよいし（例えば、デューティサイクルによって）、周波数を操作するとともにLED電流及びバス電圧の両方を二つのループで制御してもよい。

**【0080】**

本発明は、コンシューマー（消費者）用及び「プロシューマ（生産消費者）」用ドライバに適用され、例えば2W以上で、照明装置に組み込まれて使用されたり、又はHV

50

L E D用の外部L E Dドライバ等に適用される。他の適用例は、T H D要求（例えば、20%）及びH V L E Dストリング負荷が緩和された非コンセント独立プロフェッショナル（又は生産者用）ドライバである。

#### 【0081】

以上、本発明を記載及び図面によって詳細に記述及び描写してきたが、記述及び描写はあくまで説明のためであって限定をするものではない。本発明は、開示された実施形態に限定されない。図面、明細書、及び特許請求の範囲を参照することで、当業者は、発明を実施するにあたり、開示された実施形態の他の変形例を理解及び実行できるであろう。

#### 【0082】

特許請求の範囲において、「有する（又は備える、含む）」という単語は他の要素又はステップを除外せず、要素は複数を除外しない。一つの要素又は他のユニットが請求項に記載の複数の項目の機能を満たしてもよい。いくつかの手段が異なる独立請求項に記載されているからといって、これらの手段の組み合わせを好適に用いることができないとは限らない。

#### 【0083】

請求項内の参照符号は特許請求の範囲を限定しない。

10

【図1】

FIG. 1

【図2a】

FIG. 2a

【図2b】

FIG. 2b

【図3a】

FIG. 3a

【図3b】

FIG. 3b

【図 4 a】

FIG. 4a

【図 4 b】

FIG. 4b

【図 5 a】

FIG. 5a

【図 5 b】

FIG. 5b

【図 6】

FIG. 6

【図 7】

FIG. 7

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

---

フロントページの続き

(72)発明者 エルフェリッヒ レインホールド

オランダ国 5656 アーエー アインドーフェン ハイ テック キャンパス ビルディング

44

審査官 松本 泰典

(56)参考文献 特開2007-110070(JP,A)

特開2009-011109(JP,A)

特開2011-082204(JP,A)

米国特許出願公開第2007/0171680(US,A1)

特開2009-089564(JP,A)

特開平05-176532(JP,A)

米国特許第05442539(US,A)

特開平03-226266(JP,A)

(58)調査した分野(Int.Cl., DB名)

H05B 37/02

H02M 3/155

H02M 7/12