(12) 发明专利

(10) 授权公告号 CN 109075902 B

(45) 授权公告日 2022.02.08

(21) 申请号 201780028376.5

越坂直弘

(22) 申请日 2017.05.02

(74) 专利代理机构 北京康信知识产权代理有限

(65) 同一申请的已公布的文献号

责任公司 11240

申请公布号 CN 109075902 A

代理人 余刚 吴孟秋

(43) 申请公布日 2018.12.21

(51) Int.CI.

H04L 1/00 (2006.01)

(30) 优先权数据

G06F 13/42 (2006.01)

2016-099955 2016.05.18 JP

H04L 7/04 (2006.01)

(85) PCT国际申请进入国家阶段日

(56) 对比文件

2018.11.07

US 2005206542 A1, 2005.09.22

(86) PCT国际申请的申请数据

US 2005172199 A1, 2005.08.04

PCT/JP2017/017221 2017.05.02

CN 1667998 A, 2005.09.14

(87) PCT国际申请的公布数据

US 2015100711 A1, 2015.04.09

W02017/199761 EN 2017.11.23

CN 101541078 A, 2009.09.23

(73) 专利权人 索尼公司

CN 102263767 A, 2011.11.30

地址 日本东京

审查员 张焕娜

(72) 发明人 高桥宏雄 横川峰志 李惺薰

权利要求书2页 说明书12页 附图8页

(54) 发明名称

通信装置、通信方法、程序和通信系统

(57) 摘要

提供了一种通信装置，包括：发送和接收单元，其与另一通信装置发送和接收信号；误差检测单元，其通过使所述发送和接收单元接收指定接下来要发送的数据类型的前导码，并将继前导码之后接收到的信号的位序列与针对由前导码指定发送的类型而应该发送的位序列进行比较，来检测发生误差；以及冲突避免单元，如果误差检测单元检测到发生误差，则所述冲突避免单元指示所述发送和接收单元发送与继前导码之后的特定位数对应的时钟，然后，发送中止信号，该中止信号给出中途终止通信的指令。

1. 一种通信装置,包括:

发送和接收电路,被配置为与外部通信装置通信,包括经由数据信号线发送和接收数据以及经由时钟信号线发送时钟;以及

控制电路,被配置为通过将继所接收到的数据的前导码之后的第一位序列与对应于由前导码指定的数据类型第二位序列进行比较,来检测在信号中发生的误差,并且

在检测到发生误差的情况下,使所述发送和接收电路在对应于继前导码之后的至少预定位数的第一持续时间内发送时钟,

所述控制电路还被配置为响应于接收到从所述发送和接收电路发送的数据而检测从所述外部通信装置发送的确认信号或确认信号不存在中的至少一个,其中,当检测到确认信号不存在时,所述控制电路使所述发送和接收电路在忽略继确认信号不存在之后的预定数量的位之后发送命令信号。

2. 根据权利要求1所述的通信装置,其中,当所述数据的前导码指定发送包括令牌和CRC-5的循环冗余校验CRC字、并且所述控制电路基于第一位序列检测到发生令牌误差或CRC误差中的至少一个时,所述发送和接收电路发送时钟达根据至少所述CRC字中的位数的第二持续时间及发送额外时钟达第一持续时间之后,发送命令信号,所述预定位数对应于在CRC字中的位数和数据中的位数之间的差值。

3. 根据权利要求2所述的通信装置,其中,所述控制电路在额外时钟的发送期间的至少一时段内忽略所述数据。

4. 根据权利要求3所述的通信装置,其中,所述发送和接收电路依在所发送的数据的前导码的第二位的时序发送所述命令信号。

5. 根据权利要求1所述的通信装置,其中,奇偶校验的第一奇偶校验位和第二奇偶校验位包括在数据中,并且误差检测电路将第一奇偶校验位视为偶数奇偶校验,将第二奇偶校验位视为奇数奇偶校验,并且通过对从外部通信装置接收的数据进行奇偶校验来检测误差的发生。

6. 根据权利要求1所述的通信装置,其中,所述发送和接收电路能够在SDR模式和至少一个HDR模式中发送数据并且接收信号,在SDR模式中,以第一传输速率进行数据通信,在HDR模式中,以第二传输速率进行数据通信,所述第二传输速率高于所述第一传输速率。

7. 根据权利要求6所述的通信装置,其中,所述至少一个HDR模式包括其中发送和接收电路能够通信的多个额外模式,所述多个额外模式包括:双数据速率模式、三元符号纯总线模式和三元符号遗留包含总线模式。

8. 根据权利要求6所述的通信装置,其中,所述发送和接收电路发送命令,该命令给出在经过第一持续时间之后退出所述至少一个HDR模式的指令。

9. 根据权利要求6所述的通信装置,其中,所述发送和接收电路发送命令,该命令给出在经过第一持续时间之后在所述至少一个HDR模式中重新开始通信的指令。

10. 根据权利要求1所述的通信装置,其中,所述发送和接收电路经由被配置为一次一位地依次发送串行数据的数据信号线和被配置为发送预定频率的串行时钟的时钟信号线进行通信。

11. 根据权利要求10所述的通信装置,其中,所述发送和接收电路自紧接在接收由驱动数据信号线的外部通信装置发送的CRC字之后的一位驱动数据信号线。

12. 根据权利要求1所述的通信装置,其中,所述控制电路被配置为如果所述第二位序列中的位数小于所述第一位序列中的位数,则检测到误差的发生。

13. 根据权利要求1所述的通信装置,其中,所述控制电路被配置为如果在前导码的第一位中发生1位误差,则检测到发生了误差。

14. 根据权利要求1所述的通信装置,其中,所述发送和接收电路按照改进的内部集成电路标准进行通信。

15. 一种通信系统,包括:

第一通信装置,包括:

第一发送和接收电路,被配置为通信,包括经由数据信号线发送和接收数据并且经由时钟信号线发送时钟,以及

控制电路,被配置为

通过将继所接收到的数据的前导码之后的第一位序列与对应于由前导码指定的数据类型的第二位序列进行比较,来检测在信号中发生误差,并且

在检测到发生误差的情况下,使所述第一发送和接收电路在对应于继前导码之后的至少预定位数的持续时间内发送时钟;以及

第二通信装置,包括:

第二发送和接收电路,被配置为与所述第一通信装置通信,包括经由数据信号线发送和接收数据并且经由时钟信号线接收时钟,

其中,所述第二通信装置被配置为向所述第一通信装置发送第一位序列,

所述控制电路还被配置为响应于接收到从所述第一发送和接收电路发送的数据而检测从所述第二通信装置发送的确认信号或确认信号不存在中的至少一个,其中,当检测到确认信号不存在时,所述控制电路使所述第一发送和接收电路在忽略继确认信号不存在之后的预定数量的位之后发送命令信号。

16. 根据权利要求15所述的通信系统,其中,当所述数据的前导码指定发送包括令牌和CRC-5的循环冗余校验CRC字、并且所述控制电路基于第一位序列检测到发生令牌误差或CRC误差中的至少一个时,所述发送和接收电路在发送时钟达根据至少所述CRC字中的位数的第一持续时间及发送额外时钟达对应于CRC字中的位数和数据中的位数之间的差值的第二持续时间之后,发送命令信号。

17. 根据权利要求15所述的通信系统,其中,所述控制电路被配置为如果第二位序列中的位数小于第一位序列中的位数,则检测到发生了误差。

18. 根据权利要求15所述的通信系统,其中,所述控制电路被配置为如果在前导码的第一位中发生1位误差,则检测到发生了误差。

## 通信装置、通信方法、程序和通信系统

### 技术领域

[0001] 本公开涉及一种通信装置、一种通信方法、一种程序和一种通信系统，更具体地，涉及一种能够更可靠地进行通信的通信装置、通信方法、程序和通信系统。

[0002] <交叉引用相关申请>

[0003] 本申请要求于2016年5月18日提交的日本优先权专利申请JP 2016-099955的权益，其全部内容通过引用结合于此。

### 背景技术

[0004] 目前，广泛使用总线接口(IF)，用于经由安装有多个装置的板内部的总线，在装置之间进行通信，例如，内部集成电路(I2C)。

[0005] 此外，最近，人们要求实现更快的I2C速度，并且正在建立改进的集成电路(I3C)，作为下一代标准。通过I3C，主设备和从设备能够使用两条信号线双向通信。例如，进行从主设备到从设备的数据传输(写传输)和从设备到主设备的数据传输(读传输)。

[0006] 例如，专利文献1公开了一种数字数据处理系统，其中，主机处理器和子系统控制器通过I2C互连。另外，专利文献2公开了一种实现部署在标准I2C协议之上的更高层中的通信协议的方法。

[0007] 引文列表

[0008] 专利文献

[0009] PTL 1:JP 2000-99448A

[0010] PTL 2:JP 2002-175269A

### 发明内容

[0011] 技术问题

[0012] 同时，例如，如上所述的I3C规定，将在主设备和从设备之间进行使用诸如奇偶校验或循环冗余校验(CRC)等方法的误差检测，但是也将发送和接收这些误差检测不可用的信号。因此，当误差检测不可用的信号中发生误差时，人们担心主设备和从设备可能无法进行正常通信。

[0013] 鉴于这种情况，设计本公开，并且本公开能够更可靠地进行通信。

[0014] 问题的解决方案

[0015] 根据本公开第一方面的通信装置包括：发送和接收单元，其与另一通信装置发送和接收信号；误差检测单元，其通过使所述发送和接收单元接收指定接下来要发送的数据类型的前导码，并将在前导码之后接收的信号的位序列与针对由前导码指定用于发送的该类型发送的位序列进行比较，来检测发生误差；以及冲突避免单元，如果误差检测单元检测到发生误差，则所述冲突避免单元指示所述发送和接收单元发送与前导码之后的特定位数对应的时钟，然后，发送中止信号，该中止信号给出中途终止通信的指令。

[0016] 根据本公开第一方面的通信方法或程序包括：与另一通信装置发送和接收信号；

通过接收指定接下来要发送的数据类型的前导码，并将在前导码之后接收的信号的位序列与针对由前导码指定用于发送的该类型发送的位序列进行比较，来检测发生误差；并且如果检测到发生误差，则发送与前导码之后的特定位数对应的时钟，然后，发送中止信号，该中止信号给出中途终止通信的指令。

[0017] 在本公开的第一方面中，与另一通信装置发送和接收信号；并且通过接收指定接下来要发送的数据类型的前导码，并将在前导码之后接收的信号的位序列与针对由前导码指定发送的该类型发送的位序列进行比较，来检测发生误差。然后，如果检测到发生误差，则发送与前导码之后的特定位数对应的时钟，然后，发送中止信号，该中止信号给出中途终止通信的指令。

[0018] 根据本公开的第二方面的系统包括：第一通信装置，其在总线中具有控制主动权；以及第二通信装置，其根据所述第一通信装置的控制进行通信。所述第一通信装置包括：发送和接收单元，其与另一通信装置发送和接收信号；误差检测单元，其通过使所述发送和接收单元接收指定接下来要发送的数据类型的前导码，并将在前导码之后接收的信号的位序列与针对由前导码指定发送的该类型发送的位序列进行比较，来检测发生误差；以及冲突避免单元，如果误差检测单元检测到发生误差，则所述冲突避免单元指示所述发送和接收单元发送与前导码之后的特定位数对应的时钟，然后，发送中止信号，该中止信号给出中途终止通信的指令。

[0019] 在本公开的第二方面，在总线中具有控制主动权的第一通信装置以及根据所述第一通信装置的控制进行通信的第二通信装置进行通信。此外，在第一通信装置中，向第二通信装置发送信号和从第二通信装置接收信号，接收指定接下来要发送的数据类型的前导码，并且通过将在前导码之后接收的信号的位序列与针对由前导码指定发送的该类型发送的位序列进行比较，来检测发生误差。随后，如果检测到发生误差，则在发送与前导码之后的特定位数对应的时钟之后，发送中止信号，该中止信号给出中途终止通信的指令。

[0020] 发明的有益效果

[0021] 根据本公开的第一和第二方面，可以更可靠地进行通信。

## 附图说明

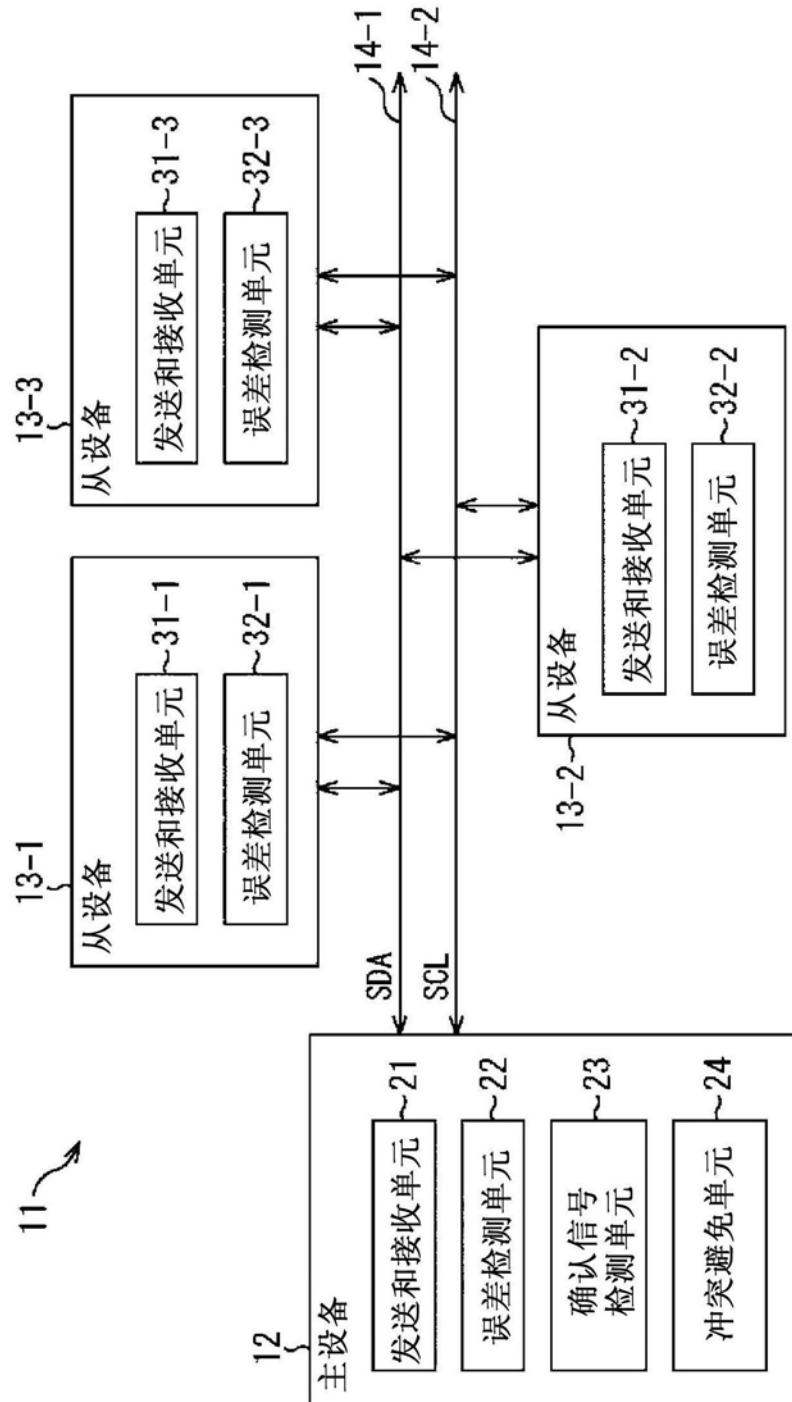

- [0022] 图1是示出应用本技术的总线IF的实施例的示例配置的方框图；

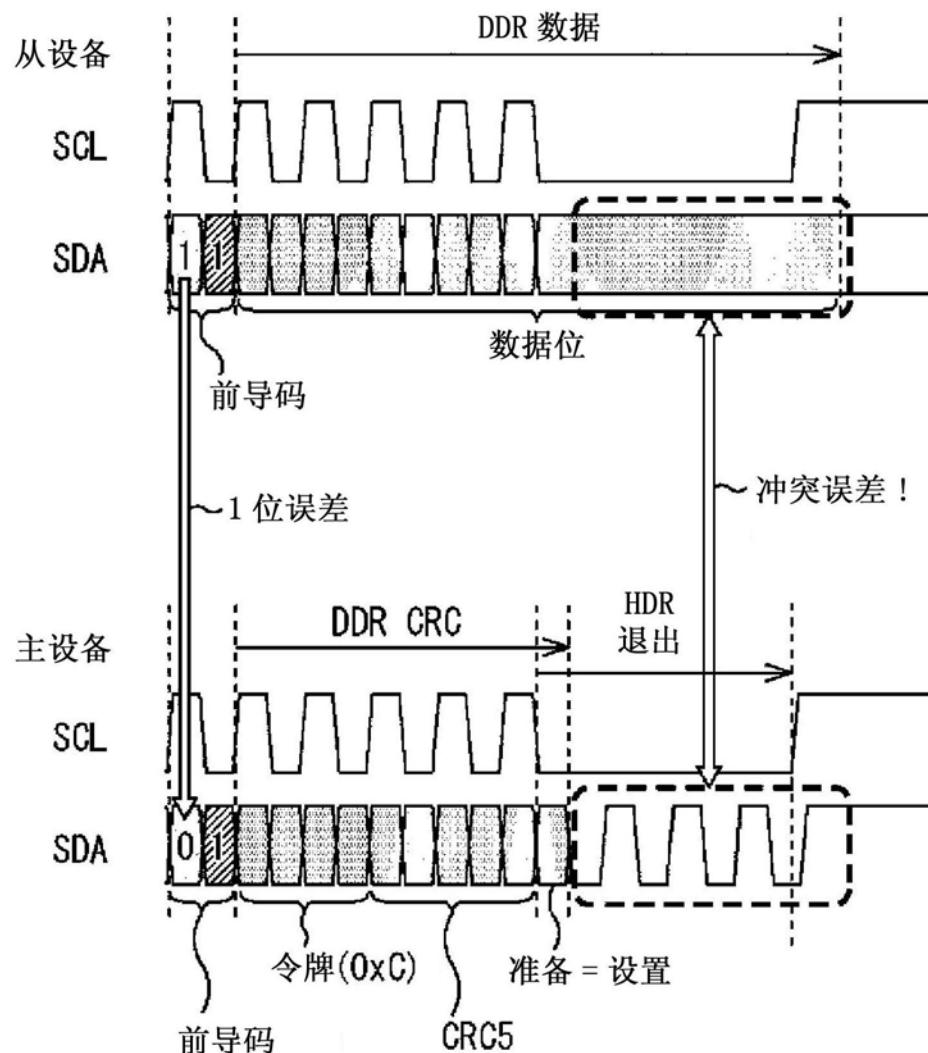

- [0023] 图2是解释冲突误差的示图；

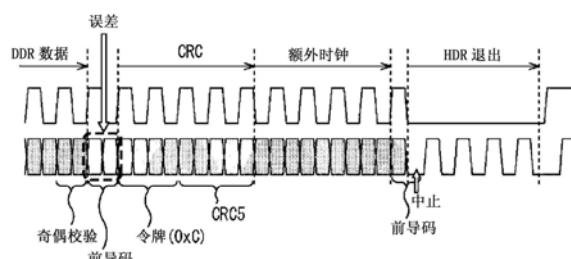

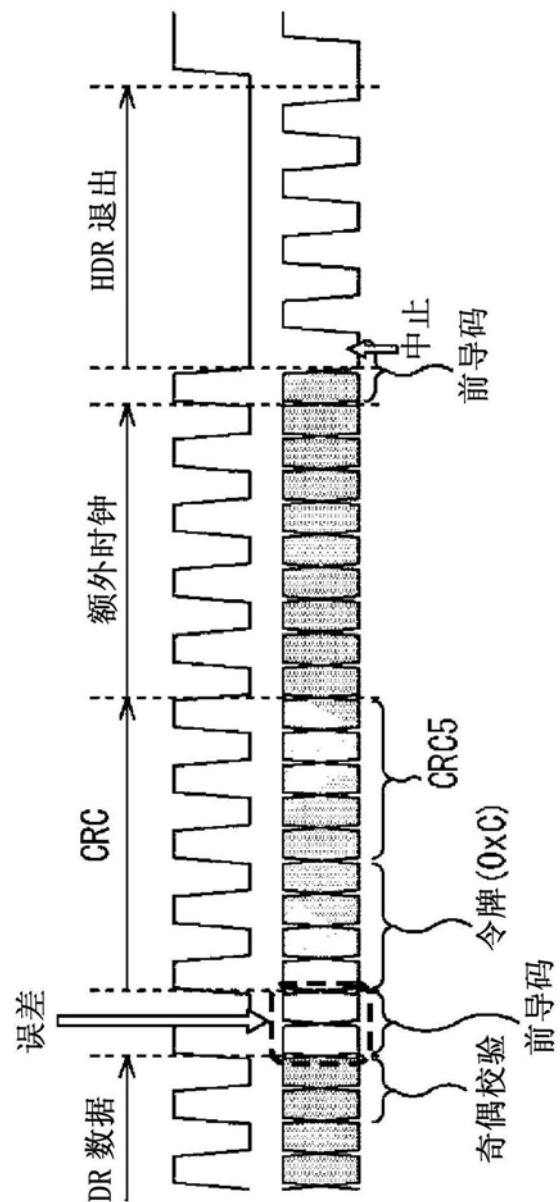

- [0024] 图3是示出避免冲突误差的格式的示例的示图；

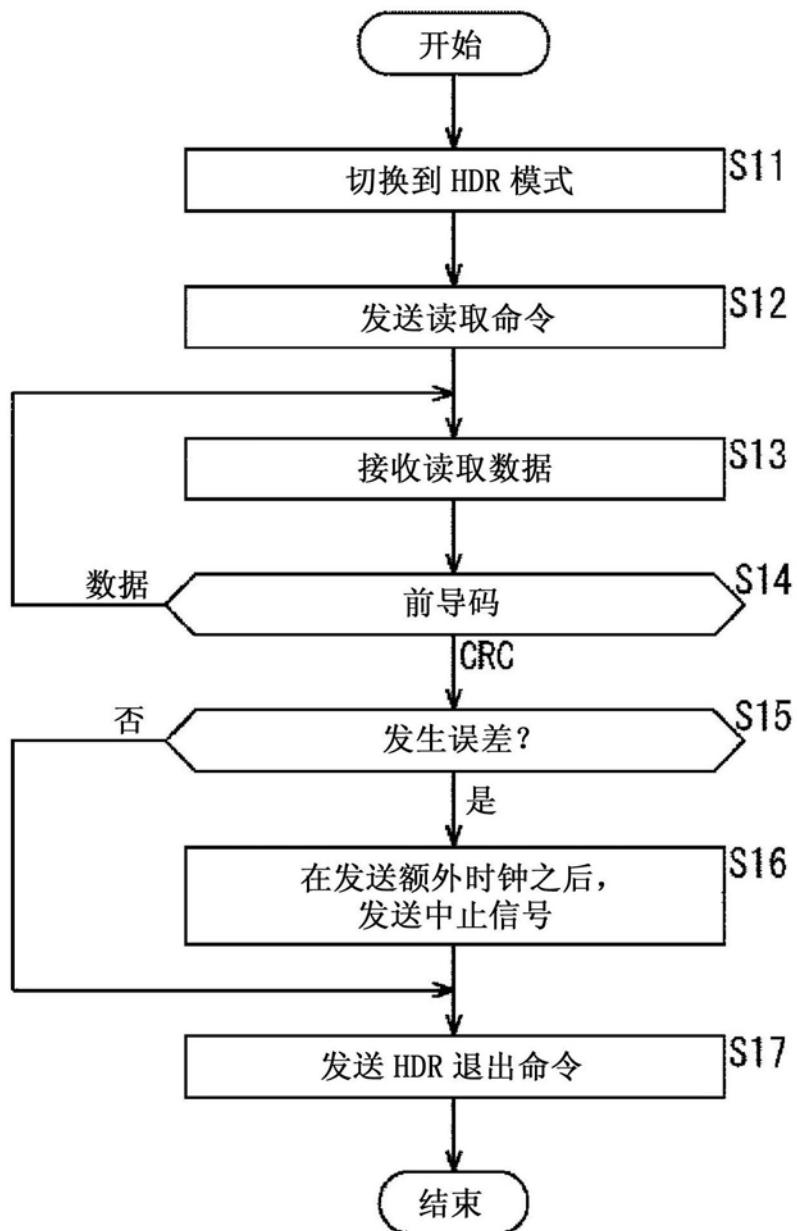

- [0025] 图4是解释主设备的DDR模式下的通信过程的流程图；

- [0026] 图5是示出主设备的示例配置的电路图；

- [0027] 图6是示出避免冲突误差的格式的另一示例的示图；

- [0028] 图7是示出避免冲突误差的格式的另一示例的示图；

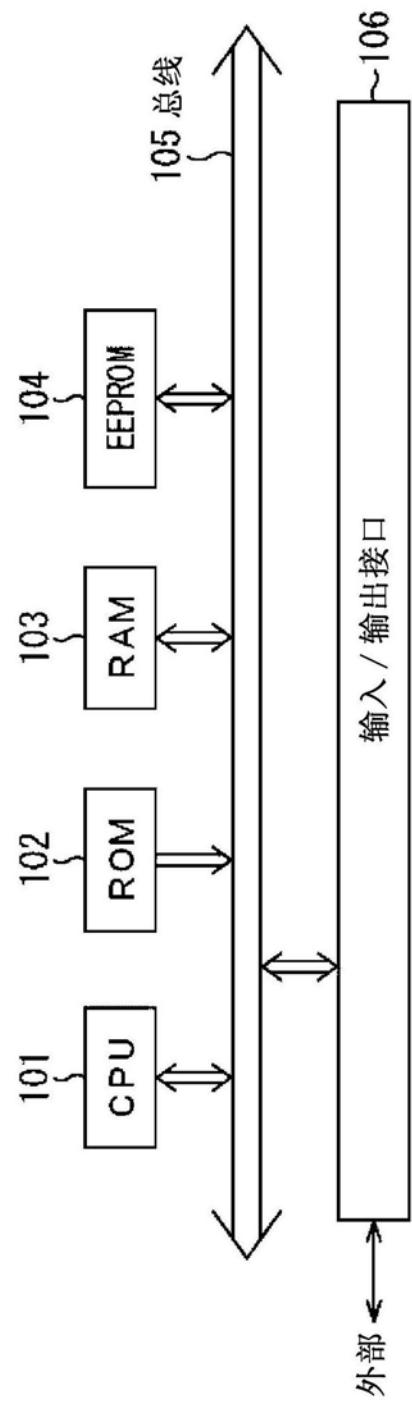

- [0029] 图8是示出应用本技术的计算机的实施例的示例配置的方框图。

## 具体实施方式

- [0030] 在下文中，将参考附图详细描述应用本技术的具体实施例。

- [0031] <总线IF的示例配置>

[0032] 图1是示出应用本技术的总线IF的实施例的示例配置的方框图。

[0033] 图1所示的总线IF 11由经由数据信号线14-1和时钟信号线14-2彼此连接的主设备12和三个从设备13-1至13-3组成。

[0034] 主设备12对总线IF 11具有控制主动权，并且能够经由数据信号线14-1和时钟信号线14-2与从设备13-1至13-3通信。

[0035] 在主设备12的控制下，从设备13-1至13-3能够经由数据信号线14-1和时钟信号线14-2与主设备12通信。注意，从设备13-1至13-3彼此类似地配置，并且在下文中，当没有单独区分时，将简单地称为从设备13。这同样适用于构成从设备13的各个方框。

[0036] 数据信号线14-1和时钟信号线14-2用于在主设备12和从设备13之间中继信号。例如，在总线IF 11中，串行数据 (SDA) 经由数据信号线14-1一次一位地依次中继，而特定频率的串行时钟 (SCL) 经由时钟信号线14-2中继。

[0037] 此外，在总线IF 11中，根据I3C标准规定了具有不同通信速度的多个传输方案，并且主设备12能够在这些传输方案之间切换。例如，在总线IF 11中，根据数据传输速率，规定了以标准传输速率进行数据通信的标准数据速率 (SDR) 模式和以比 SDR 模式更高的传输速率进行数据通信的高数据速率 (HDR) 模式。此外，在HDR模式中，该标准定义了三种模式，即，双数据速率 (DDR) 模式、三元符号纯总线 (ternary symbol pure-bus, TSP) 模式和三元符号遗留包含总线 (ternary symbol legacy-inclusive bus, TSL) 模式。注意，在总线IF 11中，规定在开始通信时以SDR模式进行通信。

[0038] 主设备12设置有发送和接收单元21、误差检测单元22、确认信号检测单元23和冲突避免单元24。

[0039] 发送和接收单元21经由数据信号线14-1和时钟信号线14-2向从设备13发送信号和从从设备13接收信号。例如，发送和接收单元21根据通过驱动时钟信号线14-2而发送的串行时钟的时间，通过驱动数据信号线14-1(将电势切换到H电平或L电平)来向从设备13发送信号。另外，发送和接收单元21接收从设备13发送的信号，作为从设备13根据时钟信号线14-2上的串行时钟的时间来驱动数据信号线14-1的结果。注意，由主设备12侧连续进行时钟信号线14-2的驱动。

[0040] 误差检测单元22检测由发送和接收单元21接收的信号中发生的误差。例如，误差检测单元22能够通过对由发送和接收单元21接收的信号进行诸如奇偶校验或循环冗余校验 (CRC) 等校验，或者通过确认将传输权从从设备13转移到主设备12时发出的令牌，来检测误差。另外，当误差检测单元22检测到由发送和接收单元21接收的信号中发生误差时，例如，误差检测单元22能够指示发送和接收单元21从一开始就与从设备13重新开始通信。

[0041] 例如，在从设备13发送的数据中包括的两个奇偶校验位之间，误差检测单元22可以将一个奇偶校验位视为偶数奇偶校验，并且将另一奇偶校验位视为奇数奇偶校验，并且通过对发送和接收单元21接收的数据进行奇偶校验，来检测发生误差。因此，即使出现主设备12或从设备13没有驱动数据信号线14-1的状态，误差检测单元22仍然能够检测数据是否正确。

[0042] 确认信号检测单元23检测其接收从发送和接收单元21发送的信号的从设备13发送的确认信号 (ACK) 或否认信号 (NACK)，从而确认从设备13是否成功接收了诸如命令或数据等信息。例如，在总线IF 11中，规定当信号中没有发生误差，并且从设备13成功接收到诸

如命令或数据等信息时,ACK将从从设备13发送到主设备12。此外,在总线IF 11中,规定当信号中发生误差,并且从设备13未能接收诸如命令或数据等信息时,NACK将从从设备13发送到主设备12。

[0043] 因此,在响应于从主设备12发送的诸如命令或数据等信息而检测到从从设备13发送的ACK的情况下,确认信号检测单元23能够确认从设备13已经成功地接收到诸如命令或数据等信息。另一方面,在响应于从主设备12发送的诸如命令或数据等信息而检测到从从设备13发送的NACK的情况下,确认信号检测单元23能够确认从设备13未能接收诸如命令或数据等信息。

[0044] 关于冲突避免单元24,如稍后参考图3所述,例如,当发送和接收单元21接收到带有发送CRC字的指令的前导码,并且误差检测单元22检测到继前导码之后的所接收到的信号中发生令牌误差或CRC误差时,在发送了对应于继前导码之后的特定位数的时钟之后,冲突避免单元24指示发送和接收单元21发送中止信号,该中止信号给出中途终止通信的指令。因此,例如,冲突避免单元24能够避免由于从从设备13发送的读取数据和从主设备12发送的HDR退出命令而发生冲突。

[0045] 另外,如果确认信号检测单元23检测到NACK,例如,在忽略了NACK之后的特定数量的位之后,冲突避免单元24指示发送和接收单元21发送中止信号,该中止信号给出中途终止通信的指令。因此,例如,冲突避免单元24能够避免由于从从设备13发送的读取数据和从主设备12发送的HDR退出命令而发生冲突。

[0046] 从设备13设置有发送和接收单元31以及误差检测单元32。

[0047] 发送和接收单元31经由数据信号线14-1和时钟信号线14-2向主设备12发送信号和从主设备12接收信号。例如,发送和接收单元31接收从主设备12发送的信号,作为主设备12根据时钟信号线14-2上的串行时钟的时间驱动数据信号线14-1的结果。此外,发送和接收单元31通过根据时钟信号线14-2上的串行时钟的时间驱动数据信号线14-1,来向主设备12发送。

[0048] 与主设备12的误差检测单元22类似,误差检测单元32检测由发送和接收单元31接收的信号中发生的误差。另外,当发送和接收单元31接收的信号中没有发生误差时,误差检测单元32促使发送和接收单元31向主设备12发送ACK,通知主设备12已经成功接收到由信号中继的信息,例如,命令或数据。另一方面,当由发送和接收单元31接收的信号中发生误差时,误差检测单元32促使发送和接收单元31向主设备12发送NACK,通知主设备12未接收由该信号中继的信息,例如,命令或数据。

[0049] 此外,当由发送和接收单元31接收的信号中发生误差,并且正常通信不可用时,例如,误差检测单元32促使从设备13忽略所有后续通信,停止对主设备12的响应,并且进入待机状态。

[0050] 在如上配置的总线IF 11中,主设备12和从设备13能够经由数据信号线14-1和时钟信号线14-2发送和接收信号,并且能够通过避免与冲突避免单元24发生冲突,更可靠地通信。

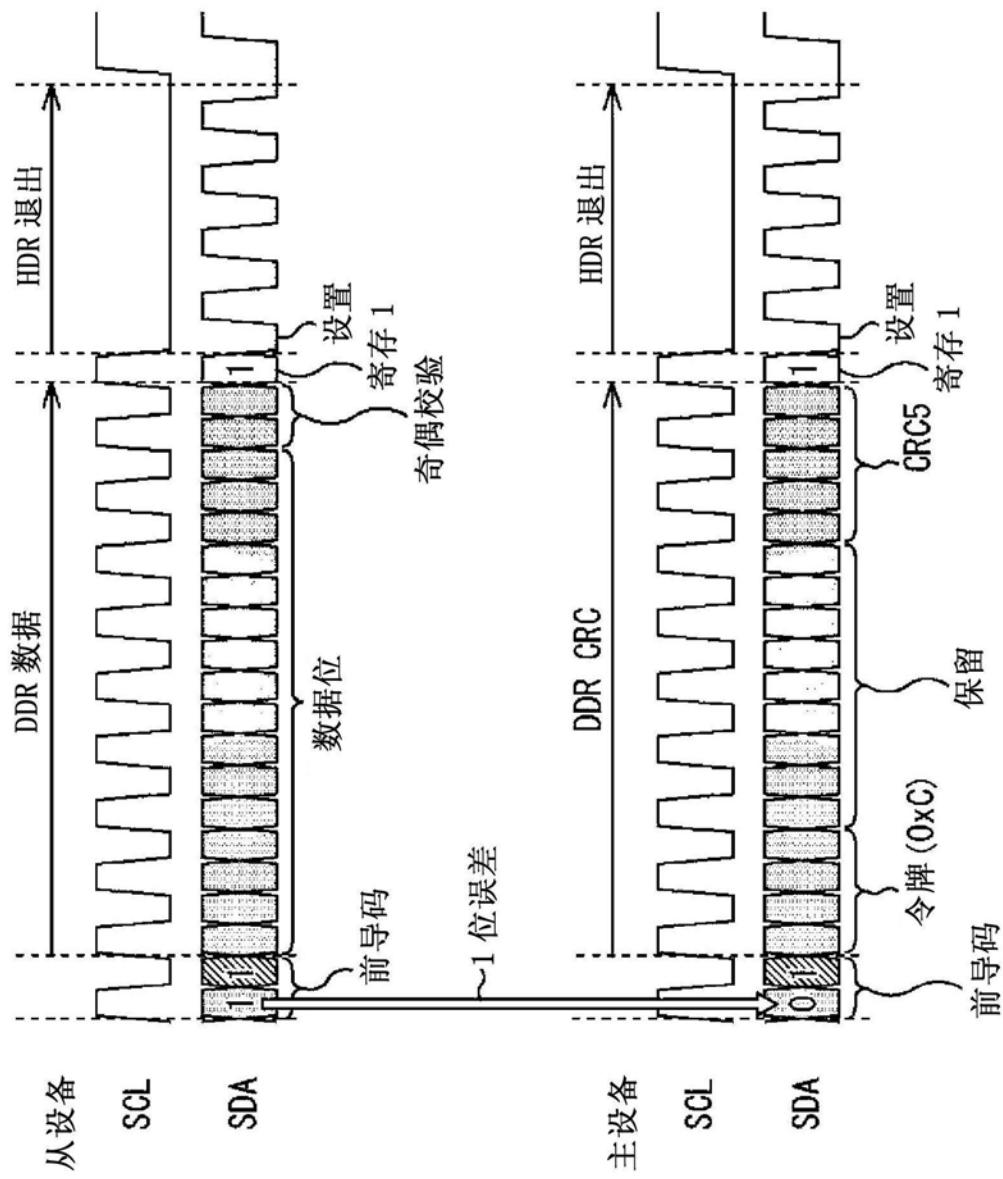

[0051] <冲突发生的解释>

[0052] 此时,在描述避免与冲突避免单元24发生冲突的技术之前,将参考图2描述冲突的发生。

[0053] 在总线IF 11中,规定当处于DDR模式时,称为前导码的2位信号用于指定接下来要发送的数据类型。然而,由于奇偶校验或CRC的误差检测对于前导码不可用,因此如果前导码中发生误差,则可能不会检测到误差。

[0054] 例如,在从设备13根据读取命令(具有从主设备12读出数据的指令)发送读取数据之后的前导码中,规定第一位由从设备13驱动,而第二位保持在H电平(高保持器)。此外,利用第一位,从设备13能够通知主设备12接下来将发送CRC字或读取数据中的一个。例如,在继前导码之后发送CRC字的情况下,规定在发送读取数据之后的前导码的第一位被驱动为0。另一方面,在发送继前导码之后的读取数据的情况下,规定在发送读取数据之后的前导码的第一位被驱动为1。

[0055] 然而,例如,如果在该前导码的第一位中发生1位误差并且该位的值被反转,则在下一次发送的读取数据和下一次发送的CRC字之间主设备12会误识别。

[0056] 换言之,如图2的上部所示,在发送读取数据的情况下,从设备13将前导码的第一位驱动为1,并且发送继前导码之后的读取数据(DDR数据)。注意,在图2中,应用灰色阴影线的部分表示由从设备13驱动的部分,而应用斜纹阴影线的部分表示保持在H电平的部分。

[0057] 相反,在前导码的第一位发生1位误差,并且前导码的第一位变为0的情况下,如图2的下部所示,主设备12误认为将从从设备13发送CRC字(DDR CRC)。因此,在这种情况下,主设备12在接收到对应于CRC字(令牌(0xC)、CRC5和Prepare=Setup)的10位之后,发送HDR退出命令(HDR退出),该命令具有在HDR模式中结束通信的指令。

[0058] 结果,存在从从设备13发送的读取数据和从主设备12发送的HDR退出命令可能冲突的风险。因此,此后,可以想象,即使主设备12已经发送了HDR退出命令,从设备13也不能正常接收HDR退出命令,因此,不能退出HDR模式,并且总线IF 11死锁,导致通信不可用的状态。

[0059] 因此,在总线IF 11中,如果主设备12已经接收到指定发送CRC字的前导码,但是在继前导码之后所接收到的信号与CRC字不匹配(即,如果发生令牌误差或CRC误差),则推断在前导码中已经发生1位误差。另外,在这种情况下,规定主设备12在发送继CRC字之后的特定数量位的额外时钟之后,发送中止信号,该中止信号给出中途终止通信的指令。结果,即使发生了如上所述的1位误差,也可以避免在从从设备13发送的读取数据和从主设备12发送的HDR退出命令之间发生冲突。

[0060] <冲突避免的解释>

[0061] 图3示出了一种格式,其中,在总线IF 11中,主设备12添加用于防止冲突的时钟,以避免由于在发送读取数据之后在前导码的第一位中发生1位误差而导致的冲突。

[0062] 如图3所示,在总线IF 11中,如果主设备12推断在从从设备13发送继读取数据(DDR数据)之后的前导码中发生误差,则规定主设备12发送与CRC字和读取数据之间的差值对应的9位额外时钟。另外,忽略在额外时钟发送期间接收的数据。

[0063] 换言之,如参考图2所描述的,假设在继读取数据之后的前导码的第一位中发生1位误差,并且即使从设备13发送读取数据,主设备12也误认为要发送CRC字。在这种情况下,主设备12检测到对应于CRC字的9位中发生令牌误差或CRC误差,并且能够推断这些误差是由于前导码中发生1位误差。

[0064] 此时,在总线IF 11中,规定从设备13接收读取命令(READ CMD),并发送继随后的

前导码之后的18位读取数据(DDR数据)。此外,在总线IF 11中,规定在从设备13发送读取数据之后的前导码中,第一位由从设备13驱动,而第二位由主设备12驱动。另外,在总线IF 11中,前导码的第二位是0的情况被规定为中止信号,该中止信号从主设备12向从设备13发出执行主设备中途终止通信的中止指令。注意,为了可靠地执行主设备中止,主设备12连续驱动读取数据之后发送和接收的前导码的第二位。

[0065] 因此,如图3所示,当继额外时钟之后的前导码的第二位被驱动为0时,从设备13检测到已经从主设备12发送了中止信号,并且能够中止发送读取数据。结果,如果主设备12发送继前导码之后的HDR退出命令(HDR退出),则从设备13能够根据HDR退出命令退出HDR模式。此后,主设备12和从设备13从SDR模式重新开始通信。

[0066] 换言之,在检测令牌误差或CRC误差的情况下,主设备12推断前导码误差。随后,如图2所示,主设备12不在发送CRC字之后立即发送HDR退出命令,而是如图3所示,在CRC字之后发送额外时钟,在额外时钟之后发送前导码,然后发送HDR退出命令。

[0067] 结果,即使主设备12在接收到读取数据之后检测到前导码中的第一位是0,主设备12也能够避免发生冲突,如参考图2所描述的。换言之,即使从设备13发送读取数据的前导码被误认为是主设备12发送CRC字的前导码,也可以避免总线IF 11死锁,并且更可靠地进行通信。

[0068] <避免冲突发生的通信方法>

[0069] 图4是说明在作为一个HDR模式的DDR模式中主设备12从从设备13读出数据的通信处理(DDR读取)的流程图。

[0070] 在步骤S11中,主设备12进行将通信从SDR模式切换到HDR模式的处理。具体地,在主设备12中,发送和接收单元21驱动数据信号线14-1和时钟信号线14-2,并且在SDR模式中,发送广播命令(0x7E+R/W=0),指示命令将立刻发送到构成总线IF 11的所有从设备13。此后,在主设备12中,当确认信号检测单元23接收到从每个从设备13发送的ACK,以确认已经成功接收广播命令时,发送和接收单元21发送用于进入HDR模式的公共命令代码(ENTHDR CCC(0x20))。

[0071] 在步骤S12中,主设备12的发送和接收单元21驱动数据信号线14-1和时钟信号线14-2,以发送读取命令。

[0072] 在步骤S13中,发送和接收单元21响应于在步骤S12中发送的读取命令,接收从从设备13发送的读取数据,此外,还接收继读取数据之后发送的前导码。

[0073] 在步骤S14中,发送和接收单元21确定在步骤S13中接收的前导码指定了发送读取数据还是CRC字。

[0074] 在步骤S14中,如果发送和接收单元21确定前导码指定发送读取数据,则处理返回到步骤S13,此后,重复类似的处理。另一方面,在步骤S14中,如果发送和接收单元21确定前导码指定发送CRC字,则处理进入步骤S15。

[0075] 在步骤S15中,发送和接收单元21接收在步骤S13中接收的继前导码之后发送的信号,并且误差检测单元22确定是否在信号中发生误差。

[0076] 在步骤S15中,如果误差检测单元22确定继指定发送CRC字的前导码之后发送的信号中发生误差,则处理进入步骤S16。换言之,在这种情况下,如果误差检测单元22检测到令牌误差或CRC误差,则冲突避免单元24推断在前导码中已经发生了误差。

[0077] 在步骤S16中,误差检测单元22发送参考图3描述的额外时钟,之后,指示发送和接收单元21发送中止信号,该中止信号给出中途终止通信的指令。相应地,发送和接收单元21在发送额外时钟之后向从设备13发送中止信号。

[0078] 在步骤S16的处理之后,发送和接收单元21发送继额外时钟之后的HDR退出命令。此外,即使在步骤S15中确定没有发生误差的情况下,在步骤S17中,发送和接收单元21发送HDR退出命令。因此,主设备12在DDR模式下从从设备13读出数据的通信过程(DDR读出)结束。

[0079] 如上所述,在总线IF 11中,即使在给出发送从设备13发送的读取数据的指令的前导码中发生1位误差,也可以避免发生冲突,并且更可靠地进行通信。

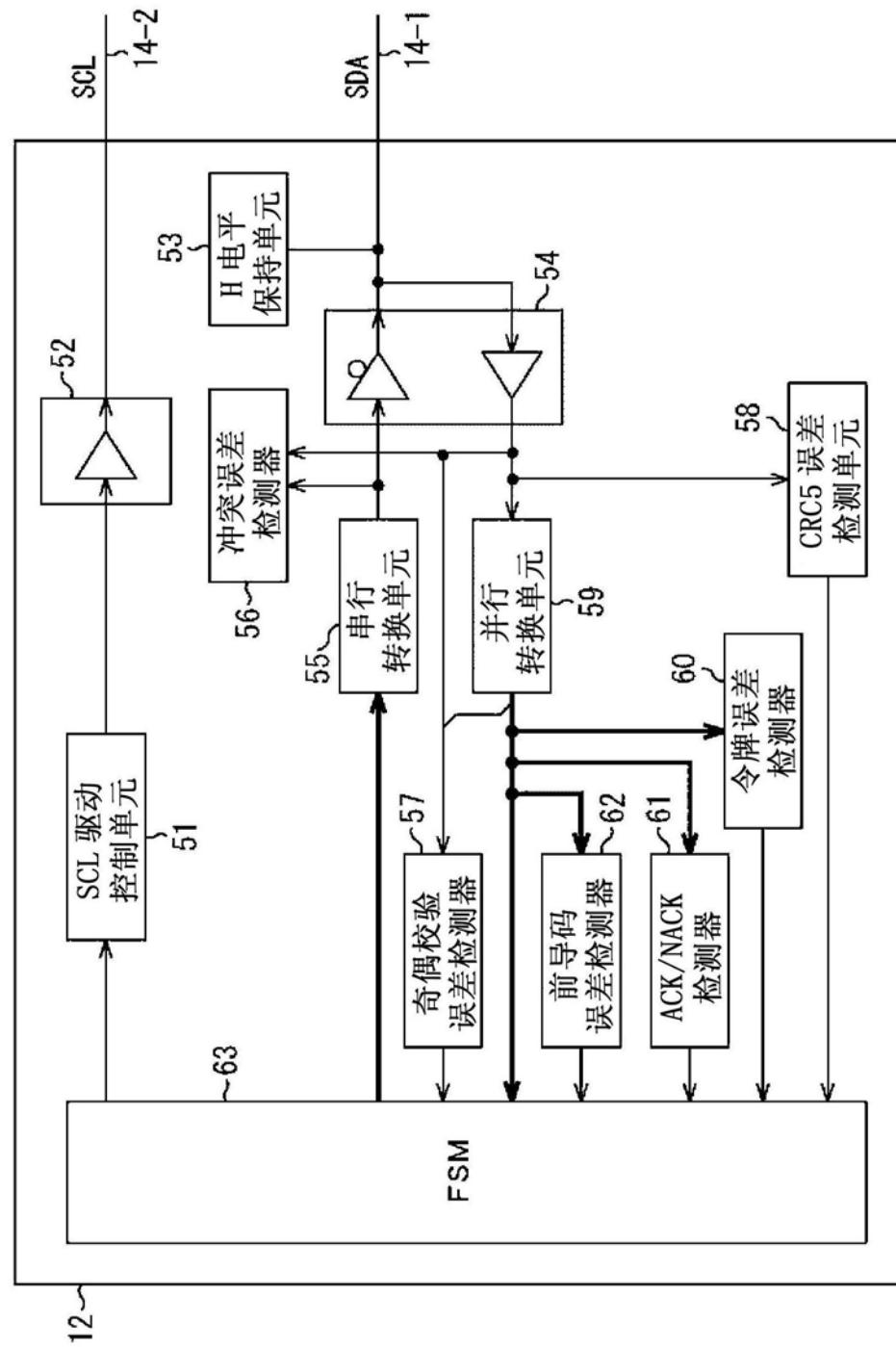

[0080] <主设备的电路图>

[0081] 接下来,图5是示出主设备12的示例配置的电路图。

[0082] 如图5所示,主设备12具有SCL驱动控制单元51、放大单元52、H电平保持单元53、放大单元54、串行转换单元55、冲突误差检测器56、奇偶校验误差检测器57、CRC5误差检测单元58、并行转换单元59、令牌误差检测器60、ACK/NACK检测器61、前导码误差检测器62和有限状态机(FSM)63。

[0083] SCL驱动控制单元51在具有用作从状态机63输出的参考的频率的信号之后,生成串行时钟,以经由时钟信号线14-2提供给从设备13,并控制驱动时钟信号线14-2。

[0084] 放大单元52将由SCL驱动控制单元51生成的时钟信号放大到经由时钟信号线14-2发送所需的特定电平,并输出到时钟信号线14-2。

[0085] H电平保持单元53将数据信号线14-1的电平保持在H电平。

[0086] 放大单元54将经由数据信号线14-1发送的串行数据放大到特定电平并输出,并将经由数据信号线14-1发送的串行数据放大到在主设备12内部处理所需的电平。

[0087] 串行转换单元55转换并输出从状态机63输出的并行数据,作为串行数据。

[0088] 冲突误差检测器56将从串行转换单元55输出的串行数据与经由数据信号线14-1发送的串行数据进行比较,从而检测数据信号线14-1上的冲突误差。

[0089] 奇偶校验误差检测器57使用添加的奇偶校验位来检测基于奇数或偶数的位误差,检测经由数据信号线14-1发送的串行数据中的误差,并将误差检测结果报告给状态机63。

[0090] CRC5误差检测单元58对应于图1中的误差检测单元22,并且通过使用添加的5位数据来检测基于CRC的位误差,检测经由数据信号线14-1发送的串行数据中的误差,并且将误差检测结果报告给状态机63。

[0091] 并行转换单元59转换并输出经由数据信号线14-1发送的串行数据,作为并行数据。

[0092] 令牌误差检测器60对应于图1中的误差检测单元22,并且通过检查由并行转换单元59转换的并行数据中包括的令牌的位序列,检测令牌中是否发生误差,并且将误差检测结果报告给状态机63。

[0093] ACK/NACK检测器61对应于图1中的确认信号检测单元23,从由并行转换单元59转换的并行数据中检测从从设备13发送的ACK或NACK,并将检测结果(ACK/NACK)报告给状态机63。

[0094] 前导码误差检测器62检测在由并行转换单元59转换的并行数据中包括的前导码

中是否发生误差，并将误差检测结果报告给状态机63。

[0095] 状态机63是顺序电路，根据输入条件和当前状态来确定其下一状态，并且例如用作图1中的发送和接收单元21和冲突避免单元24。换言之，状态机63将来自CRC5误差检测单元58和令牌误差检测器60的误差检测结果作为输入，并且如果没有发生令牌误差或CRC误差，则进入正常结束HDR模式的状态。另一方面，如果已经发生令牌误差和CRC误差，则状态机63继CRC字之后发送额外时钟，并且进入发送具有后续前导码的第二位的中止信号的状态。

[0096] 以这种方式配置主设备12，并且如上所述，即使给出发送从从设备13发送的读取数据的指令的前导码被误认为是用于发送CRC字的前导码，也可以避免总线IF 11死锁，并且更可靠地进行通信。

[0097] 然而，在总线IF 11中，当CRC字中的位数被规定为9位（4位令牌和5位CRC5）时，与读取数据中的位数（18位）不同，如前所述，发生冲突。因此，例如，当规定CRC字中的位数变得与读取数据中的位数相同的18位的格式时，可以避免发生冲突。

[0098] 换言之，如图6所示，通过采用在令牌（令牌（0xC））和CRC5之间插入了9个保留位的格式，作为CRC字的格式，来进行字对齐。因此，不再需要发送额外时钟。保留位的数量对应于令牌和CRC5中的位数（9位）与读取数据中的位数（18位）之间的差值。此外，即使在以这种格式使用CRC字的情况下，如果主设备12在接收到具有位序列0和1的前导码之后检测到令牌误差、CRC误差和接收到特定长度或更短的CRC字中的任何一个，则为了安全地停止从设备13，主设备12随后能够结束通信，类似于正常的主设备中止。

[0099] 此外，如图6所示，通过根据紧接在接收CRC字之后的位驱动数据信号线14-1从从设备13切换到主设备12，可以在早期安全地结束通信。

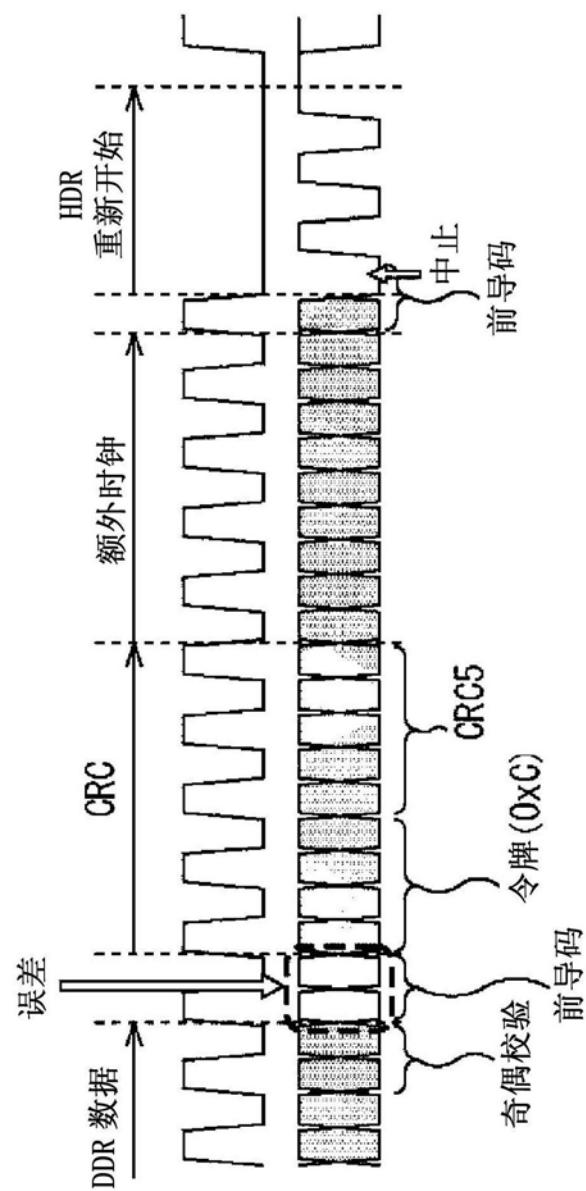

[0100] 注意，尽管上面参考图3描述的实施例描述了在发送额外时钟之后主设备12发送继前导码之后的HDR退出命令的示例，但是该配置不限于HDR退出命令的发送，只要可以避免冲突并且可以恢复通信即可。

[0101] 例如，如图7所示，在发送额外时钟之后继前导码之后，主设备12可以发送HDR重新开始命令（HDR Restart），给出在HDR模式中重新开始通信的指令，而代替图3中的HDR退出命令。以这种方式，在总线IF 11中，在根据主设备中止中途终止通信之后，可以用HDR重新开始命令恢复通信。

[0102] 注意，例如，冲突避免单元24还可以推断出如果发送和接收单元21接收CRC字而不是接收特定长度的读取数据，则发生了误差，并且如前所述，指示发送和接收单元21在发送额外时钟之后发送中止信号。

[0103] 注意，本技术不限于符合I3C标准的总线IF 11，也可以应用于符合另一标准的总线IF 11。此外，在图1所示的总线IF 11中，示出了一个示例配置，其中，从设备13-1至13-3连接，但是也可以具有例如一个或两个从设备13或者三个或更多从设备13。

[0104] 应当理解，参考前面描述的流程图描述的操作不限于按照流程图中描述的顺序在时间序列中处理，而是也可以并行或单独处理（例如，通过并行处理或面向对象的处理）。此外，虽然程序可以由单个CPU处理，但是程序也可以由多个CPU以分布式方式处理。

[0105] 此外，在本说明书中，术语“系统”表示由多个设备组成的设备的整体。

[0106] 此外，上述一系列操作可以在硬件中执行，也可以在软件中执行。在以软件执行一

系列操作的情况下,可以将构成这种软件的程序从存储该程序的程序记录介质中安装到内置于专用硬件中的计算机上,或者可替代地,安装到能够通过在其上安装各种程序来执行各种功能的计算机上,例如,通用个人计算机。

[0107] <示例硬件配置>

[0108] 图8是示出根据程序执行前述一系列处理的计算机的示例性硬件配置的方框图。

[0109] 在计算机中,中央处理单元(CPU)101、只读存储器(ROM)102、随机存取存储器(RAM)103和电子可擦除可编程只读存储器 EEPROM 104通过总线105彼此连接。总线105还与输入/输出接口106连接,并且输入/输出接口106连接到外部设备(例如,图1中的数据信号线14-1和时钟信号线14-2)。

[0110] 在如上配置的计算机中,例如,由于CPU 101经由总线105将存储在ROM 102或EEPROM 104中的程序加载到RAM 103中并执行该程序,所以执行上述一系列处理。此外,除了预先写入ROM 102之外,由计算机(CPU 101)执行的程序还可以经由输入/输出接口106从外部源在EEPROM 104中安装和更新。

[0111] 另外,本技术也可以配置如下。

[0112] (1)一种通信装置,包括:

[0113] 发送和接收单元,其与另一通信装置发送和接收信号;

[0114] 误差检测单元,其通过使所述发送和接收单元接收指定接下来要发送的数据类型的前导码,并将在继前导码之后接收的信号的位序列与针对由前导码指定用于该发送的类型发送的位序列进行比较,来检测发生误差;以及

[0115] 冲突避免单元,如果误差检测单元检测到发生误差,则所述冲突避免单元指示所述发送和接收单元发送与继前导码之后的特定位数对应的时钟,然后,发送中止信号,该中止信号给出中途终止通信的指令。

[0116] (2)根据(1)所述的通信装置,其中,

[0117] 如果由所述发送和接收单元接收的前导码指定发送包括令牌和CRC5的循环冗余校验(CRC)字,但是所述误差检测单元基于在继前导码之后接收的信号中的位序列,检测到令牌误差或CRC误差,

[0118] 则在继前导码之后发送根据CRC字中的位数的时钟以及与在CRC字中的位数和从另一通信装置读出的读取数据中的位数之间的差值对应的额外时钟之后,所述冲突避免单元使发送中止信号。

[0119] (3)根据(2)所述的通信装置,其中,

[0120] 所述冲突避免单元忽略所述发送和接收单元在发送额外时钟期间接收的信号。

[0121] (4)根据(3)所述的通信装置,其中,

[0122] 当从另一通信装置发送读取数据时,所述发送和接收单元依继读取数据之后发送和接收的2位前导码的第二位的时序发送中止信号。

[0123] (5)根据(2)所述的通信装置,其中,

[0124] 如果由所述发送和接收单元接收的前导码指定发送包括令牌和CRC5的循环冗余校验(CRC)字,但是所述误差检测单元基于在继前导码之后接收的信号中的位序列,检测到令牌误差或CRC误差,

[0125] 则所述冲突避免单元使在发送时钟之后发送中止信号,该时钟具有与CRC字对应

的位数以及当从另一通信装置读出数据时的位数,在该CRC字中,使用由令牌、CRC5以及与令牌和CRC5之间的差值对应的保留位数组成的格式。

[0126] (6) 根据(1)至(5)中任一项所述的通信装置,其中,

[0127] 所述发送和接收单元在中止信号之后发送命令,该命令给出退出特定通信模式的指令。

[0128] (7) 根据(1)至(5)中任一项所述的通信装置,其中,

[0129] 所述发送和接收单元在中止信号之后发送命令,该命令给出在特定通信模式中重新开始通信的指令。

[0130] (8) 根据(1)至(7)中任一项所述的通信装置,还包括:

[0131] 确认信号检测单元,其检测从已经接收到从所述发送和接收单元发送的信号的另一通信装置发送的确认信号或否认信号,其中,

[0132] 当所述确认信号检测单元检测到否认信号时,所述冲突避免单元指示所述发送和接收单元在忽略继否认信号之后的特定数量的位之后发送中止信号。

[0133] (9) 根据(1)至(8)中任一项所述的通信装置,其中,

[0134] 所述发送和接收单元接收从另一通信装置读出的读取数据,并且连续驱动在读取数据之后发送和接收的前导码的第二位。

[0135] (10) 根据(1)至(9)中任一项所述的通信装置,其中,

[0136] 所述发送和接收单元自紧接在接收由驱动数据信号线的另一通信装置发送的循环冗余校验(CRC)字之后的一位驱动数据信号线。

[0137] (11) 根据(1)至(10)中任一项所述的通信装置,其中,

[0138] 在数据中包括的两个奇偶校验位之间,所述误差检测单元将一个奇偶校验位视为偶数奇偶校验,并且另一奇偶校验位视为奇数奇偶校验,并通过对所述发送和接收单元接收的数据进行奇偶校验,来检测发生误差。

[0139] (12) 根据(1)至(11)中任一项所述的通信装置,其中,

[0140] 所述发送和接收单元能够在以标准传输速率进行数据通信的标准数据速率(SDR)模式下并且在以比SDR模式更高的传输速率进行数据通信的高数据速率(HDR)模式下,发送和接收信号,

[0141] (13) 根据(1)至(12)中任一项所述的通信装置,其中,

[0142] 所述发送和接收单元经由两条信号线进行通信,即,一次一位地依次发送串行数据的数据信号线以及发送特定频率的串行时钟的时钟信号线。

[0143] (14) 根据(1)至(13)中任一项所述的通信装置,其中,

[0144] 所述发送和接收单元按照改进的内部集成电路(I3C)标准进行通信。

[0145] (15) 一种通信方法,包括:

[0146] 与另一通信装置发送和接收信号;

[0147] 通过接收指定接下来要发送的数据类型的前导码,并将在继前导码之后接收的信号的位序列与针对由前导码指定发送的类型而应该发送的位序列进行比较,来检测发生误差;并且

[0148] 如果检测到发生误差,则发送与继前导码之后的特定位数对应的时钟,然后,发送中止信号,该中止信号给出中途终止通信的指令。

- [0149] (16) 一种用于使计算机执行通信过程的程序,包括:

- [0150] 与另一通信装置发送和接收信号;

- [0151] 通过接收指定接下来要发送的数据类型的前导码,并将在继前导码之后接收的信号的位序列与针对由前导码指定发送的类型而应该发送的位序列进行比较,来检测发生误差;并且

- [0152] 如果检测到发生误差,则发送与继前导码之后的特定位数对应的时钟,然后,发送中止信号,该中止信号给出中途终止通信的指令。

- [0153] (17) 一种系统,包括:

- [0154] 第一通信装置,其在总线中具有控制主动权;以及

- [0155] 第二通信装置,其根据所述第一通信装置的控制进行通信,其中,

- [0156] 所述第一通信装置包括

- [0157] 发送和接收单元,其与另一通信装置发送和接收信号;

- [0158] 误差检测单元,其通过使所述发送和接收单元接收指定接下来要发送的数据类型的前导码,并将在继前导码之后接收的信号的位序列与针对由前导码指定发送的类型而应该发送的位序列进行比较,来检测发生误差;以及

- [0159] 冲突避免单元,如果误差检测单元检测到发生误差,则所述冲突避免单元指示所述发送和接收单元发送与继前导码之后的特定位数对应的时钟,然后,发送中止信号,该中止信号给出中途终止通信的指令。

- [0160] 注意,本实施例不限于上述实施例,并且在不脱离本公开的要旨的范围内,各种修改是可能的。

- [0161] 附图标记列表

- [0162] 11 总线IF

- [0163] 12 主设备

- [0164] 13 从设备

- [0165] 14-1 数据信号线

- [0166] 14-2 时钟信号线

- [0167] 21 发送和接收单元

- [0168] 22 误差检测单元

- [0169] 23 确认信号检测单元

- [0170] 24 冲突避免单元

- [0171] 31 发送和接收单元

- [0172] 32 误差检测单元

- [0173] 51 SCL驱动控制单元

- [0174] 52 放大单元

- [0175] 53 H电平保持单元

- [0176] 54 放大单元

- [0177] 55 串行转换单元

- [0178] 56 冲突误差检测器

- [0179] 57 奇偶校验误差检测器

- [0180] 58 CRC5误差检测单元

- [0181] 59 并联转换单元

- [0182] 60 令牌误差检测器

- [0183] 61 ACK/NACK检测器

- [0184] 62 前导码误差检测器

- [0185] 63 状态机

图1

图2

图3

图4

图5

图6

图7

图8