(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3793073号

(P3793073)

(45) 発行日 平成18年7月5日(2006.7.5)

(24) 登録日 平成18年4月14日(2006.4.14)

(51) Int.C1.

F 1

|             |             |                  |      |      |      |

|-------------|-------------|------------------|------|------|------|

| <b>G09G</b> | <b>3/22</b> | <b>(2006.01)</b> | G09G | 3/22 | H    |

| <b>G09G</b> | <b>3/20</b> | <b>(2006.01)</b> | G09G | 3/20 | 641A |

|             |             |                  | G09G | 3/20 | 641P |

|             |             |                  | G09G | 3/20 | 642C |

|             |             |                  | G09G | 3/20 | 641E |

請求項の数 5 (全 17 頁)

(21) 出願番号 特願2001-349056 (P2001-349056)

(22) 出願日 平成13年11月14日 (2001.11.14)

(65) 公開番号 特開2002-221933 (P2002-221933A)

(43) 公開日 平成14年8月9日 (2002.8.9)

審査請求日 平成15年9月25日 (2003.9.25)

(31) 優先権主張番号 特願2000-354835 (P2000-354835)

(32) 優先日 平成12年11月21日 (2000.11.21)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100086287

弁理士 伊東 哲也

(72) 発明者 山崎 達郎

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 森 真起子

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 嵐野 治

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上にマトリクス状に配置された複数の行配線及び列配線を介して駆動される画像形成素子と、該複数の列配線に輝度データに対応するパルス幅の電圧パルスを印加する列配線駆動部と、該複数の行配線を順次選択し走査する行配線駆動部とを備える表示装置であつて、前記行配線の抵抗と選択された前記行配線に流れる電流によって生じる電圧降下量を、

前記複数の列配線をその総数よりも少數のブロックに分けて、列配線ブロック単位にて算出する電圧降下量算出手段を有し、

前記電圧降下量に基づいて前記輝度データを補正することを特徴とする表示装置。

10

## 【請求項 2】

基板上にマトリクス状に配置された複数の行配線及び列配線を介して駆動される画像形成素子と、該複数の列配線に輝度データに対応するパルス幅の電圧パルスを印加する列配線駆動部と、該複数の行配線を順次選択し走査する行配線駆動部とを備える表示装置であつて、前記行配線の抵抗と選択された前記行配線に流れる電流によって生じる電圧降下量を、前記複数の列配線をその総数よりも少數のブロックに分けて、列配線ブロック単位にて算出する電圧降下量算出手段と、

前記電圧降下量より補正值データを算出する手段と、

該補正值データにより前記列配線駆動部の出力電圧を可変とする手段とを備えることを特徴とする表示装置。

20

**【請求項 3】**

前記電圧降下量算出手段は、1水平走査期間を複数の期間に分割し、分割した各期間毎に電圧降下量を算出する請求項1または2記載の表示装置。

**【請求項 4】**

前記列配線駆動部は各列配線毎に出力回路を備え、各出力回路がそれぞれ異なる出力電位を有する複数の電圧供給部のいずれか一つを選択し、その選択された電圧供給部の電位により該列配線に印加される電圧パルスの波高値が決定されることを特徴とする請求項2に記載の表示装置。

**【請求項 5】**

前記画像形成素子が表面伝導型電子放出素子であることを特徴とする請求項1～4のいずれか1つに記載の表示装置。 10

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明はマトリクス配線された複数の電子放出素子やEL素子等の画像形成素子を備えた表示装置及びその駆動方法に関するものであり、特に、冷陰極電子放出素子とその電子線照射を受けて発光する蛍光面からなる表示パネルとを用いて、テレビジョン信号やコンピュータなどからの表示信号を受信し、画像表示させるテレビジョン受信機やディスプレイ装置等の表示装置において、前記表示パネルのマトリクス配線などが有する電気抵抗分に起因する冷陰極素子駆動量の減少分を補償し駆動するための、信号処理部に適するものである。 20

**【0002】****【従来の技術】**

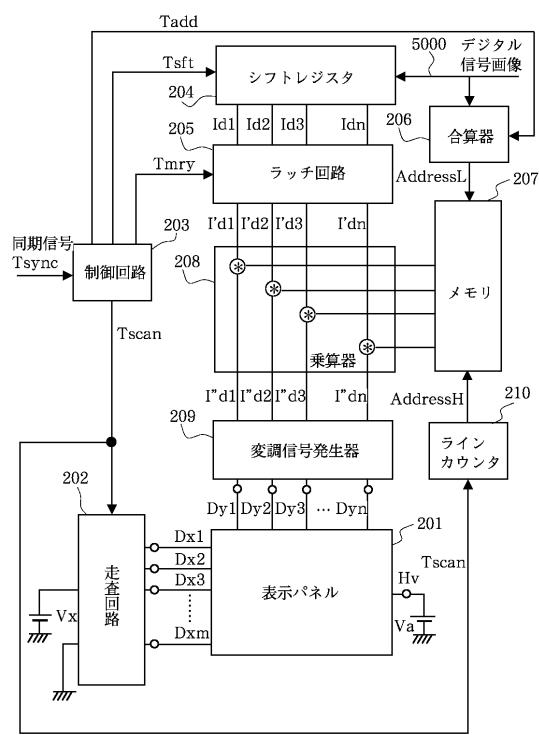

従来の表示装置としては、例えば、特開平8-248920号公報において、電子放出素子への電気的な接続配線などの電気抵抗分に起因する素子駆動電圧の減少によって生じる輝度低下を補償するような補正を行う場合について、統計演算によりその補正量を算出し、電子線要求値と補正值を合成する構成が開示されている。

**【0003】**

その特開平8-248920号公報中の第1実施例として説明されている表示装置の構成図を図17に示す。詳細な説明は該公報に書かれているので省略するが、図17に示されるように補正を行うために、各列配線毎に備えられる乗算器208にて輝度データとメモリ手段207からの補正データを乗算し、変調信号発生器209に補正後データを転送する構成が提案されている。 30

**【0004】****【発明が解決しようとする課題】**

しかしながら、上記従来の構成においては、各列配線毎の乗算器や補正データを出力するためのメモリ手段、及びメモリ手段にアドレス信号を与えるための合算器など大規模なハードウェアが必要であった。

**【0005】**

本発明は、電気的接続配線等の電気抵抗分による素子駆動電圧の減少に起因する輝度低下を補償するような補正が、従来例に係る表示装置よりも少ないハードウェアで実現出来る表示装置を提供することを目的とする。 40

**【0006】****【課題を解決するための手段】**

上記目的を達成するため、本発明の第1の表示装置は、基板上にマトリクス状に配置された複数の行配線及び列配線を介して駆動される画像形成素子と、該複数の列配線に輝度データに対応するパルス幅の電圧パルスを印加する列配線駆動部と、該複数の行配線を順次選択し走査する行配線駆動部とを備える表示装置であって、前記行配線の抵抗と選択された前記行配線に流れる電流によって生じる電圧降下量を、

前記複数の列配線をその総数よりも少数のブロックに分けて、列配線ブロック単位にて

50

算出する電圧降下量算出手段を有し、

前記電圧降下量に基づいて前記輝度データを補正することを特徴とする。

**【0007】**

本発明の第2の表示装置は、基板上にマトリクス状に配置された複数の行配線及び列配線を介して駆動される画像形成素子と、該複数の列配線に輝度データに対応するパルス幅の電圧パルスを印加する列配線駆動部と、該複数の行配線を順次選択し走査する行配線駆動部とを備える表示装置であって、前記行配線の抵抗と選択された前記行配線に流れる電流によって生じる電圧降下量を、

前記複数の列配線をその総数よりも少數のブロックに分けて、列配線ブロック単位にて算出する電圧降下量算出手段と、

10

前記電圧降下量より補正值データを算出する手段と、

該補正值データにより前記列配線駆動部の出力電圧を可変とする手段とを備えることを特徴とする。

本発明の第3の表示装置は、前記電圧降下量算出手段は、1水平走査期間を複数の期間に分割し、分割した各期間毎に電圧降下量を算出する。

**【0008】**

本発明の第4の表示装置は、前記列配線駆動部は各列配線毎に出力回路を備え、各出力回路がそれぞれ異なる出力電位を有する複数の電圧供給部のいずれか一つを選択し、その選択された電圧供給部の電位により該列配線に印加される電圧パルスの波高値が決定される。

20

本発明の第5の表示装置は、前記画像形成素子が表面伝導型電子放出素子である。

**【0010】****【発明の実施の形態】****[第1の実施形態]**

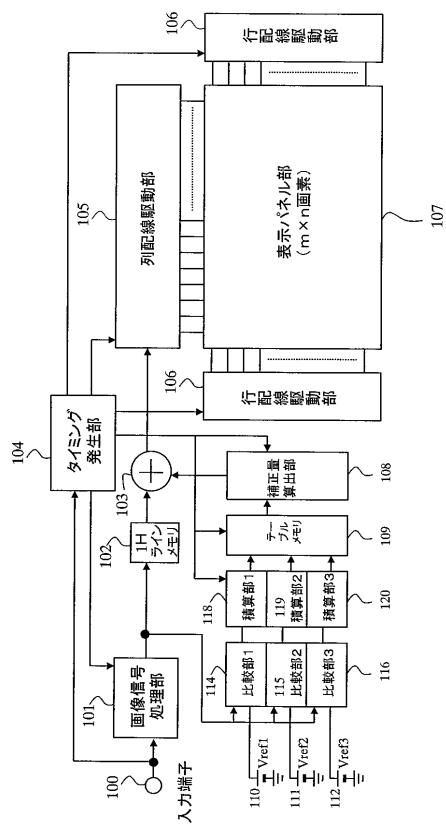

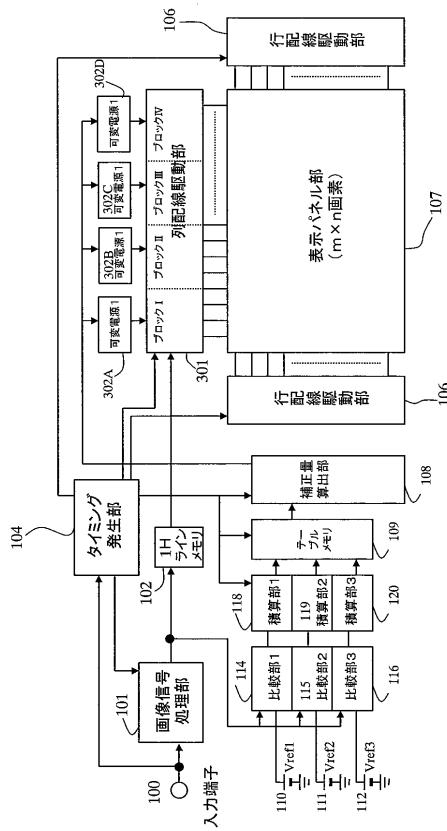

図1は本発明の第1の実施形態に係る表示装置を示す構成図である。この図において、表示パネル部107は、電子放出素子である表面伝導型電子放出素子(以下SCEと略記する)を(m×n)マトリクス状に配線したマルチ電子源と、その電子源から電子線照射を受け発光する受光面としての蛍光面とを備えて構成されている。不図示ではあるが、放出された電子線を加速するための高電圧バイアスが該蛍光面に印加される。表示パネル部107の製法については、特開平8-248920号公報において詳細に記述されているので、ここではその説明を省略する。

30

**【0011】**

特開平8-248920号公報にて詳細に記述されているように、SCEを用いた表示パネルの発光輝度階調制御方法は、いくつか考えられるが、本実施形態においては、列配線駆動部105が、入力される輝度データ即ち電子線放出量要求値データに比例したパルス幅を有する電圧パルスを列配線に印加し、行配線駆動部106が、発光させるラインに選択電圧パルスを印加し、順次選択する行を走査していくことにより、画像表示を行うことを前提とする場合を例として、以下の説明を行うものとする。このようなSCEのON時間が電子線放出量要求値データに比例する方式においては、表示パネルの蛍光面が電子照射を受ける時間は、電子線放出量要求値データに比例するために、結果として発光輝度も電子線放出量要求値データにほぼ比例する。

40

**【0012】**

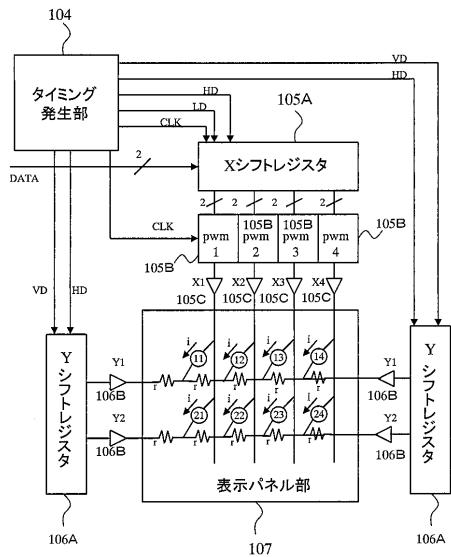

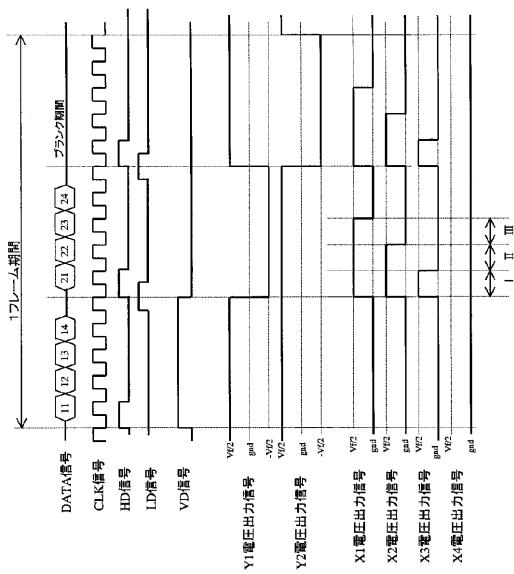

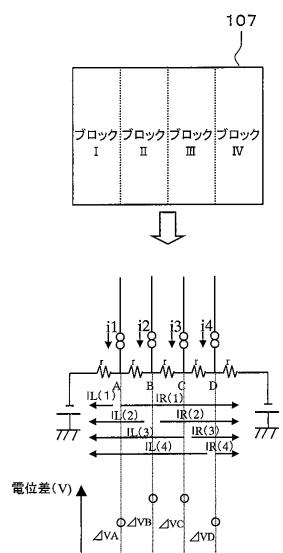

簡単な一例として、図3で示すように、本実施形態に係る表示パネル部107は、4本の列配線と2本の行配線で8個のSCE11~14, 21~24をマトリクス配線しており、階調数2ビットで表示する場合を考える。図5は図3における各部の動作タイミングを示したタイムチャートである。

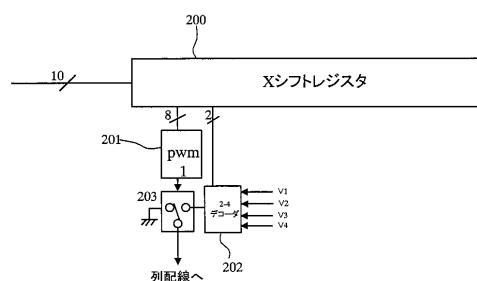

**【0013】**

図1における列配線駆動部105は、図3においては、Xシフトレジスタ105Aと、各列配線毎に備えられるパルス幅変調器105Bと、列配線駆動出力部105Cとからなる。

50

## 【0014】

Xシフトレジスタ105Aの入力データ信号は、輝度データであり、マトリクス配線された各SCEの電子線放出量要求値である。この信号は、図5のDATA信号として示されているように、行毎に点順次に送られてくる。この場合、 $2 \times 4$ マトリクス素子なので、1水平期間に1行分4個の各SCEの電子線放出量要求値を転送する。1フレームは3水平期間からなり、2水平期間をデータ転送のために備え、1水平期間をブランク期間として設けている。

## 【0015】

Xシフトレジスタ105Aは、2ビットレジスタが4段直列に接続されており、入力データをタイミング発生部104から送られてくるCLK(クロック)信号により順次読み込む。また水平期間毎に発生するLD信号によりXシフトレジスタ105Aに読み込んだデータは、パルス幅変調器pwm105Bに転送される。パルス幅変調器105Bは転送されたデータに比例したパルス幅を有する電圧信号を発生する。例えばパルス幅変調器105Bは、データラッチ手段と、カウンタ手段及びフリップフロップ手段から構成され、HD信号でフリップフロップがセットされるとともに、カウンタがスタートし、ラッチが保持するデータ数のカウント終了トリガでフリップフロップがリセットされ、このフリップフロップの出力がパルス幅信号として利用される。列配線駆動出力部105Cはパルス幅変調器105Bの出力電圧信号を所望の振幅レベルになるように増幅して列配線に印加する。この例において、各SCEの選択電位はVfであり、列配線駆動出力部105Cは接地レベルからVf/2の電位差を有する電圧信号を発生する。図5のX1～X4電圧出力信号に電子線放出量要求値がそれぞれ11B, 10B, 01B, 00B(Bは2進数であることを示す)のときの波形を示す。

10

20

30

## 【0016】

図1における行配線駆動部106は、図3においては表示パネル部107の左右に備えられた二つのYシフトレジスタ106Aと、各行配線の両側に備えられる行配線駆動出力部106Bとからなる。

## 【0017】

Yシフトレジスタ106Aは、タイミング発生部104からのVD信号をHD信号によりシフトし、列配線駆動出力部105Cが、1行目の出力電圧パルスを発生する水平期間に同期して、ほぼ1水平期間幅の電圧パルスを1行目の行配線駆動出力部106Bに出力する。同様に、Yシフトレジスタ106Aは、列配線駆動出力部105Cが、2行目のデータに相当する出力電圧パルスを発生するタイミングに同期して、電圧パルスを2行目の行配線駆動出力部106Bに出力するというように、順次走査のためのタイミングパルスの生成が行われている。

## 【0018】

行配線駆動出力部106Bは、Yシフトレジスタ106Aからの出力電圧パルス信号を所望の振幅レベルになるように増幅して行配線に印加する。この場合は-Vf/2からVf/2の電位差を有する電圧信号を発生する。図5はY1電圧出力信号及びY2電圧出力信号としてその例を示している。

40

## 【0019】

図3及び図5は動作を分かり易くするために素子(emitter)数が非常に少ない例について示しているが、素子数が増えても基本的には同様の構成で実現することができる。

## 【0020】

図1において、入力端子100は、表示すべき画像について外部からの画像信号入力を受けるための入力部である。図示していないが、制限された伝送帯域にて画像信号を伝えるために、入力画像信号が原信号より圧縮された形態で入力される場合においては、入力端子100は、圧縮信号を伸長して原信号に復調するデコード手段を含む。

## 【0021】

画像信号処理部101においては、まず入力端子100からの画像信号を表示パネル部1

50

07の素子数・画素構成に適合するようにサンプリングする。具体的には入力端子100からの画像信号の1フレーム期間中の有効走査線数が表示パネル部107の行ライン数に適合するように(必要ならば)走査線変換を行う。また、列配線数と同数の輝度データを入力信号の水平有効表示期間からサンプリングする。また、表示パネル部107の蛍光面が、例えば赤・緑・青の3原色を用いている場合は、その色配列に適合するように輝度データを配列する。各画像サンプルの量子化ビット数は、表示パネル部107で表現できる階調数に応じて決定する。画像信号は、CRTを用いた表示装置を前提にしていることが多いため、CRTの持つ(ガンマ)特性を考慮して、補正が施されていることが多い。このため、前述のように、発光輝度が電子線放出量要求値データにほぼ比例する表示パネルを対象にする場合は、この予め施されている補正をキャンセルする所謂逆補正も10

画像信号処理部101内にて行う。

## 【0022】

補正量算出部108及び加算手段103は、表示パネル部107内の素子への電気的な接続配線などの電気抵抗分に起因する素子駆動電圧の減少に伴う輝度低下を補償する補正を行なうために備えられたものであり、補正量算出部108にて算出した補正量を加算手段103にて画像信号処理部101からの出力信号に加算することにより、補正輝度データを生成する。

## 【0023】

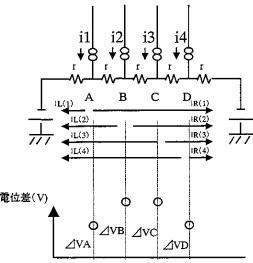

図4に表した例を用いて、接続配線の電気抵抗に起因する素子駆動電圧低下量の計算例を示す。1行目の行配線が選択されているとき、表示パネル部107に配設されている素子11~14に、駆動電流i1~i4がそれぞれ対応する列配線ドライバX1~X4から流れれる。

20

## 【0024】

行配線上の各素子接続部間電気抵抗をrとし、図示のとおり、行配線の両側を同電位で選択している場合、k番目(kは自然数1~4)の素子電流は、行配線接続端(図4にA,B,C,Dで示す)から両側のY1ドライバまでの抵抗値比により、IL(k)とIR(k)とに分流され、

$$IL(1) = (4/5) * i1, IR(1) = (1/5) * i1$$

$$IL(2) = (3/5) * i2, IR(2) = (2/5) * i2$$

$$IL(3) = (2/5) * i3, IR(3) = (3/5) * i3$$

$$IL(4) = (1/5) * i4, IR(4) = (4/5) * i4$$

30

である。すなわち行配線上の各A,B,C,D点における発生電位差VA~VDは以下の(式1)に示される。

## 【0025】

## 【数1】

(式1)

$$\Delta VA = r * \sum_{k=1}^4 (IL(k))$$

$$\Delta VB = \Delta VA + r * (\sum_{k=2}^4 (IL(k)) - \sum_{k=1}^1 (IR(k)))$$

$$\Delta VC = \Delta VB + r * (\sum_{k=3}^4 (IL(k)) - \sum_{k=1}^2 (IR(k)))$$

$$\Delta VD = \Delta VC + r * (\sum_{k=4}^4 (IL(k)) - \sum_{k=1}^3 (IR(k)))$$

上記(式1)にて求めた行配線上に発生する電位差分だけ、素子に印加される駆動電圧が減少し、輝度低下が発生する訳である。

## 【0026】

以上、行配線の両側に行配線駆動部が配置されている場合について述べたが、行配線駆動部が行配線の片側にのみ配置された場合でも同様に計算することができる。 20

## 【0027】

特開平8-248920号公報に開示されている通り、素子印加電圧( $V_f$ )と素子駆動電流( $I_f$ )・放出電流( $I_e$ )の関係は既知の特性を有しており、印加電圧( $V_f$ )を決めれば素子駆動電流( $I_f$ )の値を知ることができる。

## 【0028】

また、表示パネル部107の行配線の電気抵抗値も固定の既知の値を持つ。すなわち1行の全素子に同時に(同じパルス幅にて)駆動電圧が印加される場合は、前述の(式1)により、駆動電圧の減少分(以下電圧降下量と呼ぶ)を求めることが可能、それに起因する輝度減少分補償のための輝度データに加算すべき補正值データを算出することが出来る。 30

## 【0029】

しかしながら、実際の駆動状態においては、1行の素子が同時に同じパルス幅で駆動されることは少なく、それぞれ異なる輝度データに応じたパルス幅で各素子は駆動される。このような場合においては、輝度データに応じて発生する電圧降下量も変化する。

## 【0030】

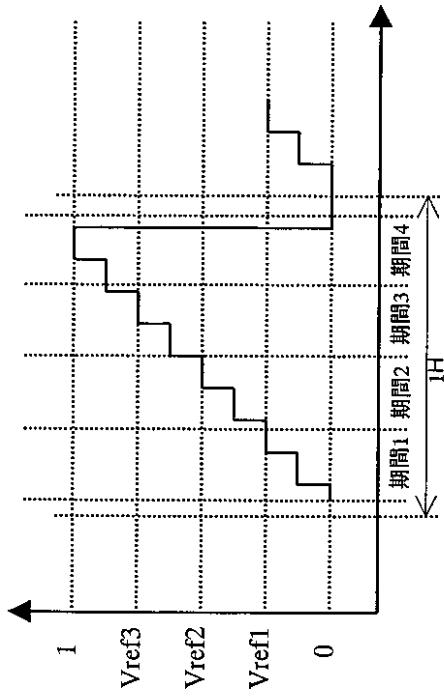

例えば図4に示す例で考えると、2ビットの輝度データによる4通りのパルス幅を取り得る。この場合は、1水平走査期間(但し、画像信号に対応しない期間を除く)を期間I, II, IIIに分割し、各分割期間毎に前記(式1)により、発生する電圧降下量を求ることにより対応することができる。このためには、輝度データをモニタして、期間I, II, III毎にどの素子が駆動されるかを検出すればよい。 40

## 【0031】

具体的には、輝度データとパルス幅は比例関係にあるから、

- ・期間Iに駆動される素子はその輝度データが01B以上のもの

- ・期間IIに駆動される素子はその輝度データが10B以上のもの

- ・期間IIIに駆動される素子はその輝度データが11B以上のもの

という基準値(近似階調レベル)と輝度データの大きさを比較するコンパレータ手段である比較部を備えることにより、図6(1)に示すような期間I, II, III毎のON/OFFテーブルを取得し、このテーブルより期間毎に(式1)により電圧降下量を計算し、その和を取ることで電圧降下量の合計を求めることができる。

## 【0032】

10

20

30

40

50

以上、図3に示す1行の素子数が4個であって、表示階調2ビットの時の補正值算出方法について説明した。この場合、図6(2)に示すように4点×3期間の12回の電圧降下量演算を行った。

#### 【0033】

原理的には素子数が増えた場合や、表示階調数が増えた場合においても、同様の方法にて補正值を算出することはできる。但し(1行の素子数)×(階調数-1)回の演算を1水平期間内に行わなければならないため、表示パネル部107の画素数が大きい場合や、表示階調数が大きい場合は、演算能力不足のため対応できない場合もある。

#### 【0034】

本実施形態においては、表示パネル部107の画素数が大きい場合や、表示階調数が大きい場合における補正值算出方法についても述べる。

本実施形態においては、下記二つの近似により演算回数を減らす。

(近似1)隣接する複数の列配線を一つのブロックとして捕らえ、ブロック単位で補正演算を行う。

(近似2)補正演算に用いる階調数(即ち、近似階調レベル)を実際の表示階調数より減らす。

#### 【0035】

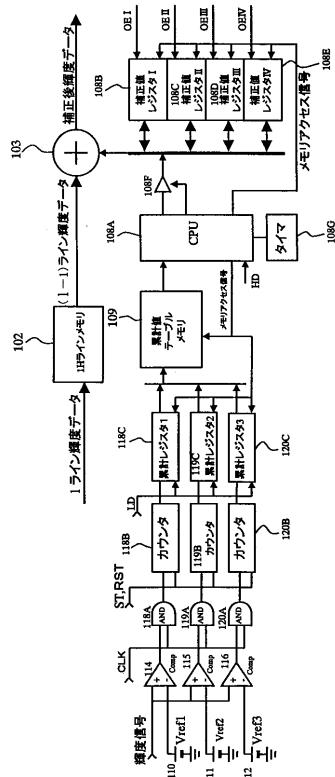

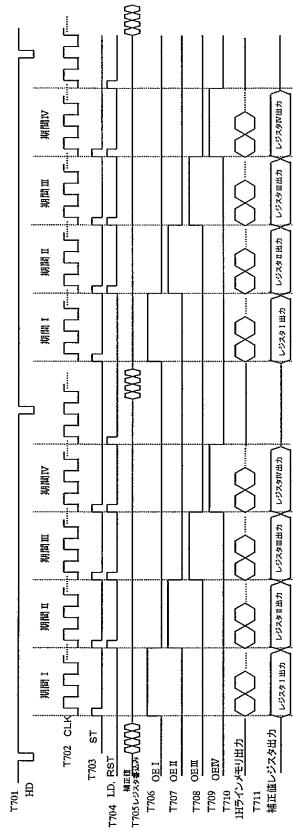

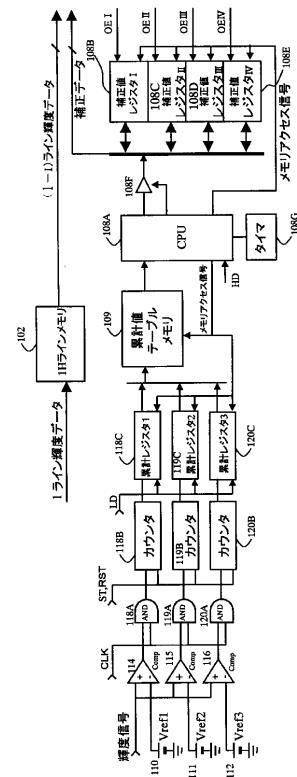

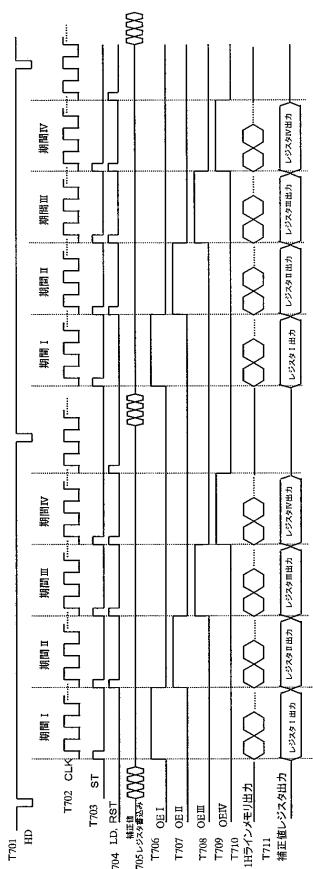

図7は図1に示す第1の実施形態の補正量算出部周辺の詳細を示す構成図である。図8は図7における各部の動作タイミングを示すタイムチャートである。これらの図を用いて近似演算例を説明する。

20

#### 【0036】

水平1(21m)ライン目の輝度データが、比較部114～116に、図7には不図示であるが図1に示した画像信号処理部101から入力される。画像信号処理部101の処理後の信号が、1Hライン(水平1ライン)メモリ102に入力される。1Hラインメモリ102は遅延回路として動作し、1ライン前の(1-1)ラインのデータが加算手段103に出力される。

#### 【0037】

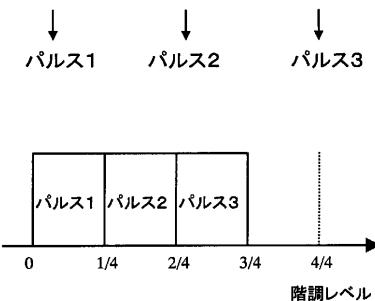

比較部114～116は、図2に示すように、規格化された入力信号レベルの0.25、0.5、0.75に閾値設定された近似階調レベルVref1～3(110, 111, 112)と入力輝度データの大きさとを比較し、近似階調レベルより輝度データが大きいときに、Hi(ハイ)レベルの出力を各比較部114～116毎に備えられた積算部118～120に出力する。図面上では分かりやすいように、比較部としてアナログコンパレータのように電圧源を用いた基準レベルや、コンパレータを書いているが、本例においては、デジタルコンパレータを使用しているのは言うまでもない。

30

#### 【0038】

積算部118～120は、ANDゲート118A～120A、カウンタ118B～120B及び累計値レジスタ118C～120Cから成る。ANDゲート118A～120Aは、比較部114～116の出力とCLK信号T702を入力し、その論理和信号をカウンタ118B～120Bに出力する。

#### 【0039】

カウンタ118B～120Bは、ST信号T703の立ち上りエッジからRST信号T704の立ち上りエッジ期間までのANDゲート118A～120Aからの出力パルス数を計数する。本例においては、図2に示す期間分割及び図8に示す動作タイミングのように、時間軸方向に期間I～IVの4期間に分割するため、ST信号T703の立ち上りエッジは各分割期間の始まりのタイミングに設定され、RST信号T704の立ち上りエッジは各分割期間の終わりのタイミングに設定される。これら図8に示すタイミング信号は図1に示すタイミング発生部104により生成される。

40

#### 【0040】

このカウンタ118B～120Bの計数値は、各分割期間の終わりのタイミングに設定されたLD信号T704にて累計値レジスタ118C～120Cに保存される。図8におい

50

て、R S T 信号とL D 信号は、T 7 0 4 として同タイミングで示されているが、当然L D 信号がR S T 信号より早く、計数値が累計値レジスタ1 1 8 C ~ 1 2 0 C に転送された後、カウンタ1 1 8 B ~ 1 2 0 B はリセットされるのは言うまでもない。累計値レジスタ1 1 8 C ~ 1 2 0 C に保存された計数値は、次のL D 信号の立ち上りエッジが来る前までにC P U 1 0 8 A からのメモリアクセス信号により累計値テーブルメモリ1 0 9 に転送される。

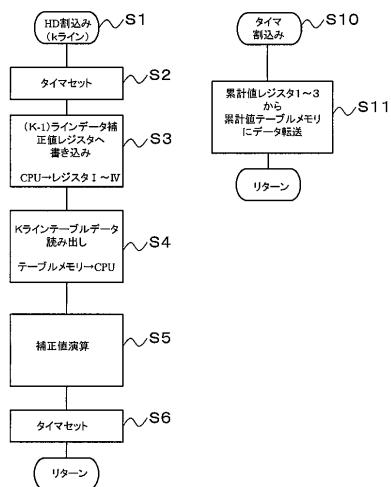

#### 【0 0 4 1】

図1における補正量算出部1 0 8 は、図7に示すようにC P U 1 0 8 A、補正值レジスタ1 0 8 B ~ E、バッファ1 0 8 F 及びタイマ1 0 8 G から成る。C P U 1 0 8 A は、不図 10 示であるがその動作を規定するプログラムが格納されるR O M 手段を備え、そのプログラムにより動作する。補正值演算に係るプログラムのフローチャートを図9に示す。C P U 1 0 8 A に入力されるH D 信号T 7 0 1 の割込み動作（ステップS 1 ）により、補正值演算は、水平周期単位で輝度データ信号と同期して行われる。

#### 【0 0 4 2】

H D 割込みイベントが発生すると、C P U 1 0 8 A は、補正值演算処理ルーチンに飛ぶ。そのルーチンにてC P U 1 0 8 A は、まずタイマ1 0 8 G をセットする（ステップS 2 ）。タイマ1 0 8 G は、1 水平期間内に数回C P U 1 0 8 A にタイマ割込みを発生させるために動作する。このタイマ割込みが発生すると、C P U 1 0 8 A はステップS 1 0 のタイマ割込みルーチンに飛び、累計値レジスタ1 ~ 3 ( 1 1 8 C ~ 1 2 0 C ) に格納されているデータを累計値テーブルメモリ1 0 9 の所定のアドレスに転送（タイマ割込み回数によりアドレスを計算する）し（ステップS 1 1 ）、終了後は元のルーチンに戻る。累計値テーブルメモリ1 0 9 のデータ例を図1 0 に示す。 20

#### 【0 0 4 3】

次に、ステップS 3 で、C P U 1 0 8 A は補正值レジスタ1 0 8 B ~ E に前の水平周期に演算した補正值データを図8におけるT 7 0 5 のタイミングで書き込む。バッファ1 0 8 F はこの書き込み期間のみ有効となる。この書き込みは輝度データの水平帰線期間中に終了する。

#### 【0 0 4 4】

補正值レジスタ1 0 8 B ~ E は、図8において、T 7 0 6 ~ 7 0 9 にて示されるO E I ~ O E I V 信号（H i の期間レジスタの出力を有効にする信号）により、期間I ~ I V に追従して該補正值レジスタ1 0 8 B ~ E の出力が切り替わり、その切り替わりに応じた補正值データが加算手段1 0 3 に出力される。 30

#### 【0 0 4 5】

その後、ステップS 4 で、C P U 1 0 8 A は累計値テーブルメモリ1 0 9 からデータを読み出し、ステップS 5 では、図1 1 に示すような近似モデルにて補正值演算を行う。

#### 【0 0 4 6】

（近似1）表示パネル部1 0 7 の総列配線数を複数ブロック単位（この場合は4 ブロック）に束ね、ブロック内各列配線を流れる駆動電流の総和をブロック電流（図1 1 におけるi 1 ~ i 4 に相当）として扱う。行配線上の素子間抵抗値もブロック毎に定める代表点間の抵抗値で考える。 40

（近似2）輝度データに応じた列配線駆動パルス幅を以下の条件でパルス1 , 2 , 3 の3 パルスで置き換える。

#### 【0 0 4 7】

- ・V r e f 1 未満の輝度データ パルス幅 0

- ・V r e f 1 以上V r e f 2 未満の輝度データ パルス幅 1 / 4 : ( パルス1 )

- ・V r e f 2 以上V r e f 3 未満の輝度データ パルス幅 2 / 4 : ( パルス2 )

- ・V r e f 3 以上の輝度データ パルス幅 3 / 4 : ( パルス3 )

#### 【0 0 4 8】

近似1 , 2 により、パルス1 ~ 3 毎の各ブロック電流は以下のように求められる。ここで、i は1 素子分の駆動電流値である。 50

i 1 ( パルス 1 ) = N A 1 × ( i / 4 ) ,

i 1 ( パルス 2 ) = N A 2 × ( i / 4 ) ,

i 1 ( パルス 3 ) = N A 3 × ( i / 4 ) ,

i 2 ( パルス 1 ) = N B 1 × ( i / 4 ) ,

i 2 ( パルス 2 ) = N B 2 × ( i / 4 ) ,

i 2 ( パルス 3 ) = N B 3 × ( i / 4 ) ,

i 3 ( パルス 1 ) = N C 1 × ( i / 4 ) ,

i 3 ( パルス 2 ) = N C 2 × ( i / 4 ) ,

i 3 ( パルス 3 ) = N C 3 × ( i / 4 ) ,

i 4 ( パルス 1 ) = N D 1 × ( i / 4 ) ,

i 4 ( パルス 2 ) = N D 2 × ( i / 4 ) ,

i 4 ( パルス 3 ) = N D 3 × ( i / 4 )

10

ここで、N A 1 ~ N A 3、N B 1 ~ N B 3、N C 1 ~ N C 3、N D 1 ~ N D 3 は、4 つの各ブロックにおいて、パルス 1 ~ 3 の輝度データを有する列配線数である。

#### 【 0 0 4 9 】

図 1 1 に示す近似モデルは、前述した図 4 と同じであるから、上記のように、パルス 1 ~ 3 毎の各ブロック電流  $i_1$  ~  $i_4$  が求められれば、(式 1)によりブロック間の電圧降下量を求めることが出来る。特開平 8 - 248920 号公報に開示されている通り、素子印加電圧 ( $V_f$ ) と素子駆動電流 ( $I_f$ )・放出電流 ( $I_e$ ) の関係は既知の特性を有しており、電圧降下量から放出電子量の低下分が求められ、その低下分を補正するための補正値は演算して得ることが出来る。

20

#### 【 0 0 5 0 】

このようにして得られた補正值データは、C P U 1 0 8 A の周辺に配置される不図示のメモリに保管され、次の H D 割込み処理時に補正值レジスタ I ~ I V に転送される。

#### 【 0 0 5 1 】

補正值データは、加算手段 1 0 3 により、(1 - 1) ラインの輝度データに加算され、補正輝度データとして、列配線駆動部 1 0 5 へ転送される。従って、1 水平走査期間において、列配線駆動部 1 0 5 から出力される駆動パルスは、例えば図 1 に示した表示パネル 1 0 7 の両側に行配線駆動部 1 0 6 を有する構成においては、同一の輝度データに対しては、電圧降下量の大きい表示パネル 1 0 7 の中央部の列配線に出力される電圧パルスのパルス幅が端部に比べて長くなる。また、行配線駆動部 1 0 6 が表示パネル 1 0 7 の片側のみに配置されている構成においては、行配線駆動部 1 0 6 から離れて配置されている列配線に印加される駆動パルスのパルス幅が長くなる。

30

#### 【 0 0 5 2 】

説明を簡単にするために、列配線ブロックを 4 個、階調パルスを 3 種に近似した例にて補正演算方法を述べたが、もちろんこれに限定されることなく、ブロック数や階調パルス種の数は任意に増減することが出来る。

#### 【 0 0 5 3 】

また、図 7 に示した例においては、列配線のブロック数と同数の補正值レジスタ 1 0 8 B ~ E を備え、同一ブロックの列配線補正是同一値で行う例について説明したが、ブロック毎に求めた補正值データを用いて直線補間により、各列配線に対する補正值データを求めることが出来る。即ち、電圧降下量及びそれから算出される補正值データは、前述した方法に従って列配線ブロック毎に計算し、ブロック内の各列配線に対しては、ブロック毎の計算値から直線補間された補正值データを用いて、補正輝度データを生成することができる。

40

#### 【 0 0 5 4 】

さらに、各期間毎に得られた補正值データに対しても、同様に直線補間により期間内の任意の期間に対する補正值データを得ることが出来る。

#### 【 0 0 5 5 】

つまり、計算量の多い電圧降下量の計算は、列配線及び水平走査期間各々に対してブロック

50

ク化して行い、計算量の少ない直線補間により、全列配線における任意の輝度データに対して補正值データを得ることができる。

【0056】

このような補正值データの補間を行う補間手段を備えることにより、より精度の高い輝度の補正を行うことが可能になるのは言うまでもない。

【0057】

この例は(近似1)のブロック分割を均等に行った場合で説明したが、もちろんこれに限定されるものではなく、例えば表示パネル部107の中心部と周辺部で束ねるブロックの大きさを変えることも出来る。

【0058】

10

[第2の実施形態]

図14は本発明の第2の実施形態に用いる列配線1列分の列配線駆動部を示す構成図である。不図示ではあるが、実際には列配線駆動部が各列配線毎に備えられる。

【0059】

この実施形態においては、Xシフトレジスタ200に入力されるデータのビット幅は10ビットである。10ビット幅というのは、輝度データ8ビットと補正值データ2ビットで考えているからである。Xシフトレジスタ200は10ビット幅×列配線数の深さを持つ。この実施形態に係るパルス幅変調器201は、第1の実施形態で説明したパルス幅変調器105Bと同機能のものであり、この場合、輝度データ8ビットの入力を受け、輝度データに応じて0～255階調に相当するパルス幅のトリガ信号をSW(スイッチ)手段203に出力する。

【0060】

補正值データ2ビットは、デコーダ202に入力され、不図示の電源給電部から入力される4種類の電圧(V1～V4)のうちの1種を補正值データにより決定し出力する。その決定は、例えば図15に示す表のように行われる。SW手段203は、列配線に印加する電圧をデコーダ202の出力電圧とするか、あるいは接地レベルの電圧とするかをパルス幅変調器201からのトリガ信号により切り替えるスイッチ手段であり、輝度データに応じたパルス幅の期間中、デコーダ202の出力電圧を列配線に印加する。

【0061】

図12は本発明の第2の実施形態における補正量算出部の構成を示し、図13はその動作タイミングを示す。

本実施形態において、補正值を演算し補正值レジスタI～IVに書き込むまでは、第1の実施形態とほぼ同じ動作である。第1の実施形態では、加算手段103により、輝度データと補正值データの加算処理を行い出力していたが、この第2の実施形態においては、別々の信号線にてXシフトレジスタ200に出力する。図14に示す出力段構成の例においては、輝度データ8ビット、補正值データ2ビットであるが、もちろんこれに限定されるものではない。第1の実施形態との相違は第2の実施形態においては、補正是出力部のデコーダ202を補正值データにより切り替えることで、電子放出素子に印加される駆動電圧を変化させて補正を実現するという点である。

【0062】

40

この実施形態においても、補正值レジスタの数を補正值演算のために近似したブロック数よりも増やすことは可能である。増やしたレジスタには、ブロック毎に求めた補正值データを用いて、直線補間により書き込むべき値を求めて、それを保持させればよい。

【0063】

[第3の実施形態]

図16は本発明の第3の実施形態に係る表示装置を示す構成図である。

本実施形態において、正値を演算し補正值レジスタI～IVに書き込むまでは、第1の実施形態とほぼ同じ動作である。第1の実施形態との相違点は、配線駆動部への補正值の与え方である。

【0064】

50

列配線駆動部 301 はほぼ第 1 の実施形態の構成と同じであるが、列配線駆動出力部 205C の機能が異なる。第 1 の実施形態においては、パルス幅変調器 105B の出力電圧信号を所望の振幅レベルになるように増幅して列配線に印加するように動作していたが、本実施形態においては、列配線に印加する振幅レベルが外部から供給される電圧値になるように動作する。

【0065】

図 16 で示す例においては、補正値演算のための近似ブロック I ~ I V 毎に可変電源 302A ~ 302D を備え、可変電源 302A ~ 302D で決定される電圧振幅を有するパルスを列配線に印加する。

【0066】

可変電源 302A ~ 302D の出力電圧は、補正量算出部 108 からの信号により制御される。例えば、可変電源 302A ~ 302D はデジタル - アナログコンバータ手段（以下 DA 手段と呼ぶ）で構成することができる。この場合は、図 7 における補正値レジスタに書き込まれた補正値データを帰線期間中に DA 手段に転送し、有効期間中は、補正値データで決まる電圧を出力するように動作すればよい。

【0067】

この実施形態においても、補正値レジスタの数を補正値演算のために近似したブロック数よりも増やすことは可能である。増やしたレジスタには、ブロック毎に求めた補正値データを用いて、直線補間により書き込むべき値を求めた結果を保持させればよく、可変電源 302X を同様に増設すればよい。

【0068】

【発明の効果】

以上説明したように本発明によれば、電子放出素子や E L 素子等の画像形成素子への電気的な接続配線などの電気抵抗分に起因する素子駆動電圧の減少に伴う輝度低下を補償することができ、それによって、表示画面全体にわたって均一で良好な画像表示を行うことができる。

【0069】

さらに、該補正を行うに当たり、表示パネルの画素数や表示階調数が大きい場合にも、2 種類の近似中の少なくともいずれか一つを導入することにより、従来よりも少ないハードウェアで該補正を実現することができ、製品コストを低減することができる。

【図面の簡単な説明】

【図 1】 本発明の第 1 の実施形態に係る表示装置を示す構成図である。

【図 2】 本発明の第 1 の実施形態におけるエリア分割・期間分割の例を示す図である。

【図 3】 本発明の第 1 の実施形態に係る表示装置における列配線駆動部・行配線駆動部の構成・動作を分かりやすく説明するための構成図を示す。

【図 4】 図 3 における行配線上に発生する電圧降下量の計算例を示す説明用図である。

【図 5】 図 3 における各部の動作タイミングを示すタイムチャートである。

【図 6】 (1) は図 3 及び図 5 におけるテーブルメモリ取得例を示す表であり、(2) は図 3 の例でパルス幅変調されたときの電圧降下量の計算例を示す表である。

【図 7】 本発明の第 1 の実施形態に係る表示装置における補正量算出部の詳細な例を示す構成図である。

【図 8】 図 7 における各部の動作タイミングを示すタイムチャートである。

【図 9】 図 7 内における C P U に係るフローチャートを示す図である。

【図 10】 図 7 における累計値テーブルメモリの内容例を示す図である。

【図 11】 本発明の第 1 の実施形態で用いた近似モデルの例を示す図である。

【図 12】 本発明の第 2 の実施形態に係る表示装置を示す構成図である。

【図 13】 図 12 における各部の動作タイミングを示すタイムチャートである。

【図 14】 本発明の第 2 の実施形態における列配線駆動部の 1 列分の構成を示す図である。

【図 15】 図 14 内のデコーダの出力テーブルを示す表である。

【図16】 本発明の第3の実施形態に係る表示装置を示す構成図である。

【図17】 従来例として引用した特開平8-248920号公報に第1実施例として記載された表示装置を示す構成図である。

【符号の説明】

111～114及び211～214：素子（電子放出素子）、100：入力端子（入力部）、101：画像信号処理部、102：ラインメモリ、103：加算手段、104：タイミング発生部、105：列配線駆動部、105A：Xシフトレジスタ、105B：パルス幅変調器、105C：列配線駆動出力部、106：行配線駆動部、106A：Yシフトレジスタ、106B：行配線駆動出力部、107：表示パネル部、108：補正量算出部、108A：C P U、108B～E：補正值レジスタ、108F：バッファ、108G：タイマ、109：テーブルメモリ、110～112：基準レベル、114～116：比較部、118～120：積算部、118A～120A：ANDゲート、118B～120B：カウンタ、118C～120C：累計値レジスタ、200：Xシフトレジスタ、201：パルス幅変調器、202：デコーダ、203：SW手段、302A～302D：可変電源。

【図1】

【図2】

【図3】

【図4】

$$\begin{aligned}

IL(1) &= (r * 4/5) * i1 & IR(1) &= (r * 1/5) * i1 \\

IL(2) &= (r * 3/5) * i2 & IR(2) &= (r * 2/5) * i2 \\

IL(3) &= (r * 2/5) * i3 & IR(3) &= (r * 3/5) * i3 \\

IL(4) &= (r * 1/5) * i4 & IR(4) &= (r * 4/5) * i4

\end{aligned}$$

$$\begin{aligned}

\Delta VA &= r * \sum_{k=1}^4 (IL(k)) \\

\Delta VB &= \Delta VA + r * \left( \sum_{k=2}^4 (IL(k)) - \frac{1}{k} (IL(1)) \right) \\

\Delta VC &= \Delta VB + r * \left( \sum_{k=3}^4 (IL(k)) - \frac{2}{k} (IL(1) + IL(2)) \right) \\

\Delta VD &= \Delta VC + r * \left( \sum_{k=4}^4 (IL(k)) - \frac{3}{k} (IL(1) + IL(2) + IL(3)) \right)

\end{aligned}$$

【図5】

【図6】

|          | 期間I | 期間II | 期間III |

|----------|-----|------|-------|

| X1電圧出力信号 | ON  | ON   | ON    |

| X2電圧出力信号 | ON  | ON   | OFF   |

| X3電圧出力信号 | ON  | OFF  | OFF   |

| X4電圧出力信号 | OFF | OFF  | OFF   |

(1)

|          | 期間I            | 期間II            | 期間III            | 1水準期間の合計                                              |

|----------|----------------|-----------------|------------------|-------------------------------------------------------|

| A点の電圧降下量 | $\Delta VA(1)$ | $\Delta VA(II)$ | $\Delta VA(III)$ | $(\Delta VA(1) + \Delta VA(II) + \Delta VA(III)) / 3$ |

| B点の電圧降下量 | $\Delta VB(1)$ | $\Delta VB(II)$ | $\Delta VB(III)$ | $(\Delta VB(1) + \Delta VB(II) + \Delta VB(III)) / 3$ |

| C点の電圧降下量 | $\Delta VC(1)$ | $\Delta VC(II)$ | $\Delta VC(III)$ | $(\Delta VC(1) + \Delta VC(II) + \Delta VC(III)) / 3$ |

| D点の電圧降下量 | $\Delta VD(1)$ | $\Delta VD(II)$ | $\Delta VD(III)$ | $(\Delta VD(1) + \Delta VD(II) + \Delta VD(III)) / 3$ |

(2)

【図7】

【図8】

【図9】

【図10】

|         | Vref1以上のデータ数 | Vref2以上のデータ数 | Vref3以上のデータ数 |

|---------|--------------|--------------|--------------|

| ブロックI   | NA1          | NA2          | NA3          |

| ブロックII  | NB1          | NB2          | NB3          |

| ブロックIII | NC1          | NC2          | NC3          |

| ブロックIV  | ND1          | ND2          | ND3          |

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【図14】

【 図 1 5 】

| 補正データ | 出力 |

|-------|----|

| 00B   | V1 |

| 01B   | V2 |

| 10B   | V3 |

| 11B   | V4 |

【 図 1 6 】

【 図 17 】

---

フロントページの続き

審査官 小川 浩史

(56)参考文献 特開平2 - 257553 (JP, A)

特開平9 - 134145 (JP, A)

特開2000 - 242208 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/20-3/38