(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6501787号

(P6501787)

(45) 発行日 平成31年4月17日(2019.4.17)

(24) 登録日 平成31年3月29日(2019.3.29)

(51) Int.Cl.

F 1

G06F 3/041 (2006.01)

G06F 3/044 (2006.01)G06F 3/041 600

G06F 3/041 520

G06F 3/041 595

G06F 3/044 120

G06F 3/044 130

請求項の数 16 (全 23 頁)

(21) 出願番号 特願2016-551799 (P2016-551799)

(86) (22) 出願日 平成27年4月14日 (2015.4.14)

(65) 公表番号 特表2017-511522 (P2017-511522A)

(43) 公表日 平成29年4月20日 (2017.4.20)

(86) 國際出願番号 PCT/US2015/025767

(87) 國際公開番号 WO2015/160819

(87) 國際公開日 平成27年10月22日 (2015.10.22)

審査請求日 平成30年3月16日 (2018.3.16)

(31) 優先権主張番号 14/254,407

(32) 優先日 平成26年4月16日 (2014.4.16)

(33) 優先権主張国 米国(US)

(73) 特許権者 397050741

マイクロチップ テクノロジー インコーポレイテッド

MICROCHIP TECHNOLOGY INCORPORATED

アメリカ合衆国 85224-6199

アリゾナ チャンドラー ウエスト チャンドラー ブルヴァード 2355

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】力検出を伴う投影容量式タッチ

## (57) 【特許請求の範囲】

## 【請求項 1】

タッチ感知表面上の複数のタッチの場所およびそれらの組み合わせられた力を決定する方法であって、前記方法は、

第1の軸を有し、平行配向に配列されている第1の複数の電極を提供するステップであって、前記第1の複数の電極の各々は、自己容量を備えている、ステップと、

前記第1の軸に実質的に垂直な第2の軸を有し、平行配向に配列されている第2の複数の電極を提供するステップであって、前記第1の複数の電極は、前記第2の複数の電極の上に位置し、前記第1の複数の電極と前記第2の複数の電極との重複交差点を備えている複数のノードを形成し、前記複数のノードの各々は、相互容量を備えている、ステップと、

基板を提供するステップであって、前記基板は、前記基板の上に配置されている前記第1の複数の電極および前記第2の複数の電極を有し、前記基板は、複数の角を有する、ステップと、

複数の力センサを提供するステップであって、前記基板の各角は、前記複数の力センサのうちのそれぞれの1つに結合されている、ステップと、

前記第1の複数の電極を走査し、前記第1の複数の電極の自己容量の値を決定するステップと、

前記走査された自己容量の値を比較し、前記第1の複数の電極のうちのどの複数の電極が自己容量の最も大きな値を有するかを決定するステップと、

10

20

前記第1の複数の電極のうちの前記自己容量の最も大きな値を有する前記複数の電極のノードを走査し、それぞれの複数のノードの相互容量の値を決定するステップと、

前記自己容量の最も大きな値を有する前記第1の電極上のそれぞれの複数のノードの走査された相互容量の値を比較するステップであって、前記相互容量の最も大きな値を有する複数のノードは、前記タッチ感知表面上の複数のタッチの場所である、ステップと、

決定されたタッチの場所から幾何学的質量中心（CM）を決定し、前記複数の力センサによって測定される力値から、および、決定されたタッチの場所から、計算力点（CFP）を決定するステップと、

前記計算力点を前記質量中心と比較し、実行されるべきアクションを決定するステップであって、前記CFPが前記CMに一致するときに前記タッチの垂直移動が決定され、前記CFPが前記CMに一致しないときに前記タッチの回転移動が決定される、ステップと、

前記タッチに対応する表示されたオブジェクトに対する前記垂直移動または前記回転移動に対応するジェスチャコマンドを生成するステップと

を含む、方法。

【請求項2】

前記自己容量値および相互容量値は、アナログフロントエンドおよびアナログ／デジタルコンバータ（ADC）を用いて測定される、請求項1に記載の方法。

【請求項3】

前記自己容量値および相互容量値は、デジタルデバイスのメモリ内に記憶されている、請求項2に記載の方法。

【請求項4】

前記デジタルデバイス内のデジタルプロセッサは、前記タッチのタッチ場所および前記タッチ場所における前記タッチ感知表面に前記タッチによって加えられるそれぞれの力を決定することにおいて、前記記憶された自己容量値および相互容量値を使用する、請求項3に記載の方法。

【請求項5】

前記複数の力センサによって測定された力値を一緒に加算することによって前記計算力点（CFP）を決定するステップと、

前記タッチ場所を使用することによって、前記幾何学的質量中心（CM）を決定するステップと

を含む、請求項1～4のいずれか一項に記載の方法。

【請求項6】

前記幾何学的CMに対する前記CFPのX-オフセット $X_R$ を決定することと、

前記幾何学的CMに対する前記CFPのY-オフセット $Y_R$ を決定することと

をさらに含む、請求項5に記載の方法。

【請求項7】

前記X-オフセット $X_R$ を決定することは、 $X_R = ((F1 + F3) * (-W / 2) + (F2 + F4) * (W / 2)) / F_R$ を解法することを含み、式中、Wは、前記タッチ感知表面の面の幅であり、 $X_R$ は、前記CMから前記CFPまでのXオフセットである、請求項6に記載の方法。

【請求項8】

前記Y-オフセット $Y_R$ を決定することは、 $Y_R = ((F1 + F2) * (-H / 2) + (F3 + F4) * (H / 2)) / F_R$ を解法することを含み、式中、Hは、前記タッチ感知表面の面の高さであり、 $Y_R$ は、前記CMから前記CFPまでのYオフセットである、請求項6または請求項7に記載の方法。

【請求項9】

タッチ感知表面上のタッチの場所およびそれらの組み合わせられた力を決定するためのシステムであって、前記システムは、

第1の軸を有し、平行配向に配列されている第1の複数の電極であって、前記第1の複

10

20

30

40

50

数の電極の各々は、自己容量を備えている、第1の複数の電極と、

前記第1の軸に実質的に垂直な第2の軸を有し、平行配向に配列されている第2の複数の電極であって、前記第1の複数の電極は、前記第2の複数の電極の上に位置し、前記第1の複数の電極と第2の複数の電極との重複交差点を備えている複数のノードを形成し、前記複数のノードの各々は、相互容量を備えている、第2の複数の電極と、

基板であって、前記基板は、前記基板の上に配置されている前記第1および第2の複数の電極を有し、前記基板は、複数の角を有する、基板と、

複数の力センサであって、前記基板の各角は、前記複数の力センサのうちのそれぞれの1つに結合されている、力センサと、

デジタルプロセッサおよびメモリであって、前記デジタルプロセッサのデジタル出力は 10 、前記第1の複数の電極および前記第2の複数の電極に結合されている、デジタルプロセッサおよびメモリと、

前記第1の複数の電極および前記第2の複数の電極と前記複数の力センサとに結合されているアナログフロントエンドと、

前記デジタルプロセッサに結合されている少なくとも1つのデジタル出力を有するアナログ／デジタルコンバータ（A D C）と

を備え、

前記アナログフロントエンド、前記A D C、および、前記プロセッサは、

前記第1の複数の電極の各々に対して、前記自己容量の値を測定することと、

前記測定された自己容量の値を前記メモリ内に記憶することと、

自己容量の最も大きな値のうちの少なくとも1つを有する、前記第1の電極のうちの少なくとも1つのノードの相互容量の値を測定することと、

前記測定された相互容量の値を前記メモリ内に記憶することと、

前記複数の力センサによって測定される力の値を前記メモリ内に記憶することと、

前記タッチの場所を決定するために前記記憶された自己容量値および相互容量値を使用することであって、前記プロセッサは、前記決定されたタッチの場所から前記タッチ感知表面上の幾何学的質量中心（C M）を決定するように構成され、前記プロセッサ（106）は、前記力値および前記決定されたタッチの場所から前記タッチ感知表面上の力点（C F P）を計算するようにさらに構成され、前記計算された力点（C F P）が前記幾何学的質量中心（C M）と比較されて、実行されるべきアクションが決定され、前記C F Pが前記C Mに一致するときに前記タッチの垂直移動が決定され、前記C F Pが前記C Mに一致しないときに前記タッチの回転移動が決定され、前記プロセッサは、前記タッチに対応する表示されたオブジェクトに対する前記垂直移動または前記回転移動に対応するジェスチャコマンドを生成するように構成されることと 30

を行うように構成される、システム。

#### 【請求項10】

前記デジタルプロセッサおよびメモリ（106）、ならびに、アナログフロントエンド（110）およびA D C（108）は、デジタルデバイスによって提供される、請求項9に記載のシステム。

#### 【請求項11】

前記デジタルプロセッサ、メモリ、アナログフロントエンド、およびA D Cは、少なくとも1つのデジタルデバイスによって提供される、請求項9に記載のシステム。

#### 【請求項12】

前記デジタルデバイスは、マイクロコントローラを備えている、請求項10に記載のシステム。

#### 【請求項13】

前記デジタルデバイスは、マイクロプロセッサ、デジタル信号プロセッサ、特定用途向け集積回路（A S I C）、およびプログラマブル論理アレイ（P L A）から成る群から選択される、請求項10に記載のシステム。

#### 【請求項14】

10

20

30

40

50

前記基板は、実質的に光透過性であり、前記第1の複数の電極および前記第2の複数の電極は、インジウムスズ酸化物(ITO)を備えている、請求項9～13のいずれか一項に記載のシステム。

【請求項15】

前記基板は、実質的に光透過性であり、前記第1の複数の電極および前記第2の複数の電極は、アンチモンスズ酸化物(ATO)を備えている、請求項9～14のいずれか一項に記載のシステム。

【請求項16】

前記基板(101)は、4つの角を備えている、請求項9～15のいずれか一項に記載のシステム。

10

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、タッチセンサに関し、より具体的には、タッチおよび/またはジェスチャ中、タッチ場所とタッチセンサに加えられる圧力(力)との両方を感知するタッチセンサに関する。

【背景技術】

【0002】

あるエリアを有するタッチ検出基板を備えているタッチセンサは、概して、基板エリアの表面へのタッチの場所、例えば、2次元X-Y座標のみを決定することができる。第3の感知入力が、X-Yタッチ場所入力と組み合わせて使用され得る追加の情報を可能にするために所望される。タッチのX-Y座標場所だけでなく、タッチセンサ基板の表面へのタッチの力も決定可能であることは、そのような特徴を伴うタッチセンサを有するデバイスとともに使用され得る別の制御オプションを与える。

20

【発明の概要】

【課題を解決するための手段】

【0003】

したがって、そこへのタッチの場所およびそれにかかる力の両方を検出するために使用され得る、タッチセンサの必要性がある。

【0004】

30

ある実施形態によると、タッチ感知表面上のタッチの場所およびその力を決定するための装置は、第1の軸を有し、平行配向に配列されている第1の複数の電極であって、第1の複数の電極の各々は、自己容量を備え得る、第1の複数の電極と、第1の軸に実質的に垂直な第2の軸を有し、平行配向に配列されている第2の複数の電極であって、第1の複数の電極は、第2の複数の電極の上に位置し、第1の複数の電極と第2の複数の電極との重複交差点を備え得る複数のノードを形成し得、複数のノードの各々は、相互容量を備えている、第2の複数の電極と、その上に配置される第1および第2の複数の電極を有する基板であって、複数の角を有し得る基板と、複数の力センサであって、基板の各角は、複数の力センサのうちのそれぞれのものに結合され得る、力センサとを備え得、複数の力センサの各々は、基板へのタッチ中、基板に加えられる力の一部を測定する。

40

【0005】

さらなる実施形態によると、基板は、実質的に光透過性であり得、第1および第2の複数の電極は、インジウムスズ酸化物(ITO)を備え得る。さらなる実施形態によると、基板は、実質的に光透過性であり得、第1および第2の複数の電極は、アンチモンスズ酸化物(ATO)を備え得る。さらなる実施形態によると、基板は、4つの角を備え得る。

【0006】

別の実施形態によると、タッチ感知表面上のタッチの場所およびその力を決定する方法は、第1の軸を有し、平行配向に配列されている第1の複数の電極を提供するステップであって、第1の複数の電極の各々は、自己容量を備え得る、ステップと、第1の軸に実質的に垂直な第2の軸を有し、平行配向に配列されている第2の複数の電極を提供するステ

50

ップであって、第1の複数の電極は、第2の複数の電極の上に位置し、第1の複数の電極と第2の複数の電極との重複交差点を備え得る複数のノードを形成し得、複数のノードの各々は、相互容量を備え得る、ステップと、その上に配置される第1および第2の複数の電極を有する基板を提供するステップであって、基板は、複数の角を有し得る、ステップと、複数の力センサを提供するステップであって、基板の各角は、複数の力センサのうちのそれぞれのものに結合され得る、ステップと、その自己容量の値を決定するために、第1の複数の電極を走査するステップと、走査された自己容量の値を比較し、第1の複数の電極のうちのどれが自己容量の最も大きな値を有し得るかを決定するステップと、それぞれの複数のノードの相互容量の値を決定するために、自己容量の最も大きな値を有する第1の複数の電極のうちの1つのノードを走査するステップと、自己容量の最も大きな値を有する第1の電極上のそれぞれの複数のノードの走査された相互容量の値を比較するステップであって、相互容量の最も大きな値を有するノードは、タッチ感知表面上のタッチの場所であり得る、ステップと、複数の力センサによって測定された力値から、タッチ感知表面上のタッチの力を決定するステップとを含み得る。10

#### 【0007】

本方法のさらなる実施形態によると、自己および相互容量値は、アナログフロントエンドおよびアナログ／デジタルコンバータ（A D C）を用いて測定され得る。本方法のさらなる実施形態によると、自己および相互容量値は、デジタルデバイスのメモリ内に記憶され得る。本方法のさらなる実施形態によると、デジタルデバイス内のデジタルプロセッサは、タッチのタッチ場所およびタッチ場所においてタッチ感知表面に対してタッチによって加えられた力を決定することにおいて、記憶された自己および相互容量値を使用し得る。本方法のさらなる実施形態によると、タッチ感知表面上のタッチの力を決定するステップは、複数の力センサによって測定される力値を一緒に加算することによって計算力点（C F P）を決定するステップを含み得る。20

#### 【0008】

さらに別の実施形態によると、タッチ感知表面上の複数のタッチの場所およびそれらの組み合わせられた力を決定する方法は、第1の軸を有し、平行配向に配列されている第1の複数の電極を提供するステップであって、第1の複数の電極の各々は、自己容量を備え得る、ステップと、第1の軸に実質的に垂直な第2の軸を有し、平行配向に配列されている第2の複数の電極を提供するステップであって、第1の複数の電極は、第2の複数の電極の上に位置し、第1の複数の電極と第2の複数の電極との重複交差点を備え得る複数のノードを形成し得、複数のノードの各々は、相互容量を備え得る、ステップと、その上に配置される第1および第2の複数の電極を有する基板を提供するステップであって、基板は、複数の角を有し得る、ステップと、複数の力センサを提供するステップであって、基板の各角は、複数の力センサのうちのそれぞれのものに結合され得る、ステップと、その自己容量の値を決定するために第1の複数の電極を走査するステップと、走査された自己容量の値を比較し、第1の複数の電極のうちのどれが自己容量の最も大きな値を有し得るかを決定するステップと、それぞれの複数のノードの相互容量の値を決定するために、自己容量の最も大きな値を有する第1の複数の電極のうちの1つのノードを走査するステップと、自己容量の最も大きな値を有する第1の電極上のそれぞれの複数のノードの走査された相互容量の値を比較するステップであって、相互容量の最も大きな値を有するノードは、タッチ感知表面上のタッチの場所であり得る、ステップと、複数の力センサによって測定される力値から、タッチ感知表面上のタッチの組み合わせられた力を決定するステップとを含み得る。30

#### 【0009】

本方法のさらなる実施形態によると、自己および相互容量値は、アナログフロントエンドおよびアナログ／デジタルコンバータ（A D C）を用いて測定され得る。本方法のさらなる実施形態によると、自己および相互容量値は、デジタルデバイスのメモリ内に記憶され得る。本方法のさらなる実施形態によると、デジタルデバイス内のデジタルプロセッサは、タッチのタッチ場所およびタッチ場所におけるタッチ感知表面に対するタッチによっ40

て加えられるそれぞれの力を決定することにおいて、記憶された自己および相互容量値を使用し得る。

【0010】

本方法のさらなる実施形態によると、タッチ感知表面上のタッチの組み合わせられた力を決定するステップは、複数の力センサによって測定された力値と一緒に加算することによって計算力点（C F P）を決定するステップと、タッチ場所および複数の力センサによって測定される力値を使用することによって、質量中心（C M）を決定するステップとを含み得る。

【0011】

本方法のさらなる実施形態によると、C Mを決定するステップは、C F PのX - オフセット $X_R$ を決定するステップと、C F PのY - オフセット $Y_R$ を決定するステップとを含み得る。本方法のさらなる実施形態によると、X - オフセット $X_R$ を決定するステップは、 $X_R = ((F_1 + F_3) * (-W/2)) + ((F_2 + F_4) * (W/2)) / F_R$ を解法するステップを含み得、式中、Wは、タッチ感知表面の面の幅であり得、 $X_R$ は、C MからC F PまでのXオフセットであり得る。本方法のさらなる実施形態によると、Y - オフセット $Y_R$ を決定するステップは、 $Y_R = ((F_1 + F_2) * (-H/2)) + ((F_3 + F_4) * (H/2)) / F_R$ を解法するステップを含み得、式中、Hは、タッチ感知表面の面の高さであり得、 $Y_R$ は、C MからC F PまでのYオフセットであり得る。

【0012】

さらに別の実施形態によると、タッチ感知表面上のタッチの場所およびそれらの組み合わせられた力を決定するためのシステムは、第1の軸を有し、平行配向に配列されている第1の複数の電極であって、第1の複数の電極の各々は、自己容量を備え得る、第1の複数の電極と、第1の軸に実質的に垂直な第2の軸を有し、平行配向に配列されている第2の複数の電極であって、第1の複数の電極は、第2の複数の電極の上に位置し、第1の複数の電極と第2の複数の電極との重複交差点を備え得る複数のノードを形成し得、複数のノードの各々は、相互容量を備え得る、第2の複数の電極と、その上に配置される第1および第2の複数の電極を有する基板であって、複数の角を有し得る基板と、複数の力センサであって、基板の各角は、複数の力センサの個別のものに結合され得る、力センサと、デジタルプロセッサおよびメモリであって、デジタルプロセッサのデジタル出力は、第1および第2の複数の電極に結合され得る、デジタルプロセッサおよびメモリと、第1および第2の複数の電極および複数の力センサに結合されるアナログフロントエンドと、デジタルプロセッサに結合されている少なくとも1つのデジタル出力を有するアナログ/デジタルコンバータ（A D C）とを備え得、自己容量の値は、アナログフロントエンドによって、第1の複数の電極毎に決定され得、測定された自己容量の値は、メモリ内に記憶され得、自己容量の最も大きな値のうちの少なくとも1つを有する、第1の電極のうちの少なくとも1つのノードの相互容量の値は、アナログフロントエンドによって測定され得、測定された相互容量の値は、メモリ内に記憶され得、複数の力センサによって測定された力の値は、メモリ内に記憶され得、デジタルプロセッサは、タッチの場所を決定するために、記憶された自己および相互容量値を使用し、複数の力センサによって測定された力値から、タッチ感知表面上の力点（C F P）および質量中心（C M）を計算し得る。

【0013】

さらなる実施形態によると、デジタルプロセッサ、メモリ、アナログフロントエンド、およびA D Cは、デジタルデバイスによって提供され得る。さらなる実施形態によると、デジタルプロセッサ、メモリ、アナログフロントエンド、およびA D Cは、少なくとも1つのデジタルデバイスによって提供され得る。さらなる実施形態によると、デジタルデバイスは、マイクロコントローラを備え得る。さらなる実施形態によると、デジタルデバイスは、マイクロプロセッサ、デジタル信号プロセッサ、特定用途向け集積回路（A S I C）、およびプログラマブル論理アレイ（P L A）から成る群から選択され得る。

【0014】

10

20

30

40

50

さらなる実施形態によると、基板は、実質的に光透過性であり得、第1および第2の複数の電極は、インジウムスズ酸化物（ITO）を備え得る。さらなる実施形態によると、基板は、実質的に光透過性であり得、第1および第2の複数の電極は、アンチモンスズ酸化物（ATO）を備え得る。さらなる実施形態によると、基板は、4つの角を備え得る。

本発明は、例えば、以下を提供する。

(項目1)

タッチ感知表面上のタッチの場所およびその力を決定するための装置であって、

第1の軸を有し、平行配向に配列されている第1の複数の電極であって、前記第1の複数の電極の各々は、自己容量を備えている、第1の複数の電極と、

前記第1の軸に実質的に垂直な第2の軸を有し、平行配向に配列されている第2の複数の電極であって、前記第1の複数の電極は、前記第2の複数の電極の上に位置し、前記第1の複数の電極と第2の複数の電極との重複交差点を備えている複数のノードを形成し、前記複数のノードの各々は、相互容量を備えている、第2の複数の電極と、

基板であって、前記基板は、前記基板の上に配置されている前記第1および第2の複数の電極を有し、前記基板は、複数の角を有する、基板と、

複数の力センサであって、前記基板の各角は、前記複数の力センサのうちのそれぞれの1つに結合されている、力センサと

を備え、

前記複数の力センサの各々は、前記基板へのタッチ中、前記基板に加えられる力の一部を測定する、装置。

(項目2)

前記基板は、実質的に光透過性であり、前記第1および第2の複数の電極は、インジウムスズ酸化物（ITO）を備えている、項目1に記載の装置。

(項目3)

前記基板は、実質的に光透過性であり、前記第1および第2の複数の電極は、アンチモンスズ酸化物（ATO）を備えている、項目1に記載の装置。

(項目4)

前記基板は、4つの角を備えている、項目1に記載の装置。

(項目5)

タッチ感知表面上のタッチの場所およびその力を決定する方法であって、前記方法は、

第1の軸を有し、平行配向に配列されている第1の複数の電極を提供するステップであって、前記第1の複数の電極の各々は、自己容量を備えている、ステップと、

前記第1の軸に実質的に垂直な第2の軸を有し、平行配向に配列されている第2の複数の電極を提供するステップであって、前記第1の複数の電極は、前記第2の複数の電極の上に位置し、前記第1の複数の電極と第2の複数の電極との重複交差点を備えている複数のノードを形成し、前記複数のノードの各々は、相互容量を備えている、ステップと、

基板を提供するステップであって、前記基板は、前記基板の上に配置されている前記第1および第2の複数の電極を有し、前記基板は、複数の角を有する、ステップと、

複数の力センサを提供するステップであって、前記基板の各角は、前記複数の力センサのうちのそれぞれの1つに結合されている、ステップと、

前記第1の複数の電極を走査し、前記第1の複数の電極の自己容量の値を決定するステップと、

前記走査された自己容量の値を比較し、前記第1の複数の電極のうちのどれが自己容量の最も大きな値を有するかを決定するステップと、

自己容量の最も大きな値を有する前記第1の複数の電極のうちの1つのノードを走査し、それぞれの複数のノードの相互容量の値を決定するステップと、

自己容量の最も大きな値を有する前記第1の電極上の前記それぞれの複数のノードの走査された相互容量の値を比較するステップであって、前記相互容量の最も大きな値を有するノードは、前記タッチ感知表面上のタッチの場所である、ステップと、

前記複数の力センサによって測定された力値から、前記タッチ感知表面上の前記タッチ

10

20

30

40

50

の力を決定するステップと

を含む、方法。

(項目 6)

前記自己および相互容量値は、アナログフロントエンドおよびアナログ / デジタルコンバータ (ADC) を用いて測定される、項目 5 に記載の方法。

(項目 7)

前記自己および相互容量値は、デジタルデバイスのメモリ内に記憶されている、項目 6 に記載の方法。

(項目 8)

前記デジタルデバイス内のデジタルプロセッサは、前記タッチのタッチ場所と、前記タッチ場所において前記タッチ感知表面に対して前記タッチによって加えられた力とを決定することにおいて、前記記憶された自己および相互容量値を使用する、項目 7 に記載の方法。

(項目 9)

前記タッチ感知表面上のタッチの力を決定するステップは、前記複数の力センサによって測定される力値を一緒に加算することによって計算力点 (CFP) を決定するステップを含む、項目 5 に記載の方法。

(項目 10)

タッチ感知表面上の複数のタッチの場所およびそれらの組み合わせられた力を決定する方法であって、前記方法は、

第 1 の軸を有し、平行配向に配列されている第 1 の複数の電極を提供するステップであって、前記第 1 の複数の電極の各々は、自己容量を備えている、ステップと、

前記第 1 の軸に実質的に垂直な第 2 の軸を有し、平行配向に配列されている第 2 の複数の電極を提供するステップであって、前記第 1 の複数の電極は、前記第 2 の複数の電極の上に位置し、前記第 1 の複数の電極と第 2 の複数の電極との重複交差点を備えている複数のノードを形成し、前記複数のノードの各々は、相互容量を備えている、ステップと、

基板を提供するステップであって、前記基板は、前記基板の上に配置されている前記第 1 および第 2 の複数の電極を有し、前記基板は、複数の角を有する、ステップと、

複数の力センサを提供するステップであって、前記基板の各角は、前記複数の力センサのうちのそれぞれの 1 つに結合されている、ステップと、

前記第 1 の複数の電極を走査し、前記第 1 の複数の電極の自己容量の値を決定するステップと、

前記走査された自己容量の値を比較し、前記第 1 の複数の電極のうちのどの複数の電極が自己容量の最も大きな値を有するかを決定するステップと、

前記自己容量の最も大きな値を有する前記第 1 の複数の電極のうちの前記複数の電極のノードを走査し、それぞれの複数のノードの相互容量の値を決定するステップと、

前記自己容量の最も大きな値を有する前記第 1 の電極上のそれぞれの複数のノードの走査された相互容量の値を比較するステップであって、前記相互容量の最も大きな値を有する複数のノードは、前記タッチ感知表面上の複数のタッチの場所である、ステップと、

前記複数の力センサによって測定される力値から、前記タッチ感知表面上の前記複数のタッチの組み合わせられた力を決定するステップと

を含む、方法。

(項目 11)

前記自己および相互容量値は、アナログフロントエンドおよびアナログ / デジタルコンバータ (ADC) を用いて測定される、項目 10 に記載の方法。

(項目 12)

前記自己および相互容量値は、デジタルデバイスのメモリ内に記憶されている、項目 1 に記載の方法。

(項目 13)

前記デジタルデバイス内のデジタルプロセッサは、前記タッチのタッチ場所および前記

10

20

30

40

50

タッチ場所における前記タッチ感知表面に対する前記タッチによって加えられるそれぞれの力を決定することにおいて、前記記憶された自己および相互容量値を使用する、項目12に記載の方法。

(項目14)

前記タッチ感知表面上のタッチの組み合わせられた力を決定するステップは、前記複数の力センサによって測定された力値を一緒に加算することによって計算力点(CFP)を決定するステップと、前記タッチ場所および前記複数の力センサによって測定される力値を使用することによって、質量中心(CM)を決定するステップとを含む、項目10に記載の方法。

10

(項目15)

前記CMを決定するステップは、前記CFPのX-オフセットXRを決定するステップと、前記CFPのY-オフセットYRを決定するステップとを含む、項目14に記載の方法。

(項目16)

前記X-オフセットXRを決定するステップは、 $XR = ((F1 + F3) * (-W/2)) + ((F2 + F4) * (W/2)) / F_R$ を解法するステップを含み、式中、Wは、前記タッチ感知表面の面の幅であり、XRは、前記CMから前記CFPまでのXオフセットである、項目15に記載の方法。

20

(項目17)

前記Y-オフセットYRを決定するステップは、 $YR = ((F1 + F2) * (-H/2)) + ((F3 + F4) * (H/2)) / F_R$ を解法するステップを含み、式中、Hは、前記タッチ感知表面の面の高さであり、YRは、前記CMから前記CFPまでのYオフセットである、項目15に記載の方法。

(項目18)

タッチ感知表面上のタッチの場所およびそれらの組み合わせられた力を決定するためのシステムであって、前記システムは、

第1の軸を有し、平行配向に配列されている第1の複数の電極であって、前記第1の複数の電極の各々は、自己容量を備えている、第1の複数の電極と、

30

前記第1の軸に実質的に垂直な第2の軸を有し、平行配向に配列されている第2の複数の電極であって、前記第1の複数の電極は、前記第2の複数の電極の上に位置し、前記第1の複数の電極と第2の複数の電極との重複交差点を備えている複数のノードを形成し、前記複数のノードの各々は、相互容量を備えている、第2の複数の電極と、

基板であって、前記基板は、前記基板の上に配置されている前記第1および第2の複数の電極を有し、前記基板は、複数の角を有する、基板と、

複数の力センサであって、前記基板の各角は、前記複数の力センサのうちのそれぞれの1つに結合されている、力センサと、

デジタルプロセッサおよびメモリであって、前記デジタルプロセッサのデジタル出力は、前記第1および第2の複数の電極に結合されている、デジタルプロセッサおよびメモリと、

40

前記第1および第2の複数の電極と前記複数の力センサとに結合されているアナログフロントエンドと、

前記デジタルプロセッサに結合されている少なくとも1つのデジタル出力を有するアナログ/デジタルコンバータ(ADC)と

を備え、

前記自己容量の値は、前記第1の複数の電極の各々に対して、前記アナログフロントエンドによって測定され、

前記測定された自己容量の値は、前記メモリ内に記憶され、

自己容量の最も大きな値のうちの少なくとも1つを有する、前記第1の電極のうちの少

50

なくとも 1 つのノードの相互容量の値は、前記アナログフロントエンドによって測定され

る。前記測定された相互容量の値は、前記メモリ内に記憶され、

前記複数の力センサによって測定される力の値は、前記メモリ内に記憶され、

前記デジタルプロセッサは、前記記憶された自己および相互容量値を使用して前記タッチの場所を決定し、前記複数の力センサによって測定された力値から前記タッチ感知表面上の力点 ( CFP ) および質量中心 ( CM ) を計算する、

システム。

( 項目 19 )

前記デジタルプロセッサ、メモリ、アナログフロントエンド、および ADC は、デジタルデバイスによって提供される、項目 18 に記載のシステム。 10

( 項目 20 )

前記デジタルプロセッサ、メモリ、アナログフロントエンド、および ADC は、少なくとも 1 つのデジタルデバイスによって提供される、項目 18 に記載のシステム。

( 項目 21 )

前記デジタルデバイスは、マイクロコントローラを備えている、項目 19 に記載のシステム。

( 項目 22 )

前記デジタルデバイスは、マイクロプロセッサ、デジタル信号プロセッサ、特定用途向け集積回路 ( ASIC ) 、およびプログラマブル論理アレイ ( PLA ) から成る群から選択される、項目 19 に記載のシステム。 20

( 項目 23 )

前記基板は、実質的に光透過性であり、前記第 1 および第 2 の複数の電極は、インジウムスズ酸化物 ( ITO ) を備えている、項目 18 に記載のシステム。

( 項目 24 )

前記基板は、実質的に光透過性であり、前記第 1 および第 2 の複数の電極は、アンチモンスズ酸化物 (ATO) を備えている、項目 18 に記載のシステム。

( 項目 25 )

前記基板は、4 つの角を備えている、項目 18 に記載のシステム。

【 図面の簡単な説明 】

【 0015 】

本開示のより完全な理解は、付随の図面と関連して想定される以下の説明を参照することによって得られ得る。

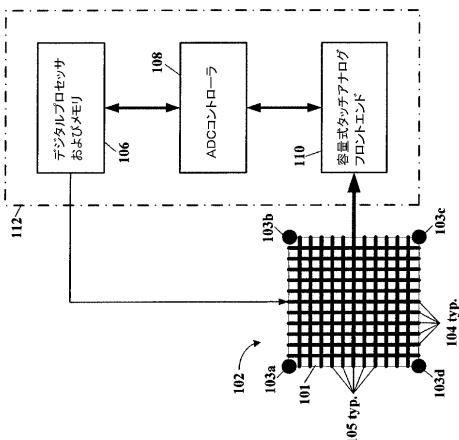

【 図 1 】図 1 は、本開示の実施形態による、容量式タッチおよび力センサ、容量式タッチアナログフロントエンド、およびデジタルプロセッサを有する、電子システムの概略プロック図を図示する。

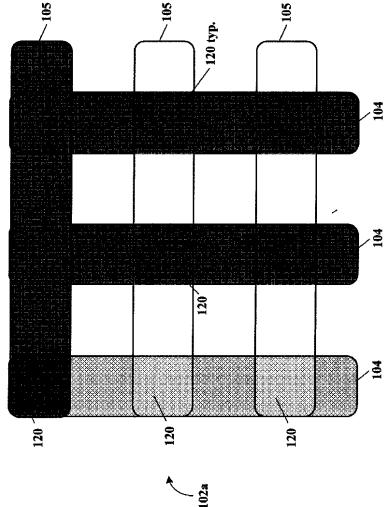

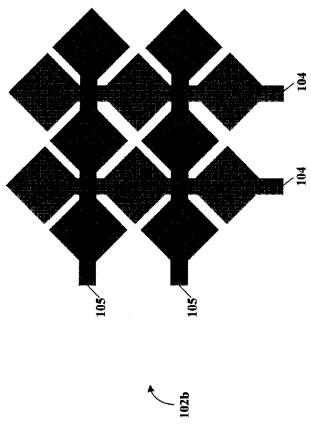

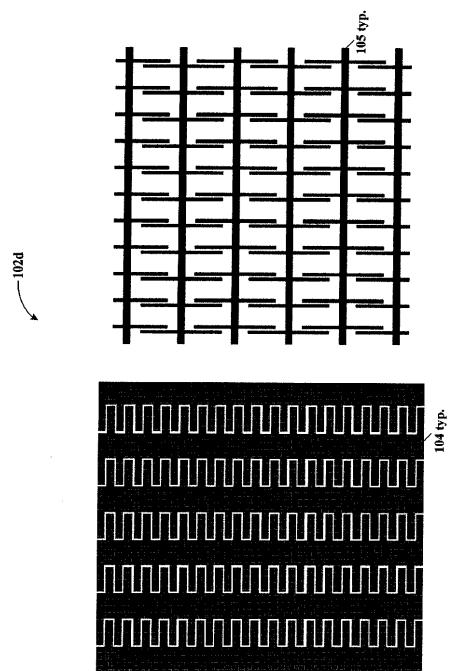

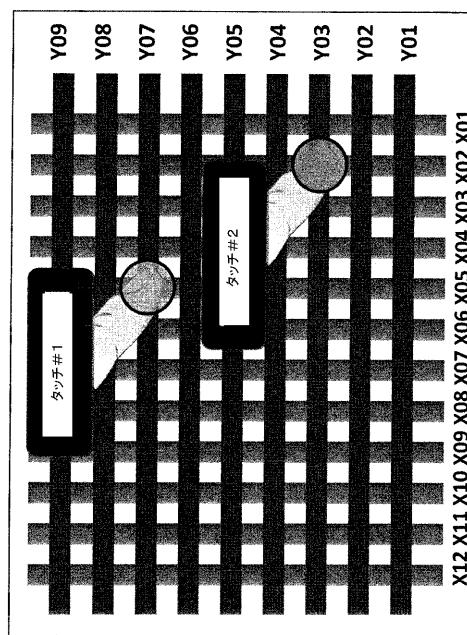

【 図 2 A 】図 2 A - 2 D は、本開示の教示による、種々の容量式タッチセンサ構成を有する、タッチセンサの基本構想図を図示する。

【 図 2 B 】図 2 A - 2 D は、本開示の教示による、種々の容量式タッチセンサ構成を有する、タッチセンサの基本構想図を図示する。 40

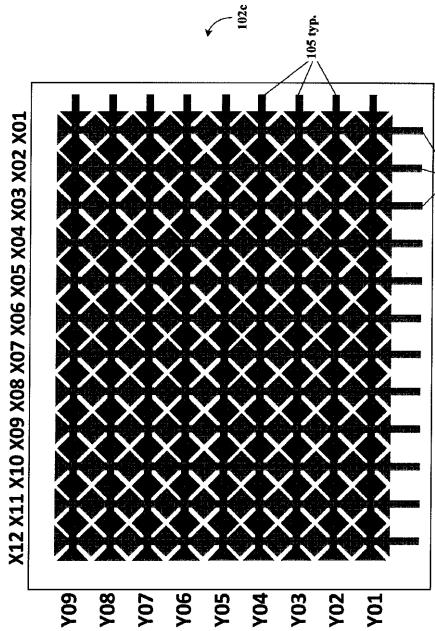

【 図 2 C 】図 2 A - 2 D は、本開示の教示による、種々の容量式タッチセンサ構成を有する、タッチセンサの基本構想図を図示する。

【 図 2 D 】図 2 A - 2 D は、本開示の教示による、種々の容量式タッチセンサ構成を有する、タッチセンサの基本構想図を図示する。

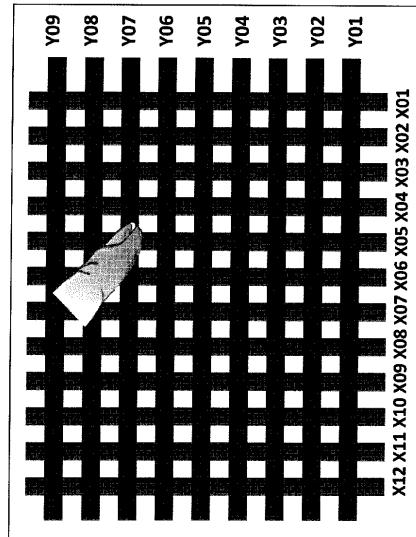

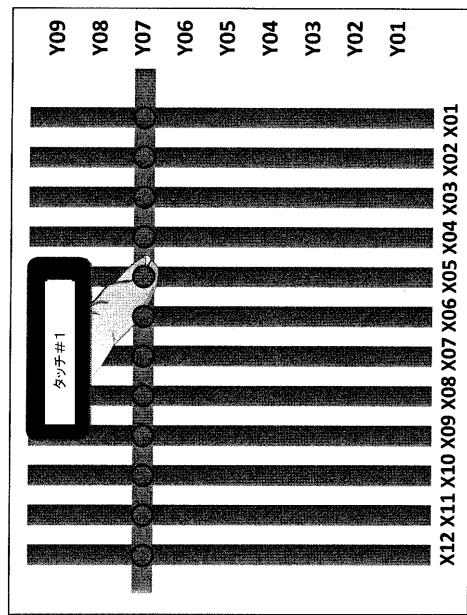

【 図 3 】図 3 および 4 は、本開示の教示による、タッチセンサへの單一タッチの自己および相互容量式タッチ検出の基本構想図を図示する。

【 図 4 】図 3 および 4 は、本開示の教示による、タッチセンサへの單一タッチの自己および相互容量式タッチ検出の基本構想図を図示する。

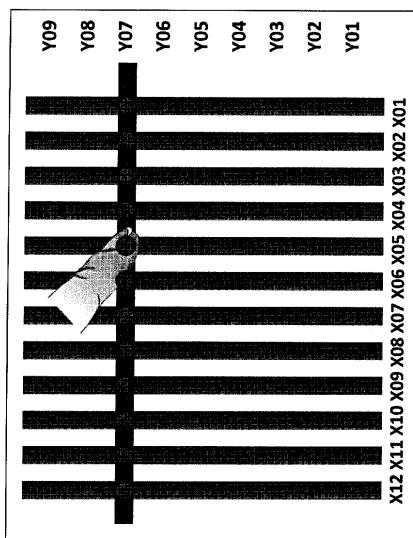

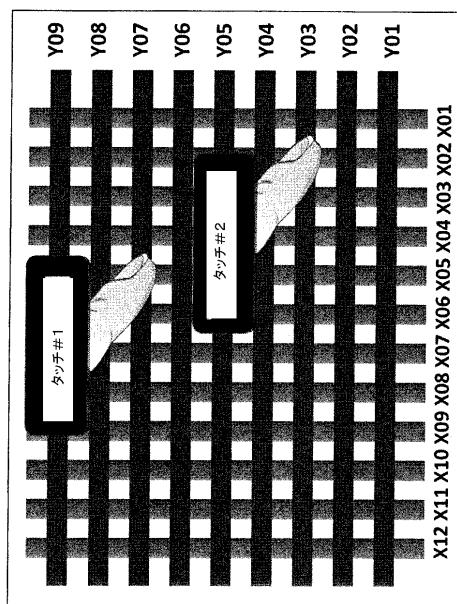

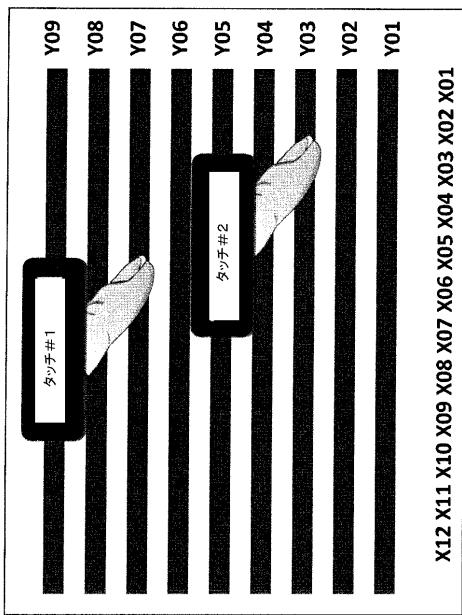

【 図 5 】図 5 - 9 は、本開示の教示による、タッチセンサへの 2 つのタッチの自己および相互容量式タッチ検出の基本構想図を図示する。 50

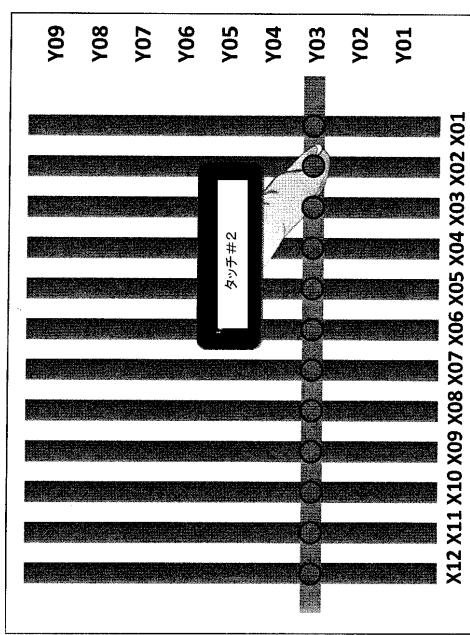

【図6】図5-9は、本開示の教示による、タッチセンサへの2つのタッチの自己および相互容量式タッチ検出の基本構想図を図示する。

【図7】図5-9は、本開示の教示による、タッチセンサへの2つのタッチの自己および相互容量式タッチ検出の基本構想図を図示する。

【図8】図5-9は、本開示の教示による、タッチセンサへの2つのタッチの自己および相互容量式タッチ検出の基本構想図を図示する。

【図9】図5-9は、本開示の教示による、タッチセンサへの2つのタッチの自己および相互容量式タッチ検出の基本構想図を図示する。

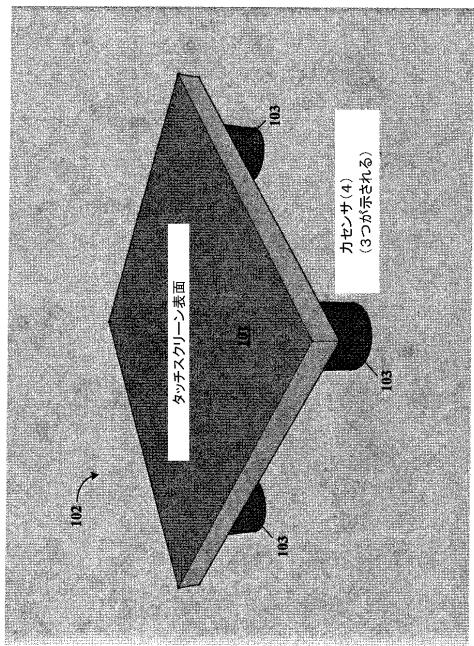

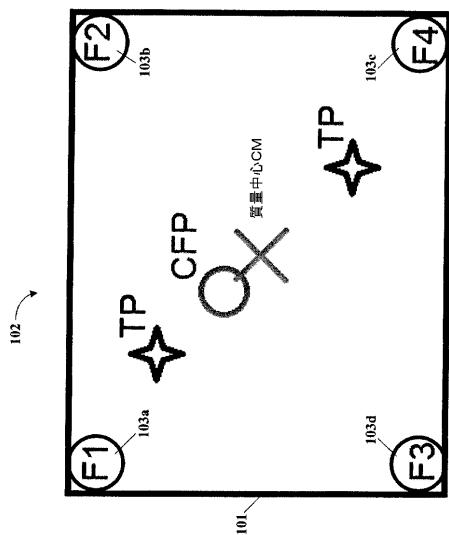

【図10】図10は、本開示のある実施形態による、タッチセンサの表面上のそこへのタッチの場所およびそれらのタッチの力の両方を検出可能なタッチセンサの概略斜視図を図示する。

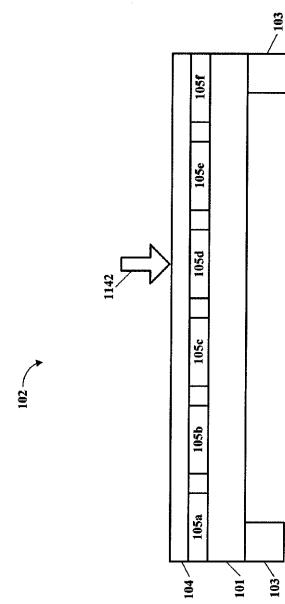

【図11】図11は、本開示のある実施形態による、タッチセンサの表面上のそこへのタッチの場所およびそれらのタッチの力の両方を検出可能なタッチセンサの概略立面図を図示する。

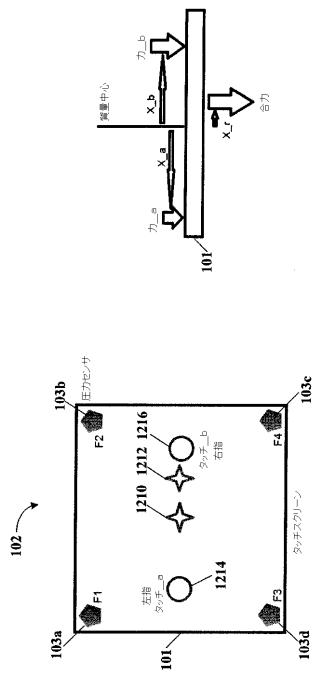

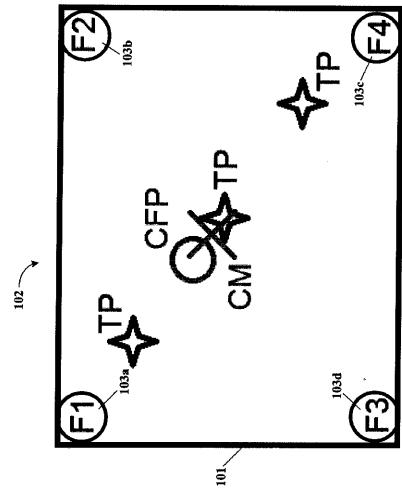

【図12】図12は、本開示の教示による、2つの同時タッチ点、結果として生じるその幾何学中心、およびタッチセンサ面に対する合力を示す、タッチセンサの概略平面および立面図を図示する。

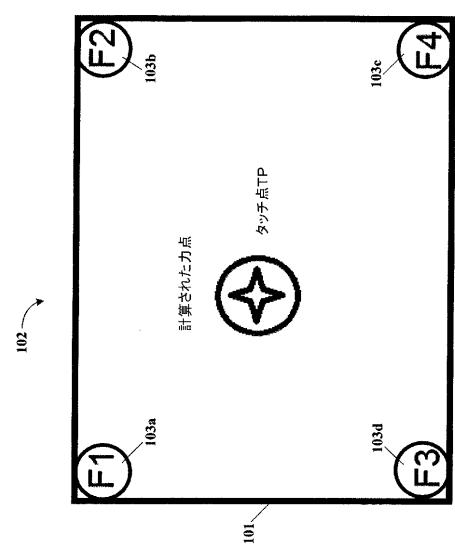

【図13】図13は、本開示の教示による、単一タッチ点およびタッチセンサ面に対する合力を示すタッチセンサ面の基本構想図を図示する

【図14】図14は、本開示の教示による、2つの同時タッチ点およびタッチセンサ面に対して結果として生じる組み合わせられた力を示すタッチセンサ面の基本構想図を図示する。

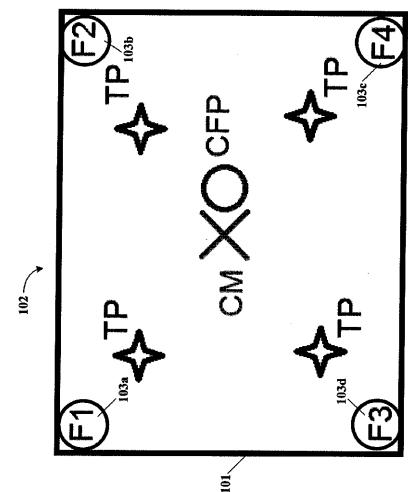

【図15】図15は、本開示の教示による、3つの同時タッチ点およびタッチセンサ面に対して結果として生じる組み合わせられた力を示すタッチセンサ面の基本構想図を図示する。

【図16】図16は、本開示の教示による、4つの同時タッチ点およびタッチセンサ面に対して結果として生じる組み合わせられた力を示すタッチセンサ面の基本構想図を図示する。

#### 【発明を実施するための形態】

##### 【0016】

本開示は、種々の修正を受け、代替形態であり得るが、その具体的例示的実施形態が、図面に図示され、本明細書に詳細に説明されている。しかしながら、具体的例示的実施形態の本明細書における説明は、本開示を本明細書に開示される特定の形態に限定することを意図するものではなく、対照的に、本開示は、添付の請求項によって定義されるあらゆる修正および均等物を対象とすることを理解されたい。

##### 【0017】

種々の実施形態によると、タッチセンサは、基板の表面上に、複数の伝導性電極行と、複数の伝導性電極行に実質的に垂直であり、かつその上にある複数の伝導性電極列とを有する基板と、基板の各角における力または圧力センサとを備え得る。用語「力」および「圧力」は、本明細書では、同じ意味で使用されるであろう。タッチがタッチセンサの表面に加えられると、タッチセンサの表面に対するタッチの場所に近接する、電極行と列との交差点によって形成されるコンデンサの容量値が変化するであろう。タッチセンサの表面へのタッチを決定する本方法は、「投影容量式（P C A P）タッチ」と呼ばれ、www.microchip.comにおいて利用可能なTodd O'ConnorによるTechnical Bulletin TB3064、Jerry Hanauerによる「mTouch™ Projected Capacitive Touch Screen Sensing Theory of Operation」と、共有に係る米国特許出願公開第US2012/0113047号「Capacitive Touch System Using Both Self and Mutual Capacitance」とにより完全に説明されており、両方とも、あらゆる目的のために、参照

10

20

30

40

50

することによって本明細書に組み込まれる。タッチセンサは、スマートフォン、タブレットコンピュータ、コンピュータディスプレイ、および、自動車、飛行機およびボートの情報および制御ディスプレイ等において使用されるタッチスクリーンディスプレイの中に組み込まれ得る。

【0018】

力または圧力センサは、タッチセンサ基板の各角に位置し得る。これらの力センサは、タッチセンサ基板上の合計力および比例力を検出する。この力情報は、次いで、事前に決定されたタッチ場所と組み合わせられ、個々のタッチ力は、次いで、3次元（3D）ジェスチャ用途のための十分な分解能で補間されることが可能である。例えば、正方形または長方形タッチセンサ基板に対して、1つ以上のタッチがタッチセンサ基板の表面に行われる度に、基板の各角に1つずつ力センサが位置する4つの力センサに力が加えられる。各力センサにおける力は、1つ以上のタッチのタッチセンサの表面上の場所に依存する。単一タッチがタッチセンサの表面に加えられるとき、4つのタッチセンサからの力情報は、単一タッチの力を決定するために使用され得る。2つのタッチがタッチセンサ基板の表面に加えられるとき、4つのタッチセンサからの力情報は、2つのタッチの既知の位置に基づいて、加えられた力を補間するために使用され得る。3つ以上のタッチがタッチセンサ基板の表面に加えられるとき、4つのタッチセンサからの力情報は、タッチ場所間の圧力バイアスを決定するために使用され得る。

【0019】

1つ以上のタッチから結果として生じる力情報は、有利には、タッチスクリーンまたはパネルの各角に1つずつの4つのタッチセンサと組み合わせて2次元タッチスクリーンまたはパネルのみを使用して、3次元（3D）ジェスチャ認識のための情報および特徴を提供するために使用されることが可能である3次元の情報を決定し、利用するために使用され得る。これは、タッチスクリーンまたはパネルのディスプレイ部分の視覚的明確性に影響を及ぼさずに、タッチスクリーンまたはパネル上のジェスチャコマンドの帯域幅、複雑性、および機能性の増加を可能にする。

【0020】

次に、図面を参照すると、具体的な例示的実施形態の詳細が、図式的に図示される。図面中の同一要素は、同一番号によって表され、類似要素は、異なる小文字の添え字を伴う同一番号によって表されるであろう。

【0021】

図1を参照すると、描寫されるのは、本開示の教示による、容量式タッチセンサと、容量式タッチアナログフロントエンドと、デジタルプロセッサとを有する電子システムの概略ブロック図である。デジタルデバイス112は、デジタルプロセッサおよびメモリ106と、アナログ/デジタルコンバータ（ADC）コントローラ108と、容量式タッチアナログフロントエンド（AFE）110とを備え得る。デジタルデバイス112は、その上にマトリクスで配列された複数の伝導性列104および行105を有する基板101と、基板101の各角に1つずつのセンサ103である4つの力センサ103とから成るタッチセンサ102に結合され得る。伝導性行105および/または伝導性列104は、例えば、限定ではないが、クリア基板（例えば、ディスプレイ/タッチスクリーン等）上の印刷回路基板導体、ワイヤ、インジウムスズ酸化物（ITO）もしくはアンチモンスズ酸化物（ATO）コーティング、または任意のそれらの組み合わせであり得ることが想定され、これは、本開示の範囲内である。デジタルデバイス112は、マイクロコントローラ、マイクロプロセッサ、デジタル信号プロセッサ、特定用途向け集積回路（ASIC）、プログラマブル論理アレイ（PLA）等を備え得、さらに、パッケージ化または非パッケージ化された1つ以上の集積回路（図示せず）を備え得る。

【0022】

図2Aから2Dを参照すると、描寫されるのは、本開示の教示による、種々の容量式タッチセンサ構成を有する、タッチセンサの基本構造である。図2Aは、伝導性列104および伝導性行105を示す。伝導性列104の各々は、休止状態である場合、または、

10

20

30

40

50

伝導性列 104 の各 1 つがその自己容量が測定されている間、伝導性行 105 が全て能動的に励起され得る場合に個々に測定され得る「自己容量」を有する。伝導性行 105 の全ての能動的励起は、伝導性列 104 の個々の容量測定のためのより強い測定信号を提供し得る。

【0023】

例えは、自己容量走査中、伝導性列 104 のうちの 1 つ上で検出されたタッチが存在する場合、その上で検出されたタッチを有するその伝導性列 104 のみ、それらの相互容量走査中にさらに測定される必要がある。自己容量走査は、伝導性列 104 のうちのどれがタッチされたかのみを決定し得、タッチされたその伝導性列 104 の軸に沿った場所は決定しない。相互容量走査は、1 つずつ、伝導性行 105 を個々に励起（駆動）し、伝導性行 105 に交わる（それを交差する）その伝導性列 104 上の場所の各 1 つに対する相互容量値を測定することによって、その伝導性列 104 の軸に沿ったタッチ場所を決定し得る。伝導性列 104 と伝導性行 105 との間に、絶縁非伝導性誘電体（図示せず）が存在し、それらを分離し得る。伝導性列 104 が、伝導性行 105 に交わる（それを交差する）場合、それによって、相互コンデンサ 120 が形成される。前述の自己容量走査の間、伝導性行 105 全ては、論理信号によって、例えは、 $V_{SS}$  に接地されるか、またはある電圧、例えは、 $V_{DD}$  まで駆動され、それによって、伝導性列 104 の各 1 つに関連付けられた個々の列コンデンサを形成し得る。

【0024】

図 2B および 2C は、伝導性列 104 および伝導性行 105 の菱形パターンのインターリービングを示す。この構成は、伝導性列 104 と伝導性行 105 との間により僅かな重複を伴って、タッチに対する各軸伝導性列および / または行のばく露（例えは、より優れた感度）を最大限にし得る。図 1D は、串状の絡み合った指を備えている受信機（上部）伝導性行（例えは、電極）105a および送信機（底部）伝導性列 104a を示す。伝導性列 104a および伝導性行 105a は、隣り合った平面図に示されるが、通常、上部伝導性行 105a は、底部伝導性列 104a の上に存在するであろう。

【0025】

図 3 および 4 を参照すると、描寫されるのは、本開示の教示による、タッチセンサへの單一タッチの自己および相互容量式タッチ検出の基本構想図である。図 3 では、指の一部の写真によって表される、タッチが、ほぼ X05、Y07 の座標にある。自己容量式タッチ検出の間、行 Y01 から Y09 の各 1 つが、その容量値を決定するために測定され得る。行 Y01 から Y09 の各 1 つに対するそれへのタッチを伴わない基線容量値が得られており、メモリ（例えは、メモリ 106 - 図 1）に記憶されていることに留意されたい。行 Y01 から Y09 の基線容量値に対するいかなる有意な容量変化も、明白であり、指タッチとして見なされるであろう。図 3 に示される実施例では、指は、行 Y07 をタッチしており、その行の容量値が変化し、それへのタッチを示すであろう。しかしながら、タッチが生じたこの行上の場所は、依然として、自己容量測定からは不明である。

【0026】

タッチされた行（Y07）が、その自己容量変化を使用して決定されると、相互容量検出が、タッチされた行（Y07）上のタッチが生じた場所を決定する際に使用され得る。これは、列 X01 から X12 の各々が、個々に励起されているときの行 Y07 の容量値を測定しながら、1 つずつ、列 X01 から X12 の各々を励起する（例えは、電圧パルスをかける）ことによって達成され得る。行 Y07 の容量値の最大変化を生じさせる列（X05）励起は、列 X05 と行 Y07 の交差点に対応するその行上の場所であり、したがって、單一タッチは、点またはノード X05、Y07 においてである。自己および相互容量式タッチ検出を使用することは、タッチセンサ 102 上の X、Y タッチ座標を得るための行および列走査の数を有意に低減させる。この例では、合計  $9 + 12 = 21$  回の走査回数に対して、9 つの行が自己容量式タッチ検出の間に走査され、12 の列が相互容量式タッチ検出の間に走査された。各ノード（場所）に対して、個々の x - y 容量式タッチセンサが使用される場合、 $9 \times 12 = 108$  回の走査回数がこの 1 つのタッチを見つけるために必

10

20

30

40

50

要となり、これは、有意な差異である。列 X 0 1 から X 2 1 の自己容量が、最初に決定され、次いで、相互容量が、各行 Y 0 1 から Y 0 9 を励起し、選択された列上のタッチ場所を見出すことによって、選択された列から決定され得ることも想定され、これは、本開示の範囲内である。

#### 【 0 0 2 7 】

図 5 から 9 を参照すると、描写されるのは、本開示の教示による、タッチセンサに対する 2 つのタッチの自己および相互容量式タッチ検出の基本構想図である。図 5 では、2 本の指の一部の写真によって表される、2 つのタッチは、タッチ # 1 の場合、ほぼ X 0 5 、 Y 0 7 の座標にあり、タッチ # 2 の場合、ほぼ X 0 2 、 Y 0 3 にある。自己容量式タッチ検出の間、行 Y 0 1 から Y 0 9 の各 1 つが、その容量値を決定するために測定され得る。行 Y 0 1 から Y 0 9 の各 1 つに対するそれへのタッチを伴わない基線容量値が得られており、メモリ（例えば、メモリ 1 0 6 - 図 1 ）に記憶されていることに留意されたい。行 Y 0 1 から Y 0 9 の基線容量値に対するいかなる有意な容量変化も、明白であり、指タッチとして見なされるであろう。図 6 に示される例では、第 1 の指は、行 Y 0 7 をタッチしており、第 2 の指は、行 Y 0 3 をタッチしており、それらの 2 つの行の容量値が変化し、それへのタッチを示すであろう。しかしながら、これらの 2 つの行上のタッチが生じた場所は、依然として、自己容量測定からは不明である。

#### 【 0 0 2 8 】

タッチされた行（ Y 0 7 および Y 0 3 ）が、その自己容量変化を使用して決定されると、相互容量検出が、タッチが生じたこれらの 2 つのタッチされた行（ Y 0 7 および Y 0 3 ）上の場所を決定する際に使用され得る。図 7 を参照すると、これは、例えば、列 X 0 1 から X 1 2 の各々が、個々に励起されるときの行 Y 0 7 の容量値を測定しながら、1 つずつ、列 X 0 1 から X 1 2 の各々を励起する（例えば、それに電圧パルスをかける）ことによって達成され得る。行 Y 0 7 の容量値の最大変化を生じさせる列（ X 0 5 ）励起は、列 X 0 5 と行 Y 0 7 の交差点に対応するその行上の場所であろう。図 8 を参照すると、同様に、列 X 0 1 から X 1 2 の各々が個々に励起されているときの行 Y 0 3 の容量値を測定することによって、タッチ # 2 が生じた列 Y 0 3 上の場所が決定される。図 9 を参照すると、2 つのタッチは、点またはノード（ X 0 5 、 Y 0 7 ）および（ X 0 2 、 Y 0 3 ）にある。選択された行の 1 つ以上（例えば、 Y 0 7 および Y 0 3 ）の容量が同時に測定されることができる場合、1 組のみの個々の列 X 0 1 から X 1 2 励起が、タッチセンサ 1 0 2 に対する 2 つのタッチを決定する際に必要とされることも想定され、これは、本開示の範囲内である。

#### 【 0 0 2 9 】

投影容量式（ P C A P ）タッチシステムを使用した多重タッチ検出およびジェスチャは、 Jerry Hanauer による共有に係る米国特許出願公開第 U S 2 0 1 2 / 0 1 1 3 0 4 7 号「 C a p a c i t i v e T o u c h S y s t e m U s i n g B o t h S e l f a n d M u t u a l C a p a c i t a n c e 」と、 Lance Lamont および Jerry Hanauer による 2 0 1 3 年 3 月 1 4 日に出願された米国特許出願第 1 3 / 8 3 0 , 8 9 1 号「 M e t h o d A n d S y s t e m F o r M u l t i - T o u c h D e c o d i n g 」とにより完全に説明されており、両方とも、あらゆる目的のために、参照することによって本明細書に組み込まれる。

#### 【 0 0 3 0 】

図 1 0 および 1 1 を参照すると、描写されるのは、それぞれ、本開示のある実施形態による、タッチセンサの表面上のそこへのタッチの場所およびそれらのタッチの力の両方を検出可能なタッチセンサの概略斜視および立面図である。概して、番号 1 0 2 によって表される、そこへのタッチの場所とそこへのそのタッチの力の両方を検出可能なタッチセンサは、基板 1 0 1 上の複数の伝導性行 1 0 5 および列 1 0 4 と、力センサ 1 0 3 が 1 つずつ基板の各角 1 0 1 に位置する力センサ 1 0 3 とを備え得る。伝導性列 1 0 4 および伝導性行 1 0 5 は、本明細書の上記でより完全に説明されるように、タッチの場所を決定する際に使用され、力センサ 1 0 3 は、基板 1 0 1 に加えられている力 1 1 4 2 の量を検出する

10

20

30

40

50

るために使用される。基板 101 は、透明、半透明、または不透明、もしくは任意のそれらの組み合わせであり得る。視覚的変位は、情報および画像をユーザに供給するために、基板 101 内に含まれるかまたはそれを通して投影し得、タッチセンサ 102 のタッチおよび / またはジェスチャ動作の間、視覚的フィードバックを提供し得る。4つより多いまたはより少ない力センサ 103 が、本開示の教示に従って、使用用途のために適切な基板 101 の任意の幾何学形状とともに使用され得ることが想定され、かつ本開示の範囲内である。

#### 【0031】

図 1 に従って参考すると、マイクロコントローラ 112 は、ここでは、そのような容量値変化の検出および評価を向上させる周辺機器を含む。種々の容量式タッチシステムの用途のより詳細な説明は、www.microchip.comにおいて利用可能な Microchip Technology Incorporated アプリケーションノート AN1298、AN1325、および AN1334 により完全に開示されており、全て、あらゆる目的のために、参考することによって本明細書に組み込まれる。そのような用途の 1 つは、容量式分圧器 (CVD) 法を利用し、容量値を決定し、および / または容量値が変化したかどうかを評価することである。CVD 法は、www.microchip.comにおいて利用可能なアプリケーションノート AN1208 により完全に説明されており、CVD 法のより詳細な説明は、Dieter Peter による共有に係る米国特許出願公開第 US2010/0181180 号「Capacitive Touch Sensing using an Internal Capacitor of an Analog-To-Digital Converter (ADC) and a Voltage Reference」に提示されており、両方とも、あらゆる目的のために、参考することによって本明細書に組み込まれる。

#### 【0032】

充電時間測定ユニット (CTMU) が、非常に正確な容量測定のために使用され得る。CTMU は、www.microchip.comにおいて利用可能なアプリケーションノート AN1250 および AN1375 と、両方とも James E. Bartling による、共有に係る米国特許第 US7,460,441 B2 号「Measuring along time period」および第 US7,764,213 B2 号「Current-time digital-to-analog converter」とにより完全に説明されており、全て、あらゆる目的のために、参考することによって本明細書に組み込まれる。

#### 【0033】

必要分解能を有する任意のタイプの容量測定回路が、複数の伝導性列 104 および / または行 105 の容量値を決定する際に使用され得、電子機器の当業者および本開示の利益を有する者は、そのような容量測定回路を実装し得ることが想定され、本開示の範囲内である。

#### 【0034】

図 12 を参考すると、描写されるのは、本開示の教示による、2つの同時タッチ点、結果として生じるその幾何学中心、およびタッチセンサ面に対する合力を示すタッチセンサの概略平面および立面図である。基板の各角 101 に1つずつ位置する4つの力センサ 103a - 103d は、タッチセンサ基板 101 上の合計釣り合い力を提供する。タッチ力バイアスは、タッチの集団の幾何学中心 (タッチ点) と個々の指の圧力レベルによって発生される合力 (計算力点) との間のオフセット、ならびに力の大きさとして定義される。例えば、図 12 に示されるのは、2つの指のタッチであり、左指圧力 (タッチ点 1214) は、右指圧力 (タッチ点 1216) より小さい。これらの2つの指タッチ間の幾何学中心は、2つのタッチ点 1214 と 1216 との間に位置する、質量中心 (CM) 1210 によって表され得る。

#### 【0035】

4つのセンサ 103a - 103d が、合力、例えば、タッチ点 1214 および 1216

10

20

30

40

50

における2つのタッチから生じる計算力点(CFP)1212を決定するために使用され得る。合力(CFP1212)は、センサ103の各々における圧力(力)を使用して、2次元計算を用いて決定され得る。4つのセンサ103への力は、全タッチ場所におけるユーザの指圧力によって発生される合計力を提供する。場所は、例えば、限定ではないが、XおよびYの合力計算によって決定される。合力(CFP1212)を計算するために、XおよびY座標系は、タッチセンサ上に重ねられ得、画面の質量中心にゼロを伴う。合力ベクトルは、次いで、以下の方程式において使用され得る。

#### 【0036】

合計の合力 $F_R$ 、(CFP1212)は、以下のように計算され得る。

$$F_R = F_1 + F_2 + F_3 + F_4 \quad (\text{方程式1})$$

10

式中、 $F_1$ 、 $F_2$ 、 $F_3$ 、および $F_4$ は、それぞれのセンサ103の各々によって測定された力である。

#### 【0037】

合計の合力 $F_R$ (CFP1212)のX-オフセット $X_R$ は、以下のように計算され得る。

$$F_R * X_R = ((F_1 + F_3) * (-W/2)) + ((F_2 + F_4) * (W/2)) \quad (\text{方程式2})$$

式中、 $W$ は、タッチセンサ102の面の幅であり、 $X_R$ は、質量中心(CM1210)から合力(CFP1212)までのXオフセットである。

#### 【0038】

合計の合力 $F_R$ (CFP1212)のY-オフセット $Y_R$ は、以下のように計算され得る。

$$F_R * Y_R = ((F_1 + F_2) * (-H/2)) + ((F_3 + F_4) * (H/2)) \quad (\text{方程式3})$$

20

式中、 $H$ は、タッチセンサ102の面の高さであり、 $Y_R$ は、質量中心(CM1210)から合力(CFP1212)までのYオフセットである。

#### 【0039】

幾何学中心は、次いで、同一X-Y座標系を使用することによって、計算され得る。合力の場所対幾何学中心を比較すると、2つのバイアス解が生じ得る。

1. 合力と幾何学中心とが一致し、押圧は、垂直移動であり得る。押圧は、多重ページドキュメントを通して検索するために、ページを挿入するために、またはオブジェクトを定位に固定するために使用され得る。

30

2. 合力は、幾何学中心からオフセットされ、押圧は、合力と幾何学中心との間の線に垂直な軸を中心とする回転移動である。回転度は、合力の大きさによって決定され得る。これは、オブジェクトを種々の軸で回転させるために機能する。

#### 【0040】

これらのバイアス解は、次いで、現在の押圧の履歴(経時的圧力増加またはタッチの移動)と組み合わせられ、いくつかの可能なジェスチャのうちのどれが生成されているかを決定し得る。他のバイアス解も、可能であり、本明細書で想定される。

#### 【0041】

図13を参照すると、描写されるのは、本開示の教示による、単一タッチ点およびタッチセンサ面に対する合力を示すタッチセンサ面の基本構想図である。4つの力センサ103は、タッチセンサ基板101の角に位置する。力センサ103は、タッチセンサ基板101上の合計釣り合い力を提供する。タッチセンサ103からの力情報およびタッチセンサ上の事前に決定されたタッチ点(TP)は、計算力点(CFP)を決定するために使用される。

40

#### 【0042】

図14を参照すると、描写されるのは、本開示の教示による、2つの同時タッチ点およびタッチセンサ面に対して結果として生じる組み合わせられた力を示すタッチセンサ面の基本構想図である。4つの力センサ103は、タッチセンサ基板101の角に位置する。

50

力センサ 103 は、タッチセンサ基板 101 上の合計釣り合い力を提供する。タッチセンサ 103 からの力情報およびタッチセンサ上の事前に決定されたタッチ点 (TP) は、質量中心 (CM) および計算力点 (CFP) を決定するために使用される。

#### 【0043】

図 15 を参照すると、描写されるのは、本開示の教示による、3つの同時タッチ点およびタッチセンサ面に対して結果として生じる組み合わせられた力を示すタッチセンサ面の基本構想図である。4つの力センサ 103 は、タッチセンサ基板 101 の角に位置する。力センサ 103 は、タッチセンサ基板 101 上の合計釣り合い力を提供する。タッチセンサ 103 からの力情報およびタッチセンサ上の事前に決定されたタッチ点 (TP) は、質量中心 (CM) および計算力点 (CFP) を決定するために使用される。

10

#### 【0044】

図 16 を参照すると、描写されるのは、本開示の教示による、4つの同時タッチ点およびタッチセンサ面に対して結果として生じる組み合わせられた力を示すタッチセンサ面の基本構想図である。4つの力センサ 103 は、タッチセンサ基板 101 の角に位置する。力センサ 103 は、タッチセンサ基板 101 上の合計釣り合い力を提供する。タッチセンサ 103 からの力情報およびタッチセンサ上の事前に決定されたタッチ点 (TP) は、質量中心 (CM) および計算力点 (CFP) を決定するために使用される。

#### 【0045】

4つより多いタッチ場所が検出され得、その CFP および CM は、4つより多いまたはより少ない力センサ 103 を使用して決定されることも想定され、本開示の範囲内である。加えて、力センサ基板 101 は、使用用途のための任意の適切な幾何学形状であり得る。

20

#### 【0046】

本開示の実施形態が、描写され、説明され、本開示の例示的実施形態を参照することによって定義されるが、そのような参照は、本開示の限定を含意するものではなく、そのような限定が、推測されるべきではない。開示される主題は、それらの当業者および本開示の利益を有するものに想起されるであろうように、形態および機能における多数の修正、改変、ならびに均等物が可能である。本開示の描写および説明される実施形態は、実施例にすぎず、本開示の範囲の包括ではない。

【図1】

【図2A】

Figure 2A

【図2B】

Figure 2B

【図2C】

Figure 2C

【図2D】

Figure 2D

【図3】

Figure 3

【図4】

Figure 4

【図5】

Figure 5

【図6】

Figure 6

【図7】

Figure 7

【図8】

Figure 8

【図9】

Figure 9

【図10】

Figure 10

【図11】

Figure 11

【図12】

Figure 12

【図13】

Figure 13

【図 1 4】

Figure 14

【図 1 5】

Figure 15

【図 1 6】

Figure 16

---

フロントページの続き

(72)発明者 ハノーアー, ジェリー

アメリカ合衆国 ウィスコンシン 53022, ジャーマンタウン, カントリー コート エ

ヌ 103ダブリュー 16737

(72)発明者 カーティス, キース イー.

アメリカ合衆国 アリゾナ 85297, ギルバート, イースト ロス アルトス 3305

審査官 星野 裕

(56)参考文献 米国特許出願公開第2013/0257799(US, A1)

米国特許出願公開第2011/0141053(US, A1)

特開2014-044708(JP, A)

米国特許出願公開第2012/0056837(US, A1)

特開2013-222450(JP, A)

特表2013-539580(JP, A)

特表2013-513870(JP, A)

特開2010-244252(JP, A)

米国特許出願公開第2010/0229091(US, A1)

特開2013-242699(JP, A)

米国特許出願公開第2013/0307821(US, A1)

米国特許出願公開第2012/0194474(US, A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 3 / 041

G 06 F 3 / 044