(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5515216号

(P5515216)

(45) 発行日 平成26年6月11日(2014.6.11)

(24) 登録日 平成26年4月11日(2014.4.11)

(51) Int.Cl.

H03L 7/22 (2006.01)

H03L 7/10 (2006.01)

F 1

H03L 7/22

H03L 7/10

Z

請求項の数 14 外国語出願 (全 13 頁)

(21) 出願番号 特願2007-341739 (P2007-341739)

(22) 出願日 平成19年12月11日 (2007.12.11)

(65) 公開番号 特開2008-148346 (P2008-148346A)

(43) 公開日 平成20年6月26日 (2008.6.26)

審査請求日 平成22年12月6日 (2010.12.6)

(31) 優先権主張番号 11/637,254

(32) 優先日 平成18年12月11日 (2006.12.11)

(33) 優先権主張国 米国(US)

(73) 特許権者 504441048

シリコン イメージ、インコーポレイテッド

アメリカ合衆国 カリフォルニア州 94

085 サニーベイル イースト アーケ

ス アベニュー 1140

(74) 代理人 100110928

弁理士 速水 進治

(74) 代理人 100127236

弁理士 天城 聰

(74) 代理人 100149696

弁理士 田中 俊夫

最終頁に続く

(54) 【発明の名称】フィードフォワード分割器を有する適応帯域幅位相ロックループ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1及び第2のサブ位相ロックループ(サブPLL)であって、第1及び第2の電圧制御式発振器(VCO)出力信号を供給する第1及び第2のVCOと、該第1及び第2のVCO出力信号の第1及び第2の周波数を可変の第1及び第2の分周率によって分割し、前記第1のサブPLLから第1の出力クロック信号を生成し、前記第2のサブPLLから第2の出力クロック信号を生成する第1及び第2のフィードフォワード分割回路とを含む第1及び第2のサブ位相ロックループ(サブPLL)と、

前記第1及び第2の分周率を選択し、前記第1のサブPLLからの前記第1の出力クロック信号又は前記第2のサブPLLからの前記第2の出力クロック信号のいずれかを出力信号として選択する位相ロックループ(PLL)制御回路であって、前記第1の出力クロック信号、前記第2の出力クロック信号、前記第1のサブPLLの前記第1のVCOによって受信される第1の制御電圧及び前記第2のサブPLLの前記第2のVCOによって受信される第2の制御電圧に基づいて、可変の分周率の選択と前記出力信号の選択をするPLL制御回路と、

を含み、

前記サブPLLの1つが、前記出力信号を提供するために前記位相ロックループ制御回路によって選択され、前記位相ロックループ制御回路が他のサブPLLに対する分周率を変更でき、

前記PLL制御回路による前記第1の分周率及び前記第2の分周率の選択は、前記第1

の制御電圧及び前記第2の制御電圧が単一の最適電圧値に対してどの程度近いかに基づいていることを特徴とする位相ロックループ出力信号を生成するチップ。

【請求項2】

前記第1の分周率は、前記第2の分周率と異なっていることを特徴とする請求項1に記載のチップ。

【請求項3】

前記第1の分周率は、2の整数べき乗に等しく、前記第2の分周率も、2の整数べき乗に等しく、

前記第1の分周率に対する前記整数は、前記第2の分周率に対する前記整数と異なっている、

10

ことを特徴とする請求項1に記載のチップ。

【請求項4】

前記第1のサブPLLの前記整数は、偶数整数であり、前記第2のサブPLLの前記整数は、奇数整数であることを特徴とする請求項3に記載のチップ。

【請求項5】

前記第1及び第2のサブPLLは、

第1及び第2の位相周波数検出器、及び

前記第1及び第2の出力クロック信号の前記周波数を分割する第1及び第2のフィードバック分割回路であって、第1及び第2の分割回路の出力を前記第1及び第2の位相周波数検出器に供給する第1及び第2のフィードバック分割回路、

20

を含む、

ことを特徴とする請求項1に記載のチップ。

【請求項6】

現在選択されていないサブPLLの変更される分周率が、選択されているサブPLLの分周率より良好である場合、前記PLL制御回路は、サブPLLの選択を選択されてないPLLに変更する請求項1に記載のチップ。

【請求項7】

第1及び第2のサブ位相ロックループ(サブPLL)の第1及び第2の電圧制御式発振器(VCO)に第1及び第2の電圧制御信号を供給する段階と、

前記第1及び第2のVCOから第1及び第2のフィードフォワード分割回路に第1及び第2のVCO出力信号を出力する段階と、

30

前記第1のサブPLLから第1の出力クロック信号を生成すると共に前記第2のサブPLLから第2の出力クロック信号を生成するために、前記第1及び第2のフィードフォワード分割回路を用いて前記第1及び第2のVCO出力信号の第1及び第2の周波数を可変の第1及び第2の分周率によって分割する段階と、

前記第1及び第2分周率を選択する段階と、

記第1のサブPLLからの前記第1の出力クロック信号又は前記第2のサブPLLからの前記第2の出力クロック信号のいずれかを出力信号として選択する段階と、

を含み、

前記サブPLLの1つの前記出力クロック信号が、前記出力信号として選択され、他のサブPLLに対する分周率を変更でき、

40

前記可変の第1及び第2の分周率の選択と前記出力信号の選択は、前記第1の出力クロック信号、前記第2の出力クロック信号、前記第1のサブPLLの前記第1のVCOによって受信される第1の制御電圧及び前記第2のサブPLLの前記第2のVCOによって受信される第2の制御電圧に基づいてなされるものであり、前記PLL制御回路による前記第1の分周率及び前記第2の分周率の選択は、前記第1の制御電圧及び前記第2の制御電圧が単一の最適電圧値に対してどの程度近いかに基づいていることを特徴とする位相ロックループ出力信号を生成する方法。

【請求項8】

前記第1の分周率は、前記第2の分周率と異なっていることを特徴とする請求項7に記載

50

の方法。

**【請求項 9】**

選択されていないサブPLLの変更される分周率が、選択されているサブPLLの分周率より良好である場合、現在選択されているサブPLLから選択されていないサブPLLへ前記出力クロック信号の選択を変更することを更に含む請求項7に記載の方法。

**【請求項 10】**

入力クロック信号を搬送する少なくとも1つの導体と、

第1及び第2の電圧制御式発振器(VCO)出力信号を供給する第1及び第2のVCOと、該第1及び第2のVCO出力信号の第1及び第2の周波数を可変の第1及び第2の分周率によって分割する第1及び第2のフィードフォワード分割回路とを含む第1及び第2のサブ位相ロックループ(サブPLL)であって、前記第1のサブPLLから第1の出力クロック信号を生成し、前記第2のサブPLLから第2の出力クロック信号を生成する第1及び第2のサブPLL、及び

前記第1及び第2の分周率を選択し、記第1のサブPLLからの前記第1の出力クロック信号又は前記第2のサブPLLからの前記第2の出力クロック信号のいずれかを出力信号として選択する位相ロックループ(PLL)制御回路、

を含むデュアル位相ロックループ(デュアルPLL)と、

を含み、

前記サブPLLの1つが、前記出力信号を提供するために前記PLL制御回路によって選択される一方で、前記PLL制御回路が他のサブPLLに対する分周率を変更でき、

前記可変の第1及び第2の分周率の選択と前記出力信号の選択は、前記第1の出力クロック信号、前記第2の出力クロック信号、前記第1のサブPLLの前記第1のVCOによって受信される第1の制御電圧及び前記第2のサブPLLの前記第2のVCOによって受信される第2の制御電圧に基づいてなされるものであり、前記PLL制御回路による前記第1の分周率及び前記第2の分周率の選択は、前記第1の制御電圧及び前記第2の制御電圧が単一の最適電圧値に対してどの程度近いかに基づいていることを特徴とする位相ロックループ出力信号を生成するチップ。

**【請求項 11】**

前記第1の分周率は、前記第2の分周率と異なっていることを特徴とする請求項10に記載のチップ。

**【請求項 12】**

前記第1の分周率は、2の整数べき乗に等しく、前記第2の分周率も、2の整数べき乗に等しく、

前記第1の分周率に対する前記整数は、前記第2の分周率に対する前記整数と異なっている、

ことを特徴とする請求項10に記載のチップ。

**【請求項 13】**

前記第1のサブPLLの整数は、偶数の整数であり、前記第2のサブPLLの整数は、奇数の整数である請求項10に記載のチップ。

**【請求項 14】**

現在選択されていないサブPLLの変更される分周率が、選択されているサブPLLの分周率より良好である場合、前記PLL制御回路は、サブPLLの選択を選択されてないPLLに変更する請求項10に記載のチップ。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の実施形態は、一般的に位相ロックループに関する。

**【背景技術】**

**【0002】**

位相ロックループ(PLL)は、一般的に集積回路チップ及びシステムに使用され、入

10

20

30

40

50

力信号に関連した周波数及び位相を有する規準信号と呼ばれる信号を発生させる。基準信号は、典型的にはクロック信号である。PLLの出力信号も、典型的には入力基準クロック信号に「固定した」クロック信号である。PLLは、マイクロプロセッサ、通信機器、及び他の電子機器を含む広範なチップにおいて使用される。

#### 【0003】

典型的なPLLは、位相周波数検出器(PFD)、チャージポンプ(CP)、ループフィルタ(LF)(ローパスフィルタとすることができる)、電圧制御発振器(VCO)、及び周波数分割回路を含む。PFDは、基準信号の位相を周波数分割回路からのフィードバック信号と比較する。基準信号及びフィードバック信号の位相関係により、PFDは、LFを通じてVCOへの電圧を昇圧又は降圧するようにCPに命令する信号をCPに供給する。LFは、信号を積分してそれを平滑化することができる。平滑化された信号は、VCOに供給される。VCOの周波数は、LFからの電圧信号に応じて高く又は低くなる。VCOの出力は、基準信号に比例して(又はそれに等しい)かつそれと同相の周波数をVCOの出力信号に持たせるループ内の周波数分割器を通じてPFDに返される。

10

#### 【0004】

多くのPFDは、周波数の差に応答することができ、これは、許容入力のロックイン範囲を拡大させる。一部のPLLは、基準クロック信号と位相検出器への基準入力との間に分割回路を含む。一部の設計では、PFDの2つの出力があり、1つは、CPにVCOへの電圧を増加させるアップ信号を有し、別のものは、CPにVCOへの電圧を低下させるダウン信号を有する。

20

適応帯域幅PLLは、処理、電圧、及び温度(PVT)変動と殆ど無関係に作動周波数に比例してその力学をスケーリングするPLLの部類を意味する。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

アナログPLL設計者が今日直面している課題の1つは、リングVCO周波数範囲の減少である。VCO制御電圧の使用可能範囲は、供給電圧が1.2V(ボルト)よりも低くなつたので相当に縮小した。一方、PLL適用領域は、拡大し続け、1つのPLLから更に広い周波数範囲を要求している。

30

#### 【課題を解決するための手段】

#### 【0006】

一部の実施形態では、チップは、第1及び第2の電圧制御式発振器(VCO)出力信号を供給するための第1及び第2のVCOと、第1及び第2VCO出力信号の第1及び第2の周波数を第1及び第2の分周率によって分割するための第1及び第2のフィードフォワード分割回路とを含む第1及び第2のサブ位相ロックループ(サブPLL)を含む。チップはまた、第1及び第2分周率を選択するための位相ロックループ制御回路を含む。

#### 【0007】

一部の実施形態では、PLL制御回路は、第1及び第2出力クロック信号と第1及び第2VCO内への第1及び第2フィードフォワード電圧信号入力とに応答して第1及び第2分周率を選択する。

40

一部の実施形態では、方法は、第1及び第2サブ位相ロックループ(サブPLL)の第1及び第2電圧制御式発振器(VCO)に電圧制御信号を供給する段階を含む。更に、本方法は、第1及び第2VCOから第1及び第2VCO出力信号と第1及び第2フィードフォワード分割回路とを出力する段階と、第1及び第2VCO出力信号の第1及び第2周波数を第1及び第2分周率によって分割する段階と、第1及び第2分周率を選択する段階とを含む。

#### 【0008】

更に別の実施形態では、チップは、入力クロック信号を搬送する少なくとも1つの導体と、デュアル位相ロックループ(デュアルPLL)とを含む。デュアルPLLは、第1及び第2VCO出力信号を供給する第1及び第2電圧制御式発振器(VCO)と、第1及び

50

第2分周率によって第1及び第2VCO出力信号の第1及び第2周波数を分割する第1及び第2フィードフォワード分割回路と含む第1及び第2サブ位相ロックループ(サブPLL)、及び第1及び第2分周率を選択する位相ロックループ制御回路を含む。

他の実施形態も説明して特許請求する。

本発明は、本発明の実施形態を示すために使用される以下の説明及び添付図面を参照することによって理解することができる。しかし、本発明は、これらの図面の詳細に限定されるものではない。

#### 【発明を実施するための最良の形態】

##### 【0009】

一部の実施形態では、本発明は、広い周波数範囲を有する適応帯域幅PLLを含む。単に例示的に、一部の実施形態では、周波数範囲は、500:1であるが、他の比率でもよい。一部の実施形態では、周波数範囲は、動的にフィードフォワード分割器の分周率を調節するデュアルPLLアーキテクチャにより拡大される。

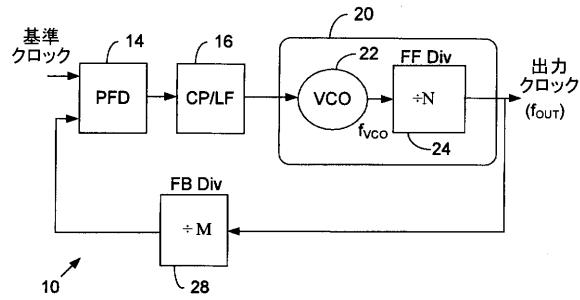

図1は、位相周波数検出器(PFD)10と、チャージポンプ(CP)／ループフィルタ(LF)16と、電圧制御式発振器(VCO)22及び分周率Nを有するフィードフォワード周波数分割器(FF Div)24を含む出力周波数制御回路20と、分周率Mを有するフィードバック周波数分割器(FB Div)28とを有するPLL10を示している。VCO22は、周波数 $f_{VCO}$ を有するVCO信号を供給する。「FF Div」24は、周波数 $f_{OUT}$ を有する出力クロック信号(out clk)を供給し、かつこの信号はまた、「FB Div」28に対しても供給される。「FB Div」28の出力は、PFD14への入力として供給される。CP/LF16のチャージポンプ及びループフィルタは、異なる回路であるが、図示を容易にするために結合されている。「FF Div」24の分周率(N)は、調節される。一部の実施形態では、VCOの調節領域が比較的狭い場合であっても、この調節によって「FF Div」24が広い領域の周波数を発生させることを可能にする。

##### 【0010】

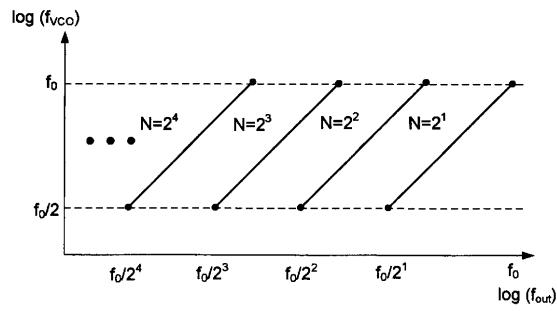

図2は、分周率Nの異なる値、例えば、 $N = 2^4$ 、 $N = 2^3$ 、 $N = 2^2$ 、 $N = 2^1$ などに対する $\log f_{VCO}$ 対 $\log f_{OUT}$ の線のグラフを示している。 $f_{VCO}$ の周波数が $f_o$ と $f_o/2$ との間で高くなる時、 $f_{OUT}$ の周波数は、 $N = 2^4$ に対する $f_o/2^4$ を始点として、 $N = 2^3$ に対する $f_o/2^3$ を始点として、 $N = 2^2$ に対する $f_o/2^2$ を始点として、 $N = 2^1$ に対する $f_o/2^1$ を始点として高くなる。1つの線(例えば、 $N = 2^4$ の線)の最高周波数が、次の線(例えば、 $N = 2^3$ の線)の最低周波数よりも高くなるように、周波数の線は、重なり合うことになることに注意されたい。

##### 【0011】

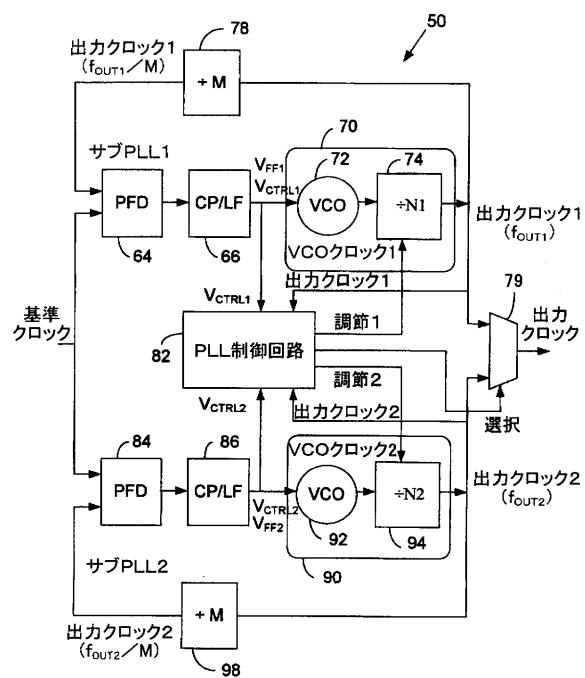

図3は、2つのPLL、サブPLL1、及びサブPLL2を含むデュアルPLL回路50を示し、各サブPLLは、図1のPLL10と同様である。サブPLL1において、PFD64は、基準クロック信号(ref clk)及び「out clk」1の周波数 $f_{OUT1}$ をMによって分割するフィードバック周波数分割器78の出力を受け取る。PFD64は、CP/LF66に対して信号を供給し、CP/LF66は、電圧信号 $V_{CTRL1}$ 及び電圧信号 $V_{FF1}$ を出力周波数制御回路70のVCO72に供給する。信号VCOclk1は、VCO72の出力であり、VCOclk1信号をN1によって分割するフィードフォワード周波数分割回路74に供給される。ここで、N1は、例えば図2及び4に示されている変数である。出力クロック信号(out clk 1)は、分割されたVCOclk1信号であり、この信号は、選択回路79に供給される。

##### 【0012】

サブPLL2において、PFD84は、基準クロック信号(ref clk)及び「out clk」1の周波数 $f_{OUT2}$ をMによって分割するフィードバック周波数分割器98の出力を受け取る。PFD84は、CP/LF86に信号を供給し、CP/LF86は、電圧信号 $V_{CTRL2}$ 及び電圧信号 $V_{FF2}$ を出力周波数制御回路90のVCO92に供給する。信号VCOclk2は、VCO92の出力であり、VCOclk2信号をN2によって分割

10

20

30

40

50

するフィードフォワード周波数分割回路 9 4 に供給される。ここで、N 2 は、例えば図 2 及び 4 に示されている変数である。出力クロック信号 (out clk 2) は、分割された VCO clk 2 信号であり、この信号は、選択回路 7 9 に供給される。

【0013】

PLL 制御回路 8 2 は、N 1 及び N 2 の値を選択し、選択回路 7 9 に選択信号を供給して、「out clk」1 又は「out clk」2 が出力信号として選択回路 7 9 によって供給されるか否かを制御する。一部の実施形態では、N 1 は N 2 に等しく、他の実施形態では、N 1 と N 2 は異なる場合がある。一部の実施形態では、PLL 制御回路 8 2 は、V<sub>CTRL1</sub> 及び V<sub>CTRL2</sub> 並びに判断を助けるための出力クロック信号「out clk」1 及び「out clk」2 を受け取る。他の実施形態では、PLL 制御回路 8 2 は、VCO × 1 k 1 及び VCO clk 2 信号を受け取る。

10

【0014】

図 3 において、周波数範囲は、フィードフォワード分割回路 7 4 及び 9 4 を通して拡張することができる。低周波数 f<sub>OUT</sub> が必要になる場合、分割器 7 4 及び 9 4 は、VCO 7 2 及び 9 2 を低 f<sub>OUT</sub> で振動させる代わりに、N 1 又は N 2 により VCO 周波数 (f<sub>VCO</sub>) を低下させる。上述のように、PLL 制御回路 8 2 は、N 1 及び N 2 を選択する。一部の実施形態では、選択上の問題は、デジタル的に選択可能な負荷コンデンサを有する LC 発振器において直面する粗周波数制御問題に類似している。従来方式は、VCO 制御電圧 (V<sub>CTRL</sub>) を外部から供給される上限と下限 (V<sub>H</sub> 及び V<sub>L</sub>) の間に設定する N を選択する段階を含む。しかし、リング発振器が、LC 発振器よりも PVT 变動に対して敏感であるので、この方式は、リング発振器に向いていないと考えられる。第 1 に、切れ目のない周波数のカバー範囲を保証するために、外部制限 V<sub>H</sub> 及び V<sub>L</sub> は、慎重にマージンを設定し、隣接周波数のサブ領域間に十分な重なりを補償することができる。第 2 に、N を変化させることは、PLL に一時的に固定を失わせることになるので、N の選択は、起動時に 1 回のみ行うことができ、十分なマージンを有するように慎重に行って、起こり得る最悪の PVT 变動を少しづつ調節することができる。これらのマージンは、VCO の広範な調節範囲を必要とし、フィードフォワード分割回路 7 4 及び 9 4 の利点を減少する。

20

【0015】

提案するデュアル PLL 回路 (図 3 におけるような) は、N を動的に変化させることを可能にし、かつ V<sub>CTRL</sub> の中間レベルに設定するために単一の電圧 V<sub>OPT</sub> を使用することにより、これらのマージンの必要性をなくすことができる。図 3 に表現したように、デュアル PLL は、異なるフィードフォワード分周率 N 1 及び N 2 を有する 2 つのサブ PLL 1 及びサブ PLL 2 を含む。一方のサブ PLL は、選択回路 7 9 を通して出力 (out clk) を駆動すると共に、他方のサブ PLL は、より良い N を検索する。後者がより良い N を見出した場合、後者は、出力を駆動する役割を引き継ぎ、前者は、新たな N の検索を開始する。固定したサブ PLL のみが出力を駆動するので、N の切り換えからの過渡状態は、出力から隠され、分周率 N を実時間で変更することができる。N の最適性は、固定された V<sub>CTRL</sub> の V<sub>OPT</sub> への接近度によって評価され、従って、使用される V<sub>CTRL</sub> の範囲は、V<sub>H</sub> 及び V<sub>L</sub> を設定することなく V<sub>OPT</sub> に合わせられることになる。従って、以前の方式において必要とされた上述のマージンは、もはや必要とされない。更に、中間 V<sub>CTRL</sub> レベルの V<sub>OPT</sub> を、VCO の PVT 状態を追跡するように設計して、常にこれを最小ジッタに対して最適な V<sub>CTRL</sub> 範囲に置くことができる。

30

40

【0016】

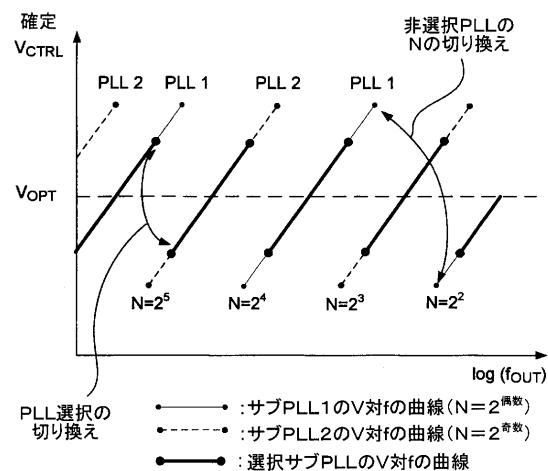

図 4 は、N 1 及び N 2 を発見するためのアルゴリズムを示している。単に一例として、一部の実施形態では、1 対の VCO 分割器は、分周率 N が 2 のべき乗をとることを仮定して 2 : 1 の狭い f<sub>VCO</sub> 範囲で広い範囲の f<sub>OUT</sub> を発生させるが、他の実施形態は、これらの詳細に限定されない。図 4 は、分周率 N の異なる値、例えば、N = 2<sup>6</sup>、N = 2<sup>5</sup>、N = 2<sup>4</sup>、N = 2<sup>3</sup>、N = 2<sup>2</sup>、N = 2<sup>1</sup> などに対する確定した f<sub>CTRL</sub> 対 log f<sub>OUT</sub> のグラフを示している。「確定した」は、PLL が確定するか又は固定されることを指す。図 4 には、3 種の類似の直線がある。細い実線は、2 偶数に等しい N の値に対するサブ PLL 1 の V

50

$V_{CTRL}$ 対  $f_{OUT}$ 特性を示している。細い破線は、 $2^{奇数}$ に等しいNの値に対するサブPLL2の  $V_{CTRL}$ 対  $f_{OUT}$ 特性を示している。太い実線は、選択されたサブPLL（サブPLL1又はサブPLL2）の  $V_{CTRL}$ 対  $f_{OUT}$ 特性を示している。図2の場合と同様に、1つの線分の最高周波数が次の線分の最低周波数よりも大きくなるように、周波数線分は、重なり合うことができる。しかし、太線の上端（大きな黒丸）は、次の線分の最下端（小さい丸）の直上にある。例えば、 $N = 2^4$ の線分の最下部の小さい丸は、 $N = 2^5$ の太線の頂点（大きい丸）と同一の  $f_{OUT}$ 値を有する。

#### 【0017】

$V_{OPT}$ により近い確定した  $V_{CTRL}$ を有するサブPLLは、出力を駆動する。サブPLLの駆動は、2つの  $V_{CTRL}$ が  $V_{OPT}$ に等しい距離を有する時、すなわち、2つのサブPLLが  $f_{OUT}$ を発生させるために最適値に等しい時に変更される。切り換えられると、出力位相は、静的位相オフセット中の偏差のためシフトすることがある。この位相シフトがチャタリングによって高周波数のジッタに変化することを防ぐために、ヒステリシスを加えることができる。また、両方の  $V_{CTRL}$ が  $V_{OPT}$ よりも高いか又は低い時、それらの一方は、  $V_{OPT}$ から離れすぎていると考えられ、選択されていないサブPLLは、それをより近づけるように係数4によってNを更新することができる。PLL50の帯域幅は、 $f_{VCO}/(N \times M)$ に比例して変えることができる。ここで、 $N \times M$ は、分周率の合計である。  $V_{OPT}$ の値を選択するための異なる方法がある。正確な  $V_{OPT}$ 値は重要ではない場合もあるが、周波数における不連続性は、回避されるべきである。これは、図4において、次の線分の下端（小さい丸）の直上にある太線の上端（大きい丸）の間にかなりの空間があつてはならないことを意味する。

#### 【0018】

一部の実施形態では、PLL制御回路82は、分周率の動的かつ欠陥なしのスイッチングを可能にする。一部の実施形態では、比較的狭い調節範囲を使用することにより、PLL50は、最良の状態中でのみVCOを作動させることによって低ジッタを達成することができる。また、分周率Nによって明示的に制御される回路帯域幅を用いて、PLL50は、以前の実現手段よりも正確な適応帯域幅力学を維持することができる。

#### 【0019】

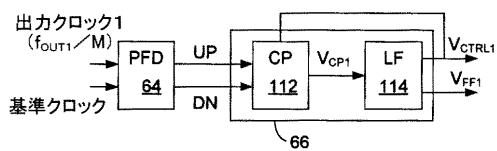

図5は、チャージポンプ112に対するアップ信号及びダウン信号の両方を供給するPFD64の実施形態を示している。図5において、図3のCPLF66は、チャージポンプ(CP)112及びループフィルタ(LF)114を含む。図6、7、及び8は、チャージポンプ112、ループフィルタ114、及びVCO72の一部の実施形態の詳細を提供するが、他の実施形態は、これらの詳細を含まない。

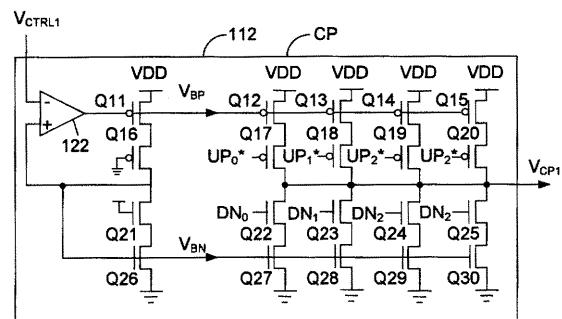

図6は、一部の実施形態によるチャージポンプ112及びそのバイアス回路の例を示すが、他の実施形態は、これらの詳細を含まない。適応式帯域幅に対して  $V_{BN}$ （負バイアス）を  $V_{BN}$ を通じて  $V_{CTRL}$ に等しく設定することにより、チャージポンプ電流は、VCO電流に追従するようにバイアスされ、比較器122にフィードバック信号として供給される。また、このフィードバックは、 $V_{BP}$ （正バイアス）を制御し、昇圧及び降圧電流が、例えば2%内に合わされて、静的位相オフセットを削減する。チャージポンプ112は、それぞれ、NMの1、2、及び4に対して、1倍、1/2倍、及び1/4倍の電流レベルをとるように区分される。Pチャンネル金属酸化膜半導体電界効果トランジスタ(PMOSFET)Q11、Q12、Q13、Q14、及びQ15のゲートは、比較器122の出力( $V_{BP}$ 信号)を受け取ると共に、Nチャンネル金属酸化膜半導体電界効果トランジスタ(NMOSFET)Q26、Q27、Q28、Q29、及びQ30のゲートは、 $V_{BN}$ 信号を受け取る。「PMOSFET」Q17、Q18、Q19、及びQ20は、アップ信号  $U_{P_0^*}$ 、 $U_{P_1^*}$ 、 $U_{P_2^*}$ 、及び  $U_{P_2^*}$ を受け取る。ここで  $U_{P_0^*}$ 、 $U_{P_1^*}$ 及び  $U_{P_2^*}$ は、 $U_{P_0}$ 、 $U_{P_1}$ 、及び  $U_{P_2}$ の論理的逆である。 $U_{P_2}$ は、 $U_{P_0}$ 及び  $U_{P_1}$ の2倍の重みを有することに注意されたい。「NMOSFET」Q22、Q23、Q24、及びQ25は、ダウン信号  $D_{N_0}$ 、 $D_{N_1}$ 、 $D_{N_2}$ 、及び  $D_{N_3}$ を受け取る。 $D_{N_2}$ は、 $D_{N_0}$ 及び  $D_{N_1}$ の2倍の重みがあることに注意されたい。「PMOSFET」Q16及び「NMOSFET」Q2

10

20

30

40

50

1 は、Q 1 6 及びQ 2 1 間に  $V_{BN}$  信号を有してQ 1 1 及びQ 2 6 間で結合される。チャージポンプ電圧  $V_{CP}$  は、「PMOSFET」Q 1 7、Q 1 8、Q 1 9、及びQ 2 0 と「NMOSFET」Q 2 2、Q 2 3、Q 2 4、及びQ 2 5 間に供給される。

#### 【0020】

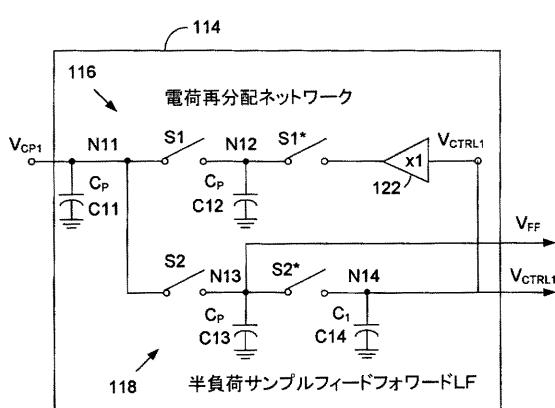

図7は、一部の実施形態によるループフィルタ114を示すが、他の実施形態は、これらの詳細を含まない。ループフィルタ114は、電荷再分配ネットワーク116及び半負荷サンプルフィードフォワードループフィルタ118を含む。電荷再分配116は、スイッチS1及びS1<sup>\*</sup>（これはS1の逆である）を含む。スイッチS1及びS1<sup>\*</sup>は、開及び閉であるかの2者択一である。コンデンサC11及びC12（それぞれ容量Cpを有する）は、それぞれ、接地とノードN11及びN12との間に結合される。バッファ112は、 $V_{CTRL}$ 信号を供給する。S1が閉であり、S1<sup>\*</sup>が開である時、 $V_{CP}$ 及び $V_{CTRL}$ 電圧は、ノード11上で統合され、C11中に蓄積される。各電荷再分配ネットワーク116は、ノード11において $V_{CP}$ 上に蓄積されるエラー電荷を半減することができる。プログラムブル分割器は、制御信号を発生し、スイッチを順に配列し、4よりも大きなN×Mに対して $N \times M / 4 (= 2^{n+m-2})$ によってループ利得を縮小する。

10

#### 【0021】

半負荷サンプルフィードフォワードループフィルタ118は、スイッチS2及びS2<sup>\*</sup>（S2<sup>\*</sup>は、S2の逆である）を含む。C13及びC14（それぞれ容量Cp及びC1を有する）は、それぞれ、接地とノードN13及びN14との間に結合される。ループフィルタ114は、基準サイクル長の半分であるフィードフォワードパルス $V_{FF}$ を生成し、基準周波数 $f_{REF}$ との望ましい比較を達成する。スイッチS1、S1<sup>\*</sup>、S2、及びS2<sup>\*</sup>は、コンデンサC11、C12、C13、及びC14上の電荷を制御するために開閉する。S1が閉じている時、C11上に蓄積された電荷は、C12と共有され、また、S2が閉じられている時、C11上の電荷は、C13と共有される。スイッチS1<sup>\*</sup>は、C12上の電圧をリセットする。スイッチS1、S1<sup>\*</sup>、S2、及びS2<sup>\*</sup>は、図8のVCO回路からの出力を受け取る論理によって制御される。

20

#### 【0022】

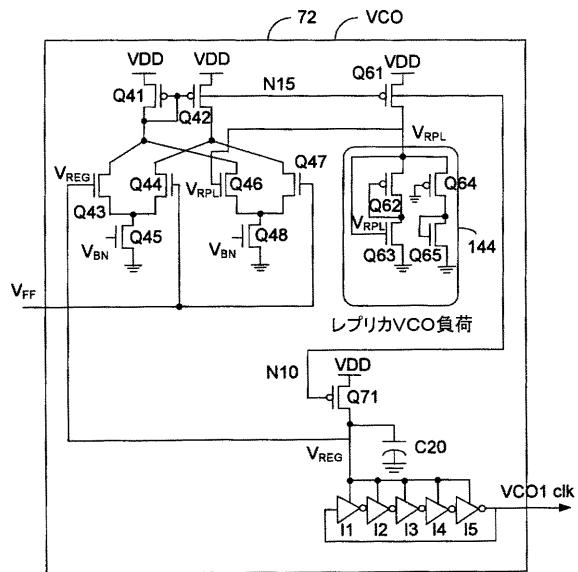

図8は、レプリカ補償電源レギュレータ（「PMOSFET」Q62及びQ64並びに「NMOSFET」Q63及びQ65を含む）を含むインバータベースのリング発振器を示している。レプリカフィードバックは、電源ノイズに応答する高速フィードバックバスを達成することによって電源ノイズ除去を改善する。ループフィルタ114からのフィードフォワード電圧 $V_{FF}$ は、「NMOSFET」Q44及びQ47のゲートによって受け取られる。 $V_{FF}$ が「high」（高い電圧を有する）の時、Q44及びQ47は、ONになり、Q42のドレーンを引き下げる。レギュレータ電圧 $V_{REG}$ が「high」の時、「NMOSFET」Q43もまた、「PMOSFET」Q41のドレーン上で引き下げられ、「PMOSFET」Q41及びQ42をONにする。Q44、Q47、Q42がONの時、ノードN15は、「low」に引き下げられ、「PMOSFET」Q61をONにする。Q61のドレーンにおける電圧 $V_{RPL}$ （レプリカ）は、「NMOSFET」Q46をONにする。「NMOSFET」Q45及びQ48のゲートは、 $V_{BN}$ 信号を受け取る。これは、図6に示すもの又は図6と同様な付加回路と同一の信号からのものであり、図8の $V_{BN}$ を発生する。

30

N15の電圧が引き下げる時、「PMOSFET」Q71はONになり、 $V_{REG}$ を昇圧してQ43をOFFにする。コンデンサC20は、電圧変動を平滑化する。電圧 $V_{REG}$ は、インバータI1、I2、I3、I4、及びI5が振動する速度を制御し、その結果インバータI5から供給されるVCO1クロック信号の周波数を制御する。

40

#### 【0023】

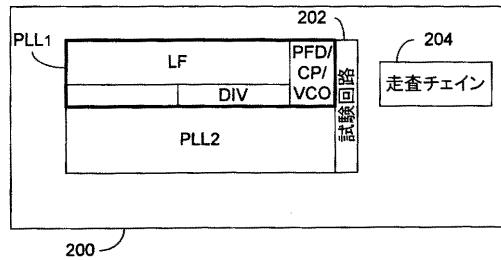

図9は、サンプルチップ200における回路レイアウトを示している。PLL1は、LF、分割器（DIV）、PFD、CP、及びVCOを含む。PLL2は、同一の構成要素を含む。試験回路202は、PLL1及びPLL2を試験する。走査チェーン204は、PLLの一部にアクセスする外部回路を提供する。適応帯域PLLは、0.13 $\mu$ m CM

50

O S 处理で実施され、以下の特性を有していた。

処理技術：0.13  $\mu$ m、N-ウェル、1P6M CMOS

面積：1.1 × 0.46 mm<sup>2</sup>

電源電圧：1.2 V 公称

ワット損：36 mW

基準周波数範囲：2 MHz ~ 1 GHz

出力周波数範囲：2 MHz ~ 1 GHz

増倍率範囲：M = 2<sup>0</sup> ~ 9

ループ帯域幅：基準周波数の ~ 1 / 100

ジッタ (M = 1, 1.024 GHz) : 13.10 ps, pp, 1.62 ps, rms 10

#### 【0024】

この例では、PLLは、広いN選択範囲2<sup>1~24</sup>を有していたが、この例示的PLLは、2 MHzから1 GHzの基準周波数範囲に固定されていた。チャージポンプにおける閾値下の漏れが、2 MHzよりも低く作動を制限した可能性がある。Nの動的選択は、成功裏に行われ、VCO振動周波数は、1~2 GHzの狭い範囲に限定された。このPLLは、M × f<sub>REF</sub>が1 GHzを超えない限り、M = 2<sup>m</sup>を有するあらゆる倍周波数を供給することができると考えられる。測定されたジッタ対基準信号f<sub>REF</sub>及びMは、PLL帯域幅がf<sub>REF</sub>で縮小することを確認した。VCO位相ノイズが測定の設定では出力ジッタを支配していたので、追跡ジッタは、帯域幅の減少に伴い増加した。f<sub>OUT</sub>にNを自己適応させることにより、デュアルPLLアーキテクチャは、VCOをジッタ傾向の低周波数振動に近づけないようにし、その結果、固定NのPLLよりも低いジッタを達成する。ジッタ傾向における不連続点は、Nが切り換わる点を示し、静的位相オフセットにおける最悪ステップ変動は、基準サイクルの3.6%であった。本発明の他の実施では、上記と異なる詳細を含むことができることに注意されたい。 20

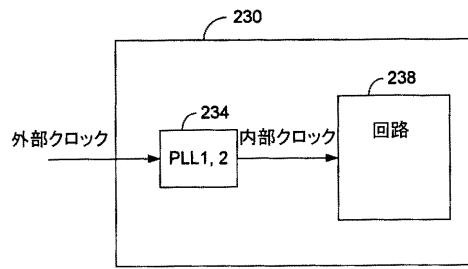

図10は、デュアルPLL234が外部クロック信号を受け取り、このデュアルPLLが回路238に内部クロック信号を供給するチップ230を示している。

#### 【0025】

本発明は、いかなる特定の信号伝達形式にも限定されない。入力及びクロック信号は、シングルエンド又は区別したものとすることができます。クロッキングは、1倍データ転送速度、2倍データ転送速度、4倍データ転送速度などとすることができます。2倍データ転送速度では、単一のクロック信号の立ち上がり立下りエッジを使用することができ、又は位相クロックからの2つを使用することができる。信号は、パケット化又は非パケット化することができる。 30

#### 【0026】

本発明の開示は、本質的に概要であって様々な詳細を含まない様々な図を含む。実際の実施においては、システム及びチップは、示されてはいないが、図の回路間に含まれる付加的な構成要素を含むであろう。図示の構成要素は、様々な付加的な入力及び出力を有することができる。本明細書に説明した様々なアルゴリズム及び方法は、ファームウェア又はソフトウェアの支援なしにハードウェア回路中で実行することができる。しかし、ファームウェア及び/又はソフトウェアは、アルゴリズム及び方法が実行される全体的システムに使用することができる。 40

図3では、分割Mは、回路78及び98に対して同じであるが、これらは異なっていてもよい。

#### 【0027】

本明細書で使用される場合、用語「実施形態」は、実施例を指す。「実施形態」、「一実施形態」、「一部の実施形態」、又は「他の実施形態」への本明細書中の参照は、これらの実施形態に関連して説明される特定の特徴、構造、又は特性が少なくとも一部の実施形態に含まれるが、本発明の全ての実施形態に含まれる必要はないことを意味する。「一部の実施形態」への異なる参照は、同じ「一部の実施形態」を指す必要はない。

#### 【0028】

本明細書が、構成要素、特徴、構造、又は特性を含む「場合がある」、「かもしれない」、又は「ことができる」と考えられる場合、この特定の構成要素、特徴、構造、又は特性は含まれる必要はない。本明細書又は特許請求の範囲が「a」を付した構造を参照する場合、これは、構造が1つのみであることを意味しない。

本発明をいくつかの実施形態によって説明したが、本発明は、説明したそれらの実施形態に限定されるべきではなく、特許請求の範囲及び精神の範囲内で修正及び変更して実施することができる。以上の説明は、従って、限定的ではなく例示的であるとみなすものとする。

【図面の簡単な説明】

【0029】

10

【図1】本発明の一部の実施形態において使用することができる構成要素を備えた位相ロックループを含むシステムのブロック図である。

【図2】異なる値の分周率Nに対する $\log f_{VCO}$ 対 $\log f_{OUT}$ の線をグラフとして表現した図である。

【図3】本発明の一部の実施形態に従ったデュアル位相ロックループのブロック図である。

【図4】異なる値の分周率Nに対する $\log f_{CTRL}$ 対 $\log f_{OUT}$ の線のグラフである。

【図5】本発明の一部の実施形態において使用することができる位相周波数検出器、チャージポンプ、及びループフィルタのブロック図である。

【図6】図5のチャージポンプのブロック図である。

20

【図7】図5のループフィルタのブロック図である。

【図8】図5の電圧制御式発振器のブロック図である。

【図9】走査チェーン回路を有する一部の実施形態によるデュアル位相ロックループの例に対するチップレイアウトのブロック図である。

【図10】内部クロック信号を回路に供給する一部の実施形態によるデュアル位相ロックループを含むブロックチップを示す図である。

【符号の説明】

【0030】

10 位相ロックループ

22 電圧制御式発振器

30

24 フィードフォワード周波数分割器

N、M 分周率

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図9】

---

フロントページの続き

(72)発明者 キム ジェハ

アメリカ合衆国 カリフォルニア州 94041 マウンテン ヴィュー イースト ダナ スト

リート 810

(72)発明者 ジョン ドグ キューン

大韓民国 151-742 ソウル ソーチョー-ク バンベ 4 ドン バンベ デウル アパ

ートメント 1005

審査官 畑中 博幸

(56)参考文献 特開平10-271002(JP, A)

特開2002-064378(JP, A)

実開平03-120133(JP, U)

特開平11-214992(JP, A)

特開昭63-305619(JP, A)

特表平10-508439(JP, A)

特開2000-252821(JP, A)

特開平03-190428(JP, A)

特開平05-145413(JP, A)

特開平08-125529(JP, A)

特表2001-520471(JP, A)

特開平11-136124(JP, A)

特開平05-227024(JP, A)

特開平05-199109(JP, A)

特開平11-330957(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03L 7/22

H03L 7/10