(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6671256号

(P6671256)

(45) 発行日 令和2年3月25日(2020.3.25)

(24) 登録日 令和2年3月5日(2020.3.5)

(51) Int.Cl.

F 1

|             |             |                  |      |      |      |

|-------------|-------------|------------------|------|------|------|

| <b>H05K</b> | <b>3/46</b> | <b>(2006.01)</b> | H05K | 3/46 | Q    |

| <b>H05K</b> | <b>3/40</b> | <b>(2006.01)</b> | H05K | 3/46 | N    |

| <b>H05K</b> | <b>3/42</b> | <b>(2006.01)</b> | H05K | 3/46 | B    |

|             |             |                  | H05K | 3/40 | E    |

|             |             |                  | H05K | 3/42 | 620B |

請求項の数 11 (全 20 頁)

(21) 出願番号 特願2016-136291 (P2016-136291)

(22) 出願日 平成28年7月8日(2016.7.8)

(65) 公開番号 特開2018-6712 (P2018-6712A)

(43) 公開日 平成30年1月11日(2018.1.11)

審査請求日 平成31年2月14日(2019.2.14)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 佐藤 淳史

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 近藤 人資

長野県長野市小島田町80番地 新光電氣

工業株式会社内

最終頁に続く

(54) 【発明の名称】配線基板及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁層と、

前記絶縁層に内蔵された電子部品と、

前記絶縁層に形成され、前記絶縁層の一方の面側に開口し、前記電子部品の電極を露出するビアホールと、

前記絶縁層に埋め込まれ、一方の面が前記絶縁層の一方の面から露出する第1配線層と、

前記第1配線層の一方の面に形成された配線パターン、及び前記配線パターンから前記ビアホール内に延在して前記電子部品の電極と直接接続されたビア配線、を含む第2配線層と、を有し、

前記絶縁層は、前記第1配線層を埋め込む第1絶縁膜、及び前記電子部品を内蔵する第2絶縁膜が積層された構造であり、

前記第1絶縁膜は、全ての前記第1配線層の側面及び他方の面、並びに前記ビア配線の側面の一部を被覆し、

前記電子部品の電極は、前記ビア配線と接する面が前記第2絶縁膜から露出し、側面が前記第2絶縁膜に被覆され、

前記ビア配線が前記配線パターンと一体である配線基板。

## 【請求項 2】

前記ビアホールは、前記電子部品の電極上に位置する前記第1配線層、及び前記第1配

線層と前記電子部品の電極との間に位置する前記絶縁層を貫通して前記電子部品の電極の一方の面を露出する請求項 1 に記載の配線基板。

**【請求項 3】**

前記第 2 配線層は、

前記第 1 配線層の一方の面上直接形成され、前記ビアホールと連通する貫通孔を備えた第 1 層と、

前記第 1 層上に形成され、前記第 1 層上から延在して前記貫通孔及び前記ビアホールの内壁に沿って形成され、更に前記ビアホール内に露出する前記電子部品の電極を被覆する第 2 層と、

前記第 2 層上に形成され、前記第 2 層上から延在して前記第 2 層が形成された前記貫通孔内及び前記ビアホール内を充填する第 3 層と、を有する請求項 1 又は 2 に記載の配線基板。 10

**【請求項 4】**

前記絶縁層の一方の面には前記配線パターンを被覆するソルダーレジスト層が形成され、

前記ソルダーレジスト層は、前記配線パターンを選択的に露出する開口部を備え、

前記開口部内に露出する前記配線パターンは、半導体チップ接続用のパッドである請求項 1 乃至 3 の何れか一項に記載の配線基板。

**【請求項 5】**

前記配線パターンは、前記ビア配線と接続された配線と、前記ビア配線と接続されていない配線と、を含み、 20

前記ビア配線と接続された配線と、前記ビア配線と接続されていない配線とは同一高さである請求項 1 乃至 4 の何れか一項に記載の配線基板。

**【請求項 6】**

前記絶縁層に形成され、前記絶縁層の他方の面側に開口し、前記電子部品の電極を露出する第 2 ビアホールと、

前記絶縁層の他方の面上形成された配線パターン、及び前記配線パターンから前記第 2 ビアホール内に延在して前記電子部品の電極と直接接続されたビア配線、を含む第 3 配線層と、を有する請求項 1 乃至 5 の何れか一項に記載の配線基板。 30

**【請求項 7】**

前記第 1 絶縁膜と前記第 2 絶縁膜との境界は、前記電子部品の電極の前記ビア配線と接する面と面一である請求項 1 乃至 6 の何れか一項に記載の配線基板。

**【請求項 8】**

最外層が金属箔である支持体を準備し、前記金属箔上に一方の面が前記金属箔と接する第 1 配線層を形成する工程と、

前記金属箔上に、前記第 1 配線層の側面及び他方の面を被覆する第 1 絶縁膜を形成する工程と、

前記第 1 絶縁膜上に、電子部品を搭載する工程と、

前記第 1 絶縁膜上に、前記電子部品を被覆する第 2 絶縁膜を形成する工程と、

前記金属箔を除く前記支持体を除去する工程と、 40

前記金属箔及び前記第 1 絶縁膜を貫通すると共に前記電子部品の電極を露出するビアホールを形成する工程と、

前記金属箔上及び前記ビアホール内に金属層を形成後、前記金属箔及び前記金属層をパターニングし、前記金属箔及び前記金属層を備えた配線パターン、及び前記配線パターンから前記ビアホール内に延在して前記電子部品の電極と直接接続されたビア配線、を含む第 2 配線層を形成する工程と、を有し、

前記第 1 絶縁膜は、全ての前記第 1 配線層の側面及び他方の面、並びに前記ビア配線の側面の一部を被覆し、

前記電子部品の電極は、前記ビア配線と接する面が前記第 2 絶縁膜から露出し、側面が前記第 2 絶縁膜に被覆され、 50

前記第2配線層を形成する工程において、前記ビア配線を前記配線パターンと一体に形成する配線基板の製造方法。

【請求項9】

前記第2配線層を形成する工程は、

前記金属箔の全面、前記ビアホールの内壁面、及び前記ビアホール内に露出する前記電子部品の電極を連続的に被覆するシード層を形成する工程と、

前記シード層を給電層に利用した電解めっき法により、前記シード層上に選択的に電解めっき層を形成する工程と、

前記電解めっき層に覆われていない部分の前記シード層及び前記金属箔をエッチングにより除去する工程と、を有する請求項8に記載の配線基板の製造方法。 10

【請求項10】

前記第1配線層を形成する工程では、前記第1配線層の、前記電子部品の電極が配置される予定の領域に、貫通孔を形成しておき、

前記ビアホールを形成する工程では、前記貫通孔に対応する位置の前記金属箔及び前記第1絶縁膜にレーザを照射し、前記電子部品の電極を露出する前記ビアホールを形成する請求項8又は9に記載の配線基板の製造方法。

【請求項11】

前記第1絶縁膜と前記第2絶縁膜との境界は、前記電子部品の電極の前記ビア配線と接する面と面一となる請求項8乃至10の何れか一項に記載の配線基板の製造方法。 20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板及びその製造方法に関する。

【背景技術】

【0002】

従来、コンデンサやインダクタ等の電子部品を内蔵した配線基板が知られている。このような配線基板の一例として、コアとなるガラスエポキシ基板に積層セラミックコンデンサを内蔵した配線基板を挙げることができる。この配線基板では、ガラスエポキシ基板の表裏面に配線が形成され、各面の配線と積層セラミックコンデンサの電極とはガラスエポキシ基板内に形成したビア配線によって接続されている（例えば、特許文献1参照）。 30

【0003】

一方、絶縁層の一方の側に埋め込み配線を備えた配線基板が知られている（例えば、特許文献2参照）。このような配線基板に電子部品を内蔵する際には、埋め込み配線と電子部品の電極との接続に、上記の配線基板と同様の接続構造を採用することができない。埋め込み配線と電子部品の電極との接続方法としては、例えば、導電ペーストを用いる方法が考えられる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2013-84692号公報

40

【特許文献2】特開2012-146793号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、埋め込み配線と電子部品の電極とを導電ペーストを用いて接続する方法では、十分な接続信頼性が得られないという問題があった。

【0006】

本発明は、上記の点に鑑みてなされたものであり、埋め込み配線と電子部品の電極との接続信頼性を向上した配線基板を提供することを課題とする。

【課題を解決するための手段】

50

## 【0007】

本配線基板は、絶縁層と、前記絶縁層に内蔵された電子部品と、前記絶縁層に形成され、前記絶縁層の一方の面側に開口し、前記電子部品の電極を露出するビアホールと、前記絶縁層に埋め込まれ、一方の面が前記絶縁層の一方の面から露出する第1配線層と、前記第1配線層の一方の面に形成された配線パターン、及び前記配線パターンから前記ビアホール内に延在して前記電子部品の電極と直接接続されたビア配線、を含む第2配線層と、を有し、前記絶縁層は、前記第1配線層を埋め込む第1絶縁膜、及び前記電子部品を内蔵する第2絶縁膜が積層された構造であり、前記第1絶縁膜は、全ての前記第1配線層の側面及び他方の面、並びに前記ビア配線の側面の一部を被覆し、前記電子部品の電極は、前記ビア配線と接する面が前記第2絶縁膜から露出し、側面が前記第2絶縁膜に被覆され、前記ビア配線が前記配線パターンと一体であることを要件とする。

10

## 【発明の効果】

## 【0008】

開示の技術によれば、埋め込み配線と電子部品の電極との接続信頼性を向上した配線基板を提供できる。

## 【図面の簡単な説明】

## 【0009】

【図1】第1の実施の形態に係る配線基板を例示する図である。

【図2】第1の実施の形態に係る配線基板の製造工程を例示する図（その1）である。

20

【図3】第1の実施の形態に係る配線基板の製造工程を例示する図（その2）である。

【図4】第1の実施の形態に係る配線基板の製造工程を例示する図（その3）である。

【図5】第1の実施の形態に係る配線基板の製造工程を例示する図（その4）である。

【図6】第1の実施の形態の変形例1に係る配線基板を例示する図である。

【図7】第1の実施の形態の変形例1に係る配線基板の製造工程を例示する図である。

【図8】第1の実施の形態の変形例2に係る配線基板を例示する断面図である。

【図9】第1の実施の形態の変形例2に係る配線基板の製造工程を例示する図である。

【図10】応用例1に係る半導体パッケージを例示する断面図である。

【図11】応用例2に係る半導体パッケージを例示する断面図である。

## 【発明を実施するための形態】

## 【0010】

30

以下、図面を参照して発明を実施するための形態について説明する。なお、各図面において、同一構成部分には同一符号を付し、重複した説明を省略する場合がある。

## 【0011】

## 第1の実施の形態

## [第1の実施の形態に係る配線基板の構造]

まず、第1の実施の形態に係る配線基板の構造について説明する。図1は、第1の実施の形態に係る配線基板を例示する図であり、図1(a)は断面図、図1(b)は図1(a)のA部周辺の部分拡大平面図である。但し、図1(b)において、第1配線層10、絶縁層20、及びソルダーレジスト層60の図示を省略している。

## 【0012】

40

図1を参照するに、配線基板1は、第1配線層10と、絶縁層20と、電子部品30と、第2配線層40と、第3配線層50と、ソルダーレジスト層60及び70とを有するコアレスの配線基板である。

## 【0013】

なお、本実施の形態では、便宜上、配線基板1のソルダーレジスト層60側を上側又は一方の側、ソルダーレジスト層70側を下側又は他方の側とする。又、各部位のソルダーレジスト層60側の面を一方の面又は上面、ソルダーレジスト層70側の面を他方の面又は下面とする。但し、配線基板1は天地逆の状態で用いることができ、又は任意の角度で配置することができる。又、平面視とは対象物をソルダーレジスト層60の一方の面の法線方向から視ることを指し、平面形状とは対象物をソルダーレジスト層60の一方の面の

50

法線方向から視た形状を指すものとする。

**【0014】**

配線基板1において、第1配線層10は、微細配線11と、上層及び下層の少なくとも一方と接続される接続用配線12とを含んでいる。第1配線層10の材料としては、例えば、銅(Cu)等を用いることができる。第1配線層10の厚さは、例えば、5~10μm程度とすることができます。

**【0015】**

ここで、微細配線とは、ライン／スペースが10μm/10μm以下の配線を指す。微細配線11のライン／スペースは、例えば、3μm/3μm~5μm/5μm程度とすることができます。なお、ライン／スペースにおけるラインとは配線幅を表し、スペースとは隣り合う配線同士の間隔(配線間隔)を表す。例えば、ライン／スペースが10μm/10μmと記載されていた場合、配線幅が10μmで隣り合う配線同士の間隔が10μmであることを表す。

**【0016】**

絶縁層20は、第1絶縁膜21及び第2絶縁膜22が積層された構造を有している。第1絶縁膜21及び第2絶縁膜22としては、感光性の絶縁性樹脂や非感光性の絶縁性樹脂(例えば、熱硬化性樹脂)を用いることができる。具体的には、第1絶縁膜21及び第2絶縁膜22に用いる絶縁性樹脂として、例えば、エポキシ系樹脂、イミド系樹脂、フェノール系樹脂、シアネット系樹脂等を挙げることができる。第1絶縁膜21及び第2絶縁膜22は、シリカやアルミナ等のフィラーを含有しても構わない。なお、第1絶縁膜21と第2絶縁膜22として、同一の絶縁性樹脂を用いてもよいし、異なる絶縁性樹脂を用いてもよい。

**【0017】**

第1絶縁膜21は、第1配線層10の側面及び下面を被覆し、上面を露出している。言い換れば、第1配線層10は第1絶縁膜21に埋め込まれ、第1配線層10の上面は第1絶縁膜21の上面から露出している。第1絶縁膜21の上面と第1配線層10の上面とは、例えば、面一とすることができます。

**【0018】**

第2絶縁膜22は、電子部品30を内蔵している。電子部品30は、本体31と電極32とを備えており、第2絶縁膜22は電極32の側面及び下面を被覆し、上面を露出している。電子部品30は、例えば、チップコンデンサ(例えば、チップセラミックキャパシタ)、チップインダクタ、チップ抵抗等の受動部品とすることができますが、後述のように、半導体チップや半導体チップの積層体等の能動部品としてもよい。なお、電子部品30がチップコンデンサである場合、電子部品30の電極32の平面形状は、例えば、500×350μm程度の矩形状である。又、電子部品30がチップセラミックキャパシタである場合、電子部品30は直方体状の本体31を有し、本体31の長手方向の両端部に電極32が設けられる。そして、電極32は、本体31の両端部の側面と上下面とを連続して被覆して設けられる。

**【0019】**

絶縁層20(第1絶縁膜21)には、絶縁層20の上面側(第1絶縁膜21の上面側)に開口し、電子部品30の電極32の上面を露出するビアホール20xが形成されている。ビアホール20xは、電子部品30の電極32上に位置する接続用配線12に形成された貫通孔12x、及び接続用配線12と電子部品30の電極32との間に位置する第1絶縁膜21を貫通する貫通孔21xが連通したものである。

**【0020】**

又、絶縁層20(第2絶縁膜22)には、絶縁層20の下面側(第2絶縁膜22の下面側)に開口し、電子部品30の電極32の下面を露出するビアホール20yが形成されている。又、絶縁層20(第1絶縁膜21及び第2絶縁膜22)には、絶縁層20の下面側(第2絶縁膜22の下面側)に開口し、第1配線層10の接続用配線12の下面を露出するビアホール20zが形成されている。

10

20

30

40

50

## 【0021】

なお、図1の例では、電子部品30の1つの電極32に対して2つのピアホール20xが設けられているが、ピアホール20xは1つの電極32に対して最低1つずつ設ければよい。もちろん、ピアホール20xは1つの電極32に対して3つ以上設けてもよい。ピアホール20yについても同様である。

## 【0022】

第2配線層40は、第1配線層10の上面に形成された配線パターン、及びこの配線パターンからピアホール20x内に延在して電子部品30の電極32と直接接続されたピア配線を含んで構成されている。A部において、電子部品30の電極32と接続された第2配線層40の配線パターン（パッド）の平面形状は、例えば、円形状とすることができます。10

。

## 【0023】

例えば、電子部品30の電極32の平面形状が $500 \times 350 \mu\text{m}$ 程度の矩形状である場合、ピア配線の電極32側の径（つまり、ピアホール20xの電極32側の径）は、 $60 \sim 100 \mu\text{m}$ 程度とすることができます。又、この場合、A部において、電子部品30の電極32と接続された第2配線層40のパッドの径は、 $90 \sim 200 \mu\text{m}$ 程度とすることができます。

## 【0024】

第2配線層40の配線パターンは、第1配線層10の上面から絶縁層20の上面（第1絶縁膜21の上面）に延在してもよい。第2配線層40のピア配線は、電子部品30の電極32上に位置する接続用配線12の内壁面及び電子部品30の電極32の上面と接して両者と導通している。すなわち、第1配線層10は、第2配線層40のピア配線を介して、電子部品30の電極32と接続されている。20

## 【0025】

第2配線層40は、第1層41と、第2層42と、第3層43とを備えている。第1層41は、接続用配線12の上面に直接形成されている。電子部品30の電極32上に位置する第1層41には、ピアホール20xと連通する貫通孔41xが形成されている。第2層42は、第1層41上に直接形成されている。A部において、第2層42は、第1層41上から延在して貫通孔41x及びピアホール20xの内壁に沿って形成され、更にピアホール20x内に露出する電子部品30の電極32の上面を被覆している。第3層43は、第2層42上に直接形成されている。A部において、第3層43は、第2層42上から延在して、内壁に第2層42が形成された貫通孔41x内及びピアホール20x内を充填している。30

## 【0026】

第1層41、第2層42、及び第3層43の材料としては、例えば、銅等を用いることができる。第2配線層40の配線パターンを構成する第1層41の厚さは、例えば、 $1.5 \sim 5 \mu\text{m}$ 程度とすることができます。第2配線層40の配線パターンを構成する第2層42の厚さは、例えば、 $0.5 \sim 1 \mu\text{m}$ 程度とすることができます。第2配線層40の配線パターンを構成する第3層43の厚さは、例えば、 $4 \sim 19 \mu\text{m}$ 程度とすることができます。40

## 【0027】

第3配線層50は、絶縁層20の下面（第2絶縁膜22の下面）に形成された配線パターン、及びこの配線パターンからピアホール20y内又は20z内に延在したピア配線を含んで構成されている。但し、第3配線層50の配線パターンは、ピア配線と接続されていない配線を含んでもよい。

## 【0028】

第3配線層50は、第1層51と、第2層52とを備えている。第1層51は、絶縁層20の下面に形成されている。A部において、第1層51は、絶縁層20の下面から延在してピアホール20yの内壁に沿って形成され、更にピアホール20y内に露出する電子部品30の電極32の下面を被覆している。A部以外において、第1層51は、絶縁層20の下面から延在してピアホール20zの内壁に沿って形成され、更にピアホール20z50

内に露出する第1配線層10の接続用配線12の下面を被覆している。

**【0029】**

第2層52は、第1層51上に直接形成されている。A部において、第2層52は、第1層51上から延在して、内壁に第1層51が形成されたビアホール20y内を充填している。A部以外において、第2層52は、第1層51上から延在して、内壁に第1層51が形成されたビアホール20z内を充填している。

**【0030】**

第1層51、及び第2層52の材料としては、例えば、銅等を用いることができる。第3配線層50の配線パターンを構成する第1層51の厚さは、例えば、0.5~1μm程度とすることができます。第3配線層50の配線パターンを構成する第2層52の厚さは、10例えば、4~19μm程度とすることができます。

**【0031】**

ソルダーレジスト層60は、絶縁層20の上面（第1絶縁膜21の上面）に、第1配線層10の上面並びに第2配線層40の上面及び側面を被覆するように形成されている。ソルダーレジスト層60は開口部60xを有し、開口部60xは第2配線層40の配線パターンを選択的に露出している。開口部60x内に露出する第2配線層40の配線パターンは、半導体チップ接続用のパッドである。

**【0032】**

第2配線層40の配線パターンは、第2配線層40のビア配線と接続された配線と、ビア配線と接続されていない配線とを含んでいるが、ビア配線と接続された配線と、ビア配線と接続されていない配線とは同一高さ（同一厚さ）である。20

**【0033】**

ソルダーレジスト層70は、絶縁層20の下面に、第3配線層50を被覆するように形成されている。ソルダーレジスト層70は開口部70xを有し、開口部70xは第3配線層50の配線パターンを選択的に露出している。開口部70x内に露出する第3配線層50の配線パターンは、他の配線基板等との接続用のパッドである。

**【0034】**

ソルダーレジスト層60及び70の材料としては、例えば、感光性のエポキシ系絶縁樹脂やアクリル系絶縁樹脂等を用いることができる。ソルダーレジスト層60及び70の夫々の厚さは、例えば、5~40μm程度とすることができます。30

**【0035】**

必要に応じ、開口部60x内に露出する第2配線層40の上面、開口部70x内に露出する第3配線層50の下面に金属層を形成してもよい。金属層の例としては、Au層や、Ni/Au層（Ni層とAu層をこの順番で積層した金属層）、Ni/Pd/Au層（Ni層とPd層とAu層をこの順番で積層した金属層）等を挙げることができる。又、金属層の形成に代えて、OSP（Organic Solderability Preservative）処理等の酸化防止処理を施してもよい。なお、OSP処理により形成される表面処理層は、アゾール化合物やイミダゾール化合物等からなる有機被膜である。

**【0036】**

又、開口部60x内に露出する第2配線層40の上面、開口部70x内に露出する第3配線層50の下面に、はんだボール等の外部接続端子を設けてもよい。40

**【0037】**

[第1の実施の形態に係る配線基板の製造方法]

次に、第1の実施の形態に係る配線基板の製造方法について説明する。図2~図5は、第1の実施の形態に係る配線基板の製造工程を例示する図である。本実施の形態では、支持体上に複数の配線基板となる部分を作製し支持体を除去後個片化して各配線基板とする工程の例を示すが、支持体上に1個ずつ配線基板を作製し支持体を除去する工程としてもよい。

**【0038】**

まず、図2(a)に示す工程では、最外層が金属箔である支持体400を準備する。50

持体 400 としては、例えば、プリプレグ 401 上にキャリア付き金属箔 408 が積層されたものを用いることができる。支持体 400 の厚さは、例えば 18 ~ 100 μm 程度とすることができる。

#### 【0039】

プリプレグ 401 は、例えば、ガラス繊維やアラミド繊維等の織布や不織布(図示せず)にエポキシ系樹脂等の絶縁樹脂を含侵させたものである。キャリア付き金属箔 408 は、銅等の金属箔からなる厚さ 10 ~ 50 μm 程度の厚箔(キャリア箔)409 上に、剥離層(図示せず)を介して、銅等の金属箔からなる厚さ 1.5 ~ 5 μm 程度の薄箔 410 が剥離可能な状態で貼着されたものである。厚箔 409 は、薄箔 410 の取り扱いを容易にするための支持材として設けられている。厚箔 409 の下面是、プリプレグ 401 の上面に接着されている。10

#### 【0040】

次に、図 2 (b) 及び図 2 (c) に示す工程では、支持体 400 の薄箔 410 の上面に、微細配線 11 及び接続用配線 12 を含む第 1 配線層 10 を形成する。具体的には、例えば、支持体 400 の薄箔 410 の上面に、第 1 配線層 10 を形成する部分に開口部を備えたレジスト層(ドライフィルムレジスト等)を形成する。そして、キャリア付き金属箔 408 をめっき給電層に利用する電解めっき法により、レジスト層の開口部内に露出する薄箔 410 の上面に銅等を析出させ第 1 配線層 10 を形成する。その後、剥離液を用いてレジスト層を剥離することで、支持体 400 の薄箔 410 の上面に、微細配線 11 及び接続用配線 12 を含む第 1 配線層 10 が形成される。なお、図 2 (b) の部分拡大平面図である図 2 (c) に示すように、第 1 配線層 10 の、電子部品 30 の電極 32 が配置される予定の領域に、予め貫通孔 12x を形成しておく。20

#### 【0041】

次に、図 2 (d) に示す工程では、薄箔 410 の上面に第 1 配線層 10 の他方の面及び側面を被覆する第 1 絶縁膜 21 を形成する。具体的には、薄箔 410 の上面に第 1 配線層 10 を被覆するように、例えば熱硬化性を有するフィルム状のエポキシ系絶縁樹脂等をラミネートして第 1 絶縁膜 21 を形成する。貫通孔 12x は、第 1 絶縁膜 21 により塞がれる。なお、この時点では、第 1 絶縁膜 21 を硬化させずに B ステージ状態(半硬化状態)としておく。

#### 【0042】

次に、図 3 (a) に示す工程では、本体 31 と電極 32 とを備えた電子部品 30 を準備し、電極 32 が貫通孔 12x 上に位置するように、電子部品 30 を第 1 絶縁膜 21 上に搭載する。第 1 絶縁膜 21 は B ステージ状態であるため、第 1 絶縁膜 21 の粘性により、電子部品 30 は第 1 絶縁膜 21 上に仮固定される。電子部品 30 は、例えば、チップマウンター等を用いて第 1 絶縁膜 21 上に搭載することができる。なお、図 2 (d) に示す工程において、B ステージ状態(半硬化状態)が維持される程度の温度で第 1 絶縁膜 21 を加熱してタック性を持たせると、電子部品 30 と第 1 絶縁膜 21 との接着力が向上する点で好適である。30

#### 【0043】

次に、図 3 (b) に示す工程では、第 1 絶縁膜 21 上に電子部品 30 を被覆する第 2 絶縁膜 22 を形成する。具体的には、第 1 絶縁膜 21 上に電子部品 30 を被覆するように、例えば熱硬化性を有するフィルム状のエポキシ系絶縁樹脂等をラミネートして第 2 絶縁膜 22 を形成する。そして、第 1 絶縁膜 21 及び第 2 絶縁膜 22 を支持体 400 側に押圧しつつ、硬化温度以上に加熱して硬化させ、第 1 絶縁膜 21 及び第 2 絶縁膜 22 からなる絶縁層 20 を作製する。40

#### 【0044】

次に、図 3 (c) に示す工程では、図 3 (b) に示す構造体から支持体 400 の一部を除去する。具体的には、支持体 400 に機械的な力を加え、キャリア付き金属箔 408 の薄箔 410 と厚箔 409 との界面を剥離する。前述のように、キャリア付き金属箔 408 は、薄箔 410 上に剥離層(図示せず)を介して厚箔 409 が貼着された構造を有するた50

め、厚箔409は、剥離層(図示せず)とともに薄箔410から容易に剥離する。

#### 【0045】

これにより、薄箔410のみが絶縁層20側に残り、支持体400を構成する他の部材(プリプレグ401及び厚箔409)が除去される。但し、剥離層とともに薄箔410から厚箔409が剥離する場合の他に、剥離層内で凝集破壊が起こり、薄箔410から厚箔409が剥離する場合もある。又、剥離層から厚箔409が剥離することで、薄箔410から厚箔409を剥離する場合もある。

#### 【0046】

次に、図3(d)に示す工程では、薄箔410に貫通孔41xを形成する。又、絶縁層20に、ピアホール20x、20y、及び20zを形成する。

10

#### 【0047】

具体的には、まず、貫通孔12xに対応する位置の薄箔410にレーザを照射して薄箔410に貫通孔12xに連通する貫通孔41xを形成する。そして、レーザ照射を継続して、貫通孔12x内の第1絶縁膜21を除去すると共に、第1配線層10の接続用配線12と電子部品30の電極32との間に位置する第1絶縁膜21を除去して電子部品30の電極32の一方の面を露出する貫通孔21xを形成する。貫通孔12xと貫通孔21xとが連通する部分が、ピアホール20xである。ピアホール20y及び20zを形成するには、絶縁層20の所定位置にレーザを照射すればよい。

#### 【0048】

なお、ピアホール20xをレーザ加工法により形成した場合には、デスマニア処理を行い、ピアホール20x内に露出する電子部品30の電極32に付着した絶縁層20の樹脂残渣を除去することが好ましい。ピアホール20y及び20zについても同様である。

20

#### 【0049】

次に、図4(a)に示す工程から図5(b)に示す工程では、第2配線層40及び第3配線層50を形成する。第2配線層40及び第3配線層50は、例えば、セミアディティブ法により形成することができる。セミアディティブ法を用いて第2配線層40及び第3配線層50を形成するには、まず、図4(a)に示すように、無電解めっき法又はスパッタ法により、シード層として、銅(Cu)等からなる金属層である第2層42及び第1層51を形成する。

#### 【0050】

30

第2層42は、薄箔410の一方の面全面、貫通孔41xの内壁面、ピアホール20xの内壁面、及びピアホール20x内に露出する電子部品30の電極32の一方の面を連続的に被覆するように形成する。又、第1層51は、絶縁層20の他方の面全面、ピアホール20yの内壁面、ピアホール20y内に露出する電子部品30の電極32の他方の面、ピアホール20zの内壁面、ピアホール20z内に露出する接続用配線12の他方の面を連続的に被覆するように形成する。

#### 【0051】

次に、図4(b)に示すように、第2層42上に第2配線層40に対応する開口部700xを備えたレジスト層700(ドライフィルムレジスト等)を形成する。同様に、第1層51上に第3配線層50に対応する開口部710xを備えたレジスト層710(ドライフィルムレジスト等)を形成する。

40

#### 【0052】

次に、図4(c)に示すように、シード層である第2層42を給電層に利用した電解めっき法により、レジスト層700の開口部700x内に銅等を析出して電解めっき層である第3層43を形成する。同様に、シード層である第1層51を給電層に利用した電解めっき法により、レジスト層710の開口部710x内に銅等を析出して電解めっき層である第2層52を形成する。

#### 【0053】

次に、図5(a)に示すようにレジスト層700及び710を除去した後、図5(b)に示すように第3層43をマスクにして、第3層43に覆われていない部分の第2層42

50

及び薄箔410をエッティングにより除去する。これにより、薄箔410から第1層41が形成され、第1層41と、第2層42と、第3層43とを備えた第2配線層40が形成される。同様に、第2層52をマスクにして、第2層52に覆われていない部分の第1層51をエッティングにより除去する。これにより、第1層51と、第2層52とを備えた第3配線層50が形成される。除去すべき層が銅からなる場合には、例えば、過酸化水素／硫酸系水溶液や、過硫酸ナトリウム水溶液、過硫酸アンモニウム水溶液等のエッティング液を用いることができる。

#### 【0054】

次に、図5(c)に示す工程では、絶縁層20の一方の面に第1配線層10及び第2配線層40を被覆するソルダーレジスト層60を形成する。又、絶縁層20の他方の面に第3配線層50を被覆するソルダーレジスト層70を形成する。ソルダーレジスト層60は、例えば、液状又はペースト状の絶縁樹脂を、スクリーン印刷法、ロールコート法、又は、スピンドルコート法等により、第1配線層10及び第2配線層40を被覆するように塗布することで形成できる。或いは、フィルム状の絶縁樹脂を、第1配線層10及び第2配線層40を被覆するようにラミネートしてもよい。絶縁樹脂としては、例えば、感光性のエポキシ系絶縁樹脂やアクリル系絶縁樹脂等を用いることができる。ソルダーレジスト層70も同様の方法により形成できる。

#### 【0055】

そして、塗布又はラミネートした絶縁樹脂を露光及び現像することでソルダーレジスト層60に第2配線層40を選択的に露出する開口部60xを形成する(フォトリソグラフィ法)。同様に、ソルダーレジスト層70に第3配線層50を選択的に露出する開口部70xを形成する(フォトリソグラフィ法)。エポキシ系樹脂やポリイミド系樹脂を主成分とする非感光性の絶縁樹脂(熱硬化性樹脂)をソルダーレジスト層60及び70の材料として用いた場合には、開口部60x及び70xをレーザ加工法やプラスト処理等により形成してもよい。

#### 【0056】

必要に応じ、開口部60x内に露出する第2配線層40の一方の面、開口部70x内に露出する第3配線層50の他方の面に、例えば無電解めっき法等により金属層を形成してもよい。金属層の例としては、前述の通りである。又、開口部60x内に露出する第2配線層40の一方の面、開口部70x内に露出する第3配線層50の他方の面に、OSP処理等の酸化防止処理を施してもよい。

#### 【0057】

図5(c)に示す工程の後、図5(c)に示す構造体をスライサー等により切断位置Cで切断して個片化することにより、複数の配線基板1(図1参照)が完成する。必要に応じ、ソルダーレジスト層60の開口部60x内に露出する第2配線層40上や、ソルダーレジスト層70の開口部70x内に露出する第3配線層50上に、はんだボール等の外部接続端子を設けてもよい。

#### 【0058】

このように、配線基板1では、絶縁層20に内蔵された電子部品30と、絶縁層20に埋め込まれた第1配線層10とを、絶縁層20の一方の面側に開口し電子部品30の電極32の一方の面を露出するビアホール20xを充填するビア配線を介して接続している。この構造では、ビア配線が電子部品30の電極32の一方の面と直接接続され、導電ペーストを介さないので、電子部品30と第1配線層10との接続信頼性を向上できる。

#### 【0059】

又、電子部品30と第1配線層10とをビア配線を用いて接続する構造は、導電ペーストを介して接続する構造と比べて小さなスペースで実現できるため、第1配線層10の微細配線11を配置可能なスペースを広くすることができる。その結果、第1配線層10の微細配線11の設計自由度を向上できる。なお、導電ペーストを介して接続する構造が大きなスペースを必要とするのは、電子部品30の電極32の側面に導電ペーストのフィレットを形成するために、第1配線層10に設けるパッドの大きさを電極32の大きさより

10

20

30

40

50

も大きくする必要があるためである。

**【0060】**

又、配線基板1では、第1配線層10において、ピア配線と接続された配線と、ピア配線と接続されていない配線とは同一高さ（同一厚さ）である。そのため、ピア配線と接続された配線と、ピア配線と接続されていない配線の両方を半導体チップ接続用のパッドとして用いる場合でも、各半導体チップ接続用のパッドと、実装する半導体チップの各電極パッドとのギャップが一定となる。その結果、第1配線層10と半導体チップとの接続信頼性を向上できる。

**【0061】**

第1の実施の形態の変形例1

10

第1の実施の形態の変形例1では、接続用配線12に貫通孔12xを形成しない例を示す。なお、第1の実施の形態の変形例1において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

**【0062】**

図6は、第1の実施の形態の変形例1に係る配線基板を例示する図であり、図6(a)は断面図、図6(b)は図6(a)のA部周辺の部分拡大平面図である。但し、図6(b)において、第1配線層10、絶縁層20、及びソルダーレジスト層60の図示を省略している。

**【0063】**

図6を参照するに、配線基板2は、接続用配線12に貫通孔12xが形成されていない点が、配線基板1(図1参照)と相違する。言い換えれば、配線基板2では、ピアホール20xを形成する位置には第1配線層10の接続用配線12が設けられていない。

20

**【0064】**

配線基板2では、A部において、絶縁層20上に形成された第2配線層40は、ピアホール20xを形成する位置の近傍に配置された第1配線層10の接続用配線12上に延在し、第1配線層10と第2配線層40とが導通している。つまり、第1配線層10は、第2配線層40の配線パターン及びピア配線を介して、電子部品30の電極32と接続されている。

**【0065】**

配線基板2を作製するには、まず、第1の実施の形態の図2(a)~図3(c)と同様の工程を実行する。但し、ピアホール20xを形成する位置には第1配線層10を形成しないようにする。

30

**【0066】**

次に、図7(a)に示すように、薄箔410に貫通孔41xを形成する。又、絶縁層20に、ピアホール20x、20y、及び20zを形成する。具体的には、第1絶縁膜21に薄箔410を介してレーザを照射し、薄箔410に貫通孔41xを形成すると共に、薄箔410と電子部品30の電極32との間の第1絶縁膜21を除去して貫通孔41xに連通するピアホール20xを形成する。ピアホール20x内には、電子部品30の電極32が露出する。ピアホール20y及び20zを形成するには、絶縁層20の所定位置にレーザを照射すればよい。

40

**【0067】**

次に、図7(b)に示すように、図4(a)に示す工程と同様にして、無電解めっき法又はスパッタ法により、シード層として、銅(Cu)等からなる第2層42及び第1層51を形成する。

**【0068】**

次に、図4(b)~図5(b)に示す工程と同様にして、図7(c)に示す構造体を作製する。その後、図5(c)と同様の工程を実行し、更にスライサー等により切断位置Cで切断して個片化することにより、複数の配線基板2(図6参照)が完成する。

**【0069】**

このように、配線基板1のように必ずしも接続用配線12に貫通孔12xを形成する必

50

要はなく、絶縁層 20 の接続用配線 12 が形成されていない領域にビアホール 20x を形成してもよい。

#### 【0070】

但し、第1の実施の形態のように、接続用配線 12 に貫通孔 12x を形成しておき、貫通孔 12x に連通する貫通孔 21x を形成してビアホール 20x とする場合には、貫通孔 12x の径でビアホール 20x の径が決まるため、ビアホール 20x の径が不要に拡大することを規制できる。又、ビアホール 20x を形成する位置が貫通孔 12x が形成された位置で決まるため、ビアホール 20x を形成する位置の精度を高めることができる。

#### 【0071】

第1の実施の形態の変形例 2

10

第1の実施の形態の変形例 2 では、電子部品 30 を内蔵する絶縁層の構造が異なる例を示す。なお、第1の実施の形態の変形例 2 において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

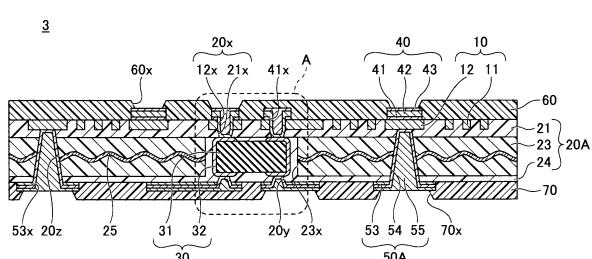

#### 【0072】

図 8 は、第1の実施の形態の変形例 2 に係る配線基板を例示する断面図である。図 8 を参照するに、配線基板 3 は、絶縁層 20 及び第3配線層 50 が絶縁層 20A 及び第3配線層 50A に置換された点が、配線基板 1 ( 図 1 参照 ) と相違する。

#### 【0073】

絶縁層 20A は、第1絶縁膜 21 と、第2絶縁膜 23 と、第3絶縁膜 24 とを備えている。第1絶縁膜 21 と第2絶縁膜 23 と第3絶縁膜 24 とは積層されている。第2絶縁膜 23 には、第2絶縁膜 23 を貫通する開口である電子部品収容部 23x が形成されており、電子部品収容部 23x 内には第1絶縁膜 21 の下面及び第2配線層 40 のビア配線を構成する第2層 42 の下端面が露出している。第2絶縁膜 23 の電子部品収容部 23x 内には電子部品 30 が配置され、電子部品 30 の電極 32 と第2配線層 40 のビア配線を構成する第2層 42 とが直接接続されている。

20

#### 【0074】

第2絶縁膜 23 は、補強材 25 を備えている。より詳しくは、第2絶縁膜 23 は、例えば、ガラスクロス ( ガラス織布 ) 等の補強材 25 にエポキシ系樹脂を主成分とする熱硬化性の非感光性樹脂を含浸させ硬化させた所謂ガラスエポキシ系樹脂である。但し、熱硬化性の非感光性樹脂はエポキシ系樹脂に限らず、例えば、ポリイミド系樹脂やシアネット系樹脂等の絶縁性樹脂を用いてもよい。第2絶縁膜 23 は、例えば、シリカやアルミナ等のフィラーを含有してもよい。又、補強材 25 としては、ガラスクロスに代えて、炭素繊維、アラミド繊維等の織布や不織布等を用いてもよい。

30

#### 【0075】

第3絶縁膜 24 は、第2絶縁膜 23 の下面に形成され、第2絶縁膜 23 の下面から電子部品収容部 23x 内に延在し、第1絶縁膜 21 の下面と電子部品収容部 23x の内壁面と電子部品 30 とが形成する空隙を充填している。第3絶縁膜 24 の材料は、例えば、第2絶縁膜 23 と同様とすることができる。図 8 の例では、第3絶縁膜 24 は補強材を備えていないが、第2絶縁膜 23 と同様に補強材を備えても構わない。

#### 【0076】

40

第3配線層 50A は、絶縁層 20A の下面 ( 第3絶縁膜 24 の下面 ) に形成された配線パターン、及びこの配線パターンからビアホール 20y 内又は 20z 内に延在したビア配線を含んで構成されている。但し、第3配線層 50A の配線パターンは、ビア配線と接続されていない配線を含んでもよい。

#### 【0077】

第3配線層 50A は、第1層 53 と、第2層 54 と、第3層 55 とを備えている。第1層 53 は、絶縁層 20A の下面に形成されている。第1層 53 には、ビアホール 20y 又は 20z と連通する貫通孔 53x が形成されている。

#### 【0078】

第2層 54 は、第1層 53 上に直接形成されている。A 部において、第2層 54 は、第

50

1層53上から延在して貫通孔53x及びビアホール20yの内壁に沿って形成され、更にビアホール20y内に露出する電子部品30の電極32の下面を被覆している。A部以外において、第2層54は、第1層53上から延在して貫通孔53x及びビアホール20zの内壁に沿って形成され、更にビアホール20z内に露出する第1配線層10の接続用配線12の下面を被覆している。

#### 【0079】

第3層55は、第2層54上に直接形成されている。A部において、第3層55は、第2層54上から延在して、内壁に第2層54が形成された貫通孔53x内及びビアホール20y内を充填している。A部以外において、第3層55は、第2層54上から延在して、内壁に第2層54が形成されたビアホール20z内を充填している。10

#### 【0080】

第1層53、第2層54、及び第3層の材料としては、例えば、銅等を用いることができる。第3配線層50Aの配線パターンを構成する第1層53の厚さは、例えば、1.5~5μm程度とすることができる。第3配線層50Aの配線パターンを構成する第2層54の厚さは、例えば、0.5~1μm程度とすることができる。第3配線層50Aの配線パターンを構成する第3層55の厚さは、例えば、4~19μm程度とすることができる。。

#### 【0081】

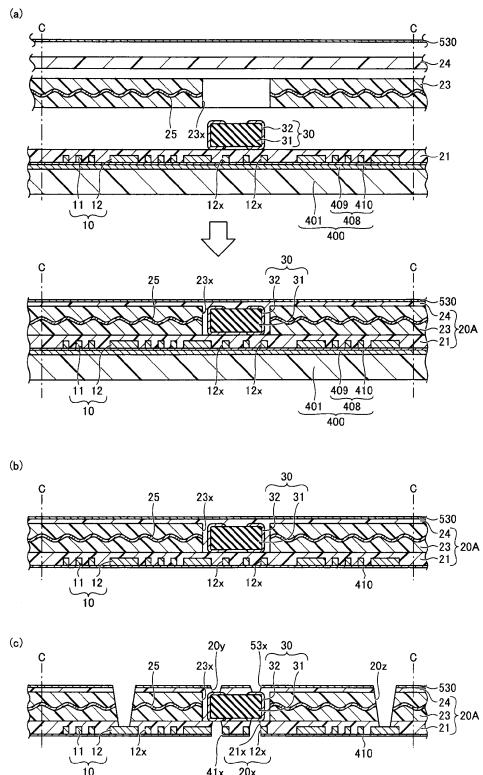

配線基板3を作製するには、まず、第1の実施の形態の図2(a)~図3(a)と同様の工程を実行する。そして、図3(b)の工程に代えて、図9(a)の工程を実行する。20

#### 【0082】

具体的には、図9(a)に示す工程では、矢印上側に示すように、補強材25を備え第2絶縁膜23を貫通する開口である電子部品収容部23xが形成されたフィルム状のエポキシ系絶縁樹脂等からなる第2絶縁膜23、フィルム状のエポキシ系絶縁樹脂等からなる第3絶縁膜24、及び銅箔等からなる薄箔530を準備する。そして、矢印下側に示すように、電子部品収容部23x内に電子部品30を収容するように、第1絶縁膜21上に第2絶縁膜23を配置し、更に第2絶縁膜23上に第3絶縁膜24及び薄箔530を順次配置する。そして、第2絶縁膜23及び第3絶縁膜24並びに薄箔530を支持体400側に押圧しつつ、第2絶縁膜23及び第3絶縁膜24を硬化温度以上に加熱して硬化させる。これにより、絶縁層20Aが形成される。電子部品収容部23x内は、第3絶縁膜24の樹脂で充填される。なお、薄箔530は、加工されて最終的に第1層53となる部分である。30

#### 【0083】

次に、図9(b)に示す工程では、図3(c)に示す工程と同様にして、図9(a)に示す構造体の支持体400に機械的な力を加え、キャリア付き金属箔408の薄箔410と厚箔409との界面を剥離する。これにより、薄箔410のみが絶縁層20A側に残り、支持体400を構成する他の部材(プリプレグ401及び厚箔409)が除去される。

#### 【0084】

次に、図9(c)に示す工程では、薄箔410に貫通孔41xを形成する。又、薄箔530に貫通孔53xを形成する。又、絶縁層20Aに、ビアホール20x、20y、及び20zを形成する。貫通孔41x及びビアホール20xの形成については、図3(d)に示す工程と同様である。40

#### 【0085】

ビアホール20yを形成するには、第3絶縁膜24に薄箔530を介してレーザを照射する。これにより、薄箔530に貫通孔53xが形成され、更に薄箔530と電子部品30の電極32との間の第3絶縁膜24が除去されて貫通孔53xと連通するビアホール20yが形成される。ビアホール20y内には、電子部品30の電極32が露出する。

#### 【0086】

同様に、ビアホール20zを形成するには、第2絶縁膜23及び第3絶縁膜24に薄箔530を介してレーザを照射する。これにより、薄箔530に貫通孔53xが形成され、50

更に薄箔 530 と第 1 配線層 10 の接続用配線 12 との間の第 2 絶縁膜 23 及び第 3 絶縁膜 24 が除去されて貫通孔 53x と連通するビアホール 20z が形成される。ビアホール 20z 内には、第 1 配線層 10 の接続用配線 12 が露出する。

#### 【0087】

次に、図 4(a) ~ 図 5(b) と同様の工程を実行する。この際、第 3 層 55 をマスクとしたエッティングで第 1 層 53 と第 2 層 54 がパターニングされ、第 3 配線層 50A が形成される。次に、図 5(c) と同様の工程を実行後、更にスライサー等により切断位置 C で切断して個片化することにより、複数の配線基板 3(図 8 参照) が完成する。

#### 【0088】

このように、第 2 絶縁膜 23 が補強材 25 を備えていることで、配線基板 3 全体の剛性 10 を高めることができる。その他の効果は、第 1 の実施の形態と同様である。

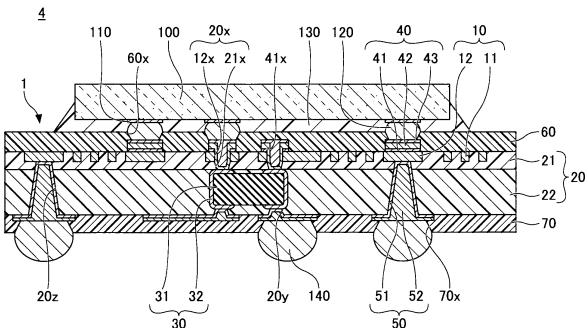

#### 【0089】

##### 配線基板の応用例 1

配線基板の応用例 1 では、第 1 の実施の形態に係る配線基板に半導体チップが搭載(フリップチップ実装)された半導体パッケージの例を示す。なお、配線基板の応用例 1 において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

#### 【0090】

図 10 は、応用例 1 に係る半導体パッケージを例示する断面図である。図 10 を参照するに、半導体パッケージ 4 は、図 1 に示す配線基板 1 と、半導体チップ 100 と、バンプ 120 と、アンダーフィル樹脂 130 と、外部接続端子 140 とを有する。半導体パッケージ 4 において、配線基板 1 のソルダーレジスト層 60 側が半導体チップ 100 が搭載されるチップ搭載面となり、配線基板 1 のソルダーレジスト層 70 側が外部接続端子 140 が形成される外部接続端子面となる。

#### 【0091】

半導体チップ 100 は、例えば、シリコン等からなる薄板化された半導体基板(図示せず)上に半導体集積回路(図示せず)等が形成されたものである。半導体基板(図示せず)には、半導体集積回路(図示せず)と電気的に接続された電極パッド 110 が形成されている。

#### 【0092】

バンプ 120 は、半導体チップ 100 の電極パッド 110 と、配線基板 1 のソルダーレジスト層 60 の開口部 60x 内に露出する第 2 配線層 40 とを電気的に接続している。バンプ 120 は、例えば、はんだバンプである。はんだバンプの材料としては、例えば Pb を含む合金、Sn と Cu の合金、Sn と Ag の合金、Sn と Ag と Cu の合金等を用いることができる。アンダーフィル樹脂 130 は、半導体チップ 100 と配線基板 1(絶縁層 20)との間に充填されている。

#### 【0093】

外部接続端子 140 は、配線基板 1 のソルダーレジスト層 70 の開口部 70x 内に露出する第 3 配線層 50 上に形成されている。外部接続端子 140 は、例えば、はんだバンプである。はんだバンプの材料としては、バンプ 120 の材料として例示したものと同様のものを用いることができる。

#### 【0094】

このように、第 1 の実施の形態に係る配線基板 1 に半導体チップ 100 を搭載することにより、半導体パッケージ 4 を実現できる。配線基板 1 のソルダーレジスト層 60 の開口部 60x 内に露出する各第 2 配線層 40 の高さは一定であるため、配線基板 1 の各第 2 配線層 40 と半導体チップ 100 の各電極パッド 110 とのギャップが一定となる。そのため、各第 2 配線層 40 と各電極パッド 110 とを容易に接続することができる。なお、配線基板 1 に代えて配線基板 2 や配線基板 3 を用いてもよい。

#### 【0095】

##### 配線基板の応用例 2

配線基板の応用例 2 では、配線基板の応用例 1 の電子部品 30 に代えて電子部品 200

10

20

30

40

50

を内蔵した半導体パッケージの例を示す。なお、配線基板の応用例2において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

#### 【0096】

図11は、応用例2に係る半導体パッケージを例示する断面図であり、図11(a)は全体図、図11(b)は図11(a)のB部周辺の部分拡大断面図である。図11を参照するに、半導体パッケージ5は、電子部品30が電子部品200に置換された点が半導体パッケージ4(図10参照)と相違する。

#### 【0097】

電子部品200は、半導体チップ210、230、及び250が積層された積層体である。半導体チップ210、230、及び250は、例えば、メモリー用チップである。

10

#### 【0098】

半導体チップ210には、半導体チップ210を貫通して半導体チップ210の両面に突出する貫通電極220が形成されている。半導体チップ230には、半導体チップ230を貫通して半導体チップ230の両面に突出する貫通電極240が形成されている。半導体チップ250には、半導体チップ250を貫通して半導体チップ250の両面に突出する貫通電極260が形成されている。

#### 【0099】

貫通電極220の半導体チップ210の下面側に突出する部分と、貫通電極240の半導体チップ230の上面側に突出する部分とは、はんだ等の接合部270を介して接合されている。又、貫通電極240の半導体チップ230の下面側に突出する部分と、貫通電極260の半導体チップ250の上面側に突出する部分とは、はんだ等の接合部280を介して接合されている。

20

#### 【0100】

貫通電極220の半導体チップ210の上面側に突出する部分は、第2配線層40のビア配線を構成する第2層42と直接接続されている。又、貫通電極260の半導体チップ250の下面側に突出する部分は、第3配線層50のビア配線を構成する第1層51と直接接続されている。

30

#### 【0101】

このように、配線基板には、電子部品として半導体チップの積層体を内蔵してもよい。この際、半導体チップの積層数は2つでもよいし、4つ以上でもよい。又、各半導体チップは同一機能を備えていてもよいし、異なる機能を備えたものが混在してもよい。又、電子部品として半導体チップの積層体に代えて、単一の半導体チップを内蔵してもよい。

#### 【0102】

以上、好ましい実施の形態等について詳説したが、上述した実施の形態等に制限されることなく、特許請求の範囲に記載された範囲を逸脱することなく、上述した実施の形態等に種々の変形及び置換を加えることができる。

#### 【0103】

例えば、配線基板の製造方法において、プリプレグ401の両面にキャリア付き金属箔408を積層して支持体とし、支持体の両面側に配線基板となる各構成部を形成し、その後支持体の不要部を分離する工程としてもよい。

40

#### 【符号の説明】

#### 【0104】

1、2、3 配線基板

4、5 半導体パッケージ

10 第1配線層

11 微細配線

12 接続用配線

12x、14x、21x、41x、53x 貫通孔

20、20A 絶縁層

20x、20y、20z ビアホール

50

|                     |           |    |

|---------------------|-----------|----|

| 2 1                 | 第 1 絶縁膜   |    |

| 2 2、 2 3            | 第 2 絶縁膜   |    |

| 2 3 x               | 電子部品収容部   |    |

| 2 4                 | 第 3 絶縁膜   |    |

| 2 5                 | 補強材       |    |

| 3 0、 2 0 0          | 電子部品      |    |

| 3 1                 | 本体        |    |

| 3 2                 | 電極        |    |

| 4 0                 | 第 2 配線層   |    |

| 4 1、 5 1、 5 3       | 第 1 層     | 10 |

| 4 2、 5 2、 5 4       | 第 2 層     |    |

| 4 3、 5 5            | 第 3 層     |    |

| 5 0、 5 0 A          | 第 3 配線層   |    |

| 6 0、 7 0            | ソルダーレジスト層 |    |

| 6 0 x、 7 0 x        | 開口部       |    |

| 1 0 0               | 半導体チップ    |    |

| 1 1 0               | 電極パッド     |    |

| 1 2 0               | バンプ       |    |

| 1 3 0               | アンダーフィル樹脂 |    |

| 1 4 0               | 外部接続端子    | 20 |

| 2 1 0、 2 3 0、 2 5 0 | 半導体チップ    |    |

| 2 2 0、 2 4 0、 2 6 0 | 貫通電極      |    |

| 2 7 0、 2 8 0        | 接合部       |    |

| 4 0 0               | 支持体       |    |

| 4 0 8               | キャリア付き金属箔 |    |

| 4 0 9               | 厚箔        |    |

| 4 1 0、 5 3 0        | 薄箔        |    |

【図1】

第1の実施の形態に係る配線基板を例示する図

【図2】

第1の実施の形態に係る配線基板の製造工程を例示する図(その1)

【図3】

第1の実施の形態に係る配線基板の製造工程を例示する図(その2)

【図4】

第1の実施の形態に係る配線基板の製造工程を例示する図(その3)

【図5】

第1の実施の形態に係る配線基板の製造工程を例示する図(その4)

【図6】

第1の実施の形態の変形例1に係る配線基板を例示する図

【図7】

第1の実施の形態の変形例1に係る配線基板の製造工程を例示する図

【図8】

第1の実施の形態の変形例2に係る配線基板を例示する断面図

【図9】

第1の実施の形態の変形例2に係る配線基板の製造工程を例示する図

【図10】

応用例1に係る半導体パッケージを例示する断面図

---

フロントページの続き

(72)発明者 深瀬 克哉

長野県長野市小島田町80番地 新光電気工業株式会社内

審査官 黒田 久美子

(56)参考文献 国際公開第2009/101723(WO,A1)

特開2015-226013(JP,A)

(58)調査した分野(Int.Cl., DB名)

H05K 3/46

H05K 3/40

H05K 3/42