(10) DE 10 2004 059 620 B4 2011.07.28

(12)

## Patentschrift

(21) Aktenzeichen: **10 2004 059 620.4**

(22) Anmelddatag: **10.12.2004**

(43) Offenlegungstag: **18.08.2005**

(45) Veröffentlichungstag

der Patenterteilung: **28.07.2011**

(51) Int Cl.: **H01L 29/06 (2006.01)**

**H01L 29/78 (2006.01)**

**H01L 29/739 (2006.01)**

**H01L 29/861 (2006.01)**

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

**2004-016663**      **26.01.2004**      **JP**

(73) Patentinhaber:

**Mitsubishi Denki K.K., Tokyo, JP**

(74) Vertreter:

**PRÜFER & PARTNER GbR, 81479, München, DE**

(72) Erfinder:

**Hatake, Kazunari, Tokio/Tokyo, JP**

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

**US 47 66 474 A**

**JP 10-3 41 018 AA**

(54) Bezeichnung: **Halbleitervorrichtung**

(57) Hauptanspruch: Halbleitervorrichtung mit einem ersten Halbleiterbereich (110) eines ersten Leitungstyps, einem zweiten Halbleiterbereich (111) eines zweiten Leitungstyps und einem dritten Halbleiterbereich (117) des ersten Leitungstyps, die eine höhere Dotierungskonzentration aufweisen als der erste Halbleiterbereich (110) und so ausgebildet sind, dass der erste Halbleiterbereich (110) zwischen ihnen liegt, einer ersten Isolierschicht (LA), die auf dem ersten Halbleiterbereich (110) ausgebildet ist, einer Mehrzahl von ersten schwebenden Feldplatten (FA), die auf der ersten Isolierschicht (LA) ausgebildet sind und oberhalb des ersten Halbleiterbereichs (110) in einer ersten Richtung angeordnet sind, die eine Richtung von dem dritten Halbleiterbereich (117) aus zu dem zweiten Halbleiterbereich (111) hin ist, einer zweiten Isolierschicht (LB), die auf den ersten schwebenden Feldplatten (FA) ausgebildet ist, einer Mehrzahl von zweiten schwebenden Feldplatten (FB), die auf der zweiten Isolierschicht (LB) ausgebildet sind und oberhalb des ersten Halbleiterbereichs (110) in der ersten Richtung angeordnet sind, einer dritten...

## Beschreibung

**[0001]** Die vorliegende Erfindung bezieht sich auf eine Technik zum Sicherstellen einer Verbesserung der Stabilität der Spannungsfestigkeit und einer Erhöhung der Spannungsfestigkeit in einer Halbleitervorrichtung, insbesondere in einer Halbleitervorrichtung mit hoher Durchbruchspannung.

**[0002]** Um zwei Leistungsschaltvorrichtungen (MOSFET, IGBT oder dergleichen) auf einer hohen Seite und einer niedrigen Seite zu treiben, z. B. in einem Inverter vom Halbbrückentyp, weist eine Leistungsvorrichtungstreiberinrichtung eine hochseitige (Hochpotentialinsel) Treiberschaltung zum Treiben der hochseitigen Leistungsschaltvorrichtung und eine niedrigseitige Treiberschaltung zum Treiben der niedrigseitigen Leistungsschaltvorrichtung auf. Da die hochseitige Schaltung in einem Zustand betrieben wird, in dem ihr Potential im Hinblick auf das Masspotential schwebt, ist eine solche Leistungsvorrichtungstreiberinrichtung mit einer Pegelschiebeschaltung zum Übertragen eines Trebersignals zu der hochseitigen Treiberschaltung versehen. Eine Pegelschiebeschaltung von einem allgemeinen Typ besteht aus einem Spannungsschaltelement mit hoher Durchbruchsspannung wie z. B. einem MOSFET, der von einem Trebersignal getrieben wird, und einem dazu in Reihe geschalteten Pegelschiebewiderstand (siehe die später erörterte [Fig. 2](#)). Ein Spannungsabfall an dem Pegelschiebewiderstand wird als Trebersignal an die hochseitige Treiberschaltung übertragen. Das Schaltelement hoher Durchbruchsspannung benötigt eine stabile und hohe Spannungsfestigkeit, um einen Durchbruch in der Leistungsvorrichtungstreiberinrichtung oder eine Erzeugung falscher Signale in der Pegelschiebeschaltung zu verhindern.

**[0003]** Eine Technik für die Verbesserung der Stabilität und Erhöhung der Spannungsfestigkeit des Schaltelements mit hoher Durchbruchsspannung wie z. B. einer Diode, sind Verfahren bekannt wie z. B. ein Verfahren des Bildens einer Mehrzahl von Feldplatten in einem schwebenden Zustand (im folgenden einfach als "schwebende Feldplatten" bezeichnet) auf einem Halbleitersubstrat mit einer dazwischen liegenden Isolierschicht, um eine Verteilung eines elektrischen Felds in einer Substratoberfläche gleichförmiger zu machen (z. B. in der JP 10-341 018 A gezeigt), sowie ein Verfahren des Verwendens einer RESURF-Struktur als Halbleitervorrichtungsstruktur, um die Verarmung in einem Substrat zu beschleunigen (in dem Patent US 4,292,642 A gezeigt).

**[0004]** Wenn eine hohe Spannung an eine Halbleitervorrichtung mit hoher Durchbruchsspannung in einem ausgeschalteten Zustand (AUS-Zustand) angelegt wird, hält die Halbleitervorrichtung mit hoher Durchbruchsspannung die Spannung. Wenn dabei in einem Halbleitersubstrat, auf dem die Vorrichtung ge-

bildet ist, lokal eine Konzentration des elektrischen Feldes (eine Spitze des elektrischen Feldes) auftritt, wird ein Durchbruch in einem pn-Übergang oder ein Durchbruch in einer Isolierschicht an diesem lokalen Abschnitt leichter bewirkt, und das bewirkt eine Verschlechterung der Spannungsfestigkeitseigenschaft. Wenn die Halbleitervorrichtung großer Durchbruchsspannung ein n-Kanal-MOSFET mit einer RESURF-Struktur ist, tritt z. B. eine Spitze eines elektrischen Feldes leicht nahe einer drainseitigen n-Schicht in einer Übergangstiefe zwischen einer an einem oberen Abschnitt des Halbleitersubstrats gebildeten n<sup>-</sup>-Schicht und einer darunter liegenden p<sup>-</sup>-Substrat und einem Substrat des Halbleitersubstrats unterhalb einer Elektrode und einem Kantenabschnitt der Feldplatte auf (im Detail später erörtert).

**[0005]** Bei der tatsächlichen Verwendung der Halbleitervorrichtung hoher Durchbruchsspannung ist ihre obere Oberfläche für den Zusammenbau mit einer Überzugisolierschicht oder einer Epoxidschicht bedeckt. Wenn eine hohe Spannung zwischen einem Drain und einer Source des MOSFET in dem AUS-Zustand angelegt ist und eine elektrische Feldspitze im Inneren auftritt, bewirkt dies z. B. eine Polarisierung der Überzugisolierschicht oder der Epoxidschicht für den Zusammenbau. Die durch die Polarisierung erzeugten elektrischen Ladungen werden für eine bestimmte Zeitspanne, nachdem das Anlegen der hohen Spannung beendet ist, gehalten. Wenn dann das nächste Mal eine hohe Spannung zwischen Drain und Source des MOSFET angelegt wird, wird mit den elektrischen Ladungen die Ausdehnung einer Verarmungsschicht lokal (insbesondere nah einer Oberfläche eines Siliziumsubstrats) unterdrückt. In dem lokalen Abschnitt, in dem die Ausdehnung der Verarmungsschicht unterdrückt wird, wird die Spitze des elektrischen Feldes höher. Wenn die Spitze in der Siliziumoberfläche ein durchbruchkritisches elektrisches Feld erreicht, bewirkt dies eine Verringerung oder eine Schwankung der Spannungsfestigkeit oder unter bestimmten Umständen einen Durchbruch der Halbleitervorrichtung.

**[0006]** US 4,766,474 A zeigt offenbar einen MOS-Transistor, bei dem mehrschichtige Abdeckelemente zum Abdecken eines Kanalbereichs bereitgestellt sind. Über dem Kanalbereich sind eine erste, zweite und dritte Isolierschicht angeordnet. Auf der ersten und zweiten Isolierschicht befinden sich Deckschichten, von denen keine mit einer Elektrode des MOS-Transistors verbunden ist. Eine Feldplattenschicht auf der dritten Isolierschicht ist durch Elemente gebildet, die mit Elektroden des MOS-Transistors verbunden sind.

**[0007]** Die Aufgabe der vorliegenden Erfindung besteht darin, eine Verbesserung der Stabilität der Spannungsfestigkeit und eine Erhöhung der Spannungsfestigkeit sicherzustellen, in dem eine Konzen-

tration eines elektrischen Felds in einem Substrat, auf dem die Halbleitervorrichtung ausgebildet ist, verringert wird.

**[0008]** Die Aufgabe wird gelöst durch eine Halbleitervorrichtung gemäß Anspruch 1, 5, oder 8. Weiterbildungen der Erfindung sind jeweils in den Unteransprüchen gekennzeichnet.

**[0009]** Da bei der Halbleitervorrichtung gemäß Anspruch 1 die Dicke  $a$  der ersten Isolierschicht groß ist, wird eine Verzerrung von Äquipotentiallinien in der ersten Isolierschicht unterdrückt, und daher wird eine elektrische Feldkonzentration in einer oberen Oberfläche des ersten Halbleiterbereichs verringert. Da der Abstand  $b$  zwischen den ersten schwebenden Feldplatten und den zweiten schwebenden Feldplatten klein ist, bewirkt weiter ein durch die ersten schwebenden Feldplatten und zweiten schwebenden Feldplatten gebildeter Kondensator eine hohe kapazitive Kopplungswirkung, um die Polarisierung der zweiten Isolierschicht zu beschleunigen. Damit wird es für die Verarmungsschicht leichter, sich in einem oberen Abschnitt des ersten Halbleiterbereichs unter einer Lücke zwischen zwei benachbarten ersten schwebenden Feldplatten auszubreiten, wo die Verarmungsschicht herkömmlicherweise Ausbreitungsschwierigkeiten hat, und die elektrische Feldkonzentration in dem Bereich wird dadurch verringert. Somit wird ein Spielraum im Hinblick auf die elektrische Feldstärke an einem Punkt eines durchbruchkritischen elektrischen Feldes größer und Probleme der Vorrichtung wie z. B. eine Verringerung der Spannungsfestigkeit und eine Instabilität der Spannungsfestigkeitseigenschaft kann unterdrückt werden. Demzufolge kann die Vorrichtung eine hohe Spannungsfestigkeit stabil halten.

**[0010]** Bei der Halbleitervorrichtung gemäß Anspruch 5 wird die elektrische Feldkonzentration in der oberen Oberfläche des ersten Halbleiterbereichs nahe dem dritten Halbleiterbereich verringert. Der Punkt des durchbruchkritischen elektrischen Feldes der Vorrichtung liegt in vielen Fällen nahe dem dritten Halbleiterbereich, und da die elektrische Feldkonzentration in der Nähe des Bereichs verringert wird, können Probleme der Vorrichtung wie eine Verringerung der Spannungsfestigkeit und eine Instabilität der Spannungsfestigkeitseigenschaft unterdrückt werden. Demzufolge kann die Vorrichtung eine hohe Spannungsfestigkeit stabil halten.

**[0011]** Bei der Halbleitervorrichtung gemäß Anspruch 8 wird die elektrische Feldkonzentration in der oberen Oberfläche des ersten Halbleiterbereichs nahe dem dritten Halbleiterbereich verringert. Der Punkt des durchbruchkritischen elektrischen Feldes der Vorrichtung liegt in vielen Fällen nahe dem dritten Halbleiterbereich, und da die elektrische Feldkonzentration in der Nähe des Bereichs verringert wird,

können Probleme der Vorrichtung wie eine Verringerung der Spannungsfestigkeit und eine Instabilität der Spannungsfestigkeitseigenschaft unterdrückt werden. Demzufolge kann die Vorrichtung eine hohe Spannungsfestigkeit stabil halten.

**[0012]** Weitere Merkmale und Zweckmäßigkeiten der Erfindung ergeben sich aus der Beschreibung von Ausführungsbeispielen anhand der beigefügten Zeichnungen.

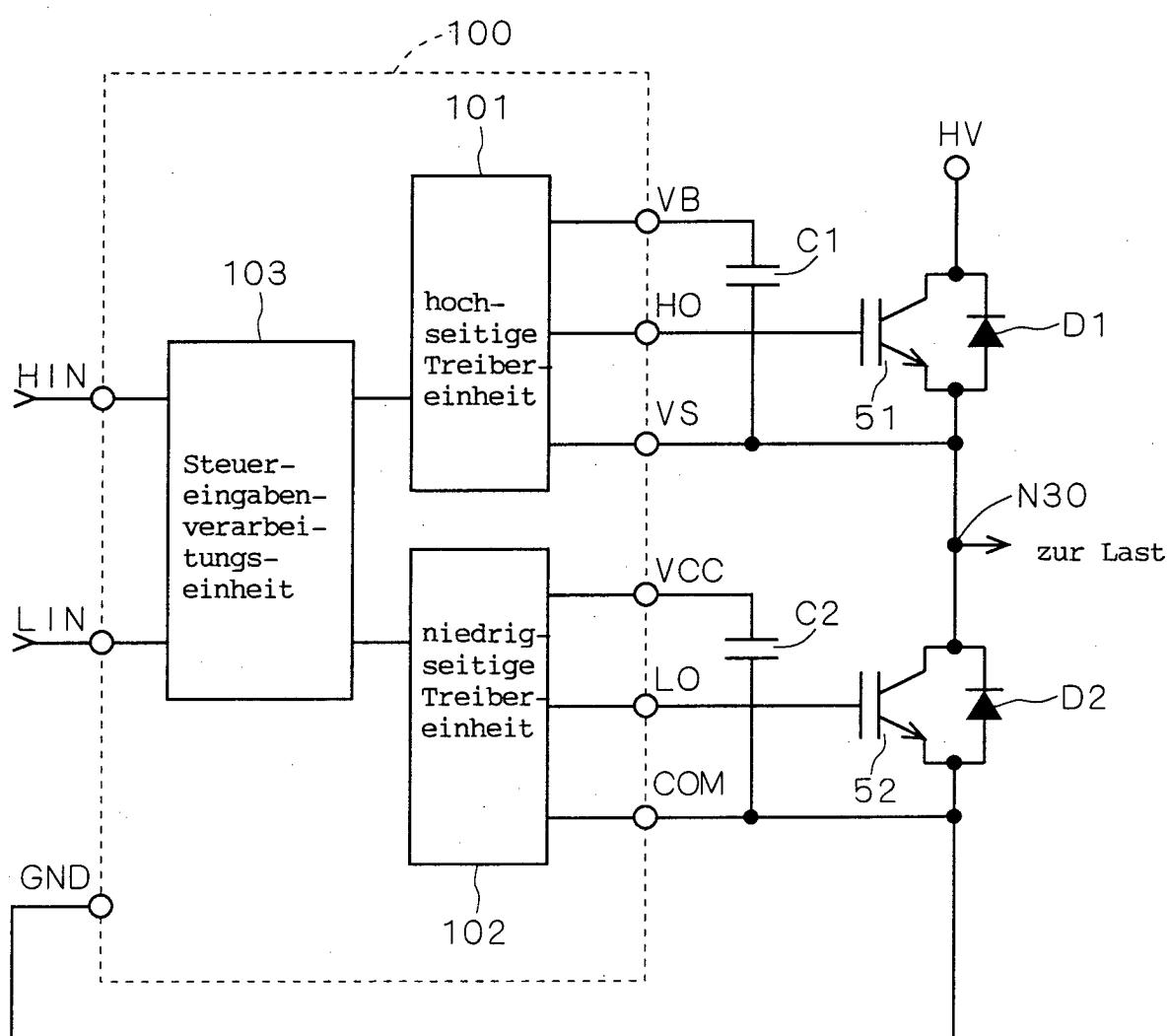

**[0013]** [Fig. 1](#) ist eine Darstellung einer Leistungsvorrichtung und einer Leistungsvorrichtungstreiberseinrichtung.

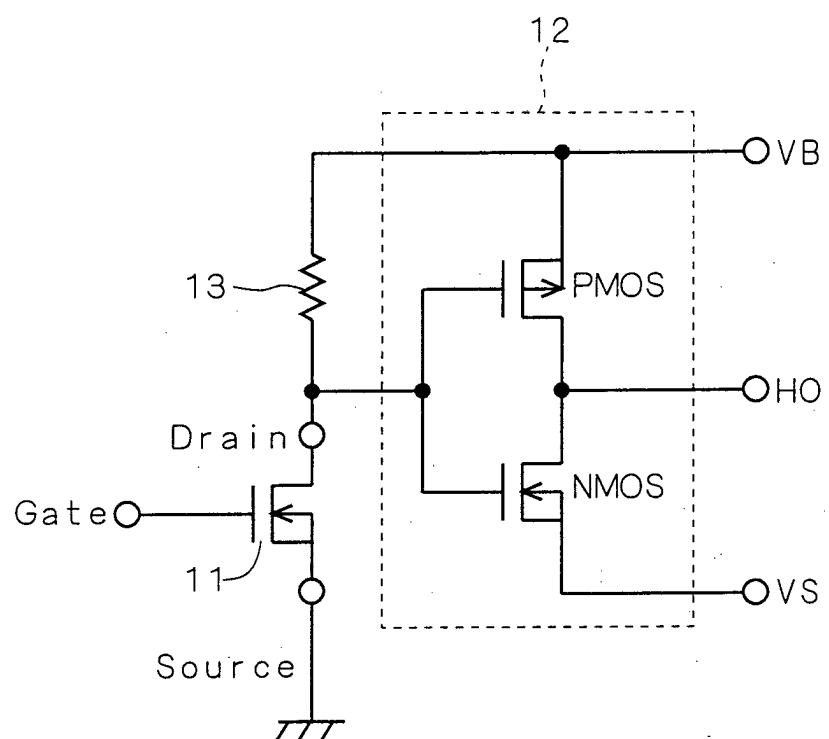

**[0014]** [Fig. 2](#) ist ein Schaltbild eines Hauptabschnitts einer hochseitigen Treibereinheit in der Leistungsvorrichtungstreiberseinrichtung.

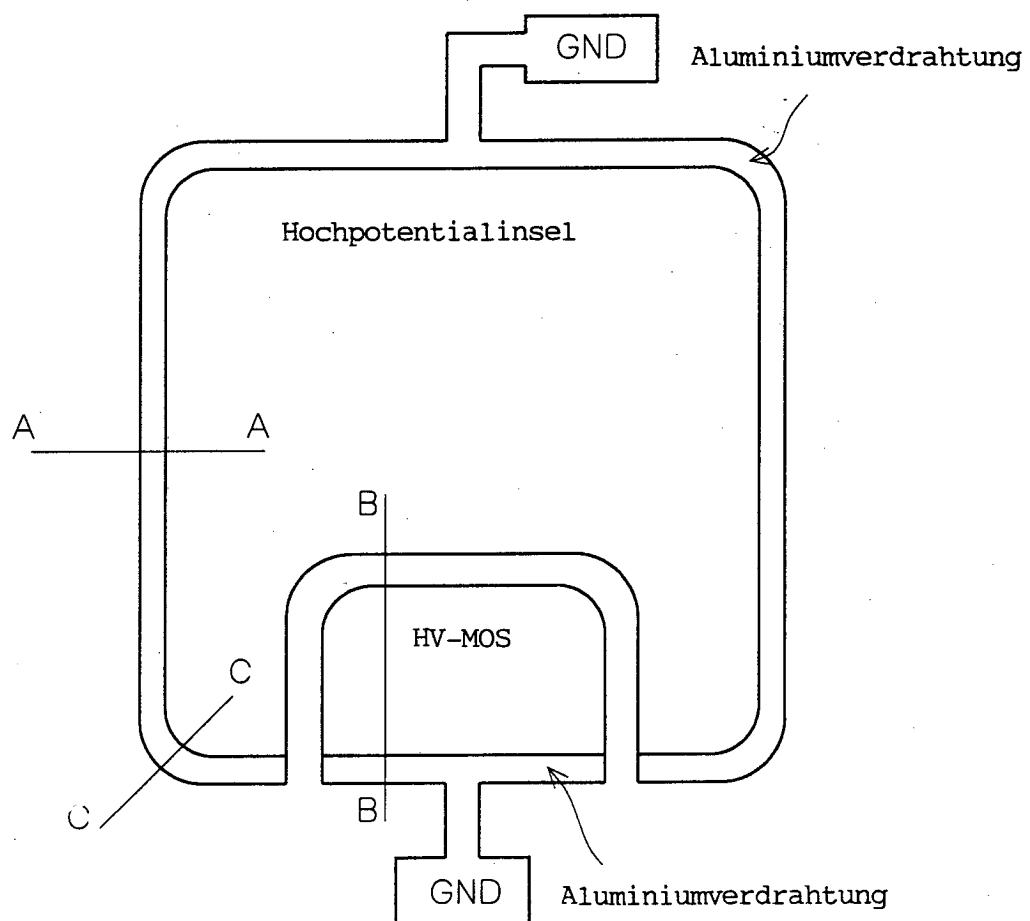

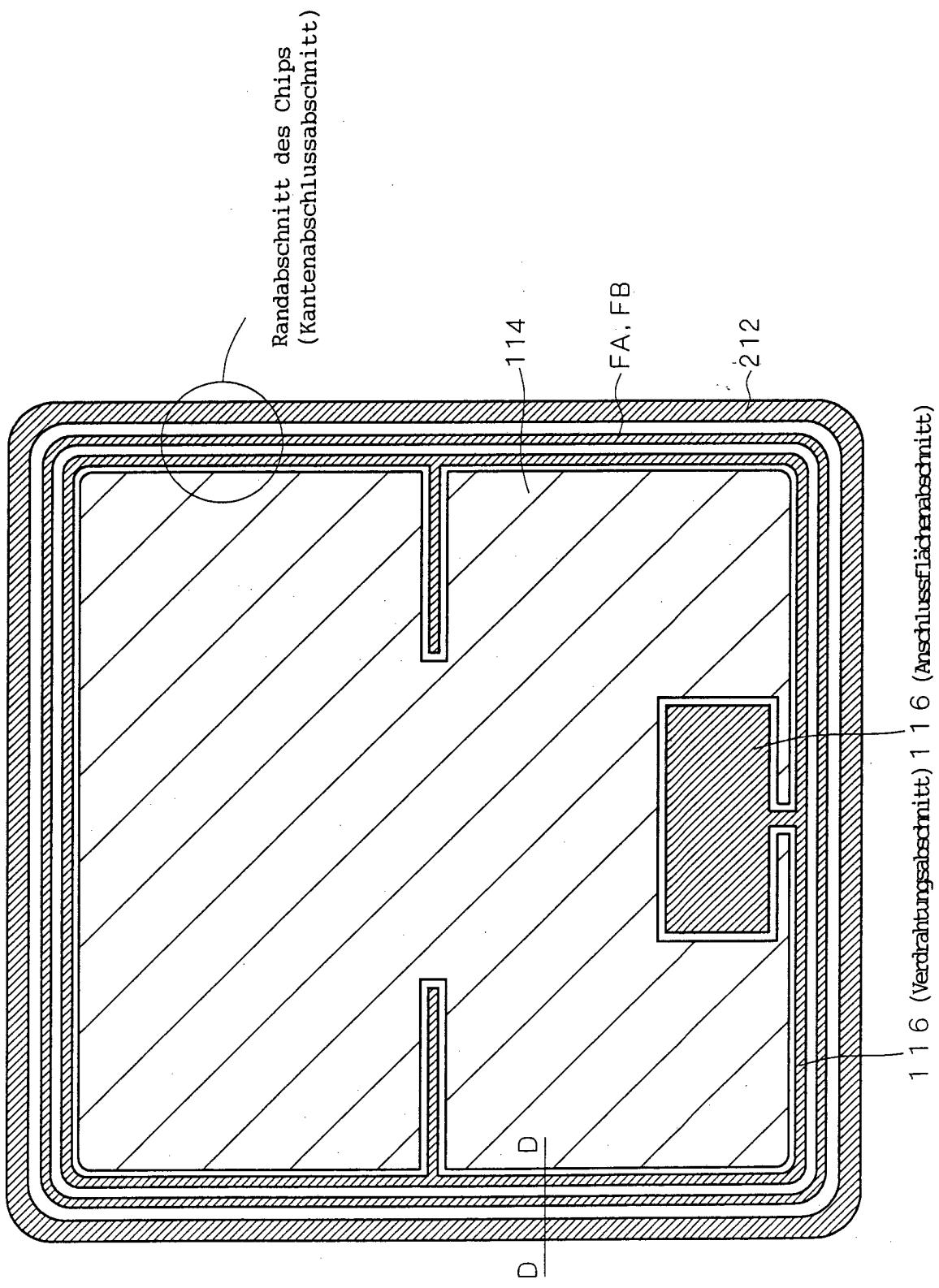

**[0015]** [Fig. 3](#) ist eine schematische Draufsicht auf ein Layout der hochseitigen Treibereinheit in der Leistungsvorrichtungstreiberseinrichtung.

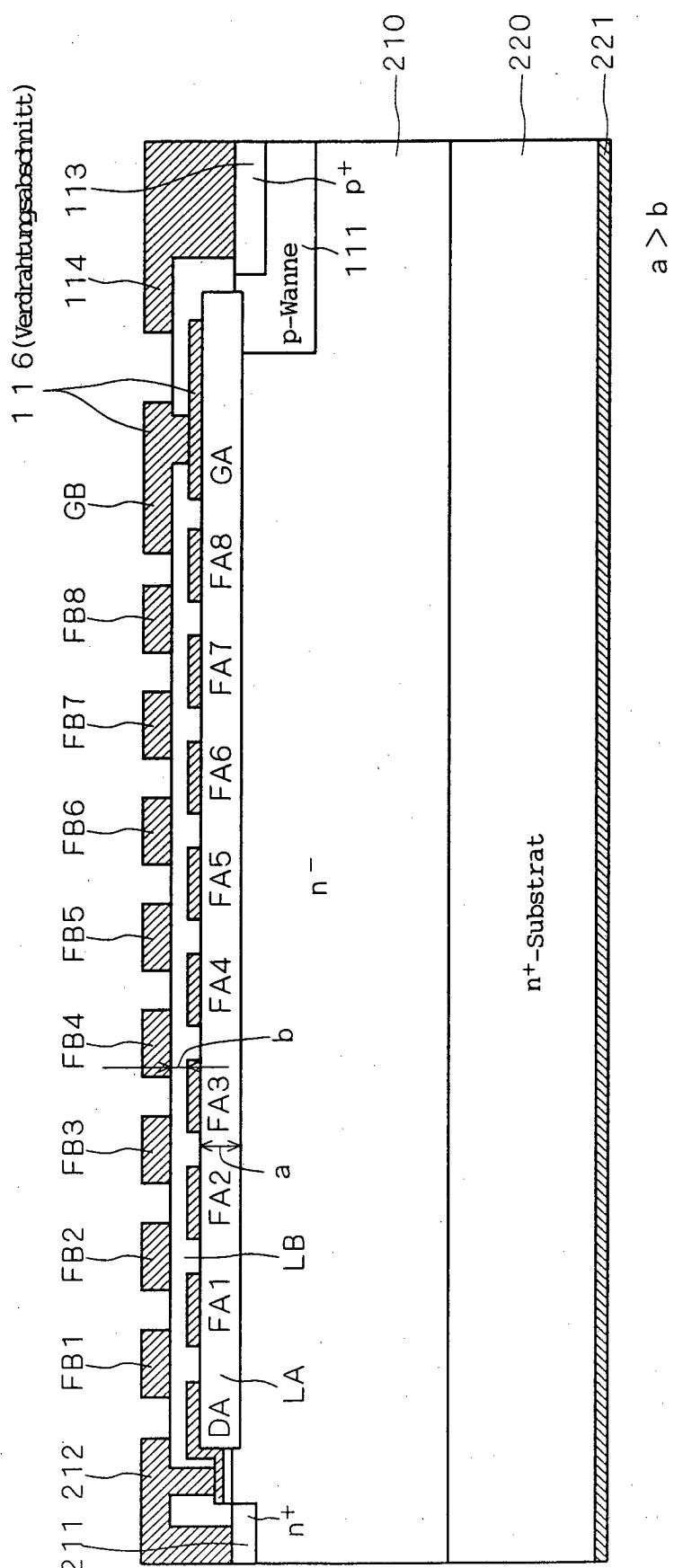

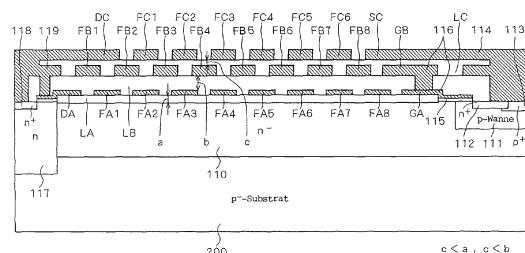

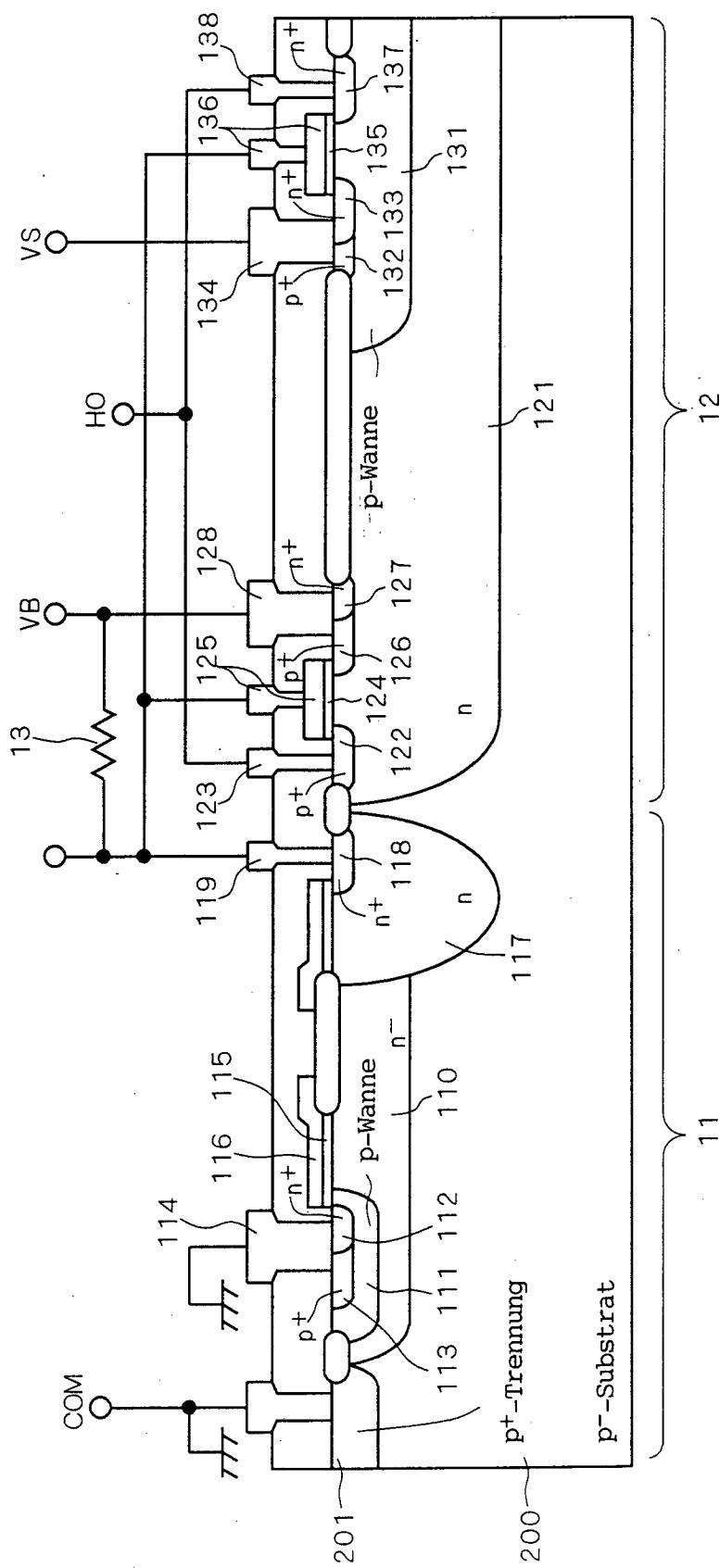

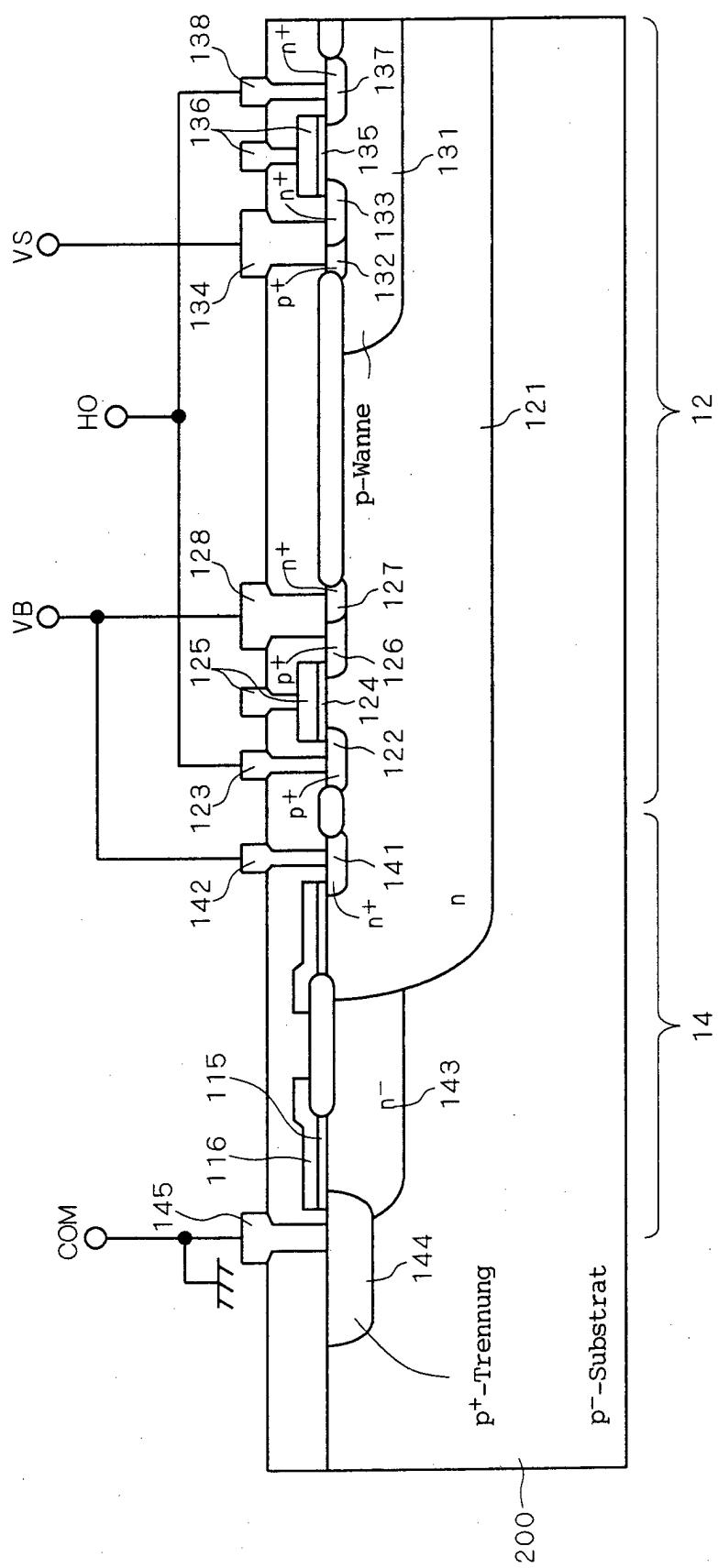

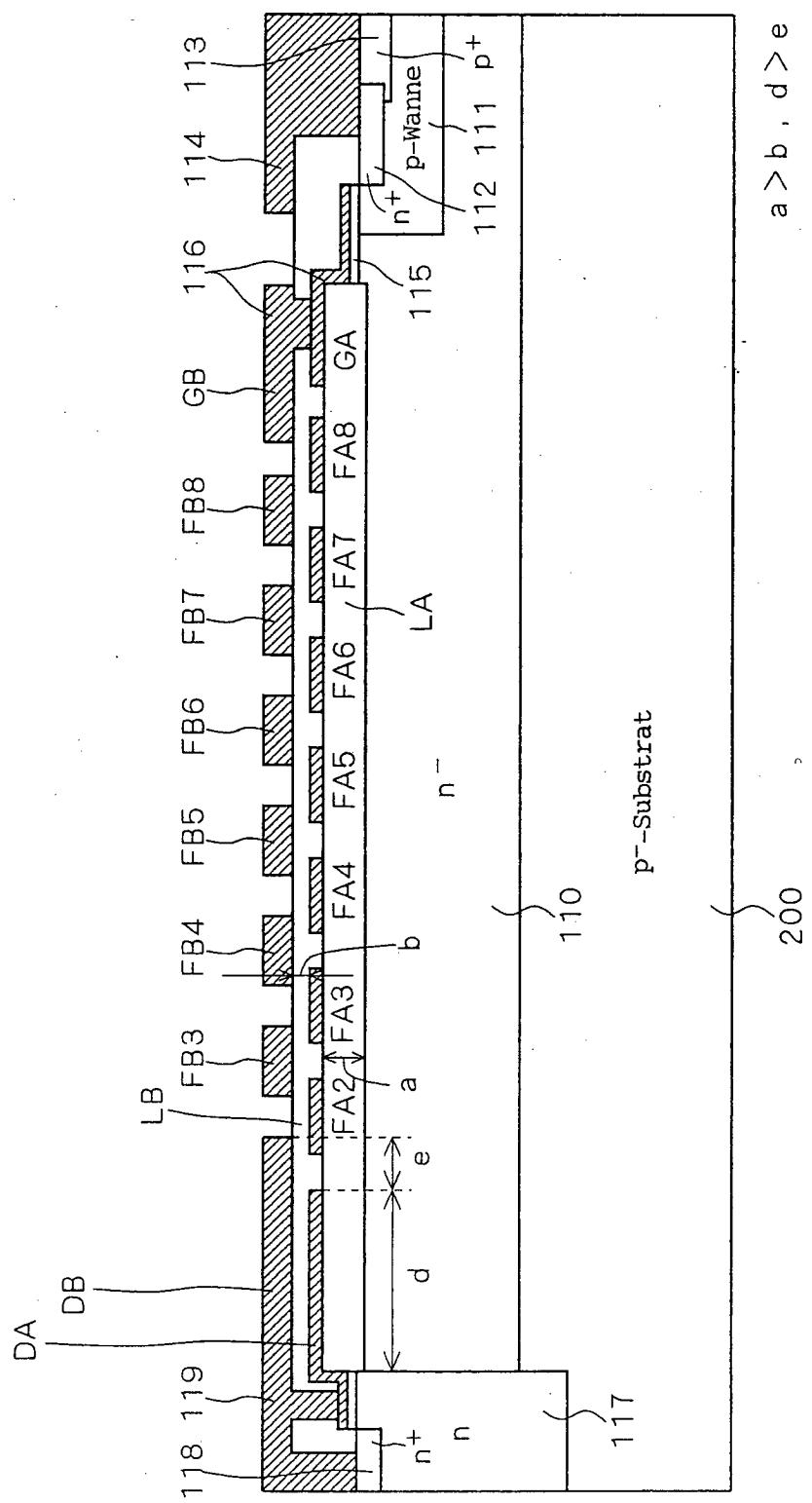

**[0016]** [Fig. 4](#) und [Fig. 5](#) sind schematische Querschnitte, die jeweils einen Hauptabschnitt der hochseitigen Treibereinheit in der Leistungsvorrichtungstreiberseinrichtung zeigen.

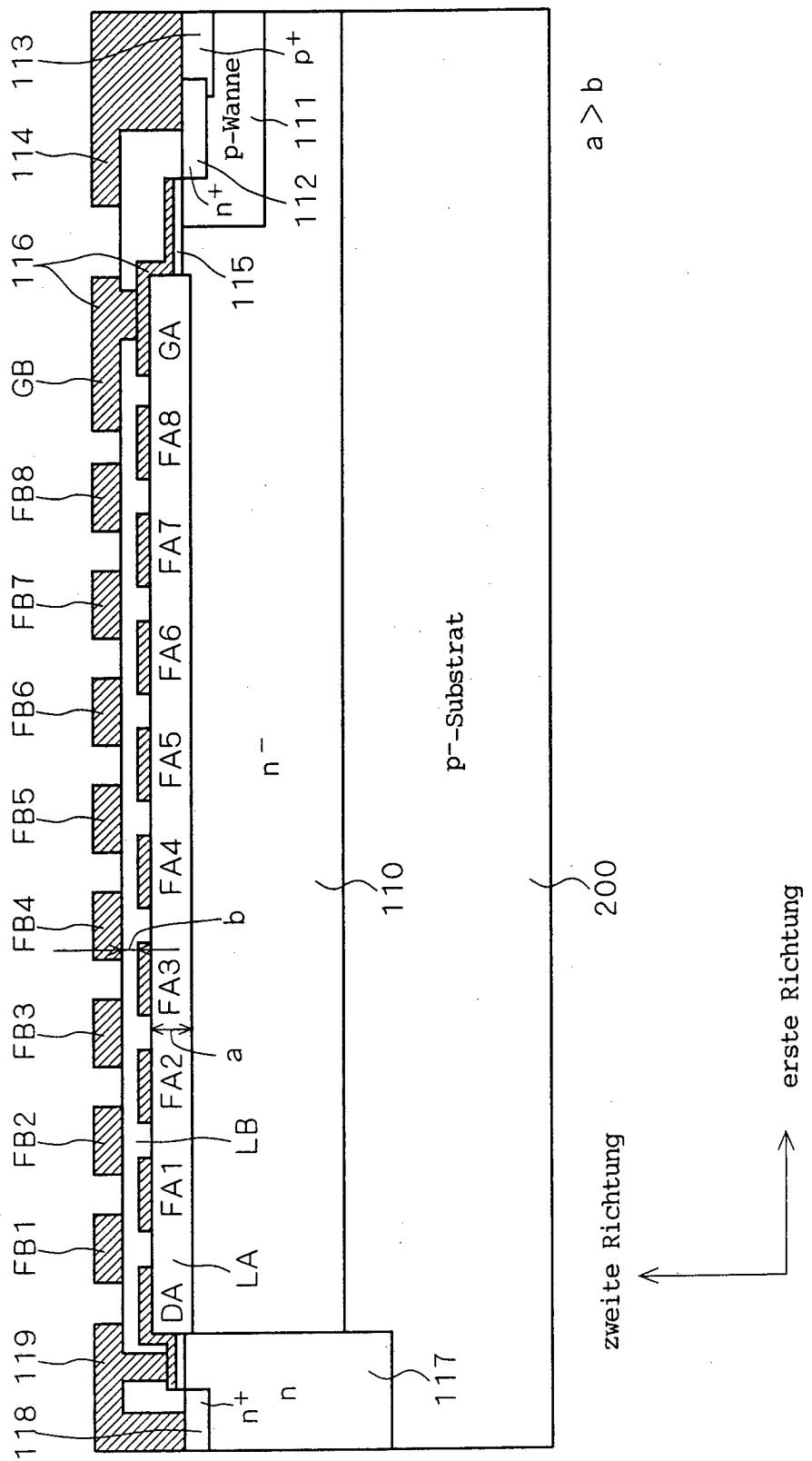

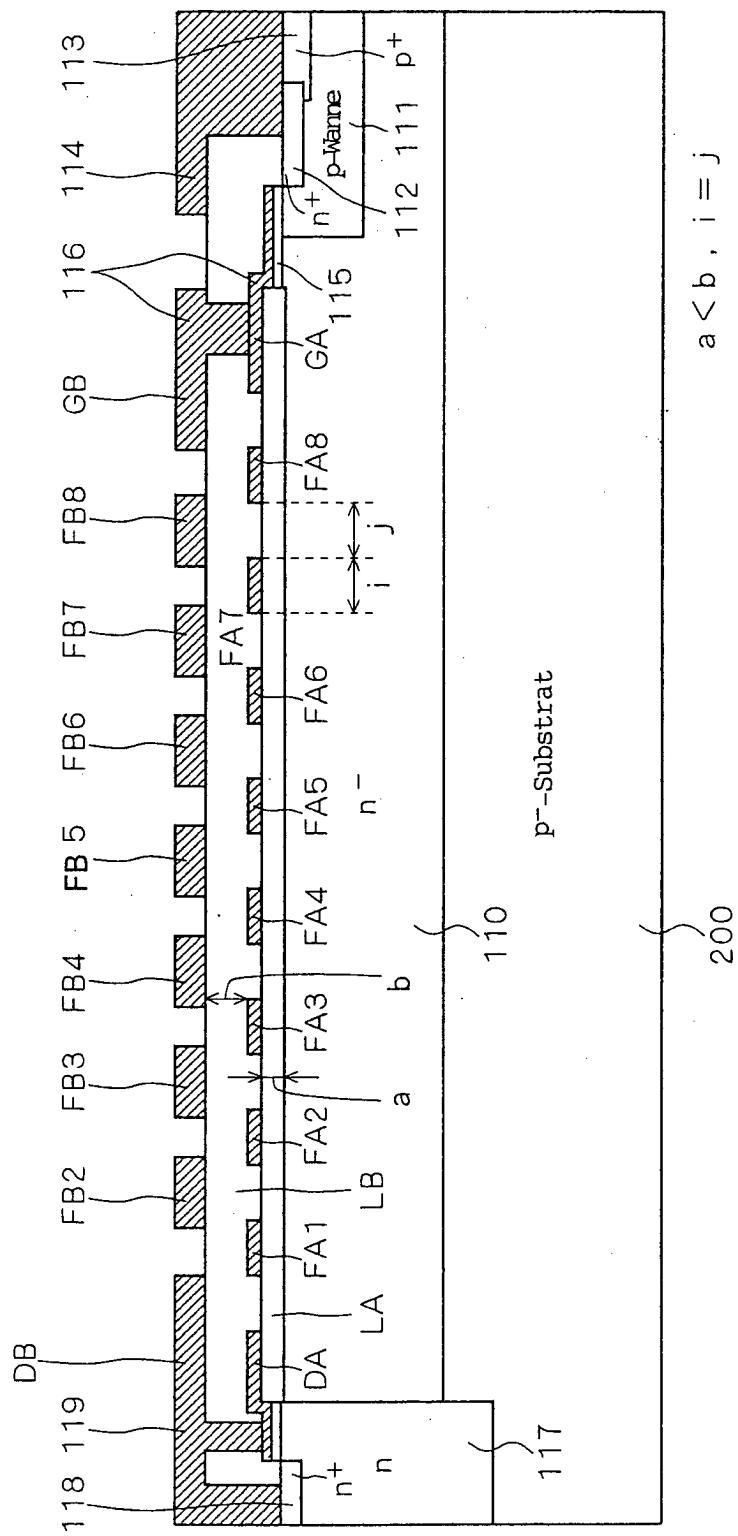

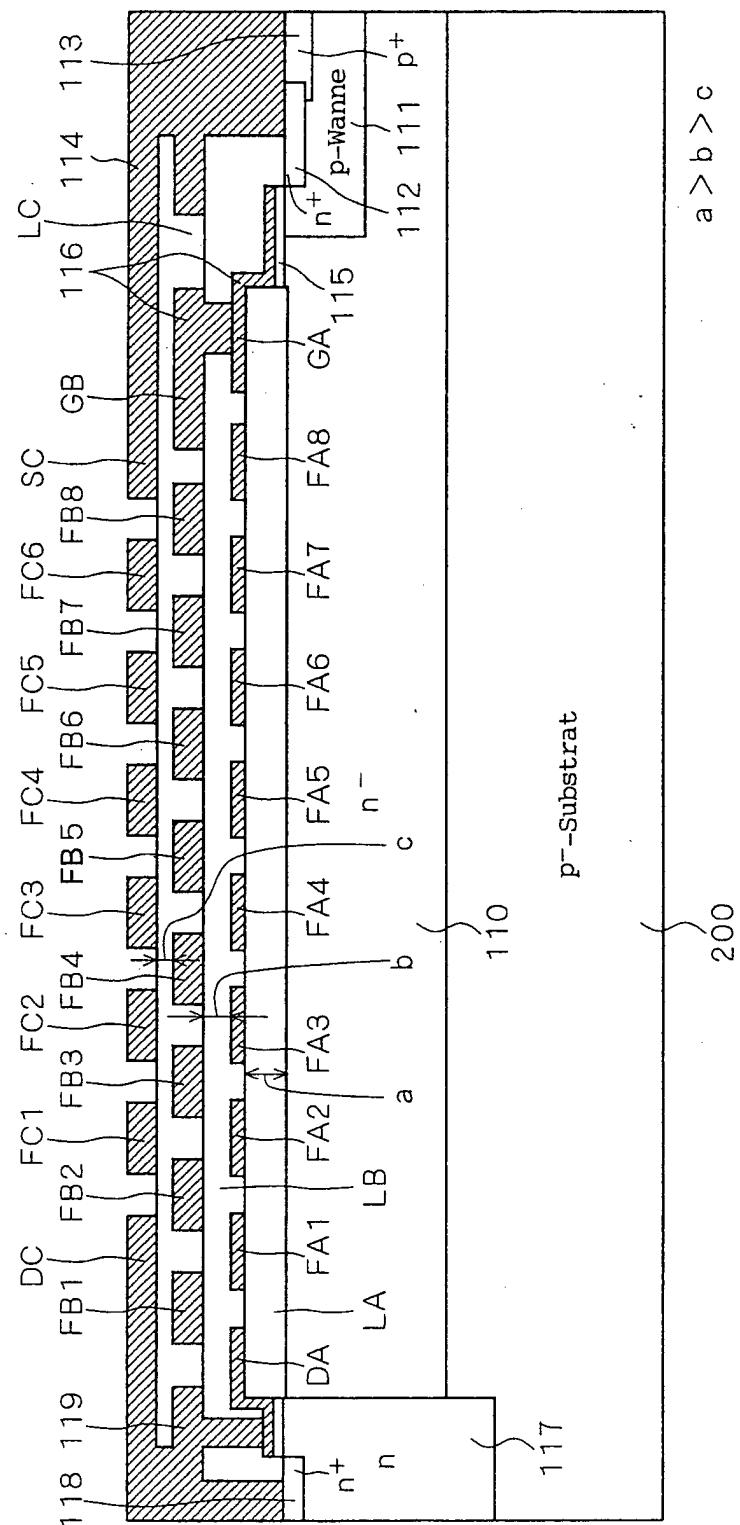

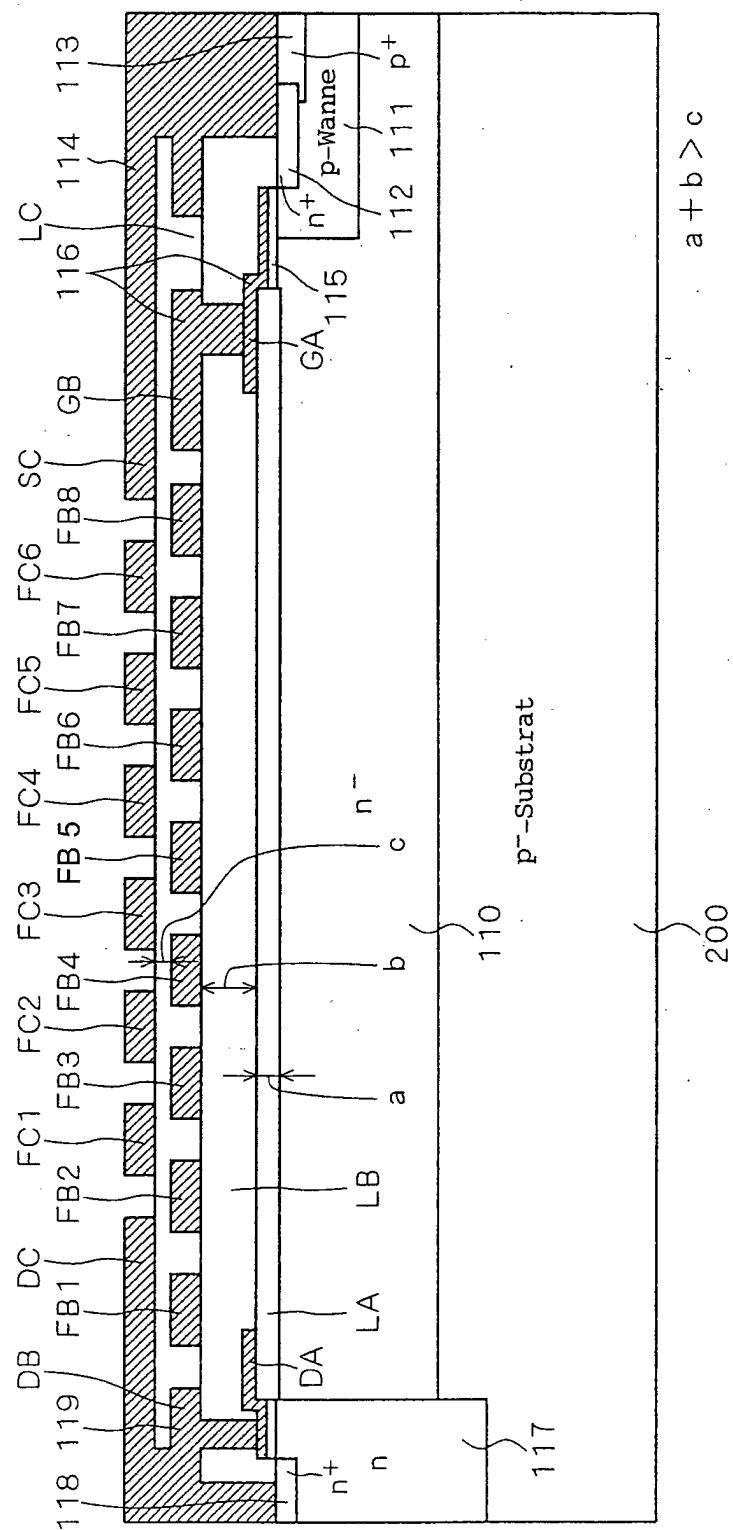

**[0017]** [Fig. 6](#) ist eine Ansicht eines Aufbaus eines HV-MOS nach einer ersten Ausführungsform.

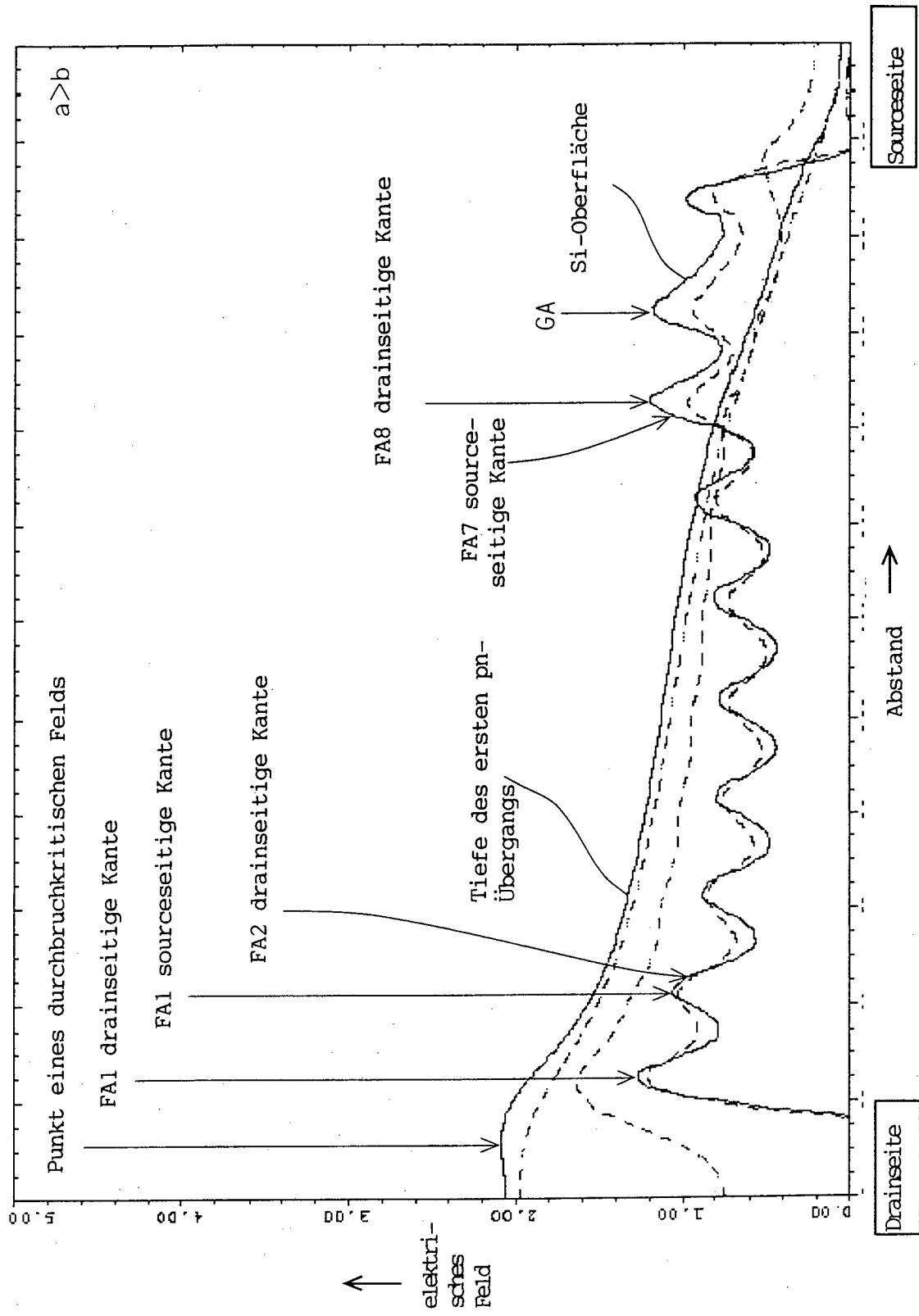

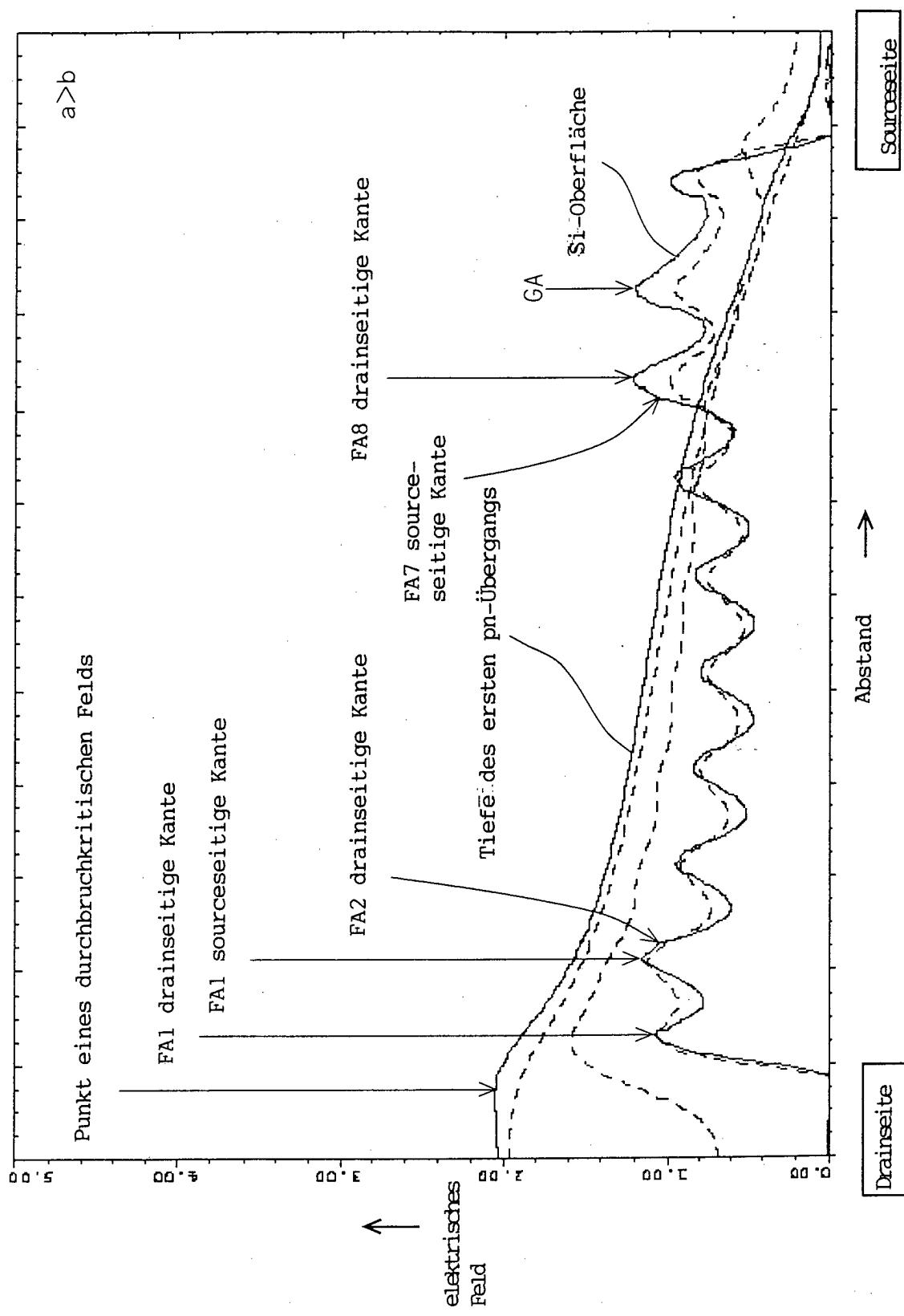

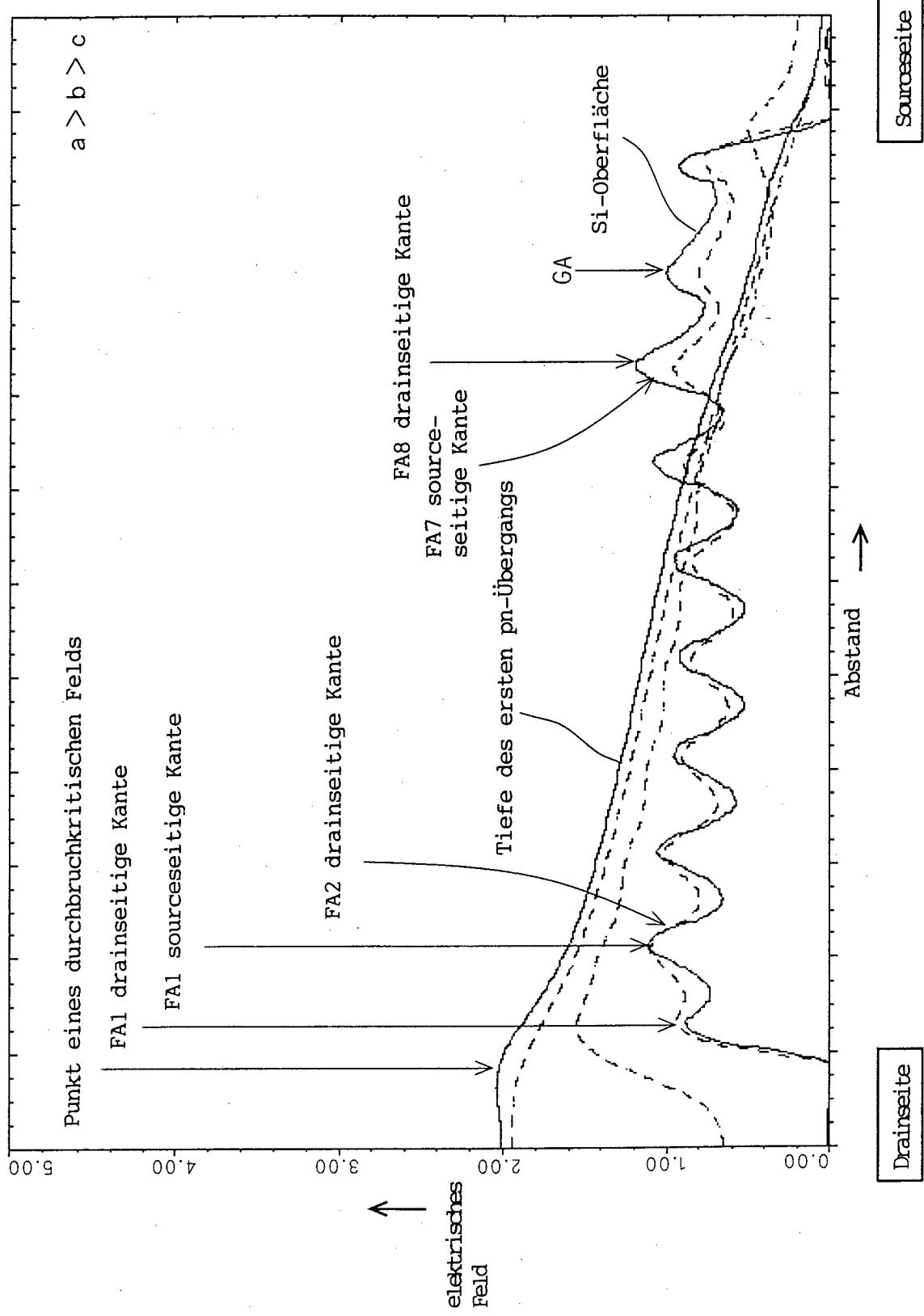

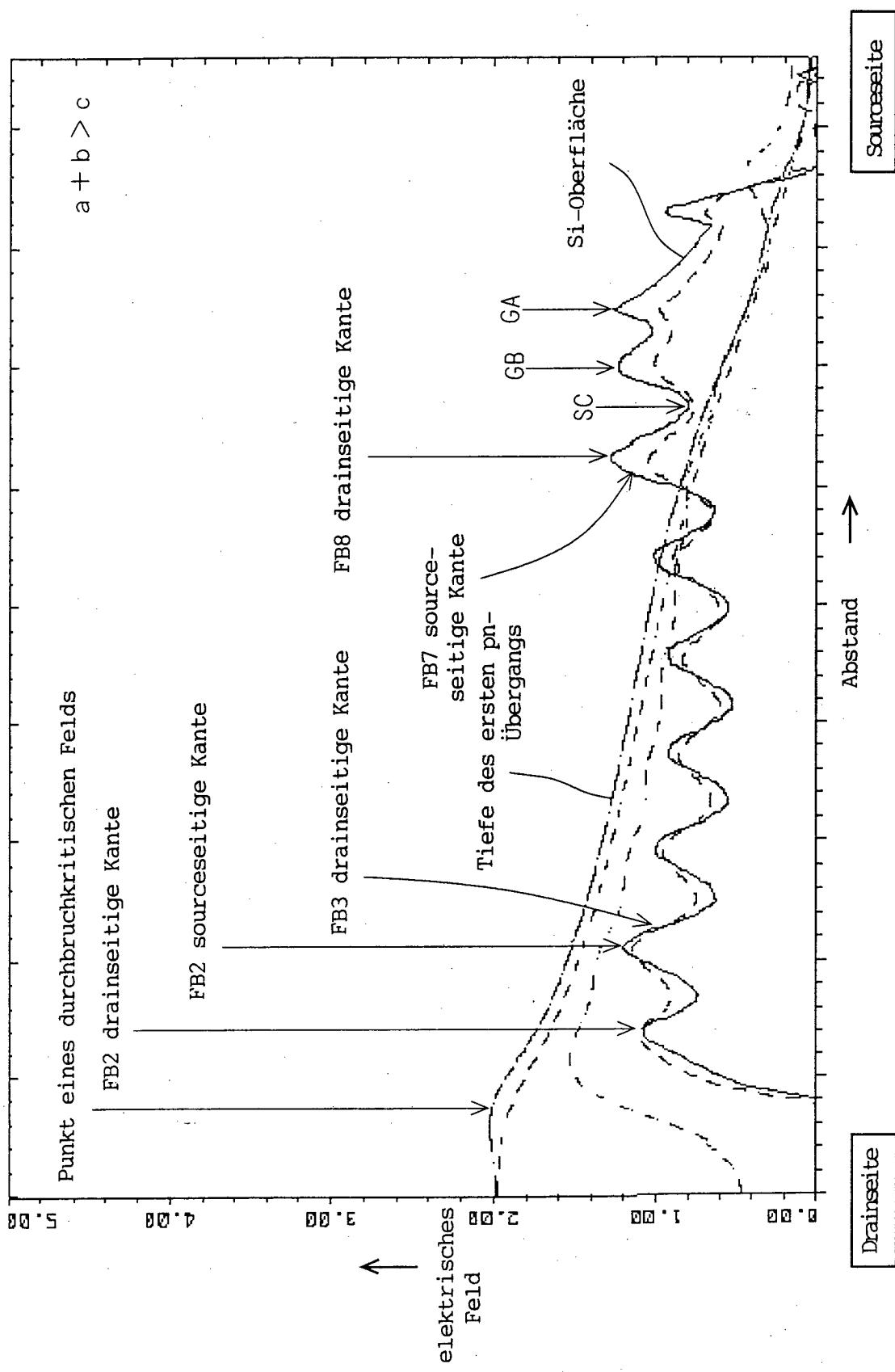

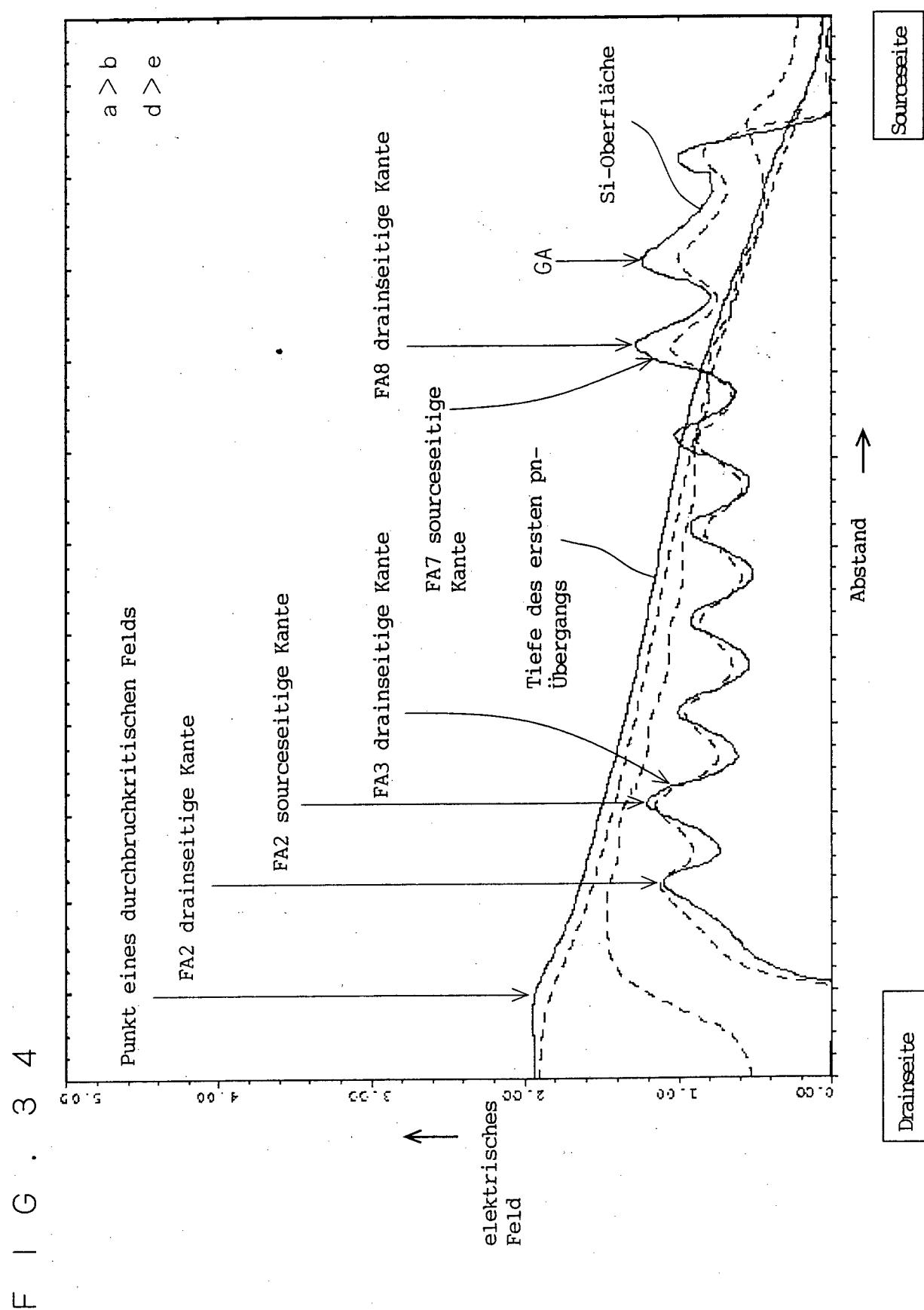

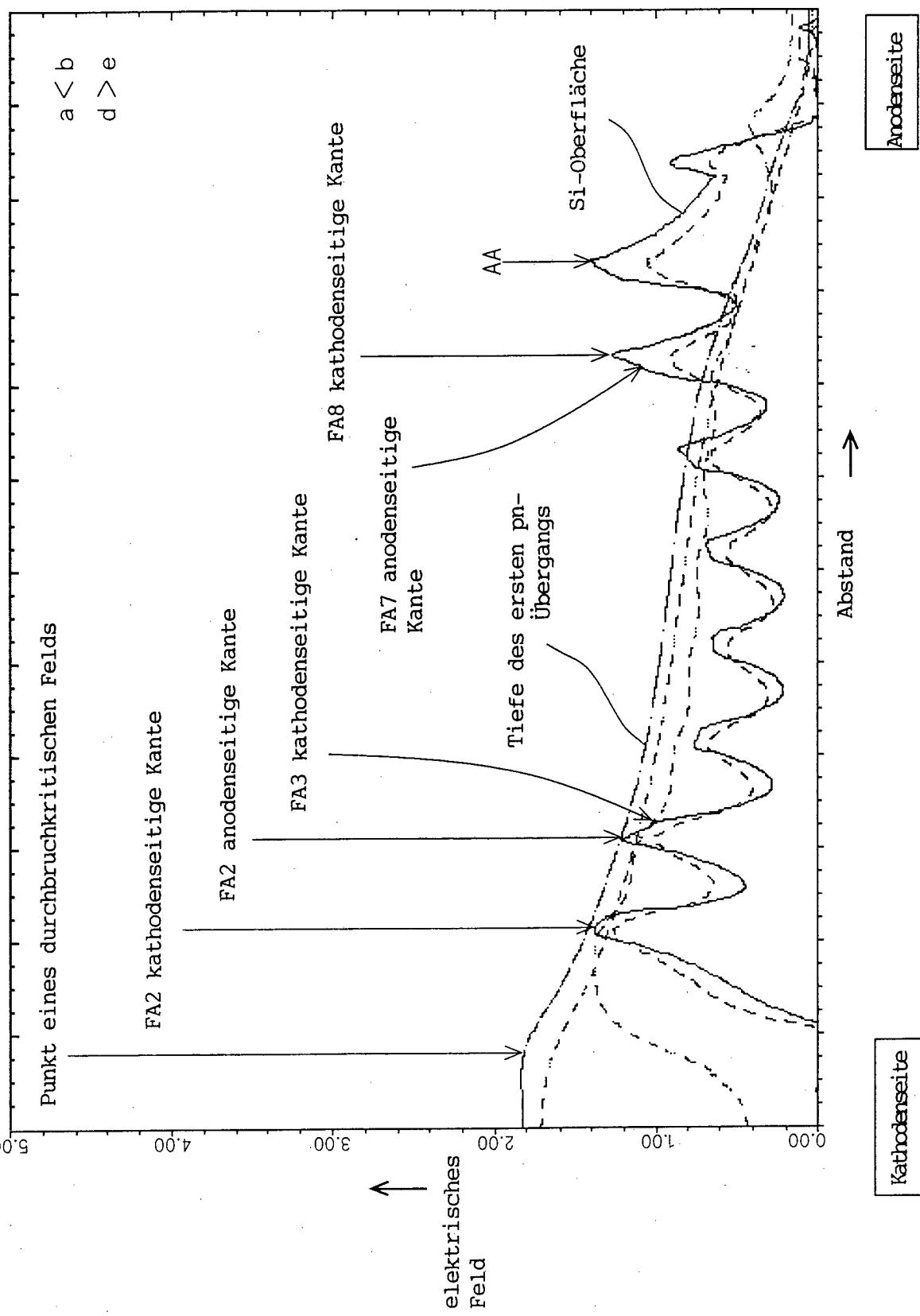

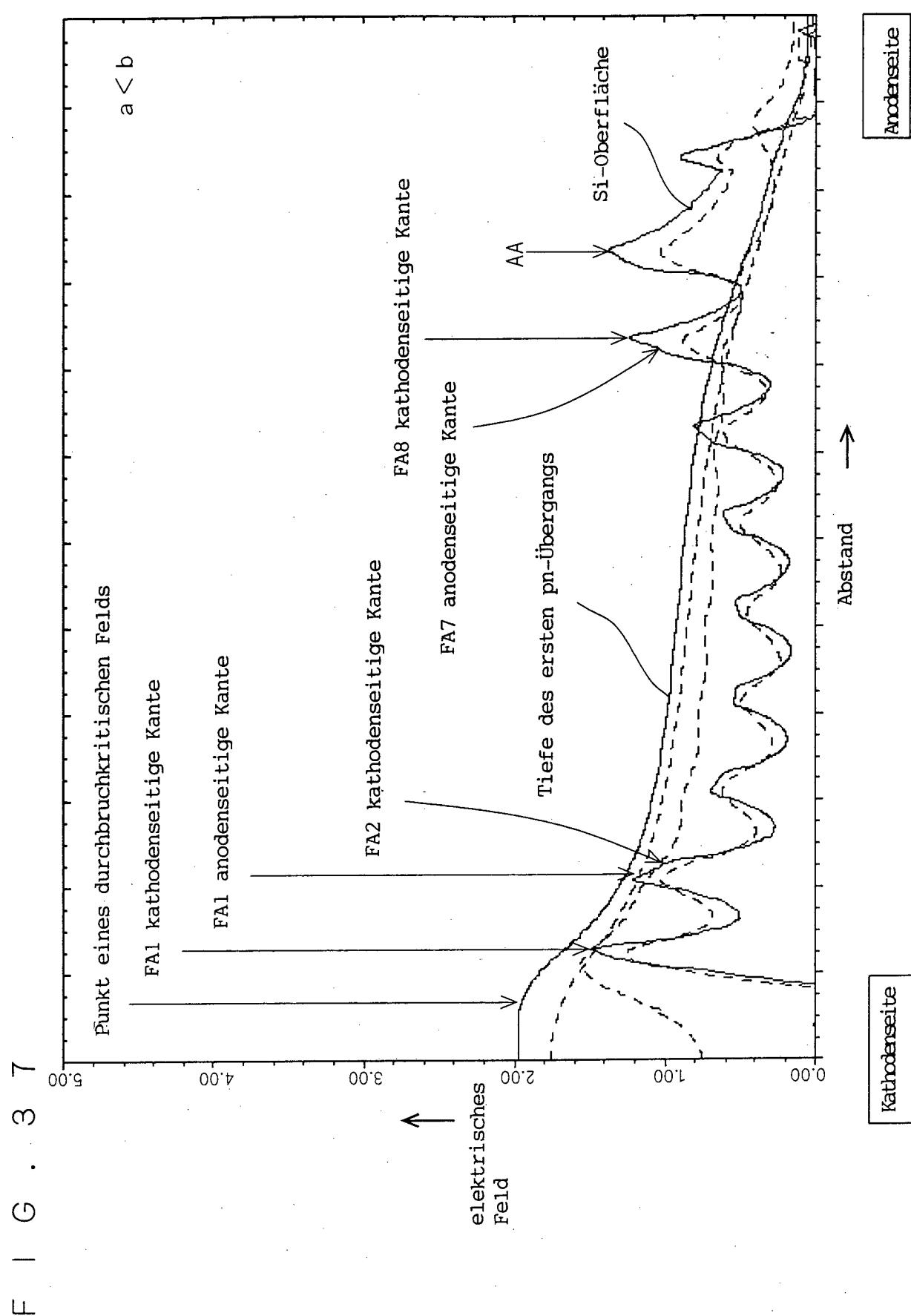

**[0018]** [Fig. 7](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source des HV-MOS nach der ersten Ausführungsform in einem AUS-Zustand zeigt.

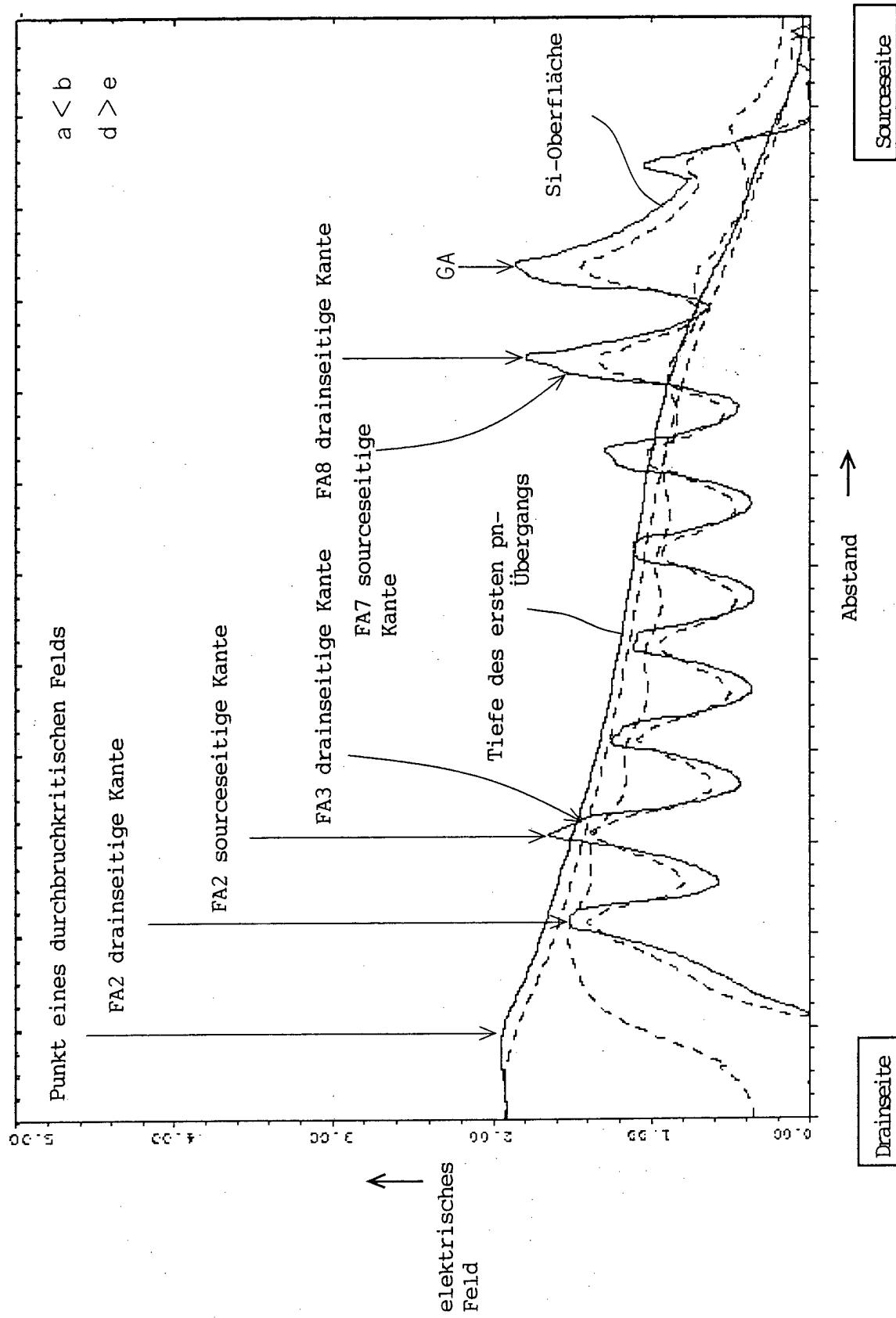

**[0019]** [Fig. 8](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source eines bekannten HV-MOS in einem AUS-Zustand zeigt.

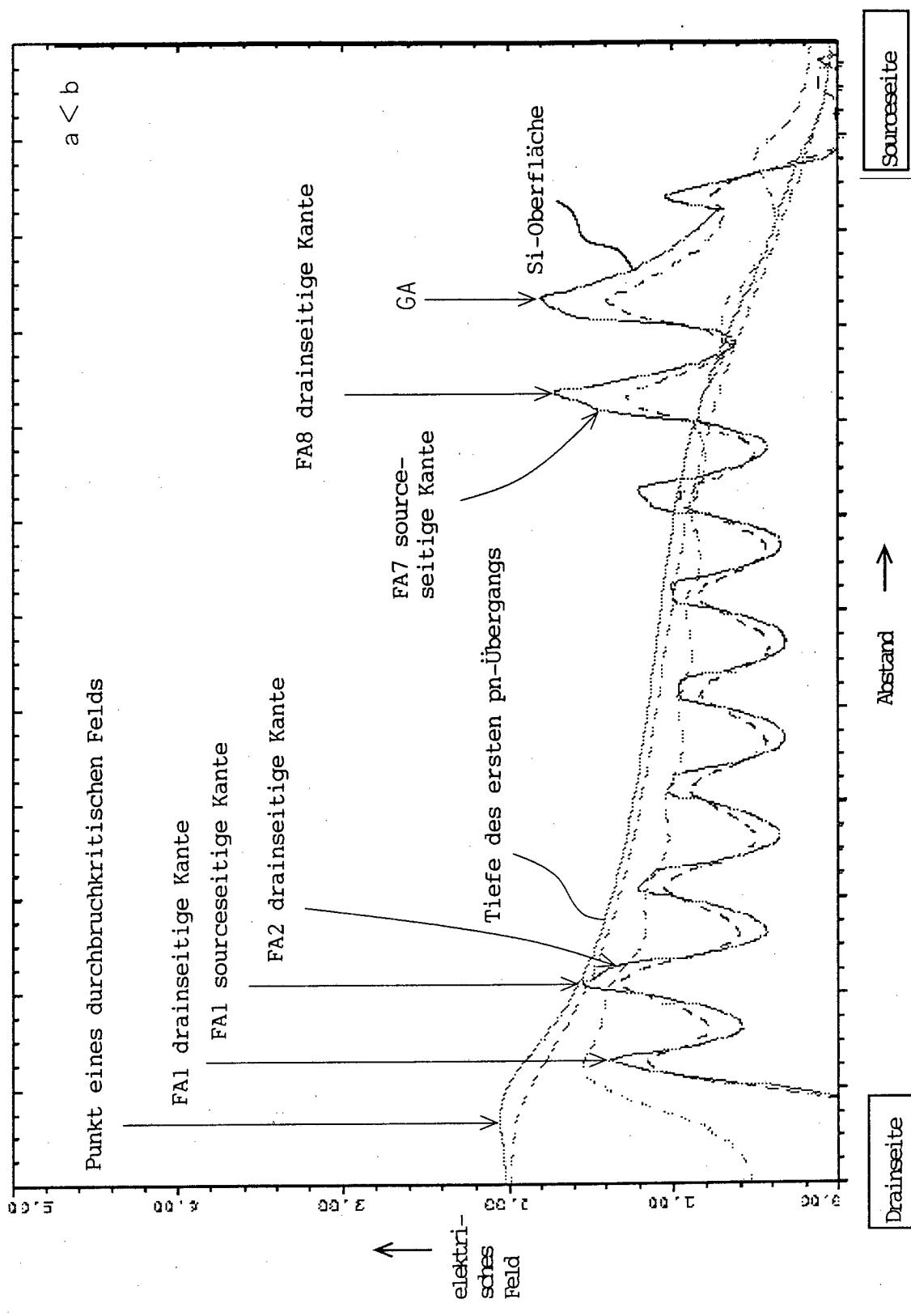

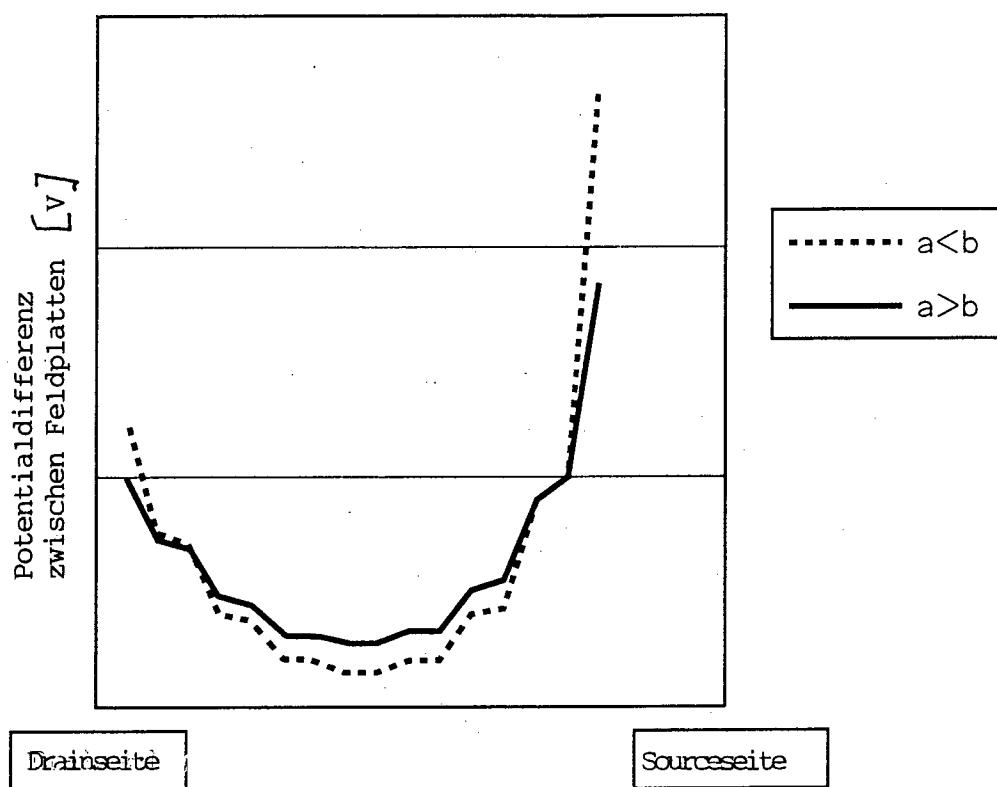

**[0020]** [Fig. 9](#) ist ein Diagramm zum Erläutern einer Wirkung der ersten Ausführungsform.

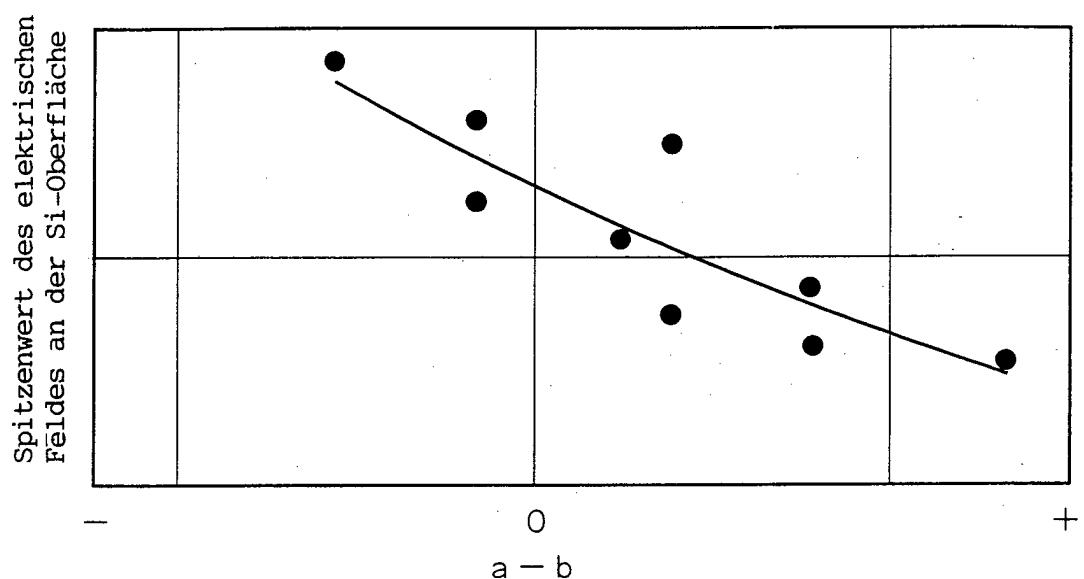

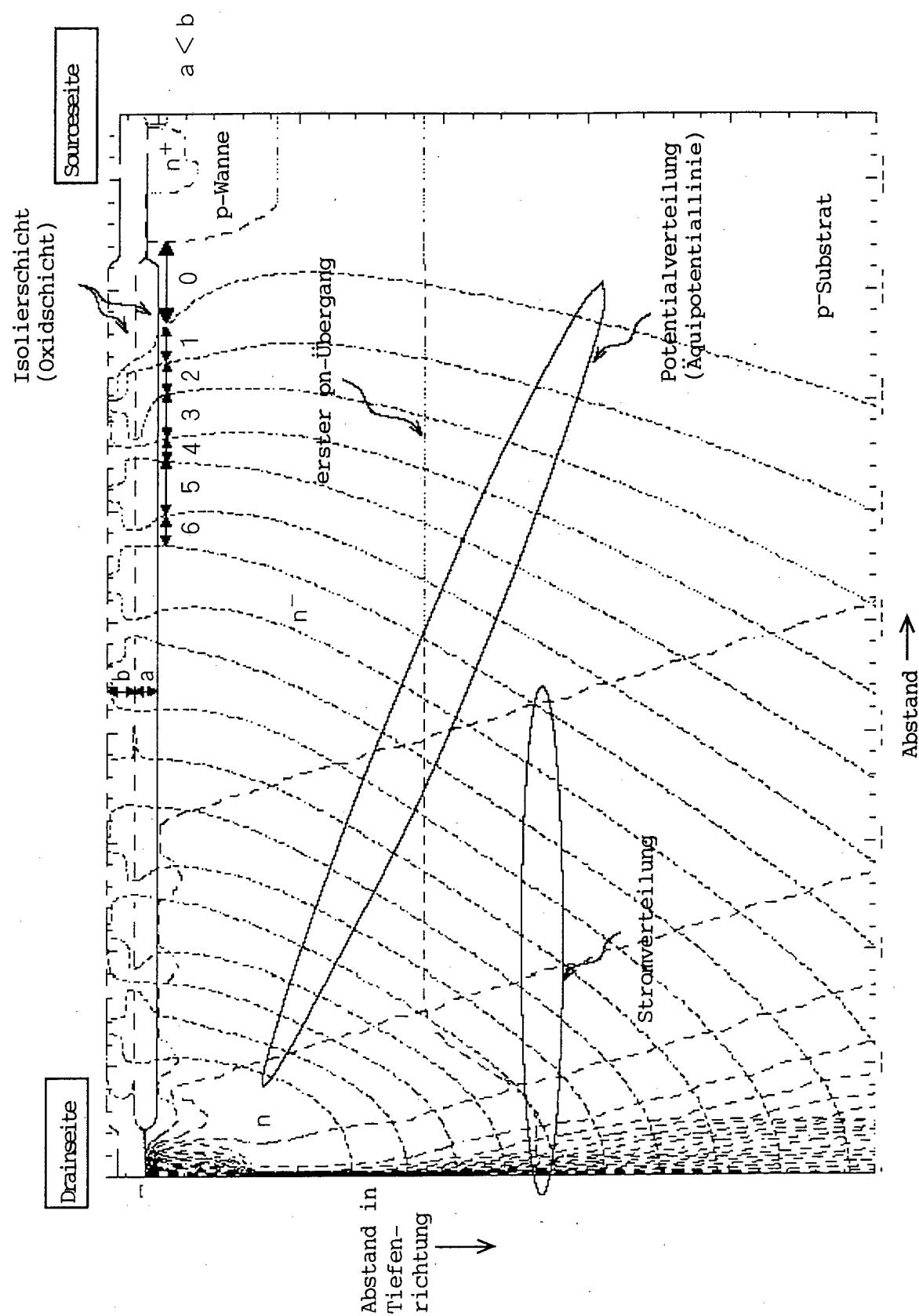

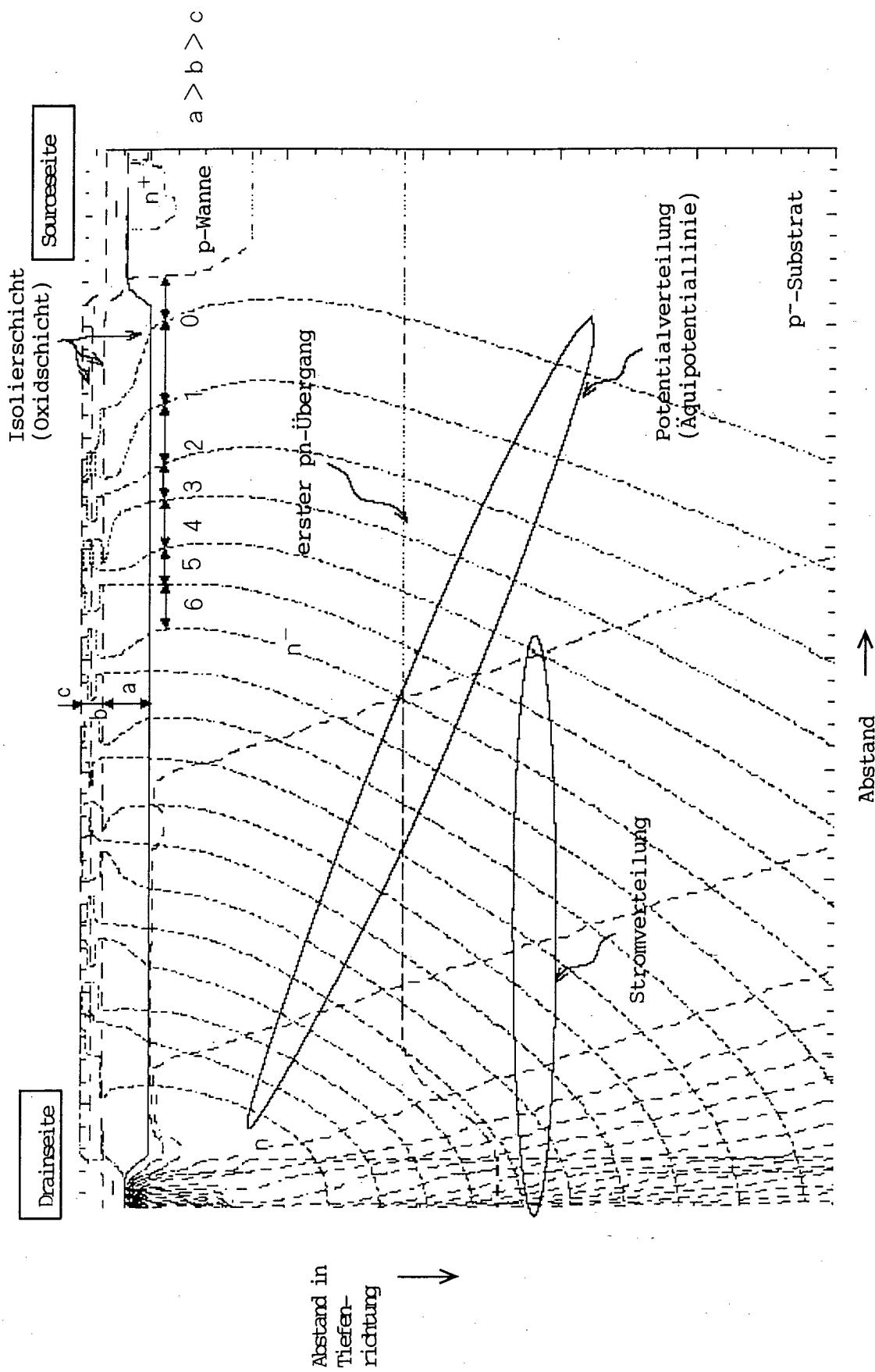

**[0021]** [Fig. 10](#) ist ein Diagramm, das eine Potenzialverteilung und eine Stromverteilung zwischen dem Drain und der Source des HV-MOS nach der ersten Ausführungsform in einem AUS-Zustand zeigt.

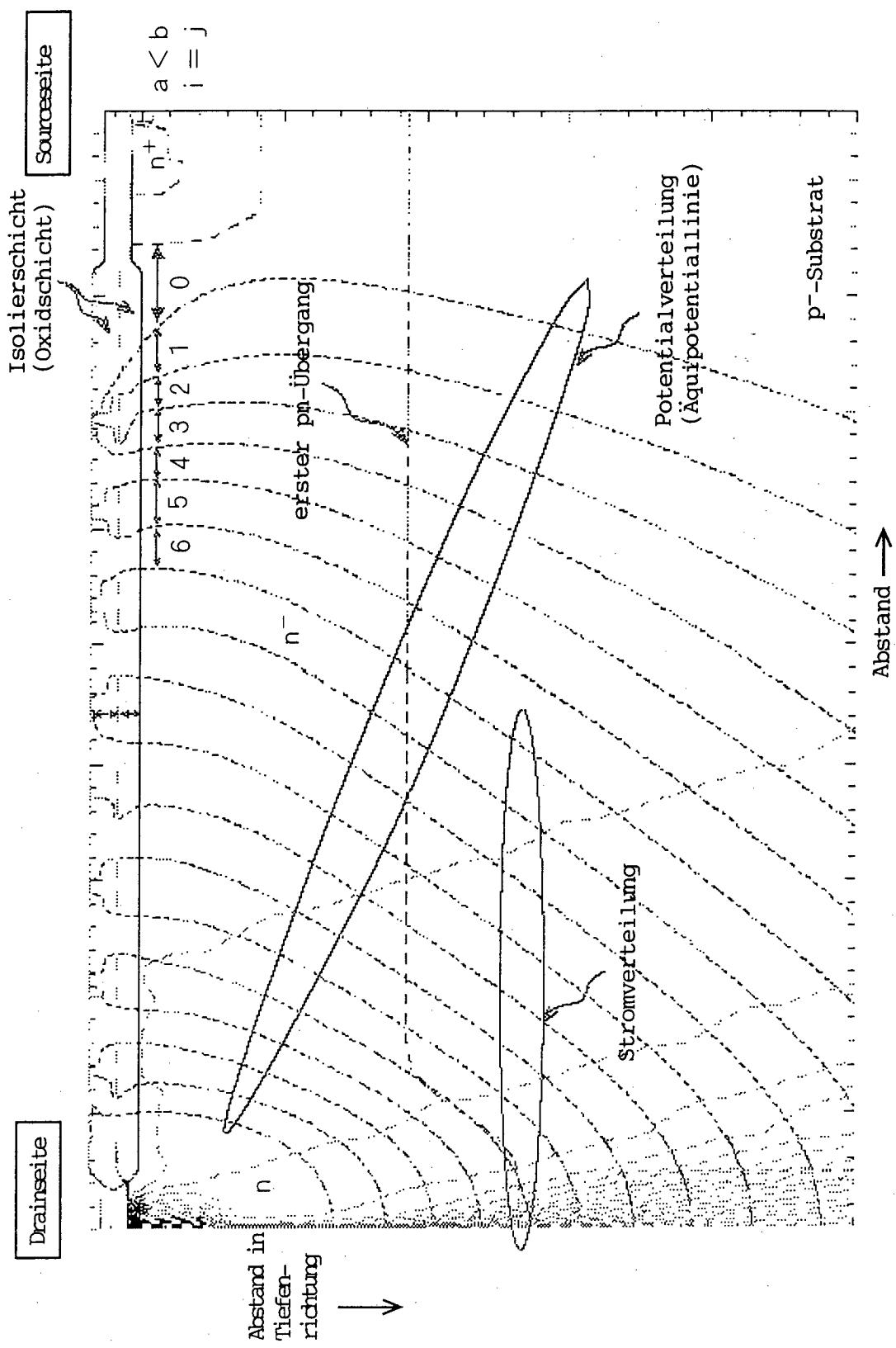

**[0022]** [Fig. 11](#) ist ein Diagramm, das eine Potenzialverteilung und eine Stromverteilung zwischen dem Drain und der Source des bekannten HV-MOS in einem AUS-Zustand zeigt.

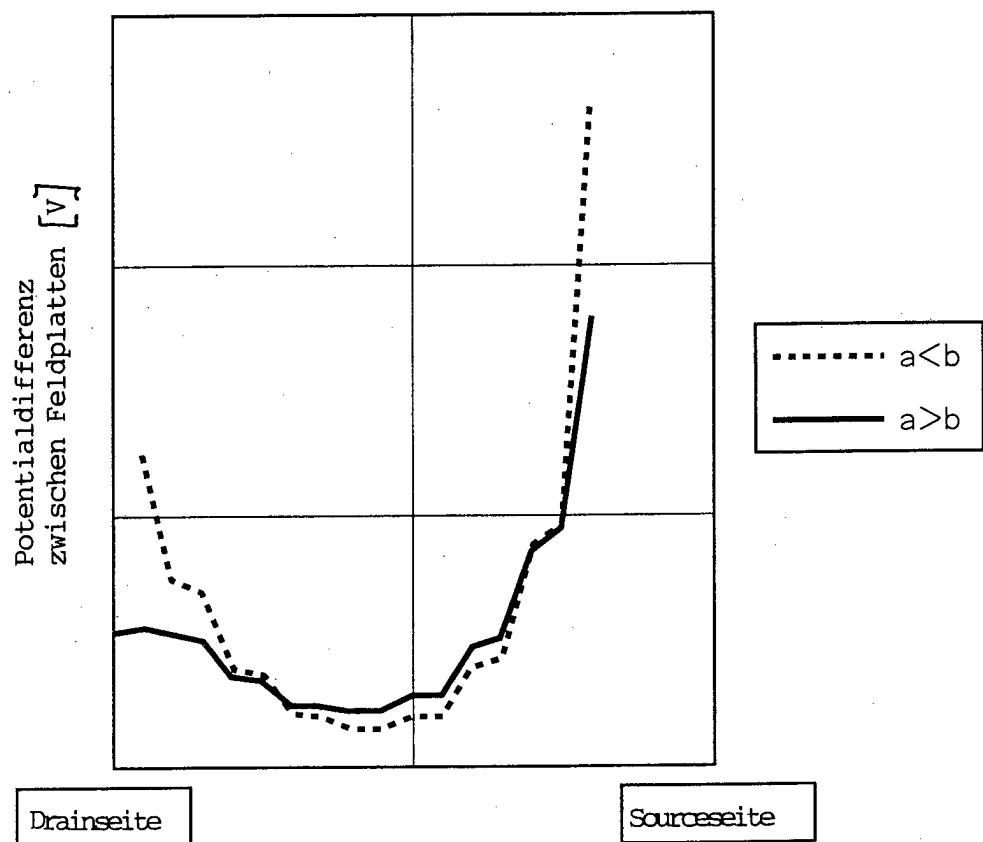

**[0023]** [Fig. 12](#) ist ein Diagramm zum Erläutern einer Wirkung der ersten Ausführungsform.

**[0024]** [Fig. 13](#) ist eine Ansicht eines Falles, bei dem die erste Ausführungsform auf eine Diode hoher Durchbruchspannung (HV-Diode) angewendet ist.

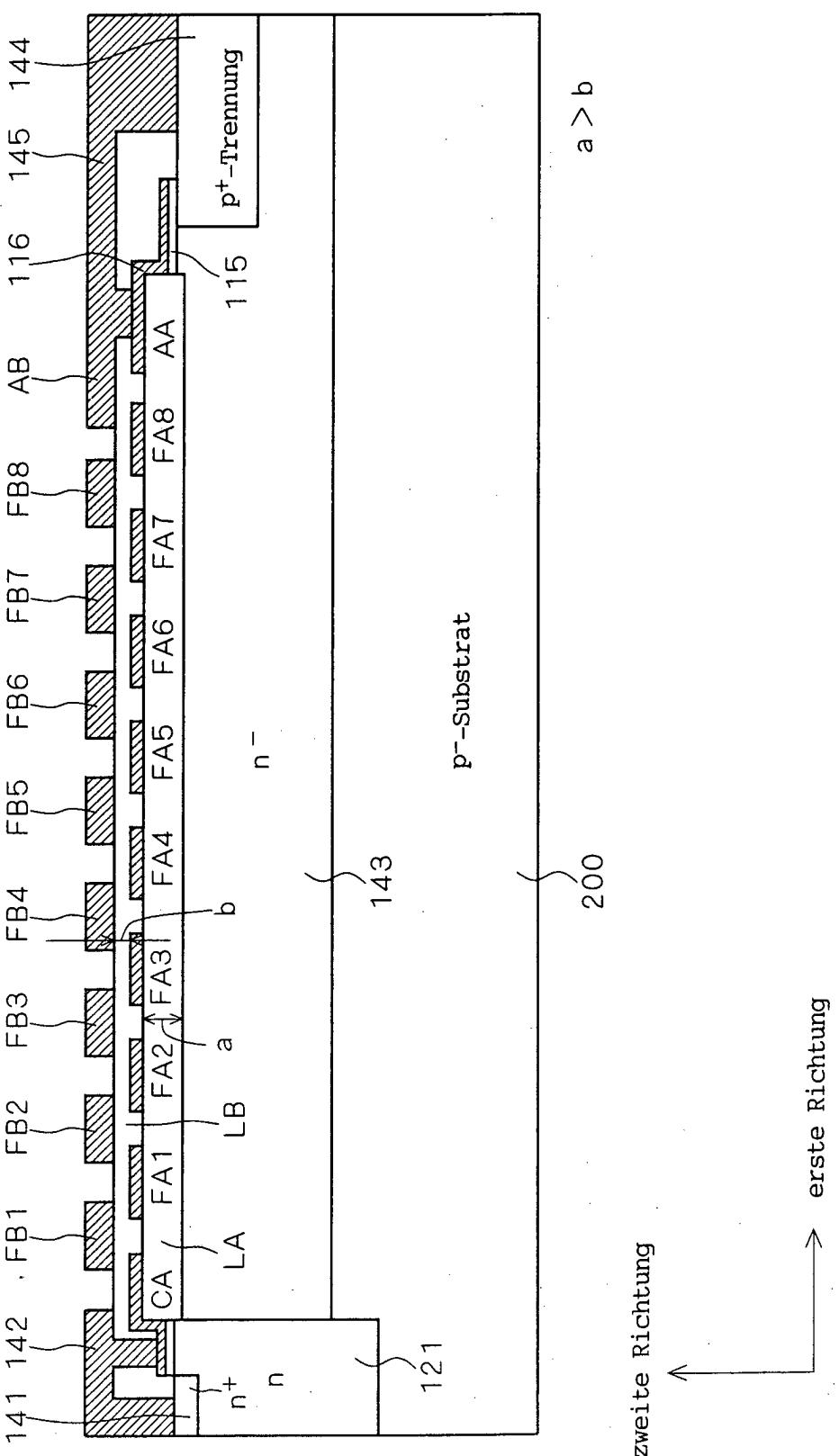

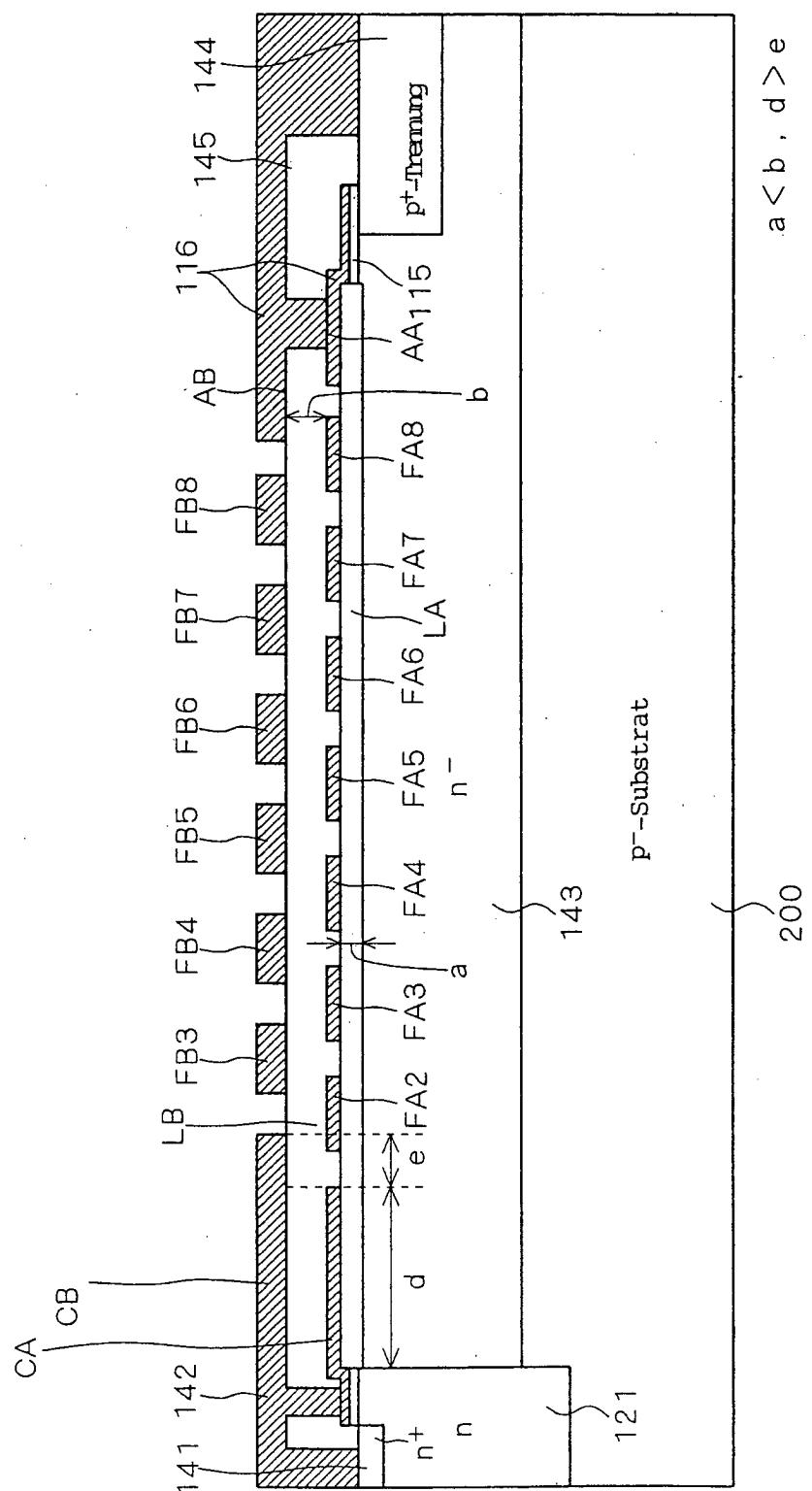

[0025] [Fig. 14](#) ist eine Ansicht eines Aufbaus eines HV-MOS nach einer zweiten Ausführungsform.

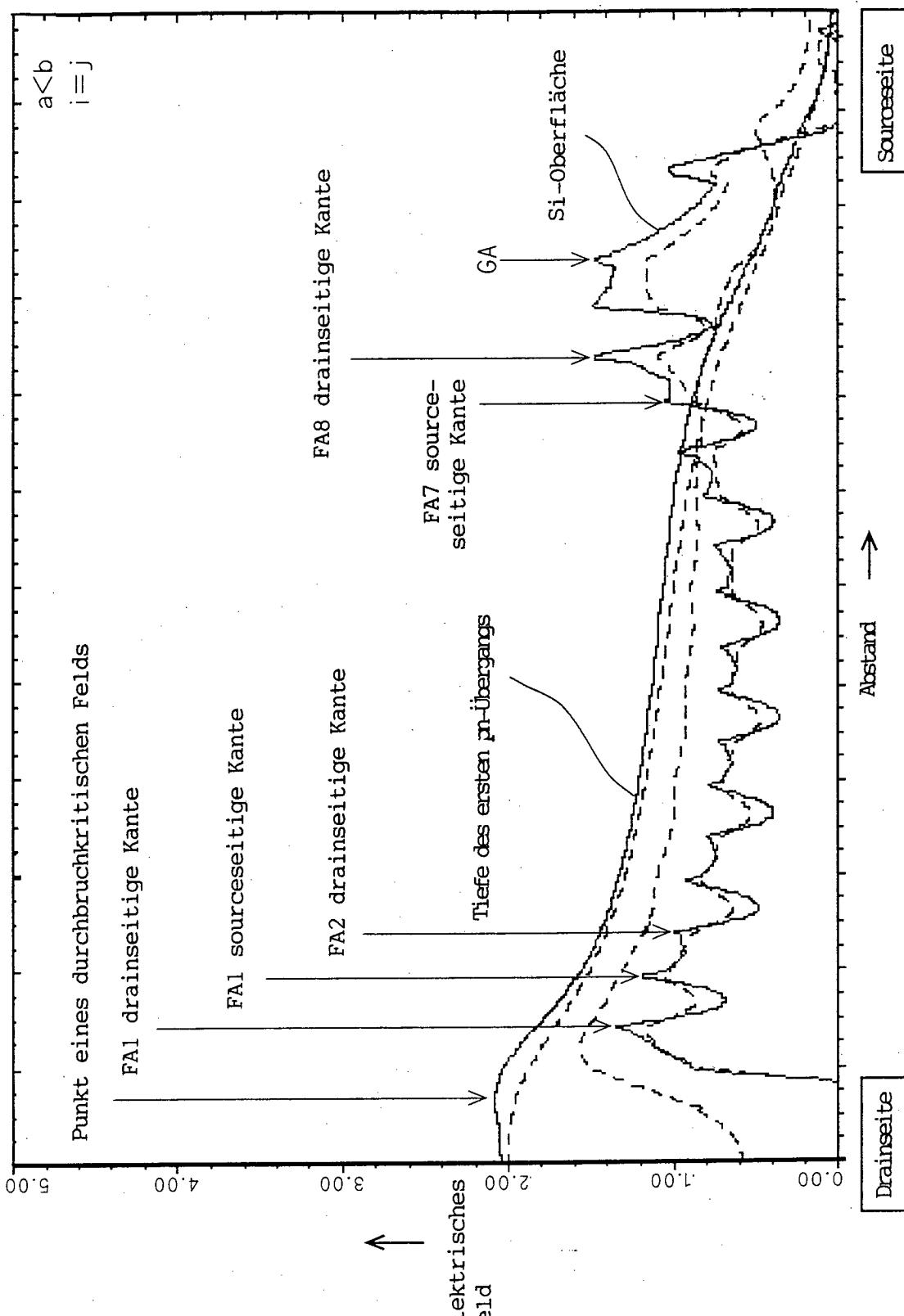

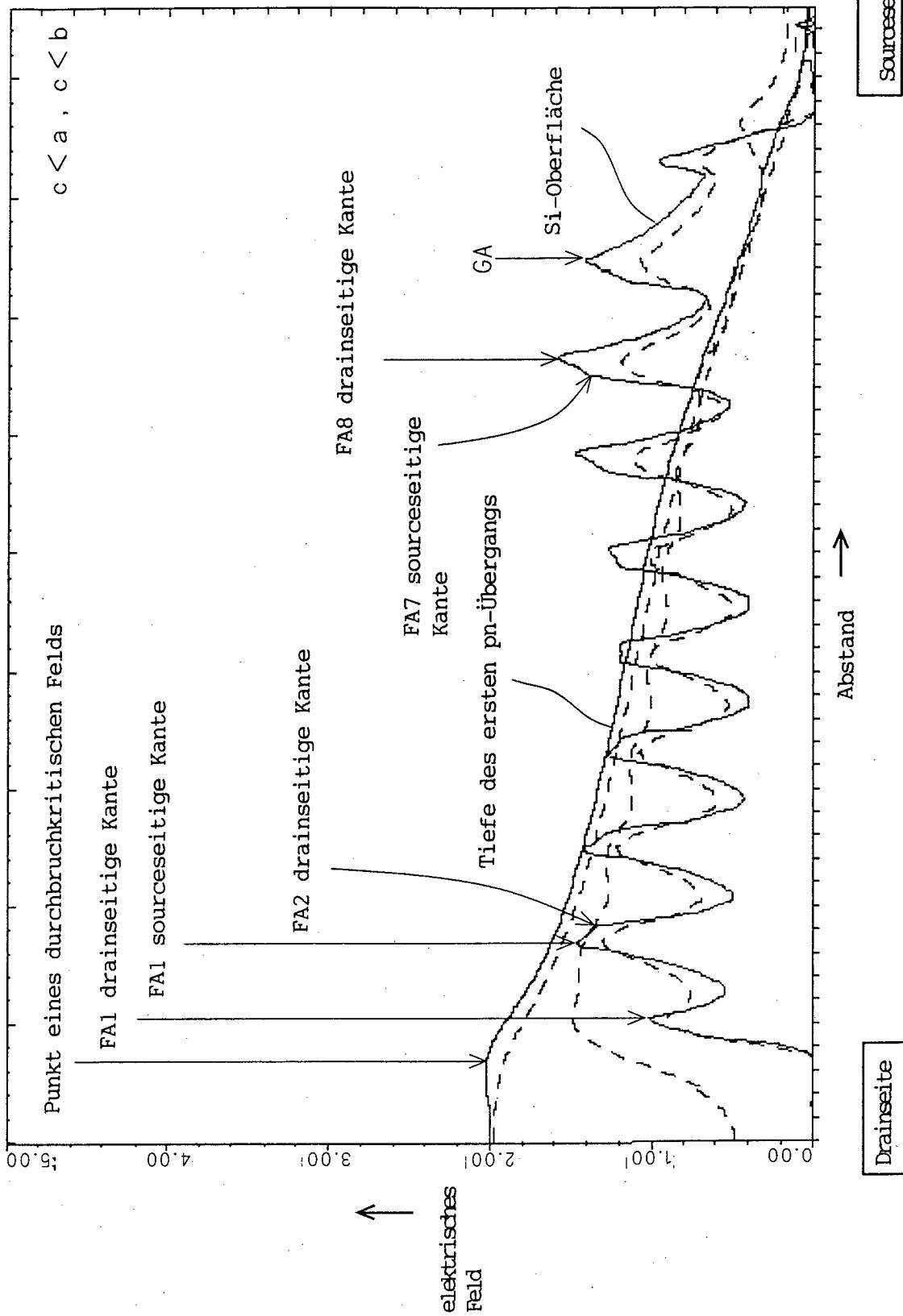

[0026] [Fig. 15](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source des HV-MOS nach der zweiten Ausführungsform in einem AUS-Zustand zeigt.

[0027] [Fig. 16](#) ist ein Diagramm zum Erläutern einer Wirkung der zweiten Ausführungsform.

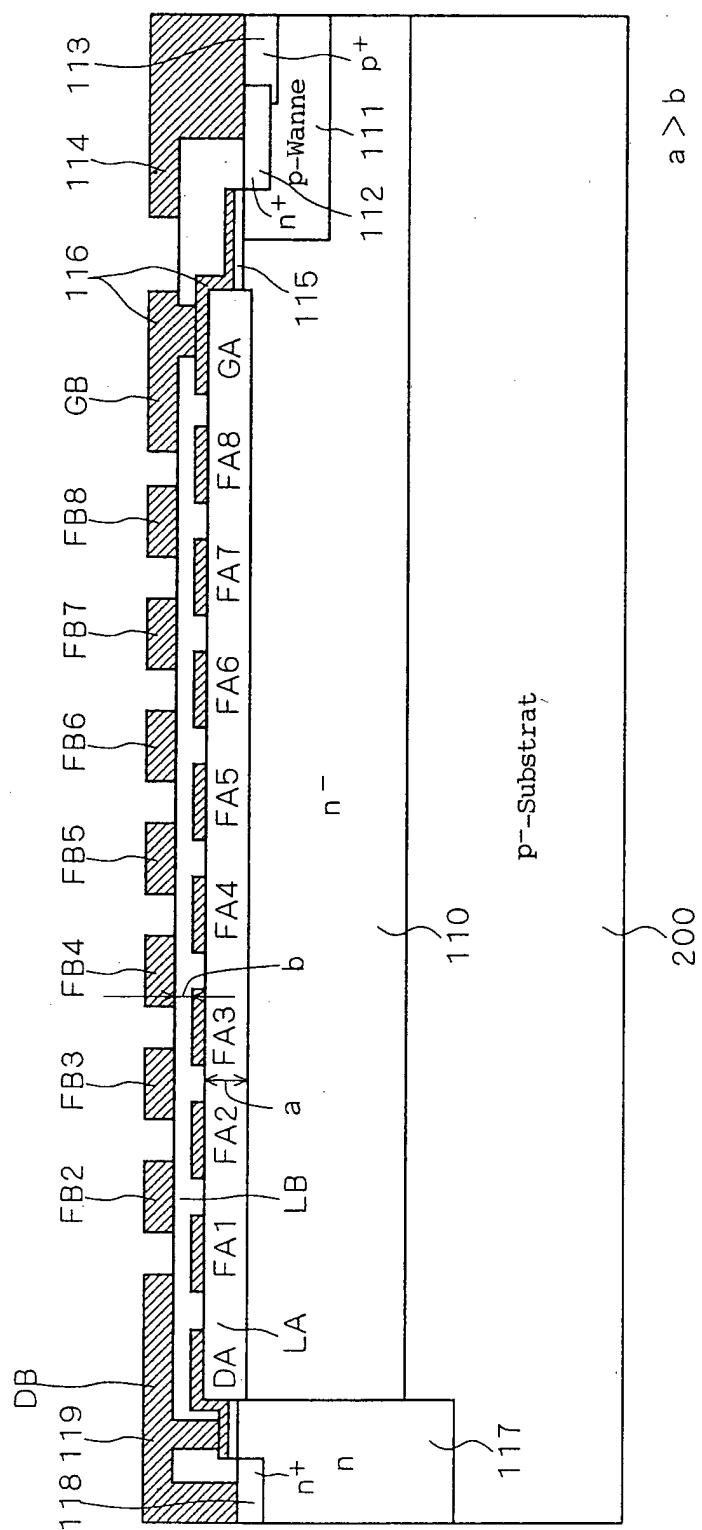

[0028] [Fig. 17](#) ist eine Ansicht eines Aufbaus eines HV-MOS nach einer dritten Ausführungsform.

[0029] [Fig. 18](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source des HV-MOS nach der dritten Ausführungsform in einem AUS-Zustand zeigt.

[0030] [Fig. 19](#) ist ein Diagramm, das eine Potenialverteilung und eine Stromverteilung zwischen dem Drain und der Source des HV-MOS nach der dritten Ausführungsform in einem AUS-Zustand zeigt.

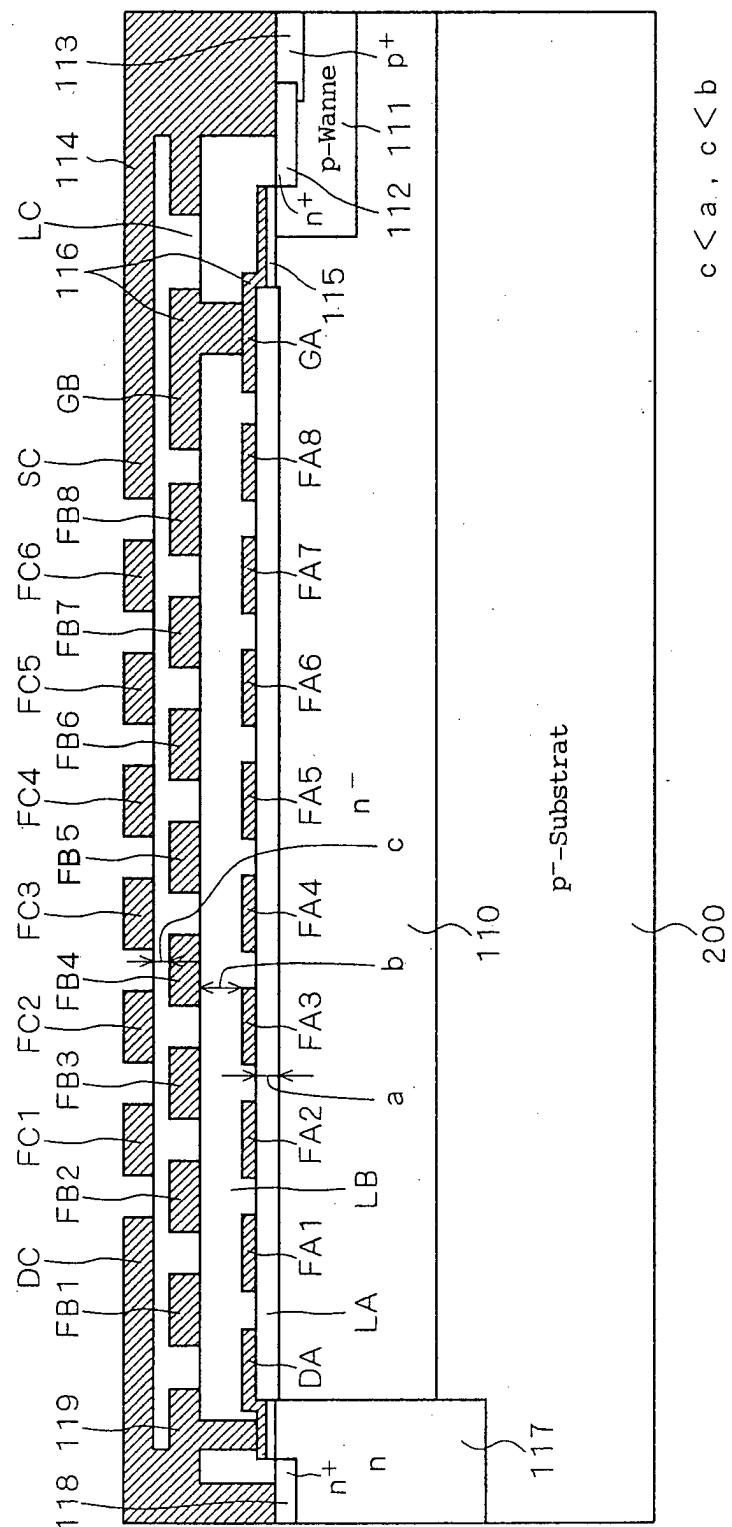

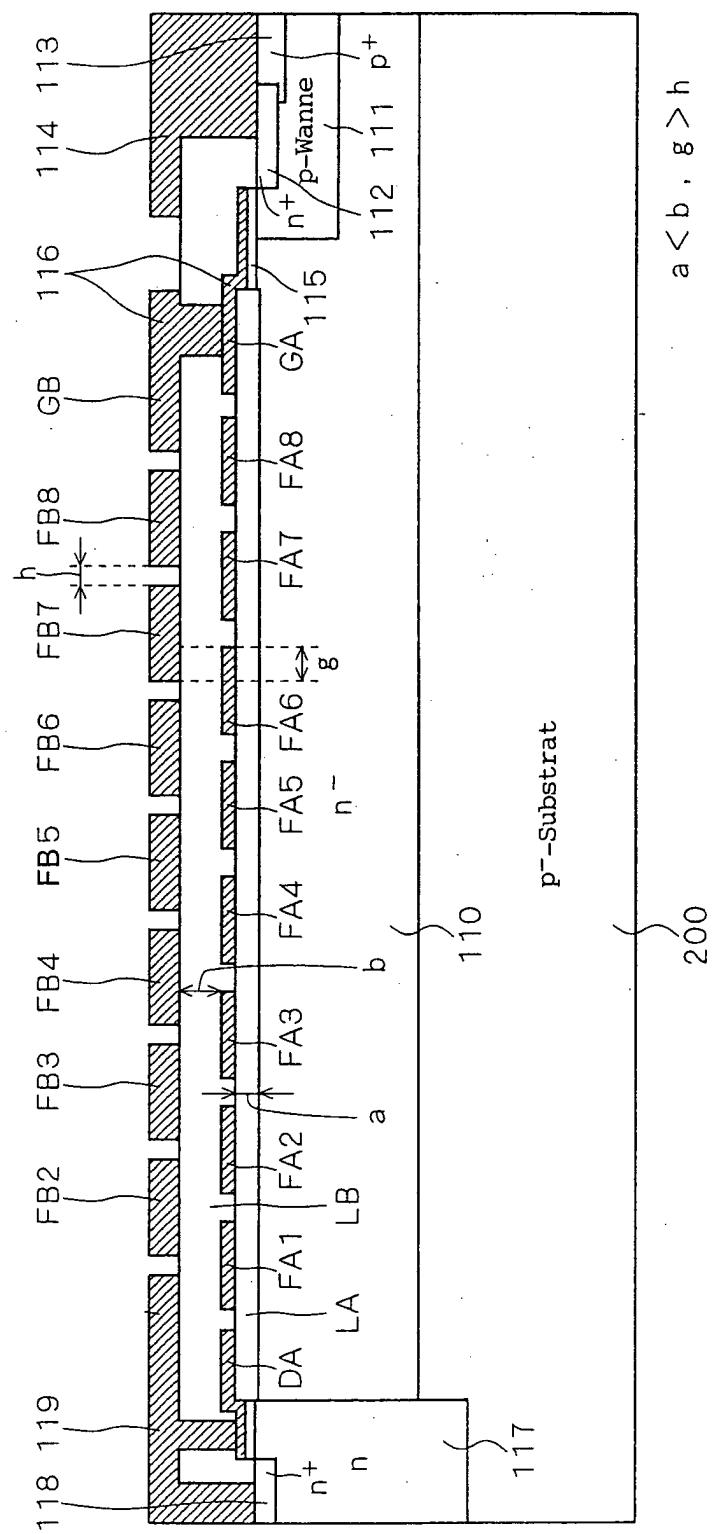

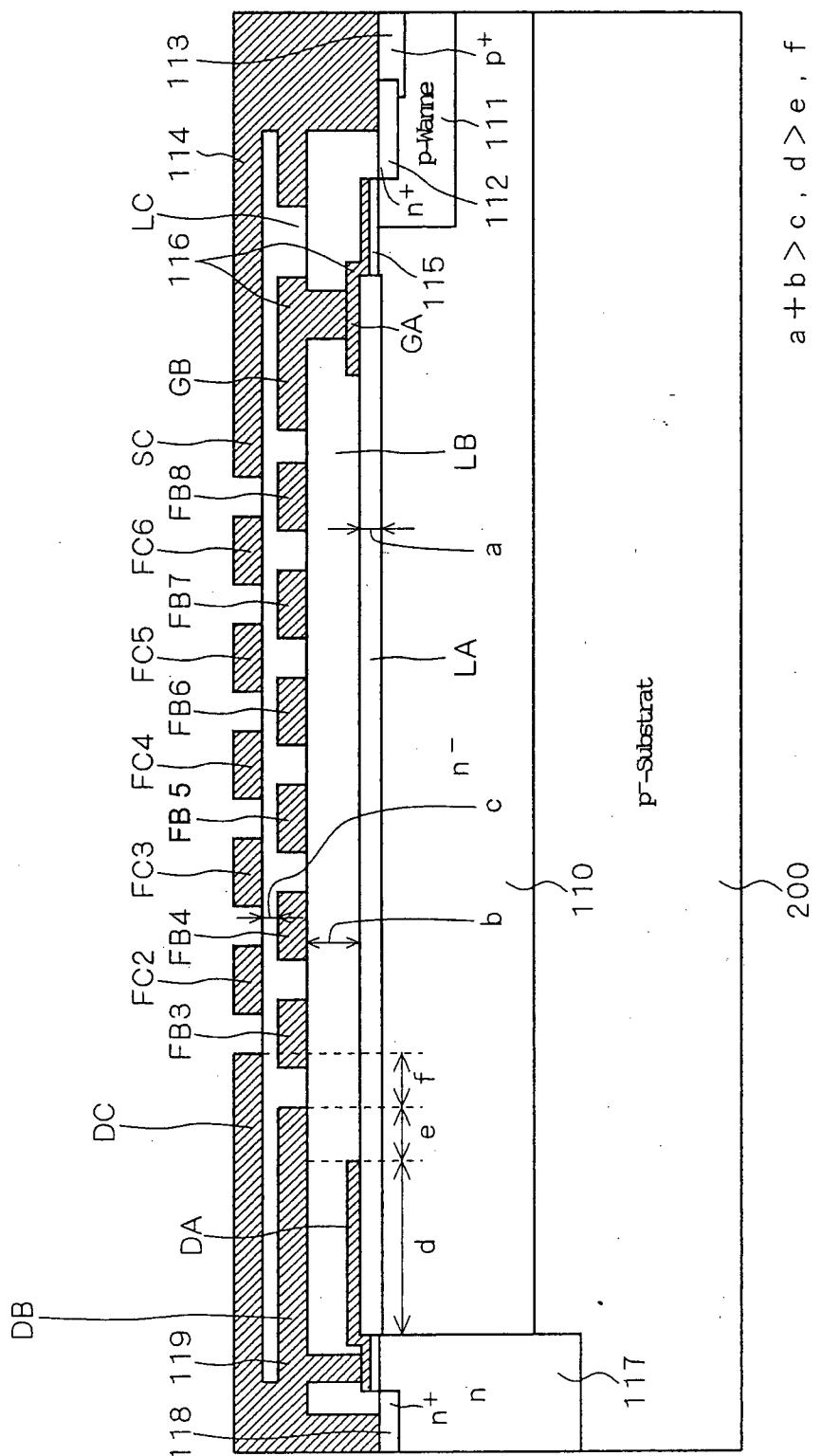

[0031] [Fig. 20](#) ist eine Ansicht eines Aufbaus eines HV-MOS nach einer zur Erfindung gehörenden vierten Ausführungsform.

[0032] [Fig. 21](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source des HV-MOS nach der zur Erfindung gehörenden vierten Ausführungsform in einem AUS-Zustand zeigt.

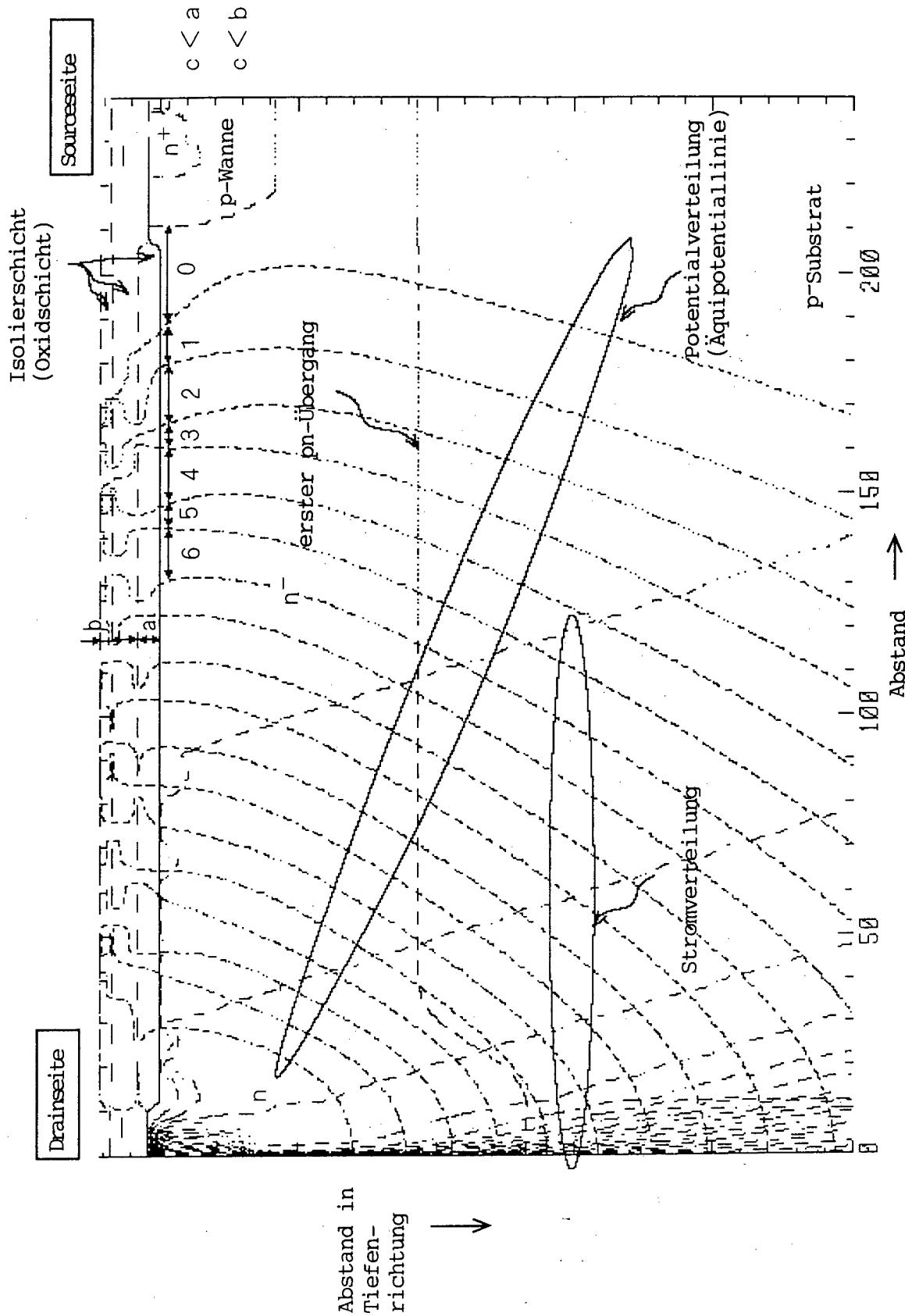

[0033] [Fig. 22](#) ist ein Diagramm, das eine Potenialverteilung und eine Stromverteilung zwischen dem Drain und der Source des HV-MOS nach der zur Erfindung gehörenden vierten Ausführungsform in einem AUS-Zustand zeigt.

[0034] [Fig. 23](#) ist eine Ansicht einer Abwandlung der zur Erfindung gehörenden vierten Ausführungsform.

[0035] [Fig. 24](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source des HV-MOS nach der Abwandlung der zur Erfindung gehörenden vierten Ausführungsform in einem AUS-Zustand zeigt.

[0036] [Fig. 25](#) ist ein Diagramm, das eine Potenialverteilung und eine Stromverteilung zwischen dem Drain und der Source des HV-MOS nach der Abwandlung der zur Erfindung gehörenden vierten Ausführungsform in einem AUS-Zustand zeigt.

[0037] [Fig. 26](#) ist eine Ansicht eines Aufbaus eines HV-MOS nach einer fünften Ausführungsform.

[0038] [Fig. 27](#) ist eine Ansicht eines Aufbaus eines HV-MOS nach einer sechsten Ausführungsform.

[0039] [Fig. 28](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source des HV-MOS nach der sechsten Ausführungsform in einem AUS-Zustand zeigt.

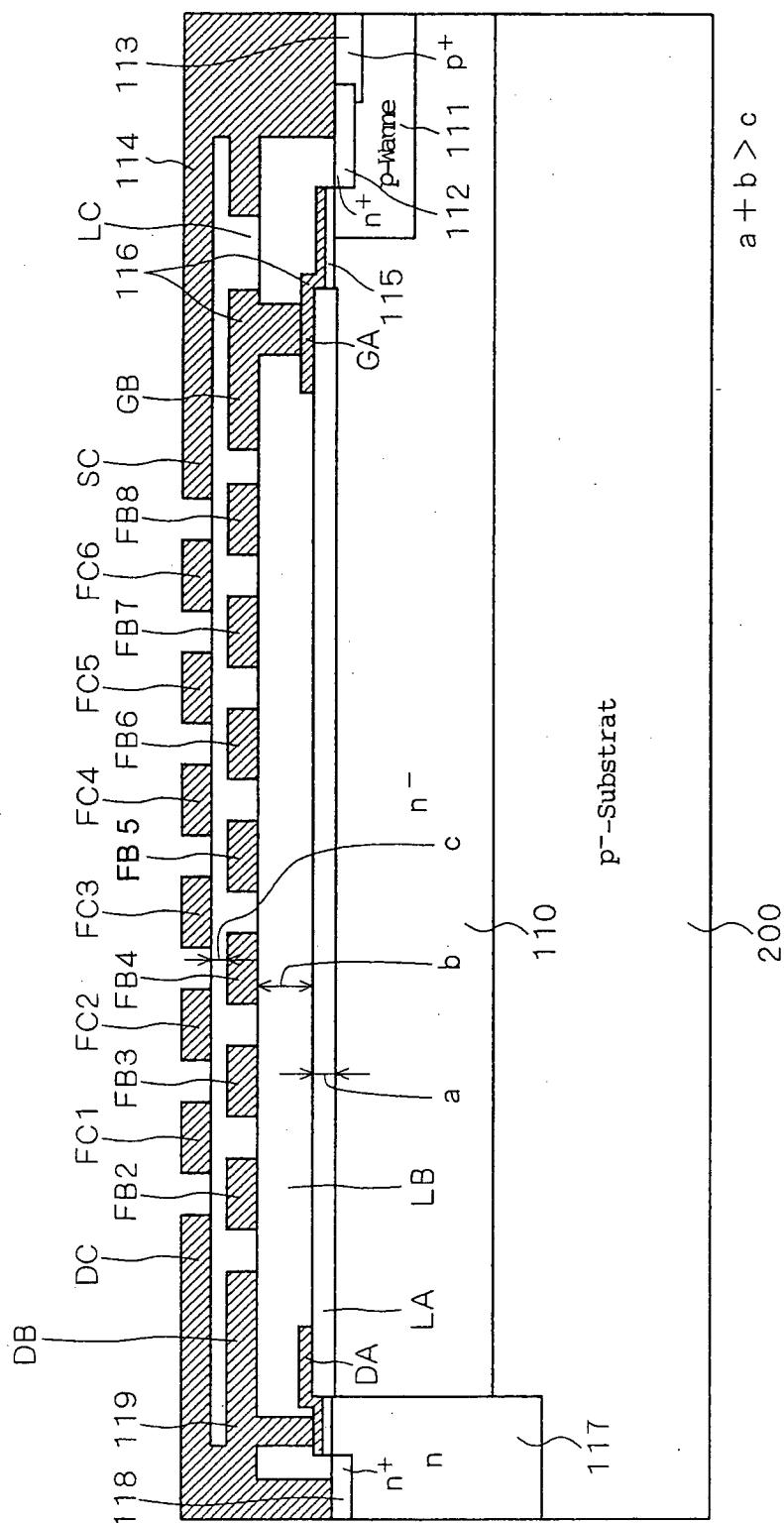

[0040] [Fig. 29](#) ist eine Ansicht einer Abwandlung der sechsten Ausführungsform.

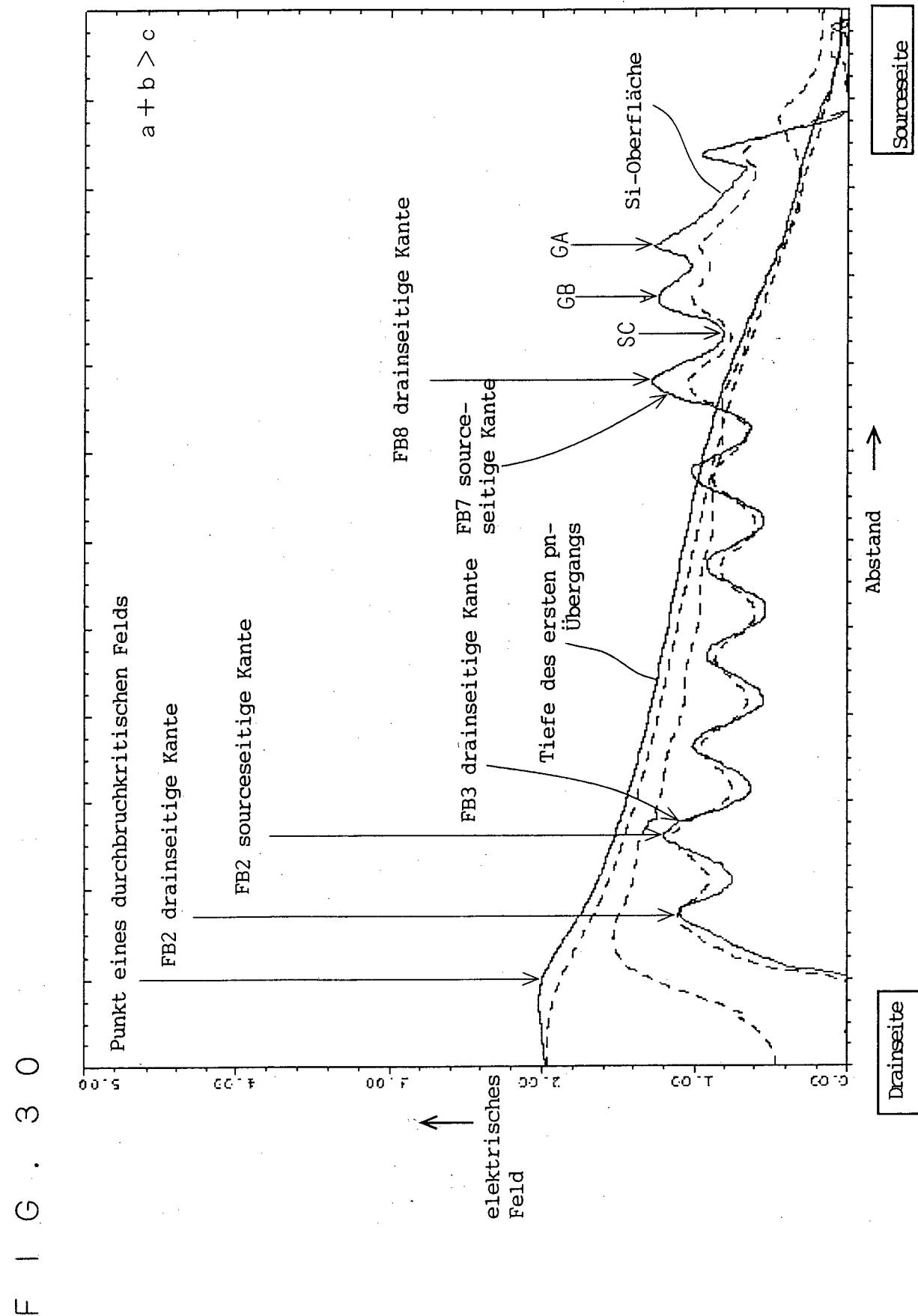

[0041] [Fig. 30](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source des HV-MOS nach der Abwandlung der sechsten Ausführungsform in einem AUS-Zustand zeigt.

[0042] [Fig. 31](#) ist eine Ansicht eines Aufbaus eines HV-MOS nach einer siebten Ausführungsform.

[0043] [Fig. 32](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source des HV-MOS nach der siebten Ausführungsform in einem AUS-Zustand zeigt.

[0044] [Fig. 33](#) ist eine Ansicht einer Abwandlung der siebten Ausführungsform.

[0045] [Fig. 34](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source des HV-MOS nach der Abwandlung der siebten Ausführungsform in einem AUS-Zustand zeigt.

[0046] [Fig. 35](#) ist eine Ansicht eines Falles, bei dem die siebte Ausführungsform auf eine HV-Diode angewendet ist.

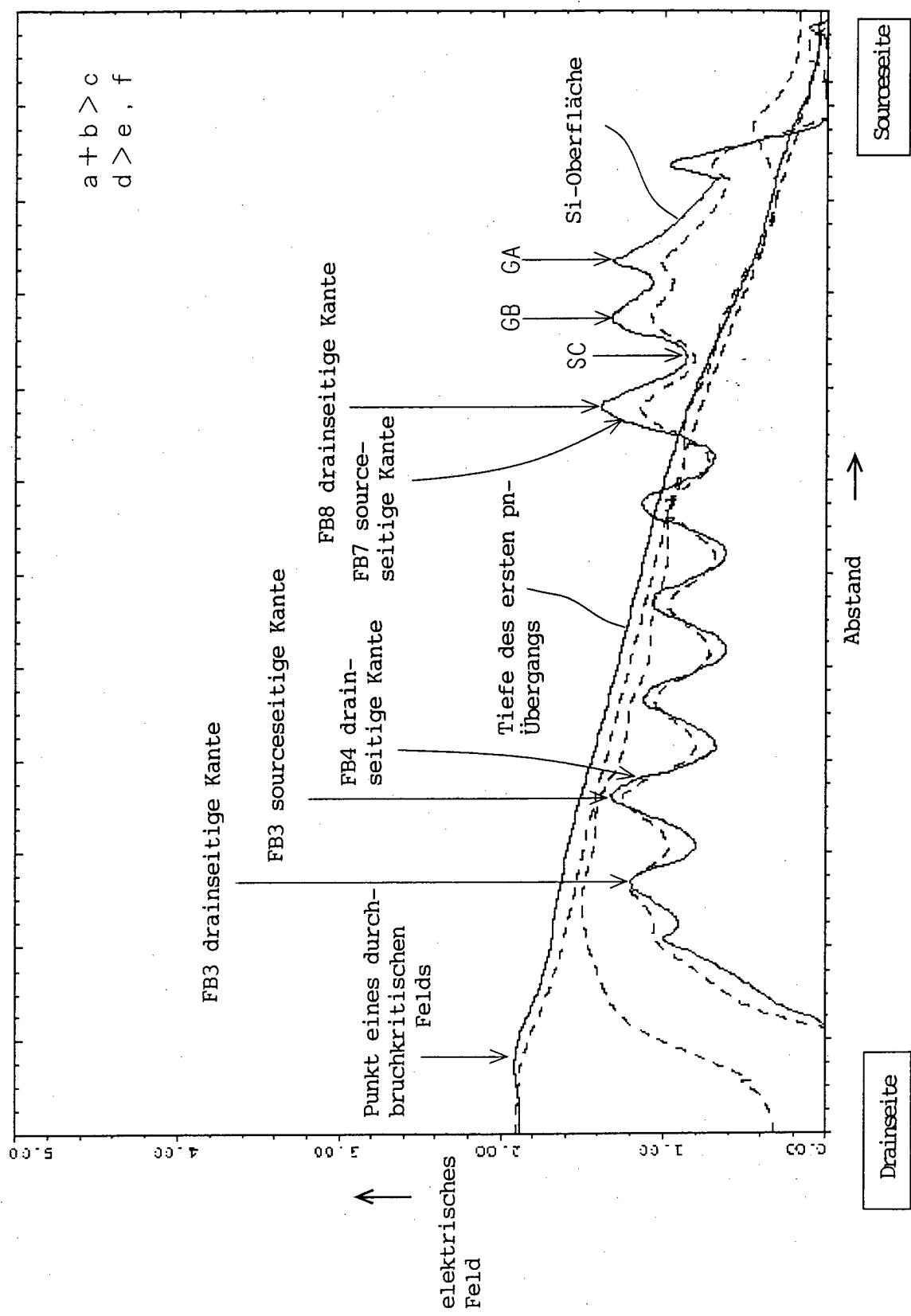

[0047] [Fig. 36](#) und [Fig. 37](#) sind Diagramme, die jeweils eine elektrische Feldverteilung zwischen einem Drain und einer Source der HV-Diode nach der siebten Ausführungsform in einem AUS-Zustand zeigt.

[0048] [Fig. 38](#) ist eine Ansicht eines Aufbaus eines HV-MOS nach einer achten Ausführungsform.

[0049] [Fig. 39](#) ist ein Diagramm, das eine elektrische Feldverteilung zwischen einem Drain und einer Source des HV-MOS nach der achten Ausführungsform in einem AUS-Zustand zeigt.

[0050] [Fig. 40](#) ist eine Ansicht einer Abwandlung der ersten Ausführungsform

[0051] [Fig. 41](#) zeigt einen Querschnitt durch die Abwandlung der ersten Ausführungsform

[0052] [Fig. 1](#) ist eine Ansicht zum Erläutern eines Beispiels einer Halbleitervorrichtung, auf die die vorliegende Erfindung angewendet werden kann, und sie zeigt eine allgemeine Leistungsvorrichtung und eine Leistungsvorrichtungstreibereinrichtung. In [Fig. 1](#) führen die n-Kanal-IGBT **51** und **52** (Insulated Gate Bipolar Transistors = Bipolartransistoren mit isoliertem Gate), die Leistungsschaltvorrichtungen sind,

das Schalten einer hohen Spannung HV durch, die eine Hauptleistungsversorgung ist. Eine Last ist mit einem Knoten N30 verbunden, und Freilaufdioden D1 und D2 sind jeweils mit den IGBT **51** und **52** verbunden, um die IGBT **51** und **52** vor einer elektromotorischen Rückspannung aufgrund der Last zu schützen.

**[0053]** Die Leistungsvorrichtungstreibereinrichtung **100** zum Treiben der IGBT **51** und **52** arbeitet entsprechend einem hochseitigen Steuereingang HIN zum Steuern des hochseitigen IGBT **51** und einem niedrigseitigen Steuereingang LIN zum Steuern des niedrigseitigen IGBT **52**. Die Leistungsvorrichtungstreibereinrichtung **100** enthält weiter eine hochseitige Treibereinheit **101** zum Treiben des hochseitigen IGBT **51** und eine niedrigseitige Treibereinheit **102** zum Treiben des niedrigseitigen IGBT **52** sowie eine Steuereingabenverarbeitungseinheit **103**.

**[0054]** Die Steuereingabenverarbeitungseinheit **103** führt eine Signalverarbeitung durch, um unerwünschte Bedingungen zu vermeiden wie z. B. einen Fall, in dem die IGBT **51** und **52** gleichzeitig eingeschaltet sind und kein Strom in die Last fließt, da ein Durchgangsstrom durch die IGBT **51** und **52** fließt, oder ähnliches. Ein hochseitiger Trebersignalausgang HO der hochseitigen Treibereinheit **101** ist mit einem Steueranschluss des IGBT **51** verbunden. Ein niedrigseitiger Trebersignalausgang LO der niedrigseitigen Treibereinheit **102** ist mit einem Steueranschluss des IGBT **52** verbunden.

**[0055]** Eine niedrigseitige feste Versorgungsspannung VCC, die als Leistungsversorgung für die niedrigseitige Treibereinheit **102** dient, wird von einer (nicht dargestellten) niedrigseitigen Festleistungsversorgung zugeführt. Eine hochseitige schwedende Offsetspannung VS dient als Referenzpotential der hochseitigen Treibereinheit **101**. Eine hochseitige schwedende Versorgungsabsolutspannung VB, die als Leistungsversorgung für die hochseitige Treiberinheit **101** dient, wird von einer (nicht dargestellten) hochseitigen schwedenden Leistungsversorgung geliefert. Eine gemeinsame Masse COM und die hochseitige schwedende Offsetspannung VS sind jeweils mit dem Emitteranschluss des IGBT **51** bzw. **52** verbunden.

**[0056]** Kondensatoren C1 und C2 sind jeweils zwischen die hochseitige schwedende Versorgungsabsolutspannung VB und die hochseitige schwedende Offsetspannung VS sowie zwischen die gemeinsame Masse COM und die niedrigseitige feste Versorgungsspannung VCC geschaltet, um eine der hochseitigen Treibereinheit **101** und der niedrigseitigen Treibereinheit **102** zugeführte Leistungsversorgungsspannung jeweils dem Betrieb der IGBT **51** und **52** entsprechenden Potentialschwankungen folgen zu lassen.

**[0057]** Somit hat die Leistungsvorrichtung den obigen Aufbau, um das Schalten der Hauptleistungsversorgung HV durch die IGBT **51** und **52** auf der Grundlage der Steuereingänge HIN und LIN durchzuführen.

**[0058]** Da die hochseitige Treibereinheit **101** so betrieben wird, dass ihr Potential im Hinblick auf das Massepotential der Schaltung in einem schwedenden Zustand ist, weist die hochseitige Treibereinheit **101** eine Pegelschiebeschaltung auf zum Übertragen eines Trebersignals zu einer hochseitigen Schaltung.

**[0059]** [Fig. 2](#) ist ein Schaltbild eines Hauptabschnitts der hochseitigen Treibereinheit **101**. In dieser Figur sind Bestandteile, die mit denen in [Fig. 1](#) identisch sind, durch dieselben Bezugszeichen bezeichnet.

**[0060]** Ein MOSFET **11** mit hoher Durchbruchspannung (im folgenden als "HV-MOS" bezeichnet) ist ein Schaltelement mit einer hohen Durchbruchspannung. Ein hochseitiger Trebersignalausgabe-CMOS **12** besteht aus einem p-MOS-Transistor und einem n-MOS-Transistor und gibt ein hochseitiges Treberignal aus. Ein Pegelschiebewiderstand **13** spielt eine Rolle, die einem Pull-Up-Widerstand entspricht zum Einstellen eines Gatepotentials des hochseitigen Trebersignalausgabe-CMOS **12**.

**[0061]** Der HV-MOS **11** führt das Schalten entsprechend dem hochseitigen Steuereingang HIN durch und ändert das Gatepotential des hochseitigen Trebersignalausgabe-CMOS **12**. Das lässt den hochseitigen Trebersignalausgabe-CMOS **12** das Schalten einer Spannung zwischen der hochseitigen schwedenden Versorgungsabsolutspannung VB und der hochseitigen schwedenden Offsetspannung VS durchführen und ein Treberignal zum Steuern des IGBT **51** an den hochseitigen Trebersignalausgang HO ausgeben.

**[0062]** [Fig. 3](#) ist eine schematische Draufsicht auf ein Layout einer Hochpotentialinsel in der Leistungsvorrichtungstreibereinrichtung **100**. Eine hochseitige Treberschaltung bestehend aus dem hochseitigen Trebersignalausgabe-CMOS **12** und dem Pegelschiebewiderstand **13** ist in einem Bereich gebildet, der Hochpotentialinsel genannt wird. Diese Figur ist eine schematische Draufsicht auf ein Layout der hochseitigen Treibereinheit **101**. Die Aluminiumverdrahtung in dieser Figur wird in Kontakt mit einem Massepotential GND gebracht. [Fig. 4](#) ist ein schematischer Querschnitt, der einen Hauptabschnitt der hochseitigen Treibereinheit **101** von [Fig. 2](#) zeigt entsprechend dem Schnitt B-B in [Fig. 3](#). In [Fig. 4](#) sind Bestandteile, die mit denen in [Fig. 1](#) und [Fig. 2](#) identisch sind, durch dieselben Bezugszeichen bezeichnet.

**[0063]** Ein Grundabschnitt einer p<sup>+</sup>-Trennung **201** erreicht einen p<sup>-</sup>-Bereich **200** eines Siliziumsubstrats (p-Substrat), und die Potentiale der p<sup>+</sup>-Trennung **201** und des p<sup>-</sup>-Bereichs **200** sind die niedrigsten in der Schaltung (das Massepotential GND bzw. das Potential der gemeinsamen Masse CCM). In einem Bereich, in dem der HV-MOS **11** gebildet ist, sind eine als erster Halbleiterbereich dienende n<sup>-</sup>-Schicht **110**, eine als zweiter Halbleiterbereich dienende p-Wanne **111** und ein n-Bereich **117** und ein n<sup>+</sup>-Drainbereich **118**, die als dritter Halbleiterbereich dienen und deren Dotierungskonzentration größer ist als die der n<sup>-</sup>-Schicht **110**, so ausgebildet, dass sie eine obere Oberfläche des Substrats erreichen. Die p-Wanne **111** ist in der n<sup>-</sup>-Schicht **110** so ausgebildet, dass sie in Kontakt mit der n<sup>-</sup>-Schicht **110** ist. Der n-Bereich **117** ist an so einer Stelle ausgebildet, dass die n<sup>-</sup>-Schicht **110** zwischen ihr und der p-Wanne **111** liegt. Anders ausgedrückt ist die p-Wanne **111** auf der einen Seite der n<sup>-</sup>-Schicht **110** ausgebildet, und der n-Bereich **117** ist an ihrer anderen Seite ausgebildet, so dass die n<sup>-</sup>-Schicht **110** zwischen ihnen liegt.

**[0064]** In der p-Wanne **111** sind weiter ein n<sup>+</sup>-Sourcebereich **112** und ein p<sup>+</sup>-Bereich **113** ausgebildet, und eine Sourceelektrode **114** ist darauf so ausgebildet, dass sie damit in Kontakt kommt. In der p-Wanne **111** zwischen dem n<sup>+</sup>-Sourcebereich **112** und der n<sup>-</sup>-Schicht **110** ist eine Gateelektrode **116** ausgebildet, wobei eine Gateisolierschicht **115** dazwischen liegt. Anders ausgedrückt dient die p-Wanne **111** als Kanalbereich des HV-MOS **11**. Eine Drainelektrode **119** des HV-MOS **11** ist so auf dem n<sup>+</sup>-Drainbereich **118** ausgebildet, dass sie damit verbunden ist.

**[0065]** In einer n-Schicht **121**, in der der p-MOS-Transistor des hochseitigen Treibersignalausgabe-CMOS **12** ausgebildet ist, sind ein p<sup>+</sup>-Drainbereich **122**, ein n<sup>+</sup>-Bereich **127** und ein p<sup>+</sup>-Sourcebereich **126** ausgebildet. Eine Drainelektrode **123** ist auf dem p<sup>+</sup>-Drainbereich **122** ausgebildet, eine Sourceelektrode **128** ist auf dem p<sup>+</sup>-Sourcebereich **126** und dem n<sup>+</sup>-Bereich **127** ausgebildet, und eine Gateelektrode **125** ist auf der n-Schicht **121** zwischen dem p<sup>+</sup>-Drainbereich **122** und dem p<sup>+</sup>-Sourcebereich **126** ausgebildet, wobei eine Gateisolierschicht **124** dazwischen liegt. In einer p-Wanne **131**, in der der n-MOS-Transistor des hochseitigen Treibersignalausgabe-CMOS **12** ausgebildet ist, sind ein p<sup>+</sup>-Bereich **132**, ein n<sup>+</sup>-Sourcebereich **133** und ein n<sup>+</sup>-Drainbereich **137** ausgebildet. Eine Sourceelektrode **134** ist auf dem p<sup>+</sup>-Bereich **132** und dem n<sup>+</sup>-Sourcebereich **133** ausgebildet, eine Drainelektrode **138** ist auf dem n<sup>+</sup>-Drainbereich **137** ausgebildet, und eine Gateelektrode **136** ist auf der p-Wanne **131** zwischen dem n<sup>+</sup>-Sourcebereich **133** und dem n<sup>+</sup>-Drainbereich **137** ausgebildet, wobei eine Gateisolierschicht **135** dazwischen liegt.

**[0066]** Die Drainelektrode **119** des HV-MOS **11** ist jeweils mit den Gateelektroden **125** und **136** des

p-MOS-Transistors und des n-MOS-Transistors des hochseitigen Treibersignalausgabe CMOS **12** verbunden, und sie ist auch mit der Sourceelektrode **128** des p-MOS-Transistors und der hochseitigen schwebenden Versorgungsabsolutspannung VB so verbunden, dass der Pegelschiebewiderstand **113** dazwischen liegt.

**[0067]** [Fig. 5](#) ist ein weiterer (von [Fig. 4](#) verschiedener) schematischer Querschnitt, der die hochseitige Treibereinheit **101** in der Leistungsvorrichtungstreibereinrichtung **100** zeigt, entsprechend den Schnitten A-A und C-C von [Fig. 3](#). In [Fig. 5](#) sind Bestandteile, die mit denen in [Fig. 4](#) identisch sind, durch dieselben Bezugszeichen bezeichnet. Ein Bereich **14** in [Fig. 5](#) bezeichnet eine (in [Fig. 1](#) oder [Fig. 2](#) nicht dargestellte) Diode hoher Durchbruchsspannung, die mit der hochseitigen Treibereinheit **101** verbunden ist.

**[0068]** Die Diode hoher Durchbruchsspannung **14** (im folgenden als "HV-Diode" bezeichnet) hat einen Aufbau wie der oben beschriebene HV-MOS **11** und eine als erste Halbleiterbereich dienende n<sup>-</sup>-Schicht **143**, eine als zweiter Halbleiterbereich dienende p<sup>+</sup>-Trennung **144** sowie die n-Schicht **121** und ein n<sup>+</sup>-Kathodenbereich **141**, die als dritter Halbleiterbereich dienen und deren Dotierungskonzentration größer ist als die der n<sup>-</sup>-Schicht **143**, sind so ausgebildet, dass sie eine obere Oberfläche des Substrats erreichen. Die p<sup>+</sup>-Trennung **144** ist in Kontakt mit einer Seite der n<sup>-</sup>-Schicht **143**, die n-Schicht **121** ist in Kontakt mit der anderen Seite der n<sup>-</sup>-Schicht **143**. Anders ausgedrückt sind die p<sup>+</sup>-Trennung **144** und die n-Schicht **121** so ausgebildet, dass die n<sup>-</sup>-Schicht **143** dazwischen liegt. Die p<sup>+</sup>-Trennung **144**, die als Anode der HV-Diode **14** wirkt, wird im folgenden als "p<sup>+</sup>-Anodenbereich **144**" bezeichnet. Eine Kathodenelektrode **142** der HV-Diode **14** ist auf dem Kathodenbereich **141** so ausgebildet, dass sie mit ihm in Kontakt kommt. Eine Anodenelektrode **145** ist auf dem p<sup>+</sup>-Anodenbereich **144** so ausgebildet, dass sie mit ihm in Kontakt kommt. Der p<sup>+</sup>-Anodenbereich **144** erreicht den p<sup>-</sup>-Bereich **200**. Da die Anodenelektrode **145** auf dem p<sup>+</sup>-Anodenbereich **144** ausgebildet ist, ist das Potential des p<sup>-</sup>-Bereichs **200** das niedrigste in der Schaltung (Massepotential GND oder Potential der gemeinsamen Masse COM). Die HV-Diode **14** hält eine Spannung zwischen der hochseitigen schwebenden Versorgungsabsolutspannung VB und dem Massepotential GND oder dem Potential der gemeinsamen Masse COM.

**[0069]** Im Folgenden werden anhand der Figuren verschiedene Ausführungsformen beschrieben. Von diesen gehört die vierte Ausführungsform zur vorliegenden Erfindung;

**[0070]** [Fig. 6](#) ist eine Ansicht eines Aufbaus eines HV-MOS nach einer ersten Ausführungsform, und sie ist eine vergrößerte Ansicht des HV-MOS **11** aus

**Fig. 4.** In **Fig. 6** sind Bestandteile, die mit denen in **Fig. 4** identisch sind, durch dieselben Bezugszeichen bezeichnet. In dieser Figur sind jedoch zur Erleichterung der nachfolgenden Erläuterung die lateralen Seiten umgekehrt wie in **Fig. 4** dargestellt.

**[0071]** Auf der n<sup>-</sup>-Schicht **110** ist eine erste Isolierschicht LA ausgebildet. Auf einer oberen Oberfläche der ersten Isolierschicht LA sind eine Mehrzahl erster schwebender Feldplatten FA (FA1 bis FA8) oberhalb der n<sup>-</sup>-Schicht **110** ausgebildet. Auf den ersten schwebenden Feldplatten FA ist weiter eine zweite Isolierschicht LB ausgebildet. Auf einer oberen Oberfläche der zweiten Isolierschicht LB sind eine Mehrzahl von zweiten schwebenden Feldplatten FB (FB1 bis FB8) oberhalb der n<sup>-</sup>-Schicht **110** ausgebildet.

**[0072]** In dieser Beschreibung wird eine Richtung von dem dritten Halbleiterbereich (hier dem n-Bereich **117**) aus zu dem zweiten Halbleiterbereich (hier der p-Wanne **111**) hin als "erste Richtung" bezeichnet, und eine Dickerichtung der ersten Isolierschicht LA und der zweiten Isolierschicht LB als eine "zweite Richtung" (in **Fig. 6** durch Pfeile angegeben). Die ersten schwebenden Feldplatten FA1 bis FA8 sind in der ersten Richtung angeordnet, und die zweiten schwebenden Feldplatten FB1 bis FB8 sind ebenfalls in der ersten Richtung angeordnet.

**[0073]** Die Drainelektrode **119** weist einen sich auf der ersten Isolierschicht LA erstreckenden Abschnitt DA auf, der als normale Feldplatte (nicht in dem schwebenden Zustand) dient und im folgenden als "erster Drainelektrodenabschnitt DA" bezeichnet wird. Weiter weist die Gateelektrode **116** einen sich auf der ersten Isolierschicht LA erstreckenden Abschnitt GA und einen sich auf der zweiten Isolierschicht LB erstreckenden Abschnitt GB auf, die beide als normale Feldplatten dienen. Im folgenden wird der Erstere als "erster Gateelektrodenabschnitt GA" und der Letztere als "zweiter Gateelektrodenabschnitt GB" bezeichnet.

**[0074]** Die ersten schwebenden Feldplatten FA und die zweiten Feldplatten FB beschleunigen die Ausdehnung einer Verarmungsschicht in der n<sup>-</sup>-Schicht **110** durch einen Feldplatteneffekt. Die jeweiligen ersten schwebenden Feldplatten FA und die jeweiligen zweiten schwebenden Feldplatten FB sind über die dazwischen liegende zweite Isolierschicht LB kapazitiv miteinander gekoppelt und bilden dadurch eine Mehrzahl von Kondensatoren. Die zweite schwebende Feldplatte FB1, die dem Drain am nächsten liegt, ist über die dazwischen liegende zweite Isolierschicht LB kapazitiv mit dem ersten Drainelektrodenabschnitt DA gekoppelt und bildet somit einen Kondensator. Die erste schwebende Feldplatte FA8, die dem Gate am nächsten liegt, ist über die dazwischen liegende zweite Isolierschicht LB kapazitiv mit dem zweiten Gateelektrodenabschnitt GB gekoppelt und

bildet somit einen Kondensator. Diese Kondensatoren in großer Anzahl teilen sich und halten die zwischen der Drainelektrode **119** und der Sourceelektrode **114** angelegte hohe Spannung, wenn der HV-MOS ausgeschaltet ist, um somit die Potentiale der jeweiligen ersten schwebenden Feldplatten FA und die der jeweiligen zweiten schwebenden Feldplatten FB festzulegen. Das verhindert eine übermäßige Beschleunigung der Ausdehnung der Verarmungsschicht durch den Feldplatteneffekt.

**[0075]** Unter der Annahme, dass die ersten schwebenden Feldplatten FA eine fortlaufende Platte seien, würde die Ausdehnung der Verarmungsschicht übermäßig beschleunigt und eine elektrische Feldkonzentration in einer Oberfläche des Siliziumsubstrats nahe beim Drain auftreten, wodurch eine Erhöhung der Spannungsfestigkeit des HV-MOS verhindert würde. In der ersten bevorzugten Ausführungsform sind eine Mehrzahl von ersten schwebenden Feldplatten FA und eine Mehrzahl von zweiten schwebenden Feldplatten FB in der ersten Richtung angeordnet, um dadurch eine übermäßige Ausdehnung der Verarmungsschicht zu unterdrücken und ein Erhöhen der Spannungsfestigkeit des HV-MOS sicherzustellen.

**[0076]** Der HV-MOS in **Fig. 6**, der eine RESURF-Struktur aufweist, stellt das Erhöhen der Spannungsfestigkeit weiter sicher. Insbesondere durch Anlegen einer Rückwärtsspannung, die kleiner als die Durchbruchspannung eines pn-Übergangs zwischen der n<sup>-</sup>-Schicht **110** und der p-Wanne **111** ist (im folgenden als "zweiter pn-Übergang" bezeichnet), an einen pn-Übergang (im folgenden als "erster pn-Übergang" bezeichnet) zwischen der n<sup>-</sup>-Schicht **110** und dem p<sup>-</sup>-Bereich **200** (den vierten Halbleiterbereich) wird die Dotierungskonzentration der n<sup>-</sup>-Schicht **110** verringert und ihre Dicke verkleinert, sodass die Verarmungsschicht sich in der n<sup>-</sup>-Schicht **110** zwischen dem n-Bereich **117** und der p-Wanne **111** von dem ersten pn-Übergang aus bis zu der oberen Oberfläche des Substrats hin erstrecken sollte.

**[0077]** In der ersten Ausführungsform ist die erste Isolierschicht LA dicker und die zweite Isolierschicht LB dünner ausgebildet als bei einem bekannten Aufbau, so dass unter der Annahme, dass a die Dicke der ersten Isolierschicht LA ist und b der Abstand zwischen den ersten schwebenden Feldplatten FA und den zweiten schwebenden Feldplatten FB in der zweiten Richtung (einer Dickerichtung der zweiten Isolierschicht LB) ist, eine Beziehung a > b eingehalten werden kann.

**[0078]** **Fig. 7** ist ein Diagramm, das eine elektrische Feldverteilung in dem HV-MOS von **Fig. 6** zu einem Zeitpunkt zeigt, zu dem eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand angelegt ist, der durch Erzeugen eines Kurzschlusses zwischen der Gate-

elektrode 116 und der Sourceelektrode 114 in dem HV-MOS bewirkt wird. Diese Figur zeigt die elektrische Feldverteilung in einem Bereich von der Siliziumsubstratoberfläche (Si-Oberfläche) bis zu der Tiefe des pn-Übergangs zwischen dem n-Bereich 117 und dem p-Bereich 200. Insbesondere zeigen die durchgezogenen Linien die elektrische Feldverteilung an der Siliziumsubstratoberfläche und die elektrische Feldverteilung in der Tiefe eines ersten pn-Übergangs zwischen der n-Schicht 110 und dem p-Bereich 200. [Fig. 8](#) dagegen ist ein Diagramm, das eine elektrische Feldverteilung wie die in [Fig. 7](#) bei einem bekannten HV-MOS zeigt (bei dem eine Beziehung  $a < b$  in [Fig. 6](#) eingehalten wird und die Drainelektrode 119 und die zweite schwebende Feldplatte FB1 miteinander verbunden sind).

**[0079]** Wie aus [Fig. 7](#) und [Fig. 8](#) ersichtlich ist ein Abschnitt mit der höchsten elektrischen Feldstärke ein Abschnitt nahe dem Drain in der Tiefe des ersten pn-Übergangs. Daher ist der Abschnitt ein Punkt eines durchbruchkritischen Feldes, der einen Wert der Spannungsfestigkeit des HV-MOS bestimmt. In der Siliziumsubstratoberfläche dagegen können elektrische Feldspitzen (elektrische Feldkonzentrationen) beobachtet werden in einem Abschnitt unter einer Kante des ersten Gateelektrodenabschnitts GA und in Abschnitten unter jeweiligen Kanten der ersten schwebenden Feldplatten FA1 bis FA8 auf ihrer Drainseite oder in Abschnitten unter ihren jeweiligen Kanten auf ihrer Sourceseite.

**[0080]** Wie in [Fig. 8](#) gezeigt sind die elektrischen Feldspitzen bei dem bekannten HV-MOS in der Siliziumsubstratoberfläche relativ groß, und der Unterschied (Spielraum) zu der elektrischen Feldstärke an dem Punkt des durchbruchkritischen elektrischen Felds ist sehr klein. Daher übersteigt die elektrische Feldspitze an der Siliziumsubstratoberfläche leicht die elektrische Feldstärke an dem Punkt des durchbruchkritischen elektrischen Felds aufgrund einer Wirkung der Polarisierung der Überzugisolierschicht oder der Epoxidschicht, die auf dem HV-MOS ausgebildet sind, während der tatsächlichen Verwendung, und das kann Probleme bewirken wie z. B. eine Verringerung der Spannungsfestigkeit und eine Instabilität der Spannungsfestigkeitseigenschaft.

**[0081]** In der ersten Ausführungsform dagegen sind nach [Fig. 7](#) die elektrischen Feldspitzen in der Substratoberfläche relativ klein. Anders ausgedrückt wird die elektrische Feldkonzentration verringert. Da der Spielraum im Hinblick auf die elektrische Feldstärke an dem Punkt des durchbruchkritischen elektrischen Felds steigt und es unwahrscheinlich ist, dass die elektrischen Feldspitzen in der Siliziumsubstratoberfläche die elektrische Feldstärke an dem Punkt des durchbruchkritischen elektrischen Feldes überschreiten, können Probleme wie z. B. eine Verringerung der Spannungsfestigkeit und eine Instabili-

tät der Spannungsfestigkeitseigenschaft unterdrückt werden. Demzufolge kann der HV-MOS eine hohe Spannungsfestigkeit stabil halten.

**[0082]** [Fig. 9](#) ist ein Diagramm, das eine Beziehung zwischen einem Wert a-b und einem Wert der elektrischen Feldspitze in der Siliziumsubstratoberfläche zeigt. Aus dieser Figur ist zu entnehmen, dass ein Wert der elektrischen Feldspitze kleiner wird, wenn ein Wert von a-b größer wird. Anders ausgedrückt steigt der Spielraum im Hinblick auf die elektrische Feldstärke an dem Punkt des durchbruchkritischen elektrischen Felds, und die obige Wirkung kann erhöht werden, indem der Wert von a-b erhöht wird, in dem die Dicke a erhöht und der Abstand b verringert wird.

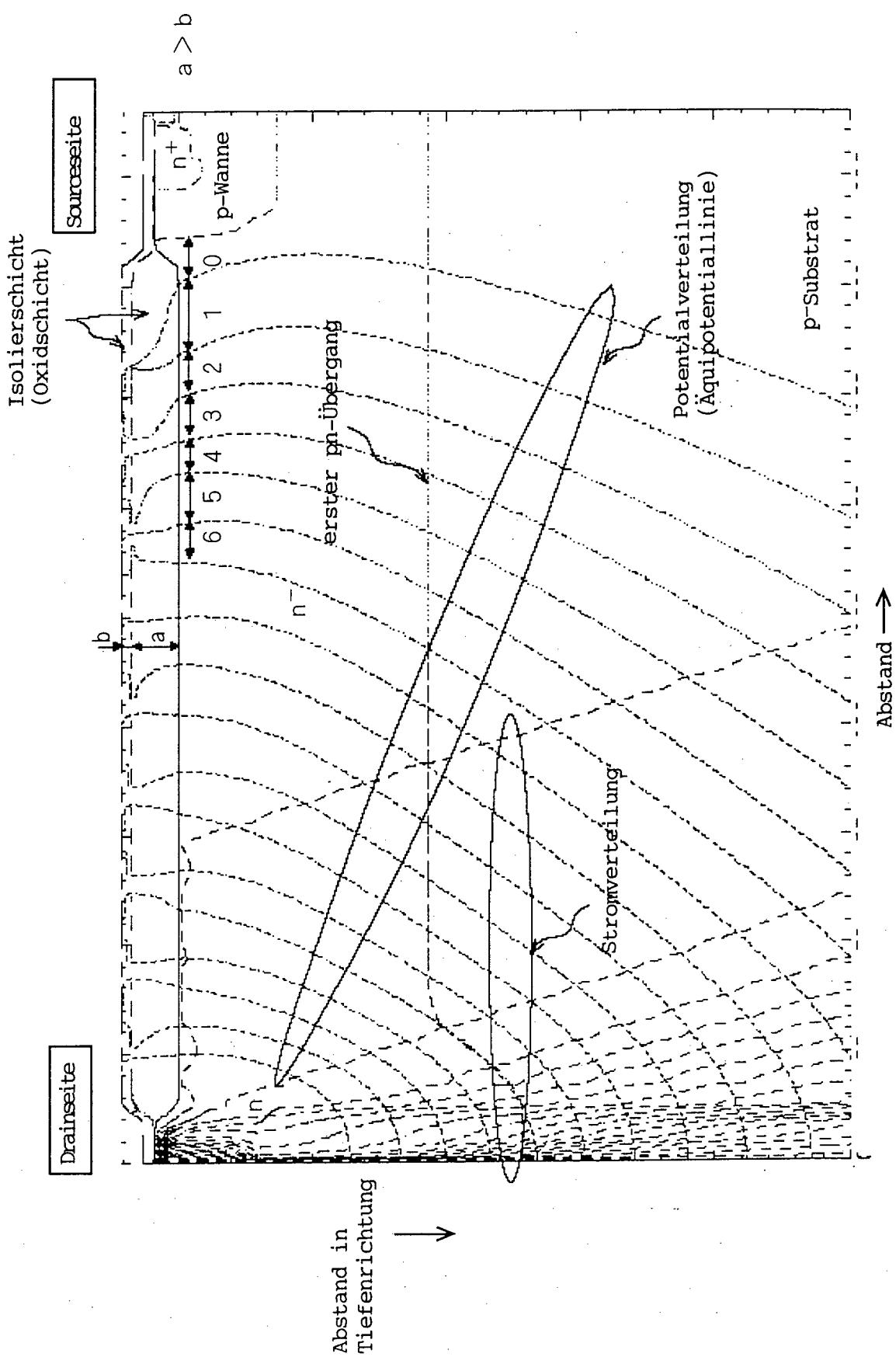

**[0083]** [Fig. 10](#) ist ein Diagramm, das eine Potentialverteilung und eine Stromverteilung in dem HV-MOS von [Fig. 6](#) zu einer Zeit zeigt, zu der eine hohe Spannung zwischen der Drainelektrode 119 und der Sourceelektrode 114 in einem AUS-Zustand des HV-MOS angelegt ist. Die Potentialverteilung wird durch Äquipotentiallinien angezeigt, und ihre Form entspricht der Ausdehnung der Verarmungsschicht von der Sourceseite aus zu der Drainseite hin. [Fig. 11](#) dagegen ist ein Diagramm, das eine Potentialverteilung und eine Stromverteilung wie die in [Fig. 10](#) dargestellt für den bekannten HV-MOS zeigt (bei dem in [Fig. 6](#) eine Beziehung  $a < b$  eingehalten ist).

**[0084]** Die Bezugszeichen 0 bis 6 in [Fig. 10](#) und [Fig. 11](#) stellen Intervalle der Äquipotentiallinien in der Siliziumsubstratoberfläche dar (in der Grenzfläche zwischen der n-Schicht 110 und der ersten Isolierschicht LA). In dem HV-MOS der ersten Ausführungsform ist die Verzerrung der Äquipotentiallinien in der ersten Isolierschicht LA wie in [Fig. 10](#) dargestellt verringert, da die Dicke a der ersten Isolierschicht LA groß ist, und die Größen der Intervalle 0 bis 6 werden dadurch gleichförmiger als in dem Fall der bekannten Technik in [Fig. 11](#). Das bedeutet, dass die Ausdehnung der Verarmungsschicht nahe der Siliziumsubstratoberfläche in dem HV-MOS der ersten bevorzugten Ausführungsform gleichförmiger ist als in dem bekannten Aufbau. Da die elektrische Feldkonzentration weniger wahrscheinlich auftritt, wenn die Ausdehnung der Verarmungsschicht gleichförmig wird, ist die Größe der elektrischen Feldspitze in der Siliziumoberfläche bei dem HV-MOS der ersten Ausführungsform zu einem niedrigeren Wert hin verringert. Somit kann auch aus der Potentialverteilung in [Fig. 10](#) die mit Bezug auf [Fig. 7](#) erörterte Wirkung beobachtet werden.

**[0085]** [Fig. 12](#) ist ein Diagramm, das eine Verteilung von Potentialunterschieden zeigt, die in den Kondensatoren, die zwischen den ersten schwebenden Feldplatten FA, den zweiten schwebenden Feldplatten FB, dem ersten Gateelektrodenabschnitt DA, dem

ersten Gateelektrodenabschnitt GA und dem zweiten Gateelektrodenabschnitt GB ausgebildet sind, zwischen dem Drain und der Source zu einer Zeit gehalten werden, zu der eine hohe Spannung zwischen der Source und dem Drain des HV-MOS in einem AUS-Zustand angelegt ist. In [Fig. 12](#) zeigt die durchgezogene Linie eine Verteilung in dem HV-MOS der in [Fig. 6](#) gezeigten ersten Ausführungsform, und die gestrichelte Linie zeigt eine Verteilung bei dem bekannten HV-MOS (bei dem eine Beziehung  $a < b$  eingehalten ist und die DrainElektrode **119** und die zweite schwebende Feldplatte FB1 in [Fig. 6](#) miteinander verbunden sind). Bei dem bekannten HV-MOS neigt eine hohe Spannung dazu, besonders in den Kondensatoren nahe der Sourceseite und der Drainseite gehalten zu werden, und es besteht die Möglichkeit, dass an diesen Abschnitten ein dielektrischer Durchbruch der zweiten Isolierschicht LB bewirkt wird. Wie in [Fig. 12](#) dargestellt sinkt die Tendenz bei dem HV-MOS der ersten Ausführungsform, und eine Schwankung der in den Kondensatoren gehaltenen Potentialunterschiede wird kleiner. Kurz gesagt erzielt die erste Ausführungsform eine Wirkung des Verhinderns des dielektrischen Durchbruchs der zweiten Isolierschicht LB, was zu einem Ansteigen der Spannungsfestigkeit des HV-MOS führt.

**[0086]** Da bei dem HV-MOS der ersten Ausführungsform der Abstand  $b$  zwischen den ersten schwebenden Feldplatten FA und den zweiten schwebenden Feldplatten FB in der Dickerichtung (der zweiten Richtung) kleiner ist, steigen die Kapazitätswerte der Kondensatoren. Da der Effekt der kapazitiven Kopplung in den Kondensatoren steigt, wird daher die Polarisierung der zweiten Isolierschicht LB beschleunigt. Bei dem bekannten Aufbau erstreckt sich die Verarmungsschicht in einem oberen Abschnitt der n-Schicht **110** leicht unter den jeweiligen ersten schwebenden Feldplatten FA, aber sie erstreckt sich schwer unter Lücken zwischen den ersten schwebenden Feldplatten FA. Bei der ersten Ausführungsform dagegen beschleunigt der Effekt der hohen kapazitiven Kopplung in den Kondensatoren die Polarisierung der zweiten Isolierschicht LB, und dies erzielt eine Wirkung, dass die Ausdehnung der Verarmungsschicht auch unter den Lücken zwischen den ersten schwebenden Feldplatten FA erleichtert wird, was zu einem Ansteigen der Spannungsfestigkeit des HV-MOS führt.

**[0087]** Wie oben erörtert kann die vorliegende Ausführungsform auf eine Halbleitervorrichtung mit einer RESURF-Struktur angewendet werden. Das erlaubt eine weitere Erhöhung der Spannungsfestigkeit verglichen mit der bekannten RESURF-Struktur. Weiterhin kann die vorliegende Ausführungsform auf eine Mehrfach-RESURF-Struktur angewendet werden, bei der die n-Schicht **110** einen mehrlagigen Aufbau hat, bei der die jeweiligen Schichten verschiedene

Dotierungskonzentration aufweisen (z. B. in dem Patent US 4,422,089 A gezeigt).

**[0088]** Auch wenn oben der Fall erläutert wurde, bei dem die vorliegende Ausführungsform auf einen MOSFET angewendet ist, ist die Anwendung der vorliegenden Ausführungsform nicht darauf beschränkt, sondern die vorliegende Ausführungsform kann weit angewendet werden, z. B. auf eine Diode, einen IGBT oder dergleichen.

**[0089]** [Fig. 13](#) ist eine Ansicht eines Falles, bei dem die erste Ausführungsform auf eine Diode hoher Durchbruchspannung (HV-Diode) angewendet ist, und sie zeigt eine vergrößerte Ansicht der HV-Diode von [Fig. 5](#). Da Bestandteile, die mit denen in [Fig. 5](#) und [Fig. 6](#) identisch sind, durch dieselben Bezeichnungen bezeichnet sind, unterbleibt ihre detaillierte Beschreibung. Auch in dieser Figur sind die lateralen Seiten zur Erleichterung der folgenden Erläuterung umgekehrt wie in [Fig. 5](#) dargestellt.

**[0090]** Die Kathodenelektrode **142** weist einen sich auf der ersten Isolierschicht LA erstreckenden Abschnitt CA auf, der als normale Feldplatte wirkt. Dieser Abschnitt wird im folgenden als "erster Kathodenelektrodenabschnitt CA" bezeichnet. Die AnodenElektrode **145** weist einen sich auf der ersten Isolierschicht LA erstreckenden Abschnitt AA und einen sich auf der zweiten Isolierschicht LB erstreckenden Abschnitt AB auf, die beide als normale Feldplatten wirken. Im folgenden wird der Abschnitt AA als "erster Anodenelektrodenabschnitt AA" und der Abschnitt AB als "zweiter Anodenelektrodenabschnitt AB" bezeichnet.

**[0091]** Da in der HV-Diode **14** wie oben erläutert die n-Schicht **143** als erster Halbleiterbereich, der p-Anodenbereich **144** als zweiter Halbleiterbereich und die n-Schicht **121** als dritter Halbleiterbereich dient, ist die "erste Richtung" in diesem Fall eine Richtung von der n-Schicht **121** zu dem p-Anodenbereich **144** (siehe Pfeile in [Fig. 13](#)).

**[0092]** Auch die HV-Diode **14** hat den RESURF-Aufbau. Insbesondere durch Anlegen einer Rückwärtsspannung, die kleiner als die Durchbruchspannung eines pn-Übergangs zwischen der n-Schicht **143** und dem p-Anodenbereich **144** ist, an einen pn-Übergang zwischen der n-Schicht **143** und dem p-Bereich **200** (den vierten Halbleiterbereich) wird die Dotierungskonzentration der n-Schicht **143** verringert und ihre Dicke verkleinert, sodass die Verarmungsschicht sich in der n-Schicht **143** zwischen dem n-Bereich **121** und dem p-Anodenbereich **144** von dem ersten pn-Übergang aus bis zu der oberen Oberfläche des Substrats hin erstrecken sollte.

**[0093]** Auch bei der HV-Diode von [Fig. 13](#) ist im Vergleich zu dem bekannten Aufbau die erste Iso-

lierschicht LA dicker und die zweite Isolierschicht LB dünner ausgebildet, so dass so dass unter der Annahme, dass  $a$  die Dicke der ersten Isolierschicht LA ist und  $b$  der Abstand zwischen den ersten schwebenden Feldplatten FA und den zweiten schwebenden Feldplatten FB in der zweiten Richtung (einer Dickerichtung der zweiten Isolierschicht LB) ist, eine Beziehung  $a > b$  eingehalten werden kann. Auch in der HV-Diode, die die Beziehung  $a > b$  erfüllt, wird die elektrische Feldspitze in der Siliziumsubstratoberfläche kleiner und die elektrische Feldkonzentration wird verringert, und daher kann dieselbe Wirkung wie oben erläutert erzielt werden, z. B. das Unterdrücken der Probleme wie ein Abnehmen der Spannungsfestigkeit und eine Instabilität der Spannungsfestigkeiteigenschaft, wie sie oben diskutiert wurden.

[0094] [Fig. 14](#) zeigt einen Aufbau eines HV-MOS entsprechend einer zweiten Ausführungsform. Der HV-MOS der zweiten Ausführungsform unterscheidet sich von dem in [Fig. 6](#) gezeigten HV-MOS der ersten Ausführungsform darin, dass die Drainelektrode **119** einen Abschnitt DB aufweist, der sich auf der zweiten Isolierschicht LB erstreckt. Dieser Abschnitt DB wirkt als normale Feldplatte (nicht in schwebendem Zustand) und wird im folgenden als "zweiter Drainelektrodenabschnitt DB" bezeichnet.

[0095] Wie in [Fig. 14](#) dargestellt ist die Länge eines Abschnitts des zweiten Drainelektrodenabschnitts DB, der sich oberhalb der ersten Isolierschicht LA in der ersten Richtung (der Richtung von dem n-Bereich **117** zu dem n<sup>+</sup>-Sourcebereich **112**) erstreckt, länger als die Länge eines Abschnitts in dem ersten Drainelektrodenabschnitt DA, der sich auf der ersten Isolierschicht LA in der ersten Richtung erstreckt. Anders ausgedrückt bedeckt der zweite Drainelektrodenabschnitt DB den ersten Drainelektrodenabschnitt DA, wobei die zweite Isolierschicht LB dazwischen liegt. Der zweite Drainelektrodenabschnitt DB überlappt teilweise einen Abschnitt der ersten schwebenden Feldplatte FA1, wobei die zweite Isolierschicht LB dazwischen liegt. Anders ausgedrückt ist der zweite Drainelektrodenabschnitt DB wie in [Fig. 14](#) dargestellt ein Abschnitt, in dem die erste schwebende Feldplatte FB1 mit der Drainelektrode **119** von [Fig. 6](#) verbunden ist.

[0096] [Fig. 15](#) ist ein Diagramm, das eine elektrische Feldverteilung in dem HV-MOS von [Fig. 14](#) zu einer Zeit zeigt, zu der eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand angelegt ist, der durch Erzeugen eines Kurzschlusses zwischen der Gateelektrode **116** und der Sourceelektrode **114** in dem HV-MOS bewirkt wird. Diese Figur zeigt die elektrische Feldverteilung in einem Bereich von der Siliziumsubstratoberfläche (Si-Oberfläche) bis zu der Tiefe des pn-Übergangs zwischen dem n-Bereich **117** und dem p-Bereich **200**. Insbesondere bezeichnen die durchgezogenen Linien die elektrische Feldverteilung in der Siliziumsubstratoberfläche und die elektrische Feldverteilung in der Tiefe des ersten pn-Übergangs zwischen der n<sup>-</sup>-Schicht **110** und dem p-Bereich **200**.

[0097] Wie aus einem Vergleich zwischen [Fig. 15](#) und [Fig. 7](#) der ersten Ausführungsform ersichtlich kann bei der zweiten Ausführungsform die elektrische Feldspitze unter einem Kantenabschnitt der ersten schwebenden Feldplatte FA1 auf der Drainseite in dem Siliziumsubstrat verringert werden. Da somit die elektrische Feldstärke nahe dem Punkt des durchbruchkritischen Feldes (einem Abschnitt in der Tiefe des ersten pn-Übergangs des n-Bereichs **117** auf der Drainseite) kleiner wird, steigt die Spannungsfestigkeit in dem HV-MOS. Kurz gesagt kann die zweite Ausführungsform im Vergleich zu der ersten Ausführungsform eine weitere Erhöhung der Spannungsfestigkeit bewirken.

[0098] [Fig. 16](#) ist ein Diagramm, das eine Verteilung der Potentialdifferenzen zeigt, die in den Kondensatoren, die zwischen den ersten schwebenden Feldplatten FA, den zweiten schwebenden Feldplatten FB, dem ersten Drainelektrodenabschnitt DA, dem ersten Gateelektrodenabschnitt GA und dem zweiten Gateelektrodenabschnitt GB gebildet werden, zwischen dem Drain und der Source zu einer Zeit gehalten werden, zu der zwischen Source und Drain des HV-MOS in einem AUS-Zustand eine hohe Spannung angelegt ist. In [Fig. 16](#) zeigt die durchgezogene Linie eine Verteilung in dem in [Fig. 14](#) gezeigten HV-MOS der zweiten Ausführungsform, und die gestrichelte Linie zeigt eine Verteilung in dem bekannten HV-MOS (bei dem in [Fig. 14](#) eine Beziehung  $a < b$  eingehalten ist). Es ist festzustellen, dass die Schwankung der in den Kondensatoren gehaltenen Potentialdifferenzen in der zweiten Ausführungsform wie in der ersten Ausführungsform kleiner wird. Kurz gesagt, erzielt auch die zweite Ausführungsform eine Wirkung des Verhinderns des dielektrischen Durchbruchs der zweiten Isolierschicht LB, was zu einem Erhöhen der Spannungsfestigkeit des HV-MOS führt.

[0099] [Fig. 17](#) ist eine Ansicht eines Aufbaus eines HV-MOS entsprechend einer dritten Ausführungsform. Da in [Fig. 17](#) Bestandteile, die mit denen in [Fig. 6](#) und [Fig. 14](#) identisch sind, durch dieselben Bezugszeichen bezeichnet sind, unterbleibt ihre detaillierte Beschreibung.

[0100] In der dritten Ausführungsform ist die Breite jeder der ersten schwebenden Feldplatten FA gleich groß wie der Zwischenraum zwischen den ersten schwebenden Feldplatten FA. Anders ausgedrückt wird unter der Annahme, dass die i Breite jeder der ersten schwebenden Feldplatten FA in der ersten Richtung (von dem n-Bereich **117** zu dem n<sup>+</sup>-Sourcebereich **112**) ist und dass j der Abstand zwischen einer der ersten schwebenden Feldplatten FA und ih-

rer benachbarten in der ersten Richtung ist, wird eine Beziehung  $i = j$  eingehalten. Weiter ist im Fall von [Fig. 17](#) die Beziehung zwischen der Dicke  $a$  (der Dicke der ersten Isolierschicht LA) und dem Abstand  $b$  (dem Abstand zwischen den ersten schwebenden Feldplatten FA und den zweiten schwebenden Feldplatten FB in der zweiten Richtung) wie bei dem bekannten Aufbau  $a < b$ . Ansonsten unterscheidet sich [Fig. 17](#) der dritten Ausführungsform nicht von [Fig. 14](#) der zweiten Ausführungsform.

**[0101]** [Fig. 18](#) ist ein Diagramm, das eine elektrische Feldverteilung in dem HV-MOS von [Fig. 17](#) zu einer Zeit zeigt, zu der eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand angelegt ist, der durch Erzeugen eines Kurzschlusses zwischen der Gateelektrode **116** und der Sourceelektrode **114** in dem HV-MOS bewirkt wird. Diese Figur zeigt die elektrische Feldverteilung in einem Bereich von der Siliziumsubstratoberfläche (Si-Oberfläche) bis zu der Tiefe des pn-Übergangs zwischen dem n-Bereich **117** und dem p<sup>-</sup>-Bereich **200**. Insbesondere zeigen die durchgezogenen Linien die elektrische Feldverteilung in der Siliziumsubstratoberfläche und die elektrische Feldverteilung in der Tiefe des ersten pn-Übergangs zwischen der n<sup>-</sup>-Schicht **110** und dem p<sup>-</sup>-Bereich **200**. Wie aus dem Bereich zwischen [Fig. 18](#) und [Fig. 8](#) ersichtlich, die die elektrische Feldverteilung in dem bekannten HV-MOS zeigt, wird in [Fig. 18](#) der dritten Ausführungsform die elektrische Feldspitze in der Siliziumsubstratoberfläche kleiner, und die elektrische Feldkonzentration wird verringert. Da somit der Spielraum im Hinblick auf die elektrische Feldstärke an dem Punkt des durchbruchkritischen elektrischen Feldes ansteigt und es unwahrscheinlich ist, dass die elektrische Feldspitze in der Siliziumsubstratoberfläche die elektrische Feldstärke an dem Punkt des durchbruchkritischen elektrischen Feldes übersteigt, können Probleme wie ein Verringern der Spannungsfestigkeit und eine Instabilität der Spannungsfestigkeiteigenschaft unterdrückt werden. Demzufolge kann der HV-MOS eine hohe Spannungsfestigkeit mit hoher Stabilität halten.

**[0102]** [Fig. 19](#) ist ein Diagramm, das eine Potentialverteilung und eine Stromverteilung in dem HV-MOS von [Fig. 17](#) zu einer Zeit zeigt, in der eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand des HV-MOS angelegt ist. Auch in [Fig. 19](#) ist die Potentialverteilung durch Äquipotentiallinien angezeigt, und die Bezugszeichen 0 bis 6 stellen Intervalle der Äquipotentiallinien in der Siliziumsubstratoberfläche (in der Grenzfläche zwischen der n<sup>-</sup>-Schicht **110** und der ersten Isolierschicht LA) dar. Da in der dritten Ausführungsform die Breite jeder der ersten schwebenden Feldplatten FA gleich dem Abstand zwischen einer der ersten schwebenden Feldplatten FA und ihrer benachbarten ist, werden die Größen der Intervalle 0 bis 6 gleichför-

miger als die in dem Fall der bekannten Technik von [Fig. 11](#). Kurz gesagt ist in dem HV-MOS der dritten Ausführungsform die Ausdehnung der Verarmungsschicht nahe der Siliziumsubstratoberfläche gleichförmiger als die in dem Aufbau der bekannten Technik, und daher ist die Größe der elektrischen Feldspitze in diesem Abschnitt zu einem kleineren Wert hin verringert. Somit kann die obige Wirkung aus der Potentialverteilung in [Fig. 19](#) beobachtet werden.

**[0103]** Auch wenn in [Fig. 17](#) die Beziehung zwischen der Dicke  $a$  und dem Abstand  $b$  durch  $a < b$  gegeben ist, kann die Beziehung zwischen  $a$  und  $b$  auch  $a > b$  sein, wobei die erste Ausführungsform auf die dritte Ausführungsform angewendet wird. In diesem Fall kann die dritte Ausführungsform auch die Wirkung der ersten Ausführungsform hervorbringen und eine weitere Erhöhung der Spannungsfestigkeit erzielen.

**[0104]** Auch wenn der Fall erörtert wurde, bei dem die vorliegende Ausführungsform auf einen MOSFET angewendet wird, ist auch in der dritten Ausführungsform die Anwendung nicht darauf beschränkt, sondern die vorliegende Ausführungsform kann weit angewendet werden, z. B. auf eine Diode, einen IGBT oder dergleichen.

**[0105]** [Fig. 20](#) ist eine Ansicht eines Aufbaus eines HV-MOS entsprechend einer vierten Ausführungsform. Da in [Fig. 20](#) Bestandteile, die mit denen in [Fig. 6](#) und [Fig. 14](#) identisch sind, durch dieselben Bezugszeichen bezeichnet sind, unterbleibt ihre detaillierte Beschreibung.

**[0106]** Der HV-MOS der vierten Ausführungsform weist zusätzlich zu dem Aufbau des HV-MOS von [Fig. 6](#) eine auf den zweiten schwebenden Feldplatten FB ausgebildete dritte Isolierschicht LC sowie eine Mehrzahl von dritten schwebenden Feldplatten FC (FC1 bis FC6) auf, die auf dieser ausgebildet sind. Die dritten schwebenden Feldplatten FC sind oberhalb der n<sup>-</sup>-Schicht **110** in der ersten Richtung angeordnet (der Richtung von dem n-Bereich **117** zu dem n<sup>+</sup>-Sourcebereich **112**). Unter der Annahme, dass  $a$  die Dicke der ersten Isolierschicht LA ist, dass  $b$  der Abstand zwischen den ersten schwebenden Feldplatten FA und den zweiten schwebenden Feldplatten FB in der zweiten Richtung (der Dickerichtung der ersten Isolierschicht LA, der zweiten Isolierschicht LB und der dritten Isolierschicht LC) ist und dass  $c$  der Abstand zwischen den zweiten schwebenden Feldplatten FB und den dritten schwebenden Feldplatten FC in der zweiten Richtung ist, ist der Abstand  $c$  kleiner (die dritte Isolierschicht LC ist dünner), so dass die Beziehungen  $c < a$  und  $c < b$  eingehalten werden können. In dem Fall von [Fig. 20](#) ist die Beziehung zwischen der Dicke  $a$  und dem Abstand  $b$  wie bei dem Aufbau der bekannten Technik  $a < b$ .

**[0107]** Weiter weist die Drainelektrode **119** einen Abschnitt DC auf, der sich auf der dritten Isolierschicht LC erstreckt, und dieser Abschnitt DC wirkt als normale Feldplatte (nicht im schwebenden Zustand). Im folgenden wird dieser Abschnitt als "dritter Drainelektrodenabschnitt DC" beendet. Weiter weist die Sourceelektrode **114** einen Abschnitt SC auf, der sich auf der dritten Isolierschicht LC erstreckt, und dieser Abschnitt SC wirkt als normale Feldplatte. Im folgenden wird dieser Abschnitt als "dritter Sourceelektrodenabschnitt SC" bezeichnet.

**[0108]** [Fig. 21](#) ist ein Diagramm, das eine elektrische Feldverteilung in dem HV-MOS von [Fig. 20](#) zu einer Zeit zeigt, zu der eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand angelegt ist, der durch Erzeugen eines Kurzschlusses zwischen der Gateelektrode **116** und der Sourceelektrode **114** in dem HV-MOS bewirkt wird. Diese Figur zeigt die elektrische Feldverteilung in einem Bereich von der Siliziumsubstratoberfläche (Si-Oberfläche) bis zu der Tiefe des pn-Übergangs zwischen dem n-Bereich **117** und dem p-Bereich **200**. Insbesondere zeigen die durchgezogenen Linien die elektrische Feldverteilung in der Siliziumsubstratoberfläche und die elektrische Feldverteilung in der Tiefe des ersten pn-Übergangs zwischen der n-Schicht **110** und dem p-Bereich **200**. Wie aus einem Vergleich zwischen [Fig. 21](#) und [Fig. 8](#), die die elektrische Feldverteilung in dem bekannten HV-MOS zeigt, ersichtlich wird in [Fig. 21](#) bei der vierten Ausführungsform die elektrische Feldspitze in der Siliziumsubstratoberfläche kleiner, und die elektrische Feldkonzentration wird verringert. Da daher der Spielraum im Hinblick auf die elektrische Feldstärke an dem Punkt des durchbruchkritischen elektrischen Feldes ansteigt und es unwahrscheinlich ist, dass die elektrische Feldspitze in der Siliziumsubstratoberfläche die elektrische Feldstärke des Punktes des durchbruchkritischen elektrischen Feldes überschreitet, können Probleme wie eine Verringerung der Spannungsfestigkeit und eine Instabilität der Spannungsfestigkeitseigenschaft unterdrückt werden. Demzufolge kann der HV-MOS eine hohe Spannungsfestigkeit stabil halten.

**[0109]** [Fig. 22](#) ist ein Diagramm, das eine Potentialverteilung und eine Stromverteilung in dem HV-MOS von [Fig. 20](#) zu einer Zeit zeigt, zu der eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand des HV-MOS angelegt ist. Auch in [Fig. 22](#) ist die Potentialverteilung durch Äquipotentiallinien gezeigt, und die Bezugszeichen 0 bis 6 stellen Intervalle der Äquipotentiallinien in der Siliziumsubstratoberfläche dar (in der Grenzfläche zwischen der n-Schicht **110** und der ersten Isolierschicht LA). Verglichen mit [Fig. 11](#), die den Fall der bekannten Technik zeigt, ist festzustellen, dass die Äquipotentiallinien der Siliziumsubstratoberfläche zu der Drainseite hin verschoben sind und die Verar-

mungsschicht in der Siliziumsubstratoberfläche leichter auszudehnen ist. Das bedeutet, dass die elektrische Feldspitze in der Siliziumsubstratoberfläche kleiner wird. Somit kann auch aus der Potentialverteilung von [Fig. 22](#) die obige Wirkung beobachtet werden.

**[0110]** Da bei dem HV-MOS der vierten Ausführungsform der Abstand c kleiner gemacht ist, steigen die Kapazitätswerte der Kondensatoren, die zwischen den zweiten schwebenden Feldplatten FB, den dritten schwebenden Feldplatten FC, dem dritten Drainelektrodenabschnitt DC und dem dritten Sourceelektrodenabschnitt SC gebildet sind. Da daher die Wirkung der kapazitiven Kopplung in den Kondensatoren ansteigt, wird die Polarisierung der dritten Isolierschicht LC beschleunigt. Das bewirkt einen Effekt, dass die Ausdehnung der Verarmungsschicht auch unter den Lücken zwischen den ersten schwebenden Feldplatten FA erleichtert wird, wo sich die Verarmungsschicht herkömmlicherweise schwer ausdehnt, was zu einem Ansteigen der Spannungsfestigkeit des HV-MOS führt.

**[0111]** Auch wenn die Beziehung zwischen der Dicke a und dem Abstand b in [Fig. 20](#) durch  $a < b$  gegeben ist, kann die Beziehung zwischen a und b auch  $a > b$  sein wie in [Fig. 23](#), bei der die erste Ausführungsform auf die vierte Ausführungsform angewendet ist. In diesem Fall kann die vierte Ausführungsform auch die Wirkung der ersten Ausführungsform hervorbringen und ein weiteres Ansteigen der Spannungsfestigkeit erzielen.

**[0112]** [Fig. 24](#) ist ein Diagramm, das eine elektrische Feldverteilung in dem HV-MOS von [Fig. 23](#) zu einer Zeit zeigt, zu der eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand angelegt ist, der durch Erzeugen eines Kurzschlusses zwischen der Gateelektrode **116** und der Sourceelektrode **114** in dem HV-MOS bewirkt wird. Diese Figur zeigt die elektrische Feldverteilung in einem Bereich von der Siliziumsubstratoberfläche (Si-Oberfläche) bis zu der Tiefe des pn-Übergangs zwischen dem n-Bereich **117** und dem p-Bereich **200**. Insbesondere zeigen die durchgezogenen Linien die elektrische Feldverteilung in der Siliziumsubstratoberfläche und die elektrische Feldverteilung in der Tiefe des ersten pn-Übergangs zwischen der n-Schicht **110** und dem p-Bereich **200**. Es ist festzustellen, dass verglichen mit [Fig. 21](#) die elektrische Feldspitze in der Siliziumsubstratoberfläche noch kleiner wird und die elektrische Feldkonzentration weiter verringert wird.

**[0113]** [Fig. 25](#) ist ein Diagramm, das eine Potentialverteilung und eine Stromverteilung in dem HV-MOS von [Fig. 23](#) zu einer Zeit zeigt, zu der eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand des HV-MOS

angelegt ist. Auch in [Fig. 25](#) ist die Potentialverteilung durch Äquipotentiallinien gezeigt, und die Bezugszeichen 0 bis 6 stellen Intervalle der Äquipotentiallinien in der Siliziumsubstratoberfläche dar. Da bei dem HV-MOS von [Fig. 23](#) die Dicke a der ersten Isolierschicht LA groß ist und die Verzerrung der Äquipotentiallinien in der ersten Isolierschicht LA unterdrückt ist, werden die Größen der Intervalle 0 bis 6 gleichförmiger als die in [Fig. 22](#). Daher ist festzustellen, dass die Größe der elektrischen Feldspitze in der Siliziumsubstratoberfläche zu einem geringeren Wert hin verringert wird.

**[0114]** Somit kann durch Anwenden der ersten Ausführungsform auf die vierte Ausführungsform eine weitere Erhöhung der Spannungsfestigkeit erzielt werden.

**[0115]** Auch wenn oben der Fall erörtert wurde, bei dem die vorliegende Erfindung auf einen MOSFET angewendet wird, ist die Anwendung der vorliegenden Erfindung nicht darauf beschränkt, sondern die vorliegende Erfindung kann weit angewendet werden, z. B. auf eine Diode, einen IGBT oder dergleichen.

**[0116]** [Fig. 26](#) ist eine Ansicht eines Aufbaus eines HV-MOS entsprechend einer fünften Ausführungsform. Da in [Fig. 26](#) Bestandteile, die mit denen in [Fig. 6](#) und [Fig. 14](#) identisch sind, durch dieselben Bezugszeichen dargestellt sind, unterbleibt ihre detaillierte Beschreibung.

**[0117]** In der fünften Ausführungsform ist die Breite jeder der ersten schwebenden Feldplatten FA und der zweiten schwebenden Feldplatten FB größer als bei dem Aufbau der bekannten Technik. Insbesondere sind die Breiten so festgelegt, dass unter der Annahme, dass g die Breite eines Abschnittes jeder der ersten schwebenden Feldplatten FA ist, der eine der zweiten schwebenden Feldplatten FB in der ersten Richtung überlappt, wobei die zweite Isolierschicht LB dazwischen ist, und dass h der Abstand zwischen einer der zweiten schwebenden Feldplatten FB und der benachbarten in der ersten Richtung ist, kann eine Beziehung  $g > h$  eingehalten werden (s. [Fig. 26](#)).

**[0118]** Weiter ist in dem Fall von [Fig. 26](#) die Beziehung zwischen der Dicke a (der Dicke der ersten Isolierschicht LA) und dem Abstand b (dem Abstand zwischen den ersten schwebenden Feldplatten FA und den zweiten schwebenden Feldplatten FE in der zweiten Richtung) wie bei dem Aufbau der bekannten Technik  $a < b$ .

**[0119]** Ansonsten unterscheidet sich [Fig. 26](#) der fünften Ausführungsform nicht von [Fig. 14](#) der zweiten Ausführungsform.

**[0120]** Da in der fünften Ausführungsform die Breite eines Abschnitts, in dem eine der ersten schwebenden Feldplatten FA die entsprechende der zweiten schwebenden Feldplatten FE überlappt, groß ist, werden die Kapazitätswerte der zwischen den ersten schwebenden Feldplatten FA und den zweiten schwebenden Feldplatten FB gebildeten Kondensatoren größer als in dem Aufbau der bekannten Technik. Da daher der hohe kapazitive Koppeleffekt in den Kondensatoren größer wird, wird die Polarisierung der zweiten Isolierschicht LB beschleunigt. Das bringt eine Wirkung hervor, die Ausdehnung der Verarmungsschicht auch unter den Lücken zwischen den ersten schwebenden Feldplatten FA zu erleichtern, was zu einem Ansteigen der Spannungsfestigkeit des HV-MOS führt.

**[0121]** Da der kapazitive Koppeleffekt in den Kondensatoren ansteigt, wird eine Schwankung von Potentialdifferenzen, die in den Kondensatoren zwischen der Source und dem Drain gehalten werden, kleiner, und die fünfte Ausführungsform kann auch eine Wirkung hervorbringen des Verhinderns des dielektrischen Durchbruchs der zweiten Isolierschicht LB.

**[0122]** Auch wenn die fünfte Ausführungsform ebenfalls den Fall darstellt, bei dem die vorliegende Erfindung auf einen MOSFET angewendet wird, ist die Anwendung der vorliegenden Erfindung nicht darauf beschränkt, sondern die vorliegende Erfindung kann weit angewendet werden, z. B. auf eine Diode, einen IGBT oder dergleichen.

**[0123]** [Fig. 27](#) ist eine Ansicht eines Aufbaus eines HV-MOS entsprechend einer sechsten Ausführungsform. Da in [Fig. 27](#) Bestandteile, die mit denen in [Fig. 20](#) identisch sind, durch dieselben Bezugszeichen bezeichnet sind, unterbleibt ihr detaillierte Beschreibung.

**[0124]** Der HV-MOS von [Fig. 27](#) hat einen Aufbau, bei dem die ersten schwebenden Feldplatten FR aus dem Aufbau von [Fig. 20](#) entfernt sind. Angenommen, dass jeweils a und b jeweils die Dicke der ersten Isolierschicht LA bzw. die der zweiten Isolierschicht LB sind und dass c der Abstand zwischen der zweiten schwebenden Feldplatten FB und den dritten schwebenden Feldplatten FC in der zweiten Richtung ist, wird eine Beziehung  $a + b > c$  eingehalten. Anders ausgedrückt haben die zweiten schwebenden Feldplatten FB und die dritten schwebenden Feldplatten FC von [Fig. 27](#) dieselbe Funktion wie die ersten schwebenden Feldplatten FR und die zweiten schwebenden Feldplatten FB der ersten Ausführungsform ([Fig. 6](#)). Daher kann der HV-MOS von [Fig. 27](#) wie der HV-MOS der ersten Ausführungsform eine hohe Spannungsfestigkeit stabil halten.

**[0125]** Der erste Drainelektrodenabschnitt DA der Drainelektrode **119** erstreckt sich auf der ersten Isolierschicht LA. Der erste Drainelektrodenabschnitt DA erstreckt auf der ersten Isolierschicht LA so in die erste Richtung, dass er einen Abschnitt der zweiten schwebenden Feldplatte FB1 teilweise überlappt, wobei die zweite Isolierschicht LB dazwischen liegt. Die Länge eines Abschnitts in dem dritten Drainelektrodenabschnitt DC, der sich oberhalb der ersten Isolierschicht LA in der ersten Richtung erstreckt, ist größer als die Länge eines Abschnittes des ersten Drainelektrodenabschnitts DA, der sich auf der ersten Isolierschicht LA in der ersten Richtung erstreckt, und länger als die Länge eines Abschnittes in dem zweiten Drainelektrodenabschnitt DB, der sich oberhalb der ersten Isolierschicht LA in der ersten Richtung erstreckt. Anders ausgedrückt bedeckt der dritte Drainelektrodenabschnitt DC den ersten Drainelektrodenabschnitt DA und den zweiten Drainelektrodenabschnitt DB.

**[0126]** [Fig. 28](#) ist ein Diagramm, das eine elektrische Feldverteilung in dem HV-MOS von [Fig. 27](#) zu einer Zeit zeigt, zu der eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand angelegt ist, der durch Erzeugen eines Kurzschlusses zwischen der Gateelektrode **116** und der Sourceelektrode **114** in dem HV-MOS bewirkt wird. Diese Figur zeigt die elektrische Feldverteilung in einem Bereich von der Siliziumsubstratoberfläche (Si-Oberfläche) bis zu der Tiefe des pn-Übergangs zwischen dem n-Bereich **117** und dem p-Bereich **200**. Insbesondere zeigen die durchgezogenen Linien die elektrische Feldverteilung in der Siliziumsubstratoberfläche und die elektrische Feldverteilung in der Tiefe des ersten pn-Übergangs zwischen der n-Schicht **110** und dem p-Bereich **200**. Es ist festzustellen, dass wie in der ersten Ausführungsform die elektrische Feldspitze in der Siliziumsubstratoberfläche niedriger wird und die elektrische Feldkonzentration verringert wird.

**[0127]** Die elektrische Feldspitze in der Siliziumsubstratoberfläche auf der Drainseite liegt unterhalb einer Kante der zweiten schwebenden Feldplatte FB2 auf der Drainseite, und keine Spitze liegt unter einer Kante der zweiten schwebenden Feldplatte FB1. Das liegt daran, dass der erste Drainelektrodenabschnitt DA, der als normale Feldplatte wirkt, sich bis zu so einer Stelle erstreckt, bei der der erste Drainelektrodenabschnitt DA die zweite schwebende Feldplatte FB1 teilweise überlappt. Da sich der dritte Drainelektrodenabschnitt DC weiter so oberhalb der ersten Isolierschicht LA erstreckt, dass er den ersten Drainelektrodenabschnitt DA und den zweiten Drainelektrodenabschnitt DB überdeckt, wird die elektrische Feldkonzentration nah der Drainelektrode in der Siliziumsubstratoberfläche weiter verringert. Da daher die elektrische Feldstärke nahe dem Punkt des durchbruchkritischen elektrischen Feldes (einem Abschnitt

in der Tiefe des ersten pn-Übergangs in dem n-Bereich **117** auf der Drainseite) kleiner wird, wird ein Wert der Spannungsfestigkeit in dem HV-MOS höher. Kurz gesagt kann in der sechsten Ausführungsform verglichen mit der ersten Ausführungsform eine weitere Erhöhung der Spannungsfestigkeit erzielt werden.

**[0128]** [Fig. 29](#) ist eine Ansicht einer Abwandlung, bei der die zweite Ausführungsform auf die sechste Ausführungsform angewendet ist. Insbesondere unterscheidet sich der Aufbau von [Fig. 29](#) von dem nach [Fig. 27](#) darin, dass der zweite Drainelektrodenabschnitt DB der Drainelektrode **119** sich auf der zweiten Isolierschicht LB erstreckt. Wie in [Fig. 29](#) dargestellt ist die Länge eines Abschnittes des zweiten Drainelektrodenabschnitts DB, der sich oberhalb der ersten Isolierschicht LA in der ersten Richtung erstreckt, größer als die Länge eines Abschnitts in dem ersten Drainelektrodenabschnitt DA, der sich auf der ersten Isolierschicht LA in der ersten Richtung erstreckt. Anders ausgedrückt überdeckt der zweite Drainelektrodenabschnitt DB den ersten Drainelektrodenabschnitt DA, wobei die zweite Isolierschicht LB dazwischen liegt. Wie in [Fig. 29](#) dargestellt ist der zweite Drainelektrodenabschnitt DB ein Abschnitt, bei dem die Drainelektrode **119** und die zweite schwebende Feldplatte FB1 von [Fig. 27](#) miteinander verbunden sind.

**[0129]** [Fig. 30](#) ist ein Diagramm, das eine elektrische Feldverteilung in dem HV-MOS von [Fig. 29](#) zu einer Zeit zeigt, zu der eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand angelegt ist, der durch Erzeugen eines Kurzschlusses zwischen der Gateelektrode **116** und der Sourceelektrode **114** in dem HV-MOS bewirkt wird. Auch in [Fig. 30](#) liegt wie in [Fig. 28](#) die elektrische Feldspitze in der Siliziumsubstratoberfläche auf der Drainseite unter einer Kante der zweiten schwebenden Feldplatte FB2 auf der Drainseite, und keine Spitze liegt unter einer Kante der zweiten schwebenden Feldplatte FB1. Da daher die elektrische Feldstärke nahe dem Punkt des durchbruchkritischen elektrischen Feldes kleiner wird, wird ein Wert der Spannungsfestigkeit in dem HV-MOS größer. Kurz gesagt, kann in dieser Abwandlung verglichen mit der zweiten Ausführungsform eine weitere Erhöhung der Spannungsfestigkeit erzielt werden.

**[0130]** Auch wenn die sechste Ausführungsform ebenfalls den Fall darstellt, bei dem die vorliegende Erfindung auf einen MOSFET angewendet wird, ist die Anwendung der vorliegenden Erfindung nicht darauf beschränkt, sondern die vorliegende Erfindung kann weit angewendet werden, z. B. auf eine Diode, einen IGBT oder dergleichen.

**[0131]** [Fig. 31](#) ist eine Ansicht eines Aufbaus eines HV-MOS entsprechend einer siebten Ausführungs-

form. Da in [Fig. 27](#) Bestandteile, die mit denen in [Fig. 6](#) und [Fig. 14](#) identisch sind, durch dieselben Bezugszeichen bezeichnet sind, unterbleibt ihre detaillierte Beschreibung.

**[0132]** In dem HV-MOS der siebten Ausführungsform erstreckt sich der erste Drainelektrodenabschnitt DA der Drainelektrode **119** auf der ersten Isolierschicht LA und der zweite Drainelektrodenabschnitt DB erstreckt sich auf der zweiten Isolierschicht LB. Weiter sind der erste Drainelektrodenabschnitt DA und der zweite Drainelektrodenabschnitt DB länger ausgebildet als in dem Aufbau der bekannten Technik. Wie in [Fig. 31](#) dargestellt ist unter der Annahme, dass d die Länge eines Abschnitts des ersten Drainelektrodenabschnitts DA ist, der sich auf der ersten Isolierschicht LA in der ersten Richtung erstreckt, ist die Länge eines Abschnitts in dem zweiten Drainelektrodenabschnitt DB, der sich oberhalb der ersten Isolierschicht LA in der ersten Richtung erstreckt, um eine Länge e größer als die Länge d. Dabei ist die Länge d hinreichend groß ausgeführt, so dass die Beziehung  $d > e$  eingehalten werden kann. Weiter ist in dem Fall von [Fig. 31](#) die Beziehung zwischen der Dicke a der ersten Isolierschicht LA und dem Abstand b zwischen den ersten schwebenden Feldplatten FA und den zweiten schwebenden Feldplatten FB in der zweiten Richtung wie bei dem Aufbau der bekannten Technik  $a < b$ . Wie in [Fig. 31](#) dargestellt ist der erste Drainelektrodenabschnitt DA ein Abschnitt, bei dem die Drainelektrode **119** mit der ersten schwebenden Feldplatte FA1 von [Fig. 6](#) verbunden ist, und der zweite Drainelektrodenabschnitt DB ist ein Abschnitt, bei dem die zweiten schwebenden Feldplatten FB1 und FB2 mit der Drainelektrode **119** von [Fig. 6](#) verbunden sind.

**[0133]** [Fig. 32](#) ist ein Diagramm, das eine elektrische Feldverteilung in dem HV-MOS von [Fig. 31](#) zu einer Zeit zeigt, zu der eine hohe Spannung zwischen der Drainelektrode **119** und der Sourceelektrode **114** in einem AUS-Zustand angelegt ist, der durch Erzeugen eines Kurzschlusses zwischen der Gateelektrode **116** und der Sourceelektrode **114** in dem HV-MOS bewirkt wird. Diese Figur zeigt die elektrische Feldverteilung in einem Bereich von der Siliziumsubstratoberfläche (Si-Oberfläche) bis zu der Tiefe des pn-Übergangs zwischen dem n-Bereich **117** und dem p<sup>-</sup>-Bereich **200**. Insbesondere zeigen die durchgezogenen Linien die elektrische Feldverteilung in der Siliziumsubstratoberfläche und die elektrische Feldverteilung in der Tiefe des ersten pn-Übergangs zwischen der n<sup>-</sup>-Schicht **110** und dem p<sup>-</sup>-Bereich **200**. Die elektrische Feldspitze in der Siliziumsubstratoberfläche auf der Drainseite liegt unterhalb einer Kante der ersten schwebenden Feldplatte FA2 auf der Drainseite.

**[0134]** Wie beispielsweise aus einem Vergleich zwischen [Fig. 32](#) und [Fig. 7](#) oder dergleichen ersichtlich liegt in der siebten Ausführungsform die elektri-

sche Feldspitze auf der Drainseite weiter weg von dem Punkt des durchbruchkritischen elektrischen Feldes (einem Abschnitt in der Tiefe des ersten pn-Übergangs des n-Bereichs **117** auf der Drainseite). Da die elektrische Feldstärke nahe dem Punkt des durchbruchkritischen elektrischen Feldes kleiner wird, steigt daher die Spannungsfestigkeit in dem HV-MOS an.