(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5039495号

(P5039495)

(45) 発行日 平成24年10月3日(2012.10.3)

(24) 登録日 平成24年7月13日(2012.7.13)

(51) Int.Cl.

F 1

G01N 21/956 (2006.01)

G01N 21/956

A

H01L 21/027 (2006.01)

H01L 21/30

531M

G03F 1/24 (2012.01)

G03F 1/24

請求項の数 4 (全 17 頁)

(21) 出願番号

特願2007-260796 (P2007-260796)

(22) 出願日

平成19年10月4日 (2007.10.4)

(65) 公開番号

特開2009-92407 (P2009-92407A)

(43) 公開日

平成21年4月30日 (2009.4.30)

審査請求日

平成22年8月30日 (2010.8.30)

(出願人による申告) 平成18年度独立行政法人新エネルギー・産業技術総合開発機構「次世代半導体材料・プロセス基板(MRA1)」委託研究、産業技術力強化法第19条の適用を受ける特許出願

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100101454

弁理士 山田 卓二

(74) 代理人 100081422

弁理士 田中 光雄

(74) 代理人 100100479

弁理士 竹内 三喜夫

(72) 発明者 寺澤 恒男

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 田中 稔彦

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】マスクプランク検査方法、反射型露光マスクの製造方法、反射型露光方法および半導体集積回路の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

検査対象となる反射型マスクプランクに向けて検査光を照射し、被検査領域を照明するステップと、

被検査領域から反射した光のうち鏡面反射光を除く散乱光を捕集し、捕集した光を第1光束および第2光束に分岐した後、第1光束の結像面から光進行方向に沿って所定距離だけ変位した位置に配置された第1画像センサ、および第2光束の結像面から光進行方向とは反対方向に所定距離だけ変位した位置に配置された第2画像センサをそれぞれ用いて、第1光束および第2光束が形成する各検査画像の強度分布を計測するステップと、

第1画像センサおよび第2画像センサからの各信号に基づいて、マスクプランクの欠陥の有無を判定するステップとを含み、

欠陥の有無を判定するステップは、

第1画像センサの信号と所定の第1閾値とを比較するステップと、

第2画像センサの信号と所定の第2閾値とを比較するステップと、

第1画像センサの信号と第2画像センサの信号とを比較するステップとを含み、

比較結果に基づいて、表面形状の凸型欠陥と凹型欠陥を識別することを特徴とするマスクプランク検査方法。

## 【請求項2】

反射型マスクプランクの上に吸収体パターンを形成するための反射型露光マスクの製造方法であって、

10

20

請求項<sub>1</sub>に記載されたマスクプランク検査方法を用いて、マスクプランクの欠陥を検査するステップと、

欠陥の位置情報を記憶するステップと、

記憶した欠陥位置情報に基づいて、吸収体パターンの形成位置を規定するための吸収体パターンマスクとマスクプランクとの相対位置を決定するステップと、

決定した相対位置に基づいて、マスクプランクの上に吸収体パターンを形成するステップとを含むことを特徴とする反射型露光マスクの製造方法。

#### 【請求項3】

請求項<sub>2</sub>記載の反射型露光マスクの製造方法を用いて得られたマスクを反射型露光装置に載置して、吸収体パターンを半導体基板に縮小投影することを特徴とする反射型露光方法。10

#### 【請求項4】

請求項<sub>3</sub>記載の反射型露光方法を用いて、半導体基板に集積回路パターンを形成することを特徴とする半導体集積回路の製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、例えば、波長が13.5nm付近の極端紫外線を用いたEUVL(Extreme Ultra Violet Lithography: 極端紫外線リソグラフィ)などに好適であるマスクプランク検査方法に関する。また本発明は、反射型露光マスクの製造方法、反射型露光方法、および半導体集積回路の製造方法に関する。20

#### 【背景技術】

#### 【0002】

半導体集積回路などの半導体デバイスは、回路パターンが描かれた原版であるマスクに露光光を照射し、前記パターンを、縮小光学系を介して半導体基板(以下、「ウエハ」と称する)上に転写する光リソグラフィ工程を繰り返し用いることによって、大量生産されている。

#### 【0003】

近年、半導体デバイスの微細化が進み、光リソグラフィの露光波長をより短くして解像度を上げる方法が検討されている。これまで波長193nmのフッ化アルゴン(ArF)エキシマレーザ光を用いたArFリソグラフィが開発されてきたが、それよりもはるかに波長の短い波長13.5nmのEUVLの開発が進んでいる。30

#### 【0004】

このEUV波長域では、物質の光吸収の関係で透過マスクが使えないため、Mo(モリブデン)とSi(シリコン)などの多層膜による反射(プラグ反射)を利用した多層膜反射基板がEUVL用のマスクプランクとして使用される。多層膜反射は一種の干渉を利用した反射である。EUVL用のマスクは、石英ガラスや低熱膨張ガラス基板の上にMoとSiなどの多層膜が被着された多層膜プランク上に吸収体パターンが形成されている。

#### 【0005】

EUVLでは、プラグ反射を利用した反射マスクであることと、露光波長が13.5nmと極めて短いことにより、露光波長の数分の1程度のごく僅かな高さの異常が発生した場合でも、その高さ異常に起因して反射率の局所的な差が生じ、転写の際、欠陥を生じさせる。従って、EUVL用マスクは、従来の透過マスクと比較して欠陥転写に関して質的に大きな差がある。40

#### 【0006】

吸収体パターンを形成する前段階でのマスクプランク欠陥検査に関しては、レーザ光をマスクプランクに対し斜めから照射し、その乱反射光から異物を検出するものと、マスクパターン露光に用いる波長と同じ波長のEUV光を用いて欠陥検出する同波長(at wavelength)欠陥検査法がある。後者の方法としては、暗視野像を用いる方法(例えば、下記特許文献1参照)と、明視野を用いるX線顕微鏡法と(例えば、下記特許文献2参照)と、50

暗視野を用いて欠陥検出し、フレネルゾーンプレートを用いた明視野系で欠陥同定を行う暗視野明視野併用法（例えば、下記特許文献3参照）などがある。

#### 【0007】

なお、従来の透過マスクプランクの検査としては、レーザ光をマスクプランクに対し斜めから照射して乱反射光から異物を検出するものと、明視野像（顕微鏡像）を検出するものがある。後者の変形としては、検出像信号の非対称性から凸欠陥か凹欠陥か判別するもの（例えば、下記特許文献4，5参照）などがある。

#### 【0008】

さらに、剥離可能なパターンを多層膜マスク上に形成して実際にパターン転写を行ない、パターンを検査することにより多層膜欠陥を検査する方法（例えば、下記特許文献6参照）が開示されている。

10

#### 【0009】

【特許文献1】特開2003-114200号公報

【特許文献2】特開平6-349715号公報

【特許文献3】米国特許出願公開第2004/0057107号明細書

【特許文献4】特開2001-174415号公報

【特許文献5】特開2002-333313号公報

【特許文献6】特開平11-354404号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

20

#### 【0010】

しかしながら、特許文献1のように、EUV光を用いた暗視野検出法では、検出感度が高く、多層膜の異常による位相欠陥の検出性能に優れるものの、欠陥の凹凸の区別を行なうことはできない。

#### 【0011】

また、特許文献2のように、明視野を用いたX線顕微鏡法では、多層膜の反射率のみを調べているため、位相の変化を起こさせる欠陥をすべて検出することはできない。

#### 【0012】

また、特許文献3のように、露光波長検査であって、明視野検査と暗視野検査とを兼ね備える方法は、検査装置が複雑になると同時に、高速な暗視野検査であっても検出感度が高くない。

30

#### 【0013】

また、特許文献4，5のように、レーザを用いた方式は、検出すべき欠陥のサイズが検査波長と比べて十分小さく感度が不足する。さらに、多層膜の表面のみの凹凸欠陥を検出するものであり、多層膜の内部にまで存在してEUV光反射の異常を発生する欠陥を捕らえることができない。

#### 【0014】

また、特許文献6のように、剥離可能なパターンを多層膜マスク上に形成して実際にパターン転写を行ない、パターンを検査することにより多層膜欠陥を検査する方法では、位相欠陥を検出できるものの、実際にパターン転写を行なう工程が必要であり、検査としては煩雑である。

40

#### 【0015】

また、上述したいづれの検査方法でも、修正が困難な欠陥が検出された場合は、たとえ微小サイズの欠陥であってもそのマスクプランクは不良品として取り扱われ、処分されることになる。

#### 【0016】

本発明の目的は、反射型マスクプランクの欠陥の存在および種類を正確かつ簡便に検査することができるマスクプランク検査方法を提供することである。

#### 【0017】

50

また本発明の目的は、上記検査方法によって欠陥の存在が判明した場合でも、信頼性の高い反射型マスクを高い歩留まりで製造できる反射型露光マスクの製造方法を提供することである。

【0018】

また本発明の目的は、上記製造方法によって得られた反射型露光マスクを用いた反射型露光方法を提供することである。

【0019】

また本発明の目的は、上記反射型露光方法を用いた半導体集積回路の製造方法を提供することである。

【課題を解決するための手段】

10

【0020】

本発明の一実施例によれば、検査対象となる反射型マスクブランクに向けて検査光を照射し、被検査領域を照明する。そして、暗視野結像光学系を用いて、被検査領域から反射した光のうち鏡面反射光を除く散乱光を捕集する。捕集した光は、光分岐素子によって第1光束および第2光束に分岐される。

【0021】

第1画像センサは、第1光束の結像面から光進行方向に沿って所定距離だけ変位した位置に配置される。第2画像センサは、第2光束の結像面から光進行方向とは反対方向に所定距離だけ変位した位置に配置される。これらの第1画像センサおよび第2画像センサは、第1光束および第2光束が形成する各検査画像の強度分布を計測する。第1画像センサおよび第2画像センサからの各信号は、画像処理部に供給され、マスクブランクの欠陥の有無を判定する。

20

【0022】

光分岐素子は、多層膜、透過型回折格子、または反射型回折格子で構成することが好ましい。

【0023】

また、第1画像センサおよび第2画像センサは、ステージの連続移動と同期して時間遅延積分 (T D I : Time Delayed Integration) 動作が可能なイメージセンサであることが好ましい。

【0024】

30

また、検査光は、マスクパターン露光に用いる波長と同じ波長であることが好ましく、例えば、波長 10 nm ~ 15 nm の極端紫外線であることが好ましい。

【0025】

また、欠陥の有無を判定する際、第1画像センサおよび第2画像センサの各信号および予め設定した第1閾値および第2閾値を相互に比較することによって、表面形状の凸型欠陥と凹型欠陥を識別することが好ましい。

【0026】

さらに、反射型マスクブランクの上に吸収体パターンを形成して、反射型露光マスクを製造する場合、上述のようにマスクブランクの欠陥を検査して、欠陥の位置情報を事前に記憶しておく。続いて、記憶した欠陥位置情報に基づいて、吸収体パターンの形成位置を規定するための吸収体パターンマスクとマスクブランクとの相対位置を決定する。このとき、例えば、吸収体パターンが欠陥を覆い隠すように、吸収体パターンマスクの位置決めが可能である。そして、決定した相対位置に基づいて、マスクブランクの上に吸収体パターンを形成する。

40

【0027】

このようにして得られたマスクを反射型露光装置に載置して、吸収体パターンを半導体基板に縮小投影することができる。さらに、こうした反射型露光方法を用いて半導体基板に集積回路パターンを形成し、半導体集積回路を製造することが可能である。

【発明の効果】

【0028】

50

この実施例によれば、反射型マスクプランクの欠陥の存在および種類を正確かつ簡便に検査できることから、欠陥生成要因の分析が可能になる。さらに、得られた欠陥位置情報を用いて、欠陥の影響を回避するように、反射型マスクプランクの上に吸収体パターンを形成することが可能になるため、反射型露光マスクの歩留まりが向上する。

**【発明を実施するための最良の形態】**

**【0029】**

実施の形態1.

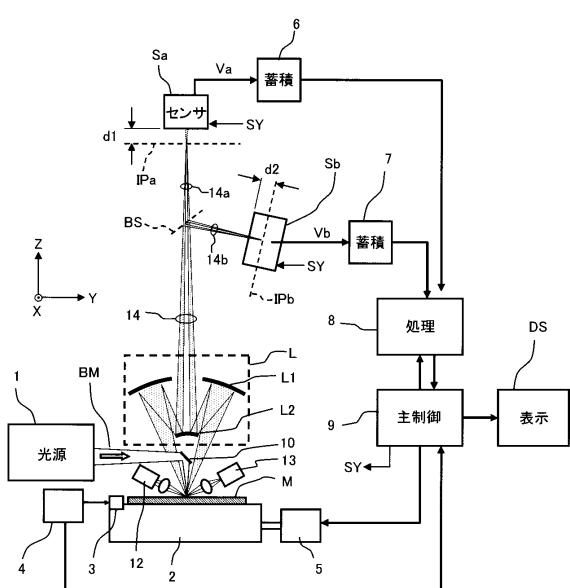

図1は、本発明に係るマスクプランク検査装置の一例を示す構成図である。マスクプランク検査装置は、反射型マスクプランクMを載置するためのステージ2と、検査光BMを発生する光源1と、照明光学系としてのミラー10と、結像光学系Lと、ビームスプリッタBSと、2個の2次元アレイセンサSa, Sbと、信号蓄積部6, 7と、画像処理部8と、装置全体の動作を制御する主制御部9などで構成される。ここで、理解容易のため、ステージ面をXY面とし、ステージ面の法線方向をZ軸とする。

10

**【0030】**

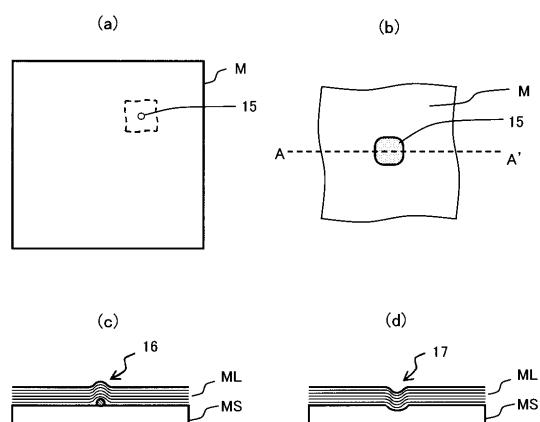

マスクプランクMは、図2に示すように、石英ガラス等の低熱膨張材で形成されたマスク基板MS上に、波長(例えば、13.5nm)の露光光に対して反射率が十分に得られるように、Si(シリコン)とMo(モリブデン)を交互に積層した多層膜MLを形成したものである。この多層膜MLの上に、所望のパターン形状を有する吸収体パターンを形成することによって、反射型露光マスクが得られる。

**【0031】**

20

図1に戻って、光源1は、露光光と同じ波長の光を含む検査光BMを発生するEUV光源で構成される。ミラー10は、凹面ミラーまたは平面ミラーで構成され、光源1からの検査光BMをスポット状にして、マスクプランクMの被検査領域を照明する。検査光BMの入射方向は、マスクプランクMの法線方向とほぼ一致するように設定される。

**【0032】**

結像光学系Lは、凹面ミラーL1と凸面ミラーL2を備え、凹面ミラーL1の中心に出射開口が設けられたシュバルツシルド(Schwarzschild)光学系として構成される。被検査領域で反射した光のうち、正反射方向およびその近傍に進行する鏡面反射光は、凸面ミラーL2によって遮断されて、暗視野光学系を構成している。一方、凹面ミラーL1に入射した散乱光は、凹面ミラーL1と凸面ミラーL2の組合せ倍率に従って拡大投影され、凹面ミラーL1の出射開口を通じてZ方向に出射される。結像光学系Lは、例えば、凹面ミラーL1による集光開口数が0.2、凸面ミラーL2による中心遮光開口数が0.1、組合せ倍率が26倍となるように設計される。

30

**【0033】**

こうした暗視野光学系を採用することにより、マスクプランクM上に欠陥が存在しない場合は、散乱光が発生せず、鏡面反射光のみとなるので、結像光学系Lには捕捉されず、2次元アレイセンサSa, Sbには入射しない。一方、マスクプランクM上に欠陥が存在する場合は、散乱光が発生して、結像光学系Lに捕捉され、2次元アレイセンサSa, Sbに入射する。そのため、高いS/N比の検査を実現できる。

**【0034】**

40

ビームスプリッタBSは、結像光学系Lの出射側に配置され、出射光束14を2つの光束14a, 14bに分岐して、光束14aの結像面IPAおよび光束14bの結像面IPbをそれぞれ形成している。本実施形態では、ビームスプリッタBSは、数対のSiとMoからなる多層膜で構成しており、EUV光に対して約30%の透過率及び約30%の反射率を有するように設計している。

**【0035】**

2次元アレイセンサSaは、正のデフォーカス像を検知するように、光束14aの結像面IPAから光進行方向に沿って所定距離d1だけ変位した位置に配置される。一方、2次元アレイセンサSbは、負のデフォーカス像を検知するように、光束14bの結像面IPbから光進行方向とは反対方向に所定距離d2だけ変位した位置に配置される。

50

## 【0036】

2次元アレイセンサS<sub>a</sub>, S<sub>b</sub>は、複数の検出画素を有する、例えば、CCD(電荷結合素子)として構成され、各受光面における光強度分布を電気信号V<sub>a</sub>, V<sub>b</sub>にそれぞれ変換する。代替として、2次元アレイセンサS<sub>a</sub>, S<sub>b</sub>は、主制御部9からの同期信号S<sub>Y</sub>に従って、ステージ2の連続移動と同期して時間遅延積分(TDI:Time Delayed Integration)動作が可能なイメージセンサで構成してもよく、信号積分によりノイズの低減および感度の向上を図ることができる。

## 【0037】

信号蓄積部6, 7は、2次元アレイセンサS<sub>a</sub>, S<sub>b</sub>からの電気信号V<sub>a</sub>, V<sub>b</sub>を一時的に保存して、ノイズ除去処理を施したり、検出信号の位置を定義する画素番号の初期化処理を行う。画像処理部8は、信号蓄積部6, 7で処理された信号を診断して、マスクブランクMでの欠陥の存在およびその種類を判定する。画像処理部8の判定結果は、主制御部9を経由してディスプレイ等の表示部DSに送られて、欠陥の有無、個数、サイズ、位置などの欠陥情報を表示する。10

## 【0038】

ステージ2は、主制御部9からのコマンドに従って、ステージ駆動部5によってXY方向にステップ移動または連続移動が可能である。ステージ2には、測長ミラー3が固定されており、レーザ測長器4によってステージ2のXY位置が精度良く計測される。計測したステージ2の位置情報は、主制御部9に伝送される。

## 【0039】

また、ステージ2の高さ(Z位置)は、レーザ光源12からマスクブランクMの表面に対して斜めに照射し、その反射光をセンサ13で検出することによって計測される。計測したステージ2の高さ情報は、主制御部9に伝送される。20

## 【0040】

ステージ2には、高さ調整機構(不図示)を組み込んでもよく、ステージ2がXY方向に移動した場合でも、センサ13に受光される反射光の位置が一定になるように、ステージ2の高さ調整を行うことによって、検査光BMの合焦制御が可能になる。

## 【0041】

さらに、ステージ2には、X軸回りの傾斜角およびY回りの傾斜角を調整する機構(不図示)を組み込んでもよく、上述のレーザ高さ計測器を複数設置することにより、ステージ2がXY方向に移動した場合でも、マスクブランクMの表面がXY面と常に平行になるように、傾き誤差を補正できる。30

## 【0042】

また、図示してはいないが、ステージ2の近傍には、マスクブランクMに形成された基準マークを検知するためのアライメントスコープが設置されている。

## 【0043】

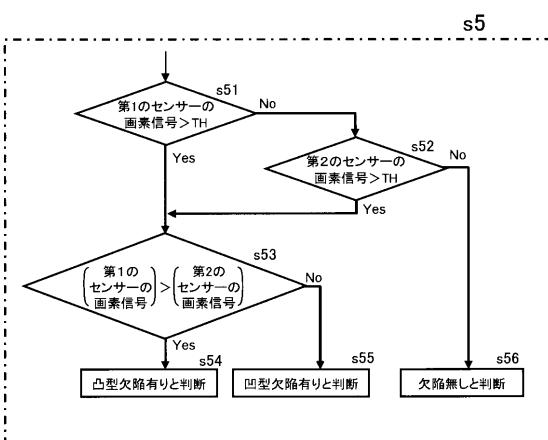

図2(a)は、反射型マスクブランクMの全体を示す平面図であり、図2(b)は、欠陥15を含む拡大図である。図2(c)と図2(d)は、A-A'線に沿った断面図であり、図2(c)は凸状欠陥の様子を示し、図2(d)は凹状欠陥の様子を示す。

## 【0044】

マスクブランクMは、マスク基板MS上に、波長(例えば、13.5nm)の露光光に対して反射率が十分に得られるように、Si(シリコン)とMo(モリブデン)を交互に積層した多層膜MLを形成したものである。40

## 【0045】

多層膜MLを成膜する際、マスク基板MS上に、異物などの微細粒子が存在すると、多層膜MLはその影響を受けて、図2(c)に示すように、多層膜MLの表面が凸形状になって、凸状の位相欠陥16が発生する。逆に、マスク基板MSの表面に、微小な窪み、ピットが存在すると、図2(d)に示すように、多層膜MLの表面が凹形状になって、凹状の位相欠陥17が発生する。

## 【0046】

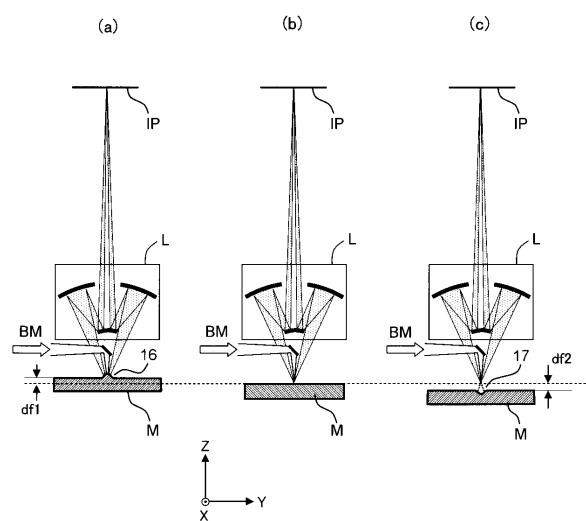

図3(a)は、凸状欠陥16を含むマスクプランクMの欠陥検出信号強度が最大となる検出状態を示す説明図である。図3(b)は、無欠陥のマスクプランクMを検出光学系の合焦位置に配置した状態を示す説明図である。図3(c)は、凹状欠陥17を含むマスクプランクMの欠陥検出信号強度が最大となる検出状態を示す説明図である。ここでは、理解容易のため、ビームスプリッタBSを省いて、結像光学系Lの結像面IPにアレイセンサを配置して光強度を検出する例について説明する。

#### 【0047】

凸状欠陥16は、僅か6nm程度の小さな高さを有する。凹状欠陥17は、僅か6nm程度の小さな深さを有する。いずれの場合も、検査光BMをマスクプランクMに対して垂直に照射した状態で、結像面IPでの光強度が最大となるようにマスクプランクMの高さを調整する合焦制御を行い、その高さを最適フォーカス位置とみなす。

10

#### 【0048】

図3(b)に示す無欠陥のマスクプランクMについて合焦制御を行ったフォーカス位置を基準として、図3(a)に示すような凸状欠陥16が存在する場合、凸状欠陥16は凸面ミラーのように作用して、フォーカス位置は距離df1だけ光路長が短くなる向きにシフトする。一方、図3(c)に示すような凹状欠陥17が存在する場合、凹状欠陥17は凹面ミラーのように作用して、フォーカス位置は距離df2だけ光路長が長くなる向きにシフトする。

#### 【0049】

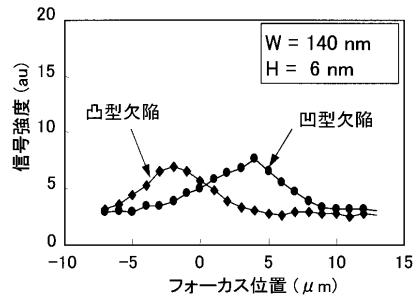

図4は、結像面IPでの信号強度とフォーカス位置の関係を示すグラフである。縦軸は暗視野検出像の信号強度を示し、横軸はフォーカス位置(フォーカスレベル)を示す。フォーカス位置の値が大きいほど、マスクプランクMの位置は結像光学系Lから離れることを意味する。なお、無欠陥のマスクプランクMのフォーカス位置は0である。ここで、直径W=140nm、高さH=6nmの凸状欠陥と、直径W=140nm、深さH=6nmの凹状欠陥が存在する場合を例示している。

20

#### 【0050】

図4を参照すると、凸状欠陥が存在する場合、合焦制御によるフォーカス位置は結像光学系Lに近づく方向にシフトし、一方、凹状欠陥が存在する場合、合焦制御によるフォーカス位置は結像光学系Lから離れる方向にシフトすることが判る。

#### 【0051】

本実施形態では、図1に示したように、結像光学系Lからの出射光束14をビームスプリッタBSによって2つの光束14a, 14bに分岐し、2個の2次元アレイセンサSa, Sbを用いて各シフト量を同時計測している。

30

#### 【0052】

ここで、結像光学系Lの倍率をMAGとして、2次元アレイセンサSaの受光面と光束14aの結像面IPAとの間の距離d1=MAG<sup>2</sup>×df1とし、2次元アレイセンサSbの受光面と光束14bの結像面IPbとの間の距離d2=MAG<sup>2</sup>×df2と設定することが好ましい。

#### 【0053】

なお、図1に示す構成において、ビームスプリッタBSは、必要に応じて、移動させて集光光路から取り外し可能であることが好ましい。すなわち、1個の2次元アレイセンサSaのみで検査信号を取り込むようにした暗視野検出装置の構成も実現可能である。この場合、センサSaの受光面を、結像光学系Lの結像面IPAとほぼ一致するように配置することが好ましく、これにより受光面に到達する検査光の光量は約3倍になる。

40

#### 【0054】

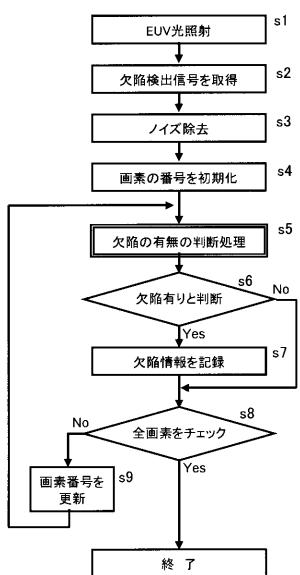

次に、図5と図6に示すフローチャートを用いて、本実施形態に係るマスクプランク検査方法を詳細に説明する。

#### 【0055】

まず図5のステップs1において、図1に示すように、多層膜MLが形成された反射型マスクプランクMをステージ2に載置して、ステージ駆動部5によって所望のXY位置に

50

位置決めを終えた後、検査光B Mを照射し、マスクブランクMの被検査領域を照明する。

**【0056】**

次にステップs 2において、結像光学系Lからの出射光束1 4をビームスプリッタBSによって2つの光束1 4 a, 1 4 bに分岐し、2次元アレイセンサS a, S bを用いて各欠陥検出信号を取得する。各検出信号は信号蓄積部6, 7に取り込まれて、続いてノイズ除去処理が施され(ステップs 3)、そして、検出信号の位置を定義する画素番号の初期化処理を行う(ステップs 4)。

**【0057】**

次にステップs 5において、画像処理部8は、欠陥の有無の判断処理を行う。次にステップs 6において、欠陥有りと判断した場合、ステップs 7に移行して、欠陥の有無、個数、サイズ、位置などの欠陥情報をデータ管理システムなどに記録する。10

**【0058】**

次にステップs 8において、すべての画素の処理が終了したかの判断を行い、処理すべき画素が残っている場合は、画素番号を更新して(ステップs 9)、ステップs 5に移行し、再び欠陥の有無の判断処理を繰り返す。

**【0059】**

図6は、ステップs 5における欠陥の有無の判断処理の詳細を示すフローチャートである。マスクブランクMに欠陥が存在すると、欠陥位置に対応する2次元アレイセンサS a, S bの何れかの画素での信号レベルが増大する。同一の箇所の検査信号が、ビームスプリッタBSを介して2個の2次元アレイセンサS a, S bに取り込まれるため、両センサの検査信号レベルが予め設定した所定の閾値THを超えるか否かを判断することにより、欠陥の有無を判定できる。20

**【0060】**

具体的には、まずステップs 5 1において、第1の2次元アレイセンサS aの所定の画素の信号と予め設定した閾値THとを比較する。画素の信号レベルが閾値TH以下であれば、ステップs 5 2において、第2の2次元アレイセンサS bの対応する画素の信号と当該閾値THとを比較する。比較の結果、いずれの画素の信号レベルも閾値TH以下であれば、欠陥無しと判断できる(ステップs 5 6)。

**【0061】**

一方、いずれの画素の信号レベルも閾値THより大きい場合、ステップs 5 3において、今度は、第1の2次元アレイセンサS aの所定の画素の信号と第2の2次元アレイセンサS bの所定の画素の信号とを比較する。前者が後者より大きければ、凸型欠陥ありと判断する(ステップs 5 4)。一方、前者が後者以下であれば、凹型欠陥ありと判断する(ステップs 5 5)。30

**【0062】**

なお、欠陥判定に使用する閾値THは、光学系に起因したノイズや2次元アレイセンサ等の電気系ノイズなどに由来する検出信号のバックグラウンドレベルの影響を予め把握しておいて、その影響を受けないように設定することが望ましい。

**【0063】**

また、2次元アレイセンサS a, S bは、同じレベルの光を受光したときに同じレベルの出力が得られるよう較正することが望ましい。このとき、ビームスプリッタBSで分岐される光束1 4 a, 1 4 bの強度が異なる場合は、光束1 4 a, 1 4 bの強度比に応じて2次元アレイセンサS a, S bの感度を較正して、同じレベルの出力が得られるように調整することが望ましい。40

**【0064】**

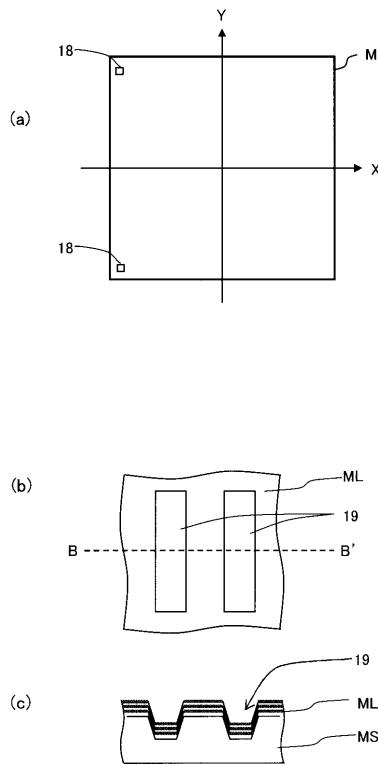

図7(a)は、基準マーク1 8が形成されたマスクブランクMの全体を示す平面図である。図7(b)は、基準マーク1 8の拡大図であり、図7(c)は、図7(b)のB-B'線に沿った断面図である。

**【0065】**

マスクブランクMは、一般に、矩形状をなし、4つの角部のうちの隣接する2つの各部50

近傍に基準マーク 18 を予め設けている。これらの基準マーク 18 は、多層膜 M L の上に吸収体パターンを形成するときの基準点として機能するものであり、マスクプランク M の検査の際、アライメントスコープ(不図示)で計測することによって、マスクプランク M の基準座標を正確に決定できる。

## 【0066】

マスクプランク M を構成する超平滑基板の表面の一部には、微細幅の凹部 19 が F I B (Focused Ion Beam) 等により予め形成されている。凹部 19 を覆うように多層膜 M L を堆積することにより、凹部 19 に対応した位置に基準マーク 18 が形成される。ここでは、一対の凹部 19 が 1 つの基準マーク 18 を構成する場合を例示している。

## 【0067】

凹部 19 を E U V 光で観察した場合、大きな位相変化を伴ったパターン部として認識できる。したがって、基準マーク 18 をマスクプランク M 上の座標の基準として用い、検出される欠陥の位置は、基準マーク 18 を基準とした相対座標で定義できる。

## 【0068】

基準マーク 18 は、電子線、紫外光、可視光を照射した場合も、その反射光からパターン検出が可能である。これにより、例えば、電子線を用いて吸収体パターンを形成する際、基準マーク 18 および欠陥は電子線により検出することが可能である。

## 【0069】

基準マーク 18 は、1 つのマスクプランク M につき 2箇所またはそれ以上に配置することが好ましい。基準マーク 18 を 2箇所またはそれ以上配置することで、マスクプランク M の回転ずれを測定でき、その修正や補正が可能となる。ただし、基準マーク 18 の配置個数があまり多すぎても基準座標の設定が難しくなるので、本実施形態では基準マーク 18 が 2 つの角部近傍に 1 個ずつ、合計 2 箇所に配置している。

## 【0070】

特に限定されないが、基準マーク 18 の平面寸法は、例えば、200 ~ 2000 nm 程度である。なお、基準マークの形成方法は、上記に限られること無く、例えば、平坦基板面上に多層膜 M L を形成した後、多層膜 M L 上に F I B や短波長レーザ光を照射しても、基準マークとして活用できる。また、マスクプランク M のエッジ位置を光学的に検出する方法を採用しても同等の効果が得られる。

## 【0071】

次に、反射型露光マスクの製造方法について説明する。上述のように検査が済んだ反射型マスクプランク M の上には、集積回路パターンに対応した吸収体パターンが形成される。従来は、修正が困難な欠陥が検出された場合、たとえ微小サイズの欠陥であってもそのマスクプランクは不良品として取り扱われ、処分される。

## 【0072】

本実施形態では、マスクプランク M に、凸型欠陥や凹型欠陥などの各種欠陥が存在している場合でも、吸収体パターンで欠陥を覆い隠すことによって、マスクプランクの不良品率を削減している。

## 【0073】

まず、上述した検査方法により、マスクプランク M の欠陥の位置情報を事前に記憶しておく。このとき上述した基準マーク 18 を利用することにより、欠陥の位置座標を正確に把握することができる。

## 【0074】

続いて、記憶した欠陥位置情報に基づいて、吸収体パターンの形成位置を規定するための吸収体パターンマスクとマスクプランクとの相対位置を決定する。このとき、例えば、吸収体パターンが欠陥を覆い隠すように、吸収体パターンマスクの位置決めが可能である。そして、決定した相対位置に基づいて、マスクプランクの上に吸収体パターンを形成する。得られた反射型露光マスクは、吸収体パターンの下に欠陥が隠れているため、半導体基板の露光投影には全く支障がない。

## 【0075】

10

20

30

40

50

以上のように、本実施形態のマスクプランクの検査装置および検査方法を用いることによって、マスクプランクの位相欠陥となる表面凹凸を容易に判断できるので、欠陥生成要因の分析が可能になり、無欠陥マスクプランク製造技術の開発を促進できる。

#### 【0076】

さらに、位相欠陥の位置が特定できるので、多層膜の上に半導体回路などのマスクパターンを定義する吸収体パターンと位相欠陥との位置関係を操作することにより、製造する反射型露光マスクの歩留まりを向上させることができる。その結果、低コストの反射型露光マスクを供給することができる。

#### 【0077】

また、反射型露光マスクを用いた露光処理では、マスクとウエハとの相対平面位置に吸収体パターンのシフト量を加味させることにより、多層膜マスクのパターンをウエハ上に位置合わせ良く形成できる。このため、半導体集積回路の性能、信頼性および歩留まりを向上させることが可能となる。また、反射型露光マスクのコスト低減により、高い性能が要求される半導体集積回路のコスト低減を推進できる。10

#### 【0078】

実施の形態2.

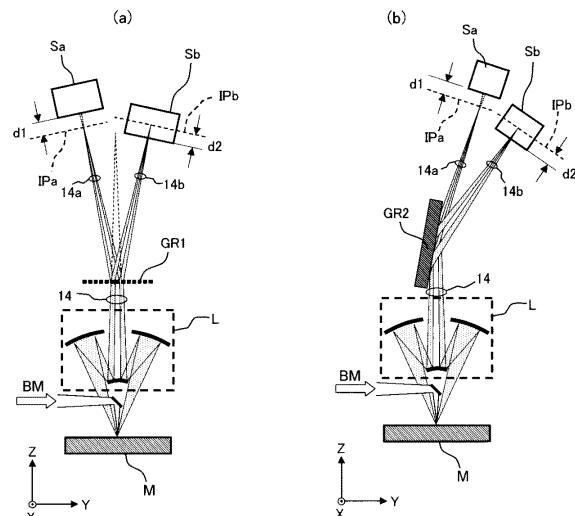

本実施形態では、図1に示した検査装置において、ビームスプリッタBSの代わりに、回折格子で構成された光分岐素子を使用した例を説明する。

#### 【0079】

図8(a)は、透過型の回折格子GR1を使用した例を示す構成図である。図8(b)は、反射型の回折格子GR2を使用した例を示す構成図である。光分岐素子以外の構成は、図1のものと同様であるため、重複説明を省く。20

#### 【0080】

図8(a)において、回折格子GR1は、ステンシル透過型回折格子で構成され、例えば、ピッチ140nmの線状開口群を有する。結像光学系Lからの出射光束14が、回折格子GR1を通過すると、格子ピッチおよび光波長で定まる回折角に従って、数次の回折光に分かれる。そのうち+1次回折光を光束14aとして利用し、-1次回折光を光束14bとして利用することができる。

#### 【0081】

図8(b)では、回折格子GR2は、反射型回折格子として構成され、光束14の平均入射角は、例えば、80度に設定される。結像光学系Lからの出射光束14が回折格子GR2に入射すると、格子ピッチおよび光波長で定まる回折角に従って、数次の回折光に分かれる。そのうち+1次回折光を光束14aとして利用し、-1次回折光を光束14bとして利用することができる。30

#### 【0082】

いずれの場合も、2次元アレイセンサSaは、正のデフォーカス像を検知するように、光束14aの結像面IPaから光進行方向に沿って所定距離d1だけ変位した位置に配置される。一方、2次元アレイセンサSbは、負のデフォーカス像を検知するように、光束14bの結像面IPbから光進行方向とは反対方向に所定距離d2だけ変位した位置に配置される。こうした配置により、センサSa,Sb間の間隔を数cm程度に維持することができる。なお、2次元アレイセンサSa,Sb間に余裕がある場合は、上記の+1次回折光と-1次回折光に限られること無く、0次回折光を2次元アレイセンサSa,Sbのいずれかに取り込むことも可能である。40

#### 【0083】

回折格子GR1,GR2で分岐される光束14a,14bの強度が異なる場合は、光束14a,14bの強度比に応じて2次元アレイセンサSa,Sbの感度を較正して、同じレベルの出力が得られるように調整することが望ましい。

#### 【0084】

本実施形態では、製作の困難な多層膜ビームスプリッタを使用することなく、堅固な回折格子を使用できるという利点がある。また、2個のセンサSa,Sbを接近配置できる50

ため、図1の配置よりも光学系の重心バランスが良く、ステージ2の走査に伴う振動の影響を受けにくい、という利点もある。

#### 【0085】

なお、位相欠陥の凹凸の形状を判別できること、検出した欠陥座標を検知でき、さらに必要であれば欠陥座標情報を吸収体パターンの作成時に反映できることは、実施の形態1の場合と同様であることはいうまでも無い。

#### 【0086】

実施の形態3。

本実施形態では、上述の反射型露光マスクを用いた投影露光方法および半導体集積回路の製造方法について説明する。

10

#### 【0087】

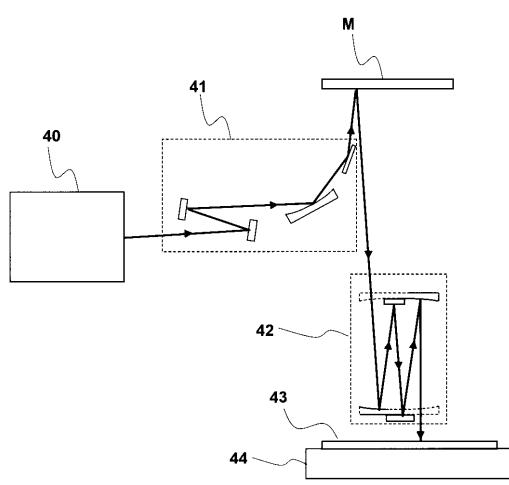

図9は、反射型露光装置の一例を示す構成図である。マスクMは、上述したマスク製造方法によって製造されたものである。光源40から発する中心波長13.5nmのEUV光は、複数の多層膜反射鏡で構成された照明光学系41を介して、マスクMのパターン面を照明する。パターン面からの反射光は、複数の多層膜反射鏡で構成された縮小投影光学系42（例えば、倍率1/4）を通過して、ウエハ43上に結像される。ウエハ43は面内で移動可能なステージ44に搭載されており、ステージ44の移動とパターン露光の繰返しにより、ウエハ43の所望の領域にマスクMに対応したパターンが転写される。

#### 【0088】

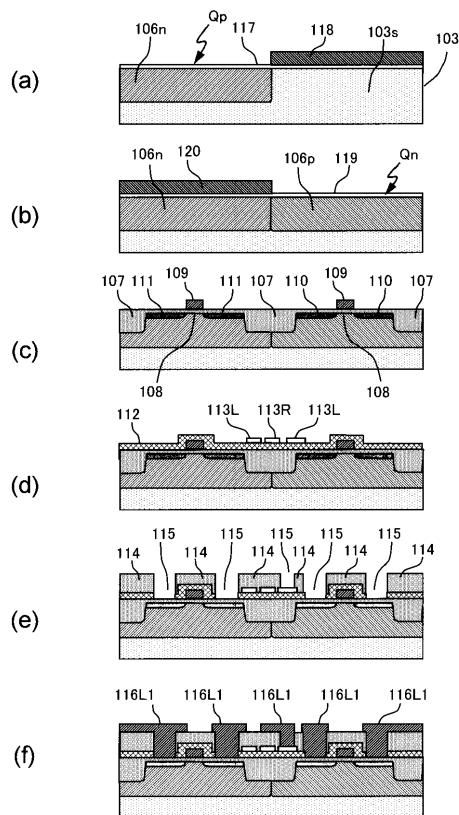

図10(a)～(f)は、半導体集積回路の製造方法の一例を説明する断面図である。ここでは、ツイン・ウェル方式のCMIS(Complimentary MIS)回路を有する半導体集積回路を製造する場合を例示するが、他の種々の方式の回路にも本発明は適用可能である。

20

#### 【0089】

半導体ウエハ103を構成する基板103sは、例えば、略円板状のn+型Si（シリコン）単結晶からなる。基板103sの上部には、例えばnウェル106nおよびpウェル106pが形成されている（図10(b)参照）。nウェル106nには、例えば、n型不純物のP（リン）またはAs（ヒ素）が導入されている。また、pウェル106pには、例えば、p型不純物のB（ホウ素）が導入されている。nウェルおよびpウェルは以下のようにして形成する。

#### 【0090】

30

まず、半導体基板103s上にマスク合わせ用のウエハライメントマークを形成する（図示せず）。このウエハライメントマークは選択酸化工程を付加してウェル形成時に作成することもできる。

#### 【0091】

続いて、図10(a)に示すように、基板103s上に酸化膜117を形成し、そして、酸化膜117の上に、インプラ（イオン・インプランテーションの略称）マスク用のレジストパターン118を通常の光リソグラフィを用いて形成する。その後、P（リン）またはAsをイオン注入して、n型ウェル106nを形成する。

#### 【0092】

40

次に、アッシング処理を行ってレジストパターン118を除去し、酸化膜117を除去した後、図10(b)に示すように、基板103sの上に酸化膜119を形成し、そして、酸化膜119の上に、インプラマスク用のレジストパターン120を通常の光リソグラフィを用いて形成する。その後、B（ホウ素）をイオン注入して、p型ウェル106pを形成する。

#### 【0093】

次に、アッシング処理を行ってレジストパターン120を除去し、酸化膜119を除去した後、図10(c)に示すように、基板103sの上側主面に、例えば、酸化シリコン膜からなる分離用のフィールド絶縁膜107を溝型アイソレーションの形状で形成する。

#### 【0094】

このアイソレーション形状は、例えば、最小寸法がウエハ上で36nmと小さく、寸法

50

精度が 3 . 5 nm と厳しい値が要求される。そのため、このアイソレーション作製時のリソグラフィとして、EUV リソグラフィを用いることができる。

#### 【 0 0 9 5 】

このフィールド絶縁膜 107 によって囲まれた活性領域には、nMIS トランジスタ Q<sub>n</sub> および pMIS トランジスタ Q<sub>p</sub> が形成される。各トランジスタのゲート絶縁膜 108 は、例えば、酸化シリコン膜からなり、熱酸化法などで形成される。

#### 【 0 0 9 6 】

また、各トランジスタのゲート電極 109 は、例えば、最小寸法がウエハ上で 32 nm と小さく、寸法精度が 3 nm と厳しい値が要求される。そのため、例えば、CVD 法等を用いて低抵抗ポリシリコンからなるゲート形成膜を堆積した後、EUV リソグラフィを用いてレジストを形成し、エッティング処理によりゲート電極 109 を形成する。この工程のリソグラフィは、一般にゲート層用リソグラフィと称され、極めて微細でかつ高い寸法精度なパターン転写が求められる。10

#### 【 0 0 9 7 】

nMIS トランジスタ Q<sub>n</sub> の半導体領域 110 は、ゲート電極 109 をマスクとして基板 103s に、例えば、P(リン) または As をイオン注入法等によって導入することにより、ゲート電極 109 に対して自己整合的に形成される。また、pMIS トランジスタ Q<sub>p</sub> の半導体領域 111 は、ゲート電極 109 をマスクとして基板 103s に、例えば、B(ホウ素) をイオン注入法等によって導入することにより、ゲート電極 109 に対して自己整合的に形成される。20

#### 【 0 0 9 8 】

ここで、ゲート電極 9 は、低抵抗ポリシリコンの単体膜で形成されることに限定されるものではなく種々変更可能である。例えば、ゲート電極 9 は、低抵抗ポリシリコン膜上にタンゲステンシリサイドやコバルトシリサイド等のようなシリサイド層を設けた、いわゆるポリサイド構造としてもよい。あるいは、ゲート電極 9 は、低抵抗ポリシリコン膜上に、窒化チタンや窒化タンゲステン等のようなバリア導体膜を介在し、さらにタンゲステン等のような金属膜を設けた、いわゆるポリメタル構造としてもよい。

#### 【 0 0 9 9 】

次に、図 10(d) に示すように、基板 103s 上に、例えば、CVD 法等を用いて酸化シリコン膜からなる層間絶縁膜 112 を堆積した後、層間絶縁膜 112 の上面に配線用のポリシリコン膜を CVD 法等によって堆積する。続いて、このポリシリコン膜上にリソグラフィを実施し、エッティングによりパターニングを行った後、パターニングされたポリシリコン膜の所定領域に不純物を導入することにより、ポリシリコン膜からなる配線 113L および抵抗 113R を形成する。30

#### 【 0 1 0 0 】

次に、図 10(e) に示すように、基板 103s 上に、例えば、CVD 法等を用いて酸化シリコン膜 114 を堆積する。そして、層間絶縁膜 112 および酸化シリコン膜 114 に対して EUV リソグラフィを用いてレジストを形成し、エッティング処理により、半導体領域 110, 111 および配線 113L の一部が露出するような接続孔 115 を形成する。微細な孔は光回折の影響により解像しにくいので、この接続孔用リソグラフィには高い解像度を持った EUV リソグラフィ技術を適用する。40

#### 【 0 1 0 1 】

次に、図 10(f) に示すように、基板 103s 上に、例えば、スパッタリング法や CVD 法等を用いて Ti(チタン)、TiN および W(タンゲステン) からなる金属膜を順次堆積した後、その金属膜の上に、EUV リソグラフィを用いてレジストを形成し、エッティング処理により、第 1 配線層 116L1 を形成する。第 1 配線層 116L1 は、微細な密集パターンと孤立パターンが含まれ、また近隣の配線を避けて配線を引き回したり、配線間を接続するため複雑なレイアウト形状となる。このため第 1 配線層のリソグラフィも高い解像度と寸法精度が要求される。

#### 【 0 1 0 2 】

50

これ以降も、第1配線層 116L1 と同様にして第2配線層(不図示)等を形成することにより、最終製品を製造することができる。

#### 【0103】

上述した一連の半導体装置の製造工程の中で、ゲート層用と接続孔および第1配線層用リソグラフィには十分高い解像性能が要求されるので、EUVリソグラフィを適用することが好ましい。

#### 【0104】

そしてゲート層用と第1配線層用のマスクには、実施の形態1～2で説明した検査装置および方法を用いてマスクプランクを検査し、マスクプランク段階で無欠陥を確認したマスクを用いることが好ましい。

10

#### 【0105】

また接続孔(コンタクトホール)用マスクには、実施の形態1～2で説明した検査装置および方法を用いてマスクプランクを検査し、マスクプランク段階で接続孔部付近に欠陥がないことを確認したマスクを用いることが好ましい。

接続孔の面積は小さく、またパターン密度も5%程度であるため、接続孔付近に欠陥が発生する比率は少なく、この方法により使用できるマスクプランクの歩留まりは高くなる。従って、本実施形態により作製した半導体集積回路の歩留まりは、従来のマスクプランク欠陥検査を行って作製したものより高くなる。

#### 【0106】

以上のように、実施の形態1～2で説明した検査装置および方法を用いてマスクプランクを検査し、マスクプランク段階で無欠陥を確認したマスクを用いることにより、信頼性の高いマスクを用いたパターン転写を行なうことができる。このため、製造した半導体集積回路の性能、信頼性および歩留まりを向上させることが可能となり、その結果、半導体集積回路のコスト低減にも寄与できる。

20

#### 【0107】

以上、本発明を各実施形態を参照しつつ具体的に説明したが、本発明は上述した各実施形態に限定されるものではなく、本発明の範囲を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【産業上の利用可能性】

#### 【0108】

30

本発明は、微細かつ高精度なパターンを含む半導体装置を高い生産効率で製造できる点で、産業上極めて有用である。

#### 【図面の簡単な説明】

#### 【0109】

【図1】本発明に係るマスクプランク検査装置の一例を示す構成図である。

【図2】図2(a)は、反射型マスクプランクMの全体を示す平面図であり、図2(b)は、欠陥15を含む拡大図であり、図2(c)は、凸状欠陥の様子を示すA-A'断面図であり、図2(d)は、凹状欠陥の様子を示すA-A'断面図である。

【図3】図3(a)は、凸状欠陥16を含むマスクプランクMの検出状態を示す説明図であり、図3(b)は、無欠陥のマスクプランクMの検出状態を示す説明図であり、図3(c)は、凹状欠陥17を含むマスクプランクMの検出状態を示す説明図である。

40

【図4】結像面IPでの信号強度とフォーカス位置の関係を示すグラフである。

【図5】本実施形態に係るマスクプランク検査方法を示すフローチャートである。

【図6】ステップs5における欠陥の有無の判断処理の詳細を示すフローチャートである。

【図7】図7(a)は、基準マーク18が形成されたマスクプランクMの全体を示す平面図であり、図7(b)は、基準マーク18の拡大図であり、図7(c)は、図7(b)のB-B'線上に沿った断面図である。

【図8】図8(a)は、透過型の回折格子GR1を使用した例を示す構成図であり、図8(b)は、反射型の回折格子GR2を使用した例を示す構成図である。

50

【図9】反射型露光装置の一例を示す構成図である。

【図10】半導体集積回路の製造方法の一例を説明する断面図である。

【符号の説明】

【0110】

1 光源、 2 ステージ、 3 測長ミラー、 4 レーザ測長器、

5 ステージ駆動部、 6, 7 信号蓄積部、 8 画像処理部、 9 主制御部、

10 ミラー、 12 レーザ光源、 13 センサ、 14, 14a, 14b 光束

18 基準マーク、 BS ビームスプリッタ、 DS 表示部、

IP, IPA, IPB 結像面、 L 結像光学系、 M マスクブランク、

MS マスク基板、 ML 多層膜、 Sa, Sb 2次元アレイセンサ、

103s 基板、 106n n型ウエル、 106p p型ウエル、

108 ゲート絶縁膜、 109 ゲート電極、 116L1 第1配線層。 10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

【 四 8 】

【 図 9 】

【 囮 1 0 】

---

フロントページの続き

(72)発明者 青田 達也

大阪府箕面市小野原東1-2-35-308

審査官 豊田 直樹

(56)参考文献 特開2007-219130(JP,A)

特開2001-235853(JP,A)

特開2007-041600(JP,A)

特開2002-181723(JP,A)

特表2005-524827(JP,A)

特開2000-241121(JP,A)

特開2001-174291(JP,A)

特開2004-193269(JP,A)

特開平04-328549(JP,A)

特開2006-010599(JP,A)

特開2002-286409(JP,A)

(58)調査した分野(Int.Cl., DB名)

G01N 21/84 - 21/958