US 20100165750A1

### (19) United States

## (12) Patent Application Publication Kim et al.

### (10) Pub. No.: US 2010/0165750 A1

### (43) **Pub. Date:**

Jul. 1, 2010

### (54) DATA INPUT DEVICE OF SEMICONDUCTOR MEMORY APPARTUS AND CONTROL METHOD THEREOF

(76) Inventors: **Ki-Ho Kim**, Gyeonggi-do (KR); **Young-Jun Ku**, Gyeonggi-do (KR)

Correspondence Address: IP & T Law Firm PLC 7700 Little River Turnpike, Suite 207 Annandale, VA 22003 (US)

(21) Appl. No.: 12/490,859

(22) Filed: Jun. 24, 2009

### (30) Foreign Application Priority Data

Dec. 26, 2008 (KR) ...... 10-2008-0134896

### **Publication Classification**

(57) ABSTRACT

A data input device of a semiconductor memory apparatus includes input means configured to input data; precharge means configured to supply a precharge voltage for converting inputted data to a differential signal; enable means configured to enable the input means and the precharge means to operate; and control means configured to control a current amount of the enable means in a standby mode.

# FIG.1 (PRIOR ART)

## FIG.2 (PRIOR ART)

| CLK    |  |

|--------|--|

| CKE    |  |

| CKEb   |  |

| VSS    |  |

| Enable |  |

## FIG.3 (PRIOR ART)

FIG.4

FIG.5

FIG.6

FIG. 7

| Function                     | CKE               |                  |      |      |      |     |             |             |     |            |

|------------------------------|-------------------|------------------|------|------|------|-----|-------------|-------------|-----|------------|

|                              | Previous<br>Cycle | Current<br>Cycle | CSb  | RASb | CASb | Web | BA0~<br>BAx | Axx~<br>A11 | A10 | A9~<br>A0  |

| Mode Register<br>Set         | Н                 | Н                | L    | L    | L    | L   | BA          | OP Code     |     |            |

| Refresh                      | Н                 | Н                | L    | L    | L    | Н   | Х           | Х           | Х   | X          |

| Self Refresh<br>Entry        | Н                 | L                | L    | L    | L    | Н   | Х           | Х           | Х   | X          |

| Self Refresh<br>Exit         | Н                 | Н                | Н    | Х    | Х    | Х   | Х           | Х           | Х   | Х          |

|                              |                   |                  | L    | Н    | Н    | Н   |             |             |     |            |

| Single bank<br>Precharge     | Н                 | Н                | L    | L    | Н    | L   | ВА          | Х           | L   | X          |

| all bank<br>precharge        | H                 | Н                | L    | L    | Н    | L   | Х           | Х           | Н   | Х          |

| Bank Avtive                  | Н                 | Н                | اــا | L    | Н    | Н   | · BA        | Row Address |     |            |

| Write                        | Н                 | Н                | L    | L    | Н    | L   | ВА          | Colu<br>mn  | L   | Coul<br>mn |

| Write with<br>Auto Precharge | Н                 | Н                | L    | Н    | L    | L   | ВА          | Colu<br>mn  | Н   | Coul<br>mn |

| Read                         | Н                 | Н                | L    | Н    | L    | Н   | ВА          | Colu<br>mn  | L   | Coul<br>mn |

| Read with<br>Auto Precharge  | Ξ                 | 工                |      | H    | ļ.   | Н   | ВА          | Colu<br>mn  | Н   | Coul<br>mn |

| No Operation                 | Н                 | Χ                | L    | Н    | Н    | Н   | χ           | Х           | Х   | Х          |

| Device<br>Deselect           | Η                 | Х                | Н    | Х    | х    | х   | Х           | Х           | χ   | Х          |

| Power Down                   | Н                 | L                | Н    | Х    | х    | Х   | Х           | Х           | х   | Х          |

| Entry                        |                   |                  | L    | Η    | Н    | Н   |             |             |     |            |

| Power Down<br>Exit           | L                 | Н                | Н    | Χ    | Х    | Х   | Х           | Х           | х   | Х          |

|                              |                   |                  | L    | Н    | Н    | Н   |             |             |     |            |

FIG.8

FIG.9

### DATA INPUT DEVICE OF SEMICONDUCTOR MEMORY APPARTUS AND CONTROL METHOD THEREOF

## CROSS-REFERENCE TO RELATED APPLICATION

[0001] The present application claims priority of Korean Patent Application No. 10-2008-0134896, filed on Dec. 26, 2008, the disclosure of which is incorporated herein by reference in its entirety.

### BACKGROUND OF THE INVENTION

**[0002]** The present invention relates to a semiconductor memory apparatus, and more particularly, to a data input device of a semiconductor memory apparatus which buffers inputted data and a method for controlling the same.

[0003] Semiconductor memory apparatuses have been essential components in most electronic products. For example, semiconductor memory apparatuses are used in various electronic products such as personal computers, televisions, audio sets and communication terminals. The semiconductor memory apparatuses used in various fields receive and store data from different electronic elements or appliances, and provide the stored data to different electronic elements or appliances upon request. Accordingly, the semiconductor memory apparatuses need circuits or devices associated with the input and output of data between the different electronic elements or appliances and the semiconductor memory apparatuses. That is to say, the semiconductor memory apparatuses need circuits or devices for transmitting and receiving data to and from the different electronic elements or appliances.

[0004] In order to store data in a semiconductor memory apparatus, an input buffer is used to temporarily store data received from a different electronic element or appliance. Such an input buffer functions to receive data from the external electronic element or appliance, amplify the received data and convert the amplified data to a level (CMOS level) to be processed in the semiconductor memory apparatus.

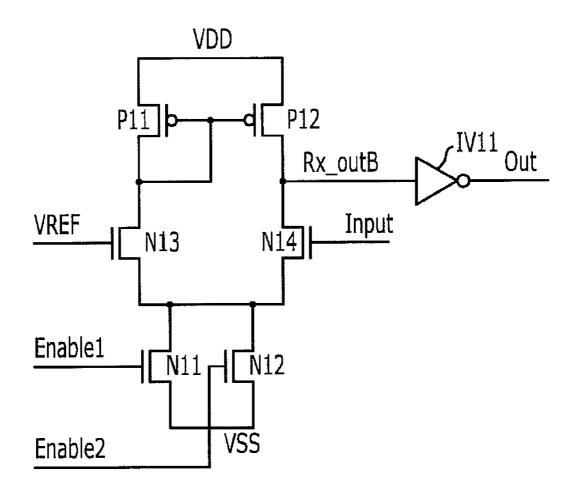

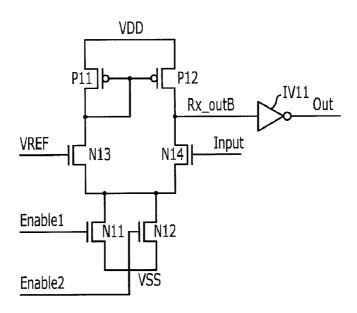

[0005] This will be described with reference to FIG. 1.

[0006] FIG. 1 is a diagram illustrating a conventional circuit for generating a differential signal as an output in an input buffer of a semiconductor memory apparatus.

[0007] The circuit includes an NMOS transistor N3 which receives an input signal INPUT through the gate thereof and an NMOS transistor N2 which receives a reference signal VREF through the gate thereof. Also, the source terminals of the NMOS transistor N3 and the NMOS transistor N2 are connected with each other so that current flows through an NMOS transistor N1. An output signal RX\_OUTB is outputted from the drain terminal of the NMOS transistor N3. The output signal RX\_OUTB is then outputted through an inverter IV1 which is connected in series to the NMOS transistor N3.

[0008] PMOS transistors P1 and P2 are respectively connected in series to the drain terminals of the NMOS transistors N2 and N3. The PMOS transistors P1 and P2, which have the gate terminals connected with each other, constitute a current mirror type. The PMOS transistors P1 and P2 are supplied with an external supply voltage VDD through the respective source terminals thereof.

[0009] The NMOS transistor N1 implements a control function of enabling and disabling the operation of a differ-

ential amplifier which is configured as described above. That is to say, if the NMOS transistor N1 is turned on, as a current path is formed via the NMOS transistor N1 to a ground voltage VSS, the differential amplifier switches to a status in which it can operate. Conversely, if the NMOS transistor N1 is turned off, as the current path to the ground voltage VSS is shut off, the operation of the differential amplifier is interrupted. Accordingly, an enable signal ENABLE is inputted to the gate terminal of the NMOS transistor N1. The enable signal ENABLE is obtained from the output of a NOR gate NOR1 which NORs a clock enable bar signal CKEB and the ground signal VSS.

[0010] A conventional data input device of a semiconductor memory apparatus, which is configured as described above, compares the input signal INPUT and the reference signal VREF, and generates the output signal RX\_OUTB corresponding to a differential signal between the two signals. The output signal RX\_OUTB generated in this way and a signal OUT inverted by the inverter IV1 are outputted. Therefore, the conventional data input device of a semiconductor memory apparatus generates the output signal RX\_OUTB corresponding to the differential signal between the input signal INPUT and the reference signal VREF and the desired output signal OUT obtained by inverting the output signal RX\_OUTB.

[0011] In the conventional data input device of a semiconductor memory apparatus, when the enable signal ENABLE generated by a clock enable signal externally inputted is in a high state, if an external input is greater than the reference voltage VREF, a high signal is generated, and if the external input is less than the reference voltage VREF, a low signal is generated.

[0012] Conversely, in the conventional data input device of a semiconductor memory apparatus, when the enable signal ENABLE generated by the clock enable signal externally inputted is in a low state, since the NMOS transistor N1 is turned off and current flow is cut off, the data input device does not operate regardless of whether or not an input signal is externally applied.

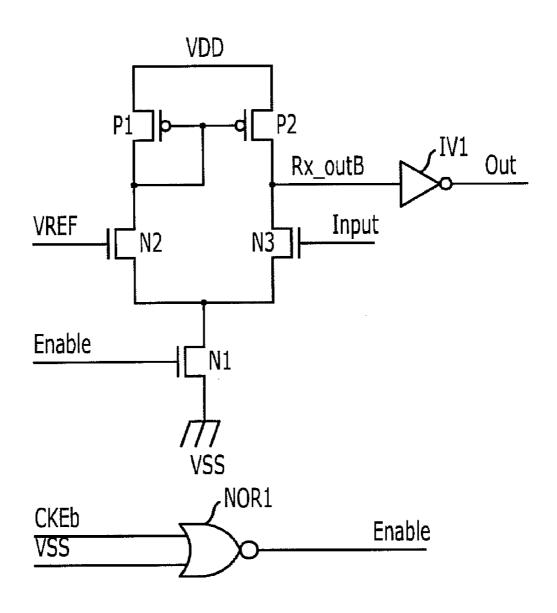

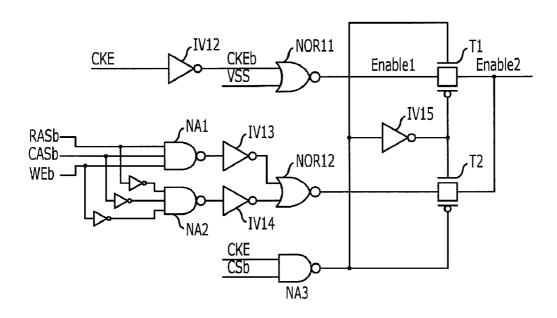

[0013] FIG. 2 illustrates a scheme in which the enable signal is generated by a clock enable signal. Referring to FIG. 2, if a clock enable signal CKE is a high signal, since the enable signal ENABLE inputted to the data input device is converted to a high level, the data input device of a semiconductor memory apparatus consumes current.

[0014] FIG. 3 is a timing diagram illustrating the operation of the conventional data input device of a semiconductor memory apparatus in a standby state. Referring to FIG. 3, the clock enable signal CKE and an external command signal CSB are in a high state, and, while other external command signals RASB, CASB and WEB toggle per every other clock signal and an address A toggles once every four clock signals, current is consumed.

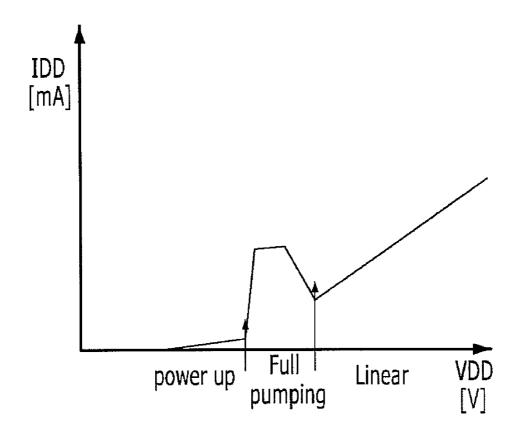

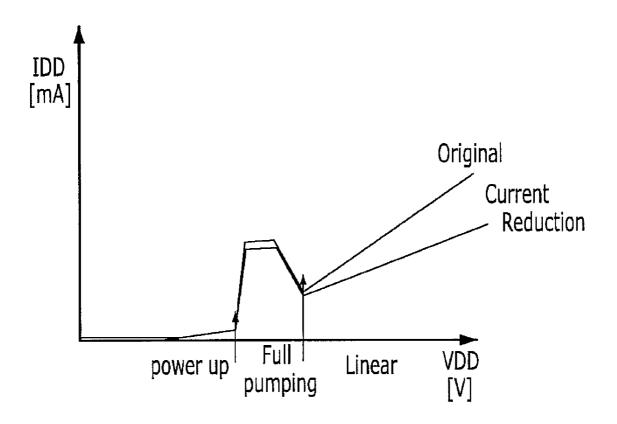

[0015] As a consequence, in the conventional data input device of a semiconductor memory apparatus, due to the fact that current consumption increases in the standby state, a standby IDD curve as shown in FIG. 4 is obtained. Specifically, a hump occurs in the IDD curve in performing a full charge-pumping operation immediately after power supply, and thereafter, the standby IDD curve linearly increases. Accordingly, in the conventional data input device of a semi-

conductor memory apparatus, controlling current consumption in the standby state is desirable.

### SUMMARY OF THE INVENTION

[0016] An embodiment of the present invention is directed to providing a data input device of a semiconductor memory apparatus which can reduce current consumption in a standby state and a method for controlling the same.

[0017] In accordance with an aspect of the present invention, there is provided a data input device of a semiconductor memory apparatus, including input means configured to input data; precharge means configured to supply a precharge voltage for converting inputted data to a differential signal; enable means configured to enable the input means and the precharge means to operate; and control means configured to control a current amount of the enable means in a standby mode.

[0018] In accordance with another aspect of the present invention, there is provided a method for controlling a data input device of a semiconductor memory apparatus, including enabling the data input device so that data can be inputted; controlling a current amount of the enabled data input device in a standby mode; inputting data to the data input device; and converting inputted data to a differential signal and outputting the differential signal.

[0019] In accordance with another aspect of the present invention, there is provided a data input device of a semiconductor memory apparatus, comprising, including a differential amplifier for comparing input to a reference voltage and outputting a differential signal based on the comparison; and a control circuit for adjusting a current driving capacity of the differential amplifier by turning on a first current path connected to the differential amplifier in response to a first enable signal and turning off a second current path connected to the differential amplifier in response to a second enable signal in a standby mode, wherein, during a time that external command signals toggle back and forth between a status of being all high signals or a status of being all low signals repeatedly, the second enable signal is controlled to be maintained at a low state signal.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0020] FIG. 1 is a view illustrating a conventional data input device of a semiconductor memory apparatus.

[0021] FIG. 2 is a view illustrating a scheme in which an enable signal is generated in the conventional data input device of a semiconductor memory apparatus.

[0022] FIG. 3 is a timing diagram illustrating the operation of the conventional data input device of a semiconductor memory apparatus in a standby state.

[0023] FIG. 4 is a graph showing a standby IDD curve of the conventional data input device of a semiconductor memory apparatus in the standby state.

[0024] FIG. 5 is a view illustrating a data input device of a semiconductor memory apparatus in accordance with an embodiment of the present invention.

[0025] FIG. 6 is a view illustrating a scheme in which enable signals used in the data input device according to the present invention are generated.

[0026] FIG. 7 is a truth table showing commands of a semi-conductor memory apparatus.

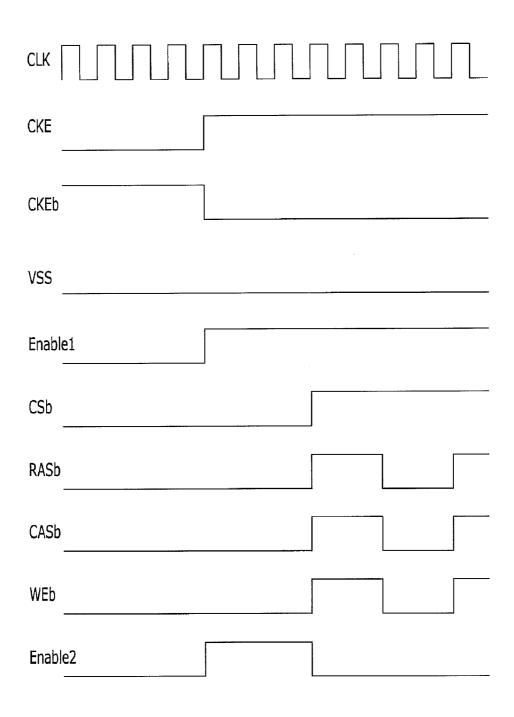

[0027] FIG. 8 is a timing diagram of the enable signals used in the data input device of a semiconductor memory apparatus according to the present invention.

[0028] FIG. 9 is a graph shown a standby IDD curve of the data input device of a semiconductor memory apparatus according to the present invention in a standby state.

#### DESCRIPTION OF SPECIFIC EMBODIMENT

[0029] Other objects and advantages of the present invention can be understood by the following description, and become apparent with reference to the embodiment of the present invention.

[0030] FIG. 5 is a view illustrating a data input device of a semiconductor memory apparatus in accordance with an embodiment of the present invention.

[0031] Referring to FIG. 5, a data input device of a semiconductor memory apparatus in accordance with an embodiment of the present invention includes an NMOS transistor N14 which is applied with an input signal INPUT through the gate thereof and an NMOS transistor N13 which is applied with a reference signal VREF through the gate thereof. The source terminals of the NMOS transistor N13 and the NMOS transistor N14 are connected with each other so that current can flow through an NMOS transistor N11 and an NMOS transistor N12 to a ground source VSS. An output signal RX\_OUTB is outputted from the drain terminal of the NMOS transistor N14. The output signal RX\_OUTB is outputted through an inverter IV11 which is connected in series to the NMOS transistor N14.

[0032] PMOS transistors P11 and P12 are connected in series to the respective drain terminals of the two NMOS transistors N13 and N14. The two PMOS transistors P11 and P12, which have the gate terminals connected with each other, constitute a current mirror. The PMOS transistors P1 and P12 are supplied with an external supply voltage VDD through the respective source terminals thereof.

[0033] The NMOS transistor N11 and the NMOS transistor N12 implement a control function of enabling and disabling the operation of a differential amplifier which is configured as described above. That is to say, if the NMOS transistor N11 is turned on, as a current path is formed via the NMOS transistor N11 to the ground source VSS, the differential amplifier switches to a status in which it can operate. Similarly, if the NMOS transistor N12 is turned on, since a current path is formed via the NMOS transistor N12 to the ground source VSS, the differential amplifier switches to a status in which it can operate. However, if both the NMOS transistor N11 and the NMOS transistor N12 are turned off, since the current paths to the ground voltage VSS are shut off, the operation of the differential amplifier is disabled.

[0034] A first enable signal ENABLE1 for turning on the NMOS transistor N11 and a second enable signal ENABLE2 for turning on the NMOS transistor N12 are generated by different source signals as shown in FIG. 6.

[0035] FIG. 6 is a control diagram for generating the first and second enable signals ENABLE1 and ENABLE2 to control the data input device shown in FIG. 5 to switch to an enabled state or a disabled state.

[0036] First, the first enable signal ENABLE1 for operating the NMOS transistor N11 is generated by a clock enable signal CKE. In other words, as the clock enable signal CKE is inverted by an inverter IV12 and a signal CKEB is generated thereby, the first enable signal ENABLE1 is generated by performing a logical NOR operation on the signal CKEB and the ground signal VSS by a NOR gate NOR11.

[0037] The second enable signal ENABLE2 maintains the same as or different state from first enable signal ENABLE1.

That is to say, when a transmission gate T1 is turned on, the first and second enable signals ENABLE1 and ENABLE2 have the same state. However, when the transmission gate T1 is turned off, the first enable signal ENABLE1 is generated on the basis of the clock enable signal CKE as described above, whereas the state of the second enable signal ENABLE2 is determined by external command signals.

[0038] Namely, the second enable signal ENABLE2 for operating the NMOS transistor N12 is generated by the external command signals RASB, CASB and WEB. A logical NAND operation is performed on the external command signals RASB, CASB and WEB by a NAND gate NA1. Also, after the external command signals RASB, CASB and WEB are inverted by inverters, a logical NAND operation is performed on the inverted signals by a NAND gate NA2. By performing a logical NOR operation on the output signals of the two NAND gates NA1 and NA2 via inverters IV13 and IV14 by a NOR gate NOR12, the second enable signal ENABLE2 is generated.

[0039] The first enable signal ENABLE1 generated through the above-described operations is supplied through or intercepted by the transmission gate T1, and the second enable signal ENABLE2 generated through the above-described operations is supplied through or intercepted by a transmission gate T2. The control of the operation of the two transmission gates T1 and T2 is implemented by the output signal of a NAND gate NA3 which performs a logical NAND operation on the clock enable signal CKE and an external command signal CSB. That is to say, the transmission gate T1 and the transmission gate T2 are selectively operated by the signal obtained by inverting the output of the NAND gate NA3 through an inverter IV15 and the output of the NAND gate NA3.

[0040] As a result, the turning-on and the turning-off of the transmission gates T1 and T2 are controlled by the output signal of the NAND gate NA3, and thereby, the states of the first and second enable signals ENABLE1 and ENABLE2 are determined.

[0041] Hereinbelow, the operating procedure of the data input device of a semiconductor memory apparatus according to the present invention will be described.

[0042] In the present invention, in order to reduce current consumption in a standby state, a method of controlling current when receiving an address is adopted. In general, a semiconductor memory apparatus must be ready to receive a command and an address at any time in a standby state. In this regard, in the present invention, a method which does not disable a semiconductor memory apparatus from being responsive to a command and an address but adjusts/reduces current driving capacity is adopted in the standby state. By doing so, operations of the semiconductor memory device in a standby state do not negatively effect operations for the normal state of the semiconductor memory device.

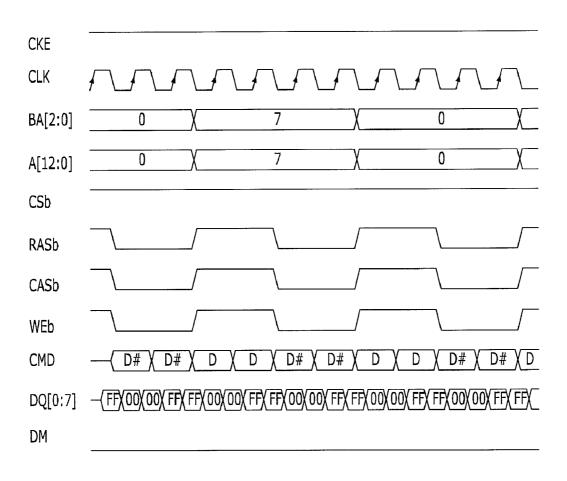

[0043] FIG. 7 is a truth table showing the commands of a semiconductor memory apparatus.

[0044] As can be readily seen from the truth table in FIG. 7, in the present invention, it is desirable to consider the relations between the present invention and functions (including self refresh exit, power down exit, and device deselect) in which the clock enable signal CKE and the external command CSB are simultaneously in a high state.

[0045] The functions of self refresh exit and power down exit are implemented by the clock enable signal CKE irrespective of other commands. Also, the function of device

deselect is implemented by the external command signal CSB. Accordingly, when the clock enable signal CKE and the external command signal CSB are in a high state, except the case in which the external command signals RASB, CASB and CSB operate the semiconductor memory apparatus, the address reception capability of the data input device according to the present invention can be decreased. In the present invention, when the clock enable signal CKE and the external command signal CSB are simultaneously in a high state and the external command signals RASB, CASB and WEB repeatedly toggle back and forth between a state where the external command signals in all high signals to a state where all the external command signals are all low signals, the address reception capability is decreased.

[0046] That is to say, in the data input device of a semiconductor memory according to the present invention, as shown in FIG. 5, the input signal INPUT and the reference signal VREF, which are respectively inputted to the NMOS transistors N14 and N13, are compared with each others, and the output signal RX\_OUTB corresponding to a difference signal between the two signals is generated. After the output signal RX\_OUTB is generated in this way, a desired output signal OUT obtained by inverting the output signal RX\_OUTB by the inverter IV11 is outputted.

[0047] In the data input device of a semiconductor memory according to the present invention, as current paths are defined by the first and second enable signals ENABLE1 and ENABLE2 inputted to the NMOS transistors N11 and N12, the data input device can operate at any time. Referring to FIG. 6, the first enable signal ENABLE1 to be inputted to the NMOS transistor N11 is generated in a manner such that, when the clock enable signal CKE is a high signal, the clock enable signal CKE is inverted by the inverter IV12 and a high signal is then outputted from the NOR gate NOR11. Therefore, the state of the first enable signal ENABLE1 is determined by the clock enable signal CKE having a high level.

[0048] Also, the first enable signal ENABLE1 outputted from the NOR gate NOR11 and having the high level is controlled in its output by the operation of the transmission gate T1 and exerts an influence on the second enable signal ENABLE2. If at least one of the clock enable signal CKE and the external command signal CSB comprises a low signal, the transmission gate T1 is turned on by the output signal of the NAND gate NA3 which has a high level, and the transmission gate T2 is turned off.

[0049] In this case, the two enable signals ENABLE1 and ENABLE2 are in the same high level state. When the two enable signals ENABLE1 and ENABLE2 are in the same high level state, as both the NMOS transistors N11 and N12 for defining current paths are turned on, the data input device of a semiconductor memory apparatus according to the present invention reaches the highest level of current driving capacity in the standby state.

[0050] Conversely, if both the clock enable signal CKE and the external command signal CSB comprise high signals, the transmission gate T1 is turned off, and at this time, the state of second enable signal ENABLE2 is determined by the external command signals RASB, CASB and CSB. That is to say, if the external command signals RASB, CASB and CSB toggle in the same state by repeating a high state and a low state as in the case of measuring standby current, the second enable signal ENABLE2 becomes a low signal. Accordingly, in this

case, the first enable signal ENABLE1 comprises a high signal, and the second enable signal ENABLE2 comprises a low signal.

[0051] Therefore, the second enable signal ENABLE2 is in a low level state, and the first enable signal ENABLE1 is in a high level state. At this time, only the NMOS transistor N11 is turned on by the first enable signal ENABLE1 being in the high level state. Accordingly, in the data input device of a semiconductor memory according to the present invention, current driving capacity in the standby state relatively decreases when compared to the case in which both the NMOS transistors N11 and N12 are turned on.

[0052] Therefore, in the present invention, the second enable signal ENABLE2 is maintained at the same state as the first enable signal ENABLE1, except when the clock enable signal CKE and the external command signal CSB comprise high signals and all the external command signals RASB, CASB and CSB are in a high level or a low level.

[0053] FIG. 8 is a timing diagram of the enable signals ENABLE1 and ENABLE2 used in the data input device of a semiconductor memory apparatus according to the present invention. Referring to FIG. 8, in the present invention, while the second enable signal ENABLE2 is maintained at the same state as the first enable signal ENABLE1, in the case where the clock enable signal CKE and the external command signal CSB are converted to a high state and the external command signals RASB, CASB and CSB toggle to a same one of a high level or a low level, the second enable signal ENABLE2 is controlled to be a low signal, so that current driving capacity due to the reception of an address in the standby state can be reduced. FIG. 9 is a graph shown a standby IDD curve of the data input device of a semiconductor memory apparatus according to the present invention in a standby state. Referring to FIG. 9, it can be confirmed that the slope of the curve decreases with the increase of the external supply voltage VDD when compared to the conventional art.

[0054] As is apparent from the above description, in the present invention, by controlling address receiving operation in a standby state, current consumption due to toggling upon the address receiving operation can be reduced. Accordingly, in the present invention, as current consumption is reduced in the standby state, power consumption of a semiconductor memory apparatus can be reduced.

[0055] The present invention has been described with respect to the specific embodiment only for the purpose of illustration. The present invention can be applied in the case of implementing control operation so as to reduce current consumption while maintaining an enable state. Therefore, it will be apparent to those skilled in the art that various changes and modifications may be made without departing from the spirit and scope of the invention as defined in the following claims.

What is claimed is:

1. A data input device of a semiconductor memory apparatus, comprising:

input means configured to input data;

precharge means configured to supply a precharge voltage for converting inputted data to a differential signal;

enable means configured to enable the input means and the precharge means to operate; and

control means configured to control a current amount of the enable means in a standby mode.

- 2. The data input device of claim 1, wherein the control means is configured to control the current amount of the enable means in address reception operation.

- 3. The data input device of claim 2, wherein the control means comprises:

- a first generation section configured to generate a first enable signal by a clock enable signal;

- a second generation section configured to generate a second enable signal by external command signals; and

- a switching section configured to transfer or stop the transfer of outputs of the first and second generation sections depending upon operational states of the clock enable signal and an external command signal.

- **4**. The data input device of claim **3**, wherein the second generation section is configured to use external command signals.

- 5. The data input device of claim 3, wherein, when the clock enable signal is in a high state, the switching section is configured to be turned on such that the first and second enable signals are controlled to be in the same state.

- **6**. The data input device of claim **3**, wherein, when the clock enable signal and the external command signal are in a high state, a state of the second enable signal is determined by the output of the second generation section.

- 7. The data input device of claim 6, wherein, during a time that external command signals toggle back and forth between a status of being all high signals or a status of being all low signals repeatedly, the second enable signal is controlled to be a low state signal.

- **8**. The data input device of claim 1, wherein the input means is configured to input data, commands and addresses.

- 9. The data input device of claim 8, wherein the input means comprises MOS transistors.

- 10. The data input device of claim 1, wherein the precharge means is formed as a current mirror type.

- 11. The data input device of claim 1, wherein the enable means comprises two NMOS transistors which are connected in parallel between the input means and a ground source and are controlled to turn-on or turn-off by the first and second enable signals.

- 12. The data input device of claim 1, wherein an inverter is connected to an output terminal of the precharge means for converting the inputted data to the differential signal.

- 13. A method for controlling a data input device of a semiconductor memory apparatus, comprising:

enabling the data input device so that data can be inputted; controlling a current amount of the enabled data input device in a standby mode;

inputting data to the data input device; and

converting inputted data to a differential signal and outputting the differential signal.

- 14. The method of claim 13, wherein controlling a current amount controls the current amount of the enabled data input device in address reception operation.

- 15. The method of claim 14, wherein controlling a current amount comprises:

generating a first enable signal by a clock enable signal; generating a second enable signal by an external command signal; and

controlling a transfer or a stop of the transfer of the first and second enable signals depending upon operational sates of the clock enable signal and the external command signal.

- 16. The method of claim 15, wherein, when the clock enable signal is in a high state, controlling a current amount is implemented such that the first and second enable signals are in the same state.

- 17. The method of claim 15, wherein, when the clock enable signal and the external command signal are in a high state, controlling is implemented such that a state of the second enable signal is determined by external command signals.

- 18. The method of claim 15, wherein, when external command signals toggle from a same signal state so that they are all high signals or all low signals to the other state, controlling a current amount is implemented such that the second enable signal is controlled to a low state.

- 19. A data input device of a semiconductor memory apparatus, comprising:

- a differential amplifier for comparing input to a reference voltage and outputting a differential signal based on the comparison; and

- a control circuit for adjusting a current driving capacity of the differential amplifier by turning on a first current path connected to the differential amplifier in response to a first enable signal and turning off a second current path connected to the differential amplifier in response to a second enable signal in a standby mode, wherein, during a time that external command signals toggle back and forth between a status of being all high signals or a status of being all low signals repeatedly, the second enable signal is controlled to be maintained at a low state signal.

- 20. The data input device of claim 19, wherein the control signal comprises a NAND gate configured to receive the external command signals and a NAND gate configured to receive inverted signals of the external command signals and a NOR gate connected to outputs of the NAND gates.

\* \* \* \* \*