(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0086517

(43) 공개일자 2017년07월26일

- (51) 국제특허분류(Int. Cl.)

*H01L 29/423* (2006.01) *H01L 21/8238* (2006.01)

*H01L 27/092* (2006.01) *H01L 29/06* (2006.01)

*H01L 29/08* (2006.01) *H01L 29/417* (2006.01)

*H01L 29/66* (2006.01) *H01L 29/775* (2006.01)

*H01L 29/78* (2006.01) *H01L 29/786* (2006.01)

- (52) CPC특허분류

*H01L 29/42392* (2013.01)

*H01L 21/823821* (2013.01)

- (21) 출원번호 10-2017-7013686

- (22) 출원일자(국제) 2015년09월30일

심사청구일자 없음

- (85) 번역문제출일자 2017년05월19일

- (86) 국제출원번호 PCT/US2015/053305

- (87) 국제공개번호 WO 2016/085570

국제공개일자 2016년06월02일

- (30) 우선권주장

62/083,714 2014년11월24일 미국(US)

14/673,485 2015년03월30일 미국(US)

전체 청구항 수 : 총 23 항

(54) 발명의 명칭 컨택트 랩 어라운드 구조

**(57) 요 약**

반도체 디바이스는 게이트 스택을 포함한다. 반도체 디바이스는 또한 게이트 스택에 근접한 반도체 디바이스의 재성장 소스/드레인 둘레에 배열되어 재성장 소스/드레인의 실질적으로 모든 표면 영역과 컨택팅하는 랩-어라운드 컨택트를 포함한다.

**대 표 도 - 도8**

(52) CPC특허분류

*H01L 27/0924* (2013.01)

*H01L 29/0673* (2013.01)

*H01L 29/0847* (2013.01)

*H01L 29/41791* (2013.01)

*H01L 29/66545* (2013.01)

*H01L 29/66795* (2013.01)

*H01L 29/775* (2013.01)

*H01L 29/785* (2013.01)

*H01L 29/78696* (2013.01)

(72) 발명자

**맥카오우트산, 발디미르**

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

**배다로글루, 머스타파**

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

**바오, 준정**

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

**추, 존 지안홍**

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

**양, 다**

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

**이프, 초 폐이**

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

## 명세서

### 청구범위

#### 청구항 1

반도체 디바이스로서,

게이트 스택; 및

상기 게이트 스택에 근접한 상기 반도체 디바이스의 채성장 소스/드레인 영역의 둘레에 배열되어, 상기 채성장 소스/드레인 영역의 실질적으로 모든 표면 영역과 컨택팅하는 랩-어라운드 컨택트를 포함하는, 반도체 디바이스.

#### 청구항 2

제 1 항에 있어서,

상기 반도체 디바이스는 FinFET(fin field-effect transistor)를 포함하고, 상기 채성장 소스/드레인 영역은 실질적으로 평행한 측벽들을 갖는 핀의 채성장 핀-부분을 포함하는, 반도체 디바이스.

#### 청구항 3

제 2 항에 있어서,

상기 게이트 스택은 상기 핀의 베이스 핀-부분의 표면 상에 있는, 반도체 디바이스.

#### 청구항 4

제 3 항에 있어서,

상기 핀의 상기 베이스 핀-부분은 실리콘, 게르마늄, 실리콘 게르마늄, 또는 인듐 인산염을 포함하는, 반도체 디바이스.

#### 청구항 5

제 1 항에 있어서,

상기 랩-어라운드 컨택트는 MIS(metal insulator semiconductor) 컨택트 또는 직접적인 컨택트를 포함하는 낸-실리사이드 컨택트인, 반도체 디바이스.

#### 청구항 6

제 5 항에 있어서,

상기 MIS 컨택트는 상기 반도체 디바이스의 NMOS(n-type metal oxide semiconductor) 영역에 결합되고 상기 직접적인 컨택트는 상기 반도체 디바이스의 PMOS(p-type metal oxide semiconductor) 영역에 결합되는, 반도체 디바이스.

#### 청구항 7

제 6 항에 있어서,

상기 MIS 컨택트는,

상기 반도체 디바이스의 상기 NMOS 영역 상의 티타늄 산화물 층( $TiO_2$ ); 및

상기 티타늄 산화물 층 상의 티타늄 층(T)을 포함하는, 반도체 디바이스.

#### 청구항 8

제 6 항에 있어서,

상기 직접적인 컨택트는 상기 반도체 디바이스의 상기 PMOS 영역 상에 티타늄 층(T)을 포함하는, 반도체 디바이스.

### 청구항 9

제 1 항에 있어서,

상기 반도체 디바이스는 게이트-올-어라운드(gate-all-around) 나노와이어 FET(field-effect transistor)를 포함하는, 반도체 디바이스.

### 청구항 10

제 1 항에 있어서,

모바일 전화, 셋톱 박스, 뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 네비게이션 디바이스, 컴퓨터, 핸드-헬드 PCS(personal communication systems) 유닛, 휴대용 데이터 유닛, 및/또는 고정 위치 데이터 유닛에 통합되는, 반도체 디바이스.

### 청구항 11

컨택트 랩-어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법으로서,

상기 반도체 디바이스의 소스/드레인 영역들을 재성장시키는 단계;

상기 반도체 디바이스의 더미 게이트를 게이트 스택으로 대체하는 단계; 및

상기 게이트 스택에 근접한 상기 반도체 디바이스의 재성장 소스/드레인 영역 둘레에 랩-어라운드 컨택트를 제조하는 단계 및 상기 랩-어라운드 컨택트를 상기 재성장 소스/드레인 영역의 실질적으로 모든 표면 영역과 컨택팅시키는 단계를 포함하는, 컨택트 랩-어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법.

### 청구항 12

제 11 항에 있어서,

상기 반도체 디바이스의 상기 소스/드레인 영역들을 재성장시키는 단계는, 제어된 <111> 패싯 형성에 따른 에피택셜 성장을 포함하는, 컨택트 랩-어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법.

### 청구항 13

제 11 항에 있어서,

상기 랩-어라운드 컨택트를 제조하는 단계는,

상기 반도체 디바이스의 NMOS(n-type metal oxide semiconductor) 영역 상에 티타늄 산화물 층( $TiO_2$ )을 증착하는 단계; 및

상기 티타늄 산화물 층 상에 티타늄 층(T)을 증착하는 단계를 포함하는, 컨택트 랩-어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법.

### 청구항 14

제 11 항에 있어서,

상기 랩-어라운드 컨택트를 제조하는 단계는, 상기 반도체 디바이스의 PMOS(p-type metal oxide semiconductor) 영역 상에 바로 티타늄 층(T)을 증착하는 단계를 포함하는, 컨택트 랩-어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법.

### 청구항 15

제 11 항에 있어서,

상기 반도체 디바이스는 모바일 전화, 셋톱 박스, 뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 네비게이션 디바이스, 컴퓨터, 핸드-헬드 PCS(personal communication systems) 유닛, 휴대용 데이터 유닛, 및/또는 고정 위치 데이터 유닛에 통합되는, 컨택트 랩-어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법.

#### 청구항 16

반도체 디바이스로서,

게이트 스택; 및

상기 게이트 스택에 근접한 상기 반도체 디바이스의 재성장 소스/드레인 영역의 실질적으로 모든 표면 영역과 컨택팅하기 위한 수단을 포함하는, 반도체 디바이스.

#### 청구항 17

제 16 항에 있어서,

상기 반도체 디바이스는 FinFET(fin field-effect transistor)를 포함하고, 상기 재성장 소스/드레인 영역은 핀의 재성장 핀-부분을 포함하는, 반도체 디바이스.

#### 청구항 18

제 17 항에 있어서,

상기 게이트 스택은 상기 핀의 베이스 핀-부분의 표면 상에 있는, 반도체 디바이스.

#### 청구항 19

제 18 항에 있어서,

상기 핀의 상기 베이스 핀-부분은 실리콘, 게르마늄, 실리콘 게르마늄, 또는 인듐 인산염을 포함하는, 반도체 디바이스.

#### 청구항 20

제 16 항에 있어서,

상기 반도체 디바이스는 게이트-올-어라운드 나노와이어 FET(field-effect transistor)를 포함하는, 반도체 디바이스.

#### 청구항 21

제 16 항에 있어서,

모바일 전화, 셋톱 박스, 뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 네비게이션 디바이스, 컴퓨터, 핸드-헬드 PCS(personal communication systems) 유닛, 휴대용 데이터 유닛, 및/또는 고정 위치 데이터 유닛에 통합되는, 반도체 디바이스.

#### 청구항 22

컨택트 랩-어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법으로서,

상기 반도체 디바이스의 소스/드레인 영역들을 재장시키기 위한 단계들;

상기 반도체 디바이스의 더미 게이트를 게이트 스택으로 대체하기 위한 단계들; 및

상기 게이트 스택에 근접한 상기 반도체 디바이스의 재성장 소스/드레인 영역 둘레에 랩-어라운드 컨택트를 제조하는 단계들 및 상기 랩-어라운드 컨택트를 상기 재성장 소스/드레인 영역의 실질적으로 모든 표면 영역과 컨택팅시키기 위한 단계들을 포함하는, 컨택트 랩-어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법.

#### 청구항 23

제 22 항에 있어서,

상기 반도체 디바이스는 모바일 전화, 셋톱 박스, 뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 네비게이션 디바이스, 컴퓨터, 핸드-헬드 PCS(personal communication systems) 유닛, 휴대용 데이터 유닛, 및/또는 고정 위치 데이터 유닛에 통합되는, 컨택트 랩-어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법.

### 발명의 설명

#### 기술 분야

[0001] 관련 출원의 교차 참조

[0002] [0001] 본 출원은, Jeffrey Junhao XU 등의 이름으로 2014년 11월 24일에 출원되고, 명칭이 "CONTACT WRAP AROUND STRUCTURE"인 미국 가특허 출원 제62/083,714호를 35 U.S.C. § 119(e) 하에서 우선권으로 주장하며, 상기 출원의 개시내용은 그 전체가 본원에 인용에 의해 명백히 포함된다.

[0003] [0002] 본 개시내용의 양상들은 반도체 디바이스들에 관한 것으로, 보다 구체적으로, 컨택트 랩 어라운드 구조에 관한 것이다.

#### 배경 기술

[0004] [0003] IC(integrated circuit) 기술이 발전함에 따라, 디바이스 지오메트리들이 축소된다. 지오메트리 및 디바이스들 간의 "피치"(간격)를 축소시키는 것은, 디바이스들로 하여금 적절한 동작 측면에서 서로 간섭하게 할 수 있다.

[0005] [0004] 펀-기반 디바이스들은 반도체 기판의 표면 상의 3-차원 구조들이다. 펀-기반 MOSFET(metal-oxide-semiconductor field-effect transistor)일 수 있는 펀-기반 트랜지스터를 FinFET라 지칭할 수 있다. 나노와이어 FET(field-effect transistor)는 또한 반도체 기판의 표면 상의 3-차원 구조이다. 나노와이어 FET는, 채널 영역과 컨택트하고 디바이스의 소스 및 드레인 영역들로서 역할을 하는 나노와이어의 도핑 부분들을 포함한다. 나노와이어 FET는 또한 MOSFET 디바이스의 예이다.

[0006] [0005] MOSFET 디바이스들의 성능은 채널 길이, 변형 및 외부 저항을 비롯한 수 많은 팩터들의 영향을 받을 수 있다. 외부 저항에 기여하는 하나의 실질적인 팩터는 소스/드레인 영역들과 전도성 층들 간의 컨택트 저항이다. 컨택트 저항들은 지오메트리 및 디바이스들 간의 "피치"(간격)가 급격히 축소되는 발전된 기술 노드들에 대한 디바이스 성능 및 스케일링 리미터(limiter)이다.

#### 발명의 내용

[0007] [0006] 반도체 디바이스는 게이트 스택을 포함한다. 반도체 디바이스는 또한 게이트 스택에 근접한 반도체 디바이스의 재성장 소스/드레인 둘레에 배열되어, 재성장 소스/드레인의 실질적으로 모든 표면-영역과 컨택팅하는 랩-어라운드 컨택트를 포함한다.

[0008] [0007] 컨택트 랩-어라운드 구조를 포함하는 반도체 디바이스를 제조하는 방법은 반도체 디바이스의 재성장 소스/드레인 영역들을 포함한다. 방법은 또한, 반도체 디바이스의 더미 게이트를 게이트 스택으로 대체하는 단계를 포함한다. 방법은 게이트 스택에 근접한 반도체 디바이스의 재성장 소스/드레인 둘레에 배열되어, 재성장 소스/드레인의 실질적으로 모든 표면 영역과 컨택팅하는 랩-어라운드 컨택트를 제조하는 단계를 더 포함할 수 있다.

[0009] [0008] 반도체 디바이스는 게이트 스택을 포함한다. 반도체 디바이스는 또한 게이트 스택에 근접한 반도체 디바이스의 재성장 소스/드레인 영역의 실질적으로 모든 표면 영역과 컨택팅하기 위한 수단을 포함한다.

[0010] [0009] 다음의 상세한 설명이 더 양호하게 이해될 수 있도록, 본 개시내용의 특징들 및 기술적 이점들을 오히려 광범위하게 약술하였다. 본 개시내용의 부가적인 특성들 및 이점들이 후술될 것이다. 본 개시내용이 본 개시내용의 동일한 목적을 수행하기 위해 다른 구조들을 변경하거나 또는 설계하기 위한 기초로서 용이하게 이용될 수 있다는 것이 당업자들에 의해 인식되어야 한다. 또한, 이러한 등가의 구성들이, 첨부된 청구항들에서 설명되는 바와 같이 본 개시내용의 교시들로부터 벗어나지 않는다는 것이 당업자들에 의해 인식될 것이다. 추가적인 목적들 및 이점들과 함께, 본 발명의 구성 및 동작 방법 둘 다에 대해 본 개시내용의 특징인 것으로 믿어지

는 신규한 특성들은, 첨부한 도면들과 관련하여 고려될 경우 다음의 설명으로부터 더 양호하게 이해될 것이다. 그러나, 도면들의 각각이 단지 예시 및 설명의 목적을 위해 제공되며, 본 개시내용의 범위의 정의로서 의도되지 않는다는 것이 명백히 이해될 것이다.

### 도면의 간단한 설명

[0011]

[0010] 본 개시내용의 양상의 더욱 완전한 이해를 위해서, 이제, 첨부 도면들과 함께 다음 설명이 참조된다.

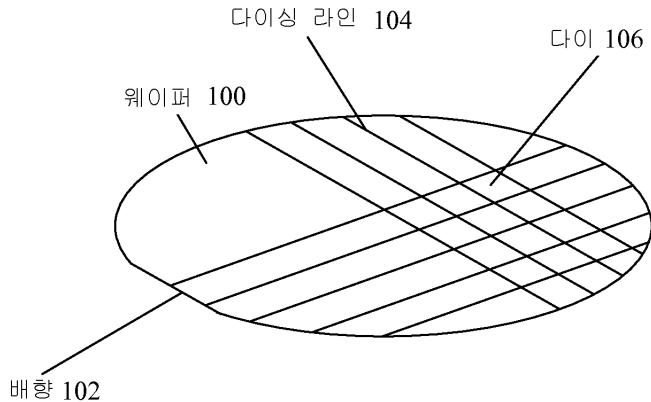

[0011] 도 1은 본 개시내용의 양상에 따른 반도체 웨이퍼의 사시도를 도시한다.

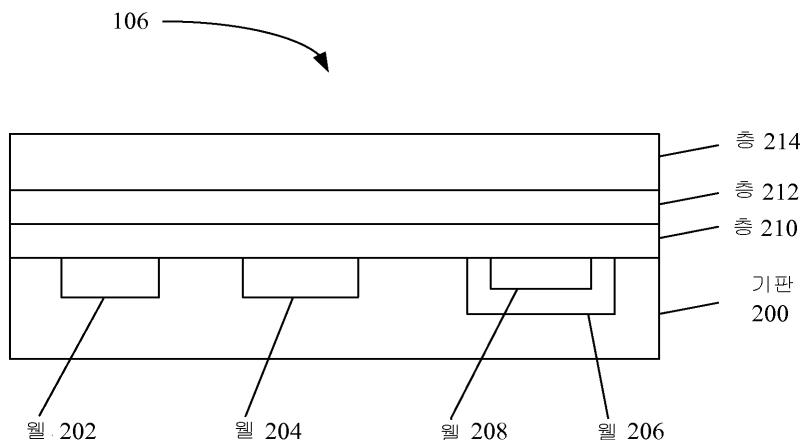

[0012] 도 2는 본 개시내용의 양상에 따른 다이의 단면도를 도시한다.

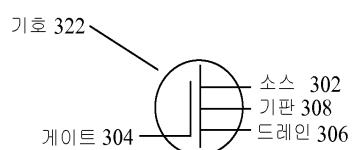

[0013] 도 3은 본 개시내용의 양상에서 MOSFET(metal-oxide-semiconductor field-effect transistor) 디바이스의 단면도를 도시한다.

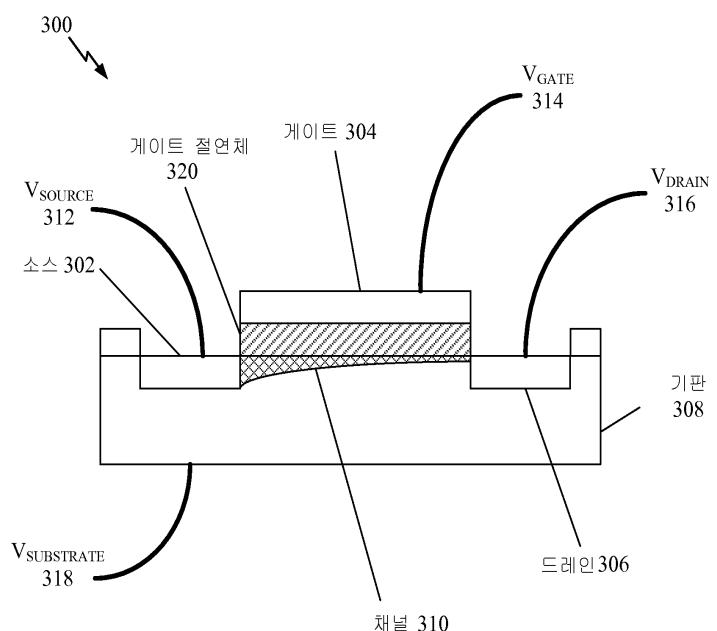

[0014] 도 4는 본 개시내용의 양상에 따른 FinFET(fin field-effect transistor)를 도시한다.

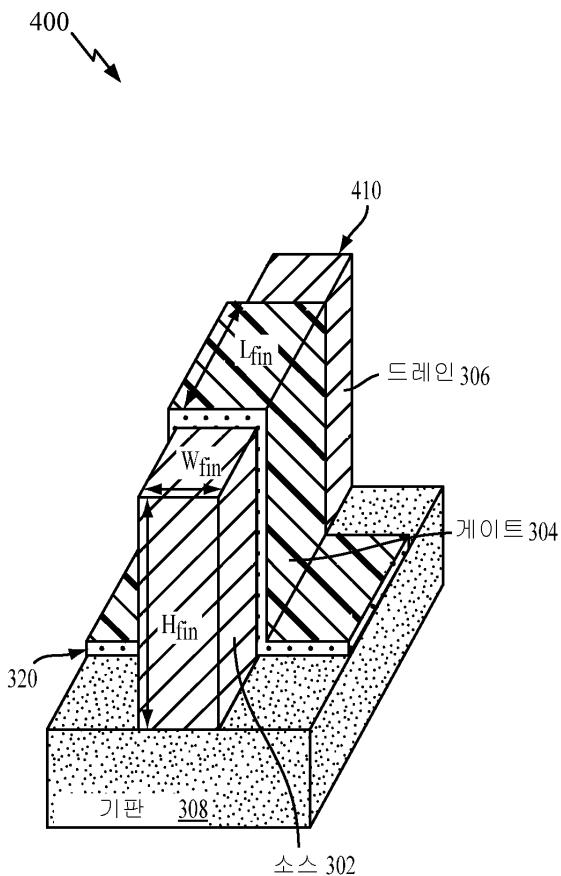

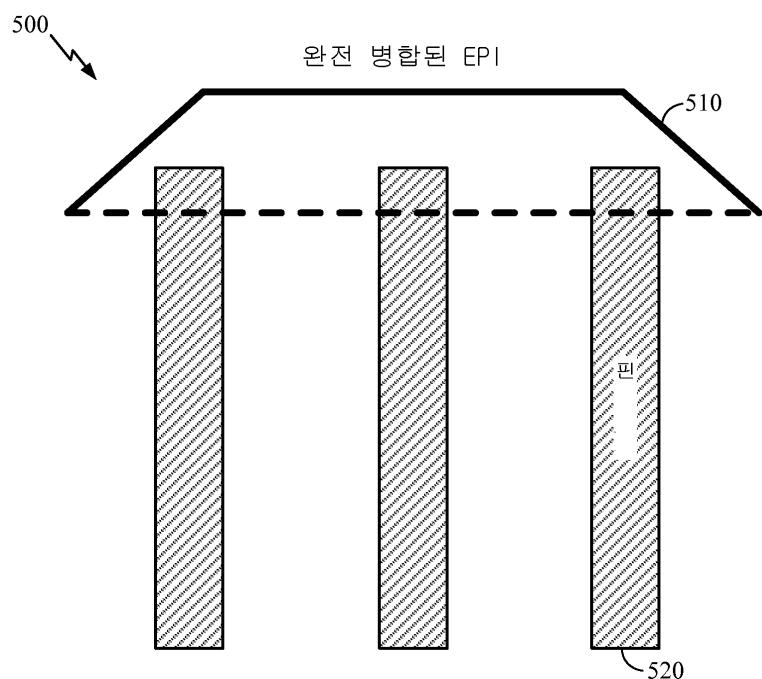

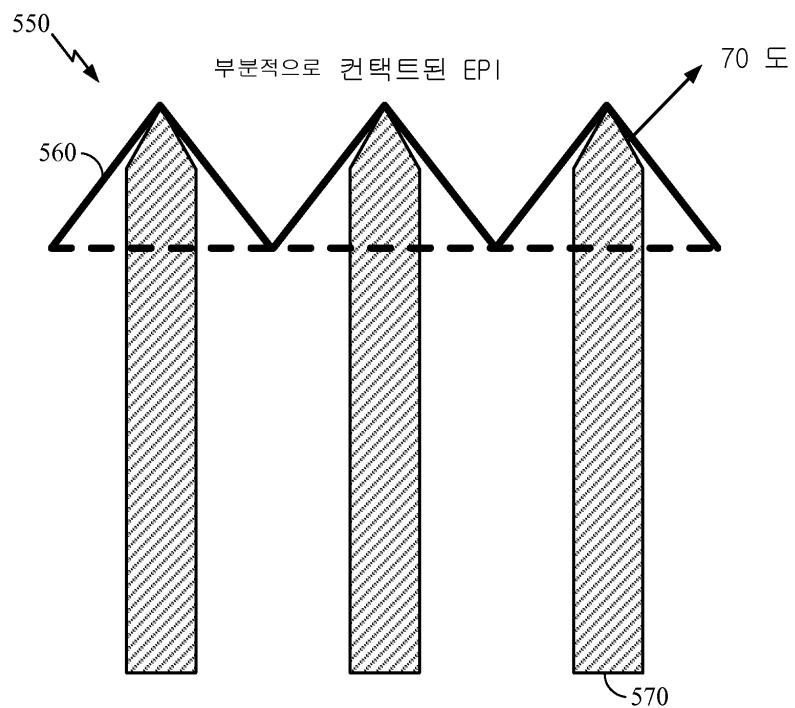

[0015] 도 5a 및 도 5b는 종래의 컨택트 구조들을 포함하는 핀-기반 구조들의 단면도들을 도시한다.

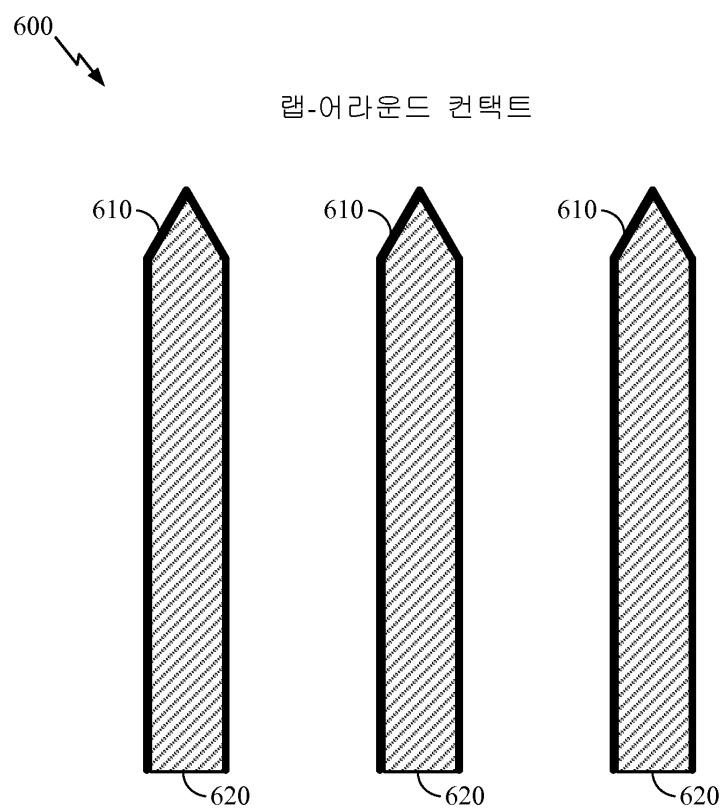

[0016] 도 6은 본 개시내용의 양상에 따른 랩-어라운드 컨택트를 포함하는 핀-기반 구조의 단면도를 도시한다.

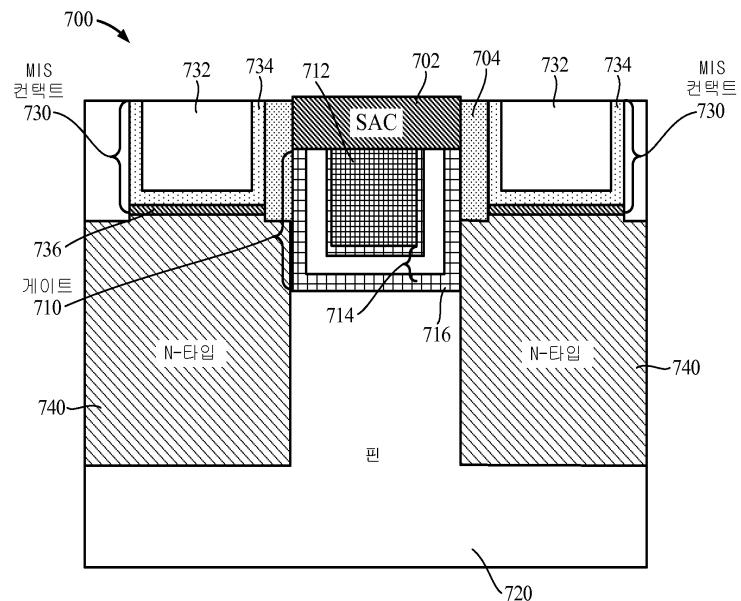

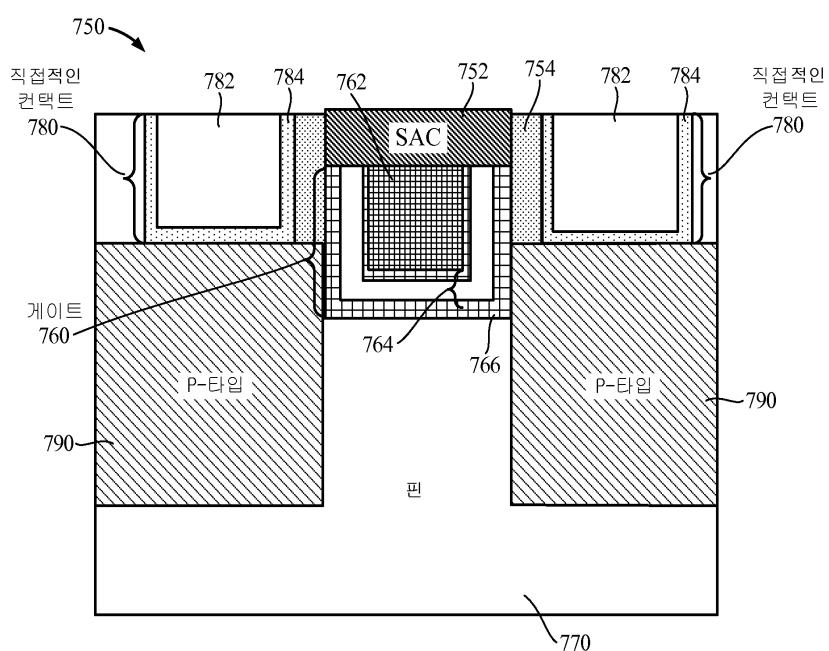

[0017] 도 7a 및 도 7b는 본 개시내용의 양상에 따른 MIS 컨택트 또는 직접적인 컨택트를 포함하는, CMOS(complementary metal oxide semiconductor) 디바이스들의 단면도들을 도시한다.

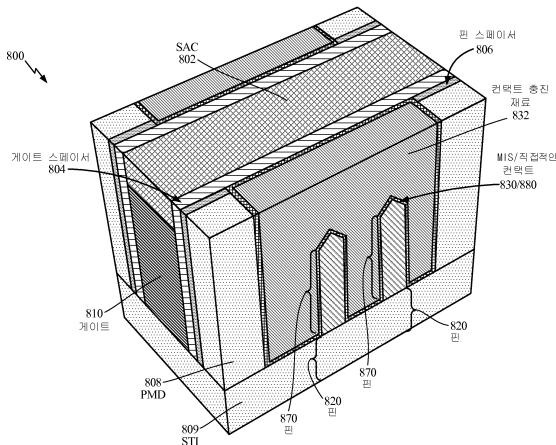

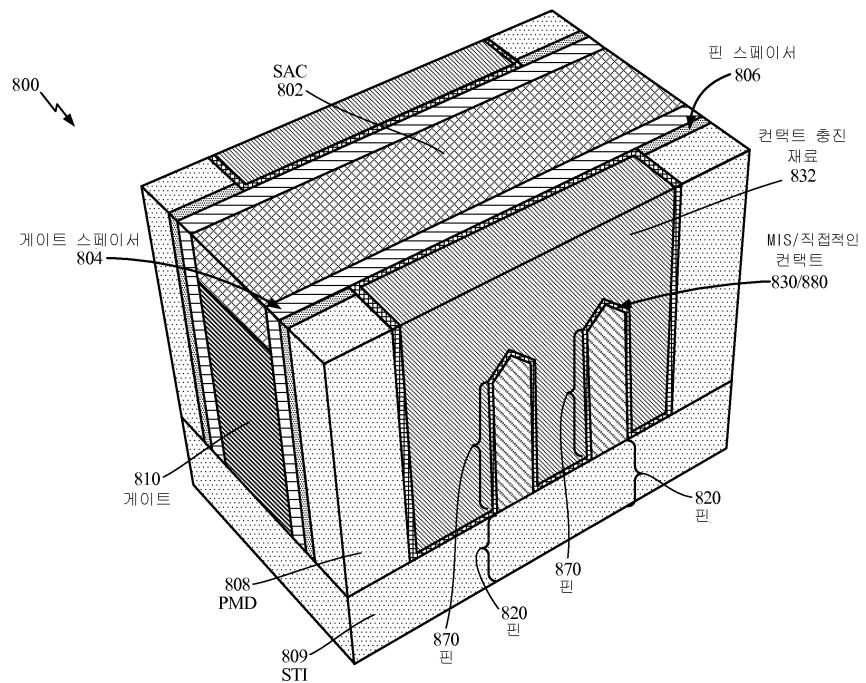

[0018] 도 8은 본 개시내용의 양상에 따른 컨택트 랩-어라운드 구조를 포함하는 핀-기반 디바이스의 단면도를 도시한다.

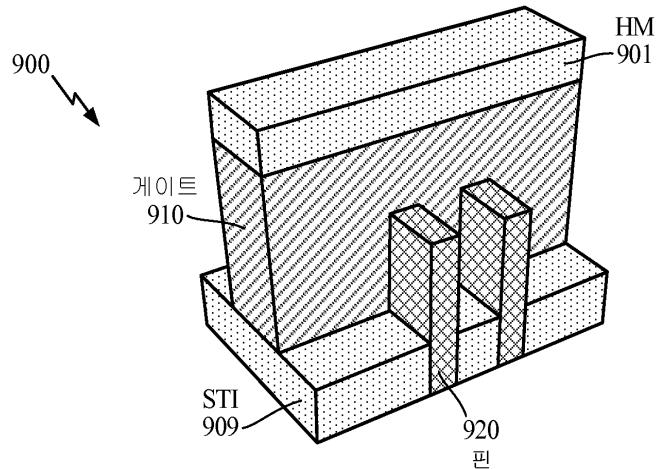

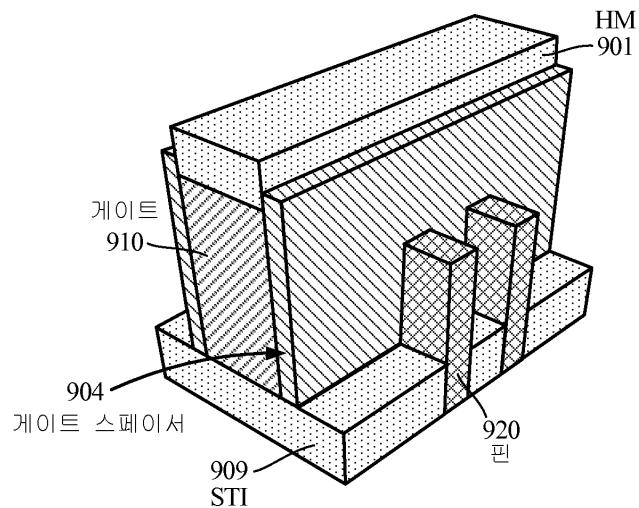

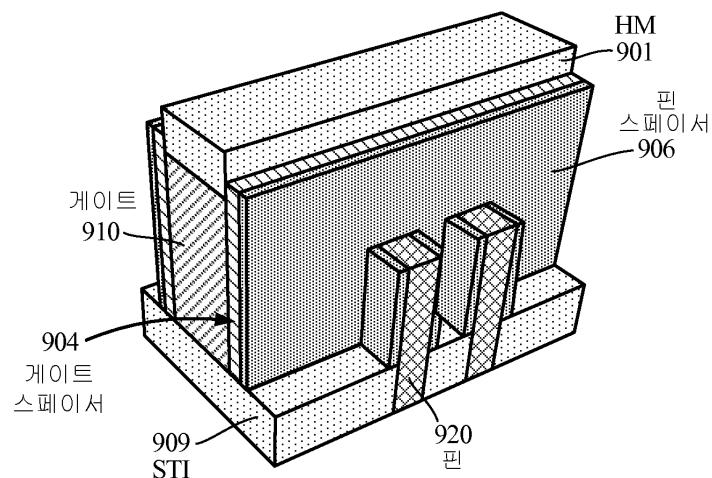

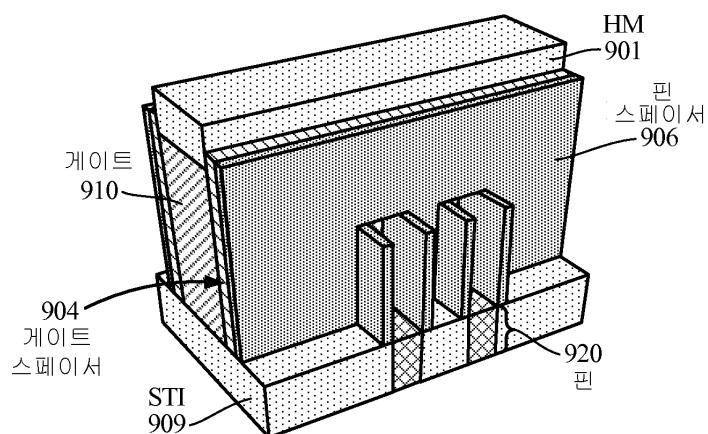

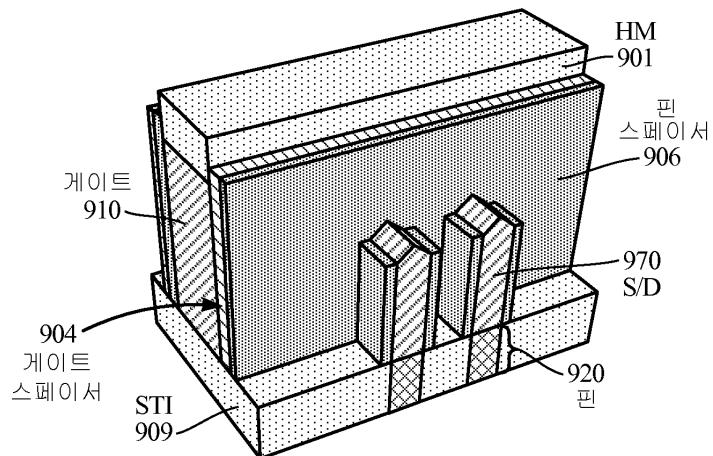

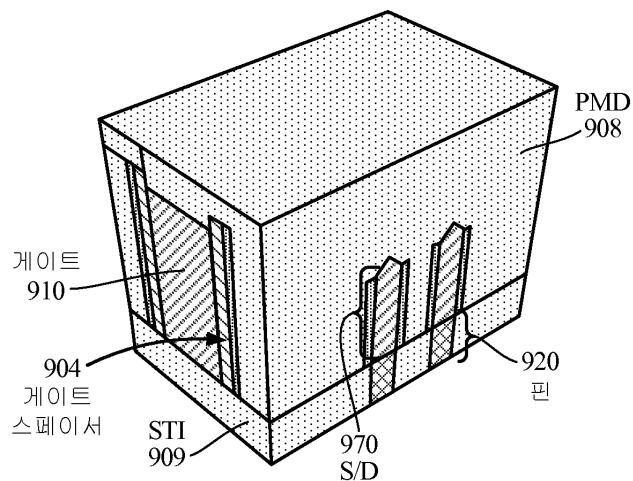

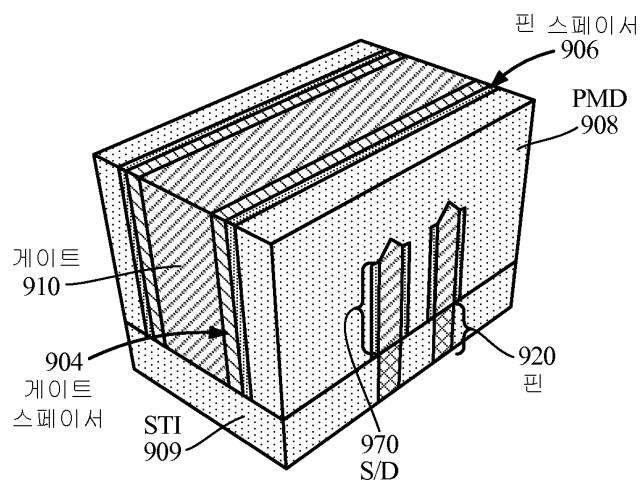

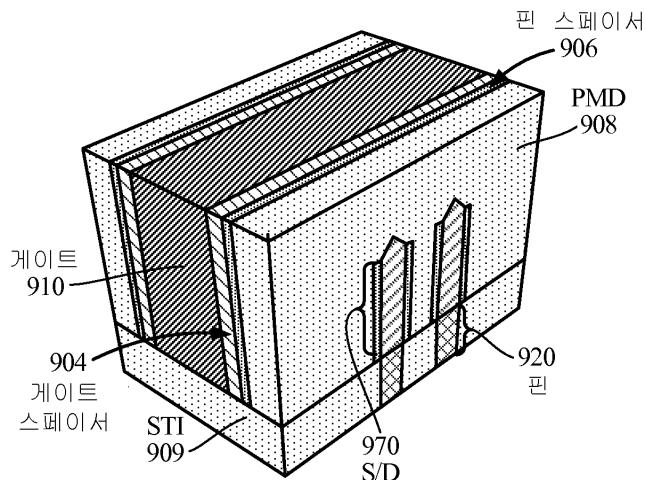

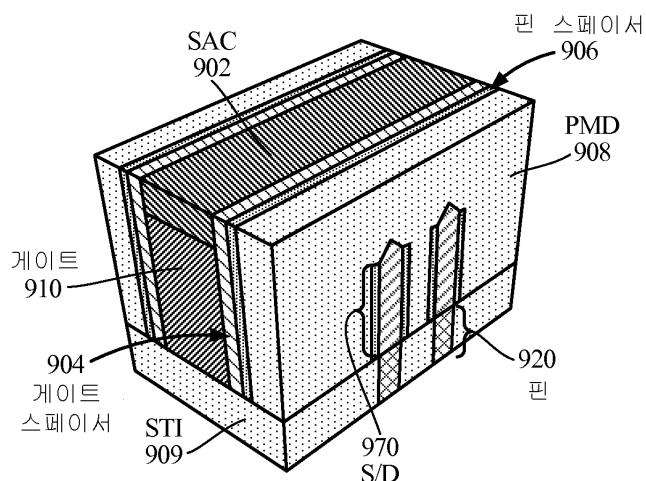

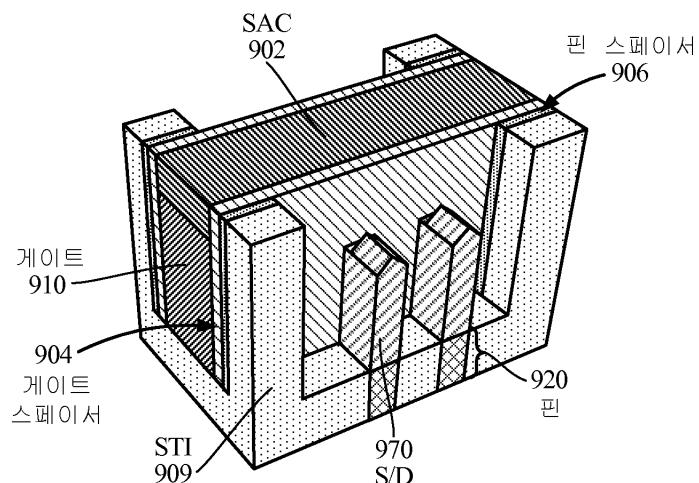

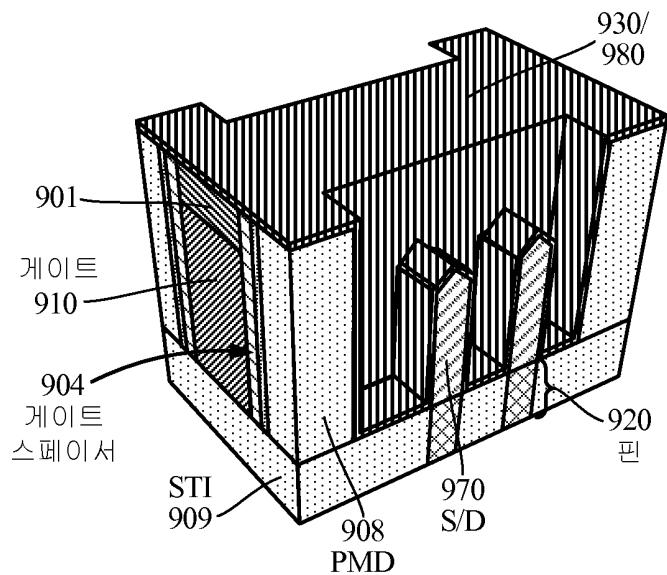

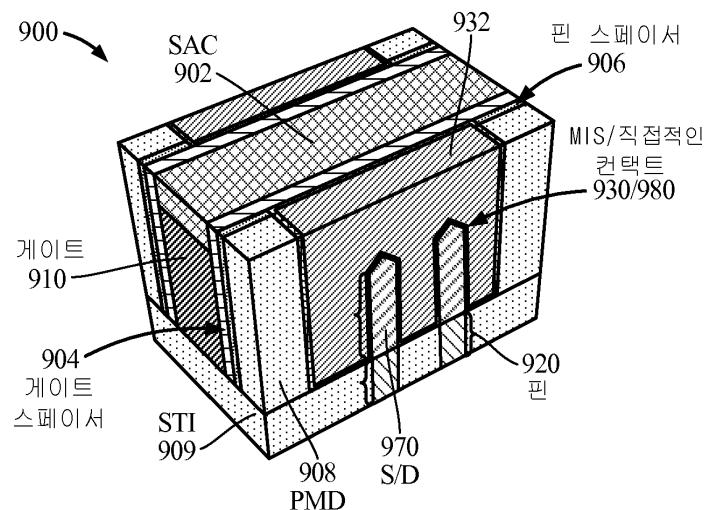

[0019] 도 9a 내지 91은 본 개시내용의 양상에 따른 랩-어라운드 컨택트들을 포함하는 핀-기반 디바이스의 형성을 도시하는 단면도들이다.

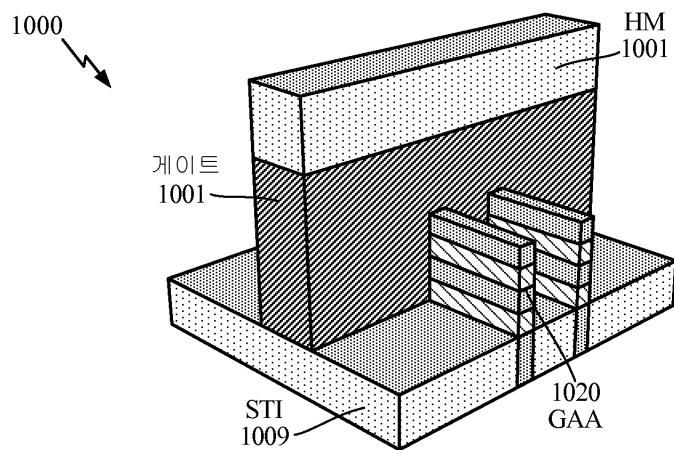

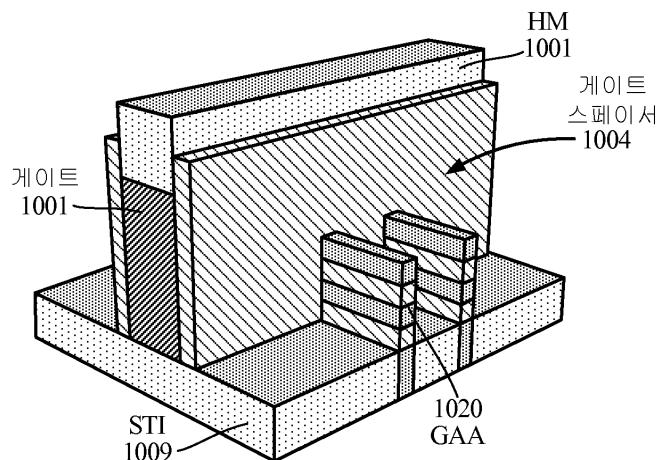

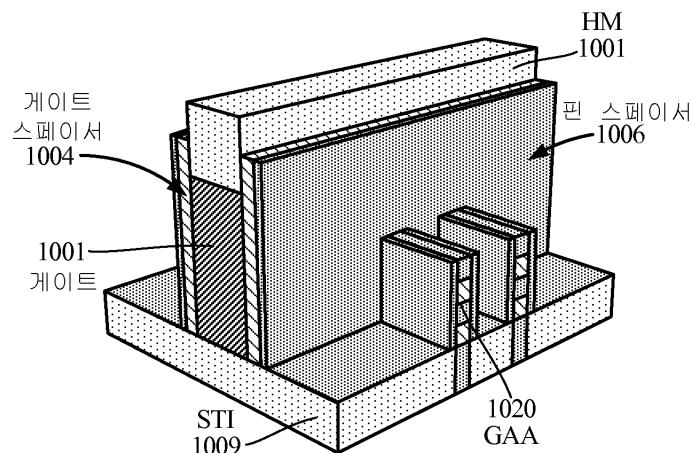

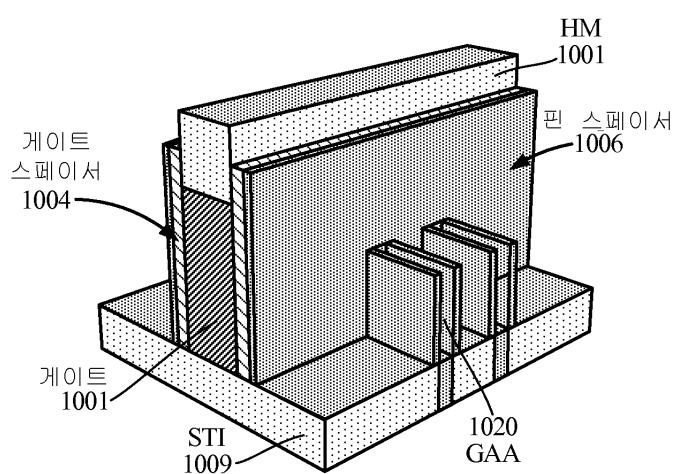

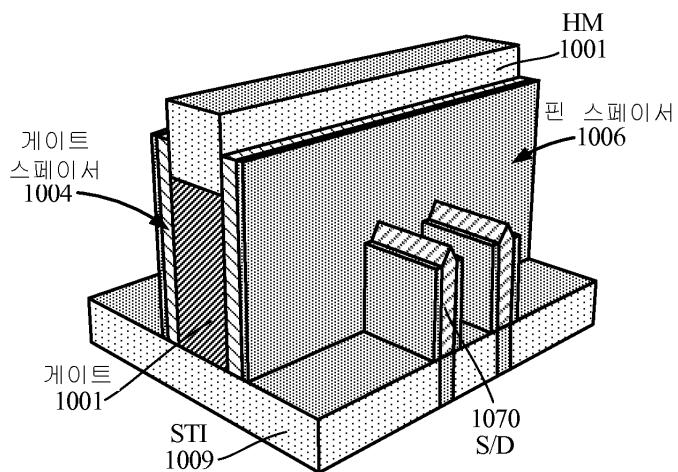

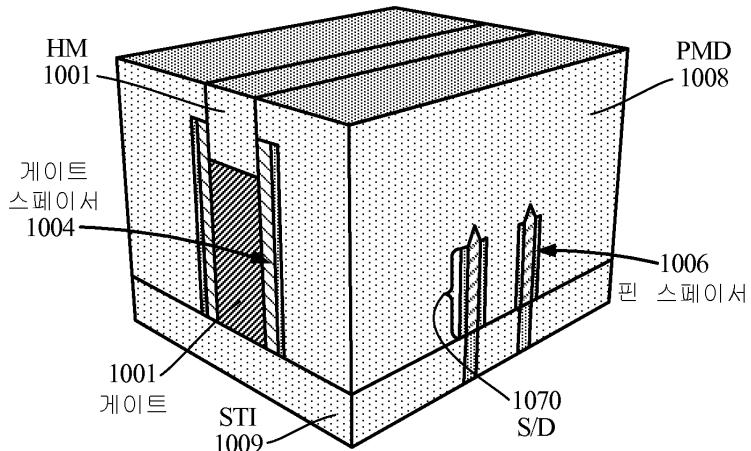

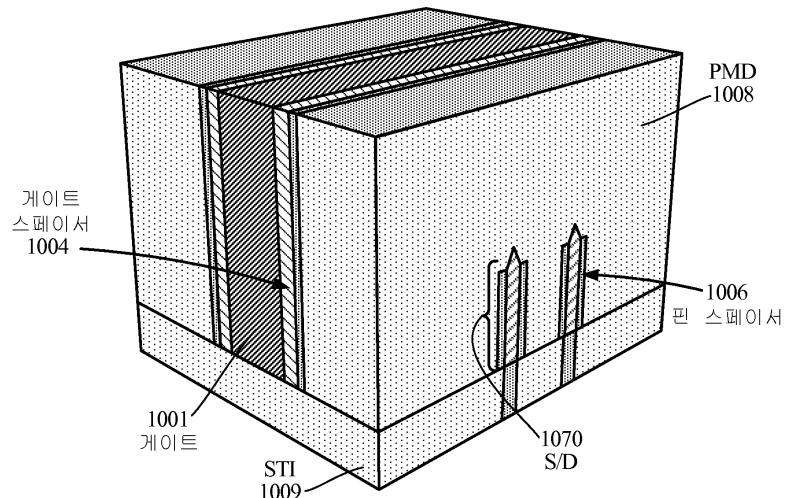

[0020] 도 10a 내지 도 10l은 본 개시내용의 양상들에 따른 랩-어라운드 컨택트들을 포함하는 GAA(gate-all-around) 나노와이어-기반 디바이스의 형성을 도시하는 단면도들이다.

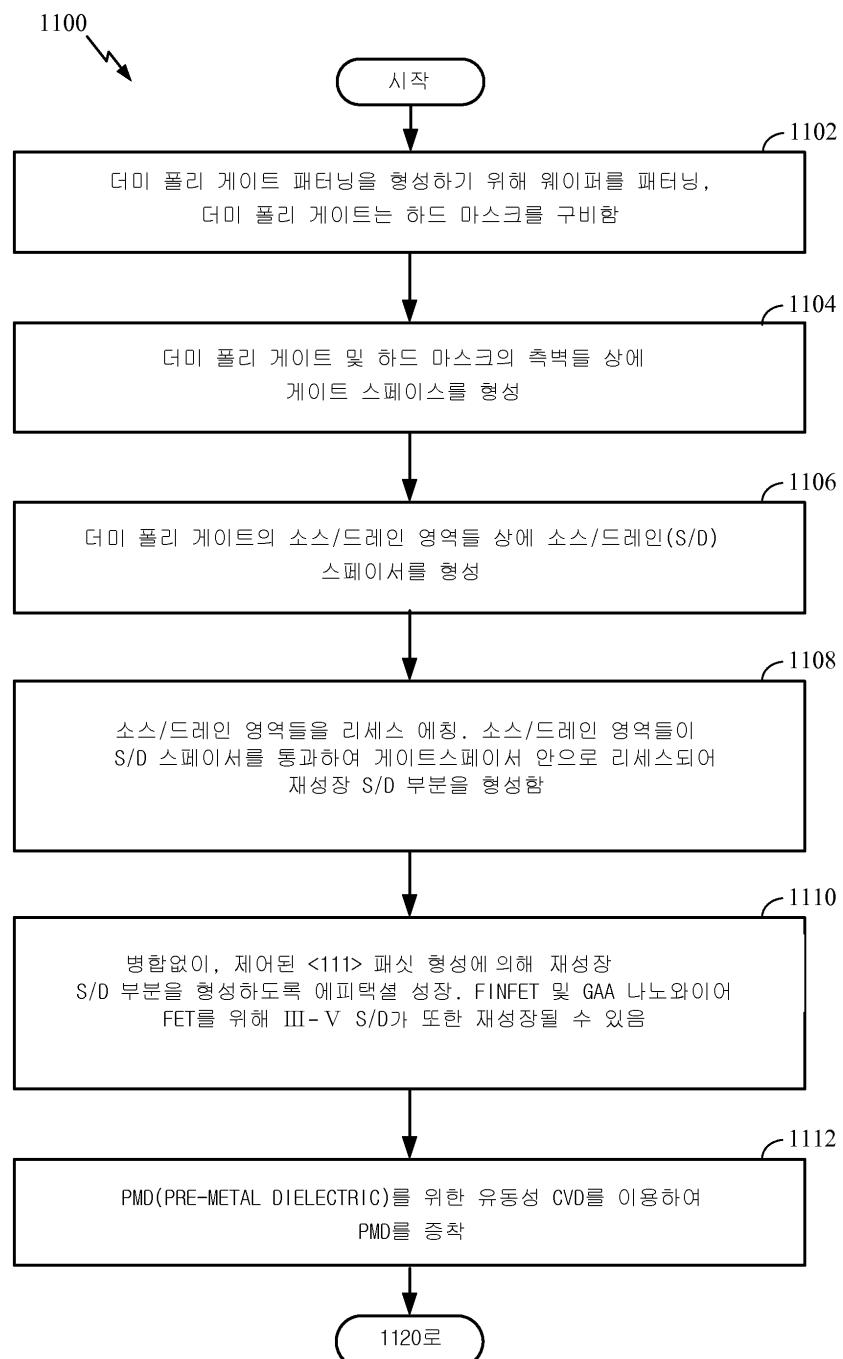

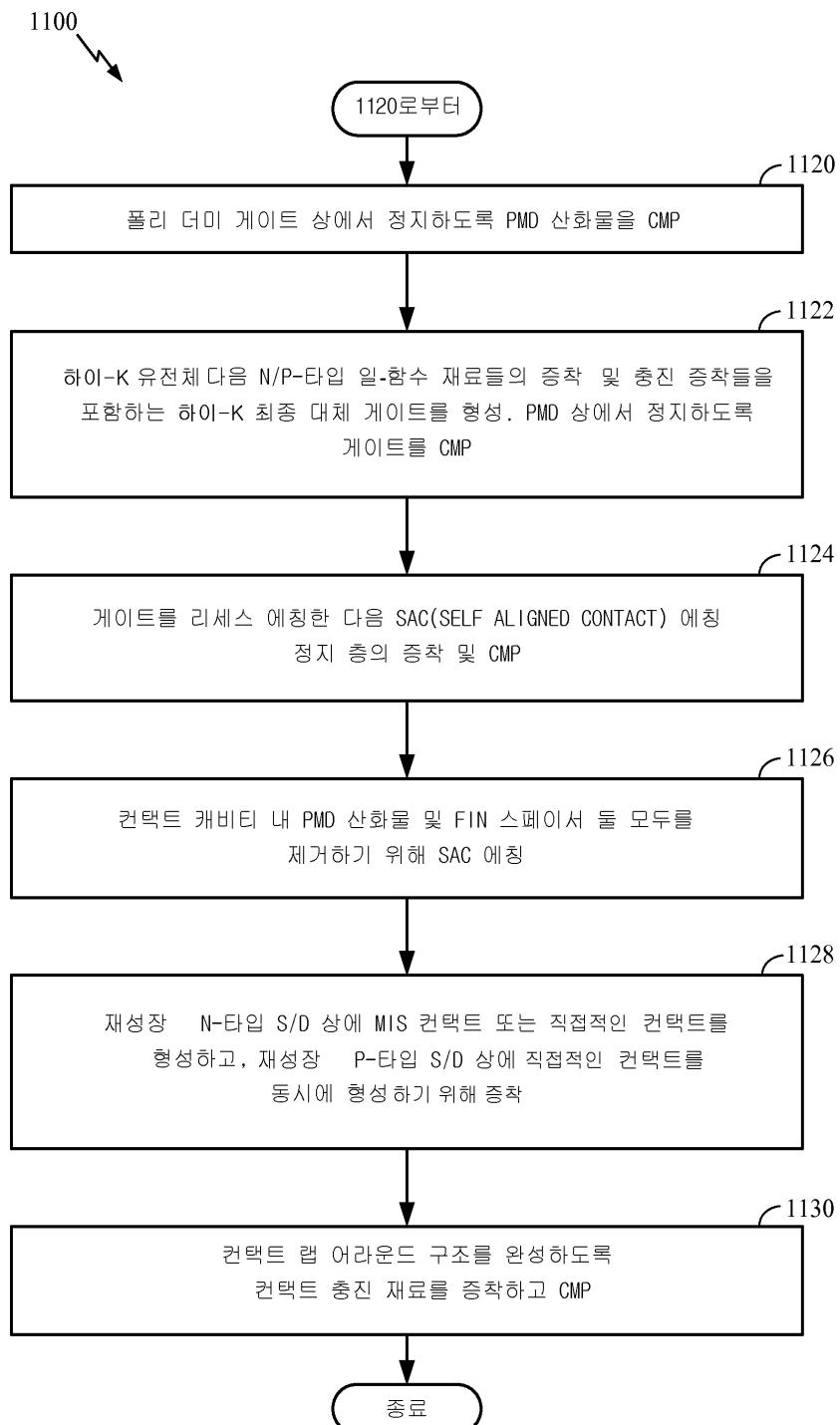

[0021] 도 11a 및 도 11b는 본 개시내용의 양상들에 따른 컨택트 랩 어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법을 도시한다.

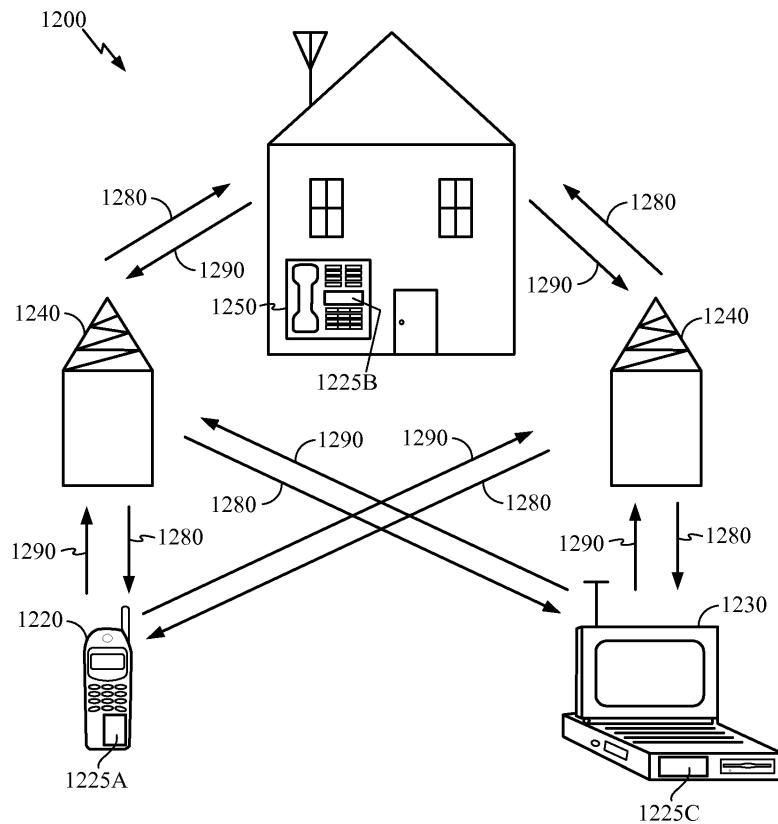

[0022] 도 12는 본 개시내용의 양상들이 유리하게 활용될 수 있는 예시적인 무선 통신 시스템을 도시하는 블록도이다.

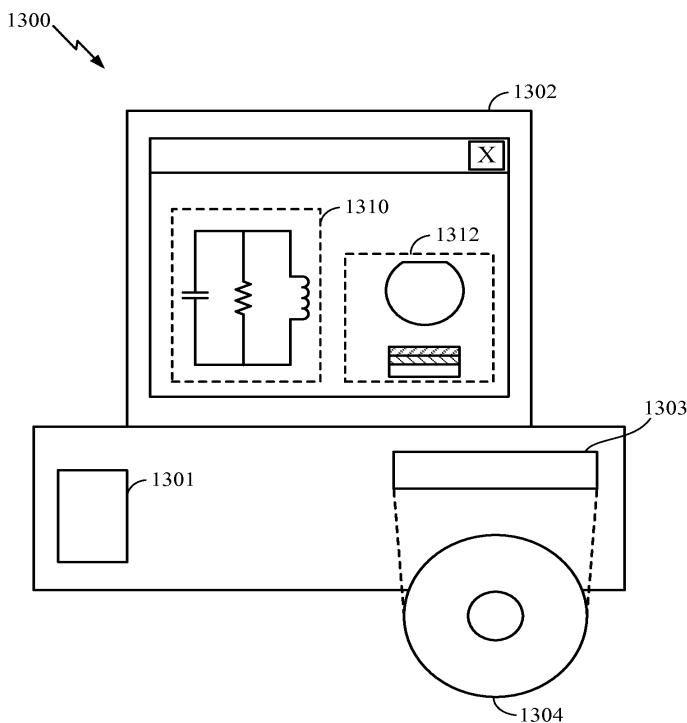

[0023] 도 13은 일 구성에 따른 핀-기반 구조의 회로, 레이아웃, 및 로직 설계를 위해 사용된 설계 워크스테이션을 도시하는 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

[0012]

[0024] 첨부된 도면과 관련하여 후술되는 상세한 설명은 다양한 구성들의 설명을 위한 것이며, 본원에 설명된 개념들이 실시될 수 있는 유일한 구성들을 나타내기 위한 것은 아니다. 상세한 설명은 다양한 개념들의 완전한 이해를 제공하기 위해서 특정 세부사항들을 포함한다. 그러나, 이들 개념들이, 이들 특정 세부 사항들 없이도 실시될 수 있다는 것은 당업자에게 명백할 것이다. 몇몇 예시들에서, 그러한 개념들을 불명료하게 하는 것을 회피하기 위해서, 잘 알려진 구조들 및 컴포넌트들은 블록도 형태로 도시되어 있다. 본원에 설명된 바와 같이, 용어 "및/또는"의 사용은 "포괄적인 또는"을 나타내기 위한 것이며, 용어 "또는"의 사용은 "배타적 또는"을 나타내기 위한 것이다.

[0013]

[0025] 반도체 제조 프로세스들은 종종 3개 파트들: FEOL(front-end-of-line), MOL(middle-of-line), 및 BEOL(back-end-of-line)로 나뉜다. 프론트-엔드-오브-라인 프로세스들은 웨이퍼 준비, 절연, 웰 형성, 게이트 패터닝, 스페이서들, 및 도편트 주입을 포함한다. 미들-오브-라인 프로세스는 게이트 및 단자 컨택트 형성을 포함한다. 그러나, 미들-오브-라인 프로세스의 게이트 및 단자 컨택트 형성은, 특히 리소그래피 패터닝을 위한 제조 플로우에서 점점 더 난제시되는 부분이다. 백-엔드-오브-라인 프로세스들은, 넌-실리사이드(non-silicide)/넌-제미니드(non-geminide) 컨택트를 사용하여 FEOL 디바이스들의 소스/드레인 영역들에 결합하기 위한 상호접속부들 및 유전체 층들을 형성하는 것을 포함한다. 이들 상호접속부들은 PECVD(plasma-enhanced chemical vapor deposition) 증착된 ILD(inter-layer dielectric) 재료들을 사용하여 듀얼 다마신 프로세스로

제조될 수 있다.

[0014] [0026] IC(integrated circuit) 기술이 발전됨에 따라, 디바이스 지오메트리들이 축소되었다. 지오메트리 및 디바이스들 간의 "피치"(간격)는 발전된 로직 기술에서 상당히 축소되었다. 예를 들어, 7 나노미터 로직 기술에서, 핀 피치가 고도로 스케일링되었고(예를 들어, 21 내지 24 나노미터), 컨택트된 게이트 피치 또한 적극적으로 축소되었다(예를 들어, 39 내지 45 나노 미터).

[0015] [0027] 핀-기반 디바이스들은 IC 기술의 상당한 발전을 나타낸다. 핀-기반 디바이스들은 반도체 기판의 표면상의 3-차원 구조들이다. 핀-기반 MOSFET(metal-oxide-semiconductor field-effect transistor)일 수 있는 핀-기반 트랜지스터를 FinFET로 지칭할 수 있다. 나노와이어 FET(nanowire field-effect transistor)는 또한 IC 기술의 상당한 발전을 나타낸다. GAA(gate-all-around) 나노와이어-기반 디바이스는 또한 반도체 기판의 표면상의 3-차원 구조이다. GAA 나노와이어-기반 디바이스는 채널 영역과 컨택트하고 디바이스의 소스 및 드레인 영역들로서 역할을 하는 나노와이어의 도핑 부분들을 포함한다. GAA 나노와이어-기반 디바이스는 또한 MOSFET 디바이스의 예이다.

[0016] [0028] MOSFET 디바이스들의 성능은 채널 길이, 변형 및 외부 저항을 비롯한 수 많은 팩터들의 영향을 받을 수 있다. 외부 저항에 기여하는 하나의 실질적인 팩터는 소스/드레인 영역들과 전도성 층들(예를 들어, 전도성 상호접속부들) 간의 컨택트 저항이다. 컨택트 저항은 지오메트리 및 디바이스들 간의 "피치"(간격)가 급격히 축소되는 발전된 기술 노드들에 대한 디바이스 성능 및 스케일링 리미터이다.

[0017] [0029] 디바이스 지오메트리들이 축소되고 추가 디바이스 구조들이 집적 회로에 추가됨에 따라, 컨택트 저항이 실질적인 디바이스 성능 및 스케일링 리미터가 된다. 예를 들어, 지오메트리 및 디바이스들 간의 "피치"(간격)가 급격히 축소되는 발전된 기술 노드들에서, 컨택트 저항은 적절한 디바이스 동작을 방해할 수 있다. 특히, 발전된 로직 기술, 이를 테면, 7 나노미터 로직 기술을 위한 개선된 디바이스 성능 및 밀도 스케일링의 계속적인 지원을 위해 컨택트 저항의 감소가 요구된다. 그러나, 핀-기반 디바이스들뿐만 아니라 GAA-나노와이어 기반 디바이스들에서, 핀들/게이트들, 및 핀/게이트 피치의 지오메트리는 상당한 컨택트 저항을 발생시킨다.

[0018] [0030] 본 개시내용의 다양한 양상들은 반도체 디바이스들을 위한 컨택트 랩-아라운드 구조를 제조하기 위한 기술들을 제공한다. 컨택트 랩 어라운드 구조의 반도체 제조를 위한 프로세스 흐름은 FEOL(front-end-of-line) 프로세스들, MOL(middle-of-line) 프로세스들, 및 BEOL(back-end-of-line) 프로세스들을 포함할 수 있다. 용어 "층"은 필름을 포함하며, 다르게 언급되지 않는 한 수직 또는 수평 두께를 나타내는 것으로 해석되어서는 안 된다는 것을 이해할 것이다. 본원에 설명된 바와 같이, 용어 "기판"은 다이싱된 웨이퍼의 기판을 지칭할 수 있거나 또는 다이싱되지 않은 웨이퍼의 기판을 지칭할 수 있다. 유사하게, 용어들 웨이퍼 및 다이는, 이러한 상호교환이 택스 크레듈러티(tax credibility)를 갖지 않는다면 상호 교환적으로 사용될 수 있다.

[0019] [0031] 본 개시내용의 양상들은 컨택트 저항을 대폭 감소시키기 위해서 MIS(metal-insulator-semiconductor) 컨택트들 또는 직접적인 컨택트들을 이용하여 고도로 스케일링된 핀들 상에 랩-아라운드 컨택트들을 형성하는 혁신적인 통합 흐름을 포함한다. 본 개시내용의 추가 양상들은 또한 컨택트 저항을 감소시키기 위해서 게이트 GAA(gate-all-around) 나노와이어-기반 디바이스들 및 기타 유사한 반도체 디바이스의 소스/드레인에 MIS 컨택트 또는 직접적인 컨택트를 제공할 수 있다. 랩-아라운드 컨택트들을 포함하는 컨택트 랩 어라운드 구조는 발전된 로직 기술의 축소된 디바이스 지오메트리들, 이를 테면, 7 나노미터 로직 기술 및 이를 능가하는 로직 기술 내에서의 동작을 가능하게 할 수 있다. 컨택트 랩-아라운드 구조는 상당한 컨택트 저항 감소를 제공하면서 기존의 재료들 및 프로세스 능력들을 사용하여 제조될 수 있다.

[0020] [0032] 도 1은 본 개시내용의 양상의 반도체 웨이퍼의 사시도를 도시한다. 웨이퍼(100)는 반도체 웨이퍼일 수 있거나, 웨이퍼(100)의 표면 상에 반도체 재료의 하나 또는 그 초과의 층들을 갖는 기판 재료일 수 있다. 웨이퍼(100)가 반도체 재료인 경우, 웨이퍼(100)는 초크랄스키(Czochralski) 프로세스를 사용하여 시드 결정(seed crystal)으로부터 성장될 수 있으며, 시드 결정은 반도체 재료의 용융 배쓰에 침지되고 천천히 회전되고 배스로부터 제거된다. 그런 다음, 용융된 재료가 결정의 배향으로 시드 결정 상에 결정화된다.

[0021] [0033] 웨이퍼(100)는, 화합물 재료, 이를 테면, 갈륨 비소(GaAs) 또는 질화 갈륨(GaN), 3원 재료, 이를 테면, 인듐 갈륨 비소(InGaAs), 4원 재료들, 또는 다른 반도체 재료들을 위한 기판 재료일 수 있는 임의의 재료일 수 있다. 다수의 재료들이 사실상 결정질일 수 있지만, 다결정질 또는 비정질 재료들이 또한 웨이퍼(100) 용으로 사용될 수 있다.

[0022] [0034] 웨이퍼(100), 또는 웨이퍼(100)에 결합된 층들에는, 웨이퍼(100)를 더욱 전도성이게 만드는 재료들이 공

급될 수 있다. 예를 들어, 제한 없이, 실리콘 웨이퍼는, 전기 전하가 웨이퍼(100)에서 흐르게 하기 위해서 웨이퍼(100)에 첨가되는 인 또는 봉소를 포함할 수 있다. 이들 첨가제들은 도펜트(dopant)들로 지칭되고 웨이퍼(100) 내에 또는 웨이퍼(100)의 부분들 내에 여분의 전하 캐리어들(전자들 또는 정공들)을 제공한다. 여분의 전하 캐리어들이 제공되는 영역들, 어느 타입의 전하 캐리어들이 제공되는지, 그리고 웨이퍼(100) 내의 추가 전하 캐리어들의 양(밀도)을 선택함으로써, 상이한 타입들의 전자 디바이스들이 웨이퍼(100) 내에 또는 웨이퍼(100) 상에 형성될 수 있다.

[0023] [0035] 웨이퍼(100)는 웨이퍼(100)의 결정 배향(crystalline orientation)을 나타내는 배향(102)을 갖는다. 배향(102)은 도 1에 도시된 바와 같이 웨이퍼(100)의 편평한 에지일 수 있거나, 또는 웨이퍼(100)의 결정질 방위를 예시하기 위한 노치 또는 다른 표시일 수 있다. 배향(102)은 웨이퍼(100) 내의 결정 격자의 평면들에 대한 밀러 지수들(Miller Indices)을 나타낼 수 있다.

[0024] [0036] 밀러 지수들은 결정 격자들의 결정학적(crystallographic) 평면들의 표기법 체계를 형성한다. 격자 평면들은, 결정의 평면( $hk\ell$ )에 대해 밀러 지수들인 3개의 정수들  $h$ ,  $k$  및  $\ell$ 로 나타내어질 수 있다. 각각의 지수는 상호 격자 벡터들에 기초하여 방향( $h$ ,  $k$ ,  $\ell$ )에 직교하는 평면을 나타낸다. 정수들은 통상 기약 분수로 기록된다(예를 들어, 이들의 최대 공약수는 1이어야 한다). 밀러 지수 (100)는 방향( $h$ )과 직교하는 평면을 나타내고; 지수 (010)는 방향  $k$ 에 직교하는 평면을 나타내고, 지수 (001)는  $\ell$ 에 직교하는 평면을 나타낸다. 일부 결정들의 경우, 음수들이 사용되고(지수 번호 위에 막대로 기록됨), 질화 갈륨과 같은 일부 결정들의 경우, 상이한 결정학적 평면들을 적절하게 설명하기 위해 4개 이상의 수치들이 활용될 수 있다.

[0025] [0037] 일단 웨이퍼(100)가 원하는 대로 프로세싱되었으면, 웨이퍼(100)는 다이싱 라인들(104)을 따라 분할된다. 다이싱 라인들(104)은, 웨이퍼(100)가 조각나거나 조각들로 분리되어야 하는 위치를 나타낸다. 다이싱 라인들(104)은, 웨이퍼(100) 상에 제조된 다양한 집적 회로들의 윤곽을 정의할 수 있다.

[0026] [0038] 다이싱 라인들(104)이 정의되면, 웨이퍼(100)는 톱질되거나 또는 다른 식으로 조각들로 분리되어 다이(106)를 형성할 수 있다. 다이(106) 각각은 많은 디바이스들을 갖는 집적 회로일 수 있거나 또는 하나의 전자 디바이스일 수 있다. 칩 또는 반도체 칩으로도 지칭될 수 있는 다이(106)의 물리적 크기는, 적어도 부분적으로, 웨이퍼(100)를 특정 크기들로 분리하는 능력뿐만 아니라 다이(106)가 포함하도록 설계되는 개별 디바이스들의 수에 의존한다.

[0027] [0039] 일단 웨이퍼(100)가 하나 또는 그 초과의 다이(106)로 분리되면, 다이(106)가 패키징에 장착되어 다이(106) 상에 제조된 디바이스들 및/또는 집적 회로들에 대한 액세스를 허용할 수 있다. 패키징은, 단일 인-라인 패키징, 듀얼 인-라인 패키징, 마더보드 패키징, 플립-칩 패키징, 인듐 도트/범프 패키징, 또는 다이(106)에 액세스를 제공하는 다른 타입들의 디바이스들을 포함할 수 있다. 다이(106)는 또한 다이(106)를 별도의 패키지에 장착하지 않고 와이어 본딩, 프로브들 또는 다른 연결부들을 통해 직접 액세스될 수 있다.

[0028] [0040] 도 2는 본 개시내용의 양상에 따른 다이(106)의 단면도를 도시한다. 다이(106)에는, 반도체 재료일 수 있고 그리고/또는 전자 디바이스들에 대한 기계적 지지체로서 역할을 할 수 있는 기판(200)이 존재할 수 있다. 기판(200)은, 전자들(N-채널로 지시됨) 또는 정공들(P-채널로 지시됨)의 전하 캐리어들이 기판(200) 전체에 걸쳐 존재하는 도핑된 반도체 기판일 수 있다. 이후, 전하 캐리어 이온들/원자들로 기판(200)을 도핑하는 것은 기판(200)의 전하 운반 능력을 변경할 수 있다.

[0029] [0041] 기판(200)(예를 들어, 반도체 기판) 내부에, FET(field-effect transistor)의 소스 및/또는 드레인일 수 있는 웰들(202 및 204)이 존재할 수 있거나, 웰들(202 및/또는 204)이 FinFET(fin structured FET)의 핀 구조들일 수 있다. 웰들(202 및/또는 204)은 또한, 웰들(202 및/또는 204)의 구조 및 다른 특성을 및 기판(200)의 주위 구조에 따라 다른 디바이스들(예를 들어, 저항기, 캐패시터, 다이오드 또는 다른 전자 디바이스들)일 수 있다.

[0030] [0042] 반도체 기판은 또한 웰(206) 및 웰(208)을 구비할 수 있다. 웰(208)은 완전히 웰(206) 내에 있을 수 있고, 어떤 경우들에는, BJT(bipolar junction transistor)를 형성할 수 있다. 웰(206)은 또한, 다이(106) 내에서 전기장 및/또는 자기장으로부터 웰(208)을 절연시키기 위한 절연 웰로서 사용될 수 있다.

[0031] [0043] 층들(예를 들어, 210 내지 214)이 다이(106)에 추가될 수 있다. 층(210)은, 예를 들어, 웰들(예를 들어, 202-208)을 서로로부터 또는 다이(106) 상의 다른 디바이스들로부터 절연시킬 수 있는 산화물 또는 절연 층일 수 있다. 이러한 경우들에서, 층(210)은 이산화 규소, 중합체, 유전체, 또는 다른 전기적 절연 층일 수 있다. 층(210)은 또한 상호접속 층일 수 있으며, 이 경우 상호접속 층은 구리, 텅스텐, 알루미늄, 합금과 같은

전도성 재료 또는 다른 전도성 또는 금속성 재료들을 포함할 수 있다.

[0032] [0044] 층(212)은 또한, 원하는 디바이스 특징들 및/또는 층들(예를 들어, 210 및 214)의 재료들에 따라 유전체 또는 전도성 층일 수 있다. 층(214)은, 외력들로부터 층들(예를 들어, 210 및 212)뿐만 아니라 웰들(202-208) 및 기판(200)을 보호할 수 있는 캡슐화 층일 수 있다. 예를 들어, 제한 없이, 층(214)은 다이(106)를 기계적 손상으로부터 보호하는 층일 수 있거나, 또는 층(214)은 다이(106)를 전자기 또는 방사선 손상으로부터 보호하는 재료의 층일 수 있다.

[0033] [0045] 다이(106) 상에 설계된 전자 디바이스들은 많은 피처들 또는 구조적 컴포넌트들을 포함할 수 있다. 예를 들어, 다이(106)는 기판(200), 웰들(202-208), 및 원한다면 층들(예를 들어, 210-214) 내로 도편트들을 첨가하는 많은 방법들에 노출될 수 있다. 예를 들어, 제한 없이, 다이(106)는 이온 주입, 확산 프로세스를 통해 결정질 격자 내로 유도되는 도편트 원자들의 증착, 화학 기상 증착, 에피택셜 성장 또는 다른 방법들에 노출될 수 있다. 층들(예를 들어, 210-214)의 선택적 성장, 재료 선택, 및 부분들의 제거를 통해, 그리고 기판(200) 및 웰들(202-208)의 선택적 제거, 재료 선택, 및 도편트 농도를 통해, 많은 상이한 구조들 및 전자 디바이스들이 본 개시내용의 범위 내에서 형성될 수 있다.

[0034] [0046] 또한, 기판(200), 웰들(202-208), 및 층들(예를 들어, 210-214)은 다양한 프로세스들을 통해 선택적으로 제거되거나 또는 추가될 수 있다. 화학 습식 에칭, CMP(chemical mechanical planarization), 플라즈마 에칭, 포토레지스트 마스킹, 다마신 프로세스들, 및 다른 방법들이 본 개시내용의 구조들 및 디바이스들을 생성할 수 있다.

[0035] [0047] 도 3은 본 개시내용의 양상의 MOSFET(metal-oxide-semiconductor field-effect transistor) 디바이스(300)의 단면도를 도시한다. MOSFET 디바이스(300)는 4개의 입력 단자들을 가질 수 있다. 4개의 입력들은 소스(302), 게이트(304), 드레인(306), 및 기판(308)이다. 소스(302) 및 드레인(306)은 기판(308)에서 웰들(202 및 204)로서 제조될 수 있거나, 또는 기판(308) 위의 영역들로서, 또는 다이(106) 상의 다른 층들의 일부로서 제조될 수 있다. 이러한 다른 구조들은 펀 또는 기판(308)의 표면으로부터 돌출되는 다른 구조일 수 있다. 또한, 기판(308)은 다이(106) 상의 기판(200)일 수 있지만, 기판(308)은 또한 기판(200)에 결합되는 층들(예를 들어, 210-214) 중 하나 또는 그 초과의 것일 수 있다.

[0036] [0048] MOSFET의 타입에 따라 단지 하나의 타입의 전하 캐리어(예를 들어, 전자들 또는 정공들)에 의해 전류가 생성되기 때문에, MOSFET 디바이스(300)는 단극성 디바이스이다. MOSFET 디바이스(300)는 소스(302)와 드레인(306) 사이의 채널(310) 내 전하 캐리어들의 양을 제어함으로써 동작한다. 전압(Vsource)(312)은 소스(302)에 인가되고, 전압(Vgate)(314)은 게이트(304)에 인가되고, 전압(Vdrain)(316)은 드레인(306)에 인가된다. 전압(Vsubstrate)(318)이 전압(Vsource)(312), 전압(Vgate)(314) 또는 전압(Vdrain)(316) 중 하나에 결합될 수 있지만, 별개의 전압(Vsubstrate)(318)이 또한 기판(308)에 인가될 수 있다.

[0037] [0049] 채널(310) 내의 전하 캐리어들을 제어하기 위해, 게이트(304)가 전하를 축적할 경우 전압(Vgate)(314)이 채널(310)에 전기장을 생성한다. 게이트(304) 상에 축적되는 반대 전하가 채널(310) 내에 축적되기 시작한다. 게이트 절연체(320)는 소스(302), 드레인(306), 및 채널(310)로부터 게이트(304) 상에 축적되는 전하들을 절연시킨다. 게이트 절연체(320)가 사이에 있는, 게이트(304) 및 채널(310)은 캐페시터를 생성하고, 전압(Vgate)(314)이 증가함에 따라, 이 캐페시터의 하나의 플레이트로서 역할을 하는 게이트(304) 상에 전하 캐리어들이 축적되기 시작한다. 게이트(304) 상의 전하들의 이러한 축적은 반대 전하 캐리어들을 채널(310) 안으로 끌어 당긴다. 결국, 충분한 전하 캐리어들이 채널(310)에 축적되어 소스(302)와 드레인(306) 사이에 전기 전도성 경로를 제공한다. 이 상태가 FET의 채널 개방으로 지칭될 수 있다.

[0038] [0050] 전압(Vsource)(312) 및 전압(Vdrain)(316)을, 그리고 전압(Vgate)(314)에 대한 이들의 관계를 변경함으로써, 채널(310)을 개방하는, 게이트(304)에 인가되는 전압의 양이 변할 수 있다. 예를 들어, 전압(Vsource)(312)은 일반적으로 전압(Vdrain)(316)의 전위보다 더 높은 전위이다. 전압(Vsource)(312)과 전압(Vdrain)(316) 사이의 전압 차가 더 커지게 하는 것은 채널(310)을 개방하는데 사용되는 전압(Vgate)(314)의 양을 변경시킬 것이다. 또한, 더 큰 전압 차는 채널(310)을 통해 전하 캐리어들을 이동시키는 기전력의 양을 변경시킬 것이며, 더 많은 전류가 채널(310)을 통해 생성된다.

[0039] [0051] 게이트 절연체(320) 재료는 실리콘 산화물일 수 있거나, 또는 실리콘 산화물과는 상이한 유전 상수(k)를 갖는 유전체 또는 다른 재료일 수 있다. 또한, 게이트 절연체(320)는 재료들의 조합 또는 재료들의 상이한 층들일 수 있다. 예를 들어, 게이트 절연체(320)는 알루미늄 산화물, 하프늄 산화물, 하프늄 산화물 질화물, 지

르코늄 산화물, 또는 이들 재료들의 라미네이트들 및/또는 합금들일 수 있다. 게이트 절연체(320)를 위한 다른 재료들이 본 개시내용의 범위를 벗어나지 않고 사용될 수 있다.

[0040] [0052] 게이트 절연체(320)를 위한 재료 및 게이트 절연체(320)의 두께(예를 들어, 게이트(304)와 채널(310) 사이의 거리)를 변경시킴으로써, 채널(310)을 개방하기 위한 게이트(304) 상의 전하량이 변할 수 있다. MOSFET 디바이스(300)의 단자들을 도시하는 기호(322)가 또한 도시되었다. (채널(310)에서 전하 캐리어들로서 전자들을 사용하는) N-채널 MOSFET들의 경우, 게이트(304) 단자의 반대쪽을 향하는 화살표가 기호(322)의 기판(308) 단자에 적용된다. (채널(310)에서 전하 캐리어들로서 정공들을 사용하는) p-타입 MOSFET들의 경우, 게이트(304) 단자를 향하는 화살표가 기호(322)의 기판(308) 단자에 적용된다.

[0041] [0053] 게이트(304)는 또한 상이한 재료들로 이루어질 수 있다. 일부 설계들에서, 게이트(304)는, 전도성 형태의 실리콘인, 폴리실리콘 또는 폴리로도 지칭되는 다결정 실리콘으로 이루어진다. 본원에서 "폴리" 또는 "폴리실리콘"으로 지칭되지만, 금속들, 합금들 또는 다른 전기 전도성 재료들인 본 개시내용에서 설명된 바와 같은 게이트(304)에 적합한 재료들로 고려된다.

[0042] [0054] 일부 MOSFET 설계들에서, 하이-K 값 재료가 게이트 절연체(320)에서 바람직 할 수 있으며, 이러한 설계들에서, 다른 전도성 재료들이 활용될 수 있다. 예를 들어, 제한 없이, "하이-K 금속 게이트" 설계는 게이트(304) 단자 용으로 구리와 같은 금속을 활용할 수 있다. "금속"으로 지칭되었지만, 다결정성 재료들, 합금들, 또는 다른 전기 전도성 재료들이 본 개시내용에 설명된 바와 같은 게이트(304)에 적절한 재료들인 것으로 간주된다.

[0043] [0055] MOSFET 디바이스(300)에 대한 상호접속을 위해, 또는 다이(106)(예를 들어, 반도체) 내의 다른 디바이스들에 대한 상호접속을 위해, 상호접속 트레이스들 또는 층들이 사용된다. 이들 상호접속 트레이스들은, 층들(예를 들어, 210-214) 중 하나 또는 그 초과의 것에 있을 수 있거나, 또는 다이(106)의 다른 층들에 있을 수 있다.

[0044] [0056] 도 4는 본 개시내용의 양상에 따른 트랜지스터를 도시한다. FinFET(fin-structured FET)(400)는 도 3과 관련하여 설명된 MOSFET 디바이스(300)와 유사한 방식으로 동작한다. 그러나, FinFET(400) 내의 핀(410)이 성장되거나 다른 식으로 기판(308)에 결합된다. 기판(308)은, 예를 들어, 산화물 층, 질화물 층, 금속 산화물 층 또는 실리콘 층으로 이루어진 반도체 기판 또는 다른 유사한 지지 층일 수 있다. 핀(410)은 소스(302) 및 드레인(306)을 포함한다. 게이트(304)가 게이트 절연체(320)를 통해 핀(410) 상에 그리고 기판(308) 상에 배치된다. 높이(Hfin), 너비(Wfin) 및 길이(Lfin)는 핀의 치수들을 나타낸다. FinFET 구조에서, FinFET(400)의 물리적 크기는 도 3에 도시된 MOSFET 디바이스(300) 구조보다 더 작을 수 있다. 이러한 물리적 크기의 축소는 다이(106) 상에 단위 면적당 더 많은 디바이스들을 허용한다.

#### 컨택트 랩 어라운드 구조

[0045] [0057] 핀-기반 디바이스들은 IC 기술의 상당한 발전을 나타낸다. 핀-기반 디바이스들은 반도체 기판의 표면상의 3-차원 구조들이다. 핀-기반 MOSFET(metal-oxide-semiconductor field-effect transistor)일 수 있는 핀-기반 트랜지스터를 FinFET로 지칭할 수 있다. 나노와이어 FET(nanowire field-effect transistor)는 또한 IC 기술의 상당한 발전을 나타낸다. GAA(gate-all-around) 나노와이어-기반 디바이스는 또한 반도체 기판의 표면상의 3-차원 구조이다. GAA 나노와이어-기반 디바이스는 채널 영역과 컨택트하고 디바이스의 소스 및 드레인 영역들로서 역할을 하는 나노와이어의 도핑 부분들을 포함한다. GAA 나노와이어-기반 디바이스는 또한 MOSFET 디바이스의 예이다. 일 구성에서, 게이트-올-어라운드(gate-all-around) 나노와이어 FET(field-effect transistor)가 설명된다.

[0046] [0058] MOSFET 디바이스들의 성능은 채널 길이, 변형 및 외부 저항을 비롯한 수 많은 팩터들의 영향을 받을 수 있다. 외부 저항에 기여하는 하나의 실질적인 팩터는 소스/드레인 영역들과 전도성 층들 간의 컨택트 저항이다. 컨택트 저항은, 지오메트리 및 디바이스들 간의 "피치"(간격)가 급격히 축소되는 발전된 기술 노드들에 대한 디바이스 성능 및 스케일링 리미터이다.

[0047] [0059] 디바이스 지오메트리들이 축소되고 추가 디바이스 구조들이 집적 회로에 추가됨에 따라, 컨택트 저항이 실질적인 디바이스 성능 및 스케일링 리미터가 된다. 예를 들어, 지오메트리 및 디바이스들 간의 "피치"(간격)가 급격히 축소되는 발전된 기술 노드들에서, 컨택트 저항은 적절한 디바이스 동작을 방해할 수 있다. 특히, 발전된 로직 기술, 이를 테면, 7 나노미터 로직 기술 및 이를 능가하는 로직 기술을 위한 개선된 디바이스 성능 및 밀도 스케일링을 계속적인 지원하기 위해, 감소된 컨택트 저항이 요구된다. 그러나, 핀-기반 디바

이스들뿐만 아니라 GAA-나노와이어 기반 디바이스들에서, 핀들/게이트들, 및 핀/게이트 피치의 지오메트리는 상당한 컨택트 저항을 발생시킨다.

[0049] [0060] 본 개시내용의 다양한 양상들은 반도체 디바이스들을 위한 컨택트 랩-어라운드 구조를 제조하기 위한 기술들을 제공한다. 컨택트 랩 어라운드 구조의 반도체 제조를 위한 프로세스 흐름은 FEOL(front-end-of-line) 프로세스들, MOL(middle-of-line) 프로세스들, 및 BEOL(back-end-of-line) 프로세스들을 포함할 수 있다. 용어 "층"은 필름을 포함하며, 다르게 언급되지 않는 한 수직 또는 수평 두께를 나타내는 것으로 해석되어서는 안 된다는 것을 이해할 것이다. 본원에 설명된 바와 같이, 용어 "기판"은 다이싱된 웨이퍼의 기판을 지칭할 수 있거나 또는 다이싱되지 않은 웨이퍼의 기판을 지칭할 수 있다. 유사하게, 용어들 웨이퍼 및 다이는, 이러한 상호교환이 택스 크레더러티(tax credibility)를 갖지 않는다면 상호 교환적으로 사용될 수 있다.

[0050] [0061] 본 개시내용의 양상들은 컨택트 저항을 대폭 감소시키기 위해서 MIS(metal-insulator-semiconductor) 컨택트들 또는 직접적인 컨택트들을 이용하여 고도로 스케일링된 핀들 상에 랩-어라운드 컨택트들을 형성하는 혁신적인 통합 흐름을 포함한다. 본 개시내용의 추가 양상들은 또한 컨택트 저항을 감소시키기 위해서 GAA(gate-all-around) 나노와이어-기반 디바이스들 및 기타 유사한 반도체 디바이스들의 소스/드레인에 MIS 컨택트 또는 직접적인 컨택트를 제공할 수 있다. 랩-어라운드 컨택트들을 포함하는 컨택트 랩 어라운드 구조들은 발전된 로직 기술의 축소된 디바이스 지오메트리들 내에서의 동작을 가능하게 할 수 있다. 컨택트 랩-어라운드 구조는 상당한 컨택트 저항 감소를 제공하면서, 기준의 재료들 및 프로세스 능력들을 사용하여 제조될 수 있다.

[0051] [0062] 도 5a는 제 1 종래의 컨택트 구조(510)를 포함하는 핀-기반 구조(500)의 단면도를 도시한다. 핀-기반 구조(500)는 접적 회로 내에서 사용될 수 있다. 핀들(520)이 기판(미도시)에 의해 지지되고 특정 타입의 전하 캐리어로 도핑될 수 있으므로, 핀들(520)은 전도성이다. 기판은 반도체 기판, SOI(silicon on insulator) 기판, BOX(buried oxide) 층 등일 수 있다. SOI 기판은 완전히 공핍될 수 있다. 핀들(520)은, 최종 디바이스에서 요구되는 전하 캐리어의 타입에 의존하여 n-타입 도편트 또는 p-타입 도편트로 도핑될 수 있다.

[0052] [0063] 핀들(520)에 대한 제 1 종래의 컨택트 구조(510)는 완전 병합된 에피택셜 성장 또는 다른 유사한 프로세스를 사용하여 제조된다. 완전 병합된 에피택셜 성장에 의해 제공되는 제 1 종래의 컨택트 구조(510)의 CA(contact area)가 다음과 같이 결정될 수 있다 :

$$CA = CD * [(NF - 1) * FP + FP / \cos(55^\circ)] \quad (1)$$

[0054] 여기서, CD는 임계 치수이고, NF는 핀들의 수이고, FP는 제 1 종래의 컨택트 구조(510)에 대한 컨택트 표면 영역 계산을 가능하게 하는 핀 피치이다.

[0055] [0064] 도 5b는 핀들(570)에 제 2 종래의 컨택트 구조(560)를 포함하는 핀-기반 구조(550)의 단면도를 도시한다. 핀-기반 구조(550)는 또한 접적 회로 내에서 사용될 수 있다. 핀들(570)이 기판(미도시)에 의해 지지되고 특정 타입의 전하 캐리어로 도핑될 수 있으므로, 핀들(570)은 전도성이다. 핀들(570)은 또한, 최종 디바이스를 위해 지정되는 전하 캐리어의 타입에 의존하여 n-타입 도편트 또는 p-타입 도편트로 도핑될 수 있다.

[0056] [0065] 제 2 종래의 컨택트 구조(560)는 부분적으로 컨택트된 에피택셜 성장 또는 다른 유사한 프로세스를 사용하여 제조된다. 이 어레이인지먼트에서, 제 2 종래의 컨택트 구조(560)는  $70^\circ$  각도로 제조된다. 부분적으로 컨택트된 에피택셜 성장에 의해 제공되는 제 2 종래의 컨택트 구조(560)의 CA(contact area)가 다음과 같이 결정될 수 있다 :

$$CA = CD * FP / \cos(55^\circ) * NF \quad (2)$$

[0058] 여기서, CD는 임계 치수이고, NF는 핀들의 수이고, FP는 제 2 종래의 컨택트 구조(560)에 대한 컨택트 표면 영역 계산을 가능하게 하는 핀 피치이다.

[0059] [0066] 도 6은 본 개시내용의 양상에 따른 랩-어라운드 컨택트(610)를 포함하는 핀-기반 구조(600)의 단면도를 도시한다. 핀-기반 구조(600)는 또한 접적 회로 내에서 사용될 수 있다. 핀들(620)이 기판(미도시)에 의해 지지되고, 특정 타입의 전하 캐리어로 도핑될 수 있으므로 핀들(620)은 전도성이다. 핀들(620)은, 최종 디바이스에서 요구되는 전하 캐리어의 타입에 의존하여 n-형 도편트 또는 p-형 도편트로 도핑될 수 있다.

[0060] [0067] 랩-어라운드 컨택트(610)는, 성장 또는 다른 유사한 프로세스에 의존하기보다는, 예를 들어, MIS(metal-insulator-semiconductor) 컨택트 또는 직접적인 컨택트를 사용하여 제조된다. MIS 컨택트 또는 직접적인 컨택

트에 의해 제공되는 랩-어라운드 컨택트(610)의 컨택트 영역은 다음과 같이 결정될 수 있다:

$$CA = CD * (2 * FH + FW / \cos(55^\circ)) * NF \quad (3)$$

[0061] 여기서, CD는 임계 치수이고, NF는 핀들의 수이고, FH는 핀 높이이고, FW는 핀 폭이고, FP는 랩-어라운드 컨택트(610)에 대한 컨택트 표면 영역 계산을 가능하게 하는 핀 피치이다.

[0062] 예를 들어, 7 나노미터 로직 기술에서, CD=14 나노미터, FP=24 나노미터, FH=35 나노미터, 및 NF = 3이다. 이러한 값들에 기초하여, 제 1 종래의 컨택트 구조(510)에 대한 컨택트 표면 영역은 식(1)에 따라 계산될 수 있고, 이에 따라  $CD=14 * [(3-1) * 24 + 24 / 0.57] = 14 * 90 = >x1.00$ 이다. 이러한 값들에 기초하여, 제 2 종래의 컨택트 구조(560)에 대한 컨택트 표면 영역은 식(2)에 따라 계산될 수 있고, 이에 따라  $CD=14 * 24 / 0.57 * 3 = 14 * 126 = >x1.40$ 이다. 이를 동일한 값을 사용하여, 랩-어라운드 컨택트(610)에 대한 컨택트 표면 영역은 식(3)에 따라 계산될 수 있고, 이에 따라  $CD=14 * (2 * 35 + 6 / 0.57) * 3 = 14 * 241 = >x2.68$ 이다. FH=60 나노미터를 가정하면, 랩-어라운드 컨택트(610)에 대한 컨택트 표면 영역은 제 1 종래의 컨택트 구조(510)에 대한 컨택트 표면 영역보다  $x4.35$  더 크고, 제 2 종래의 컨택트 구조(560)에 대한 컨택트 표면 영역보다  $x3.11$  더 크며, 이는 컨택트 저항을 약 50퍼센트(50%) 만큼 감소시킬 수 있다.

[0063] [0069] 도 7a 및 도 7b는 본 개시내용의 양상에 따른 MIS 컨택트(730) 또는 직접적인 컨택트(780)를 포함하는 CMOS(complementary metal oxide semiconductor) 디바이스들의 단면도들을 도시한다. 도 7a에서, NMOS((n-type metal oxide semiconductor) 디바이스(700))는 핀(720)을 둘러싸는 NMOS(n-type metal oxide semiconductor) 영역(740)을 포함한다. n-타입 영역들(740)은, n-타입 영역들(740)을 제공하기 위해서 인 도핑 실리콘(Si-P)으로 구성될 수 있다. 게이트(710)가 핀(720) 상에 형성된다. 게이트(710)는 하이-K 층(716), n-타입 일 함수(work function) 층(714) 및 전도성 층(712)(예를 들어, 텅스텐(W) 또는 코발트(Co))을 포함한다. 자기-정렬 컨택트(702)가 게이트(710) 상에 배치되고 게이트 스페이서(704)가 게이트(710)의 측벽들 상에 배치된다.

[0064] [0070] 본 개시내용의 양상은 NMOS 디바이스(700)의 소스/드레인 영역들에 대한 낸-실리사이드 컨택트를 고려한다. 이 어레인지먼트에서, MIS(metal-insulator-semiconductor) 컨택트(730)는 NMOS 디바이스(700)의 소스/드레인 영역들(예를 들어, n-타입 영역들(740)) 상에 증착될 수 있다. MIS 컨택트(730)는 n-타입 영역들(740) 상에 제 1 층(736)(예를 들어, 티타늄 산화물 층( $TiO_2$ ))을 포함할 수 있다. MIS 컨택트(730)는 제 1 층(736) 상에 그리고 전도성 재료(732)의 측벽들 상에 제 2 층(734)(예를 들어, 티타늄(Ti))을 포함할 수 있다.

[0065] [0071] NMOS 디바이스(700)의 n-타입 영역들(740)(예를 들어, 소스/드레인)의 경우, CVD(chemical vapor deposition) 또는 PVD(physical vapor deposition)의 제 2 층(734)(예를 들어, 티타늄 층(Ti))이 제 1 층(736)(예를 들어, 티타늄 산화물( $TiO_2$ ))과 반응하여 n-타입 영역들(740)의 인도핑 실리콘 재료 상에 MIS 컨택트(730)의 저 저항률  $Ti/TiO_{2-x}$ 를 형성할 것이다. 대안으로, n-타입 영역들(740)의 인도핑 실리콘 재료 상의 직접적인 컨택트(예를 들어, 티타늄(Ti))는 또한 옵션이다. MIS 컨택트(730)(또는 직접적인 컨택트)에 의해 제공되는 컨택트 저항률은, n-타입 영역들(740)의 인도핑 실리콘 재료 상에 증착될 경우  $7E-9 \text{ Ohm-cm}^3$ (ohms per cubic centimeter)의 범위 내에 있다.

[0066] [0072] 도 7b에서, p-타입 CMOS 디바이스(PMOS 디바이스(750))는 핀(720)을 둘러싸는 PMOS(p-type metal oxide semiconductor) 영역(790)을 포함한다. p-타입 영역들(790)은, p-타입 영역들(790)을 제공하기 위해서 붕소 도핑 실리콘 게르마늄(SiGe-B)으로 구성될 수 있다. 게이트(760)가 핀(770) 상에 형성된다. 게이트(760)는 하이-K 층(766), p-타입 일 함수 층(764) 및 전도성 층(762)(예를 들어, 텅스텐(W))을 포함한다. 자기-정렬 컨택트(752)가 게이트(760) 상에 배치되고 게이트 스페이서(754)가 게이트(760)의 측벽들 상에 배치된다.

[0067] [0073] 본 개시내용의 양상은 NMOS 디바이스(750)의 소스/드레인 영역들에 낸-제미나이드 컨택트를 고려한다. 이 어레인지먼트에서, 직접적인 컨택트(780)가 PMOS 디바이스(750)의 소스/드레인 영역들(예를 들어, p-타입 영역들(790)) 상에 증착될 수 있다. 직접적인 컨택트(780)는 p-타입 영역들(790) 상에 그리고 전도성 재료(782)의 측벽들 상에 제 1 층(784)(예를 들어, 티타늄(Ti))을 포함할 수 있다. 직접적인 컨택트(780)에 의해 제공되는 컨택트 저항률은, p-타입 영역들(790)의 붕소 도핑 게르마늄 재료 상에 증착될 경우  $2E-8 \text{ Ohm-cm}^3$ (ohms per cubic centimeter)의 범위 내에 있다.

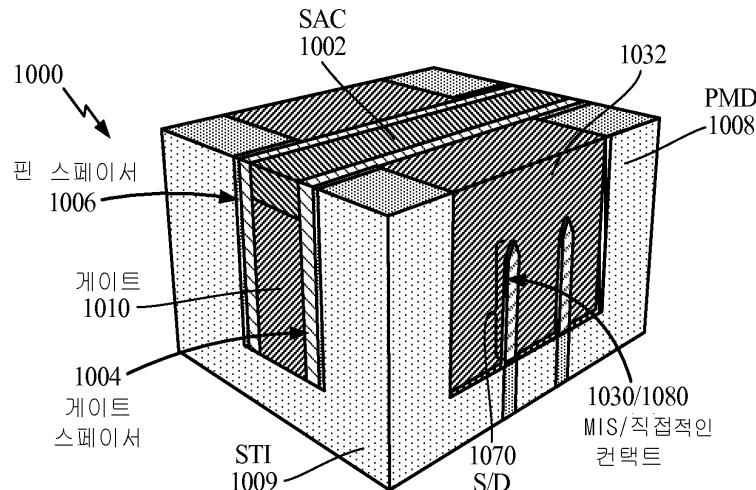

[0068] [0074] 도 8은 본 개시내용의 양상에 따른 컨택트 랩-어라운드 구조를 포함하는 핀-기반 디바이스(800)의 단면도를 도시한다. 대표적으로, 핀-기반 디바이스(800)는 베이스 핀-부분(820)을 둘러싸는 STI(shallow trench

isolation) 영역(809)을 포함한다. 베이스 핀-부분(820)은 실리콘, 게르마늄, 실리콘 게르마늄, 인듐 인산염 또는 다른 유사한 반도체 재료일 수 있다. 재성장 핀-부분(870)은, 예를 들어, 핀들을 병합하지 않고, 제어된 (111) 밀러 지수 패싯 형성을 이용하는 에피택셜 성장에 의해 베이스 핀-부분(820) 상에 형성된다. 재성장 핀-부분(870)은 핀-기반 디바이스(800)의 소스/드레인으로서 동작한다. n-타입인 핀-기반 디바이스(800)(예를 들어, NFET)의 경우, 재성장 핀-부분(870)은 인-도핑 실리콘(SiP), 탄소 인 도핑 실리콘(SiCP), 인 도핑 실리콘 게르마늄(SiGeP), 인 도핑 게르마늄(GeP), 또는 다른 유사한 3/5(III/V)족 재료로 구성된다. p-타입인 핀-기반 디바이스(800)(예를 들어, PFET)의 경우, 재성장 핀-부분(870)은 붕소 도핑 실리콘 게르마늄(SiGeB), 붕소 도핑 게르마늄(GeB), 또는 다른 유사한 도핑 재료로 구성된다.

[0070] [0075] 이 아래인지먼트에서, MIS 컨택트(830) 또는 직접적인 컨택트(880)는 핀-기반 디바이스(800)의 재성장 핀-부분(870)(소스/드레인)을 둘러싼다. 컨택트 충진 재료(832)(예를 들어, 텅스텐(W) 또는 코발트(Co))가, 재성장 핀-부분(870)을 둘러싸는 MIS 컨택트(830) 또는 직접적인 컨택트(880)의 재료 상에 배치된다. 이외에도, 산화물(예를 들어, PMD(pre-metal dielectric)(808))이 MIS 컨택트(830) 또는 직접적인 컨택트(880) 및 핀 스페이서(806)의 재료의 측벽들 상에 있다. 핀-기반 디바이스(800)는 또한 게이트(810) 상에 SAC(self-aligned contact)(802)(예를 들어, 질화물계 SAC)를 포함하는 게이트(810) 및 게이트(810)의 측벽들 상의 게이트 스페이서(804)(예를 들어, 질화물계 로우-K 게이트 스페이서)를 포함한다. SAC(802)는 또한 게이트(810)를 제조하기 위해 에칭 정지부를 제공할 수 있다. 핀-기반 디바이스(800)는 도 9a 내지 도 91에 도시된 바와 같이 형성될 수 있다. GAA(gate-all-around) 나노와이어-기반 디바이스(1000)가, 도 9a 내지 도 91에 대응하는 도 10a 내지 101에 도시된 바와 같이 형성될 수 있다. 도 9a 내지 91에 대응하는 도 10a 내지 도 101에 도시된 바와 같은 GAA 나노와이어-기반 디바이스(1000)를 형성하기 위한 프로세스가 도 11a 및 11b를 참조하여 설명된다.

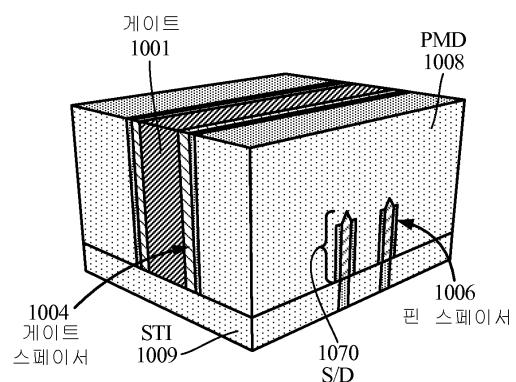

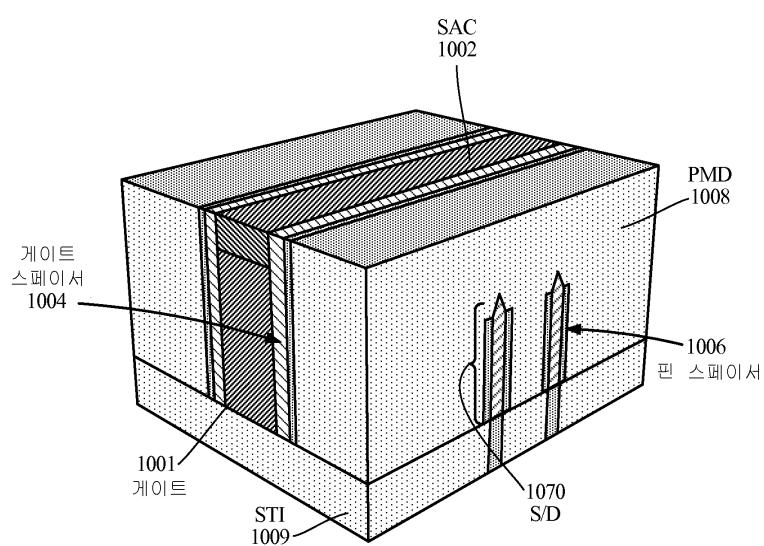

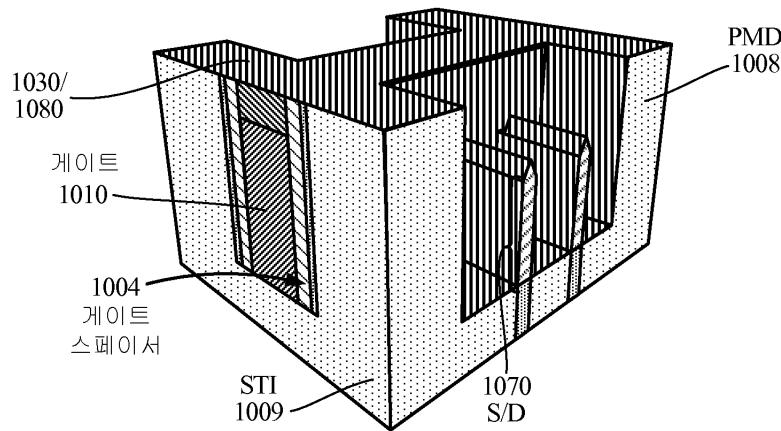

[0071] [0076] 도 11a는 본 개시내용의 양상들에 따른 컨택트 랩 어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 방법(1100)을 도시한다. 도 11a 및 11b에 설명된 프로세스는 도 9a 내지 91에 도시된 바와 같은 핀-기반 디바이스(900) 또는 도 9a 내지 도 91에 대응하는 도 10a 내지 도 101에 도시된 바와 같은 GAA 나노와이어-기반 디바이스(1000)의 형성을 가능하게 한다. 블록(1102)에서, 더미 폴리 게이트(예를 들어, 실리콘(Si))를 형성하기 위해 더미 폴리 게이트 패터닝 프로세스가 완료된 후의 인입 웨이퍼가 도시된다. 예를 들어, 도 9a/10a에 도시된 바와 같이, 하드 마스크(901/1001)(예를 들어, 산화물)가 게이트(910/1010)의 패터닝 동안 게이트(910/1010) 상에 배열된다. 게이트(910/1010)는 기판에 의해 지지될 수 있는 STI(shallow trench isolation) 영역(909/1009)에 의해 지지된다. 게이트(910/1010)의 소스/드레인 영역들은, 도 9e/도 10e에 도시된 바와 같이, 재성장 소스/드레인들(970/1070)에 의해 제공될 것이다. 이외에도, 더미 폴리 게이트는 또한 도 91/101에 도시된 바와 같이, 게이트(910/1010)를 제공하도록 대체된다.

[0072] [0077] 다시 도 11a를 참조하면, 블록(1104)에서, 게이트 스페이서(예를 들어, 질화물계 로우-K 게이트 스페이서)가 더미 게이트와 하드 마스크의 측벽들 상에 형성된다. 예를 들어, 도 9b/도 10b에 도시된 바와 같이, 게이트 스페이서(904/1004)가 게이트(910/1010) 및 하드 마스크(901/1001)의 측벽들 상에 형성된다. 블록(1106)에서, S/D(source/drain) 스페이서가 형성된다. 예를 들어, 도 9c/도 10c에 도시된 바와 같이, 소스/드레인 스페이서(906/1006)가 하드 마스크(901/1001) 및 게이트(910/1010)의 측벽들 상에 형성된다. 도 9a에 도시된 바와 같이, 핀 스페이서(906)가 핀들(920)의 측벽들 상에 형성된다. 도 10a에 도시된 바와 같이, GAA(gate-all-around) 나노와이어 스페이서(1006)가 GAA 나노와이어(1020)의 측벽들 상에 형성된다.

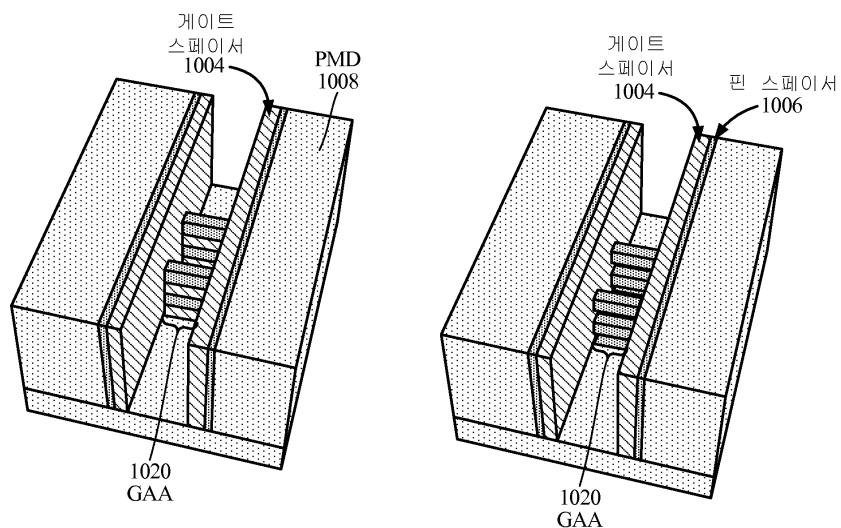

[0073] [0078] 다시 도 11a를 참조하면, 블록(1108)에서, 소스/드레인 영역들의 리세스 에칭이 수행된다. 소스/드레인 영역들이 S/D 스페이서를 통과하여 게이트 스페이서 안으로 리세스되어 재성장 소스/드레인 부분들이 형성된다. 도 9d에 도시된 바와 같이, 핀들(920)이 핀 스페이서(906) 및 게이트 스페이서(904)를 통과하여 리세스 에칭된다. 도 10d에 도시된 바와 같이, GAA 나노와이어(1020)가 GAA 스페이서(1006) 및 게이트 스페이서(1004)를 통과하여 리세스 에칭된다. LDD(lightly doped drain) 주입이, 도 9e/도 10e에 도시된 바와 같이 더 이상 재성장 소스/드레인(S/D) 영역들로부터 제공되지 않는다.

[0074] [0079] 도 11a를 다시 참조하면, 블록(1110)에서, 재성장 S/D 부분들을 형성하기 위해서 에피택셜 성장이 사용된다. 재성장 S/D 부분들은 재성장 S/D 부분들을 병합하지 않고, 제어된 (예를 들어, <111> 밀러 지수) 패싯 형성에 의해 형성될 수 있다. 예를 들어, 인 도핑 실리콘(SiP), 탄소 인 도핑 실리콘(SiCP), 또는 인 도핑 게르마늄(GeP)의 에피택셜 성장은 n-타입(예를 들어, NFET)의 재성장 S/D 영역들을 형성할 수 있다. 유사하게, 붕소 도핑 실리콘 게르마늄(SiGeB), 또는 붕소 도핑 게르마늄(GeB)의 에피택셜 성장은 p-타입(예를 들어, PFT)의 재성장 S/D 영역들을 형성할 수 있다. 도 9e/10e에 도시된 바와 같이, 재성장 S/D 영역들(970/1070)은 언

급된 에피택셜 성장을 이용하여 형성된다. 이 어레인지먼트에서, 재성장 S/D 영역들(970/1070)은 실질적으로 평행한 측벽들을 갖는다. 도 10e에 도시된 바와 같이, GAA 나노와이어-기반 디바이스(1000)는 n-타입 및 p-타입 S/D 영역들(1070) 둘 모두를 포함한다. 블록(1112)에서, PMD(pre-metal dielectric) 재료가 증착된다. 도 9f/10f에 도시된 바와 같이, PMD(908/1008)는 핀-기반 디바이스(900) 또는 GAA 나노와이어-기반 디바이스(1000) 상에 증착된다.

[0075] [0080] 도 11b는 본 개시내용의 양상들에 따른 컨택트 랩 어라운드 구조를 포함하는 반도체 디바이스를 제조하기 위한 도 11a의 방법(1100)을 추가로 도시한다. 블록(1120)에서, 폴리 더미 게이트 상에서 정지하고 폴리 더미 게이트를 노출시키도록 CMP(chemical mechanical polish) 프로세스가 PMD 재료 상에서 수행된다. 도 9g/10g에 도시된 바와 같이, 게이트(910/1010)를 노출시키기 위해서 CMP 프로세스가 PMD(908/1008) 상에서 수행된다. 블록(1122)에서, 더미 게이트를 능동 게이트로 대체하기 위해서 대체 게이트 프로세스가 수행된다. 도 9h/10h에 도시된 바와 같이, CMP 프로세스를 사용하여 PMD(908/1008) 상에서 정지하는 게이트(910/1010)를 형성하고 게이트(910/1010)를 노출시키기 위해서 더미 게이트가 제거된다.

[0076] [0081] 도 10h에 도시된 바와 같이, 하이-K 층(1016)이 GAA 나노와이어(1020)의 노출 부분 상에 증착된다. 제 1 WFM(work function material)(예를 들어, n-타입 WFM)이 GAA 나노와이어(1020)의 제 1 노출 부분 상에 증착되어 NFET를 형성한다. 이외에도, 제 2 WFM(work function material)(예를 들어, p-타입 WFM)이 GAA 나노와이어(1020)의 제 2 노출 부분 상에 증착되어 PFET를 형성한다. 전도성 층(1012)(예를 들어, 텅스텐(W) 또는 코발트(Co))이 제 1 WFM 및 제 2 WFM 상에 증착되어 게이트(1010)의 형성이 완성된다. 마지막으로, PMD(1008) 상에서 정지하도록 CMP 프로세스가 수행된다.

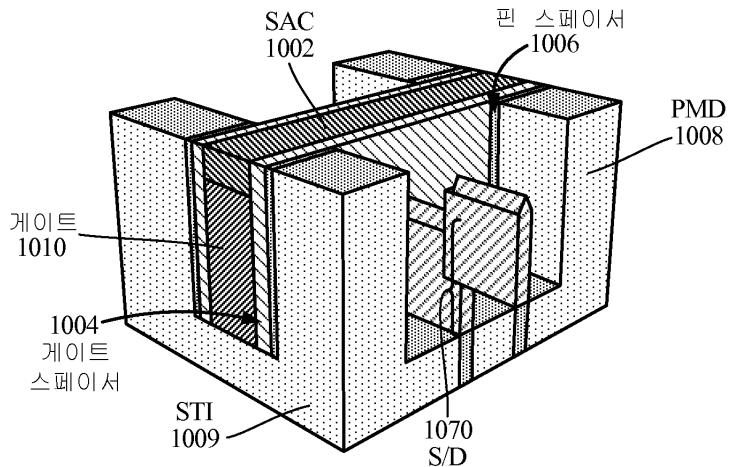

[0077] [0082] 다시 도 11b를 참조하면, 블록(1124)에서, 게이트가 리세스 예칭된 다음, 게이트의 형성을 완성하기 위해, 후속 CMP 프로세스 동안 예칭 정지 층으로서 동작하는 SAC(self-aligned contact)의 증착이 이어진다. 도 9i/10i에 도시된 바와 같이, 전도성 층이 예칭되고 SAC(902/1002)가 증착된다. CMP 프로세스가 SAC(902/1002) 상에서 수행될 수 있다. 게이트(910/1010)의 완성 후, 랩-어라운드 컨택트가 재성장 S/D 영역들(970/1070)을 둘러싸도록 형성된다.

[0078] [0083] 블록(1126)에서, 컨택트 캐비티 내의 PMD 산화물 및 스페이서 둘 모두를 제거하기 위해 SAC 예칭이 수행된다. SAC 예칭은 재성장 S/D 영역들에 대한 손상을 방지하기 위해서 손상이 적거나 전혀 없는 예칭일 수 있다. ALE(atomic layer etch)이 재성장 S/D 영역들을 노출시킬 수 있다. 도 9j/10j에 도시된 바와 같이, 재성장 SD 영역들(970/1070)을 노출시키고 STI(909/1009) 및 게이트 스페이서(904/1004) 상에서 정지하도록 PMD(908/1008) 및 핀 스페이서(906)/GAA 스페이서(1006)의 예칭이 수행된다. 블록(1128)에서, 증착은, 재성장 S/D 영역들을 둘러싸는 MIS(metal-oxide-semiconductor) 컨택트 또는 직접적인 컨택트를 형성한다. 도 9k/10k에 도시된 바와 같이, 재성장 S/D 영역들(970/1070)을 둘러싸도록 MIS 컨택트(930/1030) 또는 직접적인 컨택트(980/1080)가 형성된다. 블록(1130)에서, 컨택트 충진 재료(예를 들어, 932/1032)가 재성장 S/D 영역들을 둘러싸는 MIS 컨택트 또는 직접적인 컨택트 상에 증착된다. 도 9l/10l에 도시된 바와 같이, 핀-기반 디바이스(900) 또는 GAA 나노와이어-기반 디바이스(1000)의 형성을 완성하기 위해서, 재성장 S/D 영역들(970/1070)을 둘러싸도록 MIS 컨택트(930/1030) 또는 직접적인 컨택트(980/1080)가 형성된다.

[0079] [0084] 본 개시내용의 양상들은 컨택트 저항을 대폭 감소시키기 위해서 MIS(metal-insulator-semiconductor) 컨택트들 또는 직접적인 컨택트들을 이용하여 고도로 스케일링된 핀들 상에 랩-어라운드 컨택트들을 형성하는 혁신적인 통합 흐름을 포함한다. 본 개시내용의 추가 양상들은 또한 컨택트 저항을 감소시키기 위해서 GAA(gate-all-around) 나노와이어-기반 디바이스들 및 기타 유사한 반도체 디바이스들의 소스/드레인에 MIS 컨택트 또는 직접적인 컨택트를 제공할 수 있다. 랩-어라운드 컨택트들을 포함하는, 컨택트 랩 어라운드 구조는 발전된 로직 기술들의 축소된 디바이스 지오메트리들, 이를 테면, 7 나노미터 로직 기술 및 이를 능가하는 로직 기술 내에서의 동작을 가능하게 할 수 있다. 컨택트 랩-어라운드 구조는 상당한 실질적인 컨택트 저항 감소를 제공하면서, 기존의 재료들 및 프로세스 능력들을 사용하여 제조될 수 있다.

[0080] [0085] 본 개시내용의 양상에 따르면, 게이트 스택을 포함하는 핀-기반 구조가 설명된다. 일 구성에서, 핀-기반 구조는 게이트 스택에 근접한 핀-기반 구조의 재성장 소스/드레인 영역의 실질적으로 모든 표면 영역을 컨택팅하기 위한 수단을 포함한다. 컨택트 수단은 랩-어라운드 컨택트(610), MIS 컨택트(830) 또는 직접적인 컨택트(880)일 수 있다. 다른 양상에서, 상기 언급된 수단은 상기 언급된 수단에 의해 인용된 기능들을 수행하도록 구성되는 임의의 모듈 또는 임의의 장치 또는 재료일 수 있다.

[0081] [0086] 도 12는, 본 개시내용의 양상이 유리하게 활용될 수 있는 예시적인 무선 통신 시스템(1200)을 도시하는

블록도이다. 예시를 위해, 도 12는 3개의 원격 유닛들(1220, 1230, 및 1250) 및 2개의 기지국들(1240)을 도시한다. 무선 통신 시스템들이 더 많은 원격 유닛들 및 기지국들을 가질 수도 있음이 인식될 것이다. 원격 유닛들(1220, 1230 및 1250)은 개시된 컨택트들을 포함하는 IC 디바이스들(1225A, 1225C 및 1225B)을 포함한다. 기지국들, 스위칭 디바이스들, 및 네트워크 장비와 같은 다른 디바이스들이 또한, 개시된 하이브리드 컨택트들을 포함할 수 있다는 것이 인식될 것이다. 도 12는 기지국들(1240)로부터 원격 유닛들(1220, 1230, 및 1250)로의 순방향 링크 신호들(1280) 및 원격 유닛들(1220, 1230, 및 1250)로부터 기지국들(1240)로의 역방향 링크 신호들(1290)을 도시한다.

[0082] [0087] 도 12에서, 원격 유닛(1220)은 모바일 전화로서 도시되고, 원격 유닛(1230)은 휴대용 컴퓨터로서 도시되며, 원격 유닛(1250)은 무선 로컬 루프 시스템에서 고정 위치 원격 유닛으로서 도시된다. 예를 들어, 원격 유닛들은 모바일 전화기, 핸드 헬드 PCS(personal communication system) 유닛, 휴대용 데이터 유닛, 이를테면, 개인 휴대 정보 단말기, GPS-가능 디바이스, 내비게이션 디바이스, 셋탑 박스, 음악 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 고정 위치 데이터 유닛, 이를 테면, 겸침 장비, 또는 데이터 또는 컴퓨터 명령들을 저장하거나 또는 리트리빙하는 다른 디바이스들, 또는 이들의 임의의 조합들일 수 있다. 도 12는 본 개시내용의 양상들에 따른 원격 유닛들을 도시하지만, 본 개시내용은 이를 예시적인 도시된 유닛들로 제한되지 않는다. 본 개시내용의 양상들은 개시된 반도체 디바이스들을 포함하는 많은 디바이스들에서 적절히 활용될 수 있다.

[0083] [0088] 도 13은 앞서 개시된 컨택트들과 같은, 핀-기반 구조의 회로, 레이아웃, 및 로직 설계를 위해 사용된 설계 워크스테이션을 도시하는 블록도이다. 설계 워크스테이션(1300)은 운영 시스템 소프트웨어, 지원 파일들, 및 Cadence 또는 OrCAD와 같은 설계 소프트웨어를 포함하는 하드 디스크(1301)를 포함한다. 설계 워크스테이션(1300)은 회로(1310) 또는 핀-기반 구조들(1312), 이를 테면, 컨택트의 설계를 용이하게 하기 위해 디스플레이(1302)를 또한 포함한다. 저장 매체(1304)는 회로(1310)의 설계 또는 핀-기반 구조(1312)를 유형으로(tangibly) 저장하기 위해 제공된다. 회로(1310) 또는 핀-기반 구조(1312)의 설계는 GDSII 또는 GERBER과 같은 파일 포맷으로 저장 매체(1304) 상에 저장될 수 있다. 저장 매체(1304)는 CD-ROM, DVD, 하드 디스크, 플래시 메모리 또는 다른 적절한 디바이스일 수 있다. 또한 설계 워크스테이션(1300)은 저장 매체(1304)로부터의 입력을 받아들이거나 저장 매체(1304)에 출력을 기록하기 위한 드라이브 장치(1303)를 포함한다.

[0084] [0089] 저장 매체(1304) 상에 레코딩된 데이터는 로직 회로 구성들, 포토리소그래피 마스크들에 대한 패턴 데이터 또는 전자 빔 리소그래피와 같은 직렬 기록 툴들에 대한 마스크 패턴 데이터를 특정할 수 있다. 데이터는 추가로 로직 시뮬레이션들과 연관되는 타이밍도들 또는 넷(net) 회로들과 같은 로직 검증 데이터를 포함한다. 저장 매체(1304) 상에 데이터를 제공하는 것은 반도체 웨이퍼들을 설계하기 위한 프로세스들의 수를 감소시킴으로써 핀-기반 구조(1312) 또는 회로(1310)의 설계를 용이하게 한다.

[0085] [0090] 펌웨어 및/또는 소프트웨어 구현의 경우, 방법들은 여기에 설명된 기능들을 수행하는 모듈들(예를 들어, 절차들, 함수들 등)을 이용하여 구현될 수도 있다. 명령들을 유형으로 구현하는 머신 관독가능 매체가, 본원에 설명된 방법들을 구현하는데 사용될 수도 있다. 예를 들어, 소프트웨어 코드는 메모리에 저장되고 프로세서 유닛에 의해 실행될 수도 있다. 메모리는 프로세서 유닛 내부에서 또는 프로세서 유닛 외부에서 구현될 수도 있다. 본원에서 사용되는 바와 같이, 용어 "메모리"는 장기, 단기, 휴발성, 비휘발성, 또는 다른 메모리의 타입들을 지칭하며, 특정한 타입의 메모리 또는 메모리들의 수, 또는 메모리가 저장되는 매체들의 타입에 제한되지 않는다.

[0086] [0091] 펌웨어 및/또는 소프트웨어로 구현되는 경우, 기능들은 하나 또는 그보다 많은 명령들 또는 코드로서 컴퓨터-관독가능 매체로서 저장될 수 있다. 예들은, 데이터 구조로 인코딩된 컴퓨터 관독가능 매체 및 컴퓨터 프로그램으로 인코딩된 컴퓨터 관독가능 매체를 포함한다. 컴퓨터-관독가능 매체는 물리적 컴퓨터 저장 매체를 포함한다. 저장 매체는 컴퓨터에 의해 액세스될 수 있는 이용가능한 매체일 수도 있다. 제한이 아닌 예로서, 그러한 컴퓨터-관독가능 매체들은 RAM, ROM, EEPROM, CD-ROM 또는 다른 광학 디스크 저장부, 자기 디스크 저장 또는 다른 자기 저장 디바이스들, 또는 명령들 또는 데이터 구조들의 형태로 원하는 프로그램 코드를 저장하는데 사용될 수 있고 컴퓨터에 의해 액세스될 수 있는 다른 매체를 포함할 수 있다; 여기에 사용된 바와 같이, 디스크(disk) 및 디스크(disc)는 커넥트 디스크(disc)(CD), 레이저 디스크(disc), 광학 디스크(disc), DVD(digital versatile disc), 플로피 디스크(disk) 및 블루-레이 디스크(disc)를 포함하며, 여기서, 디스크(disk)들은 일반적으로 데이터를 자기적으로 재생하지만, 디스크(disc)들은 레이저들을 이용하여 광학적으로 데이터를 재생한다. 상기한 것들의 결합들이 또한 컴퓨터 관독가능 매체들의 범위 내에 포함되어야 한다.

[0087]

[0092] 컴퓨터 관독가능 매체 상의 저장에 부가하여, 명령들 및/또는 데이터가 통신 장치에 포함된 송신 매체들 상의 신호들로서 제공될 수도 있다. 예를 들어, 통신 장치는 명령들 및 데이터를 표시하는 신호들을 갖는 트랜시버를 포함할 수도 있다. 명령들 및 데이터는, 하나 또는 그 초과의 프로세서들로 하여금 청구항들에서 약술된 기능들을 구현하게 하도록 구성된다.

[0088]

[0093] 본 발명의 교시들 및 그들의 이점들이 상세히 설명되었지만, 첨부된 청구항들에 의해 정의된 바와 같은 본 개시물의 기술을 벗어나지 않으면서 다양한 변화들, 치환들 및 수정들이 여기서 행해질 수 있음을 이해해야 한다. 예를 들어, "상부" 및 "하부"와 같은 상대적인 용어들은 기판 또는 전자 디바이스에 대하여 사용된다. 물론, 기판 또는 전자 디바이스가 반전되는 경우, 상부는 하부가 되고, 그 역의 경우도 성립된다. 추가로, 측면들로 배향되는 경우, 위와 아래는 기판 또는 전자 디바이스의 측면들을 지칭할 수 있다. 또한, 본 출원의 범위는, 명세서에 설명된 프로세스, 머신, 제조법, 조성물, 수단, 방법들 및 단계들의 특정한 구성들로 제한되도록 의도되지 않는다. 당업자가 본 발명으로부터 용이하게 인식할 바와 같이, 본원에 설명된 대응하는 구성들과 실질적으로 동일한 기능을 수행하거나 실질적으로 동일한 결과를 달성하는, 현재 존재하거나 추후에 개발될 프로세스들, 머신들, 제조법, 물질의 합성, 수단, 방법들, 또는 단계들이 본 발명의 교시들에 따라 이용될 수도 있다. 따라서, 첨부된 청구항들은 그들의 범위 내에, 그러한 프로세스들, 머신들, 제조법, 조성물, 수단, 방법들, 또는 단계들을 포함하도록 의도된다.

[0089]

[0094] 본원의 개시내용과 관련하여 설명된 다양한 예시적인 논리 블록들, 모듈들, 회로들, 및 알고리즘 단계들은, 전자 하드웨어, 컴퓨터 소프트웨어, 또는 이 둘의 조합들로 구현될 수 있다는 것을 당업자는 추가로 인식할 것이다. 하드웨어와 소프트웨어의 상호 교환 가능성을 명확하게 설명하기 위해, 다양한 예시적인 컴포넌트들, 블록들, 모듈들, 회로들, 및 단계들이 이들의 기능성의 관점에서 일반적으로 상술되었다. 이러한 기능이 하드웨어로 구현되는지 아니면 소프트웨어로 구현되는지는 전체 시스템에 부과된 설계 제약들 및 특정 애플리케이션에 좌우된다. 해당 기술분야에서 통상의 지식을 가진 자들은 설명된 기능을 특정 애플리케이션마다 다양한 방식들로 구현할 수도 있지만, 이러한 구현 결정들이 본 개시내용의 범위를 벗어나게 하는 것으로 해석되지는 않아야 한다.

[0090]

[0095] 본원의 개시내용과 관련하여 설명되는 다양한 예시적인 로직 블록들, 모듈들, 및 회로들이 범용 프로세서, 디지털 신호 프로세서(DSP), 주문형 집적회로(ASIC), 필드 프로그래머블 게이트 어레이(FPGA) 또는 다른 프로그래머블 논리 디바이스, 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트들 또는 본원에 설명된 기능들을 수행하도록 설계된 이들의 임의의 결합으로 구현되거나 또는 수행될 수 있다. 범용 프로세서는 마이크로프로세서일 수도 있지만, 대안으로 프로세서는 임의의 종래 프로세서, 제어기, 마이크로제어기 또는 상태 머신일 수도 있다. 프로세서는 또한 컴퓨팅 디바이스들의 결합(예를 들어, DSP와 마이크로프로세서의 결합, 다수의 마이크로프로세서들, DSP 코어와 결합된 하나 이상의 마이크로프로세서들, 또는 임의의 다른 구성)으로서 구현될 수도 있다.

[0091]

[0096] 본원의 개시내용과 관련하여 설명되는 알고리즘 또는 방법의 단계들은 직접적으로 하드웨어로, 프로세서에 의해 실행되는 소프트웨어 모듈로, 또는 이 둘의 조합으로 구현될 수 있다. 소프트웨어 모듈은 RAM, 플래시 메모리, ROM, EEPROM, EEPROM, 레지스터들, 하드 디스크, 이동식 디스크, CD-ROM, 또는 당업계에 알려진 임의의 다른 형태의 저장 매체에 상주할 수 있다. 예시적인 저장 매체는 프로세서가 저장 매체로부터 정보를 판독하고 저장 매체에 정보를 기록할 수 있도록 프로세서에 결합된다. 대안으로, 저장 매체는 프로세서에 통합될 수 있다. 프로세서 및 저장 매체는 ASIC에 상주할 수 있다. ASIC은 사용자 단말에 상주할 수 있다. 대안으로, 프로세서 및 저장 매체는 사용자 단말에서 개별 컴포넌트들로서 상주할 수 있다.

[0092]

[0097] 하나 또는 그 초과의 예시적인 설계들에서, 설명된 기능들은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 조합으로 구현될 수 있다. 소프트웨어로 구현되는 경우, 기능들은 하나 또는 그 초과의 명령들 또는 코드로서 컴퓨터 관독가능 매체 상에 저장되거나 또는 이를 통해 송신될 수 있다. 컴퓨터 관독가능 매체들은 컴퓨터 저장 매체들, 및 일 장소에서 다른 장소로 컴퓨터 프로그램의 이전을 용이하게 하는 임의의 매체들을 포함하는 통신 매체 둘 모두를 포함한다. 저장 매체는 범용 또는 특수 목적용 컴퓨터에 의해 액세스될 수 있는 임의의 이용가능한 매체일 수 있다. 한정이 아닌 예시로, 이러한 컴퓨터 관독 가능 매체는 RAM, ROM, EEPROM, CD-ROM이나 다른 광 디스크 저장소, 자기 디스크 저장소 또는 다른 자기 저장 디바이스들, 또는 명령들이나 데이터 구조들의 형태로 지정된 프로그램 코드 수단을 전달 또는 저장하는데 사용될 수 있으며 범용 또는 특수 목적용 컴퓨터나 범용 또는 특수 목적용 프로세서에 의해 액세스 가능한 임의의 다른 매체를 포함할 수 있다. 또한, 임의의 접속이 컴퓨터 관독 가능 매체로 적절히 지정된다. 예를 들어, 소프트웨어가 동축 케이블, 광섬유 케이블, 연선, 디지털 가입자 라인(DSL: digital subscriber line), 또는 적외선, 라디오 및 마이크로파와 같은

무선 기술들을 사용하여 웹사이트, 서버 또는 다른 원격 소스로부터 전송된다면, 동축 케이블, 광섬유 케이블, 연선, DSL, 또는 적외선, 라디오 및 마이크로파와 같은 무선 기술들이 매체의 정의에 포함된다. 여기서 사용되는 디스크(disk 및 disc)는 CD(compact disc), 레이저 디스크(disc), 광 디스크(disc), DVD(digital versatile disc), 플로피 디스크(disk) 및 블루-레이 디스크(disc)를 포함하며, 여기서 디스크(disk)들은 대개 데이터를 자기적으로 재생하지만, 디스크(disc)들은 레이저들을 이용하여 광학적으로 데이터를 재생한다. 상기한 것들의 결합들이 또한 컴퓨터 판독가능 매체들의 범위 내에 포함되어야 한다.

[0093]

[0098] 앞의 설명은, 어떤 당업자라도 본원에 설명된 다양한 양상들을 실시할 수 있게 하기 위해서 제공된다. 이들 양상들에 대한 다양한 변형들이 당업자에게 쉽게 명백할 것이며, 여기에 정의된 일반적인 원리들은 다른 양상들에 적용될 수 있다. 따라서, 청구항들은 본원에 도시되는 양상들에 제한되도록 의도되지 않으며, 청구항들의 문언에 일치되는 전체 범위에 부합될 것이며, 여기서 단수의 엘리먼트에 대한 참조는 구체적으로 그렇게 서술되지 않는 한 "하나 및 단지 하나"가 아닌, 오히려 "하나 이상"을 의미하도록 의도된다. 구체적으로 달리 서술되지 않는 한, 용어 "일부"는 하나 이상을 지칭한다. 항목들의 리스트 중 "적어도 하나"를 지칭하는 문구는 하나의 부재들을 포함하는, 이들 항목의 임의의 조합을 의미한다. 일 예로서, "a, b, 또는 c 중 적어도 하나"는 a; b; c; a 및 b; a 및 c; b 및 c; 및 a,b, 및 c를 커버하도록 의도된다. 당업자에게 알려져 있거나 또는 추후에 알려지게 되는 본 개시내용 전체에 걸쳐 설명된 다양한 양상들의 엘리먼트들에 대한 구조적 및 기능적 등가물들 모두가 인용에 의해 본원에 명시적으로 포함되고 청구항들에 의해 포함되도록 의도된다. 또한, 본원에 개시된 어떤 것도, 이러한 개시물이 청구항들에서 명시적으로 인용되는지 여부와 관계없이 공중에 전용되도록 의도되지 않는다. 청구항 엘리먼트는, 그 엘리먼트가 문구 "~하기 위한 수단"을 이용하여 명시적으로 인용되거나 또는 방법 청구항의 경우, 엘리먼트가 문구 "~하는 단계"를 이용하여 인용되지 않는 한, 35 U.S.C. § 112 제 6 문단의 조항들에 따라 해석되지 않는다.

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

## 도면5a

도면5b

도면6

### 도면7a

도면7b

## 도면8

## 도면9a

도면9b

도면9c

도면9d

도면9e

도면9f

도면9g

도면9h

도면9i

도면9j

도면9k

도면9l

도면10a

도면10b

도면10c

도면10d

도면10e

도면10f

도면10g

도면10h

도면10i

도면10j

도면10k

도면10l

## 도면11a

## 도면11b

도면12

도면13