(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4587187号

(P4587187)

(45) 発行日 平成22年11月24日(2010.11.24)

(24) 登録日 平成22年9月17日(2010.9.17)

(51) Int.Cl.

H01L 27/146 (2006.01)

H04N 5/335 (2006.01)

F 1

H01L 27/14

H04N 5/335 74 O

請求項の数 15 (全 22 頁)

(21) 出願番号 特願2008-177064 (P2008-177064)

(22) 出願日 平成20年7月7日 (2008.7.7)

(62) 分割の表示 特願2004-358342 (P2004-358342)

分割

原出願日 平成16年12月10日 (2004.12.10)

(65) 公開番号 特開2008-263227 (P2008-263227A)

(43) 公開日 平成20年10月30日 (2008.10.30)

審査請求日 平成20年7月7日 (2008.7.7)

(31) 優先権主張番号 特願2003-415011 (P2003-415011)

(32) 優先日 平成15年12月12日 (2003.12.12)

(33) 優先権主張国 日本国 (JP)

早期審査対象出願

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 CMOS型光電変換装置及び撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

第一導電型の電荷蓄積領域と複数の第二導電型の不純物領域とを含んで構成される光電変換素子と、前記光電変換素子にて生じた電荷を転送する転送MOSトランジスタと、前記転送MOSトランジスタによって電荷が転送される第一導電型の不純物領域と、が第一導電型の半導体基板に配されたCMOS型光電変換装置であって、

前記複数の第二導電型の不純物領域は、前記電荷蓄積領域の下から前記転送MOSトランジスタのゲート電極の下まで連続して配され、且つ、少なくとも第1の不純物領域と、該第1の不純物領域と前記電荷蓄積領域との間に配された第2の不純物領域と、該第2の不純物領域と前記電荷蓄積領域との間に配された第3の不純物領域と、を含み、前記第1の不純物領域、前記第2の不純物領域および前記第3の不純物領域は、前記半導体基板に対するイオン注入によって形成され、

前記第1の不純物領域の不純物濃度ピークの濃度C1と、前記第2の不純物領域の不純物濃度ピークの濃度C2と、前記第3の不純物領域の不純物濃度ピークの濃度C3とが、 $C_2 < C_3 < C_1$ の関係を満たし、

前記CMOS型光電変換装置は、前記第3の不純物領域の上かつ前記転送MOSトランジスタのゲート電極の下に配された第二導電型のチャネルドープ領域を有していることを特徴とするCMOS型光電変換装置。

## 【請求項 2】

前記第3の不純物領域の不純物濃度ピークは、前記第3の不純物領域の前記電荷蓄積領

10

20

域側に配されていることを特徴とする請求項 1 に記載の C M O S 型光電変換装置。

**【請求項 3】**

前記第 1 の不純物領域の不純物濃度ピークの濃度  $C_1$  と前記第 2 の不純物領域の不純物濃度ピークの濃度  $C_2$  との関係が、 $3 \times C_2 < C_1$  であることを特徴とする請求項 1 あるいは 2 に記載の C M O S 型光電変換装置。

**【請求項 4】**

前記第 1 の不純物領域の不純物濃度ピークの濃度  $C_1$  と前記第 2 の不純物領域の不純物濃度ピークの濃度  $C_2$  との関係が、 $5 \times C_2 < C_1$  であることを特徴とする請求項 3 に記載の C M O S 型光電変換装置。

**【請求項 5】**

前記第 1 の不純物領域の不純物濃度ピークの濃度  $C_1$  が  $1 \times 10^{-6} \text{ cm}^{-3} < C_1 < 1 \times 10^{-8} \text{ cm}^{-3}$  であり、

前記第 2 の不純物領域の不純物濃度ピークの濃度  $C_2$  が  $1 \times 10^{-5} \text{ cm}^{-3} < C_2 < 5 \times 10^{-6} \text{ cm}^{-3}$  であり、

前記第 3 の不純物領域の不純物濃度ピークの濃度  $C_3$  が  $2 \times 10^{-5} \text{ cm}^{-3} < C_3 < 2 \times 10^{-7} \text{ cm}^{-3}$  であることを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載の C M O S 型光電変換装置。

**【請求項 6】**

前記複数の第二導電型の不純物領域のそれぞれは、前記電荷蓄積領域の下から前記光電変換素子に隣接した素子分離部の下まで連続して配されていることを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の C M O S 型光電変換装置。

**【請求項 7】**

前記チャネルドープ領域の不純物濃度ピークは、前記第 3 の不純物領域の不純物濃度ピークよりも高いことを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載の C M O S 型光電変換装置。

**【請求項 8】**

前記第 3 の不純物領域は、前記電荷蓄積領域の下部を覆っていることを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の C M O S 型光電変換装置。

**【請求項 9】**

前記電荷蓄積領域の不純物濃度ピークは、前記第 3 の不純物領域の不純物濃度ピークよりも上に配されていることを特徴とする請求項 1 乃至 8 のいずれか 1 項に記載の C M O S 型光電変換装置。

**【請求項 10】**

第一導電型の電荷蓄積領域と第二導電型の不純物領域とを含んで構成される光電変換素子と、前記光電変換素子にて生じた電荷を転送する転送 M O S ドレイントランジスタと、前記転送 M O S ドレイントランジスタによって電荷が転送される第一導電型の不純物領域と、が第一導電型の半導体基板に配された C M O S 型光電変換装置であって、

前記第二導電型の不純物領域は、前記電荷蓄積領域の下から前記転送 M O S ドレイントランジスタのゲート電極の下まで連続して配され、且つ、前記半導体基板の深部から前記電荷蓄積領域に向かって順に位置する第 1 の不純物濃度ピークと、第 2 の不純物濃度ピークと、第 3 の不純物濃度ピークとを少なくとも有し、前記第二導電型の不純物領域は、前記半導体基板に対するイオン注入によって形成され、

前記第 1 の不純物濃度ピークの濃度  $C_1$  と、前記第 2 の不純物濃度ピークの濃度  $C_2$  と、前記第 3 の不純物濃度ピークの濃度  $C_3$  とが、

$$C_2 < C_3 < C_1$$

の関係を満たし、

前記 C M O S 型光電変換装置は、前記第二導電型の不純物領域の上かつ前記転送 M O S ドレイントランジスタのゲート電極の下に配された第二導電型の他の不純物領域を有していることを特徴とする C M O S 型光電変換装置。

**【請求項 11】**

10

20

30

40

50

前記第二導電型の他の不純物領域の不純物濃度ピークは、前記第3の不純物濃度ピークよりも高いことを特徴とする請求項10に記載のCMOS型光電変換装置。

**【請求項12】**

前記第二導電型の不純物領域は、前記電荷蓄積領域の下部を覆っていることを特徴とする請求項10又は11に記載のCMOS型光電変換装置。

**【請求項13】**

前記電荷蓄積領域の不純物濃度ピークは、前記第3の不純物濃度ピークよりも上に配されていることを特徴とする請求項10乃至12のいずれか1項に記載のCMOS型光電変換装置。

**【請求項14】**

10

前記光電変換素子は、前記電荷蓄積領域の表面側に接して形成された第二導電型の表面不純物領域を有する請求項1乃至13のいずれか1項に記載のCMOS型光電変換装置。

**【請求項15】**

請求項1乃至14のいずれか1項に記載のCMOS型光電変換装置と、

該CMOS型光電変換装置へ光を結像する光学系と、

該CMOS型光電変換装置からの信号を処理する信号処理回路とを有することを特徴とする撮像システム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

20

本発明は、光電変換装置及び撮像システム、特に、CMOSエリアセンサ及び撮像システムに関する。

**【背景技術】**

**【0002】**

従来、画像信号を電気信号に変換する固体撮像素子として、CCDが知られている。このCCDはフォトダイオードアレイを有し、各フォトダイオードに蓄積された電荷にパルス電圧を印加して電気信号として読み出すようになっている。また、近年、フォトダイオードとMOSトランジスタを含む周辺回路とを1チップ化したCMOSエリアセンサが固体撮像素子として用いられている。CMOSエリアセンサはCCDと比較して、消費電力が小さい、駆動電力が低いなどの利点を有しており、今後の需要拡大が予想される。

30

**【0003】**

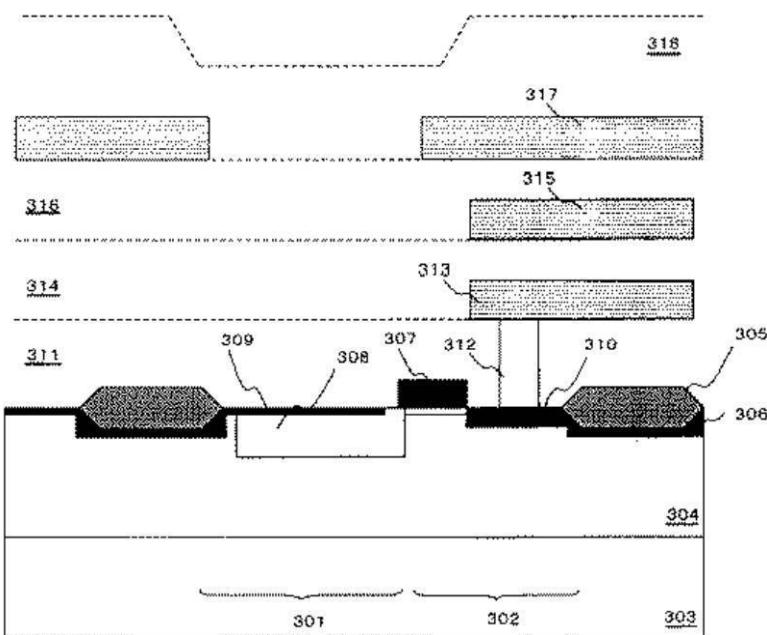

光電変換装置の代表例としてCMOSエリアセンサを図9を用いて説明する。CMOSエリアセンサのフォトダイオード部301と転送MOSトランジスタ部302の断面模式図を示す。303はN型シリコン基板、304はP型ウエル、307は転送MOSトランジスタのゲート電極、308はフォトダイオードのN型電荷蓄積領域、309はフォトダイオードを埋め込み構造とするための表面P型領域、305は素子分離のためのフィールド酸化膜、310はフローティングディフュージョンを形成し、転送MOSトランジスタのドレイン領域としての機能を持つN型高濃度領域である。

**【0004】**

311はゲート電極と第一の配線層を絶縁するシリコン酸化膜、312はコントラクトブリグ、313は第一の配線層、314は第一の配線層と第二の配線層を絶縁する層間絶縁膜、315は第二の配線層、316は第二の配線層と第三の配線層を絶縁する層間絶縁膜、317は第三の配線層、318はパッシベーション膜である。パッシベーション膜318の上層に不図示のカラーフィルター層、さらに感度向上のためのマイクロレンズを形成する。表面から入射した光は第三の配線層317により規定される開口部を通して、フォトダイオードに入る。光はフォトダイオードのN型電荷蓄積領域308あるいはP型ウエル304内で吸収され、電子・ホール対を生成する。このうち電子はN型電荷蓄積領域308に蓄積される。

40

**【0005】**

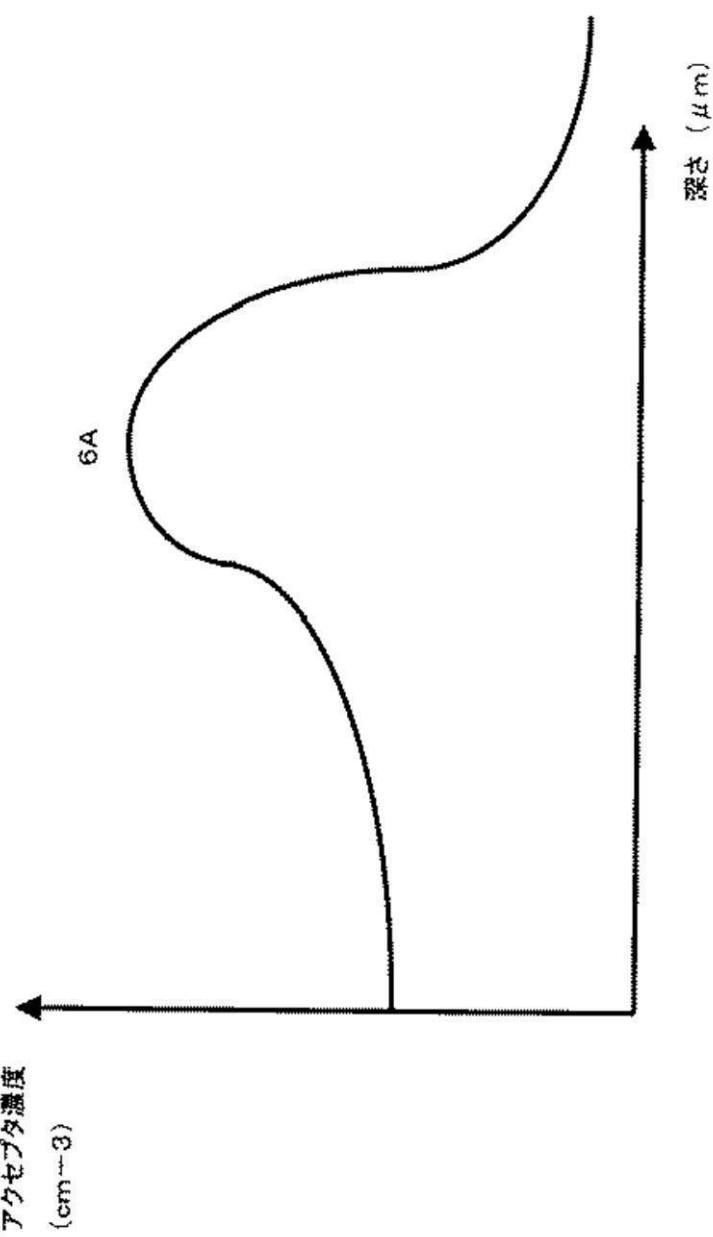

CMOSエリアセンサの従来技術としては、例えば、特許文献1に記載されている、図

50

10 (特許文献1のFig. 6)のようなキャリアプロファイルを持つ構造がある。この構造は基板内の深い領域に濃度の高い不純物拡散領域6Aをもち、ウエル内で吸収された光により発生した電荷を表面側に取り出す効率を上げ、感度を向上させる効果があると考えられる。

【特許文献1】米国特許第6,483,129号

【発明の開示】

【発明が解決しようとする課題】

【0006】

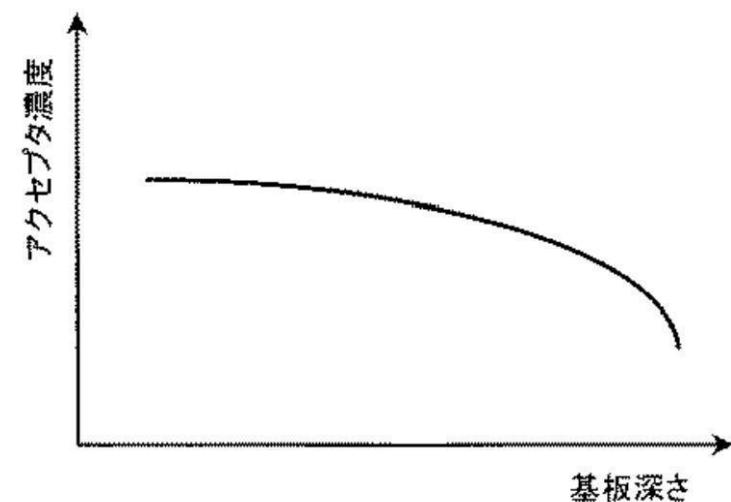

従来の光電変換装置、特に、CMOSエリアセンサにおいては、フォトダイオードのウエル層はイオン注入を行った後に熱拡散を行うことにより形成されていたため、図11に示すように、一般的には基板深さ方向の濃度分布は徐々に低くなっていた。その結果、基板深さ方向のポテンシャルバリアを持っていない構造となり、P型ウェル内で吸収された光の一部は基板方向に損失してしまうため光電変換信号としては寄与しない。特に画素サイズが小さくなるにつれ、必要とする感度が得られないという課題が現れた。また、感度や飽和電荷数やフォトダイオードからフローティングディフュージョンへの転送などの諸特性を制御する際に扱える製造条件のパラメータが少ないため、これらの性能を満足できない課題もある。

【0007】

一方、上記特許文献の図10に示す構造は、基板内の深い領域に濃度の高い不純物拡散領域をもち、感度を向上することについて効果はあると考えられるが、同時に満足すべき飽和電荷数やフォトダイオードからフローティングディフュージョンへの転送などの諸特性を制御する際に扱える製造条件のパラメータが少ないため、これらの性能を満足できないという課題がある。また、上述の特許文献1に記載されているような単純なレトログレードウエル構造では、基板で発生した暗電流がフォトダイオード内に漏れ込み、センサの性能を劣化させる。すなわち、これまでに感度向上と飽和電荷数、転送効率の向上とを両立させるという技術課題は見出されていない。

【0008】

本発明は、上記課題を解決するためになされたもので、フォトダイオードの感度をはじめとする諸特性を向上させるCMOSエリアセンサに代表される光電変換装置及び撮像システムを提供するものである。

【課題を解決するための手段】

【0009】

本発明の第1の側面は、第一導電型の電荷蓄積領域と複数の第二導電型の不純物領域とを含んで構成される光電変換素子と、前記光電変換素子にて生じた電荷を転送する転送MOSトランジスタと、前記転送MOSトランジスタによって電荷が転送される第一導電型の不純物領域と、が第一導電型の半導体基板に配されたCMOS型光電変換装置に係り、前記複数の第二導電型の不純物領域は、前記電荷蓄積領域の下から前記転送MOSトランジスタのゲート電極の下まで連続して配され、且つ、少なくとも第1の不純物領域と、該第1の不純物領域と前記電荷蓄積領域との間に配された第2の不純物領域と、該第2の不純物領域と前記電荷蓄積領域との間に配された第3の不純物領域と、を含み、前記第1の不純物領域、前記第2の不純物領域および前記第3の不純物領域は、前記半導体基板に対するイオン注入によって形成され、前記第1の不純物領域の不純物濃度ピークの濃度C1と、前記第2の不純物領域の不純物濃度ピークの濃度C2と、前記第3の不純物領域の不純物濃度ピークの濃度C3とが、 $C_2 < C_3 < C_1$ の関係を満たし、前記CMOS型光電変換装置は、前記第3の不純物領域の上かつ前記転送MOSトランジスタのゲート電極の下に配された第二導電型のチャネルドープ領域を有していることを特徴とする。

【0010】

本発明の第2の側面は、第一導電型の電荷蓄積領域と第二導電型の不純物領域とを含んで構成される光電変換素子と、前記光電変換素子にて生じた電荷を転送する転送MOSトランジスタと、前記転送MOSトランジスタによって電荷が転送される第一導電型の不純

10

20

30

40

50

物領域と、が第一導電型の半導体基板に配されたC M O S型光電変換装置に係り、前記第二導電型の不純物領域は、前記電荷蓄積領域の下から前記転送M O Sトランジスタのゲート電極の下まで連続して配され、且つ、前記半導体基板の深部から前記電荷蓄積領域に向かって順に位置する第1の不純物濃度ピークと、第2の不純物濃度ピークと、第3の不純物濃度ピークとを少なくとも有し、前記第二導電型の不純物領域は、前記半導体基板に対するイオン注入によって形成され、前記第1の不純物濃度ピークの濃度C 1と、前記第2の不純物濃度ピークの濃度C 2と、前記第3の不純物濃度ピークの濃度C 3とが $C_2 < C_3 < C_1$ の関係を満たし、前記C M O S型光電変換装置は、前記第二導電型の不純物領域の上かつ前記転送M O Sトランジスタのゲート電極の下に配された第二導電型の他の不純物領域を有していることを特徴とする。

10

#### 【発明の効果】

##### 【0011】

本発明によれば、光電変換されたキャリアを基板側に損失することなく、また基板からのノイズ電荷の入り込みを低減できるため、感度を向上させることが可能となり、更に、飽和電荷数、転送効率の向上が可能となる。

##### 【発明を実施するための最良の形態】

##### 【0012】

本発明は、光電変換素子を形成するフォトダイオードの第1の導電型の不純物領域を、不純物濃度ピークを有する不純物領域の複数で形成し、第1の不純物領域の不純物濃度ピーク濃度C 1と、該第1の不純物領域よりも基板表面側に配された第2の不純物領域の不純物濃度ピーク濃度C 2と、該第2の不純物領域よりも基板表面側に配され、フォトダイオードを形成する第2の導電型の不純物領域に近接（接して）して形成された第3の不純物領域の不純物濃度ピークの濃度C 3を、 $C_2 < C_3 < C_1$ とするものである。

20

##### 【0013】

このような構成によれば、光電変換されたキャリアを基板側に損失することなく、また基板からのノイズ電荷の入り込みを低減できるため、感度を向上させることが可能となり、更に、飽和電荷数、転送効率の向上が可能となる。

##### 【0014】

また、光電変換素子を形成するフォトダイオードの第1の導電型の不純物領域を、不純物濃度ピークを有する不純物領域の複数で形成し、該複数の不純物領域のうちフォトダイオードを形成する第2の導電型の不純物領域に近接（接して）して形成された不純物領域の不純物濃度ピークの濃度Cを、 $3 \times 10^{15} < C < 2 \times 10^{17} \text{ cm}^{-3}$ とする構成によれば、飽和電荷数、転送効率の向上を達成することが可能となる。

30

##### 【0015】

以下、本発明の実施の形態について図面を用いて詳細に説明する。

##### 【0016】

###### （第一の実施形態）

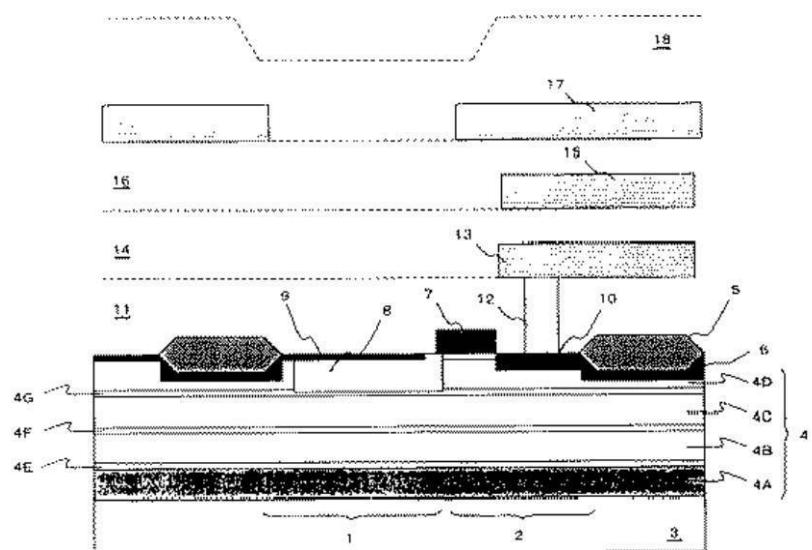

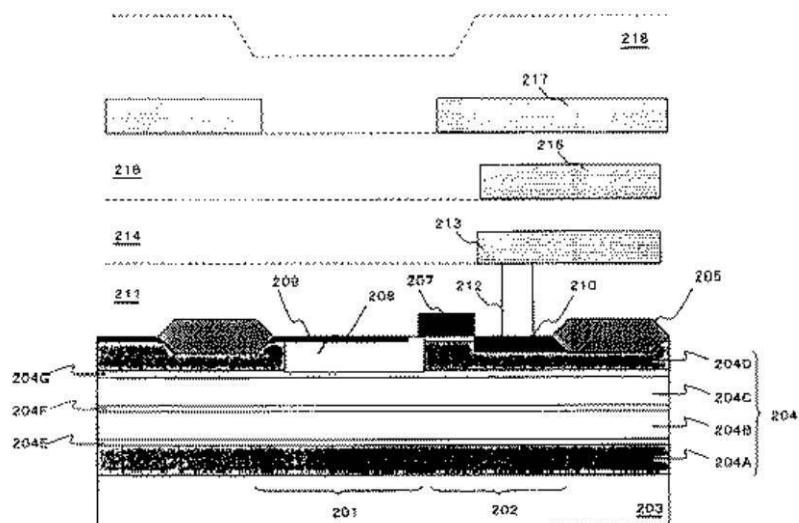

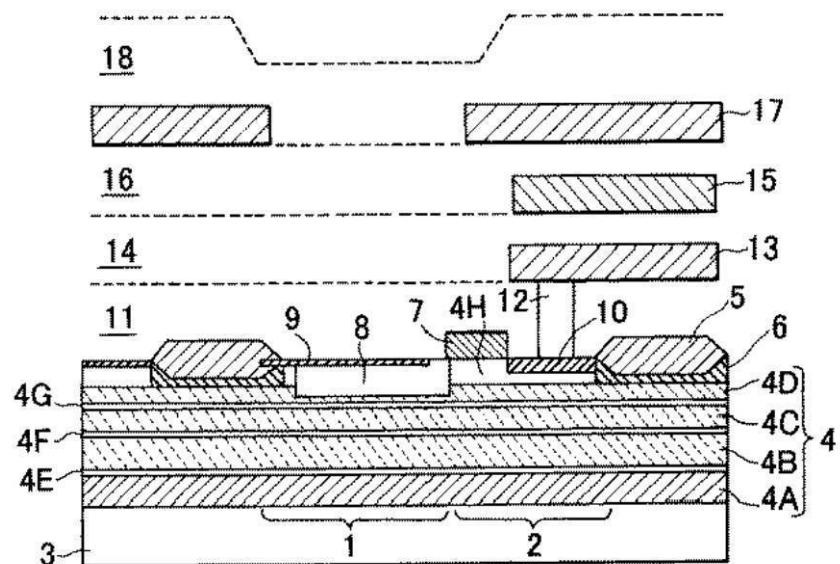

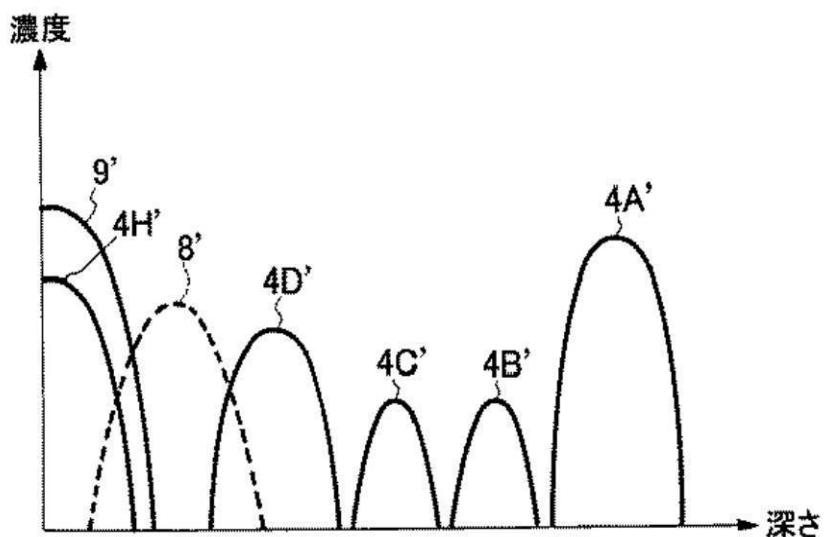

図1は本発明の実施形態を説明する断面模式図であり、C M O Sエリアセンサの光電変換素子となるフォトダイオード部1と転送M O Sトランジスタ部2を示したものである。3はN型シリコン基板、4は複数のP型不純物領域を含むP型ウエルであり、本実施形態では、4 A～4 Dの不純物領域を有する。また、不純物領域4 A～4 Dの各領域間には、N型不純物領域4 E～4 Gが挟まれている。

40

##### 【0017】

7は転送M O Sトランジスタのゲート電極、8はフォトダイオードを形成するN型不純物領域（電荷蓄積領域）、9はフォトダイオードを埋め込み構造とするための表面P型不純物領域（表面電荷再結合領域）、5は素子分離のためのフィールド酸化膜、10は電荷蓄積領域8からの電荷が転送されるフローティングディフュージョンとして機能するN型不純物領域である。

##### 【0018】

4 A～4 DのP型不純物領域よりフォトダイオードを形成するためのP型不純物領域を形

50

成しており、8のN型不純物領域よりフォトダイオードを形成するためのN型不純物領域を形成している。11はゲート電極と第一の配線層を絶縁するための層間絶縁膜として機能するシリコン酸化膜、12はコンタクトプラグ、13は第一の配線層、14は第一の配線層と第二の配線層を絶縁する層間絶縁膜、15は第二の配線層、16は第二の配線層と第三の配線層を絶縁する層間絶縁膜、17は第三の配線層、18はパッシベーション膜である。

#### 【0019】

さらに、パッシベーション膜18の上層に不図示のカラーフィルター層、感度向上のためのマイクロレンズを形成する。本実施形態では配線層は3層形成したが、センサの仕様によっては、光学特性を確保する上で、配線層を1層、あるいは2層とすることも本発明の主旨と矛盾はない。また更に受光率をあげるために、カラーフィルター層よりも受光部側にレンズ(層内レンズ)を設けてもよい。10

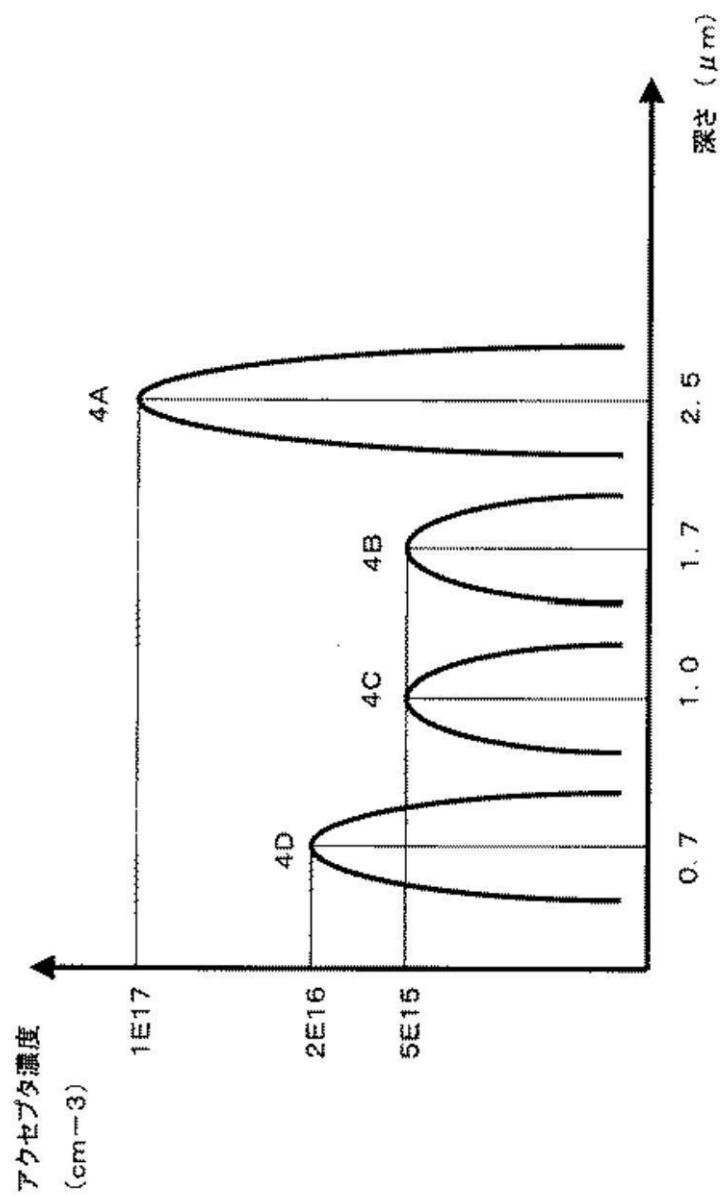

#### 【0020】

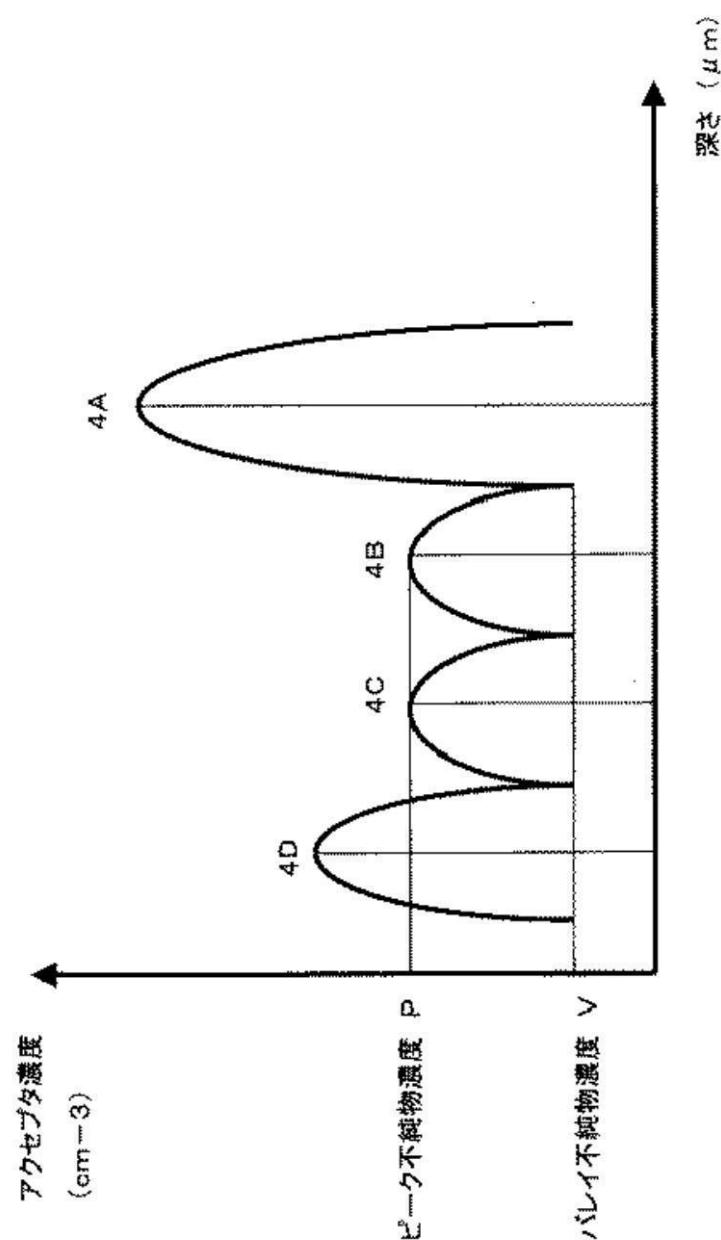

図3に示すように、不純物領域4Aはその不純物濃度ピークの濃度が $1 \times 10^{16} \text{ cm}^{-3}$ から $1 \times 10^{18} \text{ cm}^{-3}$ であり、ピークの位置する深さは基板表面から $2.0 \mu\text{m}$ から $4.0 \mu\text{m}$ のところにある。不純物領域4Bはその不純物濃度ピークの濃度が $1 \times 10^{15} \text{ cm}^{-3}$ から $5 \times 10^{16} \text{ cm}^{-3}$ であり、ピークの深さは基板表面から $1.2 \mu\text{m}$ から $2.5 \mu\text{m}$ のところにある。

#### 【0021】

不純物領域4Cはその不純物濃度ピークの濃度が $1 \times 10^{15} \text{ cm}^{-3}$ から $5 \times 10^{16} \text{ cm}^{-3}$ であり、ピークの深さは $0.8 \mu\text{m}$ から $1.5 \mu\text{m}$ のところにある。不純物領域4Dはその不純物濃度ピークの濃度が $2 \times 10^{15} \text{ cm}^{-3}$ から $2 \times 10^{17} \text{ cm}^{-3}$ であり、ピークの深さは $0.5 \mu\text{m}$ から $1.0 \mu\text{m}$ のところにある。これら範囲に関しては後述する。20

#### 【0022】

また、本実施形態ではCMOSエリアセンサに関して説明したが、CCDに適用しても同様の効果がある。その場合は、フローティングディフュージョン10の領域がVCCDに置き換わる。

#### 【0023】

ここで不純物領域4A～4Dの機能を説明する。浅い部分(基板表面側)に位置する不純物領域4B～4Dでは、光キャリアを画素内のフォトダイオードに導く繋ぎ部分を形成し、これらよりも深い部分の不純物領域層4Aで、分光感度を決めるポテンシャルピークを形成する。ここで最深部の不純物領域4Aの濃度を不純物領域4Bの濃度よりも大きく、好ましくは3倍以上の濃度、より好ましくは5倍以上とすることで、両者の間にポテンシャルバリアが形成され、入射した光により発生したキャリアを基板方向に損失することなく効率よくフォトダイオードに導くことができるため、感度の向上が可能となる。電子が熱拡散する上でポテンシャル障壁となるか否かは、概ね次の式で表現することが可能である。30

#### 【0024】

$V_b = (kT/q) \cdot 1n(N1/N2) < kT/q$  ここで $V_b$ は障壁、 $k$ はボルツマン定数、 $T$ は温度、 $q$ は素電荷、 $N1$ は障壁のピーク濃度であり $N2$ は障壁手前の濃度である。不等号の示す領域においては、熱励起によって電荷は障壁を乗り越えることができる。すなわち、 $N1/N2 < e$ の場合(概ね3以下の場合)においては障壁を乗り越えることができる。40

#### 【0025】

従って、 $N1/N2$ が3を超えるときはポテンシャル障壁が存在し、さらに、 $N1/N2$ が5を超えるときはポテンシャル障壁を超えるキャリアはほぼ無視できる。

#### 【0026】

また、不純物領域4D、4Cの濃度や深さを制御することにより、N型電荷蓄積領域8で保持できる飽和電荷数を制御することもできる。濃度に関して、4A～4Dの濃度の関50

係に関して述べると、第1の不純物領域(4A)の不純物濃度ピーク濃度C1と、該第1の不純物領域よりも基板表面側に配された第2の不純物領域(4B、4C)の不純物濃度ピーク濃度C2と、該第2の不純物領域よりも基板表面側に配され、フォトダイオードを形成する第2の導電型の不純物領域に近接(接して)して形成された第3の不純物領域(4D)の不純物濃度ピークの濃度C3を、 $C_2 < C_3 < C_1$ とすることによって、基板への電荷の損失の低減による感度向上と、転送効率の向上の両立が可能となる。

#### 【0027】

感度向上にはより深いウエルを形成するほうが、光を吸収できる不純物領域の容積が増えるため望ましいが、それを実現するためにイオン注入の回数を増加させることは、工期短縮という観点からは逸脱してしまう。そこで、ウエルとは反対導電型の領域4E～4Gがビルトインポテンシャルにより完全に空乏化しており、動作上問題とならないよう、領域4E～4Gが残るように、各不純物領域4A～4Dのイオン注入のエネルギーを設定することによってイオン注入回数を最低限で複数の不純物領域を形成することが可能となる。

10

#### 【0028】

本実施形態では、複数の不純物領域からなるP型ウエル4は電荷を電荷蓄積領域に効率良く送るための4B～4Dと最深部ウエル層の4層構成であるが、本実施形態で4B～4Dとされている不純物領域は必要とする感度に応じてウエル深さを設定するべきものであるため、その数は特に設定されない。また少なくとも一層の繋ぎウエルを形成すれば、感度向上の効果は得られる。すなわち、複数の不純物領域は、第1の不純物領域(4A)と、該第1の不純物領域よりも基板表面側に配された第2の不純物領域(4B、4C、4D)の少なくとも一つ)を含み、該第2の不純物領域よりも第1の不純物領域の方が不純物濃度ピークの濃度が高いことが好ましい。

20

#### 【0029】

複数のP型不純物領域に挟まれたN型不純物領域4E～4Gは存在しなくても問題はない。また、P型不純物領域を上下に離して配設した場合に二つのP型不純物領域が接していないなく、結果として、P型不純物領域の間にN型不純物領域が存在しても問題ない。但し、この場合は、二つのP型不純物領域に挟まれているN型不純物領域が空乏化していることが必要である。

30

#### 【0030】

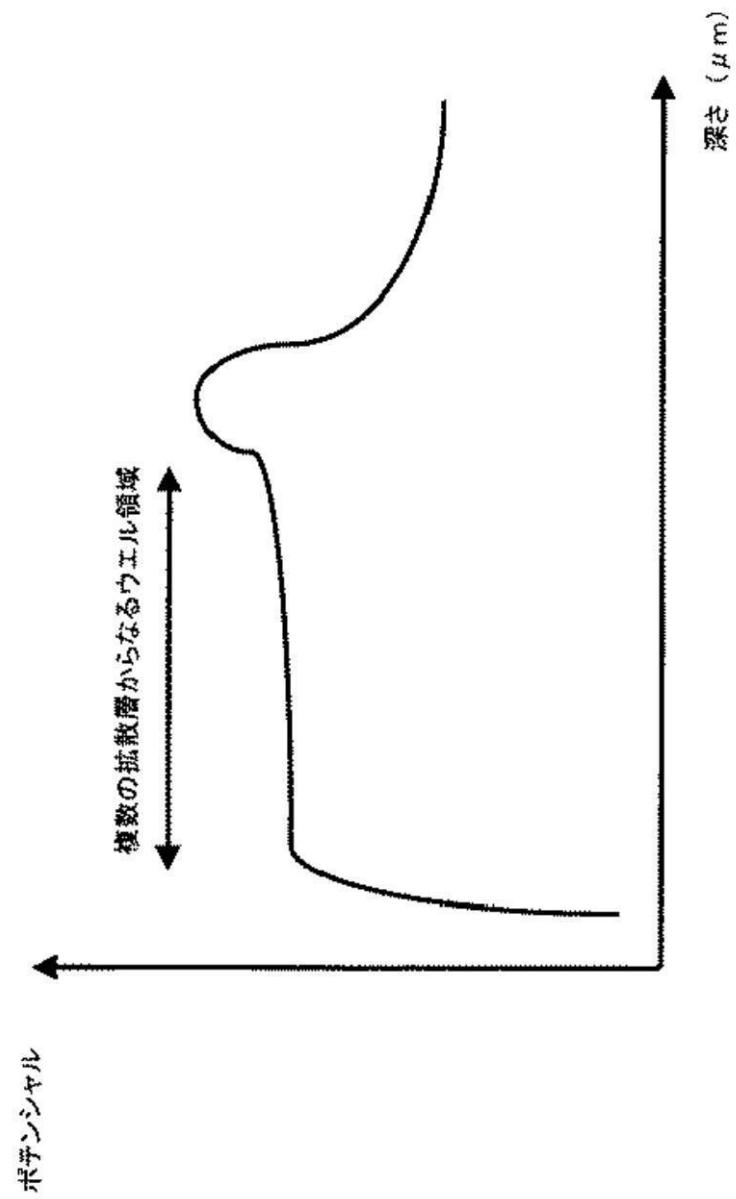

図2はウエル内のポテンシャル図である。キャリアを電子として示している。複数のp型不純物領域は各領域が接していないなくても問題がないが、その場合は間にあるn型領域4E～4Gが空乏化することにより、ポテンシャルプロファイルが概略平坦になっていることが求められる。平坦でない場合は、深いウエル層付近で発生した電子がポテンシャルバリアにより電子蓄積領域に移動する効率が悪化し、結果的に感度が低下するからである。

#### 【0031】

図3にフォトダイオードを形成するP型ウエルの不純物プロファイルを示す。本実施形態では、P型不純物領域4A～4Dがそれぞれ不純物濃度ピークをもっており、不純物領域4A～4Dはフォトダイオード特性に及ぼす影響が異なる。

40

#### 【0032】

不純物領域4Aは感度を向上させる目的でポテンシャルピークをもたせる必要があるため、不純物濃度にピークが必要である。

#### 【0033】

不純物領域4Bは、図2に示すようなポテンシャルバリアを形成するために、不純物領域4Aよりも不純物濃度ピークの不純物濃度が低い必要があり、不純物領域4Aが最大のポテンシャルピークをもつように不純物濃度ピークを設定する必要がある。

#### 【0034】

不純物領域4Cは後述する不純物領域4Dの不純物濃度プロファイルに影響を及ぼさないようにすることと、4Aと4Bの関係を維持することが必要である。

50

**【 0 0 3 5 】**

基板表面近くにある不純物領域 4 D はフォトダイオードの電荷蓄積領域と接していればよく、電荷蓄積領域で蓄積可能な飽和電子数や電荷蓄積領域からフローティングディフュージョンへの転送特性を独立に制御することが可能である。

**【 0 0 3 6 】**

各不純物領域の濃度ピークの位置は、これに限られるものではなく、特に 4 D は N 型不純物領域 8 の下（基板深さ方向に深い）を覆うように形成されてもよい。

**【 0 0 3 7 】**

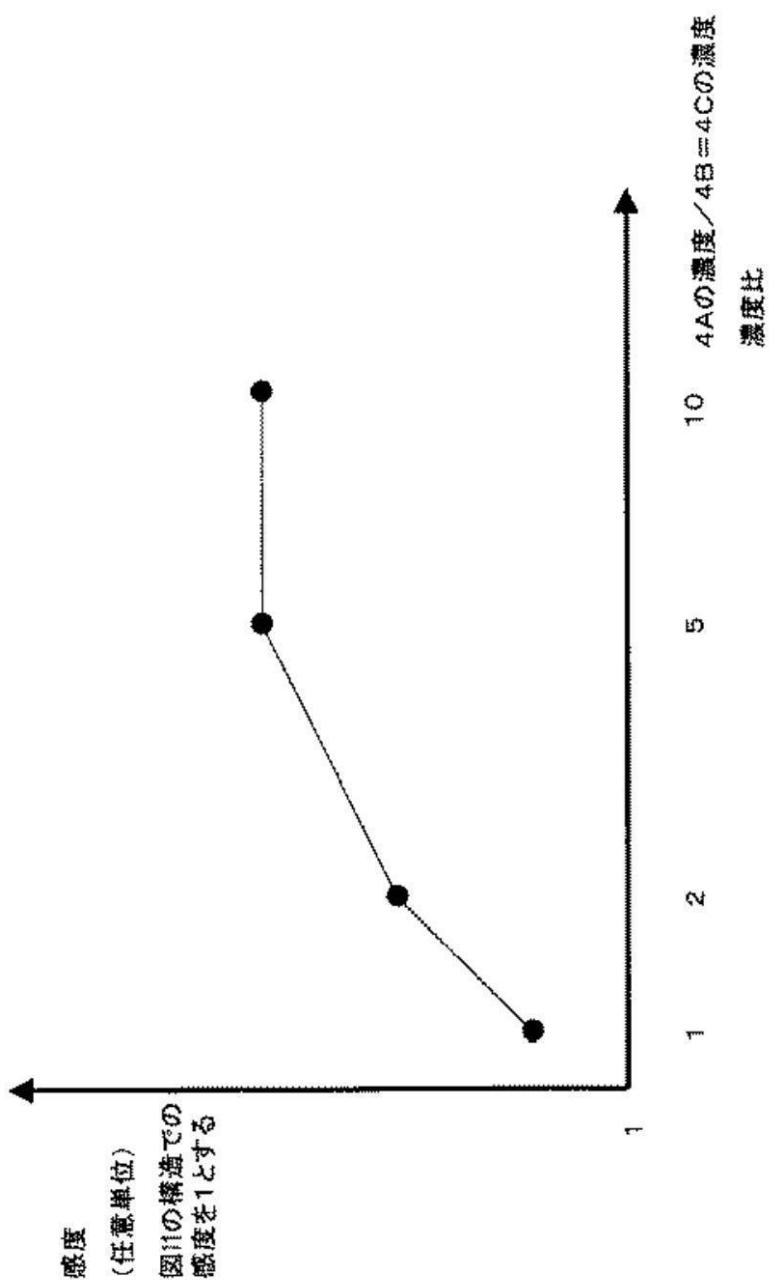

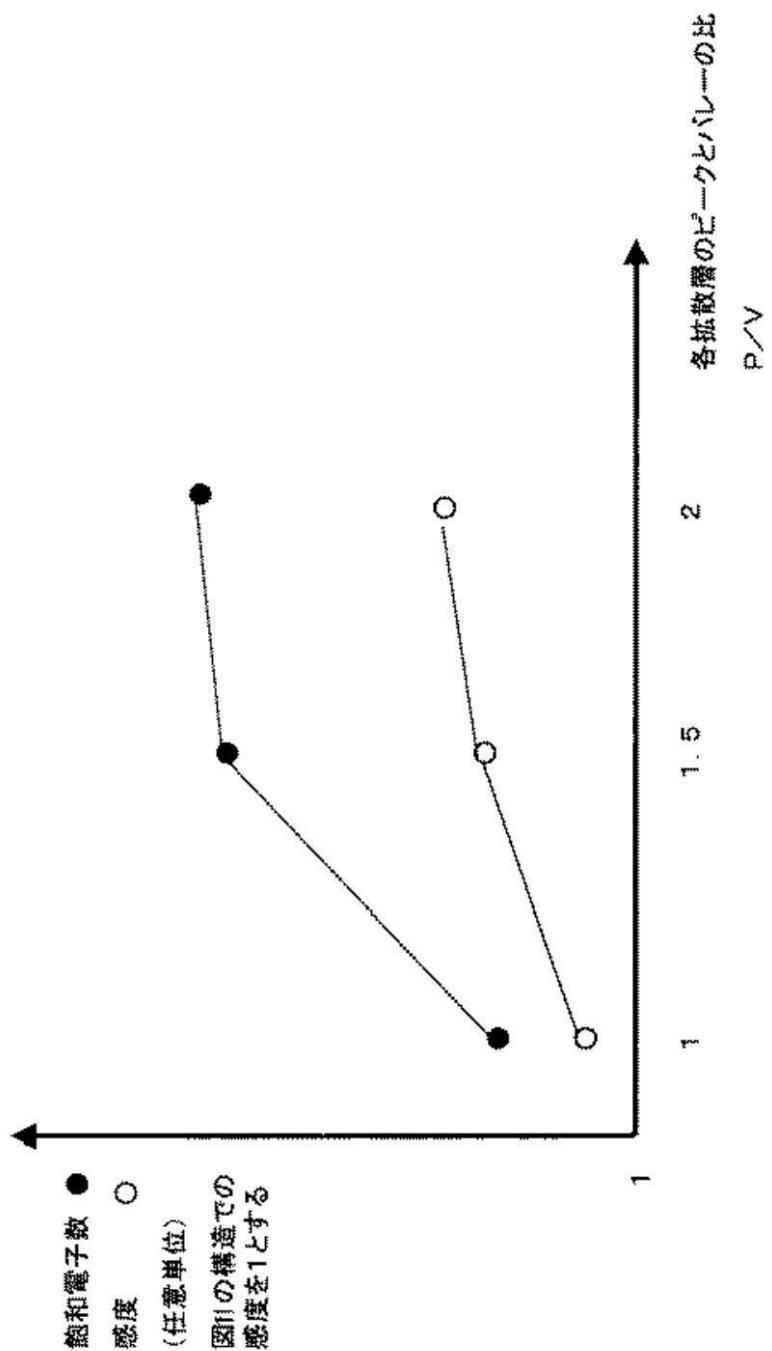

次に、4 A とそれよりも基板表面側に位置する 4 B , 4 C のピーク濃度の関係を説明する。図 4 は不純物領域 4 A の不純物ピーク濃度と不純物領域 4 B , 4 C の不純物ピーク濃度の関係を示している。ここでは、不純物領域 4 B と不純物領域 4 C のピーク濃度は等しいとしている。これらの条件により上述した不純物濃度およびピークの深さの範囲が決まる。

10

**【 0 0 3 8 】**

( 4 A の濃度 ) / ( 4 B の濃度 ) が 1 より大きければ有意差のある感度向上が認められ、2 以上あれば一層感度向上に効果があり、さらに 5 以上あれば十分な感度向上が認められる。

**【 0 0 3 9 】**

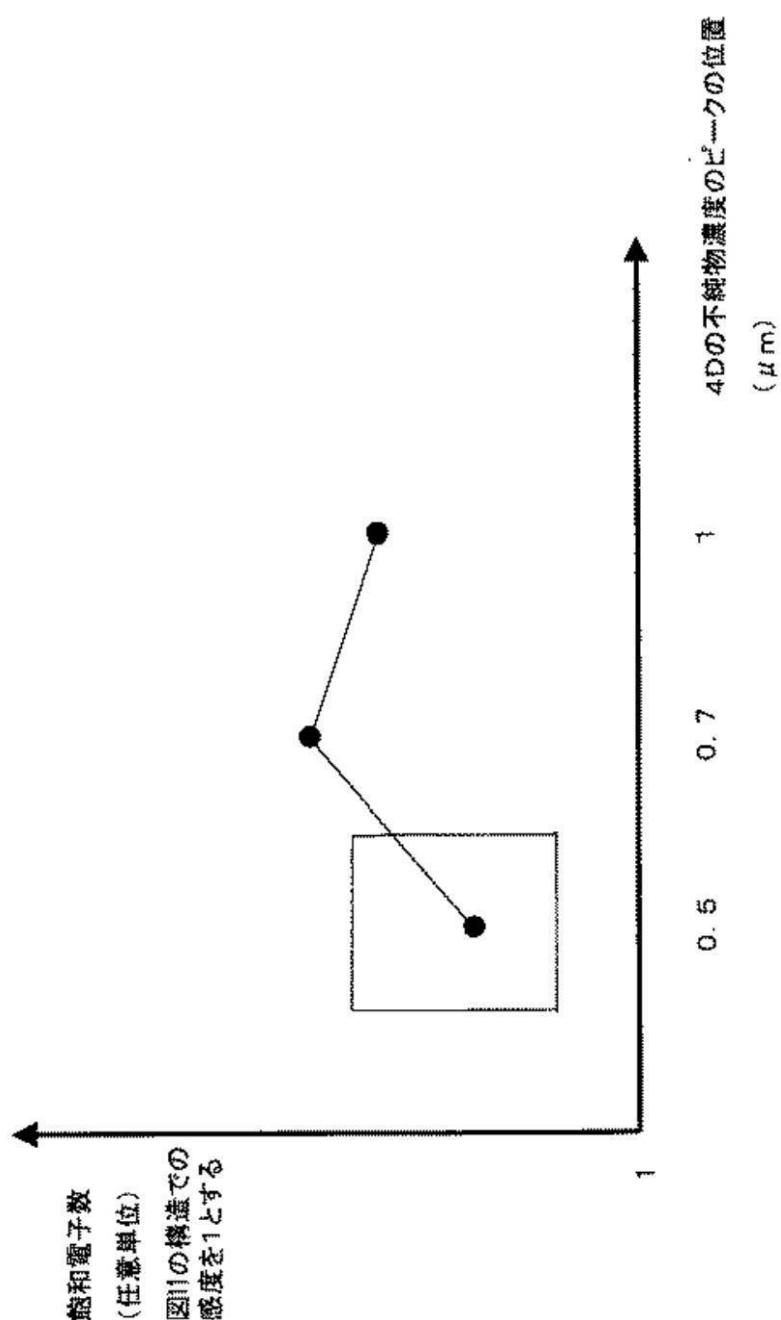

次に、不純物領域 8 に近接する 4 D のピークの位置に関して説明する。図 5 は不純物領域 4 D の不純物濃度ピークの深さと飽和電子数の関係を示している。この図より、不純物領域 4 D の拡散層の深さは最適な領域があることがわかる。具体的には、0.5 ~ 1.0 μ m あれば図 11 の構成に比べて感度は向上する。

20

**【 0 0 4 0 】**

図 6 は複数の不純物領域からなる P 型ウエルの不純物濃度のプロファイルを示し、図 7 はその濃度プロファイルと飽和電子数及び感度の関係を示している。不純物濃度ピークを持った不純物領域を高温の熱処理を行うことにより、平坦な不純物濃度プロファイルにすると（各拡散層の P / V が 1 に近くなると）、飽和電子数及び感度のいずれも特性が劣化する。これは、高温の熱処理により、基板の深い位置に配された不純物領域の不純物濃度ピークとそれより浅い不純物領域の不純物濃度の比が小さくなることと、浅い不純物領域の不純物濃度プロファイルのピーク位置が不確定になるためである。

30

**【 0 0 4 1 】**

以上から、不純物濃度ピークを有する複数の不純物領域を含むウエル中にフォトダイオードを形成することにより、感度の向上と飽和電子数の向上が両立する光電変換装置を製造可能である。

**【 0 0 4 2 】**

次に、図 1 の断面図を元に製造工程を説明する。シリコンからなる基板 3 上に通常の L O C O S 分離法あるいはリセス L O C O S 法などによりフィールド酸化膜 5 を形成する。そして、フィールド酸化膜 5 下にチャンネルトップ層 6 を形成後、複数の不純物領域からなる P 型ウエル 4 は、高エネルギーイオン注入装置を用いて、本実施形態では 4 回の P 型不純物（ボロン等）を深い領域より順次注入し、その後ドライブインのような高温の熱処理を行わないことによって形成する。この後の熱処理は最高でも 950 度である。

40

**【 0 0 4 3 】**

この P 型ウエル 4 は熱拡散を行わないため、それぞれの不純物領域の濃度を制御することが容易となる。上層部にある不純物領域 4 B ~ 4 D を低濃度にすることによって、この箇所のポテンシャルを低く出来るため、感度の向上、ならびに不純物領域 4 A とのポテンシャル差を形成しやすくなる。そして、ポリシリコン電極 7 を形成した後、イオン注入により、フォトダイオードの N 型電荷蓄積領域となる不純物領域 8 、及び P 型表面層となる不純物領域 9 、フローティングディフュージョンとなる N 型不純物領域 10 を形成する。

**【 0 0 4 4 】**

コンタクト開口工程以降の製造方法は従来の C M O S エリアセンサと同様であるので、

50

省略する。

#### 【0045】

以上のように、光電変換素子を形成するフォトダイオードの第1の導電型の不純物領域を、不純物濃度ピークを有する不純物領域の複数で形成し、第1の不純物領域の不純物濃度ピーク濃度C1と、該第1の不純物領域よりも基板表面側に配された第2の不純物領域の不純物濃度ピーク濃度C2と、該第2の不純物領域よりも基板表面側に配され、フォトダイオードを形成する第2の導電型の不純物領域に近接(接して)して形成された第3の不純物領域の不純物濃度ピークの濃度C3を、 $C_2 < C_3 < C_1$ とすることによって、吸収された光キャリアを基板方向に損失することなく効率よくフォトダイオードに導くことができ、感度向上が可能となり、更に、電荷蓄積領域からフローティングディフュージョン(読み出し領域)への転送効率を向上させることができるとなる。10

#### 【0046】

##### (第二の実施形態)

図8に本実施形態の断面模式図を示す。第一の実施形態と異なる箇所は、P型の複数の不純物領域からなるウエル204が、素子分離フィールド酸化膜205下、及び隣接画素部にまで連続して形成されている点であり、フィールド酸化膜下に素子分離のためのチャネルストップ領域が存在しない。

#### 【0047】

これは、複数の不純物領域を含むP型ウエル204中の不純物領域204Dが隣接画素間との素子分離の機能をも備えることによって、素子分離に必要なイオン注入をウエルを形成する不純物領域と同時にを行うことができ、工程、ならびにマスク数を減らすことが出来る。不純物領域204Dより深い位置にある204C、204Bの濃度を低くし、不純物領域204Aをその濃度より大きく、好ましくは2倍以上、より好ましくは5倍以上の濃度に設定すれば、素子分離特性を維持しつつ、第一の実施形態と同様に感度の向上は得られる。20

#### 【0048】

##### (第三の実施形態)

本実施形態の模式的断面図を図12に、フォトダイオード部の不純物プロファイルを模式的に示した図を図13に示す。本実施形態においては、電荷蓄積領域として機能する電荷蓄積領域が、該電荷蓄積領域に近接する4Dの一部に埋め込まれるように形成されている。このように形成することによって、空乏層の広がりを4D内に好適にとどめることができます。30

#### 【0049】

また、図12において、4Hで示されるP型不純物領域は、転送MOSトランジスタのゲート下のチャネル部に、チャネルドープ層として形成される領域と、4DのP型不純物領域が連続するよう形成されることによってP型不純物領域として形成される。4Hは転送MOSトランジスタが正常に動作するために必要な領域であり、N型不純物領域が存在しないようにすることが重要である。

#### 【0050】

具体的に、図13の不純物プロファイルを用いて説明する。4AはP型不純物領域4A、4BはP型不純物領域4Bに、4CはP型不純物領域4Cに、4DはP型不純物領域4Dに、8はN型不純物領域8に、9はP型不純物領域9に、4HはP型不純物領域4Hにそれぞれ対応するものである。転送MOSトランジスタ下では、チャネルドープ領域4HとP型不純物領域4Dの形成条件を調整することによって、N型不純物領域が形成されないような構造となっている。このような構造によれば、上記実施形態と同様に感度向上が可能となり、更に、転送MOSトランジスタの転送効率も向上させることが可能となる。40

#### 【0051】

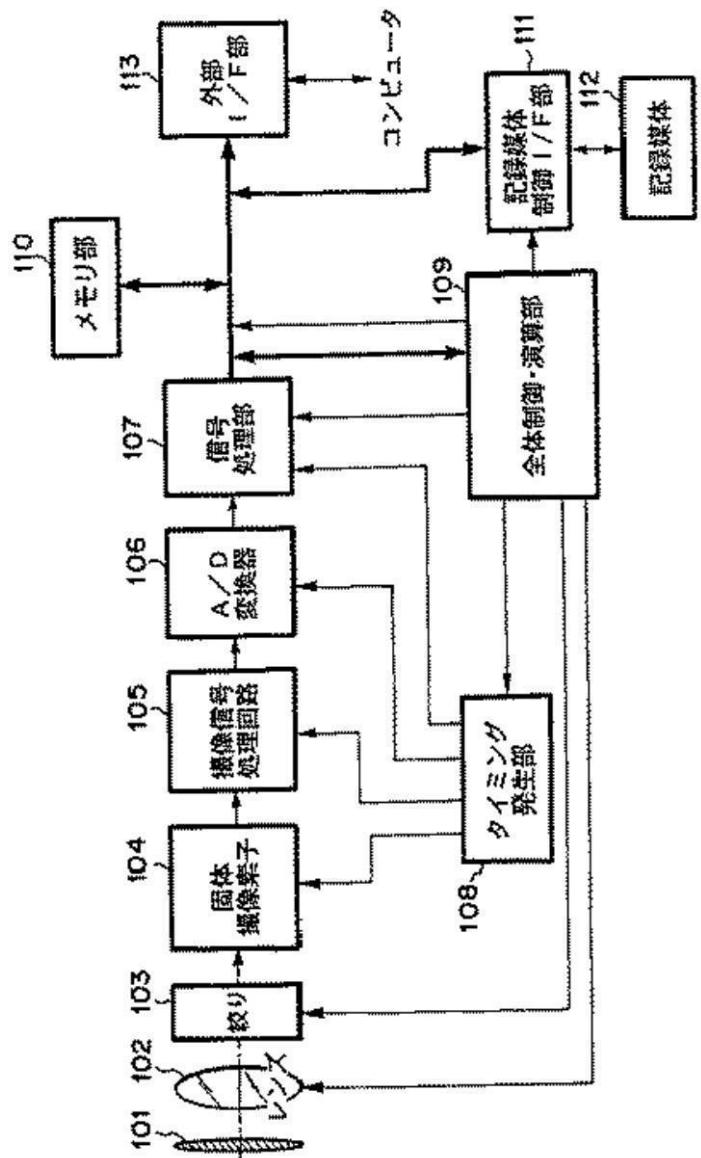

##### (撮像システムへの応用)

次に、上記実施形態の光電変換装置を用いた撮像システムについて説明する。図14は50

本発明による光電変換装置をスチルビデオカメラに使用する場合の一実施形態を示すプロック図である。

**【0052】**

図14において、101はレンズのプロテクトとメインスイッチを兼ねるバリア、102は被写体の光学像を固体撮像素子104に結像させるレンズ、103はレンズ102を通った光量を可変するための絞り、104はレンズ102で結像された被写体を画像信号として取り込むため固体撮像素子（本発明の光電変換装置に対応する）、106は固体撮像素子104より出力される画像信号のアナログ・ディジタル変換を行うA/D変換器、107はA/D変換器106より出力された画像データに各種の補正を行ったりデータを圧縮する信号処理部、108は固体撮像素子104、撮像信号処理回路105、A/D変換器106、信号処理部107に各種タイミング信号を出力するタイミング発生部、109は各種演算とスチルビデオカメラ全体を制御する全体制御・演算部、110は画像データを一時的に記憶するためのメモリ部、111は記録媒体に記録又は読み出しを行うためのインターフェース部（記録媒体制御I/F部）、112は画像データの記録又は読み出しを行うための半導体メモリ等の着脱可能な記録媒体、113は外部コンピュータ等と通信するためのインターフェース部（外部I/F部）である。

10

**【0053】**

次に、撮影時のスチルビデオカメラの動作について説明する。バリア101がオープンされると、メイン電源がオンされ、次にコントロール系の電源がオンされ、更に、A/D変換器106等の撮像系回路の電源がオンされる。

20

**【0054】**

それから、露光量を制御するために、全体制御・演算部109は絞り103を開放にし、固体撮像素子104から出力された信号はA/D変換器106でA/D変換された後、信号処理回路107に入力される。そのデータを基に露出の演算を全体制御・演算部109で行う。

**【0055】**

この測光を行った結果により明るさを判断し、その結果に応じて全体制御・演算部109は絞り103を制御する。

**【0056】**

次に、固体撮像素子104から出力された信号をもとに高周波成分を取り出し被写体までの距離の演算を全体制御・演算部109で行う。その後、レンズ102を駆動して合焦か否かを判断し、合焦していないと判断したときは、再びレンズ102を駆動し測距を行う。

30

**【0057】**

そして、合焦が確認された後に本露光が始まる。露光が終了すると、固体撮像素子104から出力された画像信号はA/D変換器106でA-D変換され、信号処理部107を通り全体制御・演算部109によりメモリ部110に書き込まれる。その後、メモリ部110に蓄積されたデータは、全体制御・演算部109の制御により記録媒体制御I/F部111を通り半導体メモリ等の着脱可能な記録媒体112に記録される。また、外部I/F部113を通り直接コンピュータ等に入力して画像の加工を行ってもよい。

40

**【産業上の利用可能性】**

**【0058】**

本発明はCCDやCMOSエリアセンサの感度を向上できるので、高感度のスチルカメラやビデオカメラに用いることができる。

**【図面の簡単な説明】**

**【0059】**

**【図1】**本発明の第一の実施形態のCMOSエリアセンサの断面図である。

**【図2】**フォトダイード部ウエル内のポテンシャル図である。

**【図3】**第一の実施形態の不純物濃度プロファイルを示す図である。

**【図4】**拡散層4Aの濃度と拡散層4B, 4Cとの比と、感度との関係を示す特性図であ

50

る。

【図5】拡散層4Dの濃度ピーク位置と飽和電子数との関係を示す特性図である。

【図6】第一の実施形態の不純物濃度プロファイルを説明するための図である。

【図7】各拡散層のピークとバレーの比と、飽和電子数との関係を示す図である。

【図8】本発明の第二の実施形態の光電変換装置の断面図である。

【図9】従来のCMOSエリアセンサの断面図である。

【図10】従来のP型ウエル濃度分布の模式図である。

【図11】従来のP型ウエル濃度分布の模式図である。

【図12】本発明の第三の実施形態の光電変換装置の断面図である。

【図13】第三の実施形態の光電変換装置のフォトダイード部の不純物プロファイルを示す図である。 10

【図14】本発明の光電変換装置をスチルビデオカメラに適用した場合の一実施形態を示すブロック図である。

#### 【符号の説明】

##### 【0060】

|                               |                      |    |

|-------------------------------|----------------------|----|

| 1 , 2 0 1 , 3 0 1             | フォトダイオード部            |    |

| 2 , 2 0 2 , 3 0 2             | 転送MOSトランジスタ部         |    |

| 3 , 2 0 3 , 3 0 3             | 半導体基板 (N型シリコン基板)     |    |

| 4 , 2 0 4 , 3 0 4             | P型ウエル                |    |

| 4 A ~ 4 D , 2 0 4 A ~ 2 0 4 D | 不純物領域                | 20 |

| 4 E ~ 4 G , 2 0 4 E ~ 2 0 4 G | N型不純物領域              |    |

| 4 H                           | P型不純物領域              |    |

| 5 , 2 0 5 , 3 0 5             | フィールド酸化膜             |    |

| 6 , 3 0 6                     | チャンネルストップ層           |    |

| 7 , 2 0 7 , 3 0 7             | 転送用MOSトランジスタのゲート電極   |    |

| 8 , 2 0 8 , 3 0 8             | N型不純物領域 (電荷蓄積領域)     |    |

| 9 , 2 0 9 , 3 0 9             | 表面P型不純物領域            |    |

| 1 0 , 2 1 0 , 3 1 0           | N型不純物領域              |    |

| 1 1 , 2 1 1 , 3 1 1           | シリコン酸化膜              |    |

| 1 2 , 2 1 2 , 3 1 2           | コントラクトプラグ            | 30 |

| 1 3 , 2 1 3 , 3 1 3           | 第一の配線層               |    |

| 1 4 , 2 1 4 , 3 1 4           | 第一の配線層と第二の配線層間の層間絶縁膜 |    |

| 1 5 , 2 1 5 , 3 1 5           | 第二の配線層               |    |

| 1 6 , 2 1 6 , 3 1 6           | 第二の配線層と第三の配線層間の層間絶縁膜 |    |

| 1 7 , 2 1 7 , 3 1 7           | 第三の配線層               |    |

| 1 8 , 2 1 8 , 3 1 8           | パッシベーション膜            |    |

| 1 0 1                         | バリア                  |    |

| 1 0 2                         | レンズ                  |    |

| 1 0 3                         | 絞り                   |    |

| 1 0 4                         | 固体撮像素子               | 40 |

| 1 0 5                         | 撮像信号処理回路             |    |

| 1 0 6                         | A/D変換器               |    |

| 1 0 7                         | 信号処理部                |    |

| 1 0 8                         | タイミング発生部             |    |

| 1 0 9                         | 全体制御・演算部             |    |

| 1 1 0                         | メモリ部                 |    |

| 1 1 1                         | 記録媒体制御I/F部           |    |

| 1 1 2                         | 記録媒体                 |    |

| 1 1 3                         | 外部I/F部               |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 譲原 浩

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 三島 隆一

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 渡邊 高典

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 市川 武史

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 田村 清一

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 柴山 将隆

(56)参考文献 特開2005-197674 (JP, A)

特開2002-170945 (JP, A)

特開2002-043557 (JP, A)

特開2001-160619 (JP, A)

特開2001-028433 (JP, A)

特開2002-016242 (JP, A)

特開2001-015727 (JP, A)

特開平11-026741 (JP, A)

特開2001-160620 (JP, A)

特開昭63-174358 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H04N 5/335