(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4583776号

(P4583776)

(45) 発行日 平成22年11月17日(2010.11.17)

(24) 登録日 平成22年9月10日(2010.9.10)

(51) Int.Cl.

F 1

|             |               |                  |             |              |                |

|-------------|---------------|------------------|-------------|--------------|----------------|

| <b>G09F</b> | <b>9/30</b>   | <b>(2006.01)</b> | <b>G09F</b> | <b>9/30</b>  | <b>3 3 8</b>   |

| <b>H01L</b> | <b>27/32</b>  | <b>(2006.01)</b> | <b>G09F</b> | <b>9/30</b>  | <b>3 6 5 Z</b> |

| <b>H01L</b> | <b>21/336</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b> | <b>6 1 2 D</b> |

| <b>H01L</b> | <b>29/786</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>27/08</b> | <b>3 3 1 E</b> |

| <b>H01L</b> | <b>27/08</b>  | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b> | <b>6 1 2 C</b> |

請求項の数 2 (全 68 頁) 最終頁に続く

(21) 出願番号

特願2004-37405 (P2004-37405)

(22) 出願日

平成16年2月13日 (2004.2.13)

(65) 公開番号

特開2005-227625 (P2005-227625A)

(43) 公開日

平成17年8月25日 (2005.8.25)

審査請求日

平成19年1月30日 (2007.1.30)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 前川 慎志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 藤井 厳

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 荒井 康行

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】表示装置の作製方法

(57) 【特許請求の範囲】

## 【請求項 1】

基板上に、第1のTFTのゲート電極、第2のTFTのゲート電極、及び第3のTFTのゲート電極を液滴吐出法または印刷法により形成し、

前記第1のTFTのゲート電極、前記第2のTFTのゲート電極、及び前記第3のTFTのゲート電極を覆うゲート絶縁膜を形成し、

前記ゲート絶縁膜上に第1の半導体膜を形成し、

前記第1の半導体膜を介して、前記第1のTFTのゲート電極、前記第2のTFTのゲート電極、及び前記第3のTFTのゲート電極上に、それぞれ保護膜を形成し、

液滴吐出法または印刷法によりレジストを形成し、

前記レジストを用いて前記第1の半導体膜をエッチングして、前記第1のTFTの第1の半導体膜、及び前記第2のTFT及び前記第3のTFTの第1の半導体膜を形成し、

前記第1のTFTの第1の半導体膜、及び前記第2のTFT及び前記第3のTFTの第1の半導体膜上に第2の半導体膜を形成し、

前記第2の半導体膜上に、前記第1のTFTのソース電極及びドレイン電極、前記第2のTFTのソース電極及びドレイン電極の一方、前記第2のTFT及び前記第3のTFTのソース電極及びドレイン電極の他方、及び前記第3のTFTのソース電極及びドレイン電極の一方を液滴吐出法または印刷法により形成し、

前記第1乃至第3のTFTのソース電極及びドレイン電極をマスクとして前記第2の半導体膜をエッチングして、

10

20

前記第1のTFTのソース電極及びドレイン電極の一方の下に第3の半導体膜を形成し、

前記第1のTFTのソース電極及びドレイン電極の他方の下に第4の半導体膜を形成し、

前記第2のTFTのソース電極及びドレイン電極の一方の下に第5の半導体膜を形成し、

前記第2のTFT及び前記第3のTFTのソース電極及びドレイン電極の他方の下に第6の半導体膜を形成し、

前記第3のTFTのソース電極及びドレイン電極の一方の下に第7の半導体膜を形成し、

前記第1のTFTのソース電極及びドレイン電極の他方の上に、液滴吐出法により複数回導電材料を滴下してピラーを形成し、

前記第1のTFTを覆う絶縁膜を塗布法により形成し、

前記絶縁膜表面をエッチングして前記ピラーを露出させ、

前記絶縁膜上に、前記ピラーと電気的に接続する第1の電極を形成し、

前記第1の電極の端部を覆って隔壁を形成し、

前記第1の電極及び前記隔壁上に電界発光層を形成し、

前記電界発光層上に第2の電極を形成することを特徴とする表示装置の作製方法。

## 【請求項2】

基板上に、第1のTFTのゲート電極、第2のTFTのゲート電極、及び第3のTFTのゲート電極を液滴吐出法または印刷法により形成し、

前記第1のTFTのゲート電極、前記第2のTFTのゲート電極、及び前記第3のTFTのゲート電極を覆うゲート絶縁膜を形成し、

前記ゲート絶縁膜上に第1の半導体膜を形成し、

前記第1の半導体膜を介して、前記第1のTFTのゲート電極、前記第2のTFTのゲート電極、及び前記第3のTFTのゲート電極上に、それぞれ保護膜を形成し、

液滴吐出法または印刷法によりレジストを形成し、

前記レジストを用いて前記第1の半導体膜をエッチングして、前記第1のTFTの第1の半導体膜、及び前記第2のTFT及び前記第3のTFTの第1の半導体膜を形成し、

前記第1のTFTの第1の半導体膜、及び前記第2のTFT及び前記第3のTFTの第1の半導体膜上に第2の半導体膜を形成し、

前記第2の半導体膜上に、前記第1のTFTのソース電極及びドレイン電極、前記第2のTFTのソース電極及びドレイン電極の一方、前記第2のTFT及び前記第3のTFTのソース電極及びドレイン電極の他方、及び前記第3のTFTのソース電極及びドレイン電極の一方を液滴吐出法または印刷法により形成し、

前記第1乃至第3のTFTのソース電極及びドレイン電極をマスクとして前記第2の半導体膜をエッチングして、

前記第1のTFTのソース電極及びドレイン電極の一方の下に第3の半導体膜を形成し、

前記第1のTFTのソース電極及びドレイン電極の他方の下に第4の半導体膜を形成し、

前記第2のTFTのソース電極及びドレイン電極の一方の下に第5の半導体膜を形成し、

前記第2のTFT及び前記第3のTFTのソース電極及びドレイン電極の他方の下に第6の半導体膜を形成し、

前記第3のTFTのソース電極及びドレイン電極の一方の下に第7の半導体膜を形成し、

前記第1のTFTのソース電極及びドレイン電極の他方の上に、液滴吐出法により複数回導電材料を滴下してピラーを形成し、

前記第1乃至第3のTFTを覆う絶縁膜を塗布法により形成し、

10

20

30

40

50

前記絶縁膜表面をエッティングして前記ピラーを露出させ、

前記絶縁膜上に、前記ピラーと電気的に接続する第1の電極を形成し、

前記第1の電極の端部を覆って隔壁を形成し、

前記第1の電極及び前記隔壁上に電界発光層を形成し、

前記電界発光層上に第2の電極を形成することを特徴とする表示装置の作製方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、画素毎に発光素子が設けられた表示装置に関する。特に、画素毎にトランジスタが設けられ、発光素子の発光を制御するアクティブマトリクス型の表示装置に関する。10

**【背景技術】**

**【0002】**

発光素子は自ら発光するため視認性が高く、発光素子を用いた表示装置は液晶表示装置(LCD)で必要となるバックライトが要らず、薄型化に最適であると共に、視野角にも制限がない。そのため、発光素子を用いた表示装置は、CRTやLCDに代わる表示装置として注目されており、近年では携帯電話やデジタルスチルカメラ等の電子機器に搭載されるなど、実用化が行われている。

**【0003】**

特に、発光素子としてOLED(Organic Light Emitting Diode)を用いた表示装置(以下、OLED表示装置と表記する)が注目されている。OLED表示装置は、応答性に優れ、低電圧で動作し、また視野角が広い等の利点を有するため、次世代のフラットパネルディスプレイとして注目されている。20

**【0004】**

OLED表示装置は、パッシブマトリクス型とアクティブマトリクス型とに分類できる。アクティブマトリクス型はビデオ信号の入力後も発光素子への電流の供給をある程度維持することができるので、パネルの大型化、高精細化に伴い、アクティブマトリクス型が採用されるようになりつつある。アクティブマトリクス型のOLED表示装置において、各画素への輝度情報の書き込みを電圧信号で行う手法と、電流信号で行う手法とがある。前者を電圧書き込み型、後者を電流書き込み型と呼ぶ。これらの駆動方法について、以下に簡単に説明する。30

**【0005】**

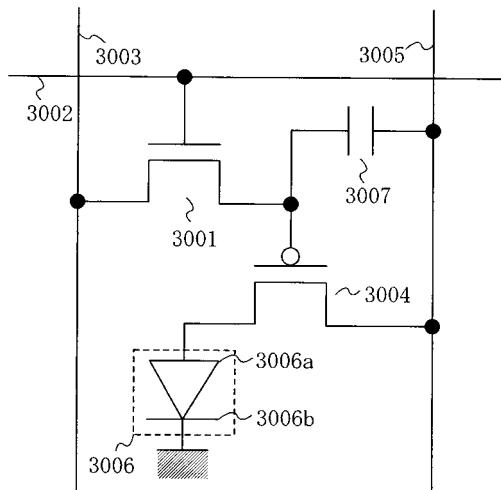

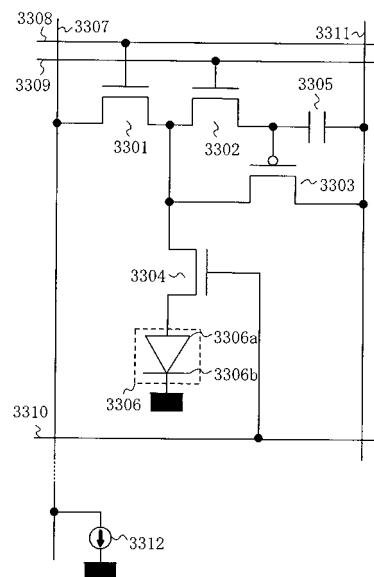

従来の電圧書き込み型のOLED表示装置の画素の構成例を図30に示す。図30において、各画素それぞれに2つのTFT(第1のTFT及び第2のTFT)と、容量素子と、OLED素子とが配置される。第1のTFT(以下、選択TFTと表記する)3001のゲート電極は、ゲート信号線3002に接続され、ソース端子とドレイン端子の一方の端子は、ソース信号線3003に接続されている。選択TFT3001のソース端子とドレイン端子のもう一方は、第2のTFT(以下、駆動TFTと表記する)3004のゲート電極及び容量素子(以下、保持容量と表記する)3007の一方の電極に接続されている。保持容量3007の他方の電極は、電源線3005に接続されている。駆動TFT3004のソース端子とドレイン端子の一方は、電源線3005に接続され、他方は、OLED素子3006の第1の電極3006aに接続されている。OLED素子3006の第2の電極3006bは、一定の電位が与えられている。40

**【0006】**

ここで、OLED素子3006の駆動TFT3004と接続されている側の電極、つまり第1の電極3006aを、画素電極と呼び、第2の電極3006bを対向電極と呼ぶ。図30において、選択TFT3001をnチャネル型TFT、駆動TFT3004をpチャネル型TFT、OLED素子の第1の電極3006aを陽極、第2の電極3006bを陰極とし、第2の電極3006bの電位を0(V)とした構成を示し、この画素を有する50

表示装置の駆動方法について、以下に説明する。

#### 【0007】

ゲート信号線 3002 に信号が入力され、導通状態となった選択 TFT3001において、ソース信号線 3003 より信号電圧が入力される。ソース信号線 3003 に入力される信号電圧によって、保持容量 3007 に電荷が蓄積される。保持容量 3007 に保持された電圧に応じて、電源線 3005 から駆動 TFT3004 のソース・ドレイン間を介して、OLED 素子 3006 に電流が流れ、OLED 素子 3006 は発光する。図 30 に示した構成の画素を有する電圧書き込み型の表示装置には、アナログ方式と、デジタル方式の 2 つの駆動方法がある。以下、この 2 つの方式を、電圧書き込み型アナログ方式、電圧書き込み型デジタル方式と呼ぶことにする。

10

#### 【0008】

電圧書き込み型アナログ方式の駆動方法では、各画素の駆動 TFT3004 のゲート電圧（ゲート・ソース間電圧）を変化させることによって、駆動 TFT3004 のドレン電流を変化させる。こうして、OLED 素子 3006 を流れる電流を変化させ、輝度を変化させる方式である。中間調を表現するためには、ゲート電圧に対して、ドレン電流の変化が大きな領域で駆動 TFT3004 を動作させる。

#### 【0009】

上述の電圧書き込み型アナログ方式の場合、各画素に、同じ電位を有する信号をソース信号線 3003 より入力した場合に、駆動 TFT3004 の電流特性のばらつきによるドレン電流のばらつきによるドレン電流の変動を受けて、OLED 素子 3006 を流れる電流が大きくばらつくという問題がある。駆動 TFT3004 の電流特性のばらつきは、閾値電圧やキャリア移動度等のパラメータに影響されている。

20

#### 【0010】

上述した駆動 TFT3004 の電流特性のばらつきの影響を低減するため、電圧書き込み型デジタル方式の駆動方法が提案されている。電圧書き込み型デジタル方式の駆動方法では、各画素の OLED3006 は一定の輝度で発行 / 非発光の 2 つの状態が選択される。このとき、図 30 における駆動 TFT3004 は、各画素の電源線 3005 と OLED3006 の画素電極 3006a の接続を選択するスイッチとして働く。電圧書き込み型デジタル方式において、OLED3006 が発光している際、駆動 TFT3004 は、ソース・ドレン間電圧 Vds の絶対値がゲート電圧 Vgs から閾値電圧 Vth を引いた電圧 Vgs - Vth の絶対値より小さな動作領域である線形領域、特に、ゲート電圧の絶対値が大きな領域で動作する。この場合、この領域で動作する TFT3004 は、閾値電圧等のばらつきによるドレン電流のばらつきは小さいため、OLED3006 を流れる電流のばらつきを抑え、発行輝度の変動を抑えることができる。

30

#### 【0011】

一方、電流書き込み型アナログ方式の画素を有する表示装置では、各画素に信号線（ソース信号線）により信号電流が入力される。ここで信号電流は、ビデオ信号の輝度情報に線形に対応する電流信号である。入力された電流信号をドレン電流とする TFT のゲート電圧が、容量部に保持される。こうして画素には、ソース信号線より信号電流が入力されなくなった後も、容量部によって記憶された電流を OLED に流し続ける。このようにソース信号線に入力する信号電流を変化させることで OLED に流れる電流を変化させ、OLED の発光輝度を制御し階調を表現する。

40

#### 【0012】

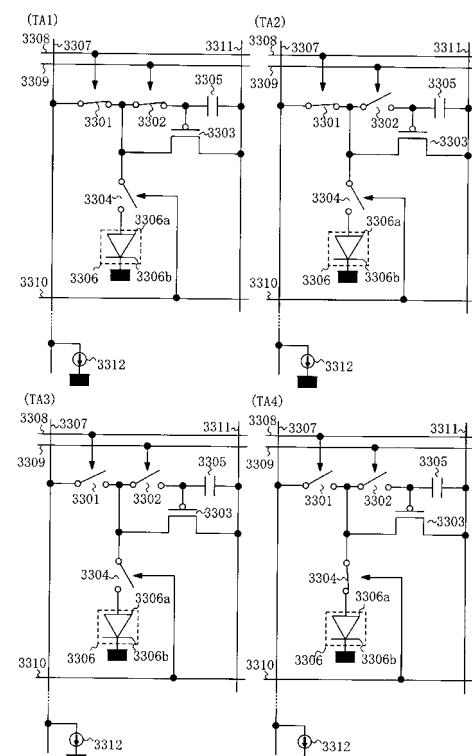

電流書き込み型アナログ方式の画素の例として、図 32 に「IDW '00p235:Active Matrix PolyLED Displays」に開示されている画素構成を示し、その駆動方法を説明する。図 32 において、画素は OLED3306、選択 TFT3301、駆動 TFT3303、容量素子（保持容量）3305、保持 TFT3302、発光 TFT3304、ソース信号線 3307、第 1 のゲート信号線 3308、第 2 のゲート信号線 3309、第 3 のゲート信号線 3310、電源線 3311 によって構成されている。

#### 【0013】

50

選択 TFT 3301 のゲート電極は、第 1 のゲート信号線 3308 に接続されている。選択 TFT 3301 のソース端子とドレイン端子は、一方はソース信号線 3307 に接続され、もう一方は、駆動 TFT 3303 のソース端子またはドレイン端子、保持 TFT 3302 のソース端子またはドレイン端子及び発光 TFT 3304 のソース端子またはドレイン端子に接続されている。保持 TFT 3302 のソース端子とドレイン端子で、選択 TFT 3301 と接続されていない側は、保持容量 3305 の一方の電極及び駆動 TFT 3303 のゲート電極に接続されている。保持容量 3005 の保持 TFT 3302 と接続されていない側は、電源線 3311 に接続されている。保持 TFT 3302 のゲート電極は、第 2 のゲート信号線 3309 に接続されている。駆動 TFT 3303 のソース端子とドレイン端子で、選択 TFT 3301 と接続されていない側は、電源線 3311 に接続されている。発光 TFT 3304 のソース端子とドレイン端子で、選択 TFT 3301 と接続されていない側は、OLED 素子 3306 の一方の電極 3306a と接続されている。発光 TFT 3304 のゲート電極は、第 3 のゲート信号線 3310 に接続されている。OLED 素子 3306 の他方の電極 3306b は、一定の電位に保たれている。

10

#### 【0014】

なお、OLED 素子 3306 の 2 つの電極 3306a 及び 3306b のうち、発光 TFT 3304 に接続されている側の電極 3306a を画素電極と呼び、他方の電極 3306b を対向電極と呼ぶ。図 32 に示す構成の画素において、ソース信号線に入力する信号電流の電流値は、ビデオ信号入力電流源 3312 により制御される構成とする。なお実際には、複数の画素列に対応する複数のビデオ信号入力電流源 3312 は、ソース信号線駆動回路の一部に相当する。ここでは、選択 TFT 3301、保持 TFT 3302 及び発光 TFT 3304 を n チャネル型 TFT とし、駆動 TFT 3303 を p チャネル型 TFT とし、画素電極 3306a を陽極とした構成の画素を示している。

20

#### 【0015】

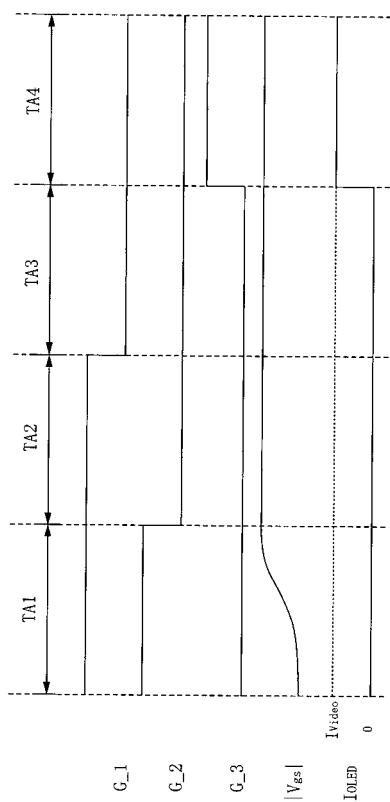

図 32 の構成の画素の駆動方法を図 39 及び図 40 を用いて説明する。なお、図 39において選択 TFT 3301、保持 TFT 3302 及び発光 TFT 3304 は、導通状態・非導通状態がわかりやすいように、スイッチで表記した。また、(TA1) ~ (TA4) それぞれの画素の状態は、図 40 のタイミングチャートにおける期間 TA1 ~ TA4 の状態に対応している。

#### 【0016】

図 40において、G\_1、G\_2、G\_3 はそれぞれ、第 1 のゲート信号線 3308、第 2 のゲート信号線 3309、第 3 のゲート信号線 3310 の電位を示す。また、|Vgs| は、駆動 TFT 3303 のゲート電圧（ゲート・ソース間電圧）の絶対値である。I<sub>OL</sub><sub>ED</sub> は、OLED 3306 を流れる電流である。I<sub>Video</sub> は、ビデオ信号入力電流源 3312 によって定められた電流値である。

30

#### 【0017】

期間 TA1において、第 1 のゲート信号線 3308 に入力された信号によって、選択 TFT 3301 が導通状態となり、また第 2 のゲート信号線 3309 に入力された信号によって、保持 TFT 3302 が導通状態となると、電源線 3311 が駆動 TFT 3303 及び選択 TFT 3301 を介して、ソース信号線 3307 と接続される。ソース信号線 3307 には、ビデオ信号入力電流源 3312 によって定められた電流量 I<sub>Video</sub> が流れるため、十分に時間が経過し定常状態となると、駆動 TFT 3303 のドレイン電流は I<sub>Video</sub> となり、ドレイン電流 I<sub>Video</sub> に対応するゲート電圧が、保持容量 3005 に保持される。このとき、発光 TFT 3304 は非導通状態である。保持容量 3005 に電圧が保持され、駆動 TFT 3303 のドレイン電流が I<sub>Video</sub> に定まった後、期間 TA2において、第 2 のゲート信号線 3309 の信号が変化し、保持 TFT 3302 が非導通状態となる。

40

#### 【0018】

次に期間 TA3において、第 1 のゲート信号線 3308 の信号が変化し、選択 TFT 3301 が非導通状態となる。また期間 TA4において、第 3 のゲート信号線 3310 に入力された信号によって、発光 TFT 3304 が導通状態となると、信号電流 I<sub>Video</sub> が、

50

電源線 3311 より駆動 TFT3303 のソース・ドレイン間を介して OLED3306 に入力される。こうして、OLED3306 は、信号電流  $I_{\text{Video}}$  に応じた輝度で発光する。

#### 【0019】

期間 TA1 ~ TA4 の一連の動作を信号電流  $I_{\text{Video}}$  の書き込み動作と呼ぶ。その際、信号電流  $I_{\text{Video}}$  をアナログ的に変化させることによって、OLED3306 の輝度を変化させ、階調を表現する。

#### 【0020】

なお図 40 のタイミングチャートにおいて、期間 TA1 では駆動用 TFT3303 のゲート電圧の絶対値  $|V_{\text{gs}}|$  は、時間の経過と共に増加し、ドレイン電流  $I_{\text{Video}}$  に対応するゲート電圧を保持する動作を示している。これは、保持容量 3305 に電荷が保持されていない状態からの書き込み動作を行う場合や、直前の書き込み動作において保持された駆動 TFT3303 のゲート電圧の絶対値  $|V_{\text{gs}}|$  が、次の書き込み動作において、ビデオ信号入力電流源 3312 により定められる所定のドレイン電流を流す際の駆動 TFT3303 のゲート電圧の絶対値  $|V_{\text{gs}}|$  より小さい場合に相当する。

10

#### 【0021】

これに限らず、直前の書き込み動作において保持された駆動 TFT3303 のゲート電圧の絶対値  $|V_{\text{gs}}|$  が、次の書き込み動作においてビデオ信号入力電流源 3312 により定められる所定のドレイン電流を流す際の駆動 TFT3303 のゲート電圧の絶対値  $|V_{\text{gs}}|$  より大きい場合は、期間 TA1 では駆動用 TFT3303 のゲート電圧の絶対値  $|V_{\text{gs}}|$  は、時間の経過と共に減少し、ドレイン電流  $I_{\text{Video}}$  に対応するゲート電圧を保持する動作となる。

20

#### 【0022】

上記のような、電流書き込み型アナログ方式の表示装置では、駆動 TFT3303 は飽和領域で動作する。駆動 TFT3303 のドレインは、ソース信号線 3307 より入力される信号電流によって定められている。つまり、駆動 TFT3303 は、閾値電圧や移動度等のばらつきがあっても、一定のドレイン電流を流し続けるようにゲート電圧が自動的に変化する。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

30

#### 【0023】

OLED 素子において、その陽極と陰極間の電圧と、流れる電流量の関係 (I-V 特性) は、OLED 素子を使用する環境温度や、OLED 素子の劣化等の影響によって変化する。そのため、従来の電圧書き込み型のデジタル方式に代表されるような、駆動 TFT を線型領域で動作させる表示装置では、OLED 素子の両電極間に一定の電圧を印加している場合においても、OLED 素子の劣化等の影響に伴い両電極間を流れる電流が変化してしまうという問題がある。

#### 【0024】

一方、図 32 に示したような画素構成を有する、従来の電流書き込み型の駆動方法を用いる表示装置においては、一定電流を OLED 素子に流すことによって輝度を表現する。電流書き込み型の画素では、駆動 TFT3303 は、飽和領域で動作している。そのため、OLED 素子 3006 の劣化前後において、OLED 素子 3006 の両電極間の電圧は変化するが、OLED 素子 3006 を流れる電流はほぼ一定の値に保たれる。

40

#### 【0025】

しかし、電流書き込み型の駆動方法では、各画素で表示を行う毎に、信号電流に応じた電荷を各画素の容量部 (保持容量) に保持し直す必要がある。この時、信号電流が小さな場合ほど、画素に信号を書き込む際に、保持容量に所定の電荷を保持するための時間が長くなるため、信号電流の素早い書き込みが困難である。また、信号電流が小さな場合は、信号電流の書き込みが行われる画素以外の、同じソース信号線に接続された複数の画素による漏れ電流等のノイズの影響が大きく、正確な輝度で画素を発光させることができ

50

きない危険性が高い。

#### 【0026】

更に、従来の電流書き込み型の表示装置において、各画素に信号電流を入力するビデオ信号入力電流源は、各画素列毎に設けられるが、それら全ての電流特性を揃える必要がある。そのため、多結晶半導体薄膜などの半導体薄膜を用いたトランジスタでは、電流特性の揃ったビデオ信号入力電流源を作製するのは困難である。よって、ビデオ信号入力電流源は、単結晶IC基板上に作製される。一方、画素が形成される基板は、コスト等の面から、ガラス等の絶縁基板（絶縁表面を有する基板）上に作製されるのが一般的である。そこで、画素が形成された基板上に、ビデオ信号入力電流源が作製された単結晶IC基板を貼り付ける必要がある。そのため、コストが高い、貼り付けの際に必要となる面積が大きく画素領域周辺の額縁の面積を小さくすることができない等の問題がある。10

#### 【0027】

また、一般的にアクティブマトリクス型の表示装置の作製において、TFTや配線等のパターニングにリソグラフィ法が用いられている。リソグラフィ法を用いる場合、フォトレジストの成膜、露光、現像、エッチング、剥離などの一連の工程を行なう必要があるため、作製工程が複雑になり、コストが高くなる。さらにリソグラフィ法には高価な露光用のマスク（フォトマスク）が必要であること、表示装置の作製に費やされるコストが抑えられない一因になっている。また、上記したように、画素部における回路構成が複雑になればなる程、それに対応したフォトマスクが必要になってくる。そして、成膜後、エッチングにより除去されてしまう部分が大部分であるため、材料が無駄になり、コスト削減という観点から好ましくない。また、無駄になる大部分の材料は結局廃棄されてしまうので、製造コストに影響を及ぼすばかりか、環境負荷の増大を招いていた。20

#### 【0028】

また、パネルが大型化されると必然的に配線が長くなるため、配線抵抗により信号が遅延するという問題が生じる。この場合、配線を厚くして断面積を広げれば、配線抵抗を下げることができ、よって信号の遅延を回避できると考えられる。しかし、リソグラフィ法を用いて配線を形成する場合、配線の厚さはせいぜい  $200 \sim 400 \mu\text{m}$  程度であり、それ以上厚いとエッチングの工程に時間がかかる望ましくない。

#### 【0029】

本発明は、上述した問題に鑑み、発光素子を劣化等による電流特性の変化によらず一定の輝度で発光させることができ、且つ各画素への信号の書き込み速度が速く、正確な階調が表現可能な表示装置の提案を課題とする。さらに本発明は、配線の作製工程に費やされるコストおよび時間を抑え、小型化可能な表示装置及びその作製方法を提供することを目的とする。30

#### 【課題を解決するための手段】

#### 【0030】

本発明による表示装置は、画素を含み、第1の電流を電圧に変換する手段と、変換された前記電圧を保持する手段と、保持された前記電圧を第2の電流に変換する手段と、デジタルの映像信号によって、前記第2の電流を発光素子に流す手段と、を有することから成ることを特徴としている。40

前記保持された前記電圧を第2の電流に変換する手段は、前記第1の電流と電流値の等しい第2の電流、又は、前記第1の電流と電流値が比例する第2の電流へ変換する手段であることを含む。

この発明に依る表示装置は、前記デジタルの映像信号とは別の信号によって、前記第2の電流を前記発光素子に流さないようにする手段を有することを特徴としている。50

#### 【0031】

また、本発明による表示装置は、複数の画素を有し、複数の画素はそれぞれ一定の電流を流す電流源回路と、デジタルの映像信号によって、オン・オフが切り替えられるスイッチ部と、発光素子と、電源線とを有し、電流源回路およびスイッチ部は少なくとも一つの

トランジスタを有しており、電流源回路のトランジスタのゲート電極、前記スイッチ部のトランジスタのゲート電極または前記電源線のいずれかが、液滴吐出法または印刷法を用いて形成されている。なお、電流源回路とスイッチ部と発光素子は、電源線と電源基準線の間に直列に接続されていることを特徴としている。

#### 【0032】

更に、本発明の表示装置は、第1の端子と第2の端子とを有し第1の端子と前記第2の端子間を流れる電流を一定に定める電流源回路と、第3の端子と第4の端子とを有しデジタルの映像信号によって第3の端子と前記第4の端子間の導通状態・非導通状態を切り替えるスイッチ部と、電源線と、電源基準線とを有する画素を含み、第3の端子と第4の端子間の導通状態が選択されたとき、第1の端子と第2の端子間を流れる電流が発光素子の陽極と陰極間に流れるように電源線と電源基準線の間に、電流源回路、スイッチ部および前記発光素子が接続されており、電流源回路のトランジスタのゲート電極、スイッチ部のトランジスタのゲート電極、電源線または電源基準線のいずれかが、液滴吐出法または印刷法を用いて形成されていることを特徴としている。10

#### 【0033】

また、本発明による表示装置は、第1の電流を第1のトランジスタのドレイン電流とする手段と、第1のトランジスタのゲート電圧を保持する手段と、ゲート電圧を第1のトランジスタと極性が等しい第2のトランジスタのゲート電圧とする手段と、デジタルの映像信号によって、第2のトランジスタのドレイン電流を発光素子に流す手段を有しており、第1のトランジスタのゲート電極または第2のトランジスタのゲート電極のうち少なくとも一方が、液滴吐出法または印刷法を用いて形成されている。前記表示装置において、第1のトランジスタのゲート長とゲート幅の比は、第2のトランジスタのゲート長とゲート幅の比と異なることと共に、第1のトランジスタのゲート電極とドレイン端子を電気的に接続する手段を有することを含む。20

また、前記表示装置は、デジタルの映像信号とは別の信号によって、第2のトランジスタのドレイン電流を発光素子に流さないようにする手段を有することを特徴としている。

#### 【0034】

本発明による表示装置は、第1の電流をトランジスタに入力してトランジスタのドレイン電流とする手段と、トランジスタのゲート電圧を保持する手段と、デジタルの映像信号によってトランジスタのソース・ドレイン端子間に電圧を印加して、保持されたゲート電圧によって定まるトランジスタのドレイン電流を発光素子に流す手段を有しており、さらにトランジスタのゲート電極が液滴吐出法または印刷法を用いて形成されていることを特徴としている。30

前記表示装置は、さらに、トランジスタのゲート電極とドレイン端子を電気的に接続する手段を有することと共に、前記デジタルの映像信号とは別の信号によって、トランジスタのドレイン電流を発光素子に流さないようにする手段を有することを含むことを特徴としている。

#### 【0035】

本発明では、上記構成を有する表示装置を、スクリーン印刷法、オフセット印刷法に代表される印刷法、または液滴吐出法を用いて形成する。なお液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出して所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。上記印刷法、液滴吐出法を用いることで、露光用のマスクを用いずとも、信号線、走査線に代表される各種配線、TFTのゲート電極、発光素子の電極などを形成することが可能になる。ただし、本発明の表示装置は、パターンを形成する全ての工程に、印刷法または液滴吐出法を用いる必要はない。例えば、配線およびゲート電極の形成には印刷法または液滴吐出法を用い、半導体膜のパターニングにはリソグラフィ法を用いる、というように、少なくとも一部の工程において印刷法または液滴吐出法を用いていればよい。またパターニングの際に用いるマスクを、印刷法または液滴吐出法で形成してもよい。40

#### 【0036】

本発明は、少なくとも一つのトランジスタを有する電流源回路と、少なくとも一つのトランジスタを有するスイッチ部と、発光素子とを電源基準線と電源線の間に直列に接続し、電流源回路のトランジスタのゲート電極、スイッチ部のトランジスタのゲート電極、電源線基準線または電源線のいずれかを、液滴吐出法または印刷法を用いて形成することを特徴としている。

#### 【0037】

また、本発明は、第1の電流を第1のトランジスタのドレイン電流とし、第1のトランジスタのゲート電圧を保持し、ゲート電圧を前記第1のトランジスタと極性が等しい第2のトランジスタのゲート電圧とし、デジタルの映像信号によって、第2のトランジスタのドレイン電流を発光素子に流す手段を有し、第1のトランジスタのゲート電極または第2のトランジスタのゲート電極のうち少なくとも一方を、液滴吐出法または印刷法を用いて形成することを特徴としている。さらに、第1のトランジスタのゲート長とゲート幅の比を、第2のトランジスタのゲート長とゲート幅の比と異なるように形成してもよい。10

#### 【0038】

また、本発明は、第1の電流をトランジスタに入力してトランジスタのドレイン電流とし、トランジスタのゲート電圧を保持し、デジタルの映像信号によってトランジスタのソース・ドレイン端子間に電圧を印加して、保持されたゲート電圧によって定まる前期トランジスタのドレイン電流を発光素子に流す手段を有しており、トランジスタのゲート電極を液滴吐出法または印刷法を用いて形成することを特徴としている。

#### 【0039】

上記構成において、発光素子は第1の電極と、第2の電極と、第1の電極と第2の電極の間に形成された電界発光層とを有し、第1の電極、第2の電極または電界発光層のいずれかを、液滴吐出法を用いて形成することを特徴としている。20

#### 【0040】

本発明は、デジタルの映像信号を用いることによって、スイッチ部のオン・オフ（導通・非導通）を切り替える。また、電流源回路を流れる一定電流の大きさは、画素外部より入力される制御信号によって定められる。スイッチ部がオン状態の場合は、発光素子には、電流源回路によって定まる一定電流が流れ発光する。スイッチ部がオフ状態の場合、発光素子には電流が流れず発光しない。このように、スイッチ部のオン・オフを映像信号によって制御し階調を表現する。30

#### 【0041】

複数のスイッチ部を設けた場合、それら複数のスイッチ部それぞれのオン・オフを切り替える信号は、映像信号であっても、その他の任意の信号であっても、また、映像信号とその他の任意の信号の両方であっても良い。ただし、複数のスイッチ部のうち少なくとも1つのスイッチ部は、映像信号によってオン・オフが切り替えられる必要がある。例えば、電源基準線と電源線との間に、発光素子と、第1のスイッチ部と第2のスイッチ部と電流源回路とが直列に接続された構成の場合、第1のスイッチ部は、映像信号によってオン・オフを切り替え、第2のスイッチ部は、映像信号とは異なる信号によってオン・オフを切り替えられる構成とすることができる。又は、第1のスイッチ部、第2のスイッチ部と共に、映像信号によってオン・オフが切り替えられるような構成とすることもできる。40

#### 【0042】

本発明の表示装置では、スイッチ部を駆動する映像信号とは別に、電流源回路を流れる一定電流を定めるための制御信号を入力する。制御信号としては、電圧信号でも電流信号でもどちらでもよい。また、電流源回路に制御信号を入力するタイミングは、任意に定めることができる。電流源回路への制御信号の入力は、スイッチ部への映像信号の入力に同期させて行っても良いし非同期で行っても良い。

#### 【0043】

本発明の表示装置では、画像表示を行う際に発光素子に流れる電流は一定に保たれるため、発光素子を劣化等による電流特性の変化によらず一定の輝度で発光させることができるものである。50

**【0044】**

本発明の表示装置では、各画素に配置した電流源回路を流れる電流の大きさは、映像信号とは別の信号によって制御され、常に一定である。また、デジタルの映像信号を用いてスイッチ部を駆動し、発光素子に一定電流を流すか流さないかを選択して、発光状態・非発光状態を切り替え、デジタル方式で階調を表現する点に特徴を有する。

**【発明の効果】****【0045】**

本発明により、発光素子を劣化等による電流特性の変化によらず一定の輝度で発光させることが可能となり、且つ各画素への信号の書き込み速度が速く、正確な階調が表現可能である駆動方法を提供することができる。

10

**【0046】**

また本発明では液滴吐出法、印刷法を用いてパターンを形成することで、リソグラフィ法で行なわれるフォトレジストの成膜、露光、現像、エッティング、剥離などの一連の工程を簡略化することができる。また、液滴吐出法、印刷法だと、リソグラフィ法と異なり、エッティングにより除去されてしまうような材料の無駄がない。また高価な露光用のマスクを用いなくとも良いので、露光装置の作製に費やされるコストを抑えることができる。

**【0047】**

さらに、リソグラフィ法とは異なり、配線を形成するためにエッティングを行なう必要がないため、配線を形成する工程に費やされる時間をリソグラフィ法の場合に比べて著しく短くすることが可能である。特に配線の厚さを0.5 μm以上、より望ましくは2 μm以上で形成する場合、配線抵抗を抑えることができるので、配線の作製工程に費やされる時間を抑えつつ、表示装置の大型化に伴う配線抵抗の上昇を抑えることができる。

20

**【発明を実施するための最良の形態】****【0048】**

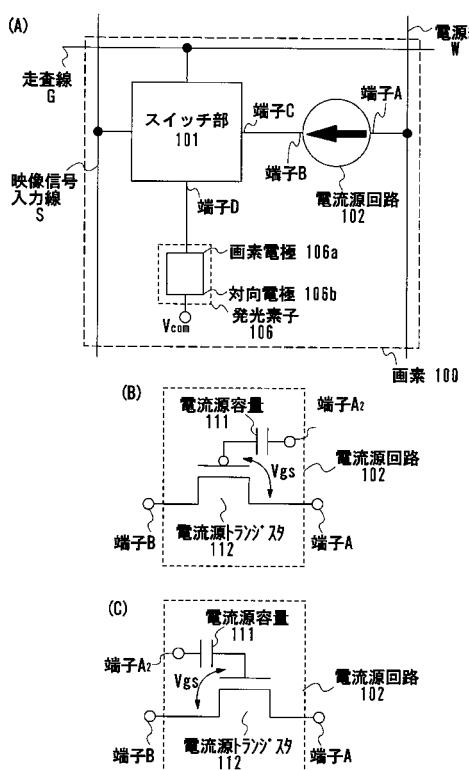

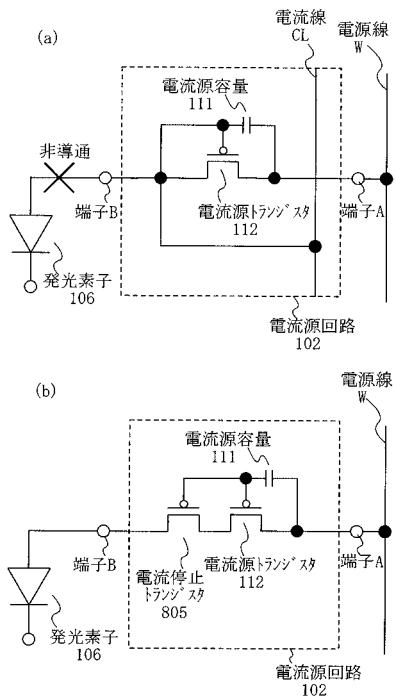

図1(A)に、本発明の表示装置における画素の構成の模式図を示す。図1(A)において、各画素100は、走査線G、映像信号入力線S、電源線W、スイッチ部101、電流源回路102及び発光素子106によって構成される。

各画素100において、スイッチ部101は端子C及び端子Dを有する。発光素子106の画素電極106aは、スイッチ部の端子Dと接続される。スイッチ部の端子Cは、電流源回路102の端子Bと接続される。電流源回路102の端子Aは電源線Wと接続されている。電流源回路102は、円の中に矢印を配置した記号によって模式的に示す。電流源回路102はこの記号の矢印の方向、つまり端子Aから端子Bの方向に、正の一定電流を流す回路であるとする。端子A又は端子Bの一方を電流源回路102の入力端子、他方を電流源回路102の出力端子と呼ぶ。

30

**【0049】**

発光状態を選択する信号が映像信号入力線Sより入力された画素100では、スイッチ部101の端子Cと端子D間が導通状態となる。こうして、スイッチ部101の端子Cと端子D間及び電流源回路102の端子Aと端子B間を介して、発光素子106の画素電極106aと電源線Wが接続される。

**【0050】**

40

スイッチ部101は、走査線Gより入力される信号によって映像信号入力線S上の映像信号の画素への入力を切り替える第1のスイッチと、画素に入力された映像信号によってオン・オフが切り替えられる第2のスイッチとを有する。第2のスイッチのオン・オフを切り替えることによって、スイッチ部の端子Cと端子Dの間の導通及び非導通状態が切り替えられる。端子C又は端子Dの一方をスイッチ部101の入力端子、他方をスイッチ部101の出力端子と呼ぶ。

発光素子106は、画素電極106aから対向電極106bへ、又はその逆の方向に電流を流し、その電流に応じて輝度が変化する素子を示す。

**【0051】**

図1(A)では、電流源回路102の端子Aが電源線Wに接続され、端子Bがスイッチ

50

部 101 の端子 C と端子 D 間を介して、発光素子 106 の画素電極 106a に接続されているので、発光素子 106 の画素電極 106a は陽極となり、対向電極 106b は陰極となる。このとき、発光素子 106 の対向電極 106b に与えられている電位  $V_{com}$  は、電源線 W の電位より低く設定されている。電位  $V_{com}$  は、電源基準線（図示せず）によって与えられている。

#### 【0052】

一方、電流源回路 102 の端子 A が、スイッチ部 101 の端子 C に接続され、端子 B が電源線 W に接続される構造としてもよい。このとき、発光素子 106 の画素電極 106a は陰極となり、対向電極 106b は陽極となる。発光素子 106 の対向電極 106b に与えられている電位  $V_{com}$  は、電源線 W の電位より高く設定されている。

10

#### 【0053】

また、電流源回路 102 とスイッチ部 101 と発光素子 106 の接続順序は任意でよいため、例えば、電流源回路 102 は、スイッチ部 101 と発光素子 106 の間に配置されてもよい。つまり、電流源回路 102 の端子 B が発光素子 106 の画素電極 106a と接続され、電流源回路 102 の端子 A がスイッチ部 101 の端子 D と接続され、スイッチ部 101 の端子 C が電源線 W に接続された構造であってもよい。更に、電流源回路 102 の端子 A と端子 B とが反転した構造であってもよい。つまり、電流源回路 102 の端子 A が発光素子 106 の画素電極 106a と接続され、電流源回路 102 の端子 B がスイッチ部 101 の端子 D と接続され、スイッチ部 101 の端子 C が電源線 W と接続された構成であってもよい。この場合、発光素子 106 の画素電極 106a は陰極となり、対向電極 106b は陽極となる。このとき、発光素子 106 の対向電極 106b に与えられている電位  $V_{com}$  は、電源線 W の電位より高く設定されている。

20

#### 【0054】

スイッチ部 101 において、端子 C と端子 D の間が導通状態となった画素 100 では、電流源回路 102 によって定まる一定電流が発光素子 106 に入力され、発光素子 106 は発光する。

#### 【0055】

電流源回路 102 の基本構造の例を図 1 (B) 及び図 1 (C) に示す。各画素の電流源回路を流れる一定電流が、電流信号によって定められる電流源回路の例を挙げる。このような構成の電流源回路を、電流制御型電流源回路と呼ぶ。図 1 (B) 及び図 1 (C) 中の端子 A 及び端子 B は、図 1 (A) 中、端子 A 及び端子 B に対応する。

30

#### 【0056】

図 1 (B) 及び図 1 (C) において、電流源回路 102 はトランジスタ（電流源トランジスタ）112 と容量素子（電流源容量）111 とを有する。飽和領域で動作する電流源トランジスタ 112 のドレイン電流が、画素の外部より入力された一定電流（以下、基準電流と表記する）に対応する一定電流（以下、画素基準電流と表記する）となる。つまり、画素の外部より一定電流（基準電流）が入力される。このときのゲート電圧  $V_{gs}$ （以下、画素対応基準電圧と表記する）が、電流源容量 111 によって保持されると、電流源トランジスタ 112 が飽和領域で動作する場合には、基準電流に対応した一定電流（画素基準電流）がドレイン電流として電流源トランジスタ 112 及び発光素子 106 に流れる。こうして、外部の電流源より基準電流が入力されなくなった後も、電流源トランジスタ 112 はソース・ドレイン間に電圧が印加されると、電流源容量 111 に保持された画素対応基準電圧に応じて画素基準電流を流す。なお、電流源容量 111 は、他のトランジスタのゲート容量などを利用することにより省略することも可能である。

40

#### 【0057】

各画素に配置された電流源容量 111 において、電流源トランジスタ 112 が画素基準電流を流すのに必要なゲート電圧を取得し保持する動作を、画素の設定動作と呼ぶ。

なお、本発明におけるトランジスタとしては、薄膜トランジスタ（TFT）でも、単結晶トランジスタ等のトランジスタでもどちらでも良い。また、有機物を利用したトランジスタでもよい。

50

例えば、単結晶トランジスタとしては、S O I 技術を用いて形成されたトランジスタとすることができる。薄膜トランジスタとしては、活性層として多結晶半導体、セミアモルファス半導体（微結晶半導体）または非晶質半導体を用いたものでもよい。例えば、シリコンを用いたTFT、セミアモルファスシリコンを用いたTFTまたはアモルファスシリコンを用いたTFTとすることができます。

#### 【0058】

セミアモルファス半導体とは、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造の半導体を含む膜である。このセミアモルファス半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5~20nmとして非単結晶半導体中に分散させて存在せしめることができるものである。セミアモルファス半導体は、そのラマンスペクトルが $520\text{ cm}^{-1}$ よりも低周波数側にシフトしており、またX線回折ではSi結晶格子に由来するとされる（111）、（220）の回折ピークが観測される。また、未結合手（ダングリングボンド）の中和剤として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。ここでは便宜上、このような半導体をセミアモルファス半導体（SAS）と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みさらに助長させることで安定性が増し良好なセミアモルファス半導体が得られる。

#### 【0059】

電流源回路102において、電流源トランジスタ112にドレイン電流が流れる場合、電流源容量111の一方の電極は電流源トランジスタ112のゲート電極と接続され、他方（図中、端子A<sub>2</sub>で示す）は一定電位が与えられる。電流源容量111に保持された電荷によって、電流源トランジスタ112のゲート電極の電位（ゲート電位）が保存される。ここで、端子A<sub>2</sub>の電位と電流源トランジスタ112のソース端子の電位とは、同じであっても良いし異なっていても良いが、電流源トランジスタに画素基準電流が流れる際はいつも、それぞれの端子間の電位差は、同じとする。こうして、電流源トランジスタ112に画素基準電流が流れる際のゲート電圧V<sub>gs</sub>（画素対応基準電圧）は保持される。飽和領域で動作するトランジスタでは、ゲート電圧V<sub>gs</sub>に応じてドレイン電流も変化する。従つて、ソース端子の電位が変化しても、ゲート電圧V<sub>gs</sub>は一定であるように、端子A<sub>2</sub>はソース端子に接続されていることが望ましい。なお、図1（B）と図1（C）では、電流源トランジスタ112の極性が異なる。図1（B）では、電流源トランジスタ112は、pチャネル型であり、図1（C）ではnチャネル型である。<sup>2</sup>

#### 【0060】

図1（A）のように接続されている場合には、電流源トランジスタ112がpチャネル型の場合、電流源トランジスタ112はソース端子からドレイン端子に電流を流す。また、電流源トランジスタ112がnチャネル型の場合、電流源トランジスタ112のドレイン端子からソース端子に電流を流す。よって、電流源トランジスタ112がpチャネル型の場合、電流源トランジスタ112のソース端子は端子Aに接続され、ドレイン端子は端子Bに接続される。一方、電流源トランジスタ112がnチャネル型の場合、電流源トランジスタ112のドレイン端子は端子Aに接続され、ソース端子は端子Bに接続される。

#### 【0061】

画素基準電流を、画素外部より入力される電流信号（基準電流）によって制御する手段としては、大きく分けて2つの方法がある。

#### 【0062】

1つは、カレントミラー方式と名付けた方式である。カレントミラー回路は、ゲート電極が電気的に接続された1対のトランジスタを有し、一方のトランジスタのゲート電極とドレイン端子が電気的に接続された構成を有する。カレントミラー方式では、カレントミラー回路を構成する1対のトランジスタのうち、一方のトランジスタを電流源トランジスタ112とし、他方のトランジスタをカレントトランジスタとする。カレントトランジスタのドレイン端子とゲート電極を電気的に接続して、そのソース・ドレイン間に基準電流を入力する手法である。

10

20

30

40

50

## 【0063】

もう1つは、同一トランジスタ方式と名付けた方式である。同一トランジスタ方式は、ドレイン端子とゲート電極が電気的に接続された電流源トランジスタ112のソース・ドレイン間に、基準電流を直接入力する手法である。なお、同一トランジスタ方式の変形として、マルチゲート方式と呼ぶものもある。

## 【0064】

カレントミラー方式を用いる電流源回路を、カレントミラー方式の電流源回路と呼び、同一トランジスタ方式を用いる電流源回路を、同一トランジスタ方式の電流源回路と呼び、マルチゲート方式を用いる電流回路をマルチゲート方式の電流源回路と呼ぶ。電流源回路102は、一旦、基準電流を入力し画素対応基準電圧を電流源容量111に保持する、

10 画素の設定動作を行った後は、電流源容量111に保持された電荷が放電しない限り、再び基準電流を入力する動作を必要としない。

## 【0065】

電流源容量111に保持された電荷は、実際には、漏れ電流の影響や様々なノイズによつて時間が経過すると変化してしまう。そこで、定期的に、画素の設定動作を繰り返す必要がある。しかし、一旦、画素の設定動作を行った後に、定期的に行う画素の設定動作では、漏れ電流によって電流源容量111に保持された電荷が変化した分のみ、電荷を保持し直せばよい。そのため、はじめの画素の設定動作と比較して、その後定期的に行う画素の設定動作に要する時間は短くてすむ。

## 【0066】

次に、本発明の表示装置のより具体的な構成とその作製方法について、図4～図7を用いて説明する。

20

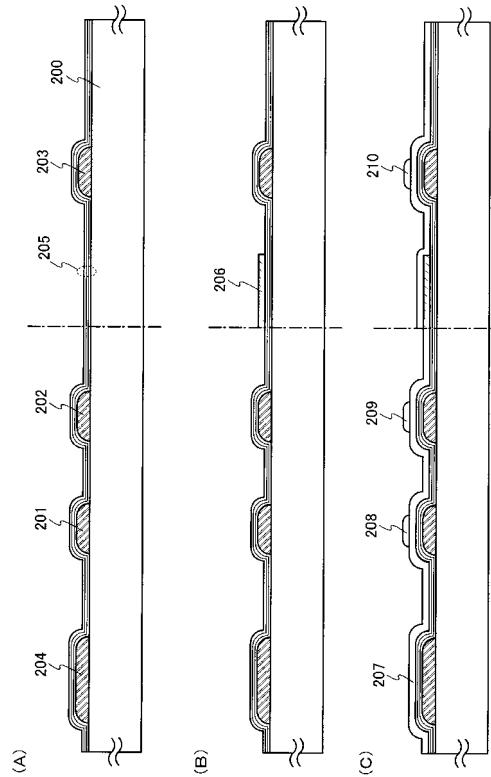

## 【0067】

まず図4(A)に示すように、TFT及び発光素子を形成する基板200を用意する。具体的に基板200は、例えばバリウムホウケイ酸ガラスや、アルミニノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、SUS基板を含む金属基板または半導体基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板は、一般的に上記基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。基板200の表面を、CMP法などの研磨により平坦化しておいても良い。

30

## 【0068】

上述した基板200の表面に、液滴吐出法、印刷法を用いて形成される導電膜または絶縁膜の密着性を高めるための前処理を施す。密着性を高めることができる方法として、例えば触媒作用により導電膜または絶縁膜の密着性を高めることができる金属または金属化合物を基板200の表面に付着させる方法、形成される導電膜または絶縁膜との密着性が高い有機系の絶縁膜、金属や金属化合物を基板200の表面に付着させる方法、基板200の表面に大気圧下または減圧下においてプラズマ処理を施し表面改質を行なう方法などが挙げられる。また、上記導電膜または絶縁膜との密着性が高い金属として、チタン、チタン酸化物の他、3d遷移元素であるSc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Znなどが挙げられる。また金属化合物として、上述した金属の酸化物、窒化物、酸窒化物などが挙げられる。上記有機系の絶縁膜として、例えばポリイミド、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む絶縁膜(以下、シロキサン系絶縁膜と呼ぶ)等が挙げられる。シロキサン系絶縁膜は、置換基に水素の他、フッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有していても良い。

40

## 【0069】

なお、基板200に付着させる金属または金属化合物が導電性を有する場合、半導体素子の正常な動作が妨げられないように、そのシート抵抗を制御する。具体的には、導電性を有する金属または金属化合物の平均の厚さを、例えば1～10nmとなるように制御したり、該金属または金属化合物を酸化により部分的に、または全体的に絶縁化したりすれば良い。或いは、密着性を高めたい領域以外は、付着した金属または金属化合物をエッチ

50

ングにより選択的に除去しても良い。また金属または金属化合物を、予め基板の全面に付着させるのではなく、液滴吐出法、印刷法、ゾル・ゲル法などを用いて特定の領域にのみ選択的に付着させても良い。なお金属または金属化合物は、基板 200 の表面において完全に連続した膜状である必要はなく、ある程度分散した状態であっても良い。

#### 【0070】

本実施の形態では、光触媒反応により密着性を高めることができる ZnO または TiO<sub>2</sub>などの光触媒を基板 200 の表面に付着させる。具体的には、ZnO または TiO<sub>2</sub>を溶媒に分散させ、基板 200 の表面に撒布したり、Zn の化合物または Ti の化合物を基板 200 の表面に付着させた後、酸化させたり、ゾル・ゲル法を用いたりすることで、結果的に ZnO または TiO<sub>2</sub>を基板 200 の表面に付着させることができる。

10

#### 【0071】

次に密着性を高めるための前処理が施された基板 200 の表面上に、液滴吐出法または各種印刷法を用いて、ゲート電極 201 ~ 203 を形成する。具体的に、ゲート電極 201 ~ 203 には、Ag、Au、Cu、Pd などの金属、金属化合物を 1つまたは複数有する導電材料を用いる。なお、分散剤により凝集を抑え、溶液に分散させることができるとならば、Cr、Mo、Ti、Ta、W、Al などの金属、金属化合物を 1つまたは複数有する導電材料を用いることも可能である。また液滴吐出法または各種印刷法による導電材料の成膜を複数回行なうことで、複数の導電膜が積層されたゲート電極を形成することも可能である。但し、吐出口から吐出する組成物は、比抵抗値を考慮して、Au、Ag、Cu のいずれかの材料を溶媒に溶解又は分散させたものを用いることが好適であり、より好適には、低抵抗な銀、銅を用いるとよい。但し、Ag、Cu を用いる場合には、不純物対策のため、合わせてバリア膜を設けるとよい。バリア膜としては、窒化珪素膜やニッケルボロン (NiB) を用いることができる。

20

#### 【0072】

また、導電性材料の周りに他の導電性材料がコーティングされ、複数の層になっている粒子でも良い。例えば、Cu を Ag でコートした導電粒子や Cu の周りにニッケルボロン (NiB) がコーティングされ、その周囲に Ag がコーティングされている 3 層構造の粒子などを用いても良い。溶媒は、酢酸ブチル、酢酸エチル等のエステル類、イソプロピルアルコール、エチルアルコール等のアルコール類、メチルエチルケトン、アセトン等の有機溶剤等を用いる。組成物の粘度は 20 cP 以下が好適であり、これは、乾燥が起こることを防止したり、吐出口から組成物を円滑に吐出できるようにしたりするためである。また、組成物の表面張力は、40 mN/m 以下が好適である。但し、用いる溶媒や、用途に合わせて、組成物の粘度等は適宜調整するとよい。一例として、ITO や、有機インジウム、有機スズを溶媒に溶解又は分散させた組成物の粘度は 5 ~ 20 MPa · S、Ag を溶媒に溶解又は分散させた組成物の粘度は 5 ~ 20 MPa · S、Au を溶媒に溶解又は分散させた組成物の粘度は 5 ~ 20 MPa · S に設定するとよい。

30

#### 【0073】

液滴吐出手段に用いるノズルの径は、0.1 ~ 50 μm (好適には 0.6 ~ 26 μm、) に設定し、ノズルから吐出される組成物の吐出量は 0.00001 pL ~ 50 pL (好適には 0.0001 ~ 40 pL) に設定する。この吐出量は、ノズルの径の大きさに比例して増加する。また、被処理物とノズル吐出口との距離は、所望の箇所に滴下するために、できる限り近づけておくことが好ましく、好適には 0.1 ~ 2 mm 程度に設定する。なお、ノズル径を変えずとも、圧電素子に印可されるパルス電圧を変えることによって吐出量を制御することもできる。これらの吐出条件は、線幅が約 10 μm 以下となるように設定しておくのが望ましい。

40

#### 【0074】

液滴吐出法を用いる場合、有機系または無機系の溶媒に該導電材料を分散させたものを、ノズルから滴下した後、室温において乾燥または焼成することで、形成することができる。具体的に本実施の形態では、テトラデカンに Ag を分散させた溶液を滴下し、200 ~ 300 で 1 min ~ 50 hr 焼成することで溶媒を除去し、ゲート電極 201 ~ 2

50

03を形成する。有機系の溶媒を用いる場合、上記焼成を酸素雰囲気下で行なうことで、効率的に溶媒を除去することができ、ゲート電極201～203の抵抗をより下げることができる。なお図示しないが、この工程でゲート電極201に接続した走査線も、同時に形成することができる。

#### 【0075】

ここで、液滴吐出法でAgを吐出する前に、酸化チタンを基板の表面に付着させた場合における、Agの密着性の評価について説明する。まずガラス基板上にスパッタ法を用いてチタンを1～5nmの膜厚で成膜した。そして230℃の焼成により成膜したチタンを酸化し、酸化チタンとした。このとき、酸化チタンで形成されている膜のシート抵抗を測定したところ、装置の測定可能の下限値 $1 \times 10^{-6}$ Ωよりも低くなつたため、十分絶縁性が高いことが確認された。10

#### 【0076】

次に、液滴吐出法を用いてAgを16箇所のエリアに滴下した後、230℃で焼成した。なお焼成後、16箇所の各エリアに形成された、短冊形のAg膜の寸法は、長さ1cm、幅200～300μm、厚さ400～500nmとなつた。

#### 【0077】

上記Ag膜が形成された基板に、カプトン(R)テープを貼った後、該テープを剥がしてAg膜の密着性を確認したところ、テープを剥がした後もAg膜の剥離は見られなかつた。また上記Ag膜が形成された基板を、0.5wt%のHF水溶液に1分間浸した後、流水洗浄を行うことで膜の密着性を確認したところ、全てのAg膜が剥がれず基板上に残存していた。なお、チタン酸化膜を溶媒に分散させた溶液を、基板の表面に散布することで、酸化チタンを基板の表面に付着させた場合も、同様の結果が得られた。ちなみに、素のガラス基板、表面をCMP研磨したガラス基板、非晶質珪素膜、窒化珪素膜または酸化珪素膜を形成したガラス基板を用いた場合には、若干の違いはあるものの、いずれも数本程度しかAg膜は残存しなかつた。従つて、酸化チタンにより高い密着性が得られていると考えられる。20

#### 【0078】

次に、ゲート電極201～203および配線204を覆うようにゲート絶縁膜205を形成する。ゲート絶縁膜205は、例えば酸化珪素、窒化珪素または窒化酸化珪素等の絶縁膜を用いることができる。ゲート絶縁膜205は、単層の絶縁膜を用いても良いし、複数の絶縁膜を積層していても良い。本実施の形態では、窒化珪素、酸化珪素、窒化珪素が順に積層された絶縁膜を、ゲート絶縁膜205として用いる。また成膜方法は、プラズマCVD法、スパッタ法などを用いることができる。低い成膜温度でゲートリーク電流を抑えることができる緻密な絶縁膜を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。また窒化アルミニウムをゲート絶縁膜205として用いることができる。窒化アルミニウムは熱伝導率が比較的高く、TFTで発生した熱を効率的に発散させることができる。30

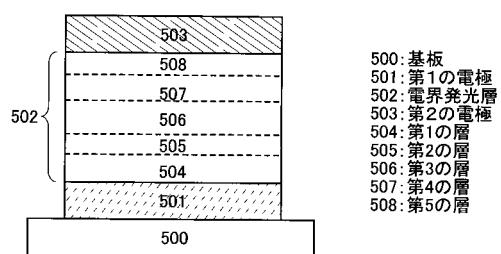

#### 【0079】

次に図4(B)に示すように、発光素子が有する第1の電極206をゲート絶縁膜205上に形成する。なお本実施の形態では、第1の電極206が陽極、後に形成される第2の電極236が陰極に相当するが、本発明はこの構成に限定されない。第1の電極206が陰極、第2の電極236が陽極に相当しても良い。40

#### 【0080】

陽極には、酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、ガリウムを添加した酸化亜鉛(GZO)などその他の透光性酸化物導電材料を用いることが可能である。ITO及び酸化珪素を含む酸化インジウムスズ(以下、ITSOとする)や、酸化珪素を含んだ酸化インジウムに、さらに2～20%の酸化亜鉛(ZnO)を混合したものを用いても良い。また陽極として上記透光性酸化物導電材料の他に、例えばTiN、ZrN、Ti、W、Ni、Pt、Cr、Ag、Al等の1つまたは複数からなる单層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン

膜とアルミニウムを主成分とする膜と窒化チタン膜との三層構造等を用いることができる。ただし透光性酸化物導電材料以外の材料で陽極側から光を取り出す場合、光が透過する程度の膜厚（好ましくは、5 nm ~ 30 nm程度）で形成する。

#### 【0081】

なお、第1の電極206は、スパッタ法、液滴吐出法または印刷法を用いて形成することが可能である。液滴吐出法または印刷法を用いる場合、マスクを用いなくても第1の電極206を形成することが可能である。またスパッタ法を用いる場合でも、リソグラフィ法において用いるレジストを、液滴吐出法または印刷法で形成することで、露光用のマスクを別途用意しておく必要がなくなり、よってコストの削減に繋がる。

#### 【0082】

また、第1の電極206は、その表面が平坦化されるように、CMP法、ポリビニルアルコール系の多孔質体で拭净し、研磨しても良い。またCMP法を用いた研磨後に、陽極の表面に紫外線照射、酸素プラズマ処理などを行ってもよい。

#### 【0083】

次に、図4(C)に示すように、第1の半導体膜207を形成する。第1の半導体膜207は非晶質（アモルファス）半導体またはセミアモルファス半導体（SAS）で形成することができる。また多結晶半導体膜を用いていても良い。本実施の形態では、第1の半導体膜207としてセミアモルファス半導体を用いる。セミアモルファス半導体は、非晶質半導体よりも結晶性が高く高い移動度が得られ、また多結晶半導体と異なり結晶化させるための工程を増やすことも形成することができる。

#### 【0084】

非晶質半導体は、珪化物気体をグロー放電分解することにより得ることができる。代表的な珪化物気体としては、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>が挙げられる。この珪化物気体を、水素、水素とヘリウムで希釈して用いても良い。

#### 【0085】

またSASも珪化物気体をグロー放電分解することにより得ることができる。代表的な珪化物気体としては、SiH<sub>4</sub>であり、その他にもSi<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などを用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素を加えたガスで、この珪化物気体を希釈して用いることで、SASの形成を容易なものとすることができます。希釈率は2倍~1000倍の範囲で珪化物気体を希釈することが好ましい。またさらに、珪化物気体中に、CH<sub>4</sub>、C<sub>2</sub>H<sub>6</sub>などの炭化物気体、GeH<sub>4</sub>、GeF<sub>4</sub>などのゲルマニウム化気体、F<sub>2</sub>などを混入させて、エネルギー bandwidth幅を1.5~2.4 eV、若しくは0.9~1.1 eVに調節しても良い。SASを第1の半導体膜として用いた TFTは、1~10 cm<sup>2</sup>/Vsecや、それ以上の移動度を得ることができる。

#### 【0086】

また異なるガスで形成されたSASを複数積層することで、第1の半導体膜を形成しても良い。例えば、上述した各種ガスのうち、弗素原子を含むガスを用いて形成されたSASと、水素原子を含むガスを用いて形成されたSASとを積層して、第1の半導体膜を形成することができる。

#### 【0087】

グロー放電分解による被膜の反応生成は減圧下または大気圧下で行なうことができる。減圧下で行なう場合、圧力は概略0.1 Pa ~ 133 Paの範囲で行なえば良い。グロー放電を形成するための電力は1 MHz ~ 120 MHz、好ましくは13 MHz ~ 60 MHzの高周波電力を供給すれば良い。圧力は概略0.1 Pa ~ 133 Paの範囲、電源周波数は1 MHz ~ 120 MHz、好ましくは13 MHz ~ 60 MHzとする。基板加熱温度は300以下でよく、好ましくは100~250とする。膜中の不純物元素として、酸素、窒素、炭素などの大気成分の不純物は1 × 10<sup>20</sup> atoms / cm<sup>3</sup>以下とすることが望ましく、特に、酸素濃度は5 × 10<sup>19</sup> atoms / cm<sup>3</sup>以下、好ましくは1 × 10<sup>19</sup> atoms / cm<sup>3</sup>以下とする。

10

20

30

40

50

## 【0088】

なお、 $\text{Si}_2\text{H}_6$ と、 $\text{GeF}_4$ または $\text{F}_2$ とを用いて半導体膜を形成する場合、半導体膜のより基板に近い側から結晶が成長するので、基板に近い側ほど半導体膜の結晶性が高い。よって、ゲート電極が第1の半導体膜よりも基板により近いボトムゲート型のTFTの場合、第1の半導体膜のうち基板に近い側の結晶性が高い領域をチャネル形成領域として用いることができるので、移動度をより高めることができ、適している。

## 【0089】

また、 $\text{SiH}_4$ と、 $\text{H}_2$ とを用いて半導体膜を形成する場合、半導体膜の表面により近い側ほど大きい結晶粒が得られる。よって、第1の半導体膜がゲート電極よりも基板により近いトップゲート型のTFTの場合、第1の半導体膜のうち基板から遠い側の結晶性が高い領域をチャネル形成領域として用いることができるので、移動度をより高めることができ、適している。10

## 【0090】

また、SASは、価電子制御を目的とした不純物を意図的に添加しないときには弱いn型の導電型を示す。これは、アモルファス半導体を成膜するときよりも高い電力のグロー放電を行なうため酸素が半導体膜中に混入しやすいためである。そこで、TFTのチャネル形成領域を設ける第1の半導体膜に対しては、p型を付与する不純物を、この成膜とともに、或いは成膜後に添加することで、しきい値制御をすることが可能となる。p型を付与する不純物としては、代表的には硼素であり、 $\text{B}_2\text{H}_6$ 、 $\text{BF}_3$ などの不純物気体を1 ppm～1000 ppmの割合で珪化物気体に混入させると良い。例えば、p型を付与する不純物としてボロンを用いる場合、該ボロンの濃度を $1 \times 10^{14} \sim 6 \times 10^{16} \text{ atoms/cm}^3$ とするときも良い。20

## 【0091】

次に、第1の半導体膜207のうち、チャネル形成領域となる部分と重なるように、第1の半導体膜207上に保護膜208～210を形成する。保護膜208～210は液滴吐出法または印刷法を用いて形成しても良いし、CVD法、スパッタ法などを用いて形成しても良い。保護膜208～210として、酸化珪素、窒化珪素、窒化酸化珪素などの無機絶縁膜、シリコン系絶縁膜などを用いることができる。またこれらの膜を積層し、保護膜208～210として用いても良い。本実施の形態では、プラズマCVD法で形成された窒化珪素、液滴吐出法で形成されたシリコン系絶縁膜を積層して、保護膜208～210として用いる。この場合、窒化珪素のパターニングは、液滴吐出法で形成されたシリコン系絶縁膜をマスクとして用い行なうことができる。30

## 【0092】

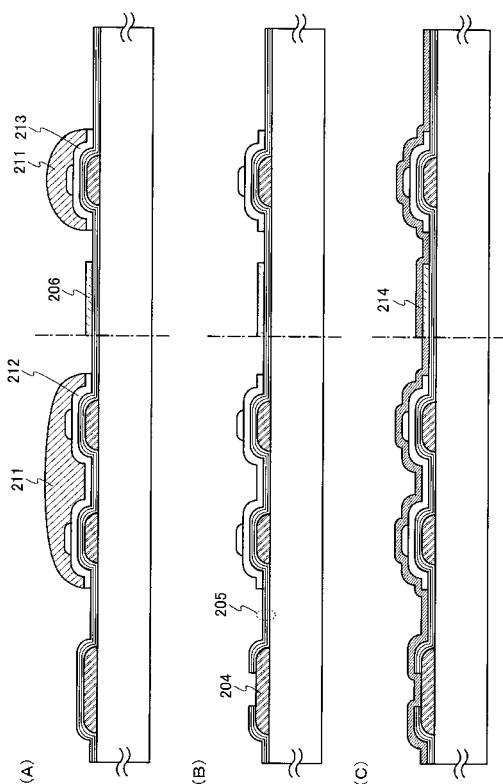

次に図5(A)に示すように、第1の半導体膜207のパターニングを行なう。第1の半導体膜207のパターニングは、リソグラフィ法を用いても良いし、液滴吐出法または印刷法で形成されたレジストをマスクとして用いても良い。後者の場合、露光用のマスクを別途用意しておく必要がなくなり、コストの削減に繋がる。本実施の形態では、液滴吐出法で形成されたレジスト211を用い、パターニングする例を示す。なおレジスト211は、ポリイミド、アクリルなどの有機樹脂を用いることができる。そして、レジスト211を用いたドライエッチングにより、パターニングされた第1の半導体膜212、213が形成される。40

## 【0093】

次に図5(B)に示すように、ゲート絶縁膜205の一部をエッチングにより選択的に除去し、配線204の一部を露出させる。ゲート絶縁膜205のエッチングには、リソグラフィ法を用いても良いし、液滴吐出法または印刷法で形成されたレジストをマスクとして用いても良い。後者の場合、露光用のマスクを別途用意しておく必要がなくなり、よってコストの削減に繋がる。

## 【0094】

次に図5(C)に示すように、パターニング後の第1の半導体膜212、213を覆うように、第2の半導体膜214を形成する。第2の半導体膜214には、一導電型を付与50

する不純物を添加しておく。p チャネル型の TFT を形成する場合には、p 型を付与する不純物として、B<sub>2</sub>H<sub>6</sub>、BF<sub>3</sub>などの不純物気体を珪化物気体に混入させると良い。例えば、p 型を付与する不純物としてボロンを用いる場合、該ボロンの濃度を  $1 \times 10^{14} \sim 6 \times 10^{16}$  atoms/cm<sup>3</sup> とすると良い。また、n チャネル型の TFT を形成する場合には、第 2 の半導体膜 214 に、n 型を付与する不純物、例えばリンを添加すれば良い。具体的には、珪化物気体に PH<sub>3</sub>などの不純物気体を加え、第 2 の半導体膜 214 を形成すれば良い。一導電型を有する第 2 の半導体膜 214 は、第 1 の半導体膜 212、213 と同様にセミアモルファス半導体、非晶質半導体で形成することができる。

#### 【0095】

なお本実施の形態では、第 2 の半導体膜 214 を第 1 の半導体膜 212、213 と接するように形成しているが、本発明はこの構成に限定されない。第 1 の半導体膜 212、213 と第 2 の半導体膜 214 の間に、LDD 領域として機能する第 3 の半導体膜を形成しておいても良い。この場合、第 3 の半導体膜は、セミアモルファス半導体または非晶質半導体で形成する。

10

#### 【0096】

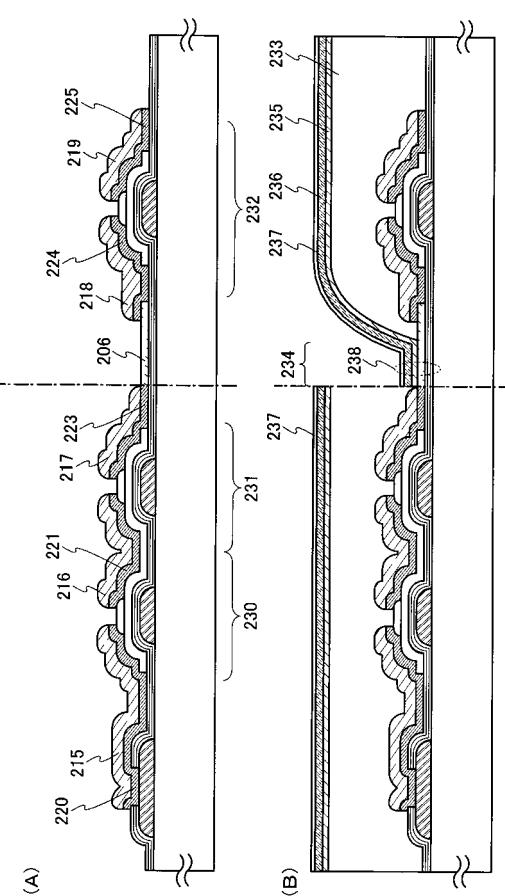

次に図 6 (A) に示すように、配線 215～219 を液滴吐出法または印刷法を用いて形成し、該配線 215～219 をマスクとして用い、第 2 の半導体膜 214 をエッチングする。第 2 の半導体膜 214 のエッチングは、真空雰囲気下もしくは大気圧雰囲気下におけるドライエッティングで行なうことができる。上記エッチングにより、第 2 の半導体膜 214 からソース領域またはドレイン領域として機能する、第 2 の半導体 220～225 が形成され、さらに第 1 の電極 206 の一部が露出される。第 2 の半導体膜 214 をエッチングする際、保護膜 208～210 によって、第 1 の半導体膜 212、213 がオーバーエッティングされるのを防ぐことができる。

20

#### 【0097】

配線 215～219 は、ゲート電極 201～203 と同様に形成することができる。具体的には、Ag、Au、Cu、Pd などの金属、金属化合物を 1 つまたは複数有する導電材料を用いる。液滴吐出法を用いる場合、有機系または無機系の溶媒に該導電材料を分散させたものを、ノズルから滴下した後、室温において乾燥または焼成することで、形成することができる。分散剤により凝集を抑え、溶液に分散させることができれば、Cr、Mo、Ti、Ta、W、Al などの金属、金属化合物を 1 つまたは複数有する導電材料を用いることも可能である。焼成は酸素雰囲気下で行ない、配線 215～219 の抵抗を下げるようにもうける。また液滴吐出法または各種印刷法による導電材料の成膜を複数回行なうことで、複数の導電膜が積層された配線 215～219 を形成することも可能である。

30

#### 【0098】

上記工程によって、TFT 230、231、232 が形成される。

#### 【0099】

次に図 6 (B) に示すように、TFT 230 と、TFT 231 と、TFT 232 と、第 1 の電極 206 の端部とを覆うように、隔壁 233 を形成する。隔壁 233 は、有機樹脂膜、無機絶縁膜またはシロキサン系絶縁膜を用いて形成することができる。有機樹脂膜ならば、例えばアクリル、ポリイミド、ポリアミドなど、無機絶縁膜ならば酸化珪素、窒化酸化珪素などを用いることができる。特に感光性の有機樹脂膜を隔壁 233 に用い、第 1 の電極 206 上に開口部 234 を形成し、その開口部 234 の側壁が連続した曲率を持って形成される傾斜面となるように形成することで、第 1 の電極 206 と後に形成される第 2 の電極 236 とが接続してしまうのを防ぐことができる。このとき、マスクを液滴吐出法または印刷法で形成することができる。また隔壁 233 自体を、液滴吐出法または印刷法で形成することもできる。なお隔壁 233 は開口部 234 を有している。

40

#### 【0100】

次に電界発光層 235 を形成する前に、隔壁 233 及び第 1 の電極 206 に吸着した水分や酸素等を除去するために、大気雰囲気下で加熱処理または真空雰囲気下で加熱処理 (

50

真空ベーク)を行なっても良い。具体的には、基板の温度を200～450、好ましくは250～300で、0.5～20時間程度、真空雰囲気下で加熱処理を行なう。望ましくは $3 \times 10^{-7}$  Torr以下とし、可能であるならば $3 \times 10^{-8}$  Torr以下とするのが最も望ましい。そして、真空雰囲気下で加熱処理を行なった後に電界発光層を成膜する場合、電界発光層を成膜する直前まで当該基板を真空雰囲気下に置いておくことで、信頼性をより高めることができる。また真空ベークの前または後に、第1の電極206に紫外線を照射してもよい。

#### 【0101】

なお、本実施の形態では、後に形成されるパッシベーション膜237を窒化珪素で形成しており、該パッシベーション膜237と、第2の電極206とが接している。窒化珪素または窒化酸化珪素を含む絶縁膜上に接するように、ITOなどの透光性酸化物導電材料と酸化珪素を含む導電膜を用い、発光素子の第1の電極または第2の電極を形成することで、上述したどの材料の組み合わせよりも、発光素子の輝度を高めることができる。また、第1の電極206にITOを用いた場合、含まれる酸化珪素によって水分が付着しやすいので、上述した真空ベークは特に有効である。

#### 【0102】

そして、隔壁233の開口部234において第1の電極206と接するように、電界発光層235を形成する。電界発光層235は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。複数の層で構成されている場合、陽極に相当する第1の電極206上に、ホール注入層、ホール輸送層、発光層、電子輸送層、電子注入層の順に積層する。なお第1の電極206が陰極に相当する場合は、電界発光層235を、電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層に積層して形成する。

#### 【0103】

なおモノクロの画像を表示する場合、もしくは白色の発光素子とカラーフィルターを用いてカラーの画像を表示する場合、電界発光層235の構造は全ての画素において同じである。三原色の光をそれぞれ発する3つの発光素子を用いてカラーの画像を表示する場合、電界発光層235は、対応する色ごとに材料、積層する層または膜厚を変えて塗り分けても良い。電界発光層を塗り分ける場合、液滴吐出法は材料の無駄がなく、工程も簡素化できるので、非常に有効である。なおカラーは、混色を用いたフルカラーであっても良いし、单一の色相を有する複数の画素を特定のエリアごとに配したエリアカラーであっても良い。

#### 【0104】

なおカラーフィルターは、特定の波長領域の光を透過させることができる着色層と、場合によっては該着色層に加え、可視光を遮蔽することができる遮蔽膜とを有する場合がある。そしてカラーフィルターは、発光素子を封止するためのカバー材上に形成する場合もあれば、素子基板に形成する場合もありうる。いずれの場合においても、着色層または遮蔽膜は、印刷法または液滴吐出法を用いて形成することが可能である。

#### 【0105】

また電界発光層235は、高分子系有機化合物、中分子系有機化合物、低分子系有機化合物、無機化合物のいずれを用いていても、液滴吐出法で形成することが可能である。また中分子系有機化合物、低分子系有機化合物、無機化合物は蒸着法で形成しても良い。

#### 【0106】

そして電界発光層235を覆うように、第2の電極236を形成する。本実施の形態では、第2の電極236は陰極に相当する。第2の電極236の作製方法は、蒸着法、スパッタ法、液滴吐出法などを材料に合わせて使い分けることが好ましい。

#### 【0107】

陰極は、仕事関数の小さい金属、合金、電気伝導性化合物、およびこれらの混合物などを用いることができる。具体的には、LiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、これらを含む合金(Mg:Ag、Al:Li、Mg:Inなど)

10

20

30

40

50

ど)、およびこれらの化合物(CaF<sub>2</sub>、CaN)の他、YbやEr等の希土類金属を用いることができる。また電子注入層を設ける場合、Alなどの他の導電層を用いることも可能である。また陰極側から光を取り出す場合は、酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、ガリウムを添加した酸化亜鉛(GZO)などその他の透光性酸化物導電材料を用いることが可能である。ITO及び酸化珪素を含む酸化インジウムスズ(以下、ITSOとする)や、酸化珪素を含んだ酸化インジウムに、さらに2~20%の酸化亜鉛(ZnO)を混合したものを用いても良い。透光性酸化物導電材料を用いる場合、後に形成される電界発光層235に電子注入層を設けるのが望ましい。また透光性酸化物導電材料を用いざとも、陰極を光が透過する程度の膜厚(好ましくは、5nm~30nm程度)で形成することで、陰極側から光を取り出すことができる。この場合、該陰極の上または下に接するように透光性酸化物導電材料を用いて透光性を有する導電層を形成し、陰極のシート抵抗を抑えるようにしても良い。10

#### 【0108】

隔壁233の開口部234において、第1の電極206と電界発光層235と第2の電極236が重なり合うことで、発光素子238が形成されている。

#### 【0109】

なお、発光素子238からの光の取り出しは、第1の電極206側からであっても良いし、第2の電極236側からであっても良いし、その両方からであっても良い。上記3つの構成にうち、目的とする構成に合わせて、陽極、陰極それぞれの材料及び膜厚を選択するようとする。本実施の形態のように第2の電極236側から光の取り出す場合、第1の電極206側から光の取り出す場合に比べて、より低い消費電力でより高い輝度を得ることができる。20

#### 【0110】

なお発光素子238を覆うようにパッシベーション膜237を形成しても良い。パッシベーション膜237は、水分や酸素などの発光素子の劣化を促進させる原因となる物質を、他の絶縁膜と比較して透過させにくい膜を用いる。代表的には、例えばDLC膜、窒化炭素膜、RFスパッタ法やCVD法などで形成された窒化珪素膜等を用いるのが望ましい。また、例えば窒化炭素膜と窒化珪素を積層した膜、ポリスチレンを積層した膜などをパッシベーション膜237として用いても良い。また上述した水分や酸素などの物質を透過させにくい膜と、該膜に比べて水分や酸素などの物質を透過させやすいが内部応力の低い膜とを積層させて、パッシベーション膜237として用いることも可能である。本実施の形態では窒化珪素を用いる。パッシベーション膜237として窒化珪素を用いる場合、低い成膜温度で緻密なパッシベーション膜237を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、パッシベーション膜237中に混入させると良い。30

#### 【0111】

なお実際には、図6(B)に示す状態まで完成したら、さらに外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

#### 【0112】

なお本実施の形態では、画素部を形成する工程について説明したが、セミアモルファス半導体を第1の半導体膜として用いる場合、走査線駆動回路を画素部と同じ基板上に形成することが可能である。またアモルファス半導体を用いたTFTで画素部を形成し、該画素部が形成された基板に別途形成された駆動回路を貼り付けても良い。40

#### 【0113】

##### (実施の形態1)

図4~図7では、第1の半導体膜と第2の半導体膜を別々の工程でパターニングしているが、本発明の表示装置はこの作製方法に限定されない。本実施の形態では図8を用いて、第1の半導体膜と第2の半導体膜を同一のマスクを用いてパターニングする例について説明する。

#### 【0114】

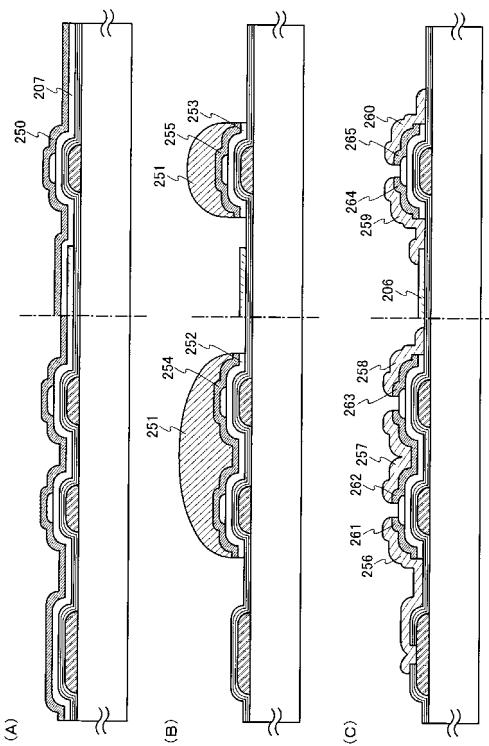

まず上述した作製方法に従って、図4(C)に示す状態まで同様に作製する。次に図8(A)に示すように、第1の半導体膜207をパターニングする前に、第2の半導体膜250を成膜する。LDD領域として用いる第3の半導体膜を形成する場合は、第1の半導体膜207を形成した後、第3の半導体膜を形成し、それから第2の半導体膜250を形成する。次に図8(B)に示すように、液滴吐出法または印刷法で形成したレジスト251をマスクとして用い、第1の半導体膜207及び第2の半導体膜250をパターニングする。図8(B)において、252、253はパターニング後の第1の半導体膜、254、255はパターニング後の第2の半導体膜に相当する。

#### 【0115】

次に図8(C)に示すように、レジスト251を除去した後に、液滴吐出法または印刷法で配線256～260を形成する。そして配線256～260をマスクとして用い、第2の半導体膜254、255を更にパターニングすることで、ソース領域またはドレイン領域として機能する第2の半導体膜261～265が形成される。そして後は、図4～図6に示した作製方法と同様に、隔壁、電界発光層、第2の電極を形成することができる。

#### 【0116】

図8に示した作製方法を用いる場合、第1の電極206と配線259とが直接接するので、該接続部分における接触抵抗を低くすることができる。

#### 【0117】

また図4～図6に示した作製方法及び図8に示した作製方法では、第2の半導体膜と、該第2の半導体膜に接している配線とを形成する前に、第1の電極を形成している例を示しているが、本発明はこの構成に限定されない。図9(A)に、図4～図6に示した作製方法において、第2の半導体膜と、該第2の半導体膜に接している配線とを形成した後に、第1の電極を形成した、画素の断面図を示す。ただし図9(A)では、TFT630、を示す。

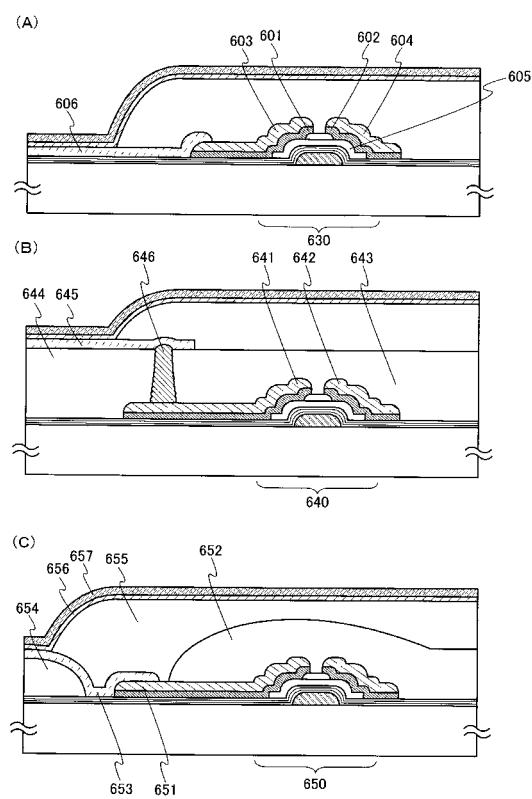

#### 【0118】

図9(A)において、601、602は、ソース領域またはドレイン領域として機能する第2の半導体膜に相当し、第2の半導体膜601上に接するように配線603が、第2の半導体膜602上に接するように配線604が形成されている。なお図9(A)では、第1の半導体膜605と第2の半導体膜601、602とを、図4～図6に示した場合のように、異なるマスクを用いたパターニングにより形成しているが、本発明はこの構成に限定されず、図8の場合のように同じマスクを用いてパターニングしても良い。そして図9(A)では、配線603上に接するように、第1の電極606が形成されている。図9(A)に示すように、第2の半導体膜601、602と、該第2の半導体膜601、602に接している配線603、604を形成した後に、第1の電極606を形成することで、第2の半導体膜601、602のパターニングの際にドライエッチングを用いても、第1の電極606の表面が荒れるのを防ぐことができる。

#### 【0119】

また図4～図6、図8、図9(A)では、第1の電極をゲート絶縁膜上に形成しているが本発明はこの構成に限定されない。図9(B)に、TFTを覆って層間絶縁膜を形成し、該層間絶縁膜上に第1の電極を形成した場合の、画素の断面図を示す。ただし図9(B)では、TFT640、TFT641を示す。図9(B)では、TFT640のソース領域またはドレイン領域と接続された配線641、642とが、層間絶縁膜643によって覆われており、該層間絶縁膜643上に第1の電極645が形成されている。層間絶縁膜643は、有機樹脂膜、無機絶縁膜またはシリコン系絶縁膜を用いて形成することができる。層間絶縁膜643に、低誘電率材料(low-k材料)と呼ばれる材料を用いていても良い。そして第1の電極645と配線641とは、層間絶縁膜643のコンタクトホール内に形成されたピラー646を通して電気的に接続されている。

#### 【0120】

図9(B)では、該ピラー646は層間絶縁膜643を形成する前に液滴吐出法を用いて形成されている。具体的には、導電材料を含む溶液を同じポイントに滴下し、液滴を重

10

20

30

40

50

ねることでピラー 646 を形成する。ピラー 646 に用いる導電材料として、ITO、ITSO に代表される透光性酸化物導電材料を用いることができる。そして、ピラー 646 を形成した後に層間絶縁膜 643 をスピンコート法などの塗布法で形成し、次に層間絶縁膜 643 の表面をエッチングすることでピラー 646 を露出させる。そして該ピラー 646 と接するように、層間絶縁膜 643 上に第 1 の電極 645 を形成する。なお層間絶縁膜 643 の表面は第 1 の電極 645 の表面に凹凸が形成されないように、平坦化されていることが望ましい。よって液滴吐出法を用いて層間絶縁膜 643 を形成する場合、液滴を吐出した後に気体を吹き付けてその表面を平坦化した後、焼成するように形成しても良い。

#### 【0121】

なお図 9 (B) では、層間絶縁膜 643 を形成する前にピラー 646 を形成しているが、層間絶縁膜 643 を形成した後にピラー 646 を形成しても良い。この場合、層間絶縁膜 643 にコンタクトホールを形成し、液滴吐出法を用いて該コンタクトホールに導電材料を含む溶液を滴下することで、ピラー 646 を形成する。コンタクトホールの形成は、ドライエッティングを用いても、ウェットエッティングを用いてもどちらでも良い。また、層間絶縁膜を形成する前に、コンタクトホールを形成する領域に撥液性を有する有機材料を液滴吐出法または印刷法などを用いて塗布しておいても良い。この場合、層間絶縁膜を形成した後、撥液性を有する有機材料を除去することで、エッチングを行なわずともコンタクトホールを形成することができる。撥液性を有する有機材料として、ポリビニルアルコール (PVA)、フルオロアルキルシラン (FAS) などを用いることができる。また撥液性を有する有機材料の除去は、水による洗浄、CF<sub>4</sub>、O<sub>2</sub>などを用いたドライエッティングで行なうことができる。

#### 【0122】

また層間絶縁膜は、液滴吐出法を用いて形成しても良い。図 9 (C) に、液滴吐出法を用いて層間絶縁膜を形成した場合の、画素の断面図を示す。図 9 (C) では、TFT650 が第 1 の層間絶縁膜 652 に覆われてあり、第 1 の層間絶縁膜 652 は液滴吐出法を用いて形成されている。TFT650 のソース領域またはドレイン領域のいずれか一方に接続された配線 651 は、第 1 の層間絶縁膜 652 と完全に重なってはおらず、一部露出している。また第 1 の層間絶縁膜 654 は、第 1 の層間絶縁膜 652 と同様に液滴吐出法を用いて形成されており、該第 1 の層間絶縁膜 652 を覆うように第 1 の電極 653 が形成されている。そして配線 651 の一部露出している部分は第 1 の電極 653 と接しており、該接している部分を覆うように更に第 2 の層間絶縁膜 655 が形成されている。

#### 【0123】

第 2 の層間絶縁膜 655 は、第 1 の層間絶縁膜 654 と重なる領域に開口部を有しており、該開口部において、第 1 の電極 653 と、第 2 の層間絶縁膜 655 上に形成された電界発光層 656 と、第 2 の電極 657 とが重なり、発光素子を形成している。

#### 【0124】

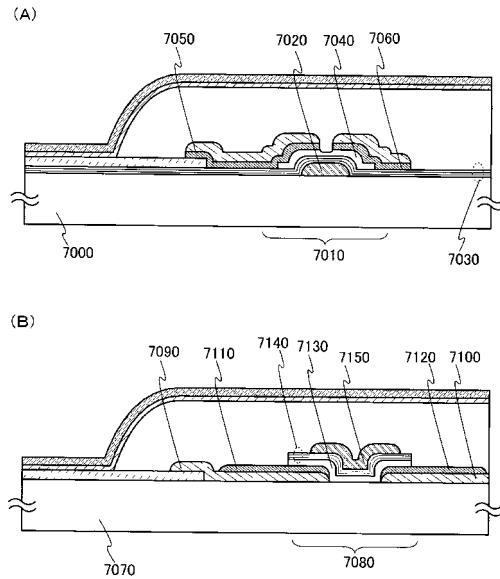

また図 4 乃至図 6、図 8、図 9 に示す表示装置では、TFT の第 1 の半導体膜と第 2 の半導体膜の間に保護膜を形成しているが、本発明はこの構成に限定されず、図 4 乃至図 6、図 8、9 の場合において、保護膜は必ずしも形成しなくて良い。図 10 (A) に、保護膜を形成していない場合の、画素の断面図を示す。図 10 (A) に示す TFT7010 は、基板 7000 上に形成されたゲート電極 7020 と、該ゲート電極 7020 を覆うように形成されたゲート絶縁膜 7030 と、該ゲート電極 7020 と重なるようにゲート絶縁膜 7030 上に形成された第 1 の半導体膜 7040 と、第 1 の半導体膜 7040 と接する第 2 の半導体膜 7050、7060 を有している。エッチングにより第 2 の半導体膜 7050、7060 を形成する際、SF<sub>6</sub>、NF<sub>3</sub>、CF<sub>4</sub>などのフッ化物気体を用いてエッチングガスとして用いる。そしてこのエッチングでは、第 1 の半導体膜 7040 とのエッチングの選択比がとれないので、処理時間を適宜調整して行なうこととなる。このエッチングにより、第 1 の半導体膜 7040 が一部露出する。

#### 【0125】

図 10 (A) のように保護膜を形成せず、第 1 の半導体膜 7040 と第 2 の半導体膜 7

10

20

30

40

50

050, 7060を、同じマスクを用いてパターニングする場合、ゲート絶縁膜7030と、第1の半導体膜7040と、第2の半導体膜7050, 7060とを、大気に触れさせることなく連続して形成することが可能である。すなわち、大気成分や大気中に浮遊する汚染物質に汚染されることなく各積層界面を形成することができるので、TFT特性のばらつきを低減することができる。

#### 【0126】

また図4乃至図6、図8、図9、図10(A)では、ゲート電極が第1の半導体膜よりも基板側に形成されているが、本発明はこの構成に限定されない。図10(B)に、第1の半導体膜がゲート電極よりも基板側に形成されている場合の、画素の断面図を示す。ただし図10(B)では、TFT7080を示す。図10(B)において、基板7070上に配線7090, 7100が形成されており、また配線7090, 7100上に接するよう、第2の半導体膜7110, 7120が形成されており、第2の半導体膜7110, 7120上に接するように第1の半導体膜7130が形成されている。そして第1の半導体膜7130上にはゲート絶縁膜7140が形成されており、第1の半導体膜7130と重なるように該ゲート絶縁膜7140上にゲート電極7150が形成されている。

10

#### 【0127】

なお、上記図4～図6、図8～図10に示したTFTは、いずれもソース領域またはドレイン領域として機能する第2の半導体膜を用いているが、第2の半導体膜は必ずしも形成する必要はない。この場合、配線が直接第1の半導体膜と接続され、該配線がソース領域またはドレイン領域として機能する。特に図10(B)に示したTFTは、第2の半導体膜を用いない場合、第2の半導体膜7110, 7120を形成するためのパターニングに用いるマスクが不要になるので、大幅に工程数を削減することができる。

20

#### 【0128】

##### (実施の形態2)

本発明の表示装置の画素構成の一例を示す。

#### 【0129】

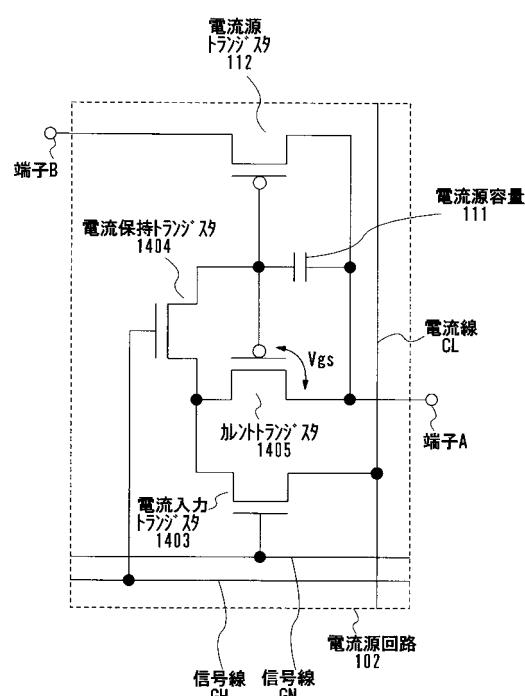

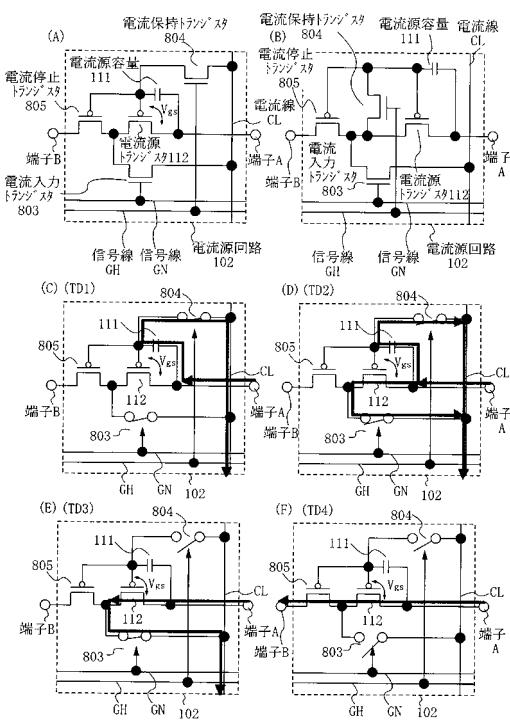

各画素に配置した電流源回路の構成例を図2に示す。なお、図2において、図1と同じ部分は、同じ符号を用いて示す。

#### 【0130】

なお、電流源回路を構成するトランジスタとしては、薄膜トランジスタ(TFT)でも、単結晶トランジスタ等のトランジスタでもどちらでも良い。

30

#### 【0131】

図2ではカレントミラー方式の電流源回路の例を示す。電流減回路102は、電流源容量111、電流源トランジスタ112、カレントトランジスタ1405、電流入力トランジスタ1403、電流保持トランジスタ1404、電流線CL、信号線GN、信号線GHとによって構成される。

電流源トランジスタ112とカレントトランジスタ1405は一対でカレントミラー回路を構成するので、極性は等しくなくてはならない。また、同一画素内のこれら2つのトランジスタの電流特性は等しいことが望まれる。ここで本実施の形態2では、簡単のため、電流源トランジスタ112とカレントトランジスタ1405の電流特性は等しいものとする。

40

#### 【0132】

図2において、電流源トランジスタ112及びカレントトランジスタ1405を、pチャネル型とした例を示す。なお、電流源トランジスタ112及びカレントトランジスタ1405をnチャネル型場合も、図1(C)に示した構造に従って、容易に応用することができる。

また、電流入力トランジスタ1403、電流保持トランジスタ1404はnチャネル型トランジスタとするが、单なるスイッチとして動作するため、pチャネル型トランジスタでもかまわない。

#### 【0133】

電流源トランジスタ 112 のゲート電極とカレントトランジスタ 1405 のゲート電極及び、電流源容量 111 の一方の電極は接続されている。また、電流源容量 111 の他方の電極は、電流源トランジスタ 112 のソース端子及びカレントトランジスタ 1405 のソース端子と接続され、電流源回路 102 の端子 A に接続されている。

カレントトランジスタ 1405 のゲート電極とドレイン端子は、電流保持トランジスタ 1404 のソース・ドレイン端子間を介して、接続されている。電流保持トランジスタ 1404 のゲート電極は、信号線 GH に接続されている。カレントトランジスタ 1405 のドレイン端子と電流線 CL は、電流入力トランジスタ 1403 のソース・ドレイン端子間を介して接続されている。電流入力トランジスタ 1403 のゲート電極は、信号線 GN に接続されている。また、電流源トランジスタ 112 のドレイン端子は、端子 B に接続されている。10

#### 【 0134 】

なお上記構成において、電流入力トランジスタ 1403 を、カレントトランジスタ 1405 と端子 A の間に配置しても良い。つまり、カレントトランジスタ 1405 のソース端子が電流入力トランジスタ 1403 のソース・ドレイン端子間を介して端子 A に接続され、カレントトランジスタ 1405 のドレイン端子が電流線 CL に接続された構成であってもよい。

#### 【 0135 】

また、上記構成において、カレントトランジスタ 1405 及び電流源トランジスタ 112 のゲート電極は、電流入力トランジスタ 1403 のソース・ドレイン端子間を介さず、電流線 CL に接続されていても良い。つまり、電流保持トランジスタ 1404 のソース端子及びドレイン端子の、カレントトランジスタ 1405 及び電流源トランジスタ 112 のゲート電極と接続されていない側が、電流線 CL に直接接続されている構成でも良い。その場合、電流線 CL の電位を調整することにより、電流保持トランジスタ 1404 のソース・ドレイン間電圧を小さくすることができる。なお、これに限定されず、電流保持トランジスタ 1404 は、導通状態となった際に、カレントトランジスタ 1405 のゲート電極の電位を電流線 CL の電位と等しくするように接続されれば良い。20

#### 【 0136 】

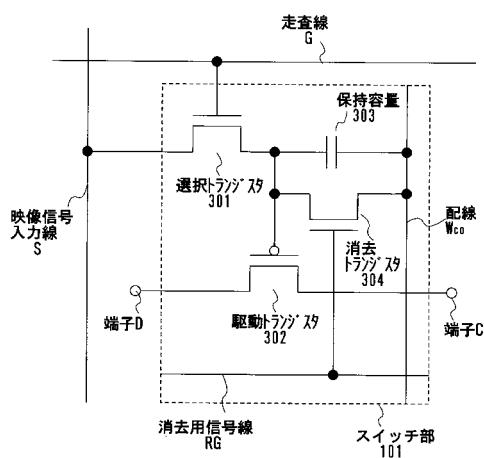

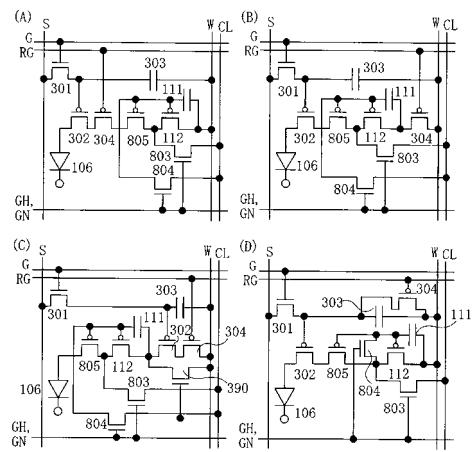

次に、図 1 (A) におけるスイッチ部の構成例を、図 3 に示す。なお、図 3 において、図 1 と同じ部分は同じ符号を用いて示す。30

#### 【 0137 】

図 3 において、スイッチ部 101 は、3 つのトランジスタ（選択トランジスタ 301、駆動トランジスタ 302、消去トランジスタ 304）と、1 つの容量素子（保持容量 303）によって構成される。保持容量 303 は、トランジスタのゲート容量などを利用することにより省略することも可能である。図 3 では、駆動トランジスタ 302 を p チャネル型トランジスタとし、選択トランジスタ 301 及び消去トランジスタ 304 を n チャネル型トランジスタとするが、この構成に限定されない。単なるスイッチとして動作するので、選択トランジスタ 301、駆動トランジスタ 302、消去トランジスタ 304 は、それぞれ n チャネル型トランジスタでも p チャネル型トランジスタでもどちらでもかまわない。40

#### 【 0138 】

なお、駆動トランジスタ 302 は、飽和領域で動作させてもよい。駆動トランジスタ 302 を飽和領域で動作させることによって、駆動トランジスタ 302 と直列に接続された電流源回路の電流源トランジスタ 112 の飽和領域特性を補うことが可能である。飽和領域特性とは、ソース・ドレイン間電圧に対してドレイン電流が一定に保たれる特性を示すものである。また、飽和領域特性を補うとは、飽和領域で動作する電流源トランジスタ 112 においても、ソース・ドレイン間電圧が増加するに従ってドレイン電流が増加するのを抑制することを意味する。なお、上記効果を得るために、駆動トランジスタ 302 と電流源トランジスタ 112 は同極性でなくてはならない。

#### 【 0139 】

10

20

30

40

50

上記の飽和領域特性を補う効果について以下に説明する。例えば、電流源トランジスタ 112 のソース・ドレイン間電圧が増加する場合に注目する。電流源トランジスタ 112 と駆動トランジスタ 302 は直列に接続されている。よって、電流源トランジスタ 112 のソース・ドレイン間電圧の変化によって、駆動トランジスタ 302 のソース端子の電位が変化する。こうして駆動トランジスタ 302 のソース・ゲート間電圧の絶対値は小さくなると、駆動トランジスタ 302 の I - V 曲線が変化する。この変化の方向はドレン電流が減少する方向である。こうして、駆動トランジスタ 302 に直列に接続された電流源トランジスタ 112 のドレン電流は減少する。同様に、電流源トランジスタ 112 のソース・ドレイン間電圧が減少すると、電流源トランジスタ 112 のドレン電流は増加する。このようにして、電流源トランジスタ 112 を流れる電流を一定に保つような効果が得られる。10

#### 【0140】

図 1 のスイッチ部の構成について以下に詳細に説明する。選択トランジスタ 301 のゲート電極は、走査線 G に接続されている。選択トランジスタ 301 のソース端子とドレン端子は、一方は映像信号入力線 S に接続され、他方は、駆動トランジスタ 302 のゲート電極に接続されている。駆動トランジスタ 302 のソース端子とドレン端子は、一方は端子 D に接続され、他方は端子 C に接続される。保持容量 303 の一方の電極は駆動トランジスタ 302 のゲート電極に接続され、他方の電極は配線 W<sub>c0</sub> に接続されている。消去トランジスタ 304 のソース端子とドレン端子は、一方は駆動トランジスタ 302 のゲート電極と接続され、他方は、配線 W<sub>c0</sub> に接続されている。消去トランジスタ 304 のゲート電極は消去用信号線 R<sub>G</sub> に接続されている。20

#### 【0141】

なお、消去トランジスタ 304 のソース端子及びドレン端子は、上記接続構造に限定されない。消去トランジスタ 304 をオンの状態とすることによって、保持容量 303 に保持された電荷が放出されるような、様々な接続構造とすることが可能である。つまり、消去トランジスタ 304 を導通または非導通させることにより、駆動トランジスタ 302 が非導通となるような接続構造とすればよい。

#### 【0142】

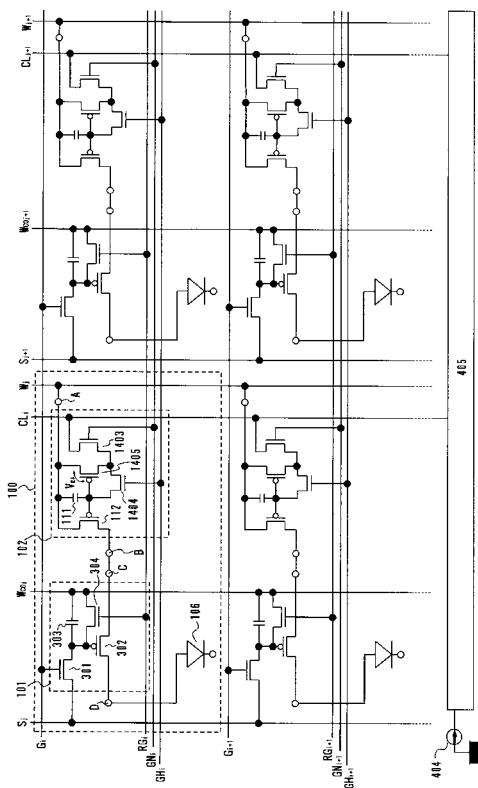

上述した構成の電流源回路及びスイッチ部を有する画素について、以下に説明する。図 2 に示す構成の電流源回路 102 と、図 3 に示す構成のスイッチ部 101 を有する画素 100 が、x 列 y 行のマトリクス状に配置した画素領域の一部の回路図を図 7 に示す。図 7において、第 i (i は自然数) 行 j (j は自然数) 列、第 (i + 1) 行 j 列、第 i 行 (j + 1) 列、第 (i + 1) 行 (j + 1) 列の 4 画素のみを代表的に示す。図 2 及び図 3 と同じ部分は同じ符号を用いて示し説明は省略する。なお、第 i 行、第 (i + 1) 行それぞれの画素行に対応する、走査線 G を G<sub>i</sub>、G<sub>i + 1</sub>、消去用信号線を R<sub>G i</sub>、R<sub>G i + 1</sub>、信号線 G<sub>N</sub> を G<sub>N i</sub>、G<sub>N i + 1</sub>、信号線 G<sub>H</sub> を G<sub>H i</sub>、G<sub>H i + 1</sub> と表記する。また、第 j 列、第 (j + 1) 列それぞれの画素列に対応する、映像信号入力線 S を S<sub>j</sub>、S<sub>j + 1</sub>、電源線 W を W<sub>j</sub>、W<sub>j + 1</sub>、電流線 C<sub>L</sub> を C<sub>L j</sub>、C<sub>L j + 1</sub>、配線 W<sub>C O</sub> を W<sub>C O j</sub>、W<sub>C O j + 1</sub> と表記する。電流線 C<sub>L j</sub>、C<sub>L j + 1</sub> には、画素領域外部より基準電流が入力される。3040

#### 【0143】

図 7 では、発光素子の画素電極を陽極とし、対向電極を陰極とした構成について示した。つまり、電流源回路の端子 A が電源線 W に接続され、端子 B がスイッチ部 101 の端子 C に接続された構成を示した。しかし、発光素子 106 の画素電極を陰極とし、対向電極を陽極とした構成の表示装置にも、本実施の形態の構成を容易に応用することもできる。図 7 では電流源トランジスタ 112 及びカレントトランジスタ 1405 は p チャネル型とした。

#### 【0144】

また図 7において、駆動トランジスタ 302 は、単なるスイッチとして機能するので、n チャネル型でも p チャネル型でもどちらでも良い。ただし、駆動トランジスタ 302 は50

、そのソース端子の電位が固定された状態で動作するのが好ましい。そのため、図7に示すような発光素子106の画素電極を陽極とし、対向電極を陰極とした構成では、駆動トランジスタ302はpチャネル型のほうが好ましい。一方、発光素子106の画素電極を陰極とし、対向電極を陽極とした構成では、駆動トランジスタ302はnチャネル型のほうが好ましい。

#### 【0145】

なお、図7において、各画素の配線 $W_{CO}$ と電源線Wとは、同じ電位に保たれていてもよいため、共用することができる。また、異なる画素間の配線 $W_{CO}$ 同士、電源線W同士、配線 $W_{CO}$ と電源線Wも共用することができる。 $GNI$ と $GH_i$ も共用できる。更に、配線W<sub>CO</sub>や配線W<sub>j</sub>のかわりに他の画素行の走査線を使用してもよい。これは、映像信号の書き込みを行っていない間、走査線の電位が一定の電位に保たれることを利用している。例えば電源線のかわりに、1つ前の画素行の走査線 $G_{i-1}$ を用いてもいい。ただしこの場合、走査線Gの電位を考慮して、選択トランジスタ301の極性に注意する必要がある。

10

#### 【0146】

図7では図示しないが、走査線Gに信号を入力する駆動回路（以下、走査線駆動回路と表記する）や、消去用信号線RGに信号を入力する駆動回路（以下、消去用信号線駆動回路と表記する）及び映像信号入力線Sに信号を入力する駆動回路（以下、信号線駆動回路と表記する）は、公知の構成の電圧信号出力型の駆動回路を自由に用いることができる。また、その他の信号線に信号を入力する駆動回路も、公知の構成の電圧信号出力型の駆動回路を自由に用いることができる。

20

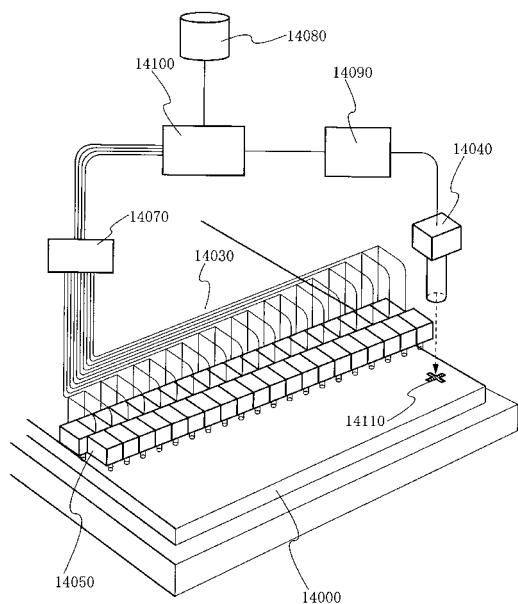

#### 【0147】

電流線 $CL_j$ 、 $CL_{j+1}$ に流れる基準電流を定めるために基準電流出力回路の外部に設けられた電流源回路（以下、参照電流源回路と表記する）を模式的に404で示す。1つの参照電流源回路404からの出力電流を用いて、複数の電流線CLに流れる基準電流を定めることができる。こうして、各電流線を流れる電流のはらつきを抑え、全ての電流線を流れる電流を正確に基準電流に定めることができる。なお本実施の形態では、全ての電流線 $CL_1 \sim CL_x$ に流れる基準電流を定める参照電流源回路404を共有した例について示す。参照電流源回路404によって定められる電流を用いて、各電流線 $CL_1 \sim CL_x$ に基準電流を出力するための回路を、基準電流出力回路と呼び図7中405で示す。

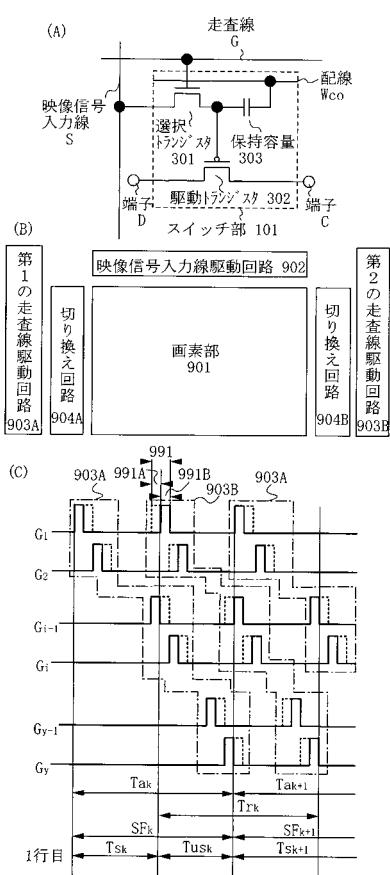

#### 【0148】

30

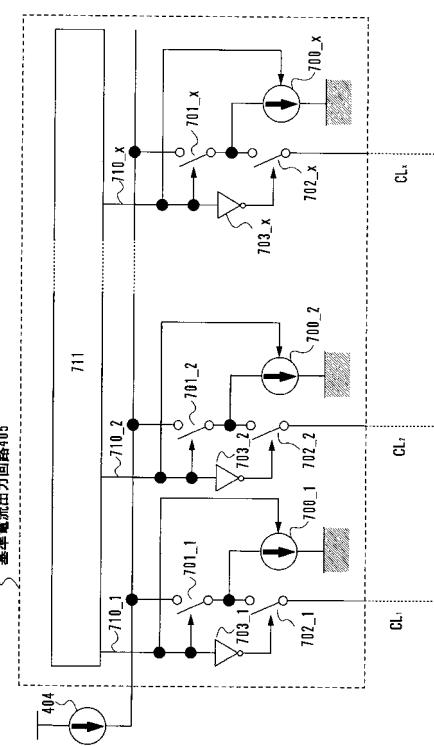

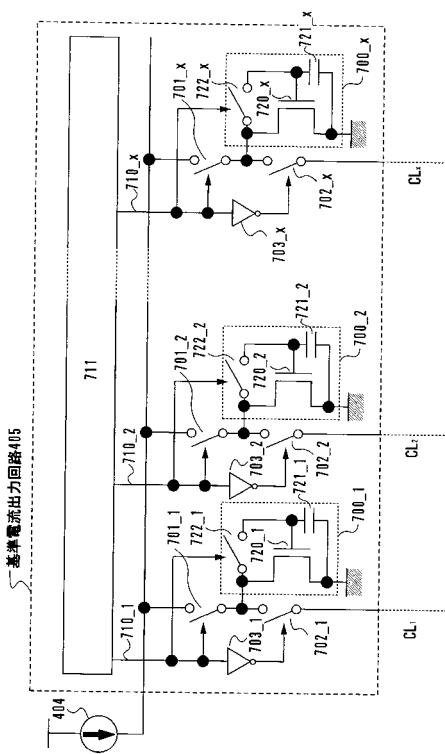

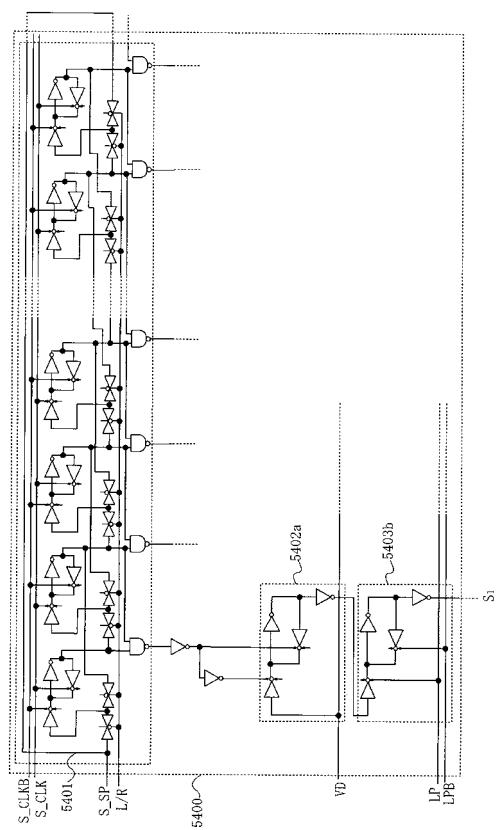

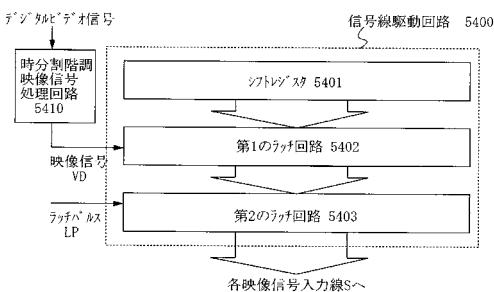

基準電流出力回路405の構成を図12に示す。基準電流出力回路405は、シフトレジスタ等のパルス出力回路711を有する。パルス出力回路711からのサンプリングパルスが入力されるサンプリングパルス線 $710_1 \sim 710_x$ が、各電流線 $CL_1 \sim CL_x$ に対応して設けられている。ある1本の電流線 $CL_j$ に対応する構成を代表的に説明する。サンプリングパルス線 $710_j$ の信号が入力される電流入力スイッチ $701_j$ 及び電流源回路 $700_j$ と、サンプリングパルス線 $710_j$ の信号がインバータ $703_j$ を介して入力される電流出力スイッチ $702_j$ とが設けられている。電流源回路 $700_j$ は、電流入力スイッチ $701_j$ を介して参照電流源回路404と接続され、電流出力スイッチ $702_j$ を介して電流線 $CL_j$ と接続される。

#### 【0149】

40

図12に示す基準電流出力回路405において、電流源回路 $700_1 \sim 700_x$ の構成を具体的に示した例を図13に示す。図13において、図12と同一部分は、同じ符号を用いて示す。なお、基準電流出力回路405は、図12、図13のような回路には限定されない。電流源回路 $700_1 \sim 700_x$ はそれぞれ、電流源トランジスタ $720_j$ と、電流源容量 $721_j$ と、電流保持スイッチ $722_j$ とを有する。電流源トランジスタ $720_j$ は、ゲート電極とソース端子が、電流源容量 $721_j$ を介して接続され、ゲート電極とドレイン端子が、電流入力スイッチ $722_j$ を介して接続される。電流入力スイッチ $722_j$ には、サンプリングパルス線 $710_j$ の信号が入力されている。電流源トランジスタ $720_j$ のソース端子は、一定の電位に保たれ、ドレイン端子は、電流入力スイッチ $701_j$ を介して参照電流源回路404と接続され、また、

50

電流出力スイッチ 702\_j を介して電流線 C\_L\_j と接続されている。なお、電流源容量 721\_j の電極の一方が、一定の電位に保たれ、他方が、電流入力スイッチ 701\_j を介して参照電流源回路 404 と接続され、且つ、電流出力スイッチ 702\_j を介して電流線 C\_L\_j と接続された構成であってもよい。

#### 【0150】

なお図13において電流源トランジスタ 720\_j は、nチャネル型でもpチャネル型でもどちらでもかまわない。ただし、電流源トランジスタ 720\_j は、ソース端子の電位が固定された状態で動作することが望ましい。そのため、電流源回路 700\_j から電流線 C\_L\_j の方へ電流が流れていく場合は電流源トランジスタ 720\_j はpチャネル型であることが望ましく、電流線 C\_L\_j から電流源回路 700\_j の方へ電流が流れいく場合は電流源トランジスタ 720\_j はnチャネル型が望ましい。どちらの極性であっても、ゲート・ソース間に電流源容量 721\_j が接続されていることが望ましい。

10

#### 【0151】

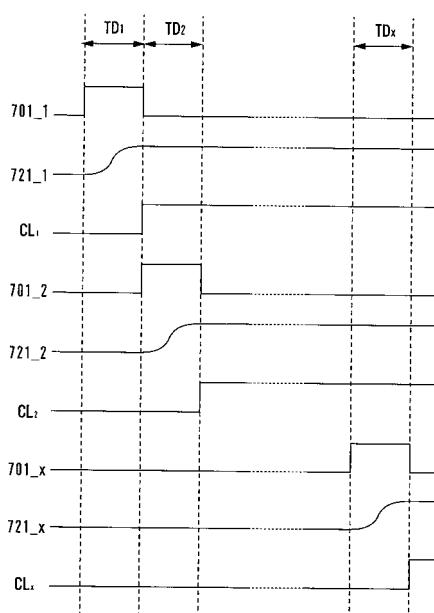

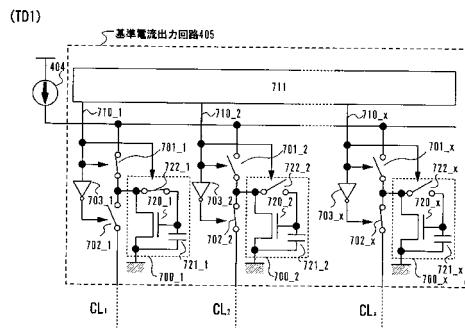

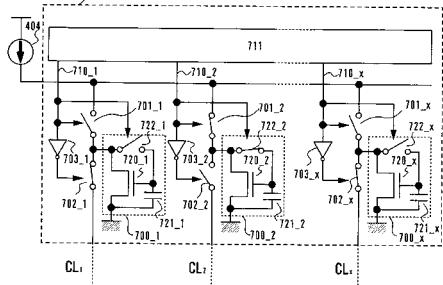

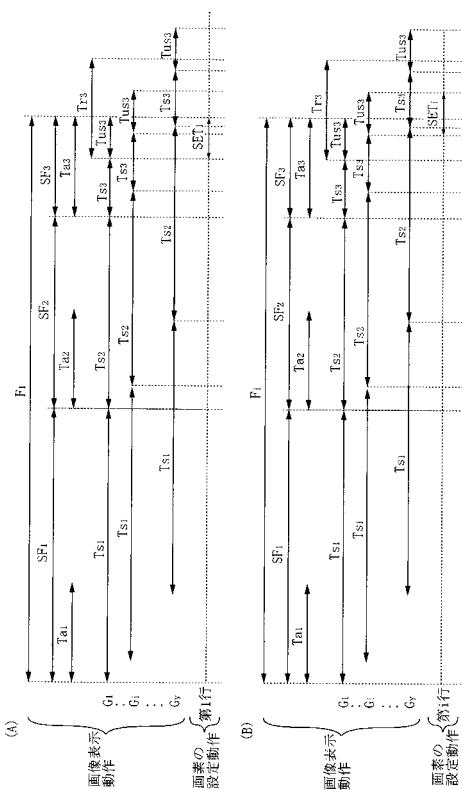

図13に示した構成の基準電流出力回路405の駆動方法について、図14及び図15を用いて説明する。図14は、基準電流出力回路405の駆動方法を示すタイミングチャートである。また、図15は、基準電流出力回路405の駆動方法を模式的に示した図である。なお、図14において、期間 TD1、期間 TD2 それぞれの際の基準電流出力回路405における各スイッチ（電流入力スイッチ、電流出力スイッチ、電流保持スイッチ）のオン・オフの状態を模式的に示した図が、図15（TD1）、図15（TD2）である。

20

#### 【0152】

期間 TD1において、パルス出力回路 711 よりサンプリングパルス線 710\_1 にパルスが出力されると、電流入力スイッチ 701\_1 及び電流保持スイッチ 722\_1 がオンの状態となる。一方電流出力スイッチ 702\_1 は、サンプリングパルス線 710\_1 に出力された信号がインバータ 703\_1 を介して入力され、オフの状態である。このとき、参照電流源回路 404 によって定められる基準電流が、電流入力スイッチ 701\_1 及び電流保持スイッチ 722\_1 を介して、電流源回路 700\_1 の電流源容量 721\_1 に入力される。なお、このとき他のサンプリングパルス線 710\_2 ~ 710\_x には、パルスが出力されていない。そのため、電流入力スイッチ 701\_2 ~ 701\_x 及び電流保持スイッチ 722\_2 ~ 722\_x は、オフの状態である。一方、電流出力スイッチ 702\_2 ~ 702\_x は、オンの状態である。時間が経過すると、電流源回路 700\_1 の電流源容量 721\_1 に電荷が保持され、電流源トランジスタ 720\_1 に、基準電流が流れる。図14において、電流源容量 721\_1 の両電極間に保持された電荷量すなわち電圧の変化を示す。

30

#### 【0153】

この後期間 TD2 が始まる。期間 TD2 においてパルス出力回路 711 の出力が変化し、サンプリングパルス線 710\_1 にパルスが出力されなくなる。すると、電流保持スイッチ 722\_1 及び電流入力スイッチ 701\_1 がオフの状態となり、電流出力スイッチ 702\_1 がオンの状態となる。こうして、電流線 C\_L\_1 には、電流源トランジスタ 720\_1 のドレン電流が流れる状態となる。ここで電流源トランジスタ 720\_1 のドレン電流は、電流源容量 721\_1 に保持された電荷によって定まる。よって、電流線 C\_L\_1 を流れる電流が基準電流に定まる。図14において、C\_L\_1 ~ C\_L\_x は、電流線 C\_L\_1 ~ C\_L\_x を流れる電流を示す。同時にサンプリングパルス線 710\_2 にパルスが出力される。こうして、電流源回路 700\_2 を流れる電流を基準電流に定める動作が開始される。同様の動作を、全てのサンプリングパルス線 710\_1 ~ 710\_x に対応する電流源回路 700\_1 ~ 700\_x について行い、期間 TD1 ~ TDx が終了する。こうして、全ての電流線 C\_L\_1 ~ C\_L\_x に流れる電流が、参照電流源回路 404 によって決められた基準電流に定まる。

40

#### 【0154】

ここで、基準電流出力回路405に電流を入力し、各電流線 C\_L\_1 ~ C\_L\_x に流れる電

50

流を基準電流に定める動作を、基準電流出力回路 405 の設定動作と呼ぶ。図 13 に示した構成の基準電流出力回路 405 の構成では、一旦、参照電流源回路 404 によって、各電流源回路 700\_1 ~ 700\_x に流れる電流を基準電流に定めた後は、電流源容量 721\_1 ~ 721\_x に保持された電荷が放電しない限り、各電流源回路 700\_1 ~ 700\_x を流れる電流は基準電流に保たれる。なお、図 13 のように電流源回路 700 の部分が同一トランジスタ方式の電流源回路の場合は、参照電流源回路 404 から入力した電流と、各電流線 CL を流れる基準電流とでは、大きさが同じになる。もし、電流源回路 700 の部分がカレントミラー方式やマルチゲート方式の電流源の場合は、参照電流源回路 404 から入力した電流と CL に流れる基準電流とでは、大きさを異ならせることができる。

10

#### 【0155】

なお図 14 では、電流源容量 721\_1 ~ 721\_x に電荷が保持されていない状態から、期間 TD1 ~ TDx の動作を一回行うことで、電流源トランジスタ 720\_1 ~ 720\_x が基準電流を流すように、所定の電荷を各電流源容量 721\_1 ~ 721\_x に保持させる手法を示した。この手法を一括書き込み方式と呼ぶ。一方、電流源容量 721\_1 ~ 721\_x に電荷が保持されていない状態から、期間 TD1 ~ TDx までの動作を繰り返し、少しづつ電流源容量 721\_1 ~ 721\_x に電荷を保持させる手法を用いることもできる。この手法では、期間 TD1 ~ TDx までの動作を複数回繰り返した後、初めて、電流源トランジスタ 720\_1 ~ 720\_x が基準電流を流すような、所定の電荷が各電流源容量 721\_1 ~ 721\_x に保持される。この手法を、分割書き込み方式と呼ぶ。分割書き込み方式において、各電流源容量 721\_1 ~ 721\_x が電荷を保持しない状態から、所定の電荷を保持するまでに、期間 TD1 ~ TDx を繰り返した回数を分割書き込み方式の分割数と呼ぶ。

20

#### 【0156】

分割書き込み方式の場合の期間 TD1 ~ TDx にそれぞれにおける各スイッチ（電流入力スイッチ 701\_1 ~ 701\_x、電流出力スイッチ 702\_1 ~ 702\_x、電流保持スイッチ 722\_1 ~ 722\_x）の状態は、一括書き込み方式と同様である。しかし、分割書き込み方式において期間 TD1 ~ TDx を 1 回行うのに要する時間は、一括書き込み方式において期間 TD1 ~ TDx を行うのに要する時間と比較して短くすることができる。なお、基準電流出力回路 405 の設定動作は、1 フレーム期間に何回行っても良いし、数フレーム期間で 1 回行っても良い。また、1 水平期間で何回行っても良いし、何回か水平期間を繰り返す毎に 1 回行っても良い。基準電流出力回路 405 の設定動作を繰り返す間隔は、基準電流出力回路の有する電流源容量 721 が電荷を保持し続ける能力に応じて、任意に選択することができる。

30

#### 【0157】

なお、基準電流出力回路 405 に入力する基準電流は、図 7、図 12、図 13、図 15 に示したように参照電流源回路 404 より入力する構成であってもよいし、参照電流源回路 404 は設けず、表示装置の外部より入力した一定電流を電流として入力する構成であっても良い。あるいは、図 12 や図 13 の電流源回路 700 に相当する電流源回路が表示装置の外部にあってもよい。また、トランジスタのばらつきが小さい場合は基準電流出力回路 405 における各々の電流源回路 700 に、必ずしも設定動作を行わなくてもよい。しかし設定動作を行う方が、より正確な電流値を出力できる。

40

#### 【0158】

次に、図 7 に示した構成の画素を有する表示装置の駆動方法を説明する。ここで、実施の形態の構成の画素では、画像表示動作（スイッチ部の駆動動作）と、電流源回路の設定動作（画素の設定動作）は、非同期で行うことができる。つまり、スイッチ部の端子 C と端子 D が導通・非導通状態に関わらず、画素の設定動作を行うことができる。

#### 【0159】

また、基準電流出力回路 405 の設定動作も、画像表示動作や画素の設定動作と同期して行うこともできるし、非同期に行うこともできる。ただし、図 13 に示したような基準

50

電流出力回路 405 の設定動作は、画素の設定動作を行っていない期間に行うのが望ましい。なぜなら、図 13 のような基準電流出力回路 405 では、その設定動作を行っている最中には、電流線 CLj に電流を出力できないからである。そこで、各電流線 CLj に、電流源回路 700 を 2 個配置すれば、一方の電流源回路が電流線 CLj に電流を出力する間に、他方の電流源回路に対して基準電流出力回路 405 の設定動作を行うことができる。そのため、基準電流出力回路 405 の設定動作と画素の設定動作を同時にを行うことができる。あるいは、電流源回路 700\_j の回路として、カレントミラー回路を用いて、カレントミラー回路を構成する 1 対のトランジスタの一方のトランジスタが電流線 CLj に電流を出力し、もう一方のトランジスタが基準電流出力回路 405 の設定動作を行えば、基準電流出力回路 405 の設定動作と画素の設定動作を同時にを行うことができる。

10

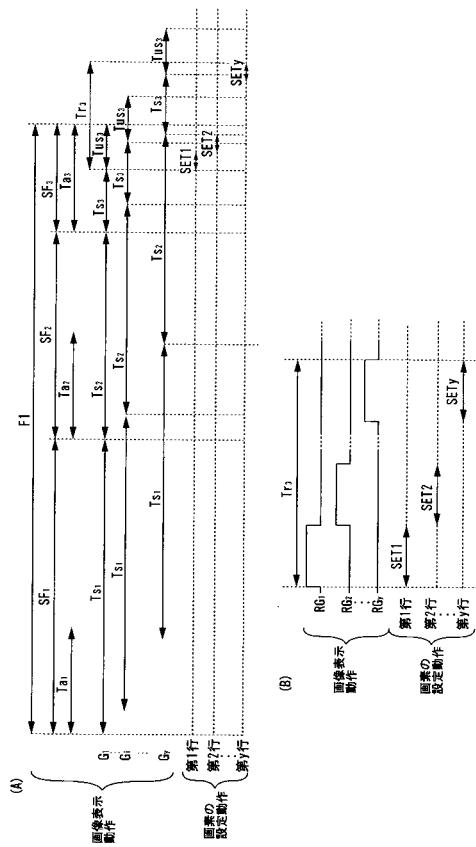

#### 【0160】

簡単のため、まず画素の設定動作と画像表示動作とを別々に説明する。画像表示動作について、図 17(A)、図 17(B) のタイミングチャート及び図 7 の回路図を用いて説明する。走査線 Gi に信号が入力され、第 i 行の画素の選択トランジスタ 301 が導通状態となる。このとき、映像信号入力線 S1 ~ Sx に映像信号が入力され、第 i 行の各画素に映像信号が入力される。そして、映像信号によって駆動トランジスタ 302 が導通状態となった画素において、端子 D と端子 C が導通状態となる。駆動トランジスタ 302 のゲート電圧は保持容量 303 によって保持される。つまり、駆動トランジスタ 302 の導通又は非導通状態は、保持される。なおこのとき、消去トランジスタ 304 は非導通状態であるとする。こうして、スイッチ部 101 の端子 D と端子 C が導通状態となった画素においては、電流源回路 102 より画素基準電流が発光素子 106 に入力されて発光する。

20

#### 【0161】

このように、各画素の発光状態及び非発光状態を選択し、デジタル方式によって階調を表現する。多階調化の方法としては、一定期間毎に、各画素の発光又は非発光状態が選択される期間を複数設定し、発光状態が選択された時間の累計を制御する階調方式（時間階調方式）や、1 画素を複数のサブ画素に分割し、発光状態が選択されたサブ画素の面積の累計を制御する階調方式（面積階調方式）等を用いることができる。また、公知の手法を用いることができる。ここでは、多階調化の手法としては時間階調方式を用いる。

#### 【0162】

ここで、消去トランジスタ 304 を導通状態とすることによって、保持容量 303 の両電極の電位を同じにし、保持容量 303 に保持された電荷を放電することによって、駆動トランジスタ 302 を一律に非導通状態とすることができます。これにより、ある行の画素に映像信号を入力している最中であっても、別の行の画素を非発光状態とすることができます。こうして、各行の画素の発光期間を任意に設定することができる。

30

#### 【0163】

図 3 で示した構成のスイッチ部は、第 1 のスイッチとして、選択トランジスタ 301、第 2 のスイッチとして、駆動トランジスタ 302 を有し、その他に消去トランジスタ 304 を有する構成である。消去トランジスタ 304 のゲート電極は、映像信号入力線 S 及び走査線 G とは別の配線、消去用信号線 RG に接続されている。こうして、消去トランジスタ 304 は、選択トランジスタ 301 や駆動トランジスタ 302 に入力される信号に関わらず、消去用信号線 RG に入力された信号によって、導通・非導通状態が切り替えられる。こうして、第 1 のスイッチや第 2 のスイッチの状態に関わらず、スイッチ部の端子 C と端子 D 間を非導通状態とすることができます。以上が、基本的な画像表示動作である。

40

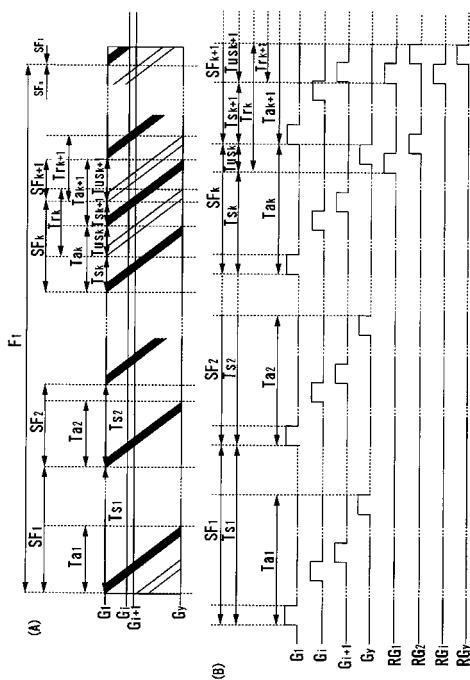

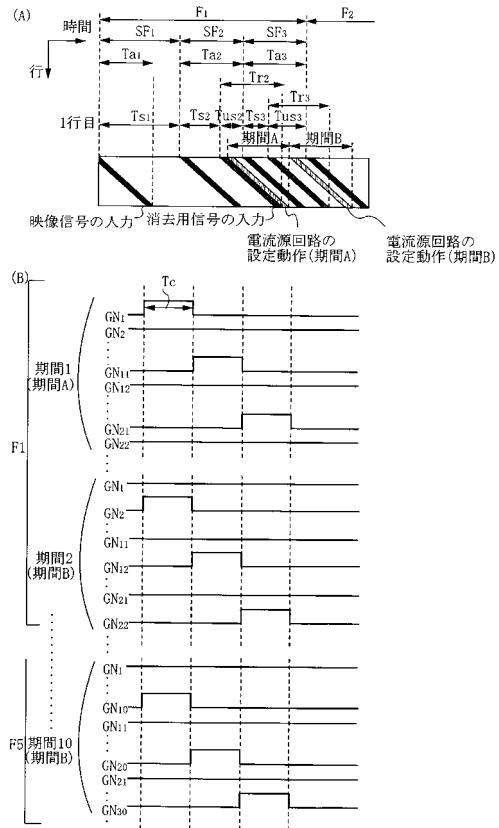

#### 【0164】

次に、図 17において、階調表示方法の具体例として、時分割階調方式を用い場合の駆動方法の一例を示す。1 画面分の画像を表示する期間を、1 フレーム期間 F と呼ぶ。1 フレーム期間 F を複数のサブフレーム期間 SF1 ~ SFn (n は自然数) に分割する。第 1 のサブフレーム期間 SF1 において、第 1 行の走査線 G1 が選択され、走査線 G1 にゲート電極が接続された選択トランジスタ 301 は導通状態となる。ここで、映像信号入力線 S1 ~ Sx に一斉に信号が入力される。なおこのとき、消去トランジスタ 304 は、非導

50

通状態である。映像信号入力線 S<sub>1</sub> ~ S<sub>x</sub> に入力された信号によって、第 1 行の各画素の駆動トランジスタ 302 の導通・非導通状態が選択され、各画素の発光・非発光状態が選択される。また、駆動トランジスタ 302 のゲート電圧は、保持容量 303 によって保持される。ここで、各画素の駆動トランジスタ 302 の導通・非導通状態を選択するために、映像信号を入力することを、画素に映像信号を書き込むと表現することにする。

#### 【0165】

導通状態を選択された駆動トランジスタ 302 は、映像信号入力線 S より新たな信号が駆動トランジスタ 302 のゲート電極に入力されるまで、又は、保持容量 303 の電荷が消去トランジスタ 304 によって放電されるまで、導通状態が保たれる。発光状態が選択された画素において、スイッチ部の端子 C と端子 D の間が導通状態となり、電流源回路 10 102 から画素基準電流が発光素子 106 に入力されて発光する。そして、第 1 行の画素の映像信号の書き込み動作が終了すると直ちに、第 2 行の画素に対応する走査線 G<sub>2</sub> が選択され、第 2 行に対応する画素への映像信号の書き込み動作が開始される。画素への映像信号の書き込み動作は、第 1 行の画素の動作と同様である。

#### 【0166】

上記動作を全ての走査線 G<sub>1</sub> ~ G<sub>y</sub> に対して繰り返し、全ての画素に映像信号を書き込む。全ての画素に映像信号を書き込む期間を、アドレス期間 T<sub>a</sub> と表記する。第 m ( m は、n 以下の自然数 ) のサブフレーム期間 S<sub>Fm</sub> に対応するアドレス期間を T<sub>am</sub> と表記する。映像信号が書き込まれた画素行は、それぞれ発光又は非発光状態が選択されている。書き込まれた映像信号に応じて、各画素行の各画素が発光又は非発光する期間を表示期間 T<sub>s</sub> と表記する。同じサブフレーム期間において、各画素行の表示期間 T<sub>s</sub> は、タイミングは異なるがその長さは全て同じである。第 m ( m は、n 以下の自然数 ) のサブフレーム期間 S<sub>Fm</sub> に対応する表示期間を T<sub>sm</sub> と表記する。

#### 【0167】

第 1 のサブフレーム期間 S<sub>F1</sub> から第 k - 1 ( k は n より小さな自然数 ) のサブフレーム期間 S<sub>Fk-1</sub> までは、表示期間 T<sub>s</sub> はアドレス期間 T<sub>a</sub> より長く設定されているとする。所定の長さの表示期間 T<sub>s1</sub> の後、第 2 のサブフレーム期間 S<sub>F2</sub> が開始される。この後、第 2 のサブフレーム期間 S<sub>F2</sub> から第 k - 1 のサブフレーム期間 S<sub>Fk-1</sub> についても、第 1 のサブフレーム期間 S<sub>F1</sub> と同様に、表示装置は動作する。ここで、複数の画素行に同時に映像信号の書き込みを行うことができないため、各サブフレーム期間のアドレス期間 T<sub>a</sub> はそれぞれ重複しないように設定されている。

#### 【0168】

一方、第 k のサブフレーム期間 S<sub>Fk</sub> から第 n のサブフレーム期間 S<sub>Fn</sub> は、表示期間 T<sub>s</sub> がアドレス期間 T<sub>a</sub> より短く設定されているとする。以下に、第 k のサブフレーム期間 S<sub>Fk</sub> から第 n のサブフレーム期間 S<sub>Fn</sub> までの表示装置の駆動方法を詳細に説明する。

#### 【0169】

第 k のサブフレーム期間 S<sub>Fk</sub> において、第 1 行の走査線 G<sub>1</sub> が選択され、走査線 G<sub>1</sub> にゲート電極が接続された選択トランジスタ 301 は導通状態となる。ここで、映像信号入力線 S<sub>1</sub> ~ S<sub>x</sub> に一斉に信号が入力される。なおこのとき、消去トランジスタ 304 は、非導通状態である。映像信号入力線 S<sub>1</sub> ~ S<sub>x</sub> に入力された信号によって、第 1 行の各画素の駆動トランジスタ 302 の導通・非導通状態が選択され、各画素の発光・非発光状態が選択される。また、駆動トランジスタ 302 のゲート電圧は、保持容量 303 によって保持される。発光状態が選択された画素において、スイッチ部の端子 C と端子 D の間が導通状態となり、電流源回路 102 から画素基準電流が発光素子 106 に入力され、発光素子 106 は発光する。第 1 行の画素の映像信号の書き込み動作が終了すると、次に第 2 行の画素に対応する走査線 G<sub>2</sub> が選択され、第 2 行に対応する画素への映像信号の書き込み動作が開始される。画素への映像信号の書き込み動作は、第 1 行の画素の動作と同様である。

#### 【0170】

10

20

30

40

50

上記動作を全ての走査線 G<sub>1</sub> ~ G<sub>y</sub> に対して繰り返し、全ての画素に映像信号を書き込みアドレス期間 T<sub>a k</sub> が終了する。上記の第 k のサブフレーム期間 S<sub>F k</sub> のアドレス期間 T<sub>a k</sub> の動作方法は、第 1 のサブフレーム期間 S<sub>F 1</sub> から第 k - 1 のサブフレーム期間 S<sub>F k - 1</sub> と同様である。異なるのは、アドレス期間 T<sub>a k</sub> が終了する前に、消去用信号線 R<sub>G 1</sub> などの選択が始まることがある。つまり、走査線 G<sub>1</sub> が選択されてから、所定の期間（この期間が表示期間 T<sub>s k</sub> に相当する）が経過したあと、消去用信号線 R<sub>G 1</sub> が選択される。そして、消去用信号線 R<sub>G 1</sub> ~ R<sub>G y</sub> を順に選択し、各画素行の消去トランジスタ 304 を順に導通状態とし、各行の画素を順に一律に非発光状態とする。全ての画素の消去トランジスタ 304 を導通状態とする期間を、リセット期間 T<sub>r</sub> と表記する。特に、第 p (p は、k 以上 n 以下の自然数) のサブフレーム期間 S<sub>F p</sub> に対応するリセット期間を T<sub>r p</sub> と表記する。

#### 【0171】

このように、ある行の画素に映像信号を入力している最中にも、別の行の画素を一律に非発光状態とすることができます。こうして、表示期間 T<sub>s</sub> の長さを自由に制御することができます。ここで、アドレス期間 T<sub>a p</sub> の長さとリセット期間 T<sub>r p</sub> の長さは同じであるとする。つまり、映像信号を書き込む際に各行を順に選択する速さと、各行の画素を順に一律に非発光状態とする際の速さとは、同じであるとする。よって、同一のサブフレーム期間において、各行の画素の表示期間 T<sub>s</sub> が始まるタイミングは異なるが、その長さはすべて同じである。

#### 【0172】

各画素行の消去トランジスタ 304 を導通状態とすることによって、各画素行の画素を一律に非発光状態とする期間を、非表示期間 T<sub>u s</sub> と表記する。同じサブフレーム期間において、各画素行の非表示期間 T<sub>u s</sub> は、タイミングは異なるがその長さは全て同じである。特に、第 p のサブフレーム期間 S<sub>F p</sub> に対応する非表示期間を T<sub>u s p</sub> と表記する。

#### 【0173】

所定の長さの非表示期間 T<sub>u s k</sub> の後、第 k + 1 のサブフレーム期間 S<sub>F k + 1</sub> が開始される。第 k + 1 のサブフレーム期間 S<sub>F k + 1</sub> から第 n のサブフレーム期間 S<sub>F n</sub> について、第 k のサブフレーム期間 S<sub>F k</sub> と同様の動作を繰り返し、1 フレーム期間 F<sub>1</sub> が終了する。ここで、サブフレーム期間 S<sub>F 1</sub> ~ S<sub>F n</sub> の、アドレス期間 T<sub>a 1</sub> ~ T<sub>a n</sub> の長さは全て同じである。以上のように表示装置を動作させ、各サブフレーム期間 S<sub>F 1</sub> ~ S<sub>F n</sub> の表示期間 T<sub>s 1</sub> ~ T<sub>s n</sub> の長さを適当に定めることによって、階調を表現する。

#### 【0174】

次に、表示期間 T<sub>s 1</sub> ~ T<sub>s n</sub> の長さの設定の仕方について述べる。例えば、T<sub>s 1</sub> : T<sub>s 2</sub> : ··· : T<sub>s n - 1</sub> : T<sub>s n</sub> を 20 : 2 - 1 : ··· : 2 - (n - 2) : 2 - (n - 1) と設定すれば 2<sup>n</sup> 階調を表現することができる。具体例として n = 3 の場合に、3 ビットの映像信号を入力し、8 階調を表現する例を挙げる。1 フレーム期間 F<sub>1</sub> は、3 つのサブフレーム期間 S<sub>F 1</sub> ~ S<sub>F 3</sub> に分割される。それぞれのサブフレーム期間の表示期間の長さの比 T<sub>s 1</sub> : T<sub>s 2</sub> : T<sub>s 3</sub> は、4 : 2 : 1 とすることができる。ある画素において、全てのサブフレーム期間 S<sub>F 1</sub> ~ S<sub>F 3</sub> で発光状態が選択された場合の輝度を 100 % とすると、第 1 のサブフレーム期間 S<sub>F 1</sub> のみ発光状態が選択された場合は、約 57 % の輝度が表現される。一方、第 2 のサブフレーム期間 S<sub>F 2</sub> のみ発光状態が選択された場合は、約 29 % の輝度が表現される。

#### 【0175】

なお上記の様に、1 フレーム期間中に、映像信号のビット数と同じ数のサブフレーム期間を設け、階調を表現する手法に限定されない。例えば、1 フレーム期間中に、映像信号のあるビットに対応する信号によって、発光状態・非発光状態が選択されるサブフレーム期間を複数設けることができる。つまり、1 ビットに対応する表示期間を複数のサブフレーム期間の表示期間の累計で表現する。特に、映像信号の上位ビットに対応する表示期間を、複数のサブフレーム期間がそれぞれ有する表示期間の累計で表現し、それらのサブフレーム期間を不連続に出現させることによって、擬似輪郭の発生を抑制することができる

10

20

30

40

50

。なお、各サブフレーム期間の表示期間  $T_s$  の長さの設定の仕方は、上記に限定されず公知のあらゆる手法を用いることができる。

#### 【0176】

図17では、第1のサブフレーム期間  $S_F_1$  から第nのサブフレーム期間  $S_F_n$  が順に出現する構成としたが、これに限定されない。各サブフレーム期間の出現する順は任意に定めることができる。また、時分割階調方式のみならず、面積階調方式によって、また、時分割階調方式と面積階調方式との組み合わせによって、階調を表現することもできる。

#### 【0177】

本実施の形態では、表示期間  $T_s$  をアドレス期間  $T_a$  より短く設定するサブフレーム期間においてのみ、リセット期間  $T_r$  及び非表示期間  $T_{us}$  を設ける駆動方法を示したがこれ限定されない。表示期間  $T_s$  をアドレス期間  $T_a$  より長く設定するサブフレーム期間においても、リセット期間  $T_r$  及び非表示期間  $T_{us}$  を設ける駆動方法とすることもできる。

10

#### 【0178】

また、図3では、消去トランジスタ304を導通状態とすることによって保持容量303の電荷を放電する構成を示したが、これに限定されない。消去トランジスタ304を導通状態することによって保持容量303の駆動トランジスタ302のゲート電極と接続された側の電位を、上げるか又は下げるかして、駆動トランジスタ302が非導通状態となる構成であれば良い。つまり、消去トランジスタ304を介して、駆動トランジスタ302のゲート電極を、駆動トランジスタ302が非導通状態となるような電位の信号が入力される配線と接続した構成であってもよい。また、上述のような消去トランジスタ304を導通状態とすることによって、保持容量303の駆動トランジスタ302のゲート電極と接続された側の電位を変化させるタイプの構成ではなく、消去トランジスタ304を駆動トランジスタ302と直列に接続し、消去トランジスタ304を非導通状態とすることによってスイッチ部101の端子Cと端子D間を非導通状態とし、非表示期間とする構成であってもよい。

20

#### 【0179】

なお、消去トランジスタを設けずに、画素を一律に非発光の状態とするリセット期間及び非表示期間を設ける手法を用いてもよい。その第1の手法は、保持容量の駆動トランジスタのゲート電極と接続されていない側の電極の電位を変化させることによって、駆動トランジスタを非導通状態とする手法である。この構成を図25に示す。保持容量303の駆動トランジスタ302のゲート電極と接続されていない側の電極は、配線Wcoに接続されている。配線Wcoの信号を変化させ、保持容量303の一方の電極の電位を変化させる。すると保持容量303に保持された電荷は保存されるため、保持容量303の他方の電極の電位も変化する。こうして、駆動トランジスタ302のゲート電極の電位を変化させて、駆動トランジスタ302を非導通状態とすることが出来る。

30

#### 【0180】

第2の手法は、1本の走査線が選択される期間を前半と後半に分割する。前半（ゲート選択期間前半と表記）には、映像信号を入力し、後半（ゲート選択期間後半と表記）には、消去信号を入力することを特徴とする。ここで、消去信号とは、駆動トランジスタのゲート電極に入力された際に、駆動トランジスタを非導通状態とするような信号であるとする。こうして、書き込み期間より短い表示期間を設定することが可能となる。この手法の詳細において、表示装置全体の構成について図25（B）を参照して説明する。表示装置はマトリクス状に配置された複数の画素を有する画素部901と、画素部901に信号を入力する映像信号入力線駆動回路902と、第1の走査線駆動回路903Aと、第2の走査線駆動回路903Bと、切り替え回路904Aと、切り替え回路904Bとを有する。第1の走査線駆動回路903Aは、ゲート選択期間前半に各走査線Gに信号を出力する回路である。また、第2の走査線駆動回路903Bは、ゲート選択期間後半に各走査線Gに信号を出力する回路である。切り替え回路904Aと切り替え回路904Bによって、第1の走査線駆動回路903Aと各画素の走査線Gとの接続又は、第2の走査線駆動回路9

40

03Bと各画素の走査線Gとの接続が選択される。映像信号入力線駆動回路902は、ゲート選択期間前半では映像信号を出力する。一方、ゲート選択期間後半では消去信号を出力する。

#### 【0181】

次いで、上記構成の表示装置の駆動方法について図25(C)を参照して説明する。なお、図17と同じ部分は同じ符号を用いて示し説明は省略する。図25(C)において、ゲート選択期間991は、ゲート選択期間前半991Aとゲート選択期間後半991Bに分割される。903Aにおいて、第1の走査線駆動回路によって各走査線が選択され、デジタルの映像信号が入力される。903Aの操作を行う期間は、書き込み期間Taに相当する。一方、903Bにおいて、第2の走査線駆動回路によって各走査線が選択され、消去信号が入力される。903Bの操作を行う期間は、リセット期間Trに相当する。こうして、アドレス期間Taより短い表示期間Tsを設定することができる。なお、ここではゲート選択期間後半に消去信号が入力されているが、そのかわりに次のサブフレーム期間のデジタルの映像信号を入力してもよい。

10

#### 【0182】

第3の手法は、発光素子の対向電極の電位を変化させることによって、非表示期間を設ける手法である。つまり、表示期間は、対向電極の電位を電源線の電位との間に所定の電位を有する様に設定する。一方、非表示期間では、対向電極の電位を電源線の電位とほぼ同じ電位に設定する。そして、非表示期間に全画素にデジタルの映像信号を入力する。つまり、そのときにアドレス期間を設ける。こうして、画素に入力されたデジタルの映像信号に関わらず、画素を非発光の状態とすることができる。

20

#### 【0183】

例えば、対向電極が全ての画素において電気的に接続されていた場合、表示期間Tsが始まるタイミング及び終わるタイミングは、全ての画素において同じである。所定の長さの表示期間Tsの後、発光素子106の対向電極の電位を再び電源線Wの電位とほぼ同じに変化させることによって、全ての画素を一斉に非発光の状態とすることができる。こうして、非表示期間TuSを設けることができる。非表示期間TuSのタイミングは、全ての画素において同じである。なお、多階調化がそれ程要求されない場合は(アドレス期間Taより短い表示期間Tsが必要ない場合)、全てのサブフレーム期間において、非表示期間TuSを設けない駆動方法であってもよい。この駆動方法を用いる場合は、消去トランジスタは必要ない。

30

#### 【0184】

また、保持容量303の代わりに、駆動トランジスタ302のゲート電極の寄生容量を積極的に利用することも可能である。同様に、電流源容量111を配置せず、電流源トランジスタ112やカレントトランジスタ1405のゲート電極の寄生容量を利用してよい。

#### 【0185】

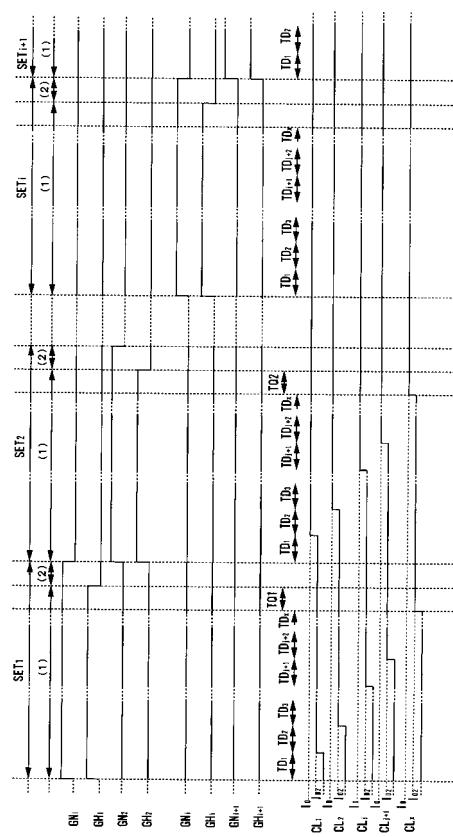

次に画素の設定動作について以下の2つの手法を説明する。

第1の手法について図16を用いて説明する。図16は、図7に示す各画素に配置された電流源回路102の設定動作(画素の設定動作)を示すタイミングチャートである。ここでは、表示装置の電源を入れた後の最初の画素の設定動作について説明する。

40

#### 【0186】

なお画素の設定動作を、図12等に示す基準電流出力回路405の設定動作と同期させて行う場合の例を挙げる。ここでは、基準電流出力回路405は、図13に示した構成を用い、図14に示したタイミングチャートを参考に、分割書き込み方式を用いて動作させる場合を例に挙げる。また簡単のため、分割書き込み方式の分割数が、2の場合の例を示す。説明のため、図14に示したタイミングチャートと同じ動作をする部分は、同じ符号を用いて表し説明は省略する。図16において、第*i*行の画素の設定動作を行う期間をSET*i*で示す。SET*i*において、第*i*行の1列目から×列目の画素の設定動作が行われる。第*i*行の1列目から×列目の画素の設定動作を、図16中、SET*i*の(1)及び(

50

2) の期間に分けて説明する。

#### 【0187】

始めに、SET 1 の期間(1)において、信号線 G N 1 及び信号線 G H 1 に入力された信号によって、図7に示す第1行の画素の電流入力トランジスタ 1403 及び電流保持トランジスタ 1404 が導通状態となる。このとき、基準電流出力回路 405 は、図14において期間 T D 1 ~ T D x に示した動作を順に行い、各電流線 CL1 ~ CLx に流れる電流が順に定められる。この際、電流  $I_{02}$  が、各電流線 CL1 ~ CLx を流れるよう定められるとしている。なおここでは、基準電流出力回路 405 は、分割書き込み方式を用いて設定動作が行われるとした。そのため、期間 T D 1 ~ T D x に示した動作を1回行ったのみでは、十分に設定動作が行われない。そのため、基準電流を  $I_0$  とすると、電流値は  $I_{02} < I_0$  である。

10

#### 【0188】

次に、各電流線 CL1 ~ CLx に電流  $I_{02}$  が流れるようになった後の、各画素の電流源回路 102 の動作について説明する。例えば、第1行第j列の画素の場合、期間 T D j が終了すると、電流線 CLj に電流  $I_{02}$  が流れるように設定される。こうして、第j列の画素のカレントトランジスタ 1405 に電流  $I_{02}$  が流れる。ここで、第1行の画素のカレントトランジスタ 1405 のゲート電極とドレイン端子とは、導通状態となった電流保持トランジスタ 1404 を介して接続されている。そのため、カレントトランジスタ 1405 は、ゲート・ソース間電圧(ゲート電圧)と、ソース・ドレイン間電圧が等しい状態、つまり飽和領域で動作し、ドレイン電流を流す。第1行 j 列の画素のカレントトランジスタ 1405 を流れるドレイン電流は、電流線 CLj を流れる電流  $I_{02}$  に定まる。こうして電流源容量 111 は、カレントトランジスタ 1405 が電流  $I_{02}$  を流す際のゲート電圧を保持する。

20

#### 【0189】

期間 T D 1 ~ T D x まで終了し、電流線 CL に流れる電流  $I_{02}$  に対応した電荷を電流源容量 721\_x が保持し終わると、期間(2)に入る。期間(2)において、信号線 G H 1 の信号が変化し、電流保持トランジスタ 1404 が非導通状態となる。これにより、第1行の画素の電流源容量 111 に、電荷が保持される。なお、図中 T Q 1 で示す期間は、電流線 CLx から第1行 x 列の画素の電流源回路 102 のカレントトランジスタ 1405 に電流  $I_{02}$  を入力し、電流源容量 111 に電荷を保持させる期間に相当する。図中に T Q 1 で示す期間が、カレントトランジスタ 1405 を流れる電流が定常状態となるために要する時間より短い場合、電流源容量 111 に十分に電荷が保持されない。しかし、ここでは簡単のため、T Q 1 が十分な長さに設定されているとする。

30

#### 【0190】

この様にして、第1行の各画素の設定動作が行われる。ここで、各画素の電流源回路 102 において、カレントトランジスタ 1405 及び電流源トランジスタ 112 のゲート電極の電位が等しい。カレントトランジスタ 1405 及び電流源トランジスタ 112 のソース端子の電位が等しい。また、カレントトランジスタ 1405 と電流源トランジスタ 112 の電流特性が等しいことが望まれる。簡単のため、ここでは、カレントトランジスタ 1405 と電流源トランジスタ 112 の電流特性が等しいとする。そのため、電流源回路 102 の端子 A と端子 B の間に電圧が印加されると、電流源トランジスタ 112 には、カレントトランジスタ 1405 を流れる電流  $I_{02}$  に応じた一定電流が流れる。

40

#### 【0191】

分割書き込み方式の基準電流出力回路 405 を用いる表示装置では、表示装置の電源を入れた後の初めの SET 1 における電流線 CL1 ~ CLx を流れる電流  $I_{02}$  は基準電流に満たない値である。そのため、この SET 1 期間における画素の設定動作は十分に行われない。つまり、表示装置の電源を入れた直後の第1行の画素の設定動作では、第1行の画素がそれぞれ有する電流源回路 102 の電流源容量 111 には、基準電流に対応する電圧(画素対応基準電圧)を保持することができない。

#### 【0192】

次に、SET 2 の期間(1)において、信号線 G N 2 及び信号線 G H 2 に入力された信号によって、第2行の画素の電流入力トランジスタ 1403 及び電流保持トランジスタ 1404 が導通状態となる。なお同時に信号線 G N 1 に入力される信号が変化し、第1行の画素の電流入力トランジスタ 1403 が非導通状態となる。こうして、第1行の画素のカレントトランジスタ 1405 及び電流源トランジスタ 112 のゲート電圧は保持されたまま、電流線 CL 1 とカレントトランジスタ 1405 の接続が切断される。

#### 【0193】

SET 2 の期間(1)において、基準電流出力回路 405 は、図 14 において期間 TD 1 ~ 期間 TD x に示した動作を順に行い、各電流線 CL 1 ~ CL x に流れる電流が順に定められる。この際、先の SET 1 期間の期間 TD 1 ~ TD x において行った動作によって、

10 基準電流出力回路 711 の電流源容量 721\_1 ~ 721\_x には、既にある程度の電荷が保持されている。SET 2 の期間 TD 1 ~ TD x の動作を行うと、表示装置の電源を入れた後、期間 TD 1 ~ TD x の動作を2回繰り返すことになる。

#### 【0194】

ここでは、分割書き込み方式の分割数を2と考えているので、SET 2 における期間 TD 1 ~ TD x が終了すると、基準電流出力回路 405 の電流源容量 721\_1 ~ 721\_x には、電流源トランジスタ 720\_1 ~ 720\_x が基準電流  $I_0$  を流すような電荷が保持される。こうして、各電流線 CL 1 ~ CL x を流れる電流が基準電流  $I_0$  に定められる。

20

#### 【0195】

こうして、表示装置の電源を入れた後の初めの SET 2 において、基準電流出力回路 405 より定められる電流線 CL 1 ~ CL x を流れる電流値が基準電流  $I_0$  に設定される。つまり、表示装置の電源を入れた後の初めの SET 2 において、基準電流出力回路 405 の設定動作が十分に行われる。

20

#### 【0196】

次に、各電流線 CL 1 ~ CL x に基準電流  $I_0$  が流れるようになった後の各画素の電流源回路の動作について説明する。例えば、第2行第 j 列の画素の場合、期間 TD j が終了すると、電流線 CL j に基準電流  $I_0$  が流れるように設定される。こうして、第 j 列の画素のカレントトランジスタ 1405 に基準電流  $I_0$  が流れる。第2行の画素のカレントトランジスタ 1405 のゲート電極とドレイン端子とは、導通状態となった電流保持トランジスタ 1404 を介して接続されている。そのため、カレントトランジスタ 1405 は、

30 ゲート・ソース間電圧(ゲート電圧)と、ソース・ドレイン間電圧が等しい状態、つまり飽和領域で動作してドレイン電流を流す。第2行 j 列の画素のカレントトランジスタ 1405 を流れるドレイン電流は、電流線 CL j を流れる基準電流  $I_0$  に定まる。こうして、電流源容

量 111 は、カレントトランジスタ 1405 が基準電流  $I_0$  を流す際のゲート電圧を保持する。

#### 【0197】

期間 TD 1 ~ TD x まで終了し、電流線 CL に流れる基準電流  $I_0$  に対応した電荷を電流源容量 721\_x が保持し終わると、期間(2)に入る。期間(2)において、信号線 G H 2 の信号が変化し、電流保持トランジスタ 1404 が非導通状態となる。これにより、第2行の画素の電流源容量 111 に電荷が保持される。なお、図中 T Q 2 で示す期間は、電流線 CL x から第2行 x 列の画素の電流源回路 102 のカレントトランジスタ 1405 に基準電流  $I_0$  を入力し、電流源容量 111 に電荷を保持させる期間に相当する。図中に T Q 2 で示す期間が、カレントトランジスタ 1405 を流れる電流が定常状態となるために要する時間より短い場合、電流源容量 111 に十分に電荷が保持されない。つまり、画素の設定動作が十分行われない。ここでは簡単のため、T Q 2 が十分な長さに設定されているとする。

40

#### 【0198】

この様にして、第2行の各画素の設定動作が行われる。各画素の電流源回路 102 にお

50

いて、カレントトランジスタ 1405 及び電流源トランジスタ 112 のゲート電極の電位が等しい。カレントトランジスタ 1405 及び電流源トランジスタ 112 のソース端子の電位が等しい。また、カレントトランジスタ 1405 と電流源トランジスタ 112 の電流特性が等しいことが望まれる。簡単のため、カレントトランジスタ 1405 と電流源トランジスタ 112 の電流特性が等しいとする。そのため、電流源回路 102 の端子 A と端子 B の間に電圧が印加されると、電流源トランジスタ 112 のソース・ドレイン間には、カレントトランジスタ 1405 を流れる基準電流  $I_0$  に応じた一定電流（画素基準電流）が流れる。

#### 【0199】

S E T 2 が終了すると、信号線 G N 2 に入力される信号が変化し、第 2 行の画素の電流入力トランジスタ 1403 が非導通状態となる。こうして、第 2 行の画素のカレントトランジスタ 1405 及び電流源トランジスタ 112 のゲート電圧は保持されたまま、電流線 C L 2 とカレントトランジスタ 1405 の接続が切断される。10

#### 【0200】

S E T 2 と同様の動作を全ての行に対して繰り返す。但し、基準電流出力回路 405 の設定動作は、S E T 2 においてすでに終了している。よって、S E T 3 以降の動作では、S E T i の期間 (1) の間継続的に電流線 C L 1 ~ C L x 全てにほぼ基準電流に等しい電流が流れている。一旦、基準電流出力回路 405 の設定動作が終了した後は、S E T i の期間 (1) が始まると直ぐに、第 i 行の全ての画素の電流源容量 111 において同時に、画素対応基準電圧を保持する動作が行われる。20

#### 【0201】

このように、S E T 2 が終了した時点で、基準電流出力回路 405 が有する各電流源容量 721\_1 ~ 721\_x には、各電流線 C L 1 ~ C L x に基準電流を流すための電荷が保持されている。そのため、S E T 3 以後の期間 T D 1 ~ T D x においては、電流源容量 721\_1 ~ 721\_x の電荷が放電した分を保持し直す動作が行われる。S E T 2 以後は、各電流線 C L 1 ~ C L x に流れる電流は、ほぼ基準電流に定まり、画素の設定動作は十分に行われる（完了する）。

#### 【0202】

S E T 1 ~ S E T y の動作を行うと、画素設定の第 1 フレーム期間が終了する。なお、信号線 G N 1 ~ G N y 及び信号線 G H 1 ~ G H y を全て 1 回ずつ選択し、全ての画素の設定動作を 1 通り行う期間を、画素設定の 1 フレーム期間と呼ぶ。画素設定の第 1 フレーム期間が終了した後、画素設定の第 2 フレーム期間が始まる。画素設定の第 2 フレーム期間においても、画素設定の第 1 フレーム期間と同様の動作を繰り返す。画素設定の第 1 フレーム期間では、第 1 行の画素の設定動作は十分に行われなかった。しかし、画素設定の第 2 フレーム期間では、基準電流出力回路 405 の設定動作が完了している。そのため、画素設定の第 2 フレーム期間において S E T 1 の動作を行うことにより、第 1 行の画素の設定動作も十分に行うことができる。このようにして、全ての画素の設定動作が十分に行われる（完了する）。

#### 【0203】

なお、図 16 のタイミングチャートにおいては、基準電流出力回路 405 の分割数は 2 と設定したが、これに限定されず、任意の数とすることができます。仮に分割数が表示装置の有する画素行の数より大きい場合、表示装置の電源を入れた後 1 回目（画素設定の第 1 フレーム期間）の画素の設定動作は、全ての画素行において十分に行われない。しかし、画素の設定動作を複数回繰り返すことによって、十分に画素の設定動作を行うことができる。また、画素設定の第 1 のフレーム期間では、どの画素の設定動作も十分に行われず、画素設定の第 2 のフレーム期間以降において、全ての画素の設定動作が完了するようにしても良い。

#### 【0204】

例えば、各設定期間 S E T i の期間 (1) の長さを短く設定し、S E T 1 ~ S E T y の動作を複数回行うことによって、徐々に画素の設定動作を行う手法を用いることができる4050

。なお、表示装置の電源を入れた直後の基準電流出力回路 405 の設定動作及び画素の設定動作は、同時に始める例を示したが、基準電流出力回路 405 の設定動作を十分に行つた後から画素の設定動作を行っても良い。

#### 【0205】

一旦、画素の設定動作を完了した後は、漏れ電流等によって電流源容量 111 に保持された電荷が減少した分を充電し直すために、画素の設定動作を行う。そのタイミングは、電流源容量 111 の放電の速さ等によって様々な形態が考えられる。なお、一旦、画素の設定動作を完了した後に再び行う画素の設定動作では、電流源容量 111 に保持された電荷が放電した分のみ充電すればよいため、始めの画素の設定動作に対して、それ以降の画素の設定動作は、各画素に基準電流を入力した後、定常状態となるまでの時間が短くてすむ。よって、1回目の画素の設定動作に対して、それ以降の画素の設定動作は、信号線 G N、信号線 G H に信号を入力する駆動回路及び基準電流出力回路 405 の駆動周波数を高く設定することも可能である。10

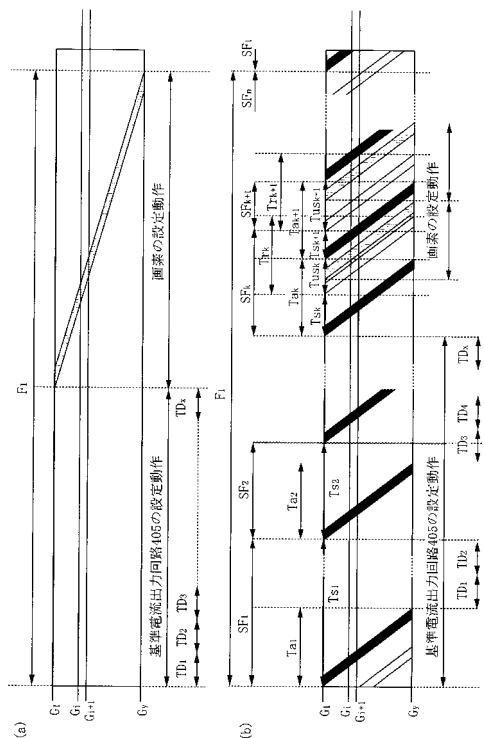

#### 【0206】

次いで、画素の設定動作の第 2 の手法について、図 26 を用いて説明する。図 26 は、図 7 に示す各画素に配置された電流源回路 102 の設定動作（画素の設定動作）を示すタイミングチャートである。図 26 (a) には、画素の設定動作と、図 12 等に示す基準電流出力回路 405 の設定動作とを、1 フレーム期間の前半と後半で行う場合の例を挙げる。ここでは、基準電流出力回路 405 は、図 13 に示した構成を用い、図 14 に示したタイミングチャートを参考に動作させる場合を例に挙げる。なお、図 14 に示したタイミングチャートと同じ動作をする部分は、同じ符号を用いて表し説明は省略する。20

#### 【0207】

まず、1 フレーム期間の前半において基準電流出力回路 405 は、図 14 において期間 T D 1 ~ T D x に示した動作を順に行い、各電流線 CL1 ~ CLx に流れる電流が順に定められる。次に、1 フレーム期間の後半における、各画素の電流源回路 102 の動作について、第 1 行の画素の場合を説明する。基準電流出力回路 405 の設定動作により、全ての電流線 CL は基準電流が流れるように設定されている。ここで、第 1 行の画素のカレントトランジスタ 1405 のゲート電極とドレイン端子とは、導通状態となった電流保持トランジスタ 1404 を介して接続されている。そのため、カレントトランジスタ 1405 は、ゲート・ソース間電圧（ゲート電圧）と、ソース・ドレイン間電圧が等しい状態（飽和領域）で動作し、ドレイン電流を流す。第 1 行 j 列の画素のカレントトランジスタ 1405 を流れるドレイン電流は、電流線 CLj を流れる基準電流に定まる。こうして電流源容量 111 は、カレントトランジスタ 1405 が基準電流を流す際のゲート電圧を保持する。次に、信号線 G H 1 の信号が変化し、電流保持トランジスタ 1404 が非導通状態となる。これにより、第 1 行の画素の電流源容量 111 に電荷が保持される。30

#### 【0208】

この様にして、第 1 行の各画素の設定動作が行われる。各画素の電流源回路 102 において、カレントトランジスタ 1405 及び電流源トランジスタ 112 のゲート電極の電位が等しく、カレントトランジスタ 1405 及び電流源トランジスタ 112 のソース端子の電位が等しくなっている。また、カレントトランジスタ 1405 と電流源トランジスタ 112 の電流特性が等しいことが望まれる。簡単のため、カレントトランジスタ 1405 と電流源トランジスタ 112 の電流特性が等しいと仮定する。そのため、電流源回路 102 の端子 A と端子 B の間に電圧が印加されると、電流源トランジスタ 112 には、カレントトランジスタ 1405 を流れた基準電流に応じた一定電流が流れる。40

#### 【0209】

次に、信号線 G N 2 及び信号線 G H 2 に入力された信号によって、第 2 行の画素の電流入力トランジスタ 1403 及び電流保持トランジスタ 1404 が導通状態となる。なお同時に信号線 G N 1 に入力される信号が変化し、第 1 行の画素の電流入力トランジスタ 1403 が非導通状態となる。こうして、第 1 行の画素のカレントトランジスタ 1405 及び電流源トランジスタ 112 のゲート電圧は保持されたまま、電流線 CL1 とカレントトランジスタ 1403 が導通する。50

ンジスタ 1405 の接続が切斷される。第 2 行の画素においても、第 1 行のときと同様、画素の設定動作が行われる。その次に第 3 行の画素、第 4 行の画素と順次同様の動作を繰り返していく。全ての行で、画素の設定動作が終了すると、1 フレーム期間が終了する。次のフレーム期間に入ると、同様に前半に基準電流出力回路 405 の設定動作が行われ、後半に画素の設定動作が行われる。一旦画素の設定動作を完了した後は、漏れ電流等によって電流源容量 111 に保持された電荷が減少した分を充電し直すために、画素の設定動作を行う。そのタイミングは、電流源容量 111 の放電の速さ等によって様々な態様が考えられる。

#### 【 0210 】

同様に、一旦、基準電流出力回路 405 の設定動作が行われた後は、容量 721 に保持された電荷が減少した分を充電しなおすために設定動作を行う。タイミングは様々であり、画素及び基準電流出力回路 405 の設定動作は、画像の表示動作とは全く無関係に動作させることができる。図 17 におけるアドレス期間  $T_a$  や表示期間  $T_s$ 、非表示期間  $T_u$  とは全く無関係に動作させることができる。その理由は、画素及び基準電流出力回路 405 の設定動作と画像の表示動作とは、お互いの動作に影響を与えないためである。従つて図 26 (a) のかわりに、図 26 (b) のようにして設定動作を行ってもよい。図 26 (b) では、信号線駆動回路が動作していない期間に基準電流出力回路 405 の設定動作を行い、残りの期間に画素の設定動作を行っている。このように、完全に任意の回数とタイミングで設定動作を行えばよい。画素の設定動作も 1 行づつ順に行う必要はなく、基準電流出力回路 405 の設定動作も 1 列づつ順に行う必要はない。

10

20

#### 【 0211 】

なお、電流保持トランジスタ 1404 のソース端子及びドレイン端子のカレントトランジスタ 1405 及び電流源トランジスタ 112 のゲート電極と接続されていない側が電流線  $C_L$  に直接接続されている構成では、全ての画素の電流入力トランジスタ 1403 が非導通状態となった際の電流線  $C_L$  には、一定電位が与えられる構成とする。この一定電位を、表示装置が有する複数の画素において、それらの電流源容量 111 に画素対応基準電圧を保持した際のカレントトランジスタ 1405 のゲート電位の平均程度に設定する。こうして、電流保持トランジスタ 1404 のソース・ドレイン端子間の電圧を小さくし、電流保持トランジスタ 1404 の漏れ電流による、電流源容量 111 に蓄積された電荷の放電を抑制することができる。電流線  $C_L$  に、一定電位を与えるか又は基準電流を流すかの切り替えは、基準電流出力回路 405 において行う構成としてもよい。

30

#### 【 0212 】

また、カレントトランジスタ 1405 のゲート長とゲート幅の比に対して、電流源トランジスタ 112 のゲート長とゲート幅の比を変化させることによって、基準電流の値に対して画素基準電流の値を変化させることも可能である。例えば、画素基準電流に対して基準電流を大きく設定すれば、画素の設定動作において電流源容量 111 が画素対応基準電圧を保持するまでに必要な時間を短縮することができ、ノイズの影響を低減することができる。

#### 【 0213 】

電流線  $C_L 1 \sim C_L x$  に対応する各画素の発光素子の特性に合わせて、複数の異なる電流値の基準電流を定めることができる。例えば、赤色発光、緑色発光、及び青色発光の発光色の異なる発光素子が設けられた各画素のそれぞれの電流線  $C_L$  に流れる基準電流の電流値を変えて設定することもできる。これにより、3 色の発光素子の発光輝度のバランスをとることができ。3 色の発光輝度のバランスの取り方は、点灯期間の長さを変えることによりおこなってもよいし、各色に対応した画素に入力する基準電流の電流値を変えることと組み合わせてもよい。或いはカレントトランジスタ 1405 と電流源トランジスタ 112 とで、ゲート長とゲート幅の比を、色ごとに変えてよい。

40

#### 【 0214 】

次いで、画像表示動作と画素の設定動作の関連について説明する。画像表示動作と画素の設定動作とを開始するタイミングは、様々な態様が考えられる。

50

**【 0 2 1 5 】**

1つは、表示装置の電源を入れた後の最初の画像表示動作を、一旦、全ての画素の設定動作が十分に終了した後に行う手法である。この場合、最初の画像表示動作から、映像信号によって発光状態が選択された画素の発光素子は、所定の輝度で発光する。

**【 0 2 1 6 】**

他の手法は、表示装置の電源を入れた後の最初の画像表示動作を、画素の設定動作を行いながら、同時に進行する手法である。この場合、画素の設定動作が完了するまでの期間に行われた画像表示動作では、映像信号によって発光状態が選択された画素の発光素子の発光輝度は、所定の輝度に達しない。そのため、正確な階調表示は、全ての画素の設定動作が十分に行われた後から、始まる。

10

**【 0 2 1 7 】**

図7で示した画素部の構成において、信号線G N、信号線G H、走査線G、消去用信号線R Gなどは、駆動のタイミングなどを考慮して、共有することができる。例えば、信号線G H iと信号線G N iとを共有することができる。なお、電流保持トランジスタ1404を非導通状態とするタイミングと電流入力トランジスタ1403を非導通状態とするタイミングが全く同じであり、画素の設定動作上問題ない。

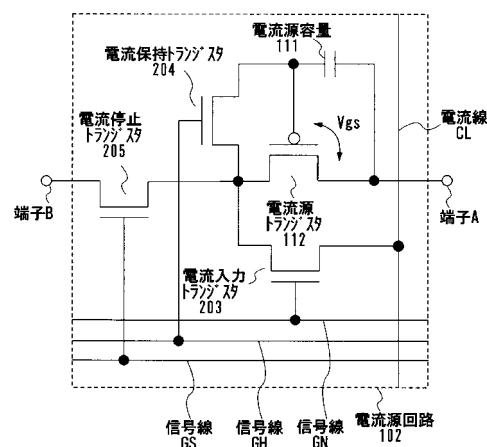

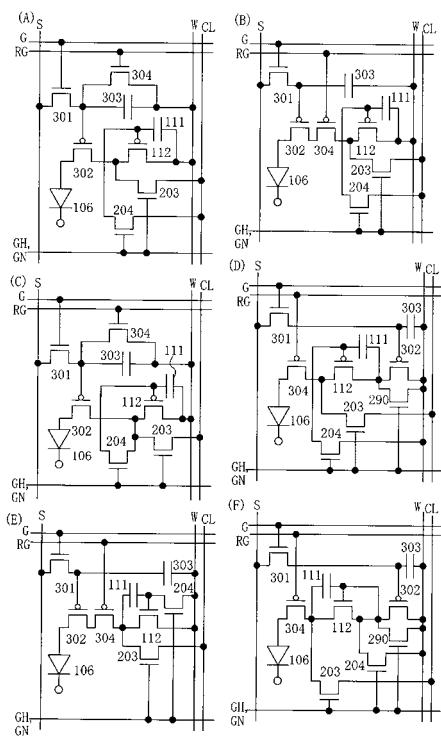

**【 0 2 1 8 】****(実施の形態3)**

本実施の形態では、同一トランジスタ方式の電流源回路の構成例を図18に示す。なお、ここでは実施の形態1と異なる部分について主に説明し、重複する部分は説明を省略する。従って、図18において図1と同じ部分は同じ符号を用いて示す。

20

**【 0 2 1 9 】**

図18において、電流源回路102は、電流源容量111、電流源トランジスタ112、電流入力トランジスタ203、電流保持トランジスタ204、電流停止トランジスタ205、電流線C L、信号線G N、信号線G H、信号線G Sとによって構成される。電流源トランジスタ112をpチャネル型とした例を示す。なお、電流源トランジスタ112をnチャネル型とする場合も、図1(C)に示した構造に従って、容易に応用することができる。

**【 0 2 2 0 】**

また、図18において電流入力トランジスタ203、電流保持トランジスタ204、電流停止トランジスタ205はnチャネル型とするが、単なるスイッチとして動作するためpチャネル型でもかまわない。但し、図18において、電流保持トランジスタ204が電流源トランジスタ112のゲートとドレイン間に接続されている場合は、電流保持トランジスタ204はpチャネル型が望ましい。その理由は、nチャネル型とした場合端子Bの電位が非常に低くなる場合があり得、その時電流保持トランジスタ204のソース電位も低くなる。その結果電流保持トランジスタ204が非導通状態となりにくくなる可能性がある。これに対し電流保持トランジスタ204をpチャネル型にしておけばその心配はない。

30

**【 0 2 2 1 】**

電流源トランジスタ112のゲート電極と電流源容量111の一方の電極は接続されている。また、電流源容量111の他方の電極は、電流源トランジスタ112のソース端子と接続されている。電流源トランジスタ112のソース端子が電流源回路102の端子Aに接続されている。電流源トランジスタ112のゲート電極とドレイン端子は、電流保持トランジスタ204のソース・ドレイン端子間に介して、接続されている。電流保持トランジスタ204のゲート電極は、信号線G Hに接続されている。電流源トランジスタ112のドレイン端子と電流線C Lは、電流入力トランジスタ203のソース・ドレイン端子間に介して接続されている。電流入力トランジスタ203のゲート電極は、信号線G Nに接続されている。また、電流源トランジスタ112のドレイン端子は、電流停止トランジスタ205のソース・ドレイン端子間に介して端子Bに接続されている。電流停止トランジスタ205のゲート電極は、信号線G Sに接続されている。

40

50

## 【0222】

また、上記構成において、電流源トランジスタ112のゲート電極は、電流入力トランジスタ203のソース・ドレイン端子間を介さず、電流線CLに接続されても良い。つまり、電流保持トランジスタ204のソース端子及びドレイン端子の、電流源トランジスタ112のゲート電極と接続されていない側が、電流線CLに直接接続されている構成でも良い。その場合、電流線CLの電位を調整することにより、電流保持トランジスタ204のソース・ドレイン間電圧を小さくすることができる。その結果、電流保持トランジスタ204が非導通状態のときに、電流保持トランジスタ204のもれ電流を小さくすることができる。なお、これに限定されず、電流保持トランジスタ204は、導通状態となつた際に、電流源トランジスタ112のゲート電極の電位を電流線CLの電位と等しくするように接続されれば良い。

## 【0223】

なお、電流保持トランジスタ204のソース端子及びドレイン端子の、電流源トランジスタ112のゲート電極と接続されていない側が、電流線CLに直接接続されている構成では、全ての画素の電流入力トランジスタ203が非導通状態となつた際の電流線CLには、一定電位が与えられる構成とする。この一定電位を、表示装置が有する複数の画素において、それらの電流源容量111に画素対応基準電圧を保持した際の、電流源トランジスタ112のゲート電位の平均程度に設定する。こうして、電流保持トランジスタ204のソース・ドレイン端子間の電圧を小さくし、電流保持トランジスタ204の漏れ電流による電流源容量111に蓄積された電荷の放電を抑制することができる。

## 【0224】

電流線CLに、一定電位を与えるか又は基準電流を流すかの切り替えは、基準電流出力回路405において行う構成としてもよい。なお、電流保持トランジスタ204を電流源トランジスタ112のゲートと電流線CLの間で接続する場合は、電流保持トランジスタ204の極性は何でもよい。電流保持トランジスタ204をnチャネル型にしても電流線CLの電位が低くなり過ぎるようなことはないので、電流保持トランジスタ204が非導通状態となりにくくなることもない。

スイッチ部の構成としては、実施の形態2において説明したものと同様であり、様々な構成を用いることができる。一例としては、図3に示したものと同様の構成とし説明は省略する。

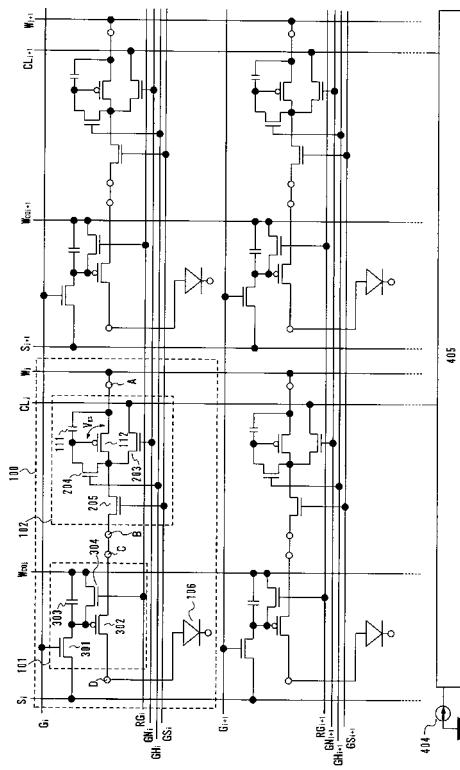

## 【0225】

図18に示した構成の電流源回路102と、図3に示した構成のスイッチ部101を有する画素100が、マトリクス状に配置した画素領域の一部の回路図を、図19に示す。図19において、第i行j列、第(i+1)行j列、第i行(j+1)列、第(i+1)行(j+1)列の4画素のみを代表的に示す。図18及び図3と同じ部分は、同じ符号を用いて示し、説明は省略する。なお、第i行、第(i+1)行それぞれの画素行に対応する、走査線をGi、Gi+1、消去用信号線をRGi、RGi+1、信号線GNをGNi、GNi+1、信号線GHをGHi、GHi+1、信号線GSをGSi、GSi+1と表記する。また、第j列、第(j+1)列それぞれの画素列に対応する、映像信号入線SをSj、Sj+1、電源線WをWj、Wj+1、電流線CLをCLj、CLj+1、配線WcoをWcoj、Wcoj+1と表記する。電流線CLj、CLj+1には、画素領域外部より基準電流が入力される。

## 【0226】

発光素子106の画素電極は端子Dに接続され、対向電極は対向電位が与えられている。図19では、発光素子の画素電極を陽極とし、対向電極を陰極とした構成について示した。つまり、電流源回路の端子Aが電源線Wに接続され、端子Bがスイッチ部101の端子Cに接続された構成を示した。しかし、発光素子106の画素電極を陰極とし、対向電極を陽極とした構成の表示装置にも、本実施の形態3の構成を容易に応用することができる。

## 【0227】

10

20

30

40

50

図19では電流源トランジスタ112はpチャネル型とした。

また図19において、駆動トランジスタ302は、単なるスイッチとして機能するのとnチャネル型でもpチャネル型でもどちらでも良い。ただし、駆動トランジスタ302は、そのソース端子の電位が固定された状態で動作するのが好ましい。そのため、図19に示すような発光素子106の画素電極を陽極とし、対向電極を陰極とした構成では、駆動トランジスタ302はpチャネル型のほうが好ましい。なお、第19図において、各画素の配線WCOと電源線Wとは、同じ電位に保たれていてもよいため、共用することができる。また、異なる画素間の配線WCO同士、電源線W同士、配線WCOと電源線Wも共用することができる。

#### 【0228】

10

図19で示した画素部の構成において、信号線GN、信号線GH、信号線GS、走査線G、消去用信号線RGなどは、駆動のタイミングなどを考慮して、共有することができる。例えば、信号線GH<sub>i</sub>と信号線GN<sub>i</sub>とを共有することができる。この場合、電流入力トランジスタ203を非導通状態となるタイミングと電流保持トランジスタ204を非導通状態とするタイミングが全く同じであり、画素の設定動作上、問題ない。別の例としては、信号線GS<sub>i</sub>と信号線GN<sub>i</sub>とを共有することができる。この場合、電流入力トランジスタ203の極性と異なる極性の電流停止トランジスタ205を用いる。こうして、電流入力トランジスタ203のゲート電極と電流停止トランジスタ205のゲート電極に同じ信号を入力した際に、一方のトランジスタを導通状態とし、他方のトランジスタを非導通状態とすることができます。更に、消去用信号線RGと信号線GSも共有することができる。

#### 【0229】

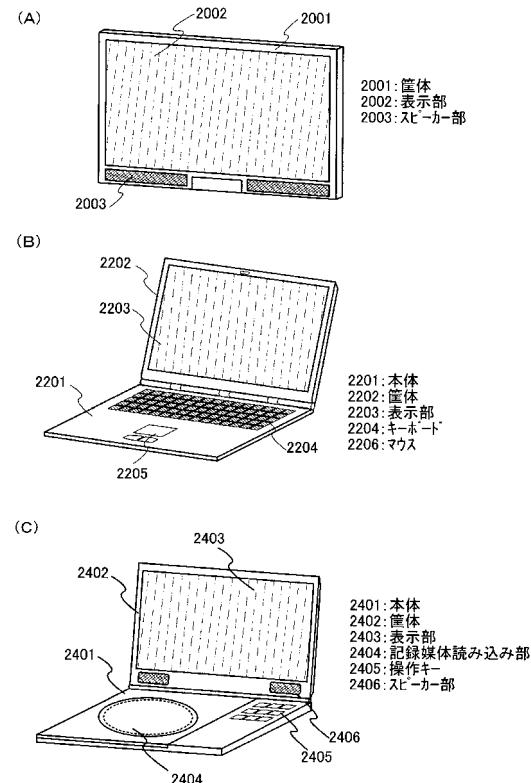

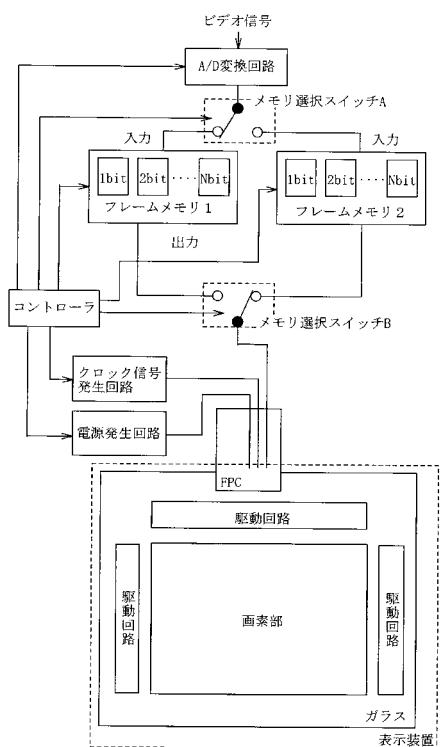

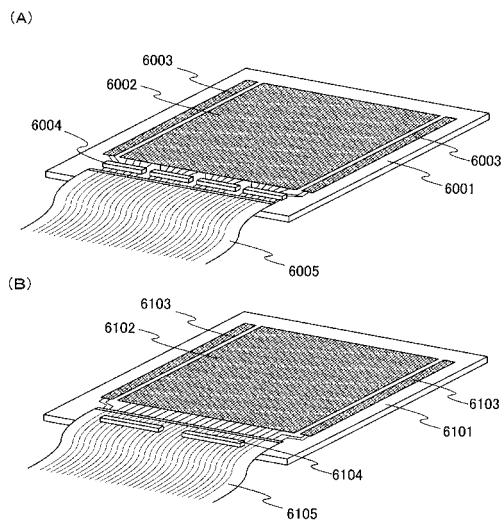

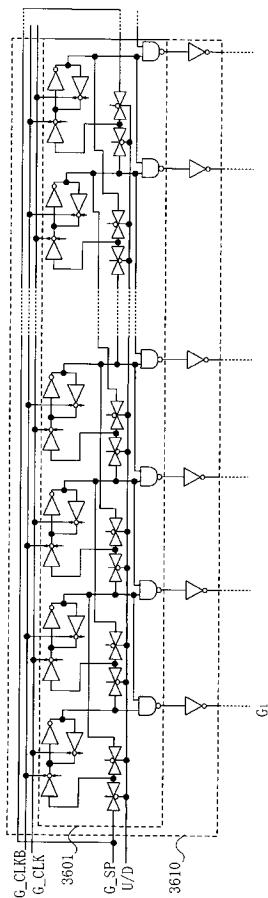

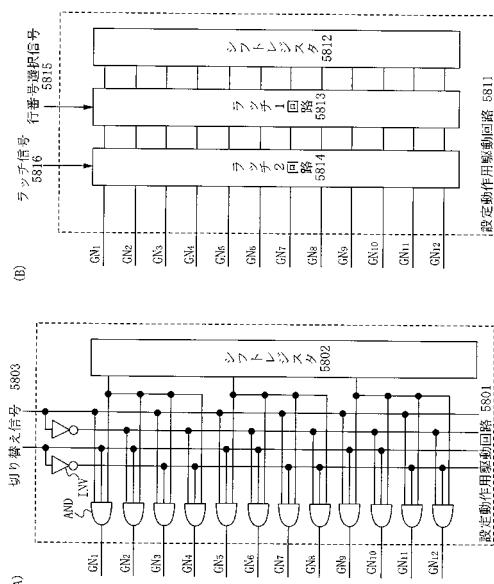

20