(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6866792号

(P6866792)

(45) 発行日 令和3年4月28日(2021.4.28)

(24) 登録日 令和3年4月12日(2021.4.12)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 653A |

| HO1L 29/423 | (2006.01) | HO1L 29/78 | 652K |

| HO1L 29/49  | (2006.01) | HO1L 29/78 | 652C |

| HO1L 29/417 | (2006.01) | HO1L 29/78 | 652M |

| HO1L 29/06  | (2006.01) | HO1L 29/78 | 652N |

請求項の数 7 (全 18 頁) 最終頁に続く

(21) 出願番号

特願2017-141943 (P2017-141943)

(22) 出願日

平成29年7月21日(2017.7.21)

(65) 公開番号

特開2019-21871 (P2019-21871A)

(43) 公開日

平成31年2月7日(2019.2.7)

審査請求日

令和1年9月16日(2019.9.16)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 110001128

特許業務法人ゆうあい特許事務所

(72) 発明者 萩野 勇志

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

(72) 発明者 合田 健太

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

審査官 恩田 和彦

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

トレンチゲート構造を有する半導体装置であって、

第1導電型のドリフト層(12)と、

前記ドリフト層上に形成された第2導電型のチャネル層(13)と、

前記チャネル層の表層部に形成された第1導電型の第1不純物領域(15)と、

前記ドリフト層を挟んで前記チャネル層と反対側に形成され、前記ドリフト層よりも高不純物濃度とされた第1導電型または第2導電型の第2不純物領域(11)と、を有する半導体基板(10)と、

前記第1不純物領域および前記チャネル層を貫通して前記ドリフト層に達し、所定方向を長手方向とするトレンチ(16)内にゲート絶縁膜(17)を介して所定のゲート電圧が印加されるゲート電極(18)が配置された前記トレンチゲート構造と、

前記半導体基板上に形成され、前記ゲート電極と電気的に接続されるゲートライナー(19)と、を備え、

前記ゲートライナーは、前記半導体基板の面方向に対する法線方向から視たとき、前記トレンチの長手方向と交差する方向に延設され、かつ前記トレンチと交差する状態で形成されており、

前記チャネル層は、前記ゲートライナーの下方に位置する領域と異なる領域に形成され、

前記ドリフト層上であって、前記ゲートライナーの下方に位置する領域には、前記チャ

10

20

ネル層と繋がる第2導電型のリサーフ層(14)が形成されており、

前記トレンチ内には、前記ゲート絶縁膜を介し、前記トレンチの底部側に所定の電位に維持されるシールド電極(26)が配置され、前記トレンチの開口部側に前記ゲート電極が配置されており、

前記ゲート電極が配置される領域をセル領域(1)とし、前記セル領域を囲む領域を外周領域(2)とすると、

前記トレンチは、前記長手方向の端部が前記外周領域まで延設され、

前記シールド電極は、前記トレンチの前記外周領域に位置する部分にて前記トレンチの開口部まで引き出され、

前記半導体基板上には、前記トレンチの開口部にて前記シールド電極と電気的に接続されるシールドライナー(27)が形成されており、

前記ドリフト層上であって、前記シールドライナーの下方に位置する領域には、第2導電型の外周リサーフ層(28)が形成され、

前記外周領域には、前記外周リサーフ層を含むガードリング(30)が構成されており

、

前記リサーフ層は、前記チャネル層よりも高不純物濃度とされている半導体装置。

【請求項2】

前記リサーフ層は、前記チャネル層よりも深くまで形成されている請求項1に記載の半導体装置。

【請求項3】

トレンチゲート構造を有する半導体装置であって、

第1導電型のドリフト層(12)と、

前記ドリフト層上に形成された第2導電型のチャネル層(13)と、

前記チャネル層の表層部に形成された第1導電型の第1不純物領域(15)と、

前記ドリフト層を挟んで前記チャネル層と反対側に形成され、前記ドリフト層よりも高不純物濃度とされた第1導電型または第2導電型の第2不純物領域(11)と、を有する半導体基板(10)と、

前記第1不純物領域および前記チャネル層を貫通して前記ドリフト層に達し、所定方向を長手方向とするトレンチ(16)内にゲート絶縁膜(17)を介して所定のゲート電圧が印加されるゲート電極(18)が配置された前記トレンチゲート構造と、

前記半導体基板上に形成され、前記ゲート電極と電気的に接続されるゲートライナー(19)と、を備え、

前記ゲートライナーは、前記半導体基板の面方向に対する法線方向から視たとき、前記トレンチの長手方向と交差する方向に延設され、かつ前記トレンチと交差する状態で形成されており、

前記チャネル層は、前記ゲートライナーの下方に位置する領域と異なる領域に形成され、

前記ドリフト層上であって、前記ゲートライナーの下方に位置する領域には、前記チャネル層と繋がる第2導電型のリサーフ層(14)が形成されており、

前記トレンチ内には、前記ゲート絶縁膜を介し、前記トレンチの底部側に所定の電位に維持されるシールド電極(26)が配置され、前記トレンチの開口部側に前記ゲート電極が配置されており、

前記ゲート電極が配置される領域をセル領域(1)とし、前記セル領域を囲む領域を外周領域(2)とすると、

前記トレンチは、前記長手方向の端部が前記外周領域まで延設され、

前記シールド電極は、前記トレンチの前記外周領域に位置する部分にて前記トレンチの開口部まで引き出され、

前記半導体基板上には、前記トレンチの開口部にて前記シールド電極と電気的に接続されるシールドライナー(27)が形成されており、

前記ドリフト層上であって、前記シールドライナーの下方に位置する領域には、第2導

10

20

30

40

50

電型の外周リサーフ層（28）が形成され、

前記外周領域には、前記外周リサーフ層を含むガードリング（30）が構成されており、

前記リサーフ層は、前記チャネル層よりも深くまで形成されている半導体装置。

【請求項4】

前記ゲートライナーは、前記半導体基板の面方向に対する法線方向から視たとき、前記リサーフ層内に位置している請求項1ないし3のいずれか1つに記載の半導体装置。

【請求項5】

トレンチゲート構造を有する半導体装置の製造方法であって、

第1導電型のドリフト層（12）を有する半導体基板（10）を用意することと、

10

前記半導体基板に、所定方向を長手方向とするトレンチ（16）を形成することと、

前記トレンチ内にゲート絶縁膜（17）を介して所定のゲート電圧が印加されるゲート電極（18）を形成することで前記トレンチゲート構造を形成することと、

前記半導体基板上に前記ゲート電極と電気的に接続されるゲートライナー（19）を形成することと、

前記ゲートライナーを形成した後、不純物をイオン注入して熱処理することにより、前記ドリフト層上に第2導電型のチャネル層（13）を形成することと共に、前記チャネル層の表層部に第1導電型の第1不純物領域（15）を形成することと、を行い、

前記ゲートライナーを形成することでは、前記半導体基板の面方向に対する法線方向から視たとき、前記トレンチの長手方向と交差する方向に延設され、かつ前記トレンチと交差するように前記ゲートライナーを形成し、

20

前記トレンチを形成することの前に、前記ゲートライナーの下方となる領域に、第2導電型のリサーフ層（14）を形成することを行い、

前記チャネル層を形成することでは、前記リサーフ層と繋がる前記チャネル層を形成することを行う半導体装置の製造方法。

【請求項6】

前記半導体基板を用意することでは、前記ゲート電極が配置されるセル領域（1）と、前記セル領域を囲む外周領域（2）と、を有する前記半導体基板を用意し、

前記トレンチを形成することでは、前記セル領域から前記外周領域まで延設された前記トレンチを形成し、

30

前記トレンチゲート構造を形成することでは、前記トレンチの底部側に所定の電位に維持されるシールド電極（26）を形成することと、前記トレンチの開口部側に前記ゲート電極を形成することと、を行い、

前記シールド電極を形成することでは、前記トレンチの前記外周領域に位置する部分にて前記トレンチの開口部まで引き出された前記シールド電極を形成し、

前記外周領域にて前記シールド電極と電気的に接続されるシールドライナー（27）を形成することと、

前記トレンチを形成することの前に、前記シールドライナーの下方となる領域を含み、前記セル領域を囲むガードリング（30）の少なくとも一部を構成する第2導電型の外周リサーフ層（28）を形成することと、を行う請求項5に記載の半導体装置の製造方法。

40

【請求項7】

前記シールドライナーを形成することでは、端部を有する前記シールドライナーを形成し、

前記チャネル層および前記第1不純物領域を形成することでは、前記イオン注入および前記熱処理を行うことにより、前記外周リサーフ層と連結され、前記外周リサーフ層と共に前記ガードリングを構成する第2導電型の第3不純物領域（29）を形成する請求項6に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

50

本発明は、トレンチゲート構造を有する半導体装置およびその製造方法に関するものである。

【背景技術】

【0002】

従来より、トレンチゲート構造を有するMOSFET(すなわち、Metal Oxide Semiconductor Field Effect Transistor)素子が形成された半導体装置が提案されている(例えば、特許文献1参照)。具体的には、この半導体装置は、N<sup>-</sup>型のドリフト層上にP型のチャネル層が形成され、チャネル層の表層部にN<sup>+</sup>型のソース層が形成された半導体基板を用いて構成されている。半導体基板には、ソース層およびチャネル層を貫通するように、一面側から複数のトレンチが形成されている。そして、各トレンチは、壁面に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極によって埋め込まれている。また、半導体基板の一面上には、トレンチが形成されている部分と異なる部分に、ゲート電極と電気的に接続されるゲートライナーが形成されている。言い換えると、半導体基板の一面上には、トレンチと交差しないようにゲートライナーが形成されている。

10

【0003】

さらに、半導体基板の一面上には、ソース層およびチャネル層と電気的に接続される第1電極が配置されている。また、半導体基板の一面と反対側の他面には、ドレイン層と電気的に接続される第2電極が配置されている。

【0004】

このような半導体装置は、次のように製造される。すなわち、まず、半導体基板にトレンチを形成し、熱酸化等してトレンチの壁面にゲート絶縁膜を形成する。次に、トレンチが埋め込まれるように、CVD(すなわち、Chemical Vapor Deposition)法等によってPoly-Siを成膜しゲート電極を形成する。続いて、半導体基板上に形成されたPoly-Siをパターニングし、ゲートライナーを形成する。そして、P型不純物やN型不純物をイオン注入して熱処理することにより、チャネル層およびソース層を形成する。その後は、第1電極および第2電極等を適宜形成することにより、上記半導体装置が製造される。

20

【先行技術文献】

【特許文献】

【0005】

30

【特許文献1】特開2017-45827号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、近年では、半導体装置の小型化を図ることが望まれている。このため、本発明者らは、ゲートライナーをトレンチと交差するように形成することにより、半導体装置の小型化を図ることについて検討した。しかしながら、ゲートライナーをトレンチと交差させた半導体装置を上記製造方法で製造すると、ゲートライナーを形成した後に不純物をイオン注入等してチャネル層等を形成するため、ゲートライナーがマスクとなって当該ゲートライナーの下方の領域にチャネル層が形成されない。つまり、ゲートライナーの下方では、ドリフト層が直接半導体基板の一面に達する構成となってしまう。このため、上記のような製造方法によって半導体装置を製造すると、ゲートライナーの下方の領域で高電界が集中し易くなり、リーク電流が発生し易くなってしまう。

40

【0007】

本発明は上記点に鑑み、半導体装置の小型化を図りつつ、リーク電流を発生し難くできる半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するための請求項1および3では、トレンチゲート構造を有する半導体装置であって、第1導電型のドリフト層(12)と、ドリフト層上に形成された第2導電

50

型のチャネル層（13）と、チャネル層の表層部に形成された第1導電型の第1不純物領域（15）と、ドリフト層を挟んでチャネル層と反対側に形成され、ドリフト層よりも高不純物濃度とされた第1導電型または第2導電型の第2不純物領域（11）と、を有する半導体基板（10）と、第1不純物領域およびチャネル層を貫通してドリフト層に達し、所定方向を長手方向とするトレンチ（16）内にゲート絶縁膜（17）を介して所定のゲート電圧が印加されるゲート電極（18）が配置されたトレンチゲート構造と、半導体基板上に形成され、ゲート電極と電気的に接続されるゲートライナー（19）と、を備え、ゲートライナーは、半導体基板の面方向に対する法線方向から視たとき、トレンチの長手方向と交差する方向に延設され、かつトレンチと交差する状態で形成されており、チャネル層は、ゲートライナーの下方に位置する領域と異なる領域に形成され、ドリフト層上であって、ゲートライナーの下方に位置する領域には、チャネル層と繋がる第1導電型のリサーフ層（14）が形成されており、トレンチ内には、ゲート絶縁膜を介し、トレンチの底部側に所定の電位に維持されるシールド電極（26）が配置され、トレンチの開口部側にゲート電極が配置されており、ゲート電極が配置される領域をセル領域（1）とし、セル領域を囲む領域を外周領域（2）とすると、トレンチは、長手方向の端部が外周領域まで延設され、シールド電極は、トレンチの外周領域に位置する部分にてトレンチの開口部まで引き出され、半導体基板上には、トレンチの開口部にてシールド電極と電気的に接続されるシールドライナー（27）が形成されており、ドリフト層上であって、シールドライナーの下方に位置する領域には、第2導電型の外周リサーフ層（28）が形成され、外周領域には、外周リサーフ層を含むガードリング（30）が構成されている。

10

そして、請求項1では、リサーフ層は、チャネル層よりも高不純物濃度とされている。

請求項3では、リサーフ層は、チャネル層よりも深くまで形成されている。

#### 【0009】

これによれば、ゲートライナーは、半導体基板の面方向に対する法線方向から視たとき、トレンチと交差するように形成されている。このため、ゲートライナーがトレンチと交差しないように形成されている場合と比較して、半導体装置の小型化を図ることができる。

。

#### 【0010】

また、ゲートライナーの下方には、リサーフ層が形成されている。このため、リサーフ層が形成されていない場合と比較して、ゲートライナーの下方の領域にドレイン層側から伸びる高電界が達することを抑制でき、リーク電流が発生することを抑制できる。

30

#### 【0011】

また、請求項5では、トレンチゲート構造を有する半導体装置の製造方法であって、第1導電型のドリフト層（12）を有する半導体基板（10）を用意することと、半導体基板に、所定方向を長手方向とするトレンチ（16）を形成することと、トレンチ内にゲート絶縁膜（17）を介して所定のゲート電圧が印加されるゲート電極（18）を形成することでトレンチゲート構造を形成することと、半導体基板上にゲート電極と電気的に接続されるゲートライナー（19）を形成することと、ゲートライナーを形成した後、不純物をイオン注入して熱処理することにより、ドリフト層上に第2導電型のチャネル層（13）を形成することと共に、チャネル層の表層部に第1導電型の第1不純物領域（15）を形成することと、を行い、ゲートライナーを形成することでは、半導体基板の面方向に対する法線方向から視たとき、トレンチの長手方向と交差する方向に延設され、かつトレンチと交差するようにゲートライナーを形成し、トレンチを形成することの前に、ゲートライナーの下方となる領域に、第2導電型のリサーフ層（14）を形成することを行い、チャネル層を形成することでは、リサーフ層と繋がるチャネル層を形成するようにしている。

40

#### 【0012】

これによれば、ゲートライナーを形成することの前にリサーフ層を形成している。このため、ゲートライナーの下方にリサーフ層が形成された半導体装置を製造することができる。

50

## 【0013】

なお、上記および特許請求の範囲における括弧内の符号は、特許請求の範囲に記載された用語と後述の実施形態に記載される当該用語を例示する具体物等との対応関係を示すものである。

## 【図面の簡単な説明】

## 【0014】

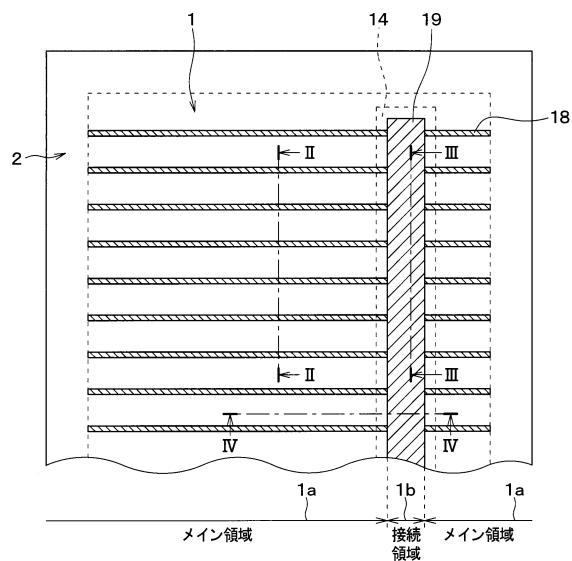

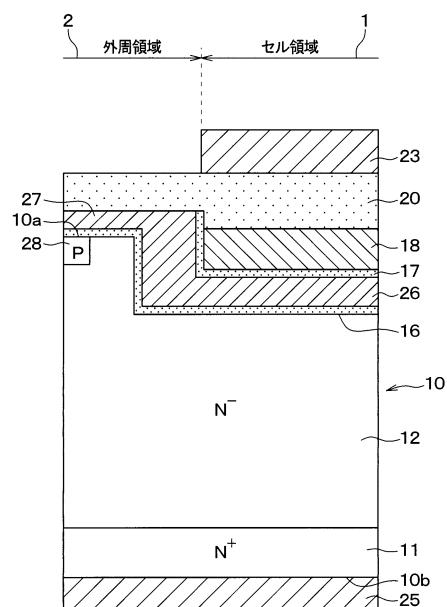

【図1】半導体装置の平面レイアウト図である。

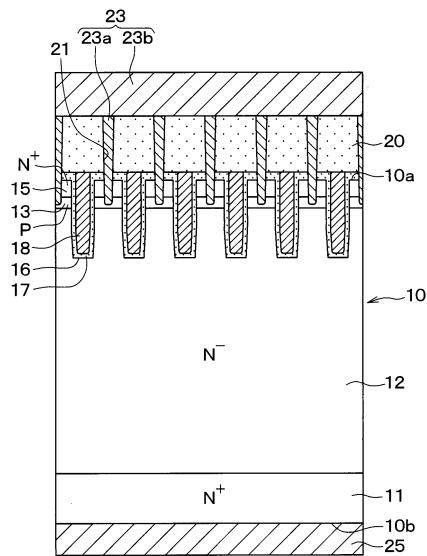

【図2】図1中のII - II線に沿った断面図である。

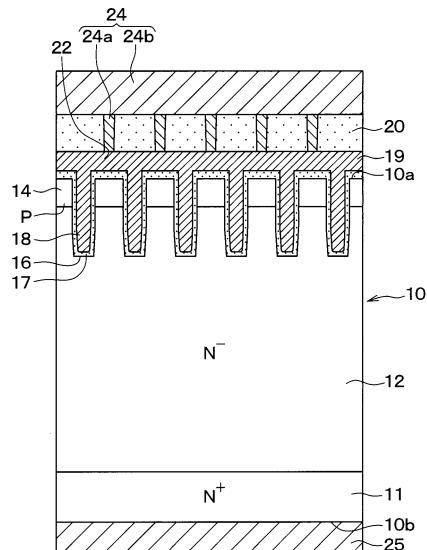

【図3】図1中のIII - III線に沿った断面図である。

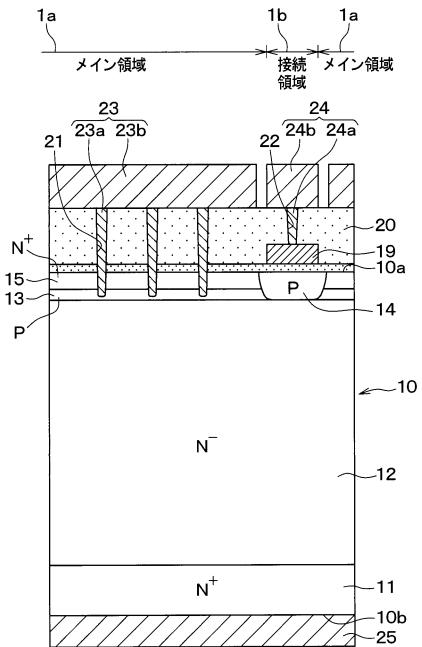

【図4】図1中のIV - IV線に沿った断面図である。

10

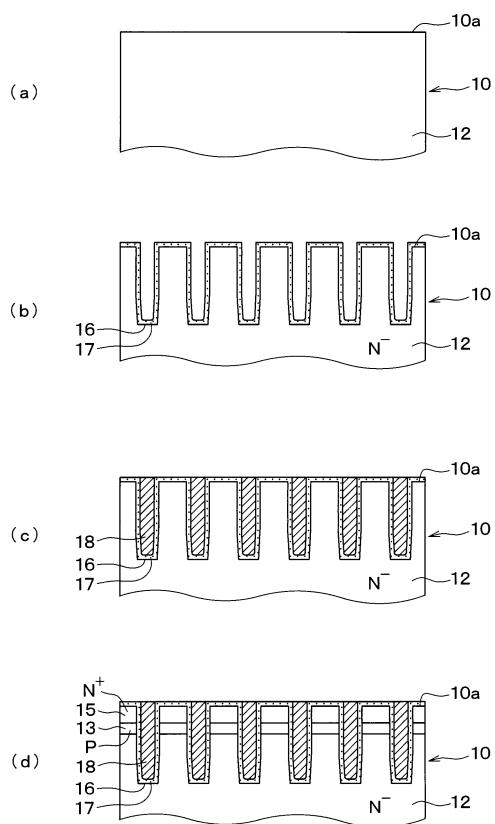

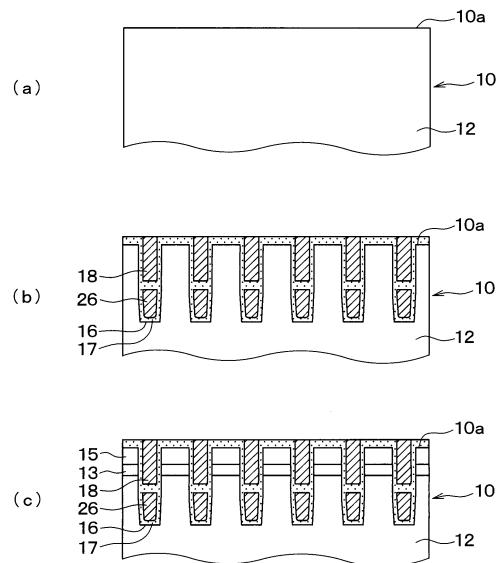

【図5】図2に示す半導体装置の製造工程を示す断面図である。

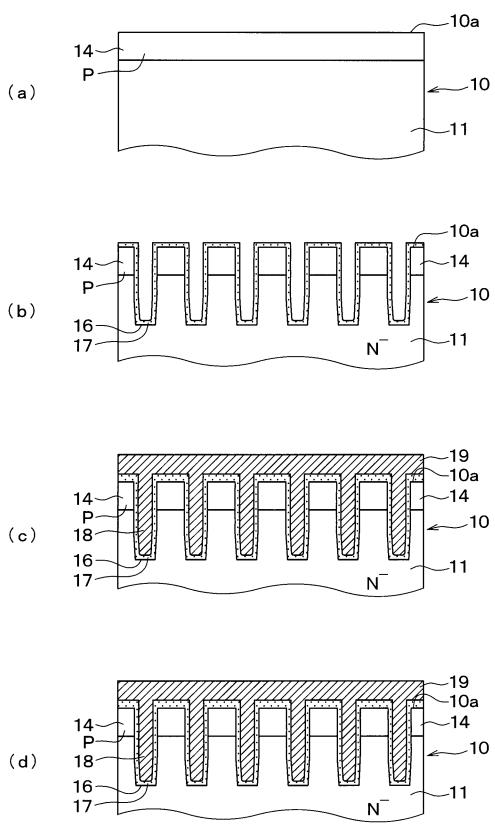

【図6】図3に示す半導体装置の製造工程を示す断面図である。

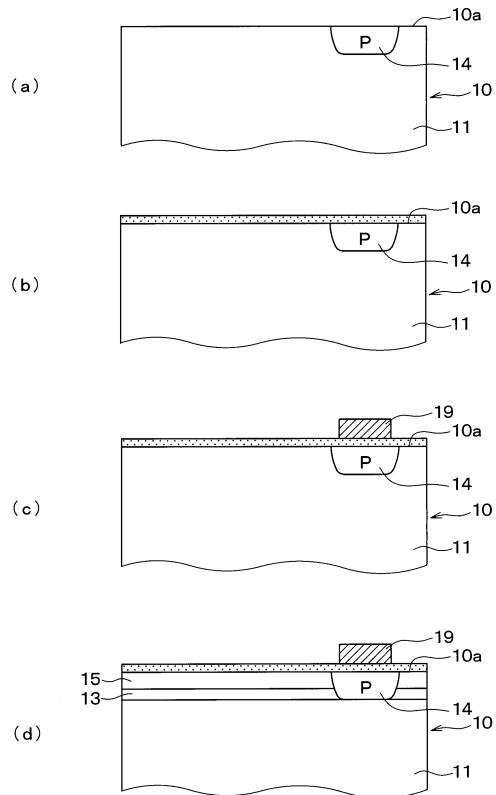

【図7】図4に示す半導体装置の製造工程を示す断面図である。

【図8】第2実施形態における半導体装置の断面図である。

【図9】第2実施形態における図8とは別の半導体装置の断面図である。

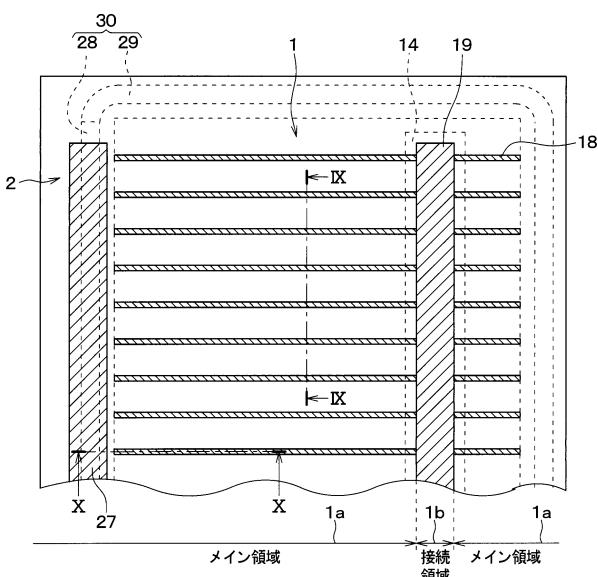

【図10】第2実施形態における半導体装置の平面レイアウト図である。

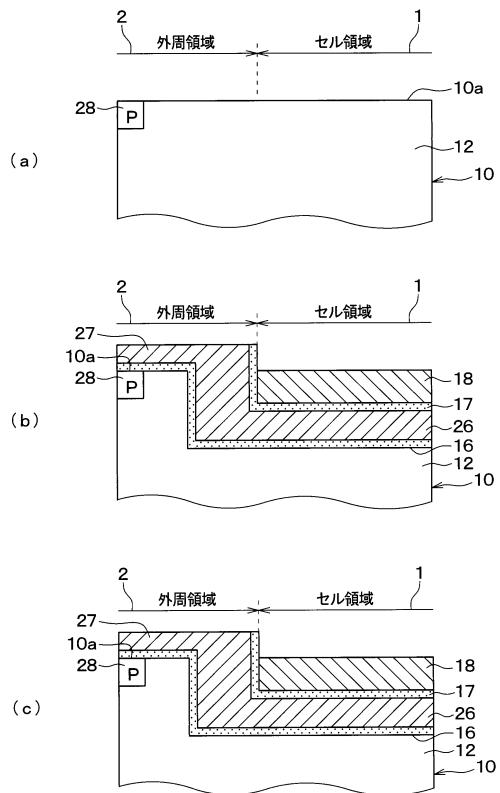

【図11】図8に示す半導体装置の製造工程を示す断面図である。

【図12】図9に示す半導体装置の製造工程を示す断面図である。

【図13】第3実施形態における半導体装置の平面レイアウト図である。

【図14】第4実施形態における半導体装置の平面レイアウト図である。

20

## 【発明を実施するための形態】

## 【0015】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。

## 【0016】

## (第1実施形態)

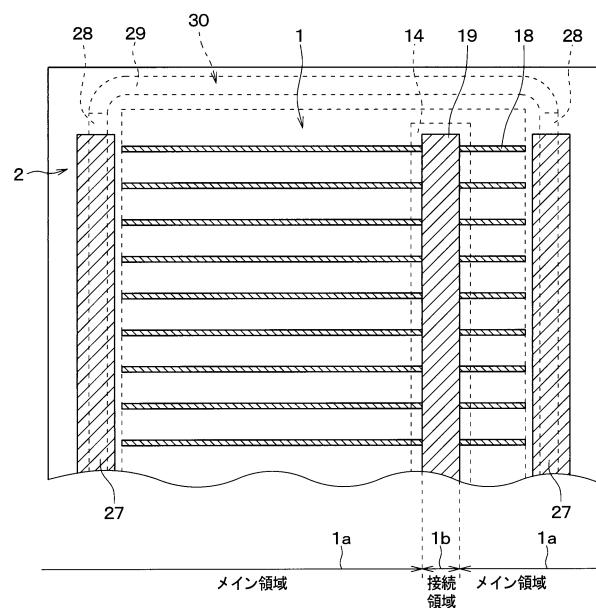

第1実施形態について説明する。まず、本実施形態の半導体装置の構成について説明する。本実施形態の半導体装置は、図1に示されるように、セル領域1と当該セル領域を囲む外周領域2とを有している。そして、セル領域1は、メイン領域1aと接続領域1bとを有している。なお、図1は、後述するゲート電極18、ゲートライナー19、およびリサーフ層14の位置関係を示す平面レイアウト図であり、断面図ではないが、理解をし易くするためにゲート電極18およびゲートライナー19にハッチングを施してある。また、本実施形態のセル領域1は、後述するゲート電極18が配置され、電流を流す素子としての機能を主に発揮する部分である。接続領域1bは、セル領域1のうちの後述するゲートライナー19が配置される領域のことであり、メイン領域1aは、セル領域1のうちの接続領域1bと異なる領域のことである。

30

## 【0017】

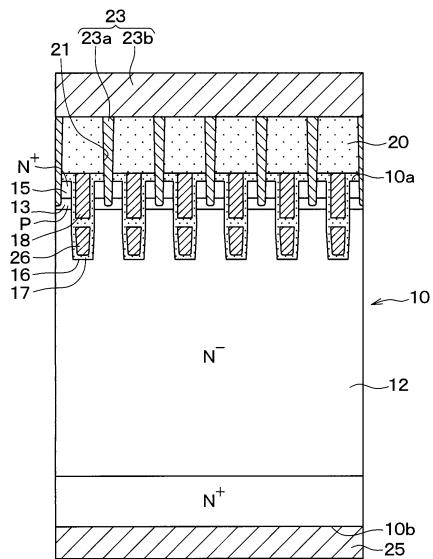

半導体装置は、図2～図4に示されるように、N<sup>+</sup>型のドレイン層11と、ドレイン層11の表面上に形成され、ドレイン層11よりも不純物濃度が低くされたN<sup>-</sup>型のドリフト層12とを有する半導体基板10を有している。なお、ドレイン層11は、不純物濃度が高濃度とされたN<sup>+</sup>型のシリコン基板等によって構成される。また、本実施形態では、ドレイン層11が第2不純物領域に相当している。

40

## 【0018】

ドリフト層12上(すなわち、半導体基板10の一面10a側)には、図2および図4に示されるように、メイン領域1aにおいて、比較的不純物濃度が低く設定されたP型のチャネル層13が形成されている。また、ドリフト層12上には、図3および図4に示されるように、接続領域1bにおいて、チャネル層13と不純物濃度がほぼ等しくされたP型のリサーフ層14が形成されている。本実施形態では、リサーフ層14は、チャネル層13とほぼ同じ深さまで形成されている。また、リサーフ層14は、後述するゲートライナー19の延設方向に沿って形成されており、ゲートライナー19の下方の全領域に形成

50

されている。つまり、リサーフ層14は、半導体基板10の一面10aに対する法線方向（すなわち、面方向に対する法線方向）から視たとき、後述するゲートライナー19が当該リサーフ層14内に位置するように形成されている。

【0019】

チャネル層13上には、図2および図4に示されるように、ドリフト層12よりも高不純物濃度とされたN<sup>+</sup>型のソース層15が形成されている。つまり、メイン領域1aでは、ドリフト層12上に、ドリフト層12側から順にチャネル層13およびソース層15が形成されている。なお、本実施形態では、ソース層15が第1不純物領域に相当している。

【0020】

また、半導体基板10には、図2および図3に示されるように、一面10a側からドリフト層12に達する複数のトレンチ16が形成されている。本実施形態では、複数のトレンチ16は、半導体基板10の一面10aの面方向のうちの所定方向に沿ってストライプ状に等間隔に形成され、メイン領域1aおよび接続領域1bに形成されている。

【0021】

具体的には、トレンチ16は、メイン領域1aでは、ソース層15およびチャネル層13を貫通してドリフト層12に達するように形成され、接続領域1bでは、リサーフ層14を貫通してドリフト層12に達するように形成されている。

【0022】

各トレンチ16は、各トレンチ16の壁面を覆うように形成されたゲート絶縁膜17と、このゲート絶縁膜17の上に形成されたゲート電極18とにより埋め込まれている。これにより、トレンチゲート構造が構成されている。なお、本実施形態では、ゲート絶縁膜17は、酸化膜等で構成され、ゲート電極18は、Poly-Si等で構成される。

【0023】

そして、接続領域1bには、図1、図3および図4に示されるように、半導体基板10の一面10a上に、Poly-Si等で構成されるゲートライナー19が形成されている。具体的には、ゲートライナー19は、半導体基板10の一面10aに対する法線方向から視たとき、トレンチ16（すなわち、ゲート電極18）の延設方向と交差する方向に延設されていると共に、各トレンチ16と交差するように形成されている。そして、ゲートライナー19は、各トレンチ16の開口部上において、各ゲート電極18と電気的に接続されている。

【0024】

また、本実施形態では、ゲートライナー19は、半導体基板10の一面10aに対する法線方向から視たとき、リサーフ層14内に位置するように形成されている。言い換えると、ゲートライナー19の下方の全領域には、リサーフ層14が形成されている。

【0025】

さらに、半導体基板10の一面10a上には、図2～図4に示されるように、ゲート電極18およびゲートライナー19を覆うように、酸化膜等で構成される層間絶縁膜20が形成されている。この層間絶縁膜20には、メイン領域1aにおいて、ソース層15およびチャネル層13を露出させる第1コンタクトホール21が形成されている。また、層間絶縁膜20には、接続領域1bにおいて、ゲートライナー19を露出させる第2コンタクトホール22が形成されている。

【0026】

具体的には、第1コンタクトホール21は、複数形成されており、隣接する各トレンチ16間において、それぞれソース層15を貫通してチャネル層13に達するように形成されている。これにより、ソース層15は、第1コンタクトホール21の側面から露出し、チャネル層13は、第1コンタクトホール21の側面および底面から露出した状態となっている。

【0027】

また、第2コンタクトホール22は、複数形成されており、ゲートライナー19を露出

10

20

30

40

50

させるように形成されている。なお、第2コンタクトホール22は、少なくともゲートライナー19の一部が露出する構成とされていればよい。つまり、第2コンタクトホール22は、複数形成されていてもよいし、例えば、1つのみ形成されていてもよい。

【0028】

そして、層間絶縁膜20上には、第1コンタクトホール21を通じてソース層15およびチャネル層13と電気的に接続されるソース電極層23が形成されている。また、層間絶縁膜20上には、第2コンタクトホール22を通じてゲートライナー19と接続され、当該ゲートライナー19を介してゲート電極18と電気的に接続されるゲート電極層24が形成されている。

【0029】

本実施形態では、ソース電極層23は、第1コンタクトホール21内に埋め込まれる第1埋込電極部23aと、層間絶縁膜20上に配置されて第1埋込電極部23aと電気的に接続される第1上層電極部23bとを有する構成とされている。同様に、ゲート電極層24は、第2コンタクトホール22内に埋め込まれる第2埋込電極部24aと、層間絶縁膜20上に配置されて第2埋込電極部24aと電気的に接続される第2上層電極部24bとを有する構成とされている。なお、第1、第2埋込電極部23a、24aは、本実施形態では、W(すなわち、タンゲステン)で構成されている。つまり、第1、第2埋込電極部23a、24aは、いわゆるWプラグとされている。また、第1、第2上層電極部23b、24bは、A1(すなわち、アルミニウム)等で構成されている。

【0030】

また、ドレイン層11を挟んでドリフト層12と反対側には、ドレイン層11と電気的に接続されるドレイン電極25が形成されている。つまり、半導体基板10の他面10b上には、ドレイン層11と電気的に接続されるドレイン電極25が形成されている。

【0031】

外周領域2には、特に図示しないが、耐圧向上を図るためのガードリングや、当該ガードリングと電気的に接続される外周電極等が適宜形成されている。

【0032】

以上が本実施形態における半導体装置の構成である。なお、本実施形態では、N<sup>+</sup>型、N型、N<sup>-</sup>型が第1導電型に相当しており、P型、P<sup>+</sup>型が第2導電型に相当している。また、上記のように、本実施形態の半導体基板10は、ドレイン層11、ドリフト層12、チャネル層13、ソース層15を含んで構成されている。

【0033】

このような半導体装置では、セル領域1において、ゲートライナー19の下方にもP型のリサーフ層14が形成されている。このため、ゲートライナー19の下方にリサーフ層14が形成されていない場合と比較して、ゲートライナー19の下方に高電界が集中することを抑制できる。したがって、ゲートライナー19の下方の部分にてリーク電流が発生することを抑制できる。

【0034】

次に、上記半導体装置の製造工程について、図5～図7を参照しつつ説明する。なお、図5は、図2に相当する断面図であり、図6は、図3に相当する断面図であり、図7は、図4に相当する断面図である。また、各図の(a)～(d)は、それぞれ同じ工程の状態を示している。

【0035】

まず、図5(a)、図6(a)、図7(a)に示されるように、ドレイン層11上にドリフト層12が積層された半導体基板10を用意する。なお、ここでは、ドレイン層11上にドリフト層12が積層された半導体基板10を用意する例について説明するが、下記の工程を行った後、イオン注入および熱処理を行うことで半導体基板10の他面10b側にドレイン層11を形成するようにしてもよい。

【0036】

次に、図6(a)および図7(a)に示されるように、半導体基板10の一面10a上

10

20

30

40

50

に図示しないマスクを配置し、ゲートライナー 19 が形成される下方の領域に P 型不純物を適宜イオン注入して熱拡散することにより、リサーフ層 14 を形成する。その後、マスクを除去する。

【0037】

そして、図 5 (b)、図 6 (b)、図 7 (b) に示されるように、図示しないマスクを配置し、ドライエッチング等を行って上記トレンチ 16 を形成する。その後、熱酸化等を行い、トレンチ 16 の壁面にゲート絶縁膜 17 を形成する。なお、この工程では、半導体基板 10 の一面 10a 上にも絶縁膜が形成される。

【0038】

続いて、図 5 (c)、図 6 (c)、図 7 (c) に示されるように、各トレンチ 16 が埋め込まれるように、CVD 法等で Poly-Si を成膜する。これにより、各トレンチ 16 には、ゲート絶縁膜 17 を介してゲート電極 18 が配置されたトレンチゲート構造が構成される。そして、図示しないマスクを配置してドライエッチング等を行い、半導体基板 10 の一面 10a 上に形成された Poly-Si を適宜パターニングしてゲートライナー 19 を形成する。この際、ゲートライナー 19 は、上記で説明したように、半導体基板 10 の一面 10a に対する法線方向から視たとき、各トレンチ 16 と交差し、かつ下方にリサーフ層 14 層が位置するように形成される。その後、マスクを除去する。

【0039】

なお、リサーフ層 14 を形成する工程およびゲートライナー 19 を形成する工程では、半導体基板 10 の一面 10a に対する法線方向から視たとき、リサーフ層 14 内にゲートライナー 19 が位置するようにリサーフ層 14 およびゲートライナー 19 が形成される。

【0040】

次に、図 5 (d)、図 6 (d)、図 7 (d) に示されるように、P 型不純物および N 型不純物をイオン注入して熱拡散することにより、チャネル層 13 およびソース層 15 を形成する。この際、ゲートライナー 19 の下方には、当該ゲートライナー 19 がマスクとなって不純物が注入されない。しかしながら、本実施形態では、ゲートライナー 19 の下方には、既にリサーフ層 14 が形成されている。このため、この工程では、チャネル層 13 とリサーフ層 14 とが繋がるように当該チャネル層 13 を形成する。これにより、セル領域 1 では、ドリフト層 12 上にチャネル層 13 またはリサーフ層 14 が形成された構成となる。

【0041】

その後は、特に図示しないが、ゲート電極 18 およびゲートライナー 19 を覆うように、層間絶縁膜 20 を CVD 法等により形成する。そして、層間絶縁膜 20 上にフォトレジスト等を配置し、当該フォトレジストをマスクとして層間絶縁膜 20 に第 1 コンタクトホール 21 および第 2 コンタクトホール 22 を形成する。

【0042】

続いて、チャネル層 13 およびソース層 15 と電気的に接続されるソース電極層 23 を形成すると共に、ゲートライナー 19 と接続されるゲート電極層 24 を形成する。ソース電極層 23 およびゲート電極層 24 を形成する際には、例えば、まず、第 1 コンタクトホール 21 および第 2 コンタクトホール 22 内に CVD 法等で W を埋め込み、第 1、第 2 埋込電極部 23a、24a を形成する。次に、層間絶縁膜 20 上に積層された W 膜を除去する。その後、層間絶縁膜 20 上に CVD 法等で Al 等の金属膜を成膜し、成膜した金属膜をパターニングすることにより、第 1 埋込電極部 23a と電気的に接続される第 1 上層電極部 23b を形成すると共に、第 2 埋込電極部 24a と電気的に接続される第 2 上層電極部 24b を形成する。以上のようにして、本実施形態の半導体装置が製造される。

【0043】

以上説明したように、本実施形態では、ゲートライナー 19 は、半導体基板 10 の一面 10a に対する法線方向から視たとき、トレンチ 16 と交差するように形成されている。このため、ゲートライナー 19 がトレンチ 16 と交差しないように形成されている場合と比較して、半導体装置の小型化を図ることができる。

10

20

30

40

50

## 【0044】

また、ゲートライナー19の下方には、リサーフ層14が形成されている。このため、リサーフ層14が形成されていない場合と比較して、ゲートライナー19の下方の領域にドレイン層11側から延びる高電界が達することを抑制でき、リーク電流が発生することを抑制できる。

## 【0045】

さらに、ゲートライナー19は、半導体基板10の一面10aに対する法線方向から見たとき、リサーフ層14内に位置するように形成されている。つまり、セル領域1は、ドリフト層12上にチャネル層13またはリサーフ層14が形成された状態となっている。このため、さらにリーク電流が発生することを抑制できる。

10

## 【0046】

そして、リサーフ層14は、ゲートライナー19を形成する前に形成するようにしている。このため、ゲートライナー19の下方にリサーフ層14が配置された半導体装置を容易に製造することができる。

## 【0047】

また、チャネル層13およびソース層15は、トレンチゲート構造を形成した後に形成される。このため、例えば、トレンチ16の僅かな出来栄えの変化に基づいてチャネル層13およびソース層15を形成する際のイオン注入や熱処理等の条件を変更でき、信頼度の高い半導体装置を製造できる。

## 【0048】

20

## (第2実施形態)

第2実施形態について説明する。本実施形態は、第1実施形態に対して、トレンチゲート構造を変更したものであり、その他に関しては上記第1実施形態と同様であるため、ここでは説明を省略する。

## 【0049】

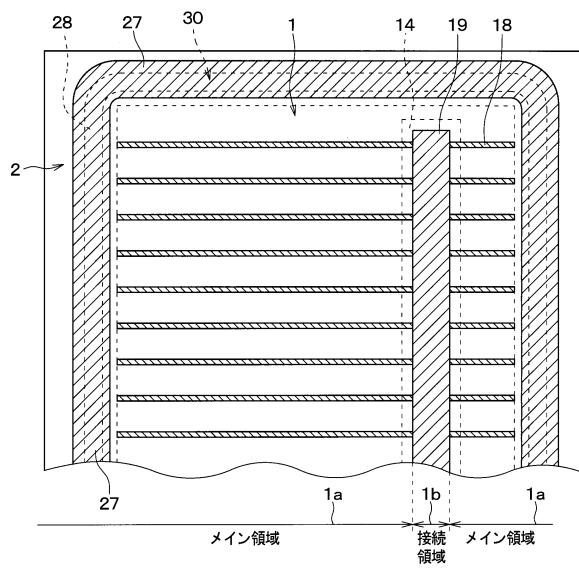

本実施形態では、図8および図9に示されるように、トレンチゲート構造は、いわゆるスプリットゲート構造とされている。具体的には、各トレンチ16には、底部側にシールド電極26が配置され、開口部側にゲート電極18が配置されている。つまり、各トレンチ16には、シールド電極26とゲート電極18とが積層されて配置されている。そして、トレンチ16の上段側に配置されたゲート電極18によって上段側ゲート構造が構成され、トレンチ16の底部側に配置されたシールド電極26によって下段側ゲート構造が構成されている。

30

## 【0050】

なお、シールド電極26とゲート電極18との間には、ゲート絶縁膜17が配置されている。また、ゲート電極18は、半導体基板10の一面10a側からチャネル層13の底部よりも深い位置まで形成されている。つまり、ゲート電極18は、トレンチ16の開口部側に配置されるが、ゲート電圧が印加された際、チャネル層13にソース層15とドリフト層12とを繋ぐチャネルが形成されるように配置されている。そして、各ゲート電極18は、上記第1実施形態と同様に、ゲートライナー19と電気的に接続されている。

## 【0051】

40

また、各トレンチ16は、図9に示されるように、セル領域1から外周領域2まで延設されている。本実施形態では、トレンチ16は、延設方向における一端部が外周領域2に位置するように形成されている。そして、各シールド電極26は、図9および図10に示されるように、それぞれトレンチ16の外周領域2に位置する部分にて、トレンチ16の開口部まで引き出され、外周領域2に形成されたシールドライナー27と電気的に接続されている。

## 【0052】

なお、本実施形態では、シールドライナー27は、図10とは別断面において、A1配線等を介してソース電極層23と電気的に接続され、ソース電極層23と同電位とされている。つまり、シールド電極26は、ソース電極層23の電位に維持されている。また、

50

シールドライナー 27 は、トレンチ 16 の延設方向における一端部側において、トレンチ 16 の延設方向と直交する方向に延設され、端部を有する形状とされている。

【0053】

外周領域 2 では、図 9 および図 10 に示されるように、シールドライナー 27 の下方に P 型の外周リサーフ層 28 が形成されている。さらに、外周領域 2 では、シールドライナー 27 の下方と異なる領域において、外周リサーフ層 28 と繋がる P 型層 29 が形成されている。本実施形態では、外周リサーフ層 28 と P 型層 29 とが連結されることにより、セル領域 1 を囲むガードリング 30 が構成されている。なお、本実施形態では、P 型層 29 が第 3 不純物領域に相当している。

【0054】

以上が本実施形態における半導体装置の構成である。次に、上記半導体装置の製造工程について図 11 および図 12 を参照しつつ説明する。なお、図 11 は、図 9 に相当する断面図であり、図 12 は図 10 に相当する断面図である。

【0055】

まず、図 11 (a) および図 12 (a) に示されるように、半導体基板 10 の一面 10a 上に図示しないマスクを配置し、シールドライナー 27 が形成される下方の領域を含む位置に P 型不純物を適宜イオン注入して熱拡散することにより、外周リサーフ層 28 を形成する。その後、マスクを除去する。なお、この工程は、特に図示しないが、リサーフ層 14 を形成する工程と同時に行われる。

【0056】

次に、図 11 (b) および図 12 (b) に示されるように、トレンチ 16 を形成した後、熱酸化や CVD 法等を適宜行って上記スプリットゲート構造を形成する。なお、この際、トレンチ 16 は、外周領域 2 まで延設されるようにする。また、シールド電極 26 を形成する際には、トレンチ 16 の外周領域 2 に位置する部分にて、トレンチ 16 の開口部まで引き出されるようにする。そして、半導体基板 10 の一面 10a 上に形成された Poly-Si を適宜パターンングし、シールド電極 26 と電気的に接続されるシールドライナー 27 を形成する。

【0057】

続いて、図 11 (c) および図 12 (c) に示されるように、P 型不純物およびN 型不純物をイオン注入して熱拡散することにより、チャネル層 13 およびソース層 15 を形成する。なお、この工程では、シールドライナー 27 の下方には、当該シールドライナー 27 がマスクとなって不純物が注入されない。このため、図 12 (c) とは別断面において、外周リサーフ層 28 と繋がるように P 型層 29 を形成することにより、外周領域 2 にガードリング 30 を構成する。

【0058】

その後は、特に図示しないが、上記第 1 実施形態と同様に、ソース電極層 23 およびゲート電極層 24 等を形成することにより、上記半導体装置が製造される。

【0059】

このように、スプリットゲート構造を有する半導体装置としてもよい。また、トレンチ 16 の底部側にシールド電極 26 を配置することにより、トレンチ 16 の底部に電界集中が発生することを抑制でき、耐圧の向上を図ることができる。

【0060】

(第 3 実施形態)

第 3 実施形態について説明する。本実施形態は、第 2 実施形態に対して、シールドライナー 27 の構成を変更したものであり、その他に関しては上記第 2 実施形態と同様であるため、ここでは説明を省略する。

【0061】

本実施形態では、図 13 に示されるように、外周領域 2 には、トレンチ 16 の延設方向における両端部側にシールドライナー 27 が形成されている。また、特に図示しないが、トレンチ 16 は、延設方向における両端部側が外周領域 2 まで延設されている。そして、

10

20

30

40

50

シールド電極 26 は、トレンチ 16 の延設方向における両端部側にて開口部まで引き出され、外周領域 2 に形成された各シールドライナー 27 と電気的に接続されている。

【0062】

また、外周領域 2 では、各シールドライナー 27 の下方に P 型の外周リサーフ層 28 が形成されている。そして、シールドライナー 27 の下方と異なる領域には、各外周リサーフ層 28 と繋がり、各外周リサーフ層 28 と共にガードリング 30 を構成する P 型層 29 が形成されている。

【0063】

以上説明したように、本実施形態では、各シールド電極 26 は、トレンチ 16 の延設方向における両端部側から引き出され、各シールド電極 26 と電気的に接続されている。このため、シールド電極 26 内の電位をほぼ均等にできる。

10

【0064】

なお、このような半導体装置は、特に図示しないが次のように製造される。すなわち、図 11 (a) および図 12 (a) の工程において、各シールドライナー 27 が形成される下方の領域を含む位置にそれぞれ外周リサーフ層 28 を形成する。そして、図 11 (b) および図 12 (b) の工程において、延設方向の両端部が外周領域 2 に位置するようにトレンチ 16 を形成し、外周領域 2 に位置する両端部にてシールド電極 26 とシールドライナー 27 とが電気的に接続されることによって製造される。

【0065】

(第 4 実施形態)

20

第 4 実施形態について説明する。本実施形態は、第 3 実施形態に対して、シールドライナー 27 の構成を変更したものであり、その他に関しては上記第 3 実施形態と同様であるため、ここでは説明を省略する。

【0066】

本実施形態では、図 14 に示されるように、シールドライナー 27 は、セル領域 1 を囲むように形成されている。つまり、シールドライナー 27 は、枠状に形成されており、端部を有しない形状とされている。そして、シールドライナー 27 の下方には、セル領域 1 を囲むように外周リサーフ層 28 が形成されている。つまり、本実施形態では、外周リサーフ層 28 のみによってガードリング 30 が構成されており、P 型層 29 は形成されていない。

30

【0067】

以上説明したように、本実施形態では、シールドライナー 27 は、セル領域を囲むように形成されている。このため、外周領域 2 におけるセル領域 1 側の全領域において、電界強度の緩和を図ることができる。

【0068】

なお、このような半導体装置は、特に図示しないが、次のように製造される。すなわち、図 11 (a) および図 12 (a) の工程において、セル領域 1 を囲むように外周リサーフ層 28 を形成し、図 11 (b) および図 12 (b) の工程において、セル領域 1 を囲むようにシールドライナー 27 を形成することによって製造される。

【0069】

40

(他の実施形態)

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

【0070】

例えば、上記各実施形態では、第 1 導電型を N 型、第 2 導電型を P 型とする場合について説明したが、第 1 導電型を P 型、第 2 導電型を N 型とする半導体装置としてもよい。つまり、上記各実施形態で説明した各部の導電型を反転させた構造としてもよい。

【0071】

上記各実施形態において、リサーフ層 14 は、チャネル層 13 より高不純物濃度とされているてもよい。また、上記各実施形態において、リサーフ層 14 は、チャネル層 13 より

50

深くされていてもよい。これらによれば、ゲートライナー 19 の下方で高電界が集中することをさらに抑制でき、さらにリーク電流が発生することを抑制できる。

【0072】

さらに、上記各実施形態において、リサーフ層 14 は、チャネル層 13 より低不純物濃度とされていてもよい。また、上記各実施形態において、リサーフ層 14 は、チャネル層 13 より浅く形成されていてもよい。このような半導体装置としても、リサーフ層 14 が形成されていることにより、ゲートライナー 19 の下方で高電界が集中することを抑制できる。

【0073】

そして、上記各実施形態において、リサーフ層 14 は、ゲートライナー 19 の下方の領域の一部に形成されていてもよい。このような半導体装置としても、リサーフ層 14 が形成されていない場合と比較して、ゲートライナー 19 の下方で高電界が集中することを抑制できる。

【0074】

さらに、上記各実施形態において、ゲート電極 18 とゲートライナー 19 は、異なる材料で形成されていてもよく、例えば、ゲートライナー 19 は、アルミニウム等で構成されていてもよい。同様に、上記第 2 ~ 第 4 実施形態において、シールド電極 26 とシールドライナー 27 は、異なる材料で形成されていてもよく、例えば、シールドライナー 27 は、アルミニウム等で構成されていてもよい。

【0075】

そして、上記各実施形態において、ドレイン層 11 を備える代わりに、P 型のコレクタ層を備えるようにしてもよい。つまり、半導体基板 10 に IGBT ( すなわち、Insulated Gate Bipolar Transistor ) 素子が形成されていてもよい。なお、このような構成とする場合は、コレクタ層が第 2 不純物領域に相当する。また、ドレイン層 11 上に、N 型のカラム領域と P 型のカラム領域とが配置されたスーパージャンク構造を有する半導体装置としてもよい。

【0076】

さらに、上記各実施形態において、ドリフト層 12 の表層部にドレイン層 11 が形成され、半導体基板 10 の面方向に電流を流す横型の半導体装置としてもよい。

【0077】

さらに、上記各実施形態において、第 1 コンタクトホール 21 および第 2 コンタクトホール 22 の壁面に、Ti ( すなわち、チタン ) 、または TiN ( すなわち、窒化チタン ) 等で構成されるバリアメタルが形成されていてもよい。なお、このようなバリアメタルは、例えば、第 1 、第 2 埋込電極部 23a 、 24a を形成する前に、スパッタ法等で形成される。

【0078】

そして、上記各実施形態において、第 1 ソース電極層 23 は、第 1 埋込電極部 23a と第 1 上層電極部 23b とが同じ材料を用いて構成されていてもよく、例えば、アルミニウムで構成されていてもよい。同様に、第 2 ゲート電極層 24 は、第 2 埋込電極部 24a と第 2 上層電極部 24b とが同じ材料を用いて構成されていてもよく、例えば、アルミニウムで構成されていてもよい。

【0079】

さらに、上記各実施形態において、ソース層 15 は、チャネル層 13 の表層部に選択的に形成されていてもよい。つまり、半導体基板 10 の一面 10a がチャネル層 13 およびソース層 15 を有する構成とされていてもよい。この場合、第 1 コンタクトホール 21 は、チャネル層 13 およびソース層 15 が露出されればよいため、半導体基板 10 の一面 10a より深くまで形成されなくててもよい。つまり、第 1 コンタクトホール 21 は、半導体基板 10 の一面 10a からチャネル層 13 およびソース層 15 が露出するように形成されればよい。

【符号の説明】

10

20

30

40

50

## 【0080】

- 1 1 ドレイン層(第2不純物領域)

- 1 2 ドリフト層

- 1 3 チャネル層

- 1 4 リサーフ層

- 1 5 ソース層(第1不純物領域)

- 1 6 トレンチ

- 1 7 ゲート絶縁膜

- 1 8 ゲート電極

- 1 9 ゲートライナー

10

【図1】

【図2】

【 図 3 】

【 四 4 】

【 図 5 】

【 义 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| H 0 1 L | 29/58 | G       |

| H 0 1 L | 29/50 | M       |

| H 0 1 L | 29/78 | 6 5 2 P |

(56)参考文献 米国特許出願公開第2010/0140689(US, A1)

国際公開第99/012214(WO, A1)

特開2013-143522(JP, A)

特開2012-059841(JP, A)

特開2017-017078(JP, A)

特開平04-162572(JP, A)

米国特許出願公開第2014/0197483(US, A1)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 9 / 7 8

H 0 1 L 2 9 / 0 6

H 0 1 L 2 9 / 4 1 7

H 0 1 L 2 9 / 4 2 3

H 0 1 L 2 9 / 4 9