(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4175303号

(P4175303)

(45) 発行日 平成20年11月5日(2008.11.5)

(24) 登録日 平成20年8月29日(2008.8.29)

(51) Int.Cl.

H03F 3/34 (2006.01)

G05F 1/56 (2006.01)

F 1

H03F 3/34

G05F 1/56 310 F

## 請求項の数 5 外国語出願 (全 13 頁)

(21) 出願番号 特願2004-223407 (P2004-223407)

(22) 出願日 平成16年7月30日 (2004.7.30)

(65) 公開番号 特開2005-57763 (P2005-57763A)

(43) 公開日 平成17年3月3日 (2005.3.3)

審査請求日 平成16年7月30日 (2004.7.30)

(31) 優先権主張番号 0318237.5

(32) 優先日 平成15年8月4日 (2003.8.4)

(33) 優先権主張国 英国(GB)

## 前置審査

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

(74) 代理人 100127661

弁理士 宮坂 一彦

(72) 発明者 ビナヤカ アグラワラ

イギリス ケンブリッジ CB4 O F E

9 a ケンブリッジ サイエンスパーク

ミルトンロード エプソンケンブリッジ

研究所内

最終頁に続く

(54) 【発明の名称】電力変換回路および電力変換方法

## (57) 【特許請求の範囲】

## 【請求項 1】

出力ノードと、

第1增幅器と、

前記出力ノードと前記第1增幅器の間に位置するPMOSトランジスタである第1トランジスタと、

前記第1トランジスタと前記第1增幅器の間に位置する第2增幅器と、

前記出力ノードと前記第1增幅器の間に位置するNMOSトランジスタである第2トランジスタと、

前記第2トランジスタと前記第1增幅器の間に位置する第3增幅器と、を含み、

前記第1增幅器が基準電圧と前記出力ノードにおける出力電圧とを入力するものであり、

前記第2增幅器が前記第1增幅器からの出力と前記出力電圧とを入力するものであり、

前記第3增幅器が前記第1增幅器からの出力と前記出力電圧とを入力するものであり、

前記第2增幅器がプルアップ部を構成し、電流ソースに直列配列されたNMOSトランジスタを備え、前記第3增幅器がプルダウン部を構成し、電流シンクに直列配列されたPMOSトランジスタを備え、

前記第1增幅器が第1ゲインステージを構成し、前記第2增幅器が第2ゲインステージを構成し、

前記第1ゲインステージのゲインが前記第2ゲインステージのゲインより大きく、前記第2ゲインステージの帯域幅が前記第1ゲインステージの帯域幅より大きい、

10

20

ことを特徴とする電圧変換回路。

**【請求項 2】**

請求項 1 に記載の電圧変換回路において、

さらに、前記第 1 増幅器と前記第 2 増幅器との間に位置するレベルシフタ回路を含み、

前記第 1 増幅器からの出力が前記レベルシフタ回路を介して前記第 2 増幅器に入力されるものである、

ことを特徴とする電圧変換回路。

**【請求項 3】**

請求項 1 または 2 に記載の電圧変換回路において、

前記第 1 増幅器が前記第 2 増幅器よりも低速である、

ことを特徴とする電圧変換回路。

10

**【請求項 4】**

請求項 1 ないし 3 のいずれか一項に記載の電圧変換回路において、

前記第 1 増幅器が前記第 2 増幅器よりも消費電力が小さい、

ことを特徴とする電圧変換回路。

**【請求項 5】**

請求項 1 ないし 4 のいずれか一項に記載の電圧変換回路において、

前記第 1 パワートランジスタの一方の端子が前記出力ノードと前記第 2 パワートランジスタの一方の端子とに接続されている、

ことを特徴とする電圧変換回路。

20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、電力変換回路および電力変換方法に関する。

**【背景技術】**

**【0002】**

集積回路 (IC) では、現在、オンチップ電源の需要が高い。IC では異なる電源電圧レベルが必要とされることが多いため、オンチップ電源があるレベル、すなわち比較的高いレベルの電圧を、同一 IC 内で使用するために別のレベル、すなわちより低いレベルの電圧に変換することが必要となる。同一 IC 内での使用のための高電圧レベルから低電圧レベルへの変換は、通常、インダクタおよびコンデンサのような外部部品を使用する切換変換器、または半導体 IC に完全に組込みが可能な線形または切換変換器のいずれかによっておこなわれる。

30

**【0003】**

組込み型の変換器としては、線形変換器が一般的に望ましい。これは、回路部品が少なくて済み、よって電圧変換プロセスのための IC 回路配置に必要な装置が少なくて済むためである。したがって、携帯装置用に設計される IC に使用するには、電力効率がよりよい切換変換器と比較しても、線形変換器の方がより適すると考えられる。

**【0004】**

線形電力変換器は、外部電源および負荷の間に、自動調整可能な電気抵抗を与えることにより機能する。抵抗は負荷および出力電流に応じて自己調整するため、負荷端子における電圧は一定となる。

40

**【0005】**

負荷が、外部電源からの出力電圧  $V_{out}$  から電流  $I_{load}$  を引き込む場合、負荷における電力消費は次の式により求められる。

$$P_{load} = V_{out} \times I_{load}$$

**【0006】**

しかし、この電力変換機能を果たすために外部電源から供給されるべき電流は、線形電力変換器の電流消費を  $I_{converter}$  とすると、 $I_{load} + I_{converter}$  となる。したがって、外部電源に必要な電力出力は次の式により求められる。

$$P_{tot} = V_{dd} \times (I_{load} + I_{converter})$$

【0007】

よって、電圧変換器の電力効率は次の式により求められる。

$$\eta_{power} = P_{load} / P_{tot} = \frac{V_{out} \times I_{load}}{V_{dd} \times (I_{load} + I_{converter})}$$

【0008】

$V_{out}$  は常に  $V_{dd}$  よりも小さいため、たとえ変換器電流がゼロになったとしても、電力効率は決して 1 (100%) にはならない。このため、線形電力変換器の性能は、通常、変換器の「電流効率」と言われ、次の式で表される。

$$\eta_{current} = I_{load} / I_{tot} = \frac{I_{load}}{I_{load} + I_{converter}}$$

10

【0009】

電力変換器においては、その回路の制御部においていくらかの電流を消費する。よって、変換器の効率は常に 1 未満である。

【0010】

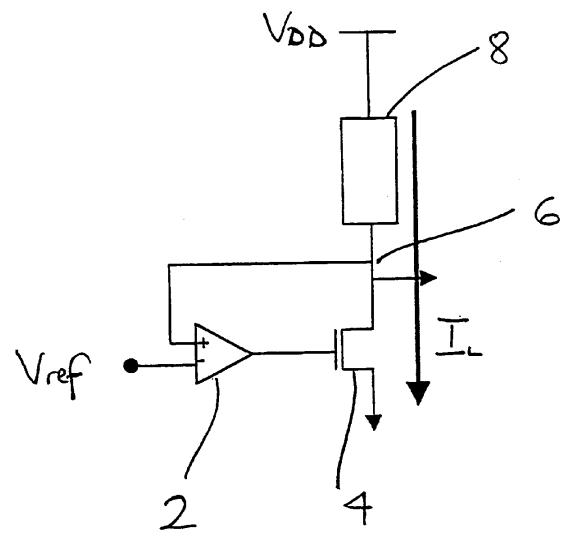

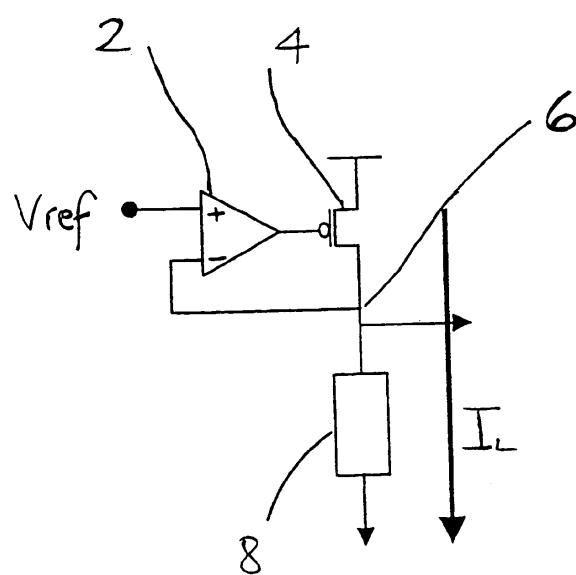

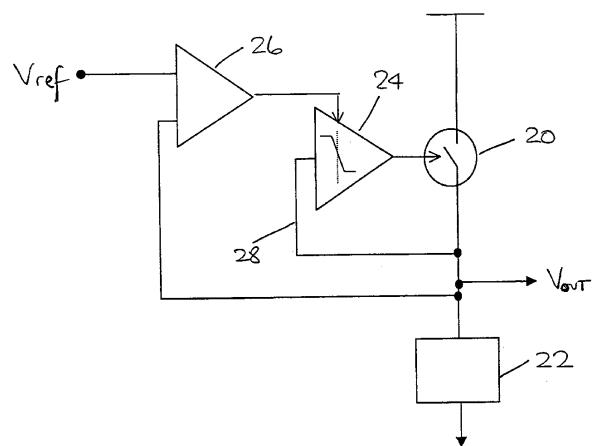

図 1 に線形電力変換器の典型例を示す。これはプルダウン変換器の一例である。このプルダウン回路において、差動増幅器 2 は比較器として働き、出力ノード 6 での電圧が基準電圧  $V_{ref}$  と比較し高いか低いかに応じて、トランジスタ 4 の形式で、固体スイッチのオンオフを切り替える。トランジスタ 4 は、負荷 8 に直列接続され、電圧源  $V_{DD}$  に接続される。図 2 に同じ回路のプルアップ版を示す。スイッチはこれらの回路において、出力電圧が基準電圧よりも低ければオンに、高ければオフに切り替えられる。

20

【0011】

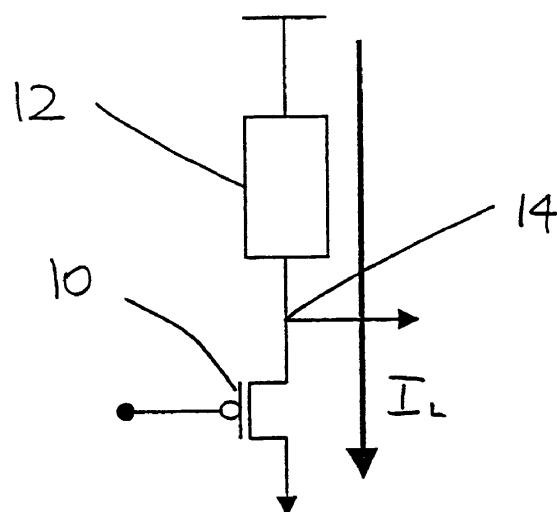

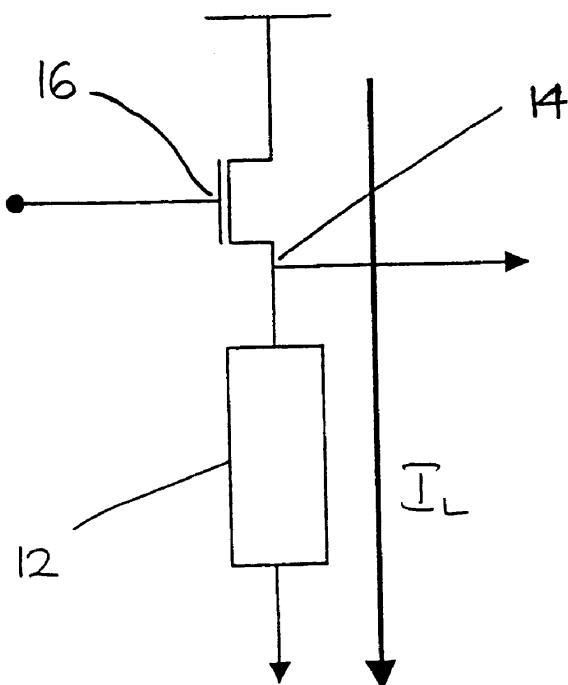

図 3 は、より簡易的なプルダウン線形変換器を示す。これは負荷 12 に直列接続された PMOS トランジスタ 10 で構成される。このプルダウン回路において、PMOS トランジスタ 10 のゲート電圧は、基準電圧と等価なバイアス電圧に加え、PMOS トランジスタの閾値電圧よりもわずかに高い所定の電圧により固定される。したがって、出力ノード 14 での電圧が上昇すると、PMOS トランジスタのソース・ゲート電圧もこれにならい、負荷 12 を介して PMOS トランジスタに流れ込む電流も同様である。つまり、PMOS トランジスタは、実質的にダイオードとして機能する。この電流は、負荷電流  $I_L$  の比較的小さい変動にも適切に機能する。しかし、この回路の出力抵抗は大きく、さらに変動しやすいため、負荷電流も変化し、出力電圧には比較的大きく非線形の変動が起こる。したがって、負荷電流に比較的大きい変動があると、出力電圧において、許容範囲を超えて大きく、非線形の、制御する必要のある変動が起こる。図 4 に NMOS トランジスタ 16 をスイッチとして使用する、同じ回路のプルダウン版を示す。

30

【発明の開示】

【発明が解決しようとする課題】

【0012】

現在使われている電力変換装置はまた、次の二つの問題を抱えている。電流効率の低さ、および負荷電流の変化への対応が通常遅いという点である。

【0013】

負荷電流の変動が大きくなく大変速くもない場合は、既知の回路も十分に機能する。よ

40

50

り簡易的な回路では出力抵抗が大きいため、負荷電流の変動が大きすぎると出力における電圧中に大きなオフセットを引き起こす。このオフセットは、ダイオードスイッチとして機能するトランジスタを物理的に大きくすることによってのみ減少することができる。しかし、これは I C 配置上の限られた面積を大きく占拠してしまい、十分な対処法とはいえない。

#### 【 0 0 1 4 】

より複雑な既知の回路では、スイッチを大きくすることなく出力抵抗を減少させるために、増幅されたフィードバックを使用する。この場合、フィードバック増幅器のゲイン（増幅率）と等価な係数によって、スイッチの出力抵抗を減少させる。しかし、高ゲインのフィードバック増幅器は、次の二つの問題を引き起こす。一つは、回路のループゲインが高いため回路の安定性が下がり、回路を安定させるために何らかの形で補正が必要となる点である。ここでさらに、これに対処することにより回路速度が落ち、負荷電流が大変急速に変動すると回路は対応できない。二点目は、切換トランジスタは通常大型であるため、そのゲート容量もまた大きいという問題である。このため、フィードバック増幅器は、負荷電流が変動するたびにこのゲート容量を帶電および放電する比較的大量の電流を消費することになる。これにより、回路の電流効率が減少する。

10

#### 【 0 0 1 5 】

したがって、本発明の目的は、上記の問題を少なくとも実質的に緩和した、改良版の電圧変換回路を提供することである。本発明に係る回路は、既知の従来回路をオフセットを減少させるよう改良し、この改良された回路とフィードバック型電力変換器の組合せによつて低出力オフセット、高速および高電流効率を実現する。

20

#### 【課題を解決するための手段】

#### 【 0 0 1 6 】

本発明に係る電圧変換回路の一態様は、出力ノードと、第1増幅器と、前記出力ノードと前記第1増幅器の間に位置するPMOSトランジスタである第1トランジスタと、前記第1トランジスタと前記第1増幅器の間に位置する第2増幅器と、前記出力ノードと前記第1増幅器の間に位置するNMOSトランジスタである第2トランジスタと、前記第2トランジスタと前記第1増幅器の間に位置する第3増幅器と、を含み、前記第1増幅器が基準電圧と前記出力ノードにおける出力電圧とを入力するものであり、前記第2増幅器が前記第1増幅器からの出力と前記出力電圧とを入力するものであり、前記第3増幅器が前記第1増幅器からの出力と前記出力電圧とを入力するものであり、前記第2増幅器がプルアップ部を構成し、電流ソースに直列配列されたNMOSトランジスタを備え、前記第3増幅器がプルダウン部を構成し、電流シンクに直列配列されたPMOSトランジスタを備え、前記第1増幅器が第1ゲインステージを構成し、前記第2増幅器が第2ゲインステージを構成し、前記第1ゲインステージのゲインが前記第2ゲインステージのゲインより大きく、前記第2ゲインステージの帯域幅が前記第1ゲインステージの帯域幅より大きい、ことを特徴とする。

30

#### 【 0 0 1 7 】

上記電圧変換回路において、さらに、前記第1増幅器と前記第2増幅器との間に位置するレベルシフタ回路を含み、前記第1増幅器からの出力が前記レベルシフタ回路を介して前記第2増幅器に入力されるものである、ことが好ましい。また、前記第1増幅器が前記第2増幅器よりも低速である、ことが好ましい。また、前記第1増幅器が前記第2増幅器よりも消費電力が小さい、ことが好ましい。また、前記第1トランジスタの一方の端子が前記出力ノードと前記第2トランジスタの一方の端子とに接続されている、ことが好ましい。

40

#### 【発明を実施するための最良の形態】

#### 【 0 0 1 8 】

詳細を例示するために、図面を参照して本発明の実施の形態を説明する。

#### 【 0 0 1 9 】

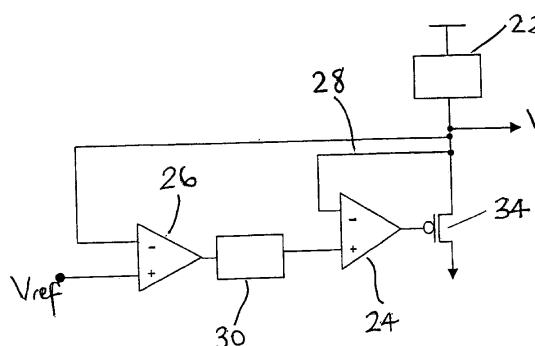

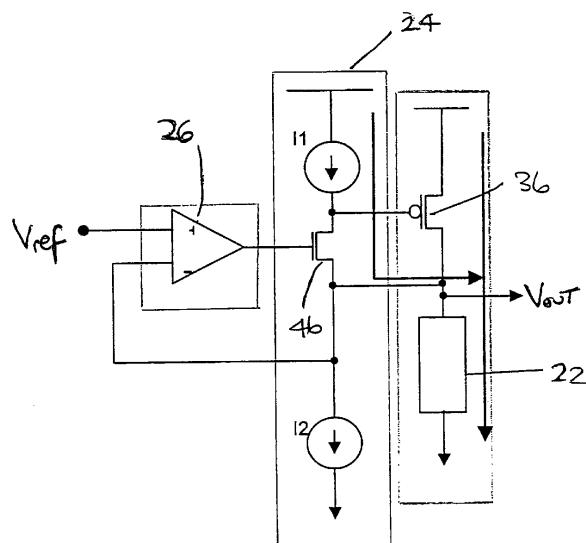

図5は、本発明に係るプルダウン電力変換回路の概念を示す。実質的に、この回路は、

50

負荷 2 2 を介して電流を調整する M O S スイッチ 2 0 と、M O S スイッチ 2 0 を制御する高速電流検出増幅器 2 4 と、高速電流検出増幅器 2 4 に対しバイアス電圧を与える高ゲインで比較的低速のフィードバック増幅器 2 6 とを含むと考えられる。したがって、ゲインについてはフィードバック増幅器 2 6 の方が高速電流検出増幅器 2 4 よりも高いが、帯域幅については高速で動作するその性能により高速電流検出増幅器 2 4 の方が、比較的低速のフィードバック増幅器 2 6 よりも広い。高速電流検出増幅器は、図 5 に示す例においては、制御可能な変換特性を備える。

#### 【 0 0 2 0 】

反転および非反転増幅器のいずれにも、変換特性として知られる入出力特性が備わっており、その中央部ではこの特性の傾斜により増幅器のゲインが与えられる。増幅器の入力電圧を  $V_{in}$ 、出力電圧を  $V_{out}$  とすると、この増幅器のゲインは次の式で求められる。

$V_{out}$  の変化 ÷  $V_{in}$  の変化

#### 【 0 0 2 1 】

この特性の中央部の各端部では、 $V_{in}$  が低すぎるまたは高すぎる場合、ゲインはゼロとなる。すなわち、 $V_{in}$  が多少増加または減少しても、 $V_{out}$  は実質的に変化しない。したがって、高ゲインの領域はこの特性の中央部であると考えられる。

#### 【 0 0 2 2 】

増幅器が制御可能な特性を備える場合、この技術においては、制御電圧  $V_{cont}$  を増加 / 減少（または減少 / 増加）することによりシフトする入出力特性を備えると考えられる。

#### 【 0 0 2 3 】

非反転増幅器の場合、 $V_{cont}$  が増加すると、変換特性は、この特性の高ゲイン中央部が  $V_{in}$  の値がより高い点にくるようシフトする。もちろん、増幅器の種類によっては、この特性の中央部が  $V_{in}$  の値がより低い点にくるようシフトするものもある。

#### 【 0 0 2 4 】

同じ原則が反転増幅器にも当てはまるが、変換特性は非反転増幅器の場合と比べて逆の傾斜を描く。

#### 【 0 0 2 5 】

図 5 に示す実施形態では、高速増幅器 2 4 は負荷電流を直接検出することにより動作し、スイッチトランジスタ 2 0 のゲートにおける電圧は、負荷電流の増加または減少に応じて増加または減少される。スイッチトランジスタ 2 0 には、負荷 2 2 への正確な電流量が流れ込み、出力電圧  $V_{out}$  が上昇するのを防ぐ。高速増幅器 2 4 の動作に必要な電流は、リンク 2 8 を介して負荷電流によって部分的に供給される。最小負荷電流が高速増幅器 2 4 に必要な電流よりも大きい場合、この高速増幅回路の電流消費全量は負荷 2 2 から流れ込み、回路の高速増幅器部による総電流消費をゼロとし、全体の電流効率が向上される。

#### 【 0 0 2 6 】

高速増幅器 2 4 の動作に必要なバイアス電圧は、ゲインは大変高いが比較的低速のフィードバック増幅器 2 6 によって適応的に生成される。回路のこの部分により、電力変換回路全体のオフセットが低く保たれる。電力変換器の出力電圧  $V_{out}$  が基準電圧  $V_{ref}$  と等価でない場合、これを差動増幅器としてのフィードバック増幅器 2 6 が検出すると、高速増幅器に与えられたバイアス電圧は出力電圧  $V_{out}$  が基準電圧  $V_{ref}$  と等価になるように制御される。フィードバック増幅器 2 6 は動作が大変遅いため、電力消費要件の長期平均をおこない、高速増幅器 2 4 のバイアス電圧を最適なレベルに維持するよう調整する。増幅器 2 6 は大変低速であるため、その電力消費も大変小さい。つまり、負荷によって少なくとも部分的に供給される比較的高速な増幅器 2 4 の動作に必要な電流と組み合わせると、回路全体の総電流消費は極めて小さく、回路全体の電流効率が大変高くなる。また、I C に組み込まれるこの回路に必要な面積は、図 1 に示す回路の面積よりも小さく、既知の線形電力変換器に比べてさらに有益である。

#### 【 0 0 2 7 】

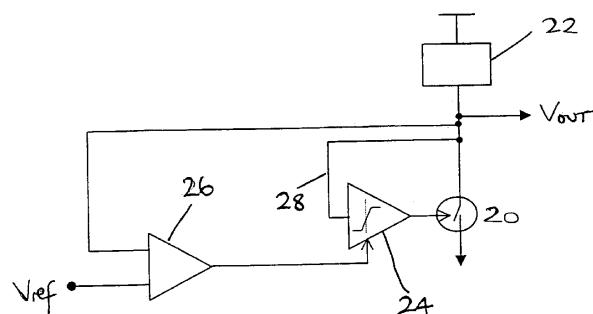

図 5 は、変換特性の負の傾斜として示される反転増幅器を含む高速増幅器 2 4 を備えた、プルアップ型線形電力変換器を示す。しかし、本発明の原則は、図 6 に示す高速増幅器

10

20

30

40

50

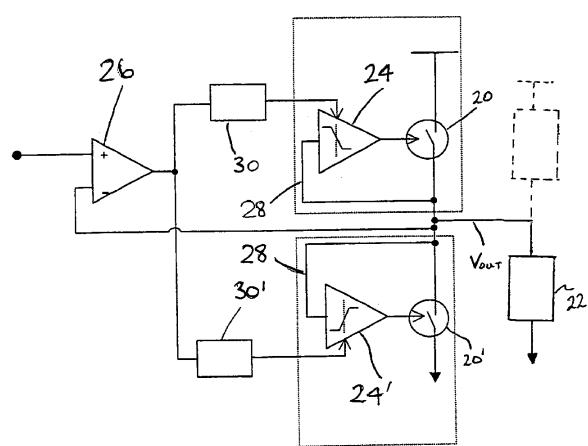

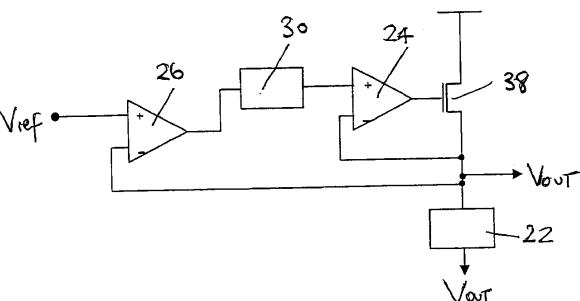

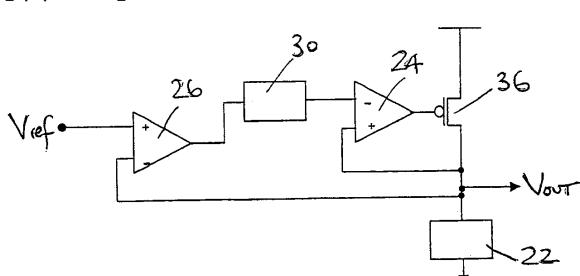

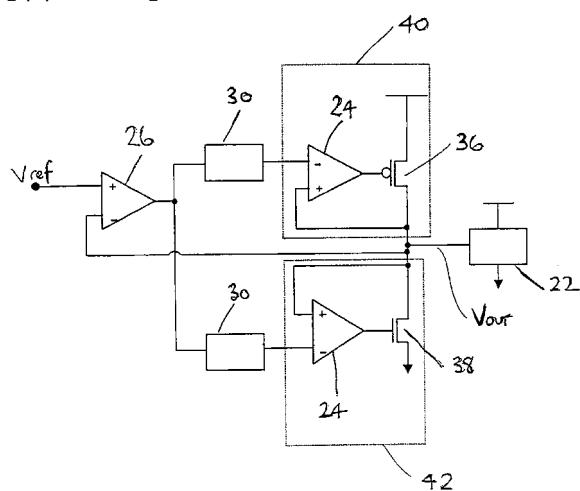

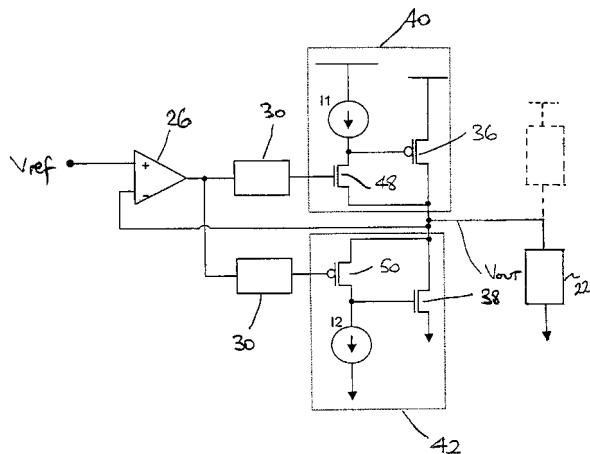

24として非反転型増幅器を使用しているプルダウン変換回路や、図7に示すプルアップおよびプルダウン機能を備えた電力変換器にも適用できる。図7に示されるように、高速増幅器において回路のプルアップおよびプルダウン部としてそれぞれ使用される反転および非反転増幅器は、高ゲイン増幅器26を共有し、高ゲイン増幅器26および高速増幅器24の間に、変換特性の高ゲイン部上での高増幅器24の動作を最適化するためのレベルシフタ回路30をそれぞれ備える。高ゲイン増幅器26を共有することにより、個別のプルアップおよびプルダウン変換器を使用する場合と比較し、特に高速増幅器の電流消費がリンク28を介して負荷からのものである場合に、回路効率が改善される。

#### 【0028】

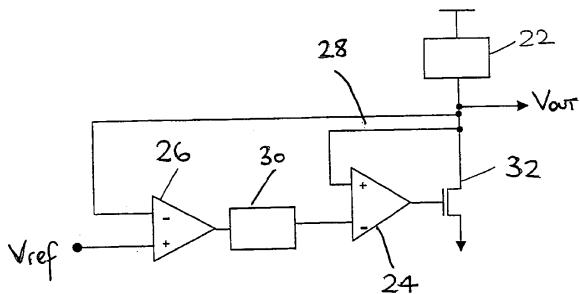

図8aおよび図8bは、それぞれ図5に示すプルアップ回路および図6に示すプルダウン回路の実装例を示す。図8aのプルアップ回路において、スイッチ20はN MOSトランジスタ32により実施される。図8bのプルダウン回路において、スイッチはP MOSトランジスタ34により実施される。これらの各回路例では、高速増幅器が高速差動増幅器として構成され、各回路は、高速増幅器が確実に変換特性の最適部上で動作するためのレベルシフタ回路を含む。

#### 【0029】

図9aは、スイッチとしてP MOSトランジスタ36を使用したプルアップ変換器の一例を示す。図9bは、スイッチとしてN MOSトランジスタ38を使用したプルダウン変換器の一例を示す。9aおよび9bに示す例は、高速増幅器24および高ゲイン増幅器26への入力が図8aおよび8bに示すものの反対である点を除き、図8aおよび8bに示す例と同じである。

#### 【0030】

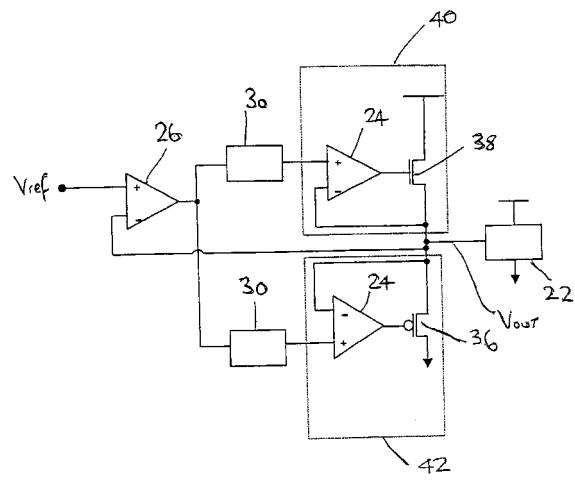

図10aは、プルアップおよびプルダウン機能を有する変換器の一例を示す。回路のプルアップ部40中のスイッチとしてP MOSトランジスタを使用し、回路のプルダウン部42中のスイッチとしてN MOSトランジスタを使用する。本例では、変換器のプルアップ部40およびプルダウン部42は高ゲイン増幅器26を共有する。

#### 【0031】

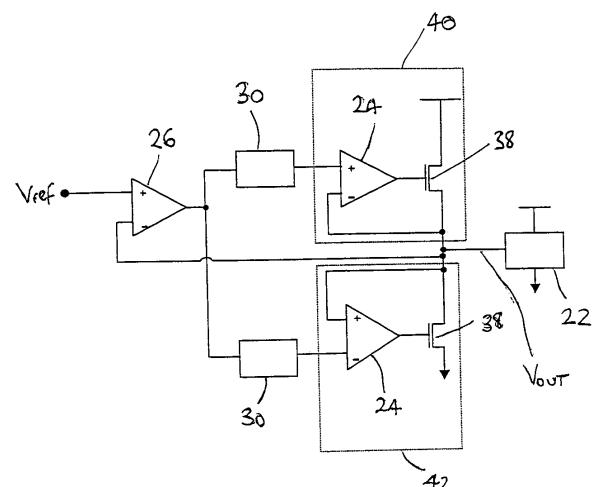

図10bもプルアップおよびプルダウン機能を有する変換器の一例を示す。ここでは回路のプルアップ部40中のスイッチとしてN MOSトランジスタを使用し、回路のプルダウン部42中のスイッチとしてP MOSトランジスタを使用する。本例においても、変換器のプルアップ部40およびプルダウン部42は高ゲイン増幅器26を共有する。しかし、本例では高速増幅器24に供給する差動増幅器の負の入力は、出力ノードに負荷22へと接続される。

#### 【0032】

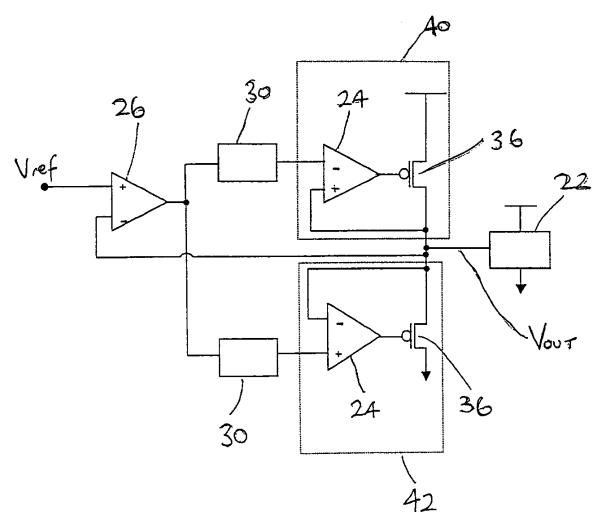

図10cは、プルアップおよびプルダウン機能を有する変換器の別の例を示す。ここでは回路のプルアップ部40および回路のプルダウン部42中のスイッチとしてN MOSトランジスタを使用する。本例では、プルアップ部高速増幅器の負の入力およびプルダウン部高速増幅器の正の入力が、ノードに負荷22へと接続される。

#### 【0033】

図10dは、プルアップおよびプルダウン機能を有する変換器のさらに別の例を示す。ここでは回路のプルアップ部40および回路のプルダウン部42中のスイッチとしてP MOSトランジスタを使用し、高速差動増幅器の正および負の入力に適切に接続される。

#### 【0034】

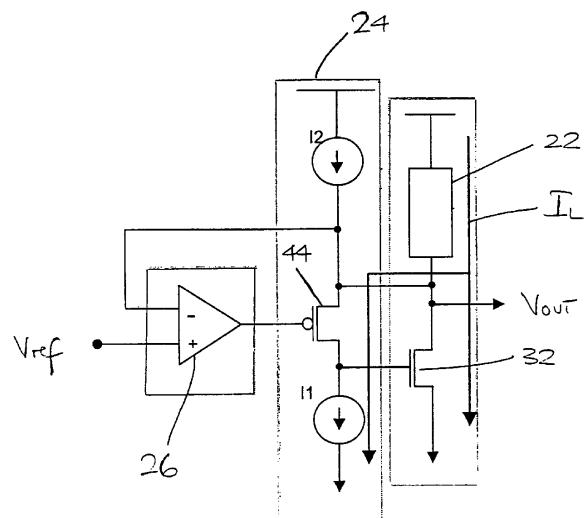

図11は、図8aに示す回路の実用的な実装を概略的に示す図であり、高速増幅器は電流シンクI1および電流ソースI2の間に直列配置されたP MOSトランジスタ44を備える。電流ソースI2からの電流値は、電流シンクI1に流れ込む電流、つまり負荷電流 $I_L$ の最小期待値よりもわずかに大きい。これはいかなる状態においても、高速増幅器24の適切な動作を保証するためである。しかし、一般的には、負荷電流の最小期待値は電流シンクI1から供給される電流よりも大きいことが知られており、したがって電流ソースI2は必ずしも必要ではない。このような場合、回路は高ゲイン増幅器26が必要とす

10

20

30

40

50

る電流のみを消費する。つまり、高ゲイン増幅器は低速で動作するため、消費量は大変少ない。したがって、このような状況において、回路全体の電流効率は大変高い。

#### 【0035】

図12は、図9aに示す回路の実用的な実装を概略的に示す図であり、高速増幅器24は電流ソースI1および電流シンクI2の間に直列配置されたN MOSトランジスタ46を備える。本例において、I2の値はI1、すなわち負荷電流の最小期待値よりもわずかに大きくなるよう構成される。図11に示す回路と同様に、負荷電流の最小期待値はI1よりも大きく、したがって電流シンクI2は必ずしも必要ではない。この状況においても、回路は高ゲイン増幅器26が必要とする電流のみを消費する。つまり、消費量は大変少なく、回路全体の効率は大変高い。

10

#### 【0036】

図13は、図10aに示す回路の実用的な実装を示す。これはプルアップおよびプルダウン機能を備える。本例では、回路40のプルアップ部の高速増幅器は、電流ソースI1に直列配置されたN MOSトランジスタを備え、この回路のプルダウン部の高速増幅器は、電流シンクI2に直列配置されたPMOSトランジスタを備える。図11に示すプルダウン変換器または図12に示すプルアップ変換器と違い、I1およびI2からの電流は回路のいかなる動作中にも流れ続ける。これにより図11および図12に示す回路と比較し電流効率が落ちるが、それでも従来回路と比較すると電流効率は大変高い。これは、両高速増幅器24が高ゲインフィードバック増幅器26を共有し、I1およびI2の値がいずれも負荷電流を下回るからである。

20

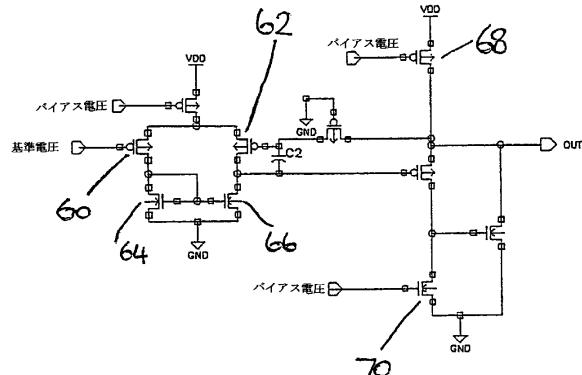

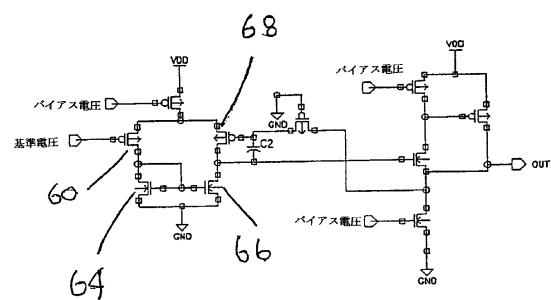

#### 【0037】

図14は、図11に示すプルダウン変換器の実用的な実装を示す。高ゲインフィードバック増幅器26は、単純差動対であるPMOSトランジスタ60および62、ならびにNMOSトランジスタ64および66で構成される。また、高速増幅器24の電流ソースおよび電流ドレインとして、単純PMOSトランジスタ68およびNMOSトランジスタ70を備える。本例では、フィードバック増幅器26は、ミラー補償によって安定化される。

#### 【0038】

図15は、図12に示すプルアップ変換回路の実用的な実装を示す。図14に示す回路と同様に、フィードバック増幅器は単純差動対であり、高速増幅器の電流ソースおよび電流ドレインは単純PMOSおよびNMOSトランジスタからなる。

30

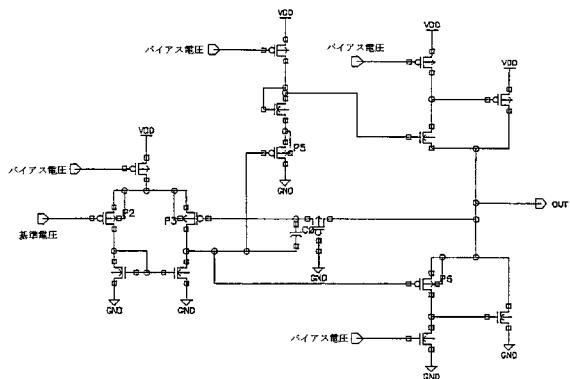

#### 【0039】

図16は、図13に示す回路の実用的な実装を示し、プルアップおよびプルダウン機能を備える。高ゲインフィードバック増幅器および高速増幅器は、図13および図14に示す回路と同様の回路部品によって製造される。しかし、本実装においては、レベルシフタ回路を使用し、回路のプルアップおよびプルダウン高速部の両方を同一のフィードバック増幅器により制御する。

#### 【0040】

本発明は、いかなる設計の電圧変換器にも適用可能であるが、特に負荷電流が大変高く速い場合の用途に適する。これには、デジタルスイッチを電圧変換器によって制御する必要のある場合も含まれる。本変換回路はまた、ICの設計において省スペース要件を満たすための大変高い電流効率を提供する。

40

#### 【0041】

本回路は、用途が大変広く、線形電力調整器が必要な用途に使用可能である。これには内蔵ICのあらゆる用途が含まれる。

#### 【0042】

本書の記載はあくまで一例示であり、本発明はその範囲から逸脱することなく、当業者の知識に基づき変更を加えて実施可能である。

#### 【図面の簡単な説明】

#### 【0043】

【図1】既知のフィードバック補助プルダウン電力変換回路を示す。

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8 a】

【図8 b】

【図9 b】

【図9 a】

【図10 a】

【図 10 b】

【図 10 c】

【図 10 d】

【図 11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(72)発明者 サイモン タム

イギリス ケンブリッジ C B 4 0 F E 9 a ケンブリッジ サイエンスパーク ミルトンロード エプソンケンブリッジ研究所内

審査官 畑中 博幸

(56)参考文献 実開昭 55-112714 (JP, U)

特開昭 62-239607 (JP, A)

特開 2002-157031 (JP, A)

特開平 02-150912 (JP, A)

特開平 01-223520 (JP, A)

特開 2001-159922 (JP, A)

特開平 05-216548 (JP, A)

特開昭 57-157313 (JP, A)

特開昭 63-211414 (JP, A)

特開平 09-120317 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 03 F 3 / 34

G 05 F 1 / 56