(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-283822

(P2009-283822A)

(43) 公開日 平成21年12月3日(2009.12.3)

(51) Int.Cl.

H01S 5/227 (2006.01)

H01S 5/323 (2006.01)

F 1

H01S 5/227

H01S 5/323

テーマコード(参考)

5 F 1 7 3

審査請求 未請求 請求項の数 4 O L (全 11 頁)

(21) 出願番号

特願2008-136513 (P2008-136513)

(22) 出願日

平成20年5月26日 (2008.5.26)

(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

100082175

弁理士 高田 守

100106150

弁理士 高橋 英樹

瀧口 透

東京都千代田区丸の内二丁目7番3号 三

菱電機株式会社内

奥貫 雄一郎

東京都千代田区丸の内二丁目7番3号 三

菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体レーザ及びその製造方法

## (57) 【要約】

【課題】10 Gbps 以上の高速変調が可能な半導体レーザを得る。

【解決手段】p型InPクラッド層12(p型クラッド層)、AlGaInAs歪量子井戸活性層14(活性層)及びn型InPクラッド層16(n型クラッド層)が積層されたリッジ構造18が形成されている。リッジ構造18の両側は埋込層20で埋め込まれている。埋込層20は、pn接合30を構成する低キャリア濃度p型InP層26(p型半導体層)とn型InP層24(n型半導体層)を有する。低キャリア濃度p型InP層26のpn接合近辺のキャリア濃度は $5 \times 10^{17} \text{ cm}^{-3}$ 以下である。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

p型クラッド層、活性層及びn型クラッド層が積層されたリッジ構造と、前記リッジ構造の両側を埋め込む埋込層とを備え、前記埋込層は、pn接合を構成するp型半導体層及びn型半導体層を有し、前記p型半導体層又は前記n型半導体層の前記pn接合近辺のキャリア濃度は $5 \times 10^{17} \text{ cm}^{-3}$ 以下であることを特徴とする半導体レーザ。

## 【請求項 2】

p型クラッド層、活性層及びn型クラッド層を積層した積層体を形成する工程と、前記積層体をエッチングしてリッジ構造を形成する工程と、前記リッジ構造の両側を埋込層で埋め込む工程とを備え、前記埋込層として、p型半導体層とn型半導体層の間にアンドープ半導体層を挿入した構造を形成し、前記アンドープ半導体層に、前記p型半導体からp型ドーパントを拡散させて、キャリア濃度が $5 \times 10^{17} \text{ cm}^{-3}$ 以下のp型の半導体層にすることを特徴とする半導体レーザの製造方法。

## 【請求項 3】

前記アンドープ半導体層として、アンドープInP層、アンドープInGaAsP層、アンドープAlInAs層の何れかを形成することを特徴とする請求項2に記載の半導体レーザの製造方法。

## 【請求項 4】

p型クラッド層、活性層及びn型クラッド層を順番に積層した積層体を形成する工程と、前記積層体をエッチングしてリッジ構造を形成する工程と、前記リッジ構造の両側を埋込層で埋め込む工程とを備え、前記埋込層として、p型InP層、n型InP層、半絶縁性FeドープAl(Ga)InAs層、半絶縁性FeドープInP層を順番に積層し、前記半絶縁性FeドープInP層を形成した後に、前記半絶縁性FeドープAl(Ga)InAs層を表面に露出させないことを特徴とする半導体レーザの製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、リッジ構造の両側を埋込層で埋め込んだ埋込型の半導体レーザ及びその製造方法に関するものである。

## 【背景技術】

## 【0002】

埋込型の半導体レーザの埋込層として、pn接合を有するものや、半絶縁性InP層を有するものが提案されている。また、半絶縁性InP層を有する埋込層におけるリーク電流を抑制するために、埋込層に半絶縁性Al(Ga)InAs層を更に設けた半導体レーザが提案されている(例えば、特許文献1参照)。

## 【特許文献1】特開平8-255950号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0003】

最近、10Gbps以上の高速変調で使用するレーザ半導体が強く求められている。しかし、pn接合を有する埋込層を持つ従来のレーザでは、埋込層におけるpn接合容量が大きく、10Gbps以上の高速変調が不可能であった。

## 【0004】

また、特許文献1では、埋込層を形成した後に、半絶縁性FeドープAl(Ga)InAs層は表面に露出され、酸化される。酸化された半絶縁性FeドープAl(Ga)InAs層

10

20

30

40

50

A s 層の上に別の半導体層を成長させても、正常に成長されず、欠陥や表面の凹凸が発生する。この結果、半導体レーザの特性が低下し、歩留まりが低下するという問題があった。

### 【0005】

本発明は、上述のような課題を解決するためになされたもので、第1の目的は、10Gbps以上の高速変調が可能な半導体レーザ及びその製造方法を得るものである。

### 【0006】

本発明の第2の目的は、リーク電流が少なく、高速変調が可能な半導体レーザを歩留まり良く得ることができる半導体レーザの製造方法を得るものである。

### 【課題を解決するための手段】

### 【0007】

第1の発明は、p型クラッド層、活性層及びn型クラッド層が積層されたリッジ構造と、前記リッジ構造の両側を埋め込む埋込層とを備え、前記埋込層は、pn接合を構成するp型半導体層及びn型半導体層を有し、前記p型半導体層又は前記n型半導体層の前記pn接合近辺のキャリア濃度は $5 \times 10^{17} \text{ cm}^{-3}$ 以下であることを特徴とする半導体レーザである。

### 【0008】

第2の発明は、p型クラッド層、活性層及びn型クラッド層を積層した積層体を形成する工程と、前記積層体をエッチングしてリッジ構造を形成する工程と、前記リッジ構造の両側を埋込層で埋め込む工程とを備え、前記埋込層として、p型半導体層とn型半導体層の間にアンドープ半導体層を挿入した構造を形成し、前記アンドープ半導体層に、前記p型半導体からp型ドーパントを拡散させて、キャリア濃度が $5 \times 10^{17} \text{ cm}^{-3}$ 以下のp型の半導体層にすることを特徴とする半導体レーザの製造方法である。

### 【0009】

第3の発明は、p型クラッド層、活性層及びn型クラッド層を順番に積層した積層体を形成する工程と、前記積層体をエッチングしてリッジ構造を形成する工程と、前記リッジ構造の両側を埋込層で埋め込む工程とを備え、前記埋込層として、p型InP層、n型InP層、半絶縁性FeドープAl(Ga)InAs層、半絶縁性FeドープInP層を順番に積層し、前記埋込層を形成した後に、前記半絶縁性FeドープAl(Ga)InAs層を表面に露出させないことを特徴とする半導体レーザの製造方法である。

### 【発明の効果】

### 【0010】

第1の発明により、10Gbps以上の高速変調が可能な半導体レーザを得ることができる。第2の発明により、10Gbps以上の高速変調が可能な半導体レーザの製造方法を得ることができる。第3の発明により、リーク電流が少なく、高速変調が可能な半導体レーザを歩留まり良く得ることができる。

### 【発明を実施するための最良の形態】

### 【0011】

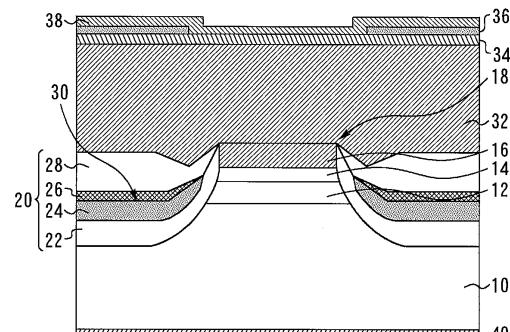

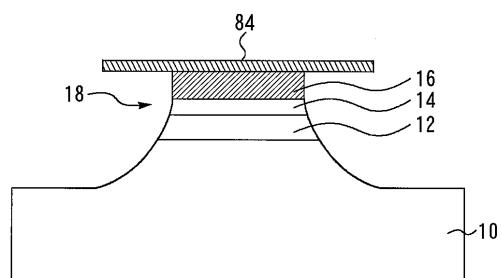

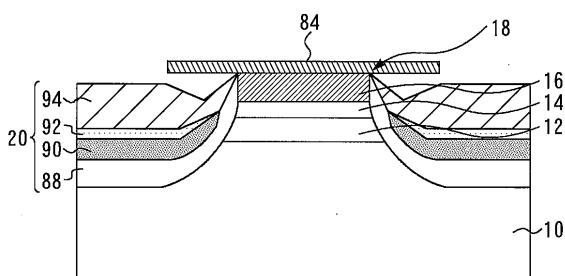

実施の形態1.

図1は、本発明の実施の形態1に係る半導体レーザを示す断面図である。p型InP基板10(半導体基板)上に、p型InPクラッド層12(p型クラッド層)、AlGaInAs歪量子井戸活性層14(活性層)及びn型InPクラッド層16(n型クラッド層)が順番に積層されたリッジ構造18が形成されている。ここで、p型InPクラッド層12のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ 、n型InPクラッド層16のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ である。

### 【0012】

リッジ構造18の両側は埋込層20で埋め込まれている。埋込層20は、下から順番に、p型InP層22、n型InP層24、低キャリア濃度p型InP層26、p型InP層28を有する。低キャリア濃度p型InP層26(p型半導体層)とn型InP層24(n型半導体層)がpn接合30を構成する。ここで、p型InP層22のキャリア濃度

10

20

30

40

50

は  $1 \times 10^{18} \text{ cm}^{-3}$ 、n型InP層24のキャリア濃度は  $1 \times 10^{19} \text{ cm}^{-3}$ 、低キャリア濃度p型InP層26のキャリア濃度は  $1 \times 10^{17} \text{ cm}^{-3}$ 、p型InP層28のキャリア濃度は  $1 \times 10^{18} \text{ cm}^{-3}$ である。

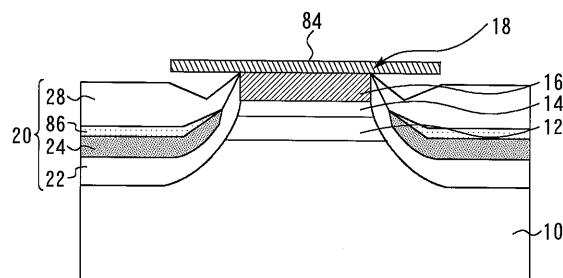

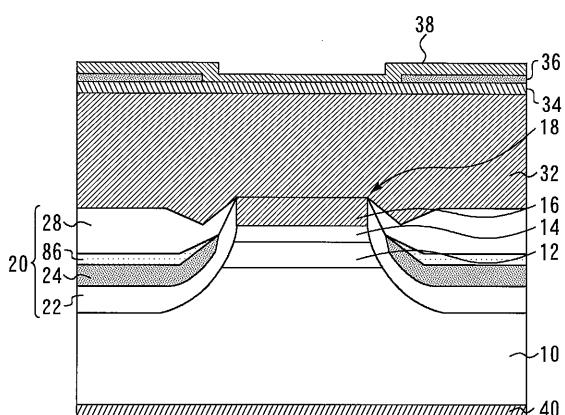

#### 【0013】

リッジ構造18及び埋込層20の上にn型InP層32、n型InPコンタクト層34、SiO<sub>2</sub>絶縁膜36、Ti/Pt/Auのn型電極38が順番に形成されている。p型InP基板10の下面にTi/Pt/Auのp型電極40が形成されている。ここで、n型InP層32のキャリア濃度は  $1 \times 10^{18} \text{ cm}^{-3}$ 、n型InPコンタクト層34のキャリア濃度は  $1 \times 10^{19} \text{ cm}^{-3}$ である。

#### 【0014】

本発明の実施の形態1に係る半導体レーザの効果について、従来の半導体レーザと比較して説明する。図2は、従来の半導体レーザを示す断面図である。従来の半導体レーザでは、低キャリア濃度p型InP層26が存在しないため、p型InP層28とn型InP層24がpn接合42を構成する。このpn接合42のp型キャリア濃度は  $1 \times 10^{18} \text{ cm}^{-3}$ であり、n型キャリア濃度は  $1 \times 10^{19} \text{ cm}^{-3}$ である。その他の構成は、実施の形態1の半導体レーザと同様である。

#### 【0015】

半導体レーザの駆動時において埋込層20のpn接合には逆バイアスが印加される。このpn接合の容量Cは下式で計算される。

#### 【0016】

#### 【数1】

$$C = S \times \sqrt{\frac{\epsilon_r \times \epsilon_0 \times e}{2 \times \left( \frac{1}{N_d} + \frac{1}{N_a} \right) \times V_{built}}}$$

S : pn接合面積、r : 比誘電率、o : 真空誘電率、Nd : n型キャリア濃度、Na : p型キャリア濃度、V<sub>built</sub> : ビルトイン・ポテンシャル

#### 【0017】

従来の半導体レーザでは、pn接合42の容量Cは2.8pF、遮断周波数f<sub>c</sub>は9GHzであり、10Gbps以上の高速変調には不十分である。一方、本実施の形態に係る半導体レーザでは、低キャリア濃度p型InP層26を挿入してpn接合30のp型キャリア濃度を従来の  $1 \times 10^{18} \text{ cm}^{-3}$ から  $1 \times 10^{17} \text{ cm}^{-3}$ に低減している。このため、pn接合30の容量Cを0.9pFに低減することができ、遮断周波数f<sub>c</sub>は22GHzとなるため、10Gbps以上の高速変調が可能となる。

#### 【0018】

なお、低キャリア濃度p型InP層26のキャリア濃度が低いほどpn接合30の容量を下げることができ、高速変調が可能となるが、pn接合近辺のキャリア濃度が  $5 \times 10^{17} \text{ cm}^{-3}$ 以下であれば十分な効果が得られる。

#### 【0019】

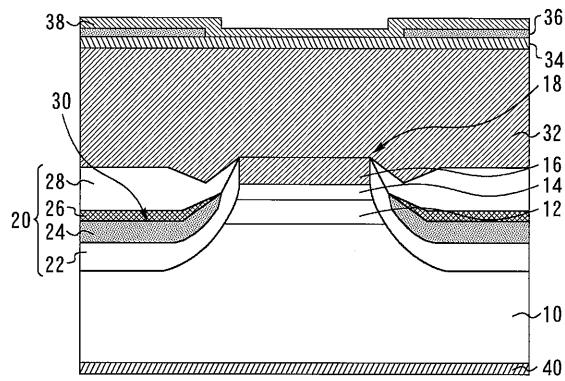

#### 実施の形態2.

図3は、本発明の実施の形態2に係る半導体レーザを示す断面図である。低キャリア濃度p型InP層26の代わりに低キャリア濃度n型InP層44を設けている。低キャリア濃度n型InP層44のキャリア濃度は  $1 \times 10^{17} \text{ cm}^{-3}$ である。p型InP層28(p型半導体層)と低キャリア濃度n型InP層44(n型半導体層)がpn接合46を構成する。その他の構成は実施の形態1と同様である。

#### 【0020】

本実施の形態に係る半導体レーザでは、低キャリア濃度n型InP層44を挿入してpn接合46のn型キャリア濃度を従来の  $1 \times 10^{19} \text{ cm}^{-3}$ から  $1 \times 10^{17} \text{ cm}^{-3}$ に低減している。このため、pn接合46の容量Cを0.9pFに低減することができ、遮断周波数f<sub>c</sub>は22GHzとなるため、10Gbps以上の高速変調が可能となる。

10

20

30

40

50

## 【0021】

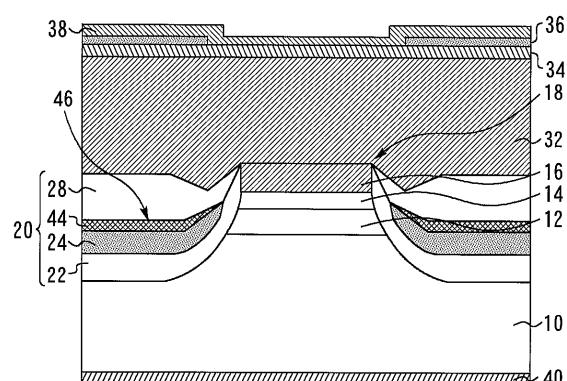

## 実施の形態3.

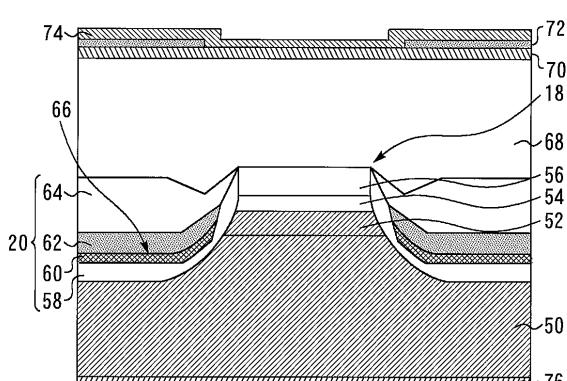

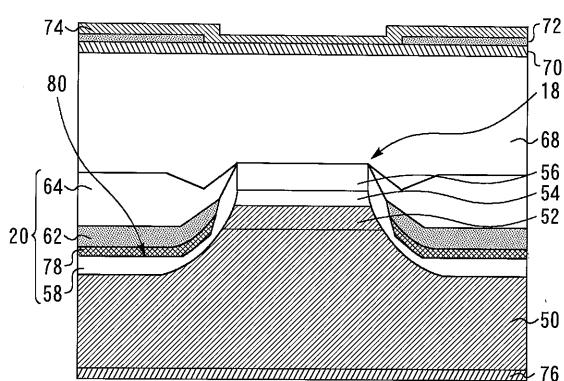

図4は、本発明の実施の形態3に係る半導体レーザを示す断面図である。実施の形態1とは基板の導電型が異なる。

## 【0022】

n型InP基板50(半導体基板)上に、n型InPクラッド層52(n型クラッド層)、AlGaInAs歪量子井戸活性層54(活性層)及びp型InPクラッド層56(p型クラッド層)が順番に積層されたリッジ構造18が形成されている。ここで、n型InPクラッド層52のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ 、p型InPクラッド層56のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ である。10

## 【0023】

リッジ構造18の両側は埋込層20で埋め込まれている。埋込層20は、下から順番に、p型InP層58、低キャリア濃度p型InP層60、n型InP層62、p型InP層64を有する。低キャリア濃度p型InP層60(p型半導体層)とn型InP層62(n型半導体層)がpn接合66を構成する。ここで、p型InP層58のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ 、低キャリア濃度p型InP層60のキャリア濃度は $1 \times 10^{17} \text{ cm}^{-3}$ 、n型InP層62のキャリア濃度は $1 \times 10^{19} \text{ cm}^{-3}$ 、p型InP層64のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ である。

## 【0024】

リッジ構造18及び埋込層20の上にp型InP層68、p型InGaAsコンタクト層70、SiO<sub>2</sub>絶縁膜72、Ti/Pt/Auのp型電極74が順番に形成されている。n型InP基板50の下面にTi/Pt/Auのn型電極76が形成されている。ここで、p型InP層68のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ 、p型InGaAsコンタクト層70のキャリア濃度は $1 \times 10^{19} \text{ cm}^{-3}$ である。20

## 【0025】

本実施の形態に係る半導体レーザでは、低キャリア濃度p型InP層60を挿入してpn接合66のp型キャリア濃度を従来の $1 \times 10^{18} \text{ cm}^{-3}$ から $1 \times 10^{17} \text{ cm}^{-3}$ に低減している。このため、pn接合66の容量Cを0.9pFに低減することができ、遮断周波数fcは22GHzとなるため、10Gbps以上の高速変調が可能となる。

## 【0026】

## 実施の形態4.

図5は、本発明の実施の形態4に係る半導体レーザを示す断面図である。低キャリア濃度p型InP層60の代わりに低キャリア濃度n型InP層78を設けている。低キャリア濃度n型InP層78のキャリア濃度は $1 \times 10^{17} \text{ cm}^{-3}$ である。p型InP層58(p型半導体層)と低キャリア濃度n型InP層78(n型半導体層)がpn接合80を構成する。その他の構成は実施の形態3と同様である。30

## 【0027】

本実施の形態に係る半導体レーザでは、低キャリア濃度n型InP層78を挿入してpn接合80のn型キャリア濃度を従来の $1 \times 10^{19} \text{ cm}^{-3}$ から $1 \times 10^{17} \text{ cm}^{-3}$ に低減している。このため、pn接合80の容量Cを0.9pFに低減することができ、遮断周波数fcは22GHzとなるため、10Gbps以上の高速変調が可能となる。40

## 【0028】

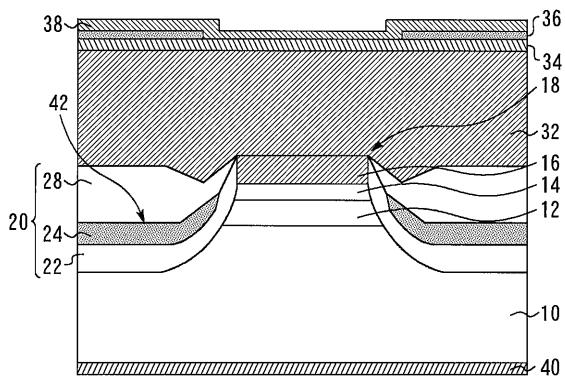

## 実施の形態5.

本発明の実施の形態5に係る半導体レーザの製造方法について図面を参照しながら説明する。

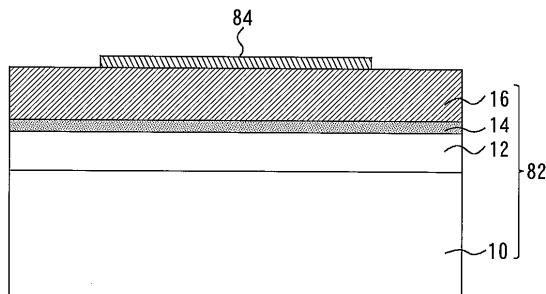

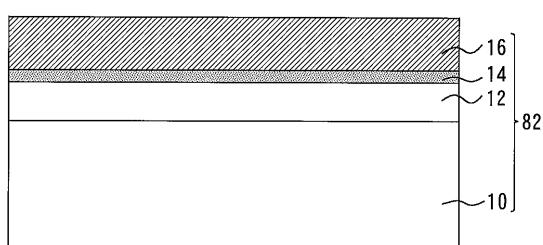

## 【0029】

まず、図6に示すように、p型InP基板10(半導体基板)上に、p型InPクラッド層12(p型クラッド層)、AlGaInAs歪量子井戸活性層14(活性層)及びn型InPクラッド層16(n型クラッド層)を積層した積層体82をMOCVD法により形成する。50

## 【0030】

次に、図7に示すように、n型InPクラッド層16上にSiO<sub>2</sub>絶縁膜84を形成し、パターニングする。そして、図8に示すように、SiO<sub>2</sub>絶縁膜84をマスクとして用いたウェットエッティング等により、積層体82をエッティングしてリッジ構造18を形成する。

## 【0031】

次に、図9に示すように、リッジ構造18の両側を埋込層20で埋め込む。ここでは、埋込層20として、下から順番に、p型InP層22、n型InP層24(n型半導体層)、アンドープInP層86(アンドープ半導体層)、p型InP層28(p型半導体層)をMOCVD法により形成する。

10

## 【0032】

次に、図10に示すように、SiO<sub>2</sub>絶縁膜84をエッティング除去した後に、リッジ構造18及び埋込層20の上にn型InP層32、n型InPコンタクト層34を順番にMOCVD法により形成し、その上にSiO<sub>2</sub>絶縁膜36、Ti/Pt/Auのn型電極38を形成する。p型InP基板10の下面にTi/Pt/Auのp型電極40を形成する。

## 【0033】

その後、アンドープInP層86に、p型InP層28からp型ドーパント(例えばZn)を拡散させて、キャリア濃度が $5 \times 10^{17} \text{ cm}^{-3}$ 以下のp型の半導体層にする。これにより、実施の形態1に係る半導体レーザと同様の構造の半導体レーザが製造される。従って、実施の形態1と同様の効果を得ることができる。

20

## 【0034】

なお、アンドープ半導体層として、アンドープInP層86の代わりに、アンドープInGaAsP層やアンドープAlInAs層を用いてもよい。InGaAsP層は、InP層に比べp型ドーパントの拡散係数が小さいので、キャリア濃度を低くすることができる。また、AlInAs層は、InGaAsP層に比べp型ドーパントの拡散係数が更に小さいので、更にキャリア濃度を低くすることができる。

## 【0035】

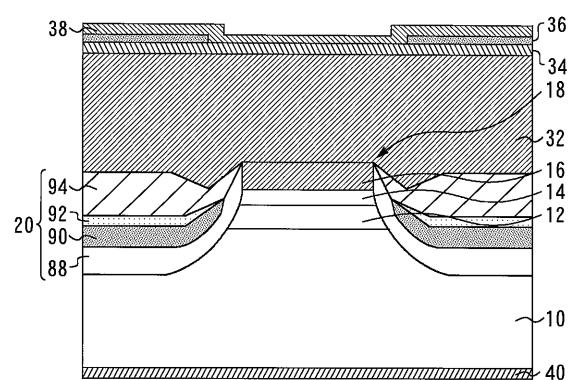

実施の形態6。

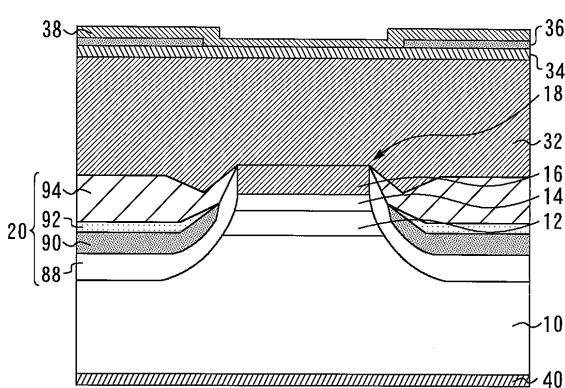

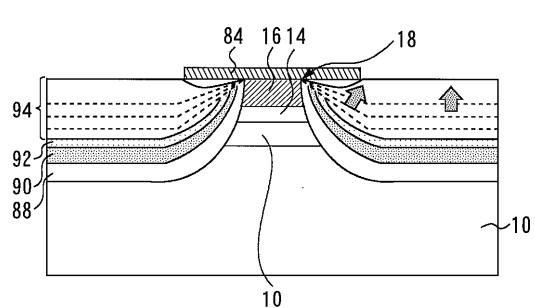

図11は、本発明の実施の形態6に係る半導体レーザを示す断面図である。実施の形態1に係る半導体レーザと同じ構成要素には同じ符号を付し、説明を省略する。

30

## 【0036】

リッジ構造18の両側は埋込層20で埋め込まれている。埋込層20は、下から順番に、p型InP層88、n型InP層90、半絶縁性FeドープAl(Ga)InAs層92、半絶縁性FeドープInP層94を有する。ここで、p型InP層88のキャリア濃度は $1 \times 10^{18} \text{ cm}^{-3}$ 、n型InP層90のキャリア濃度は $1 \times 10^{19} \text{ cm}^{-3}$ 、半絶縁性FeドープAl(Ga)InAs層92のキャリア濃度は $8 \times 10^{16} \text{ cm}^{-3}$ 、半絶縁性FeドープInP層94のキャリア濃度は $8 \times 10^{16} \text{ cm}^{-3}$ )である。

## 【0037】

本実施の形態に係る半導体レーザでは、半絶縁性FeドープInP層94を埋込層20に用いているので、埋込層20の容量を0.1pFと非常に小さな値に低減でき、より高速な変調が可能となる。また、InPよりバンドギャップが大きい半絶縁性FeドープAl(Ga)InAs層92を埋込層20に挿入しているため、電子のオーバーフローを抑制して、埋込層20を縦方向に貫通するリーク電流を抑制することができる。

40

## 【0038】

本実施の形態6に係る半導体レーザの製造方法について図面を参照しながら説明する。まず、実施の形態5と同様に図6～図8の工程を行ってリッジ構造18を形成する。

## 【0039】

次に、図12に示すように、リッジ構造18の両側を埋込層20で埋め込む。ここでは、埋込層20として、下から順番に、p型InP層88、n型InP層90、半絶縁性Fe

50

eドープAl(Ga)InAs層92、半絶縁性FeドープInP層94をMOCVD法により形成する。

【0040】

次に、図13に示すように、 $\text{SiO}_2$ 絶縁膜84をエッチング除去した後に、リッジ構造18及び埋込層20の上にn型InP層32、n型InPコンタクト層34を順番にMOCVD法により形成し、その上に $\text{SiO}_2$ 絶縁膜36、Ti/Pt/Auのn型電極38を形成する。p型InP基板10の下面にTi/Pt/Auのp型電極40を形成する。以上の工程により、本実施の形態に係る半導体レーザが製造される。

【0041】

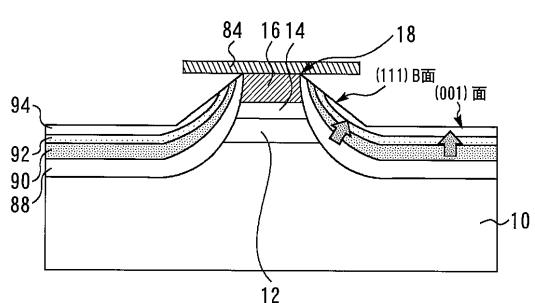

本実施の形態の特徴は、図11に示すように、半絶縁性FeドープInP層94を形成した後に、半絶縁性FeドープAl(Ga)InAs層92を表面に露出させないことがある。このような埋込層20の成長について更に詳細に説明する。

【0042】

まず、図14に示すように、p型InP層88、n型InP層90、半絶縁性FeドープAl(Ga)InAs層92は、(001)面から上方向に、そしてリッジ構造18の側面から横方向に、それぞれ結晶成長していく。ただし、これらの半導体層は、(111)B面上には成長しない。

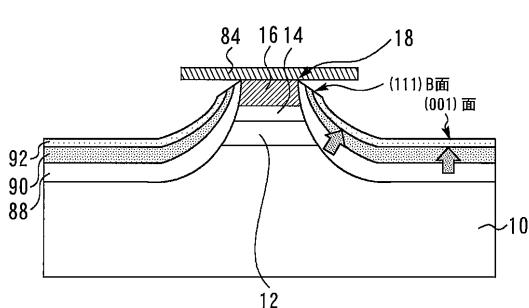

【0043】

次に、図15に示すように、半絶縁性FeドープInP層94の結晶成長が進むと、(111)B面と(001)面が出会い、半絶縁性FeドープInP層94の成長表面が(111)B面と(001)面のみになる。

【0044】

次に、図16に示すように、(001)面上だけでなく、(111)B面上でも半絶縁性FeドープInP層94の成長が始まる。

【0045】

このように(111)B面と(001)面が出会う前に、半絶縁性FeドープAl(Ga)InAs埋込層20を成長し終えれば、半絶縁性FeドープAl(Ga)InAs層92を、表面に露出させることなく、半絶縁性FeドープInP層94で完全にカバーすることができる。

【0046】

よって、本実施の形態では、半絶縁性FeドープInP層94を形成した後に、半絶縁性FeドープAl(Ga)InAs層92を表面に露出させないため、半絶縁性FeドープAl(Ga)InAs層92の酸化を防ぐことができる。従って、半絶縁性FeドープAl(Ga)InAs層92上にn型InP層32を欠陥無く正常に成長させることができたため、リーク電流が少なく、高速変調が可能な半導体レーザを歩留まり良く得ることができる。

【図面の簡単な説明】

【0047】

【図1】本発明の実施の形態1に係る半導体レーザを示す断面図である。

【図2】従来の半導体レーザを示す断面図である。

【図3】本発明の実施の形態2に係る半導体レーザを示す断面図である。

【図4】本発明の実施の形態3に係る半導体レーザを示す断面図である。

【図5】本発明の実施の形態4に係る半導体レーザを示す断面図である。

【図6】本発明の実施の形態5に係る半導体レーザの製造方法を説明するための断面図である。

【図7】本発明の実施の形態5に係る半導体レーザの製造方法を説明するための断面図である。

【図8】本発明の実施の形態5に係る半導体レーザの製造方法を説明するための断面図である。

【図9】本発明の実施の形態5に係る半導体レーザの製造方法を説明するための断面図である。

10

20

30

40

50

ある。

【図10】本発明の実施の形態5に係る半導体レーザの製造方法を説明するための断面図である。

【図11】本発明の実施の形態6に係る半導体レーザを示す断面図である。

【図12】本発明の実施の形態6に係る半導体レーザの製造方法を説明するための断面図である。

【図13】本発明の実施の形態6に係る半導体レーザの製造方法を説明するための断面図である。

【図14】本発明の実施の形態6に係る半導体レーザの製造方法を説明するための断面図である。 10

【図15】本発明の実施の形態6に係る半導体レーザの製造方法を説明するための断面図である。

【図16】本発明の実施の形態6に係る半導体レーザの製造方法を説明するための断面図である。

【符号の説明】

【0048】

12, 56 p型InPクラッド層 (p型クラッド層)

14, 54 AlGaInAs歪量子井戸活性層 (活性層)

16, 52 n型InPクラッド層 (n型クラッド層)

18 リッジ構造

20 埋込層

24, 62 n型InP層 (n型半導体層)

26, 60 低キャリア濃度p型InP層 (p型半導体層)

28, 58 p型InP層 (p型半導体層)

30, 46, 66, 80 pn接合

44, 78 低キャリア濃度n型InP層 (n型半導体層)

86 アンドープInP層 (アンドープ半導体層)

88 p型InP層

90 n型InP層

92 半絶縁性FeドープAl(Ga)InAs層

94 半絶縁性FeドープInP層

10

20

30

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 15】

【図 14】

【図 16】

---

フロントページの続き

(72)発明者 境野 剛

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

F ターク(参考) 5F173 AA26 AF84 AF92 AF98 AF99 AH30 AP05 AP16 AP17 AP32

AP53 AR36 AR61 AR65 AR93