(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3912937号

(P3912937)

(45) 発行日 平成19年5月9日(2007.5.9)

(24) 登録日 平成19年2月9日(2007.2.9)

(51) Int.C1.

F 1

G 11 C 16/04 (2006.01)

G 11 C 16/02 (2006.01)G 11 C 17/00 621 A

G 11 C 17/00 641

請求項の数 10 (全 18 頁)

(21) 出願番号

特願平11-226913

(22) 出願日

平成11年8月10日(1999.8.10)

(65) 公開番号

特開2001-57093 (P2001-57093A)

(43) 公開日

平成13年2月27日(2001.2.27)

審査請求日

平成16年9月17日(2004.9.17)

(73) 特許権者 506094345

スパンション インク

アメリカ合衆国 カリフォルニア州 94

088 サニーベイル 915 デグウェイ

ン ドライブ

(74) 代理人 110000291

特許業務法人コスマス特許事務所

(72) 発明者 河村 祥一

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 滝谷 亮一

最終頁に続く

(54) 【発明の名称】非導電性のチャージトラップゲートを利用した多ビット不揮発性メモリ

## (57) 【特許請求の範囲】

## 【請求項 1】

多ビット情報を記録する不揮発性メモリにおいて、

半導体基板表面に形成された第1及び第2のソース・ドレイン領域と、その間のチャネル領域上に形成された第1の絶縁層、非導電性のトラップゲート、第2の絶縁層、及びコントロールゲートとを有し、

前記トラップゲート内に局所的に電荷をトラップする第1の状態と、

前記トラップゲート全体に電荷を注入する第2の状態とを有することを特徴とする不揮発性メモリ。

## 【請求項 2】

請求項1において、

前記第1の状態は、前記第1及び第2のソース・ドレイン領域それぞれの近傍の第1及び第2のトラップゲート領域に、局所的に電荷をトラップする2つの状態を含むことを特徴とする不揮発性メモリ。

## 【請求項 3】

請求項1または2において、

前記第1の状態への書き込みには、前記第1及び第2のソース・ドレイン領域間に所定の電圧を印加して、前記チャネル領域に発生させたホットエレクトロンを注入することで行われ、

前記第2の状態への書き込みには、前記半導体基板と前記コントロールゲート間に所定

10

20

の電圧を印加して、電荷をトンネル注入することで行われることを特徴とする不揮発性メモリ。

【請求項 4】

請求項 1 または 2 において、

前記半導体基板と前記コントロールゲート間に所定の消去電圧を印加して、前記トラップゲート全体または前記トラップゲートの局所領域に存在する電荷を引き抜くことで、消去動作が行われることを特徴とする不揮発性メモリ。

【請求項 5】

請求項 1 または 2 において、

順番に電圧が異なる第 1 の読み出し電圧、第 2 の読み出し電圧及び第 3 の読み出し電圧とを有し、10

前記第 2 の読み出し電圧が前記コントロールゲートに印加されて、前記第 2 の状態か否かが読み出され、

前記第 1 または第 3 の読み出し電圧が前記コントロールゲートに印加されて、前記第 1 の状態か否かが読み出されることを特徴とする不揮発性メモリ。

【請求項 6】

請求項 2 において、

順番に電圧が異なる第 1 の読み出し電圧、第 2 の読み出し電圧及び第 3 の読み出し電圧とを有し、20

前記第 2 の読み出し電圧が前記コントロールゲートに印加されて、前記第 2 の状態か否かが読み出され、20

前記第 1 または第 3 の読み出し電圧が前記コントロールゲートに印加されて、前記第 1 の状態か否かが読み出され、

更に、前記第 1 の状態か否かの読み出しにおいて、前記第 1 のソース・ドレイン領域に第 2 のソース・ドレイン領域より高い電圧を印加して、前記第 2 のトラップゲート領域についての前記第 1 の状態か否かが読み出され、前記第 2 のソース・ドレイン領域に第 1 のソース・ドレイン領域より高い電圧を印加して、前記第 1 のトラップゲート領域についての前記第 1 の状態か否かが読み出されることを特徴とする不揮発性メモリ。

【請求項 7】

多ビット情報を記録する不揮発性メモリにおいて、30

半導体基板表面に形成された第 1 及び第 2 のソース・ドレイン領域と、その間のチャネル領域上に形成された第 1 の絶縁層、非導電性のトラップゲート、第 2 の絶縁層、及びコントロールゲートとを有し、

前記トラップゲート内であって前記第 1 のソース・ドレイン領域の近傍の第 1 のトラップゲート領域に、電荷をトラップする第 1 の状態と、30

前記トラップゲート内であって前記第 2 のソース・ドレイン領域の近傍の第 2 のトラップゲート領域に、電荷をトラップする第 2 の状態と、

前記トラップゲート全体に電荷を注入する第 3 の状態とを有することを特徴とする不揮発性メモリ。

【請求項 8】

請求項 7 において、40

前記第 1 または第 2 の状態への書き込みには、前記第 1 及び第 2 のソース・ドレイン領域間に所定の電圧を印加して、前記チャネル領域に発生させたホットエレクトロンを前記トラップゲートに注入することで行われ、

前記第 3 の状態への書き込みには、前記半導体基板と前記コントロールゲート間に所定の電圧を印加して、前記半導体基板から前記トラップゲート全体に電荷をトンネル注入することで行われることを特徴とする不揮発性メモリ。

【請求項 9】

請求項 8 において、50

前記半導体基板と前記コントロールゲート間に所定の消去電圧を印加して、前記トラップ

プゲート全体または前記トラップゲートの局所領域に存在する電荷を引き抜くことで、消去動作が行われることを特徴とする不揮発性メモリ。

**【請求項 10】**

請求項 7において、

順番に電圧が異なる第 1 の読み出し電圧、第 2 の読み出し電圧及び第 3 の読み出し電圧とを有し、

前記第 2 の読み出し電圧が前記コントロールゲートに印加されて、前記第 3 の状態か否かが読み出され、

前記第 1 または第 3 の読み出し電圧が前記コントロールゲートに印加されて、前記第 1 または第 2 の状態か否かが読み出されることを特徴とする不揮発性メモリ。

10

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、非導電性のチャージトラップゲートを利用して、1つのメモリセルに多ビット情報を記録することができる新規な不揮発性メモリに関する。

**【0002】**

**【従来の技術】**

半導体を利用した不揮発性メモリは、電源をオフにしても情報を保持することができ、且つ高速読み出しができることから、情報記録媒体として広く利用されている。近年においては、携帯情報端末に利用されたり、デジタルカメラやMP3データのデジタルミュージックなどの記録媒体として利用されている。

20

**【0003】**

現在普及しているフラッシュメモリなどの不揮発性メモリは、ソース、ドレイン領域の間のチャネル領域上に、導電性のフローティングゲートとコントロールゲートを有する構造である。かかる不揮発性メモリは、フローティングゲートがゲート絶縁膜内に埋め込まれて構成され、このフローティングゲートに電荷（チャージ）を注入する、しないにより、1ビットの情報を記憶する。かかる普及型の不揮発性メモリは、フローティングゲートが導電性であるので、ゲート酸化膜にわずかでも欠陥が存在すると、その欠陥を通じてフローティングゲート内の電子が全て消失してしまい、信頼性を高くできない問題がある。

**【0004】**

30

上記の普及型の不揮発性メモリとは別に、フローティングゲートの代わりに非導電性のチャージトラップゲートを設けて、ソース側及びドレイン側にチャージをトラップさせて、2ビットの情報を記憶する新しいタイプの不揮発性メモリが提案されている。例えば、PCT出願、WO99/07000「Two Bit Non-Volatile Electrically Erasable and Programmable Semiconductor Memory Cell Utilizing Asymmetrical Charge Trapping」にかかる不揮発性メモリが記載されている。この不揮発性メモリは、トラップゲートが非導電性であるので、局所的に注入した電子が消失する確率は低く、信頼性を高くすることができる。

**【0005】**

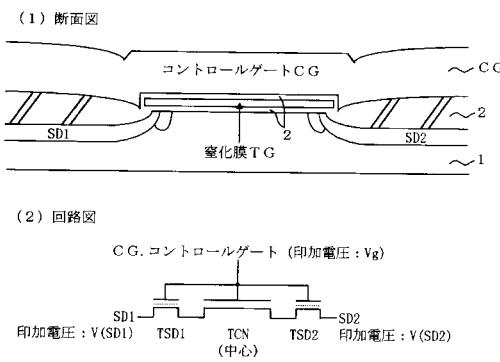

図1は、上記従来の2ビット不揮発性メモリの構成を示す図である。図1(1)はその断面図であり、図1(2)はその等価回路図である。シリコン基板1の表面に、ソース・ドレイン領域SD1, SD2が形成され、シリコン窒化膜などで形成されるトラップゲートTGと導電材料のコントロールゲートCGがチャネル領域上に形成される。トラップゲートTGは、シリコン酸化膜などの絶縁膜2内に埋め込まれていて、全体でMONOS(Metal-Oxide-Nitride-Oxide-Semiconductor)構造になる。シリコン窒化膜とシリコン酸化膜とのバンドギャップの差を利用して、シリコン窒化膜にチャージをトラップさせて保持させることができる。

40

**【0006】**

この不揮発性メモリの特徴的な構成は、トラップゲートTGが、誘電体などの非導電性物質からなり、このトラップゲートTGにチャージを注入した場合、トラップゲート内をチャージが移動することができない。従って、第1のソース・ドレイン領域SD1の近傍に

50

チャージを注入した場合と、第2のソース・ドレイン領域SD2の近傍にチャージを注入した場合とを区別することができ、2ビットのデータを記録することができる。

【0007】

図1(2)は、上記の2ビット不揮発性メモリの等価回路図である。トラップゲートTGが、非導電性であるので、第1のソース・ドレイン領域SD1の近傍の第1のトラップゲート領域TSD1と、第2のソース・ドレイン領域SD2の近傍の第2のトラップゲート領域TSD2とに、別々のMOSトランジスタが形成されている構成と等価になる。そして、後述する読み出しやプログラム(書き込み)動作では、第1及び第2のソース・ドレイン領域SD1, SD2は、一方がソース領域としてまたはドレイン領域として利用されるので、本明細書では、それぞれ、第1のソース・ドレイン領域SD1、第2のソース・ドレイン領域SD2と称する。 10

【0008】

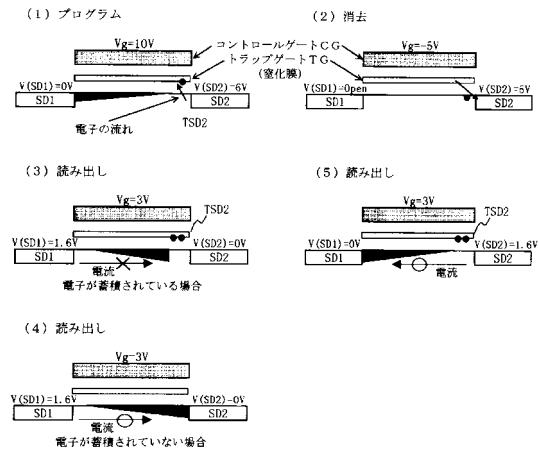

図2は、従来の2ビット不揮発性メモリのプログラム、消去及び読み出しを説明するための図である。第1のソース・ドレイン領域SD1に印加される電圧をV(SD1)、第2のソース・ドレイン領域SD2に印加される電圧をV(SD2)、コントロールゲートに印加される電圧をVgとする。

【0009】

図2(1)に示される通り、不揮発性記憶メモリのプログラム(書き込み)は、例えばVg=10V、V(SD1)=0V、V(SD2)=6Vを印加し、第2のソース・ドレイン領域SD2の近傍で発生したホット・エレクトロンを、第2のソース・ドレイン領域SD2に近い第2のトラップゲート領域TSD2中に注入することにより行われる。 20

【0010】

また、消去動作では、コントロールゲートCGにVg=-5V、第1または第2のソース・ドレイン領域SD1またはSD2、もしくはその両方に5Vを印加し、FNトンネル(ファウラー・ノルドハイム・トンネル)現象を利用してトラップゲートTG中から電子を引き抜く。同時にソース・ドレイン領域SD1、SD2の近傍で発生したホット・ホールをトラップゲートTGに注入することにより、トラップゲートTG中の電荷を中和する。

【0011】

次に、読み出しへは、第1及び第2のソース・ドレイン領域SD1, SD2間に、プログラムとは反対方向の電圧を印加し、第2のトラップゲート領域TSD2に電子がトラップされているか否かを検出する。即ち、第2のトラップゲート領域TSD2の状態を読み出すためには、例えばVg=3V、V(SD1)=1.6V、V(SD2)=0Vを印加する。ここで、図2(3)のように、第2のソース・ドレイン領域SD2付近の第2のトラップゲート領域TSD2に電子が存在すると、ゲート下のチャネルが第2のソース・ドレイン領域SD2までつながらず、チャネル電流が流れない(0データ格納状態)。逆に図2(4)のように、第2のソース・ドレイン領域SD2付近の第2のトラップゲート領域TSD2に電子が存在しなければ、チャネルが第2のソース・ドレイン領域SD2までつながり、チャネル電流が流れる(1データ格納状態)。こうして、第2のトラップゲート領域TSD2に電子が蓄積されているか否かを、セルトランジスタのオン・オフ、つまり電流の有無で検出することができる。 30

【0012】

また、不揮発性記憶メモリの読み出しにおいて、図2(4)のように、Vg=3V、V(SD1)=0V、V(SD2)=1.6Vとして、第1及び第2のソース・ドレイン領域間の電圧印加状態を上記図2(3)と逆にすると、仮に第2のトラップゲート領域TSD2に電子が存在しても、チャネルがピンチ・オフしたMOSトランジスタと同じ状態になり、チャネル電流が流れる。従って、このような電圧印加状態では、第1のソース・ドレイン領域SD1付近の第1のトラップゲート領域TSD1に電子が蓄積されているか否かを、第2のトラップゲート領域TSD2の電子の有無にかかわらず検出することができる。 40

【0013】

上記の通り、従来のメモリでは、第1のソース・ドレイン領域SD1付近の窒化膜の領域TSD1と第2のソース・ドレイン領域SD2付近の窒化膜の領域TSD2に電子を蓄積した 50

りしなかったりすることで、2ビットの情報を記録することができ、大容量化やチップ面積縮小による1チップあたりのコスト削減に有利である。

【0014】

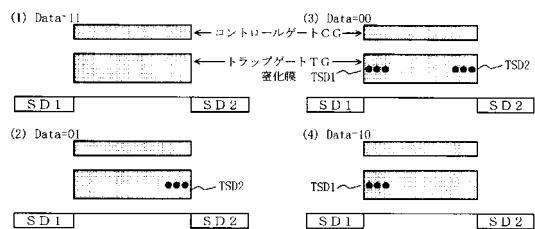

図3は、上記の不揮発性メモリの2ビットの情報を記録した状態を示す図である。図中、黒丸は電子を示す。図3(1)は、第1及び第2のトラップゲート領域TSD1, TSD2のいずれにも電子が捕獲されていない状態で、データ=11を示す。図3(2)は、第2のトラップゲート領域TSD2に電子が捕獲されている状態で、データ=01を示す。図3(3)は、第1及び第2のトラップゲート領域TSD1, TSD2に電子が捕獲されている状態で、データ=00を示し、更に、図3(4)は、第1のトラップゲート領域TSD1に電子が捕獲されている状態で、データ=10を示す。

10

【0015】

【発明が解決しようとする課題】

上記の2ビット不揮発性メモリは、1つのメモリセルで2ビットを記憶することができて、大容量化に有利であるが、最近の不揮発性メモリに要求される大容量化の要請は、更に厳しい。即ち、静止画像データから音楽データ、更に動画データまで記録することができる場合、更に多くのビットを1つのメモリセルで記録することができることが望まれる。

【0016】

そこで、本発明の目的は、1つのメモリセルで3ビットの情報を記録することができる新規な不揮発性メモリを提供することにある。

20

【0017】

更に、本発明の目的は、1つのメモリセルで3ビットの情報を記録することができる新規な不揮発性メモリの読み出し方法、プログラム方法、消去方法などを提供することにある。

【0018】

【課題を解決するための手段】

上記の目的を達成するために、本発明の一つの側面は、半導体基板の表面に、第1及び第2のソース・ドレイン領域と、その間のチャネル領域上に、絶縁膜を介して非導電性のトラップゲートと導電性のフローティングゲートとを有する不揮発性メモリである。そして、本発明の不揮発性メモリは、第1及び第2のソース・ドレイン領域間に電圧を印加して、第1または第2のソース・ドレイン領域の近傍に発生させたホットエレクトロンを、それら近傍の第1または第2のトラップゲート領域に局所的に捕獲する第1または第2の状態と、コントロールゲートとチャネル領域間に電圧を印加して、トラップゲート全体に電子（または電荷）を注入する第3の状態とを有する。

30

【0019】

上記の第3の状態にするかしないかにより、1ビットの情報が記録され、第1及び第2の状態にするかしないかにより、2ビットの情報が記録される。従って、合計で3ビットの情報が1つのメモリセルに記録されることになる。

【0020】

上記の目的を達成するために、本発明の別の側面は、多ビット情報を記録する不揮発性メモリにおいて、

40

半導体基板表面に形成された第1及び第2のソース・ドレイン領域と、その間のチャネル領域上に形成された第1の絶縁層、非導電性のトラップゲート、第2の絶縁層、及びコントロールゲートとを有し、

前記トラップゲート内に局所的に電荷をトラップする第1の状態と、前記トラップゲート全体に電荷を注入する第2の状態とを有することを特徴とする。

【0021】

上記の発明によれば、非導電性のトラップゲート全体に電子を注入する場合と、局所的に注入する場合とで、異なるデータを記録することができる。局所的に注入する位置を複数にすることで、より多くのデータを記録することができる。

50

## 【0022】

上記の発明の好ましい実施例は、前記第1の状態への書き込みには、前記第1及び第2のソース・ドレイン領域間に所定の電圧を印加して、前記チャネル領域に発生させたホットエレクトロンを注入することで行われ、前記第2の状態への書き込みには、前記半導体基板と前記コントロールゲート間に所定の電圧を印加して、電荷をトンネル注入することで行われることを特徴とする。

## 【0023】

上記の発明の好ましい実施例は、前記半導体基板と前記コントロールゲート間に所定の消去電圧を印加して、前記トラップゲート全体または前記トラップゲートの局所領域に存在する電荷を引き抜くことで、消去動作が行われることを特徴とする。

10

## 【0024】

上記の発明の好ましい実施例は、順番に電圧が異なる第1の読み出し電圧、第2の読み出し電圧及び第3の読み出し電圧とを有し、前記第2の読み出し電圧が前記コントロールゲートに印加されて、前記第2の状態か否かが読み出され、前記第1または第3の読み出し電圧が前記コントロールゲートに印加されて、前記第1の状態か否かが読み出されることを特徴とする。

## 【0025】

上記目的を達成するために、本発明の更に別の側面は、多ビット情報を記録する不揮発性メモリにおいて、

半導体基板表面に形成された第1及び第2のソース・ドレイン領域と、その間のチャネル領域上に形成された第1の絶縁層、非導電性のトラップゲート、第2の絶縁層、及びコントロールゲートとを有し、

20

前記トラップゲート内であって前記第1のソース・ドレイン領域の近傍の第1のトラップゲート領域に、電荷をトラップする第1の状態と、前記トラップゲート内であって前記第2のソース・ドレイン領域の近傍の第2のトラップゲート領域に、電荷をトラップする第2の状態と、前記トラップゲート全体に電荷を注入する第3の状態とを有することを特徴とする。

## 【0026】

## 【発明の実施の形態】

以下、図面を参照して本発明の実施の形態例を説明する。しかしながら、かかる実施の形態例が、本発明の技術的範囲を限定するものではない。

30

## 【0027】

本実施の形態例の不揮発性メモリは、図1に示した通り、例えばP型の半導体基板1の表面に、N型の第1及び第2のソース・ドレイン領域SD1, SD2を有する。また、それらの間のチャネル領域上には、順番にシリコン酸化膜2、例えばシリコン窒化膜からなる非導電性のトラップゲートTG、シリコン酸化膜2、そして導電性のコントロールゲートCGが形成される。トラップゲートTGは、シリコン酸化膜2に埋め込まれて、電気的にフローティング状態にある。また、トラップゲートTGは、非導電性材料が好ましく、シリコン窒化膜などの絶縁性物質が利用される。

## 【0028】

本実施の形態例の不揮発性メモリは、トラップゲートTGに局所的に電子をトラップさせるか否かの状態に加えて、トラップゲートTG内全体に電子をトラップするか否かの状態を有する。即ち、従来例において示したのと同様に、第1及び第2のソース・ドレイン領域SD1, SD2の近傍のトラップゲートTGの領域にホットエレクトロンを局所的にトラップすることで、2ビット情報を記録する。更に、本実施の形態例では、トラップゲートTG全体にコントロールゲートCGと半導体基板1との間に電界を印加して電子をトンネル注入することで、トラップゲート全体に電子をトラップすることで、更に1ビットの情報を記録する。

40

## 【0029】

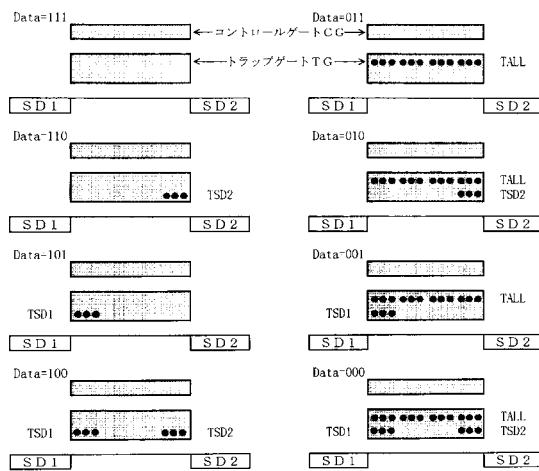

図4は、本実施の形態例における不揮発性メモリの3ビット情報に対応する電子のトラッ

50

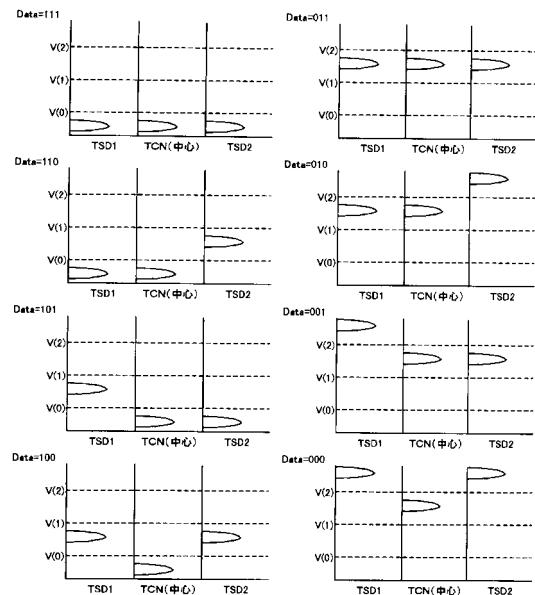

ブ状態を示す図である。また、図5は、同様に本実施の形態例における不揮発性メモリの3ビット情報に対応する閾値電圧の状態を示す図である。図4には、トラップゲートTG内の全体TALLに電子がトラップされている状態と、トラップゲートTGの第1及び第2のソース・ドレイン領域SD1, SD2の近傍の局所的な領域、第1及び第2のトラップゲート領域TSD1, TSD2、に電子がトラップされている状態との組み合わせが示される。また、図5には、メモリセルのチャネル領域を、第1及び第2のトラップゲート領域TSD1, TSD2に対応する部分と、その間のトラップゲートの中央領域TCNに対応する部分とに分けて、それぞれの閾値電圧状態を示す。

#### 【0030】

尚、図5に示された、電圧V(0)、V(1)、V(2)は、読み出し時にコントロールゲートCGに印加される第1、第2及び第3の読み出し電圧を示す。また、本実施の形態例において、データ0は、読み出し電圧を印加してチャネルに電流が流れない状態（非導通）に対応し、データ1は、チャネル電流が流れる状態（導通）に対応する。

#### 【0031】

本実施の形態例の不揮発性メモリは、3ビットの情報を記憶するが、トラップゲートTG全体に電子が捕獲されるか否かで、最上位ビットの情報を、第1のトラップゲート領域TSD1に電子が捕獲されるか否かで2ビット目の情報を、そして、第2のトラップゲート領域TSD2に電子が捕獲されるか否かで、3ビット目（最下位ビット）の情報をそれぞれ記憶する。

#### 【0032】

最初に、メモリセルは、トラップゲートTGに何も電子がトラップされていない状態で、データ=111を記憶する。この状態では、図5に示される通り、3つの領域TSD1, TSD2, TCN（トラップゲートの中央領域）のいずれも閾値電圧は低い状態にある。即ち、電圧V(0)より低い状態にある。

#### 【0033】

次に、メモリセルは、第2のトラップゲートTSD2に電子がトラップされている状態で、データ=110を記憶する。この状態では、図5に示される通り、領域TSD2における閾値電圧のみが、第1の読み出し電圧V(0)より高くなる。それ以外の領域TSD1, TCNにおける閾値電圧は、第1の読み出し電圧V(0)より低いままである。

#### 【0034】

更に、第1のトラップゲートTSD1に電子がトラップされている状態で、データ=101を記憶する。この状態では、図5に示される通り、領域TSD1における閾値電圧のみが、第1の読み出し電圧V(0)より高くなる。それ以外の領域TSD2, TCNにおける閾値電圧は、第1の読み出し電圧V(0)より低いままである。

#### 【0035】

そして、第1及び第2のトラップゲートTSD1, TSD2に電子がトラップされている状態で、データ=100を記憶する。この状態では、図5に示される通り、領域TSD1, TSD2における閾値電圧が、第1の読み出し電圧V(0)より高くなる。そして、中央の領域TCNにおける閾値電圧は、第1の読み出し電圧V(0)より低いままである。

#### 【0036】

上記の3つの状態は、後述する通り、第2の読み出し電圧V(1)と第1の読み出し電圧V(0)を利用することにより、読み出すことが可能である。

#### 【0037】

データ=011, 010, 001, 000は、全てトラップゲートTG全体に電子がトラップされている状態であって、上記と同様に、それぞれ第1及び第2のトラップゲート領域TSD1, TSD2に電子がトラップされていない状態（011）、第2のトラップゲート領域TSD2に電子がトラップされている状態（010）、第1のトラップゲート領域TSD1に電子がトラップされている状態（001）、及び第1及び第2のトラップゲートTSD1, TSD2の両方に電子がトラップされている状態（000）に対応する。

#### 【0038】

10

20

30

40

50

その場合、図5に示される通り、上記の4つの状態は、全ての領域TSD1, TSD2, TCDにおいて、閾値電圧が第2の読み出し電圧V(1)より高い。そして、領域TSD1, TSD2が、第3の読み出し電圧V(2)より高いか低いかに分けられる。即ち、ファウラー・ノルドハイム・トンネル現象(以下FNトンネル現象と称する)により、トラップゲートTG全体に電子が注入されると、それだけでメモリセルトラップゲートの閾値電圧は第2の読み出し電圧V(1)よりも高くなる。そして、更に、第1または第2のトラップゲート領域TSD1, TSD2に局所的に電子をトンネル注入すると、それぞれに対応する領域の閾値電圧が、第3の読み出し電圧V(2)より高くなる。

#### 【0039】

従って、上記の4つの状態は、第2の読み出し電圧V(1)と第3の読み出し電圧V(2) 10)とにより読み出すことができる。

#### 【0040】

次に、本実施の形態例における不揮発性メモリの書き込み(プログラム)動作、読み出し動作、そして消去動作を順に説明する。

#### 【0041】

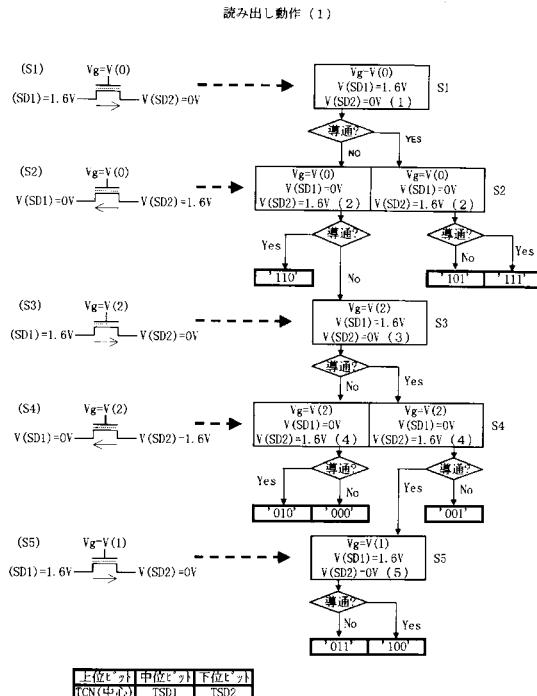

##### [読み出し動作1]

第1の読み出し動作として、3ビットのデータを一度に読み出す場合について説明する。図6は、本実施の形態例における不揮発性メモリの第1の読み出し動作のフローチャート図である。3ビットのデータを検出するためには、5工程S1～S5を必要とする。以下に説明する通り、第1、第2及び第3の読み出し電圧V(0)、V(1)、V(2)を適宜コントロールゲートCGに印加し、第1及び第2のソース・ドレイン領域に電圧V(SD1)、V(SD2)を、両領域間に右方向または左方向の電界になるように適宜印加して読み出しが行われる。 20

#### 【0042】

まず、工程S1に示す通り、メモリセルへの印加電圧をVg=V(0)、V(SD1)=1.6V、V(SD2)=0Vにする。この時、セルトランジスタが導通(読み出しデータ1)であれば、中心の閾値電圧(以下Vt#centerと略す)は第1の読み出し電圧V(0)より小さく、また第2のトラップゲート領域TSD2付近の閾値電圧(以下Vt#sd2と略す)も第1の電圧V(0)より小さいので、格納されているデータは101か111であるとわかる。セルトラップゲートが非導通(読み出しデータ0)ならば、中心の閾値電圧はVt#center>V(0)もしくはVt#sd2>V(0) 30)と考えられ、それ以外のデータが格納されていることが検出される。

#### 【0043】

次に工程S2に示す通り、コントロールゲートへの印加電圧はVg=V(0)のままで、第1及び第2のソース・ドレイン領域の印加電圧V(SD1)とV(SD2)とを入れ替える。この時、工程S1で導通してデータ1が読み出され、工程S2でも導通してデータ1が読み出された場合は、閾値電圧はVt#center<V(0)かつVt#sd2<0であり、かつ第1のトラップゲート領域TSD1付近の閾値電圧(以下Vt#sd1と略す)も第1の読み出し電圧V(0)より小さいので、データは111と特定される。工程S1で導通してデータ1が読み出され、工程S2で非導通になりデータ0が読み出された場合は、閾値電圧はVt#center<V(0)、Vt#sd2<V(0)、かつVt#sd1>V(0)なので、データは101と特定される。 40

#### 【0044】

一方、工程S1で非導通になりデータ0が読み出され、工程S2で導通してデータ1が読み出された場合、閾値電圧はVt#center<V(0)、Vt#sd2>V(0)、Vt#sd1<V(0)なので、データは110と特定される。工程S1で非導通になりデータ0が読み出され、工程S2でも非導通になりデータ0が読み出された場合は、Vt#center>V(0)もしくはVt#sd2>V(0)かつVt#sd1>V(0)と考えられ、上記で特定されたデータ以外のデータが格納されていると判定される。

#### 【0045】

次に、工程S3では、メモリセルへの印加電圧をVg=V(2)、V(SD1)=1.6V、V(SD2)=0Vにする。この時、セルトランジスタが非導通になり読み出されたデータが0ならば、閾値電圧 50

は  $Vt\#sd2 > V(2)$  なので、格納されているデータは 010 か 000 であるとわかる。セルトランジスタが導通して読み出されたデータが 1 であれば、閾値電圧は  $Vt\#sd2 < V(2)$  なので、格納されているデータは 001、100、011 のどれかと判定できる。

#### 【0046】

次に、工程 S 4 では、コントロールゲートへの印加電圧を  $Vg=V(2)$  のままで、第 1 及び第 2 のソース・ドレイン領域への電圧  $V(SD1)$  と  $V(SD2)$  とを入れ替える。この時、工程 S 3 で非導通になりデータ 0 が読み出され、工程 S 4 でも非導通になりデータ 0 が読み出された場合は、閾値電圧は  $Vt\#sd2 > V(2)$  かつ  $Vt\#sd1 > V(2)$  なので、データは 000 と特定される。

#### 【0047】

一方、工程 S 3 で非導通になりデータ 0 が読み出され、工程 S 4 で導通になりデータ 1 が読み出された場合は、閾値電圧は  $Vt\#sd2 > V(2)$  かつ  $Vt\#sd1 < V(2)$  なので、データは 010 と特定される。

#### 【0048】

他方、工程 S 3 で導通してデータ 1 が読み出され、工程 S 4 で非導通になりデータ 0 が読み出された場合、閾値電圧は  $Vt\#sd2 < V(2)$  かつ  $Vt\#sd1 > V(2)$  なので、データは 001 と特定される。また、工程 S 3 で導通してデータ 1 が読み出され、工程 S 4 でも導通してデータ 1 が読み出された場合、 $Vt\#center < V(0)$ 、 $Vt\#sd2 > V(0)$  かつ  $Vt\#sd1 > V(0)$  か、 $Vt\#center > V(0)$ 、 $Vt\#sd2 < V(2)$  かつ  $Vt\#sd1 < V(2)$  の 2 つの状態が考えられる。即ち、データ 100 か 011 である。

#### 【0049】

最後に 100 か 011 を特定するために、工程 S 5 に示される通り、印加電圧を  $Vg=V(1)$ 、 $V(SD1)=1.6V$ 、 $V(SD2)=0V$  にする。第 1 及び第 2 のソース・ドレイン領域への電圧  $V(SD1)$  と  $V(SD2)$  は逆の関係でもよい。この時、コントロールゲートに第 2 の読み出し電圧  $V(1)$  が印加されているので、セルトランジスタが導通してデータ 1 が読み出されれば、閾値電圧は  $Vt\#center < V(1)$  なので、データは 100 と特定される。逆に、非導通になりデータ 0 が読み出されれば、閾値電圧は  $Vt\#center > V(1)$  なので、データは 011 と特定される。

#### 【0050】

以上のメモリセルへの電圧印加例は一例であり、種々の変形例が考えられる。例えば、最初に上記工程 S 5 の如く、コントロールゲート C G への電圧  $Vg$  を第 2 の読み出し電圧  $V(1)$  にして、導通するか否かをチェックすることで、最上位ビットが 0 か 1 かに分離することができる。そして、その後、上記の工程 S 1, S 2 を実行することで、データ 111~100 を検出することができる。或いは、上記の工程 S 3, S 4 を実行することで、データ 011~000 を検出することができる。

#### 【0051】

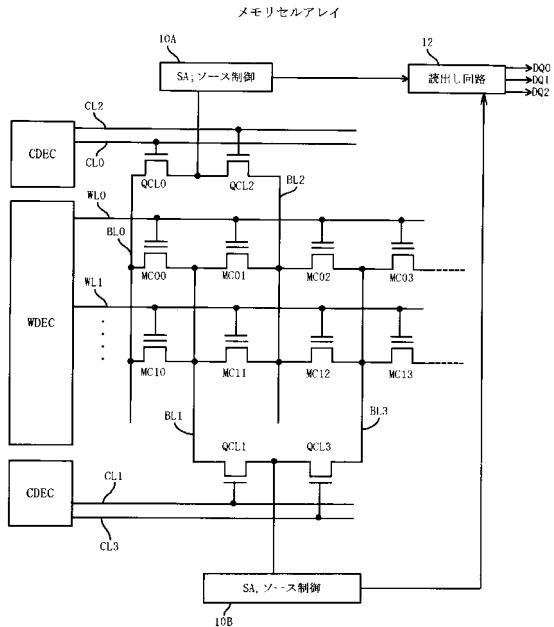

図 7 は、本実施の形態例におけるメモリセルアレイの例を示す回路図である。図 7 には、4 本のビット線  $B_{L0} \sim B_{L3}$  と 2 本のワード線  $W_{L0}, W_{L1}$  とが示され、それらの交差位置にメモリセル  $M_{C00} \sim M_{C13}$  が配置される。それぞれのメモリセルの第 1 及び第 2 のソース・ドレイン領域は、ビット線に接続され、コントロールゲートはワード線に接続される。

#### 【0052】

ワード線はワードデコーダ  $WDEC$  により選択され、ビット線はコラムデコーダにより選択されたコラム選択信号  $C_{L0} \sim C_{L3}$  により選択されたトランジスタを介して、センスアンプ及びソース制御回路  $10A, 10B$  に接続される。また、それらの回路  $10A, 10B$  が読み出したデータが、読み出し回路  $12$  に供給され、上記した読み出しシーケンスの結果、3 ビットのデータが出力端子  $DQ_0 \sim DQ_2$  に出力される。

#### 【0053】

上下に設けられたコラムゲートトランジスタ  $QCL0 \sim QCL3$  の導通を適宜組み合わせることで、メモリセルの第 1 及び第 2 のソース・ドレイン領域に読み出し用の電圧を印加す

10

20

30

40

50

ることができ、メモリセルの導通と非導通に対応するデータ1, 0を読み出すことができる。

【0054】

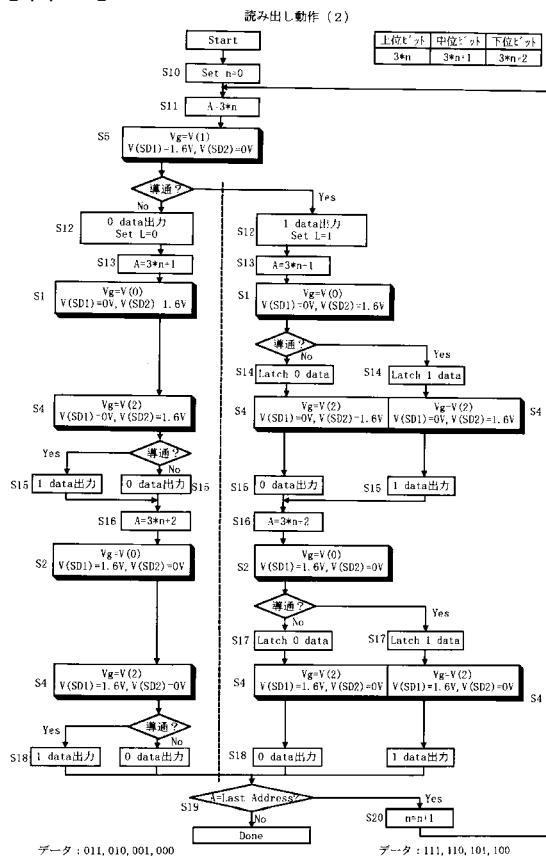

[読み出し動作2]

次に、3ビットのデータをシーケンシャルに読み出す第2の読み出し動作を説明する。図8は、本実施の形態例における不揮発性メモリの第1の読み出し動作のフローチャート図である。また、図9は、その場合のセンスアンプ回路の回路図である。図8中の工程S1～S5は、図6の工程S1～S5に対応する。

【0055】

第2の読み出し動作では、各メモリセルに3ビットのデータが記憶されているので、その最上位桁(トラップゲート全体に電子がトラップされているか否か)と、2番目の桁(第1のトラップゲート領域に電子がトラップされているか否か)と、3番目の桁(第2のトラップゲート領域に電子がトラップされているか否か)とに、 $3 * n$ 番地、 $3 * n + 1$ 番地、 $3 * n + 2$ 番地(但し $n$ は0以上の整数)のアドレス割り当てで読み出し動作を行う。従って、図8中、Aは上記のアドレスを示す。

【0056】

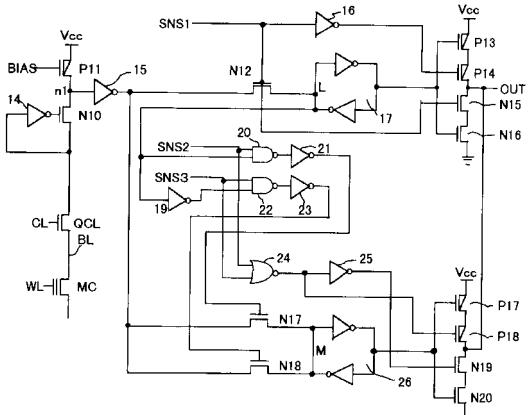

図9に示したセンスアンプ回路は、ビット線B\_LにコラムゲートQ\_C\_Lを介してトランジスタP11, N10からなるプリセンス回路が接続され、インバータI5を介して、メインアンプ側に接続される。ラッチ回路17には、トラップゲート全体に電子がトラップされているか否かの最上位桁のデータがラッチされ、出力インバータP13, P14, N15, N16を介して出力端子OUTに出力される。また、第1または第2のトラップゲート領域に電子がトラップされているか否かの2桁目及び3桁目のデータは、ラッチ回路26にラッチされ、出力インバータP17, P18, N19, N20を介して出力端子OUTに出力される。

【0057】

図8にもどり、最初に $n$ を0にセットし(S10)、アドレスを最上位桁の $3 * n$ にして(S11)データの読み出しを始める。

【0058】

最初の読み出し工程として、工程S5に示される通り、コントロールゲートに第2の読み出し電圧を印加し( $Vg=V(1)$ )、トラップゲート全体に電子が蓄積されているかどうかをチェックする。その為に、図9のセンスアンプ回路では、電圧印加をSNS1=High, SNS2=SN S3=Lowにし、トランジスタN12, P14, N15を導通させ、トランジスタN17, N18を非導通にさせる。

【0059】

もしトラップゲート全体に電子が蓄積されていれば、メモリセルMCは導通せずに、ノードn1はHレベルになり、インバータI5により反転されて、ラッチ回路17にラッチされ、出力はOUT=Low(データ0)となる。もしトラップゲート全体に電子が蓄積されていなければ、上記と逆になり、出力はOUT=High(データ1)となる。これが0番地のデータとなる。このとき、制御信号はSNS1=Highであるので、ラッチ回路17内のノードLは、電子が蓄積されているか否かに伴うメモリセルの導通、非導通に従って、LowかHighのいずれかにセットされる(S12)。

【0060】

次にアドレスを一つ進めて、 $A = 3 * n + 1$ とし(S13)、第1のトラップゲート領域TSD1の電子の有無をチェックする。そして、コントロールゲートの電圧を第1の読み出し電圧 $Vg=V(0)$ とし、更に第1及び第2のソース・ドレイン領域の電圧を、 $V(SD1)=0V$ 、 $V(SD2)=1.6V$ とする(S1)。更に、センスアンプ回路における制御信号を、SNS1=Low, SNS2=High, SNS3=Lowにする。

【0061】

このとき、上記の最上位ビット読み出し動作で電子がトラップされて非導通で、出力がOUT=Low(データ0)だったメモリセルは、この工程S1では読む必要がなく、データ出力

10

20

30

40

50

は行われない。一方、最上位ビット読み出しでOUT=High(データ1)だったメモリセルは2桁目のビットをセンスする必要がある。即ち、図9のセンスアンプ回路において、ノードLがHighにセットされ、NANDゲート20がLレベルを出力し、トランジスタN17が導通し、インバータ15の出力はトランジスタN17を介してラッチ回路26にラッチされる。

#### 【0062】

もし第1のトラップゲート領域TSD1に電子が蓄積されていれば、メモリセルMCは非導通になり、ラッチ回路26内のノードMはM=Low、電子が蓄積されていなければメモリセルは導通になり、ノードMはM=Highになる。制御信号SNS2=Highであるので、トラップゲートP18, N19は導通状態になりCMOSインバータは活性化され、ノードMがHighかLowかに従って、出力OUTにはHigh(データ1)かLow(データ0)が出力される。

10

#### 【0063】

次に最上位桁の読み出しの時に出力がOUT=Low(データ0)だったメモリセルのデータを決定する為に、メモリセルへの印加電圧をVg=V(2)、V(SD1)=0V、V(SD2)=1.6Vとする(S4)。そして、センスアンプ回路の制御信号をSNS1=SNS2=Low、SNS3=Highとする。このとき、もし第1のトラップゲート領域TSD1にトラップゲート全体に蓄積されている以上の電子が蓄積されていれば、メモリセルは非導通になり、出力はOUT=Low、蓄積されていなければ導通になり、出力はOUT=High(データ1)である(S15)。上記の工程S1とS4により得られたデータが2桁目のデータとなる。

#### 【0064】

更に、アドレスを一つ進めてA=3\*n+2にする(S16)。そして、メモリセルへの印加電圧をVg=V(0)、V(SD1)=1.6V、V(SD2)=0Vとする(S2)。この時制御信号はSNS1=Low、SNS2=High、SNS3=Lowである。このとき、上記の最上位桁の読み出し動作でOUT=Low(データ0)だったメモリセルは読む必要がなく、データ出力は行われない。一方、最上位桁の読み出しでOUT=High(データ1)だったメモリセルはセンスする必要があり、2桁目の読み出しと同様にトランジスタN17が導通し、ラッチ回路26にデータがラッチされる。

20

#### 【0065】

もし第2のトラップゲート領域TSD2に電子が蓄積されていれば、メモリセルは非導通となり、ノードM=Low、電子が蓄積されていなければメモリセルは導通となり、ノードM=Highである。制御信号がSNS2=Highなので、ノードMがHighかLowかに従って、出力OUTにはHigh(データ1)かLow(データ0)が出力される(S17)。

30

#### 【0066】

次に最上位桁の読み出しで出力OUT=Low(データ0)だったメモリセルのデータを決定する為に、メモリセルへの印加電圧をVg=V(2)、V(SD1)=1.6V、V(SD2)=0Vとする(S4)。この場合は制御信号は、SNS1=SNS2=Low、SNS3=Highである。

#### 【0067】

このとき、もし第2のトラップゲートTSD2に、トラップゲート領域全体に蓄積されている以上の電子が蓄積されていれば、メモリセルは非導通になり、出力はOUT=Low(データ0)、蓄積されていなければメモリセルは導通し、出力はOUT=High(データ1)である(S18)。上記工程S2とS4により読み出されたデータが、3桁目のデータである。

40

#### 【0068】

以上で、1つのメモリセルに対する3つのアドレスに対応するデータがシリアルに読み出すことができた。あとは次のメモリセルに進んで同じ動作を最終アドレスに達するまで繰り返すことになる。もちろん途中で読み出し動作を止めてもよいし、0番地ではなく任意のアドレスからのシーケンシャルに読み出しある可能である。

#### 【0069】

##### [書き込み(プログラム)動作]

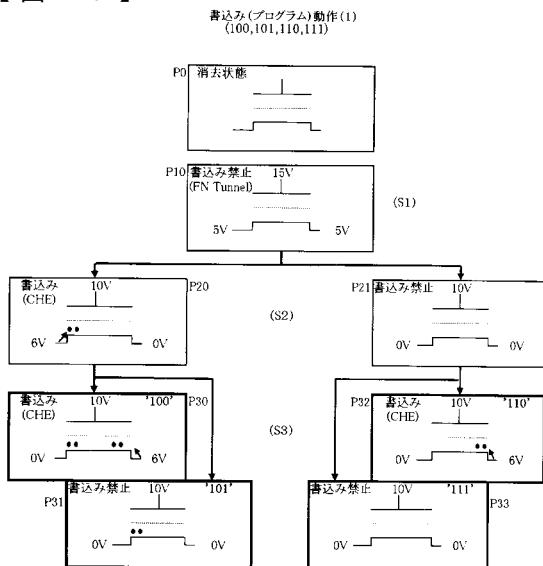

図10, 11は、本実施の形態例における不揮発性メモリの書き込み(プログラム)動作を説明するフローチャート図である。図10, 11は、トラップゲートTGに電子がト

50

ツプされていない消去状態 P 0 から、書き込み工程 S 1 , S 2 , S 3 を順次行うことで、3 ビット情報の 8 つの書き込み状態 P 3 0 ~ P 3 7 に至るフロー・チャートを示す。従って、図 1 0 , 1 1 を左右方向で結合することで、全体の書き込み（プログラム）の工程が示される。

#### 【 0 0 7 0 】

通常、メモリセルアレイは、ワード線とビット線の交差位置にメモリセルが設けられる。そして、コントロールゲート CG、第 1 及び第 2 のソース・ドレイン領域 S D 1 , S D 2 、そしてチャネル領域に所定の電圧を印加して、複数のメモリセルに異なるデータを書き込むことが一般的である。従って、図 1 0 , 1 1 には、かかる複数のメモリセルへの書き込みができるようにする書き込み工程が示される。

10

#### 【 0 0 7 1 】

最初に、図 1 0 に従って、消去状態 P 0 からデータ = 1 0 0 , 1 0 1 , 1 1 0 , 1 1 1 をメモリセルに書き込む場合について説明する。

#### 【 0 0 7 2 】

書き込みは 3 つの工程 S 1 , S 2 , S 3 で行われる。工程 S 1 では、トラップゲート T G 全体に電子を蓄積させたくないの、状態 P 1 0 に示される通り、印加電圧を  $V_g=15V$  、  $V(SD1)=5V$  、  $V(SD2)=5V$  として、 FN トンネル現象を禁止してチャネルからトラップゲート T G への電子注入を禁止する。この時、後述する図 1 1 の書き込み工程では、データ 0 0 0 , 0 0 1 , 0 1 0 , 0 1 1 を書き込むメモリセルに対して電子の注入が行われる。

#### 【 0 0 7 3 】

次に、工程 S 2 では、データ 1 0 0 , 1 0 1 を書き込むメモリセルには、状態 P 2 0 に示される通り、印加電圧を  $V_g=10V$  、  $V(SD1)=6V$  、  $V(SD2)=0V$  として、アバランシェ・ブレイクダウンにより発生したチャネル・ホット・エレクトロンを第 1 のソース・ドレイン領域 SD 1 付近のトラップゲート領域 T S D 1 に局所的に注入する。データ 1 1 0 , 1 1 1 のメモリセルには、第 1 のソース・ドレイン領域 SD 1 付近のトラップゲート領域 T S D 1 に電子を注入したくないので、状態 P 2 1 に示される通り、  $V_g=10V$  、  $V(SD1)=0V$  、  $V(SD2)=0V$  として、書き込みを禁止する。

20

#### 【 0 0 7 4 】

工程 S 2 の書き込み動作後、メモリセルへの印加電圧を  $V_g=V(0)$  、  $V(SD1)=0V$  、  $V(SD2)=1.6V$  として、書き込みベリファイを行う。ベリファイがパスすれば工程 S 3 へ進み、フェイルした場合はパスするまで工程 S 2 を繰り返す。上記ベリファイをパスすれば、第 1 のトラップゲート領域 T S D 1 の閾値電圧が、第 1 の読み出し電圧  $V(0)$  を越える。但し、このとき書き込み後の閾値レベルが第 2 の読み出し電圧  $V(1)$  を越えないように注意する必要がある。従って、コントロールゲート CG に第 2 の読み出し電圧  $V_g=V(1)$  を印加してベリファイを行い、書き込み状態と判定された場合には、メモリセルへの印加電圧を  $V_g=-5V$  、  $V(SD1)=5V$  、  $V(SD2)=OPEN$  として消去動作を行い、再び工程 S 2 を行う。

30

#### 【 0 0 7 5 】

最後に、工程 S 3 では、データ 1 0 0 , 1 1 0 を書き込むメモリセルには、状態 P 3 0 , P 3 2 に示される通り、印加電圧を  $V_g=10V$  、  $V(SD1)=0V$  、  $V(SD2)=6V$  として、アバランシェ・ブレイクダウンにより発生したチャネル・ホット・エレクトロンを、第 2 のソース・ドレイン領域 SD 2 付近の第 2 のトラップゲート領域 T S D 2 に注入する。また、データ 1 0 1 , 1 1 1 を書き込むメモリセルには、第 2 のソース・ドレイン領域 SD 2 付近の第 2 のトラップゲート T S D 2 に電子を注入したくないので、状態 P 3 1 , P 3 3 に示される通り、メモリセルへの印加電圧は  $V_g=10V$  、  $V(SD1)=0V$  、  $V(SD2)=0V$  として、書き込みを禁止する。

40

#### 【 0 0 7 6 】

書き込み動作後、メモリセルへの印加電圧を  $V_g=V(0)$  、  $V(SD1)=1.6V$  、  $V(SD2)=0V$  として書き込みベリファイを行う。ベリファイがパスすれば書き込み動作を終了し、フェイルした場合はパスするまで工程 S 3 を繰り返す。この場合も、書き込み後の閾値レベルが第 2 の読み出し電圧  $V(1)$  を越えないように注意する必要がある。その為に、コントロールゲートへの電圧を  $V_g=V(1)$  としてベリファイを行い、メモリセルが非導通状態になって書き込み状態と判

50

定された場合には、印加電圧を  $V_g = -5V$ 、  $V(SD1) = 5V$ 、  $V(SD2) = OPEN$  として消去動作を行い、再び工程 S 3 を行う。

#### 【 0 0 7 7 】

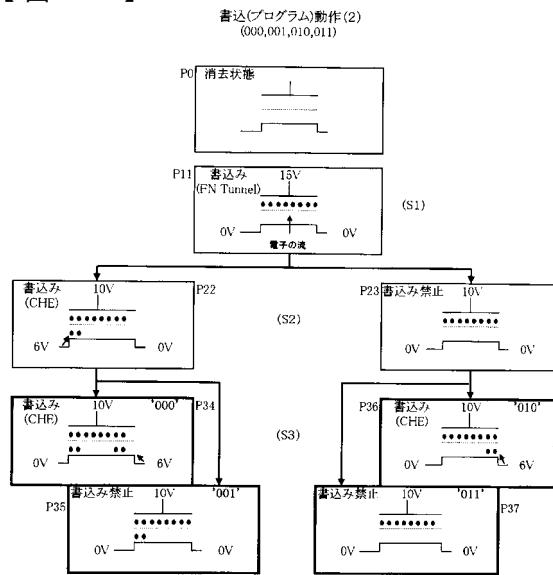

次に、図 1 1 に従って、消去状態 P 0 からデータ = 0 0 0, 0 0 1, 0 1 0, 0 1 1 をメモリセルに書き込む場合について説明する。

#### 【 0 0 7 8 】

図 1 0 の場合と同様に、書き込み動作は 3 つの工程 S 1 ~ S 3 で行われる。工程 S 1 では、トラップゲート T G 全体に電子を蓄積させる必要があるので、状態 P 1 1 に示す通り、印加電圧を  $V_g = 15V$ 、  $V(SD1) = 0V$ 、  $V(SD2) = 0V$  として、 FN トンネル現象を利用してチャネルからトラップゲート T G に電子を注入する。書き込み動作後、印加電圧を  $V_g = V(1)$ 、  $V(SD1) = 1.6V$  10 、  $V(SD2) = 0V$  として書き込みベリファイを行う。その結果、ベリファイがパスすれば工程 S 2 へ進み、フェイルした場合はパスするまで工程 S 1 を繰り返す。上記ベリファイがパスすると、閾値電圧は、第 2 の読み出し電圧  $V(1)$  より高くなる。

#### 【 0 0 7 9 】

次に、工程 S 2 では、データ 0 0 0, 0 0 1 を書き込むメモリセルには、状態 P 2 2 に示される通り、印加電圧を  $V_g = 10V$ 、  $V(SD1) = 6V$ 、  $V(SD2) = 0V$  として、アバランシェ・ブレイクダウンにより発生したチャネル・ホット・エレクトロンを第 1 のトラップゲート領域 T S D 1 に注入する。データ 0 1 0, 0 1 1 を書き込むメモリセルには、第 1 のトラップゲート領域 T S D 1 に電子を注入したくないので、状態 P 2 3 に示される通り、印加電圧を  $V_g = 10V$ 、  $V(SD1) = 0V$ 、  $V(SD2) = 0V$  として、書き込みを禁止する。20

#### 【 0 0 8 0 】

書き込み動作後、印加電圧を  $V_g = V(2)$ 、  $V(SD1) = 0V$ 、  $V(SD2) = 1.6V$  として書き込みベリファイを行う。その結果、ベリファイがパスすれば工程 S 3 へ進み、フェイルした場合はパスするまで工程 S 2 を繰り返す。上記ベリファイがパスすれば、第 1 のトラップゲート領域 T S D 1 に対応するチャネル領域の閾値電圧は、第 3 の読み出し電圧  $V(2)$  よりも高くなる。

#### 【 0 0 8 1 】

最後に、工程 S 3 では、データ 0 0 0, 0 1 0 を書き込むメモリセルには、状態 P 3 4, 3 6 に示される通り、印加電圧  $V_g = 10V$ 、  $V(SD1) = 0V$ 、  $V(SD2) = 6V$  として、アバランシェ・ブレイクダウンにより発生したチャネル・ホット・エレクトロンを第 2 のトラップゲート領域 T S D 2 に注入する。また、データ 0 0 1, 0 1 1 を書き込むメモリセルには、第 2 のトラップゲート領域 T S D 2 に電子を注入したくないので、状態 P 3 5, 3 7 に示される通り、印加電圧は  $V_g = 10V$ 、  $V(SD1) = 0V$ 、  $(SD2) = 0V$  として、書き込みを禁止する。30

#### 【 0 0 8 2 】

書き込み動作後、  $V_g = V(2)$ 、  $V(SD1) = 1.6V$ 、  $V(SD2) = 0V$  として書き込みベリファイを行う。ベリファイがパスすれば書き込み動作を終了し、フェイルした場合はパスするまで工程 S 3 を繰り返す。上記ベリファイがパスすれば、第 2 のトラップゲート領域 T S D 2 に対応する閾値電圧が、第 3 の読み出し電圧  $V(2)$  より高くなる。

#### 【 0 0 8 3 】

##### [ 消去動作 ]

本実施の形態例における不揮発性メモリの消去動作は、 FN トンネル現象を利用して、トラップゲート T G 内の電子をチャネル領域側に引き抜くことにより行われる。トラップゲート T G 全体に電子が注入されている場合も、第 1 及び第 2 のトラップゲート領域に電子がトラップされている場合も、すべて、同様にして消去することができる。40

#### 【 0 0 8 4 】

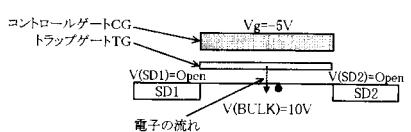

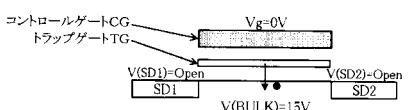

図 1 2 は、本実施の形態例における不揮発性メモリの消去動作を示す図である。図 1 2 には、4 種類の消去動作が示される。図 1 2 ( a ) の消去動作では、コントロールゲート C G に  $V_g = -5V$ 、チャネル領域に  $V(BULK) = 10V$ 、第 1 及び第 2 のソース・ドレイン領域をオープン ( フロー・ティング ) にすると、トラップゲート T G 内に捕獲されている電子が、トラップゲート T G の下側のゲート酸化膜をトンネル現象により通過し、チャネル領域に引き抜かれる。50

## 【0085】

図12(b)は、上記の消去動作を、正電圧を利用して行う。即ち、コントロールゲート CG に  $V_g = 0V$ 、チャネル領域に  $V(BULK) = 15V$ 、第1及び第2のソース・ドレイン領域をオープン(フローティング)にする。その結果、同様にして電子が引き抜かれる。

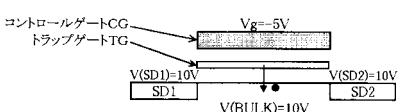

## 【0086】

図12(c)の消去動作では、チャネル領域とソース・ドレイン領域とを同電位にして、それらの間のPN接合が順バイアス状態になることを防止する。即ち、コントロールゲート CG に  $V_g = -5V$ 、チャネル領域に  $V(BULK) = 10V$ 、第1及び第2のソース・ドレイン領域も 10Vにする。それにより、トンネル現象により電子が引き抜かれる。

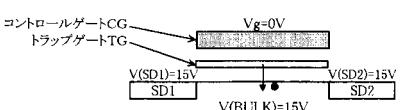

## 【0087】

図12(d)の消去動作は、上記の動作を正電圧を利用して行う。即ち、コントロールゲート CG に  $V_g = 0V$ 、チャネル領域に  $V(BULK) = 15V$ 、第1及び第2のソース・ドレイン領域を同様に 15Vにする。それにより、ソース・ドレイン領域のPN接合が順バイアスに保たれたまま、トンネル現象によりトラップゲート TG 内の電子が引き抜かれる。

## 【0088】

以上、本発明の保護範囲は、上記の実施の形態例に限定されるものではなく、特許請求の範囲に記載された発明とその均等物にまで及ぶものである。

## 【0089】

## 【発明の効果】

以上、本発明によれば、非導電性のトラップゲートをゲート絶縁膜内に埋め込んで、トラップゲート全体にチャージを注入する状態と、トラップゲートの一部の領域に局部的にチャージを注入してトラップさせる状態とを利用して、多値のデータを一つのメモリセルに記録することが可能になる。

## 【図面の簡単な説明】

【図1】従来の2ビット不揮発性メモリの構成を示す図である。

【図2】従来の2ビット不揮発性メモリのプログラム、消去及び読み出しを説明するための図である。

【図3】従来の不揮発性メモリの2ビットの情報を記録した状態を示す図である。

【図4】本実施の形態例における不揮発性メモリの3ビット情報に対応する電子のトラップ状態を示す図である。

【図5】本実施の形態例における不揮発性メモリの3ビット情報に対応する閾値電圧の状態を示す図である。

【図6】本実施の形態例における不揮発性メモリの第1の読み出し動作のフローチャート図である。

【図7】本実施の形態例におけるメモリセルアレイの例を示す回路図である。

【図8】本実施の形態例における不揮発性メモリの第2の読み出し動作のフローチャート図である。

【図9】第2の読み出し動作で利用するセンスアンプ回路の回路図である。

【図10】本実施の形態例における不揮発性メモリの書き込み(プログラム)動作を説明するフローチャート図である。

【図11】本実施の形態例における不揮発性メモリの書き込み(プログラム)動作を説明するフローチャート図である。

【図12】本実施の形態例における不揮発性メモリの消去動作を示す図である。

## 【符号の説明】

CG コントロールゲート

TG トラップゲート

SD1, SD2 第1及び第2のソース・ドレイン領域

TSD1, TSD2 第1及び第2のトラップゲート領域

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

消去動作

(a) 負電圧を用いたFN Tunnelによる消去

(b) 正電圧を用いたFN Tunnelによる消去

(c) 負電圧を用いたFN Tunnelによる消去 その他

(d) 正電圧を用いたFN Tunnelによる消去 その他

---

フロントページの続き

(56)参考文献 特開昭60-200566(JP,A)

特開平09-074146(JP,A)

特開平07-201189(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/02—16/06

H01L 27/105

H01L 27/8246

H01L 27/108

H01L 27/8242