OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

⑪ Número de publicación: **2 715 027**

⑮ Int. Cl.:

**G06F 1/08**

(2006.01)

⑫

## TRADUCCIÓN DE PATENTE EUROPEA

T3

⑯ Fecha de presentación y número de la solicitud internacional: **01.07.2016 PCT/US2016/040797**

⑰ Fecha y número de publicación internacional: **09.02.2017 WO17023463**

⑯ Fecha de presentación y número de la solicitud europea: **01.07.2016 E 16751042 (9)**

⑯ Fecha y número de publicación de la concesión europea: **09.01.2019 EP 3332302**

---

⑭ Título: **Mitigación de caída/exceso en Redes de distribución de energía (PDN)**

⑯ Prioridad:

**03.08.2015 US 201514817057**

⑮ Fecha de publicación y mención en BOPI de la traducción de la patente:

**31.05.2019**

⑮ Titular/es:

**QUALCOMM INCORPORATED (100.0%)

5775 Morehouse Drive

San Diego, CA 92121-1714, US**

⑯ Inventor/es:

**PAL, DIPTI RANJAN;

ALLAM, MOHAMED WALEED;

KIM, INGYEOM y

PENZES, PAUL IVAN**

⑯ Agente/Representante:

**FORTEA LAGUNA, Juan José**

**ES 2 715 027 T3**

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

## DESCRIPCIÓN

Mitigación de caída/exceso en Redes de distribución de energía (PDN)

5 **REFERENCIA CRUZADA A SOLICITUD RELACIONADA**

**[0001]** Esta solicitud reivindica la prioridad y el beneficio de la solicitud de patente no provisional nº 14/817,057 presentada en la Oficina de Patentes y Marcas de los Estados Unidos el 3 de agosto de 2015.

10 **ANTECEDENTES****Campo**

**[0002]** Los aspectos de la presente divulgación se refieren, en general, a las redes de distribución de energía (PDN), y, más concretamente, a la mitigación de caída/exceso en PDN.

**Antecedentes**

**[0003]** El escalado de frecuencia dinámico se usa ampliamente para cambiar dinámicamente la frecuencia de reloj de un procesador basándose en casos de uso. Por ejemplo, la frecuencia de reloj del procesador puede incrementarse cuando el procesador se está usando para una aplicación de alta velocidad, y puede reducirse cuando el procesador se está usando para una aplicación de baja velocidad para ahorrar energía.

**[0004]** Se llama la atención sobre el documento WO 2003/073244 A2, que describe un procedimiento y un mecanismo para generar una señal de reloj con un aumento o disminución relativamente lineal de la frecuencia de reloj. Se genera una primera señal de reloj con una primera frecuencia que se usa entonces para generar una segunda señal de reloj con una segunda frecuencia. La segunda frecuencia se genera eliminando impulsos seleccionados de la primera señal de reloj. Los patrones de bits particulares se almacenan en un elemento de almacenamiento. Los bits se seleccionan y se transportan entonces desde el elemento de almacenamiento a una frecuencia determinada mediante la primera señal de reloj. Los bits transportados se usan para construir la segunda señal de reloj. Seleccionando el patrón particular de bits seleccionados y transportados, se puede determinar la frecuencia de la segunda señal de reloj. Además, cambiando los patrones de bits dentro de los registros en momentos seleccionados, se puede hacer que la frecuencia de la segunda señal de reloj cambie de una manera relativamente lineal.

35 **SUMARIO**

**[0005]** De acuerdo con la presente invención, se proporcionan un sistema y un procedimiento para cambiar la frecuencia de reloj, como se expone en las reivindicaciones independientes. Los modos de realización de la invención se reivindican en las reivindicaciones dependientes.

**[0006]** A continuación se ofrece un resumen simplificado de uno o más modos de realización para proporcionar un entendimiento básico de dichos modos de realización. Este resumen no es una visión general extensiva de todos los modos de realización contemplados y no está previsto para identificar ni elementos clave ni críticos de todos los modos de realización ni delimitar el alcance de algunos o de todos los modos de realización. Su único propósito es presentar algunos conceptos de uno o más modos de realización de una forma simplificada como preludio a la descripción más detallada que se presenta más adelante.

**[0007]** Según un aspecto, se describe un sistema en el presente documento. El sistema comprende un circuito de reloj configurado para generar una primera señal de reloj, y un circuito de rampa de frecuencia configurado para recibir la primera señal de reloj del circuito de reloj, para proporcionar una segunda señal de reloj basándose en la primera señal de reloj, y para ajustar una frecuencia de la segunda señal de reloj. El sistema también comprende un controlador de reloj configurado para indicar al circuito de rampa de frecuencia que reduzca la frecuencia de la segunda señal de reloj.

**[0008]** Un segundo aspecto se refiere a un procedimiento para el cambio de la frecuencia de reloj. El procedimiento comprende reducir una frecuencia de una segunda señal de reloj, en el que la segunda señal de reloj se proporciona a partir de una primera señal de reloj, deshabilitar la segunda señal de reloj, y cambiar la primera señal de reloj de una primera frecuencia de reloj a una segunda frecuencia de reloj después de que se deshabilita la segunda señal de reloj. El procedimiento también comprende habilitar la segunda señal de reloj después de que la primera señal de reloj se cambia a la segunda frecuencia de reloj, y aumentar la frecuencia de la segunda señal de reloj.

**[0009]** Un tercer aspecto se refiere a un aparato para cambiar la frecuencia de reloj. El aparato comprende medios para reducir una frecuencia de una segunda señal de reloj, en el que la segunda señal de reloj se proporciona a partir de una primera señal de reloj, medios para deshabilitar la segunda señal de reloj, y medios para cambiar la primera señal de reloj de una primera frecuencia de reloj a una segunda frecuencia de reloj después de que se deshabilita la segunda señal de reloj. El aparato también comprende medios para habilitar la segunda señal de reloj después de

que la primera señal de reloj se cambia a la segunda frecuencia de reloj, y medios para aumentar la frecuencia de la segunda señal de reloj.

5 [0010] Para el cumplimiento de los objetivos anteriores y los relacionados, el uno o más modos de realización comprenden las características descritas con todo detalle de aquí en adelante y señaladas particularmente en las reivindicaciones. La descripción siguiente y los dibujos adjuntos exponen con detalle ciertos aspectos ilustrativos del uno o más modos de realización. Sin embargo, estos aspectos son indicativos de apenas algunas de las diversas maneras en las que pueden emplearse los principios de diversos modos de realización, y los modos de realización descritos están concebidos para incluir todos dichos aspectos y sus equivalentes.

## 10 BREVE DESCRIPCIÓN DE LOS DIBUJOS

[0011]

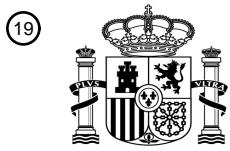

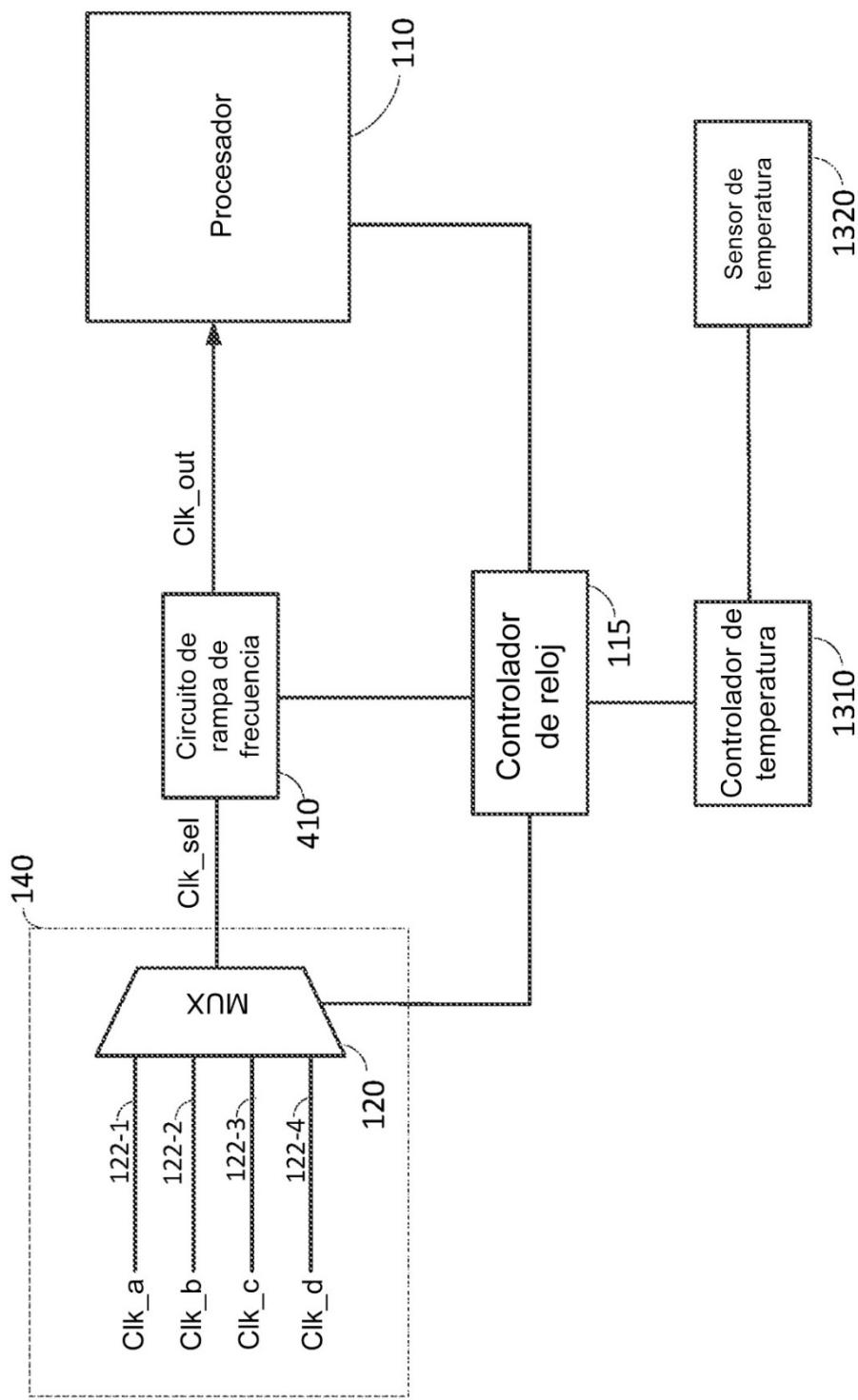

15 La FIG. 1A muestra un sistema a modo de ejemplo con escalado de frecuencia.

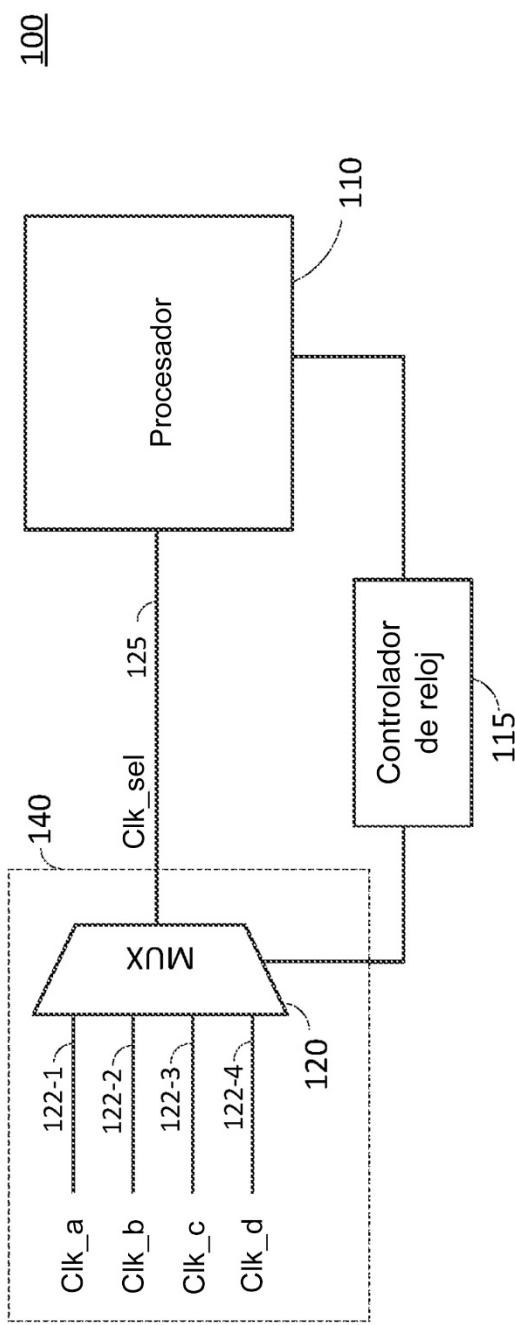

La FIG. 1B muestra un sistema a modo de ejemplo que comprende un bucle de enganche de fase (PLL) y divisores de frecuencia.

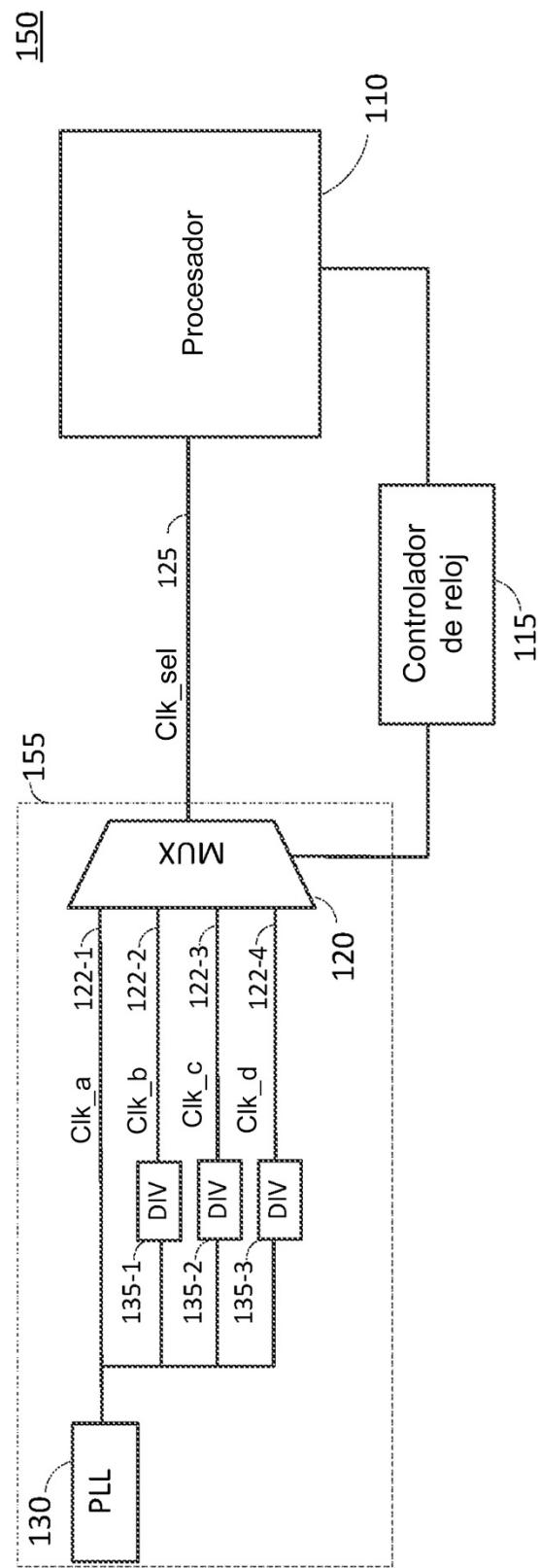

20 La FIG. 1C muestra un sistema a modo de ejemplo que comprende PLL y divisores de frecuencia.

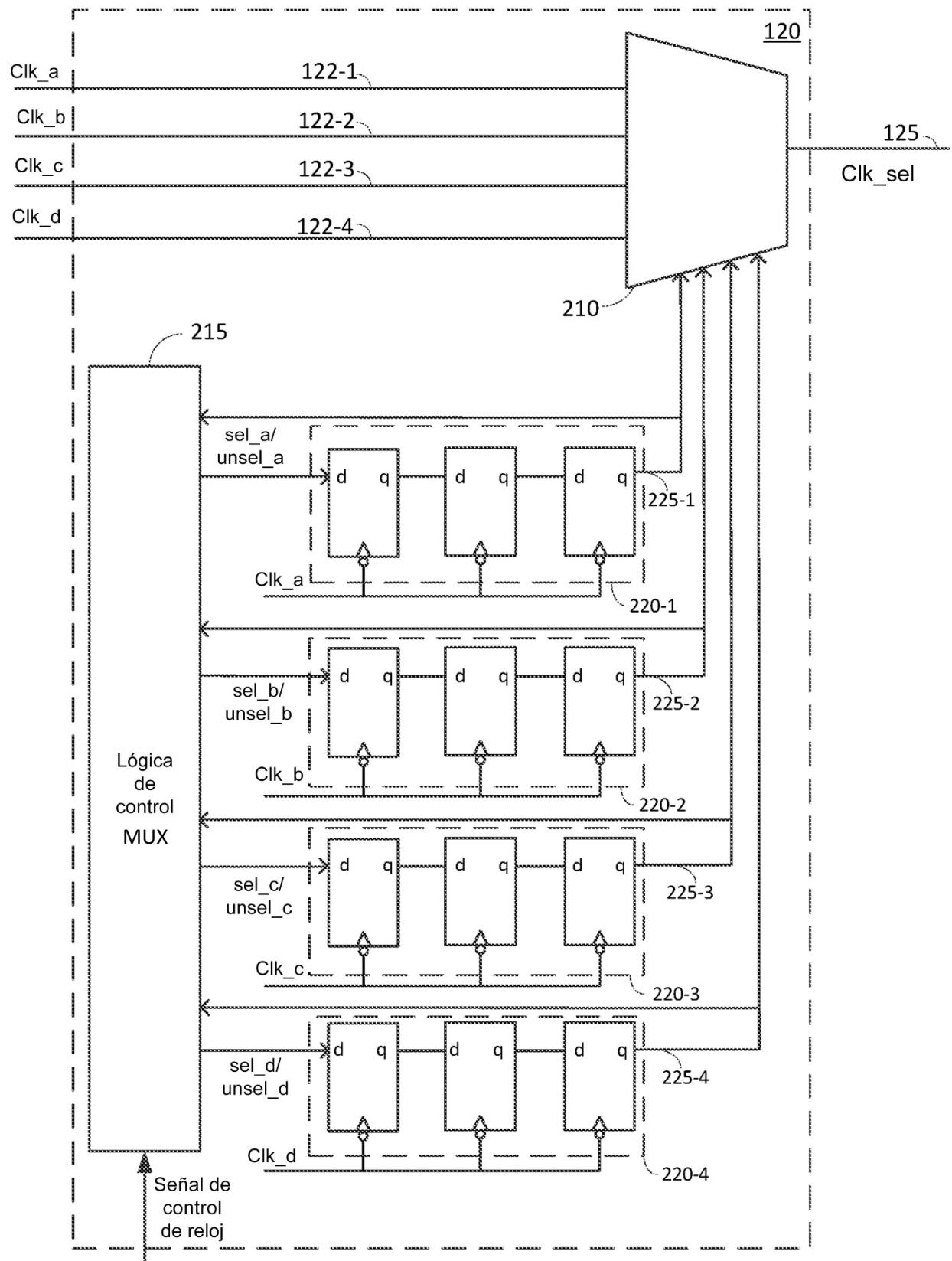

La FIG. 2 muestra una implementación a modo de ejemplo de un multiplexor libre de fallos.

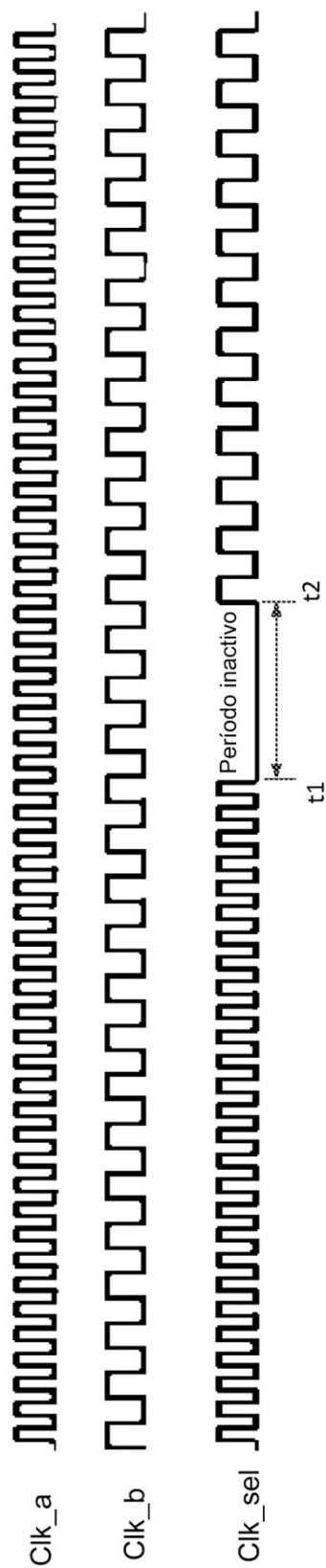

25 La FIG. 3 es un diagrama de tiempo que ilustra un ejemplo de cambio de reloj.

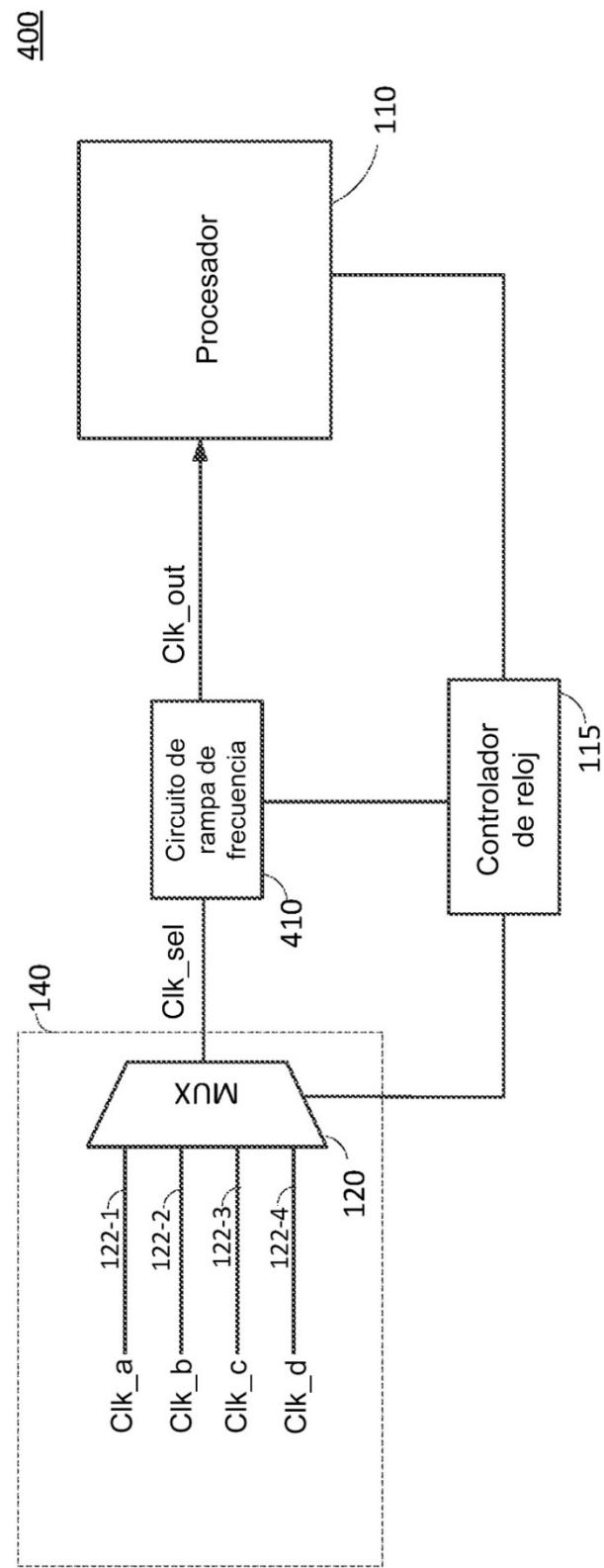

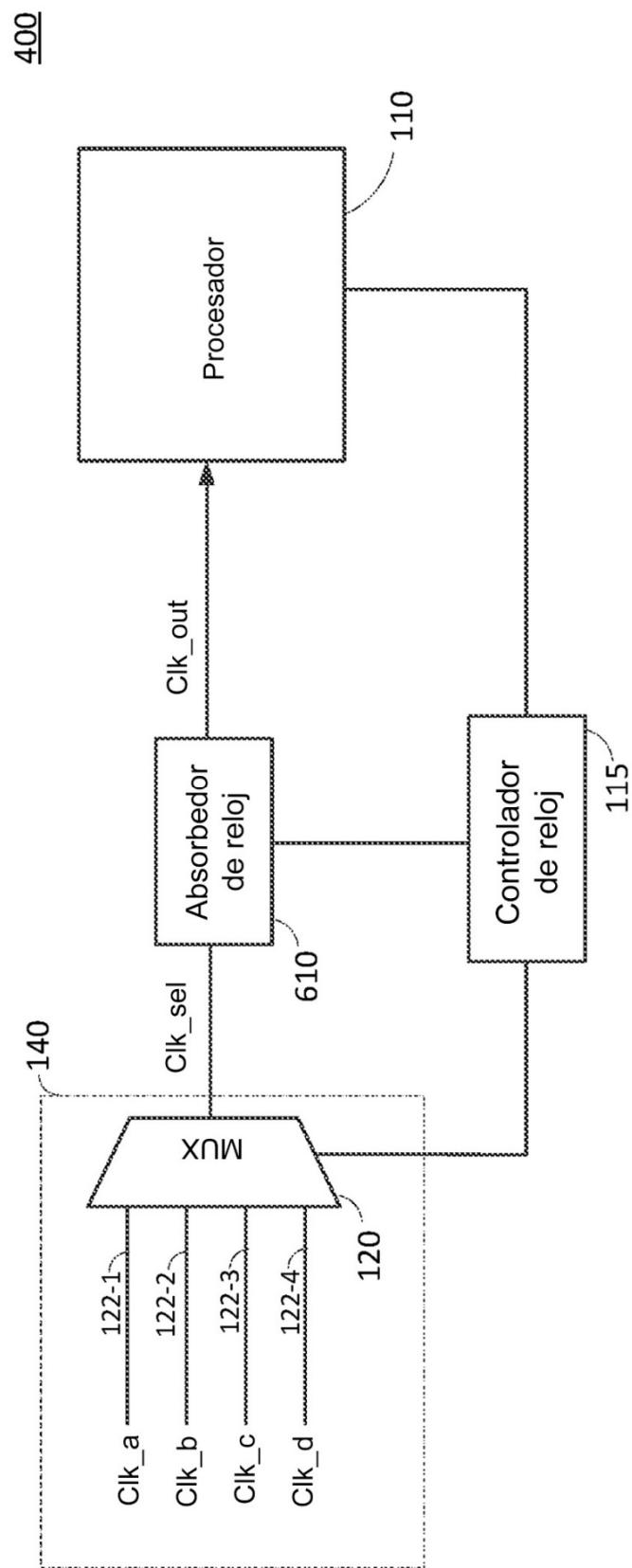

La FIG. 4 muestra un sistema con escalado de frecuencia de acuerdo con un modo de realización de la presente divulgación.

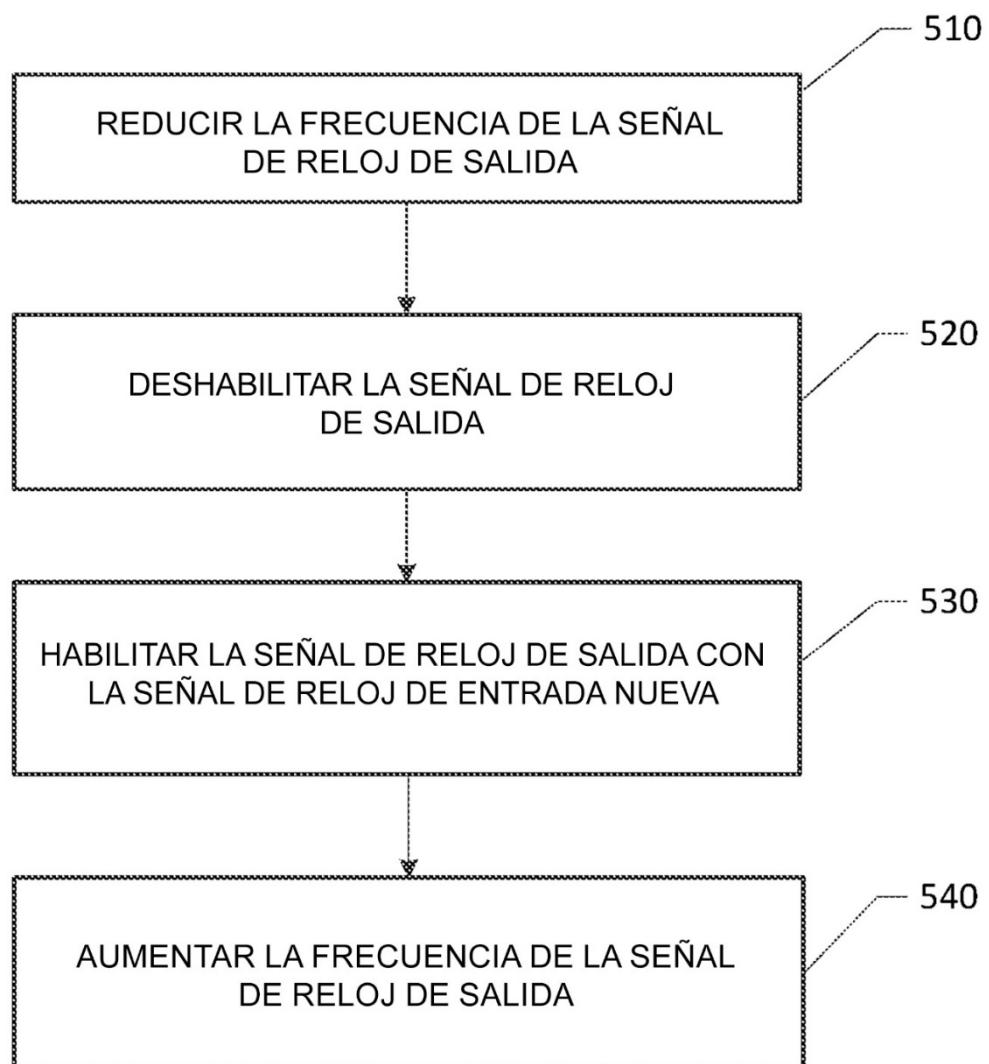

30 La FIG. 5 muestra un procedimiento a modo de ejemplo para el cambio de reloj de acuerdo con un modo de realización de la presente divulgación.

La FIG. 6 muestra un sistema que comprende un吸收edor de reloj de acuerdo con un modo de realización de la presente divulgación.

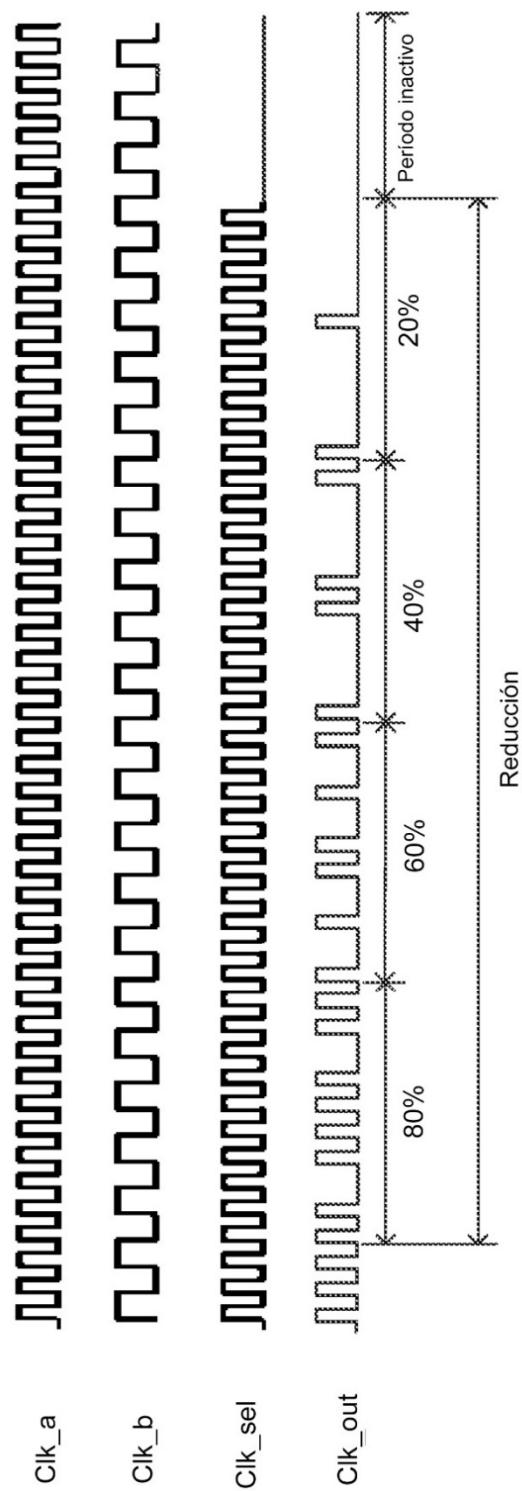

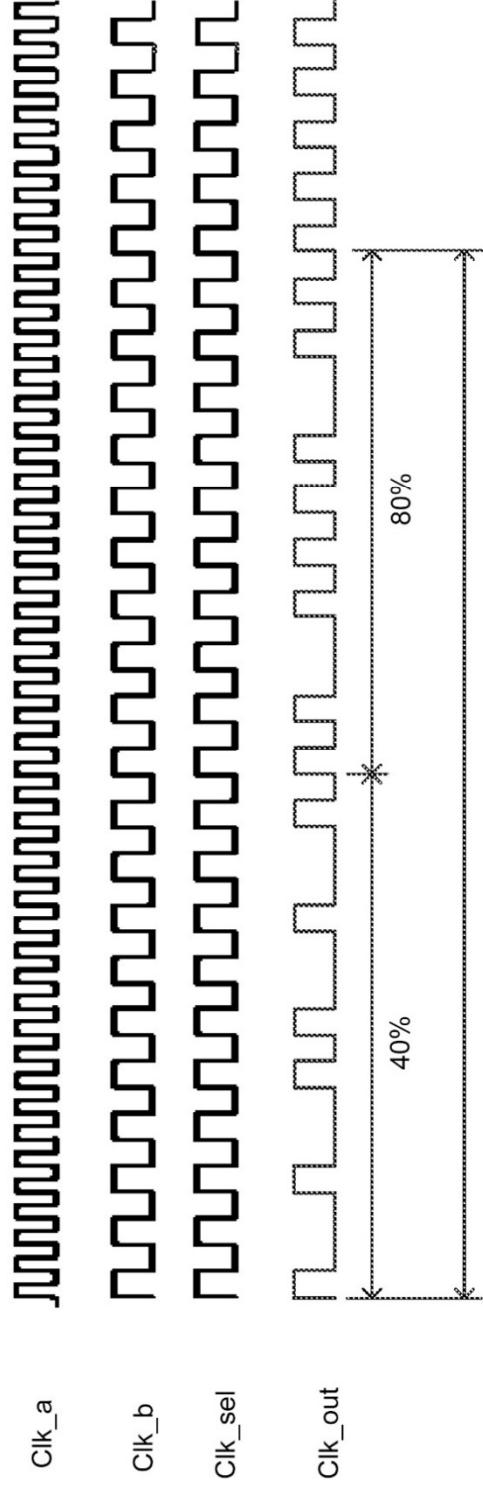

35 Las FIG. 7A y 7B muestran diagramas de tiempo que ilustran un ejemplo de cambio de reloj de acuerdo con un modo de realización de la presente divulgación.

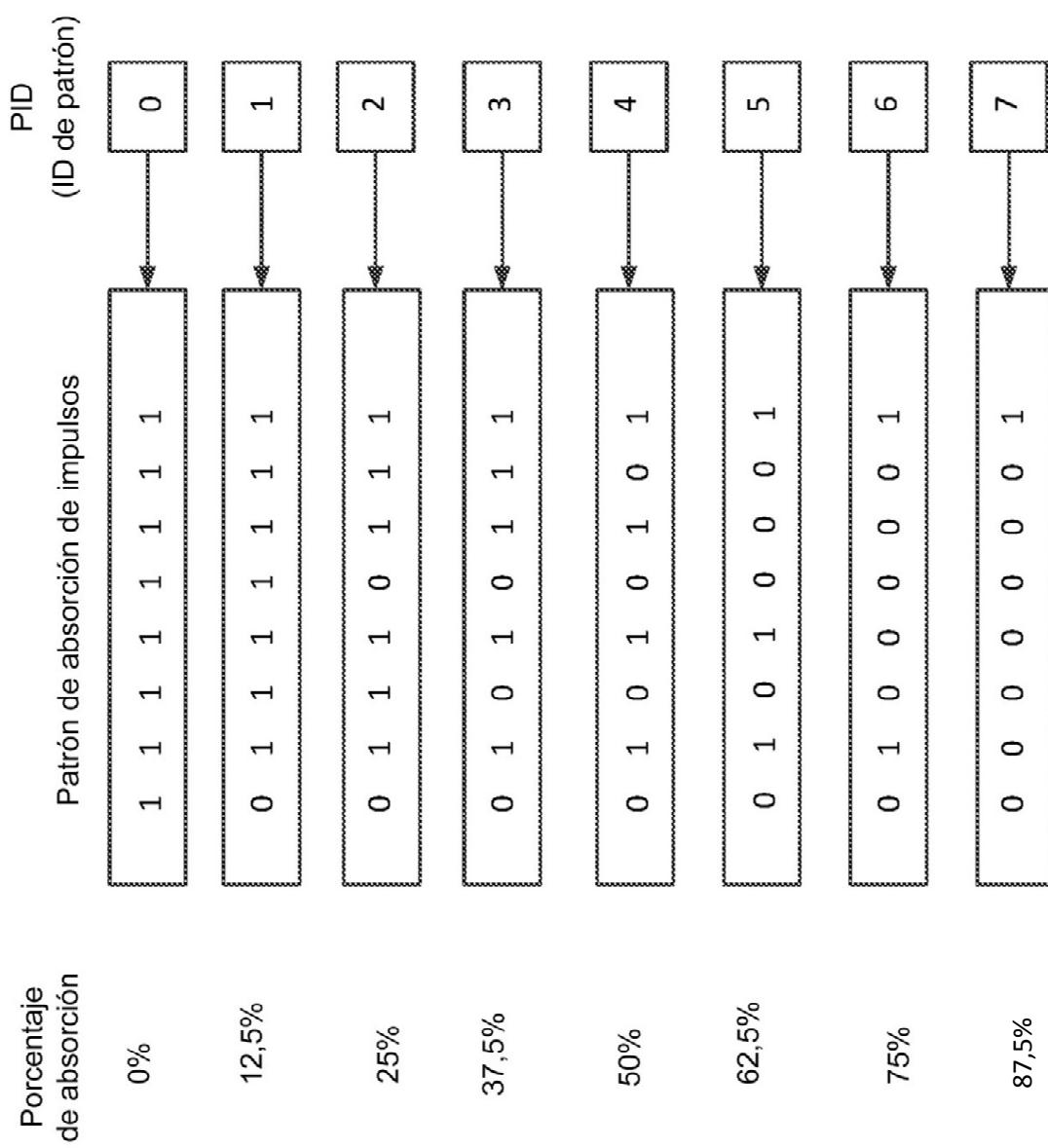

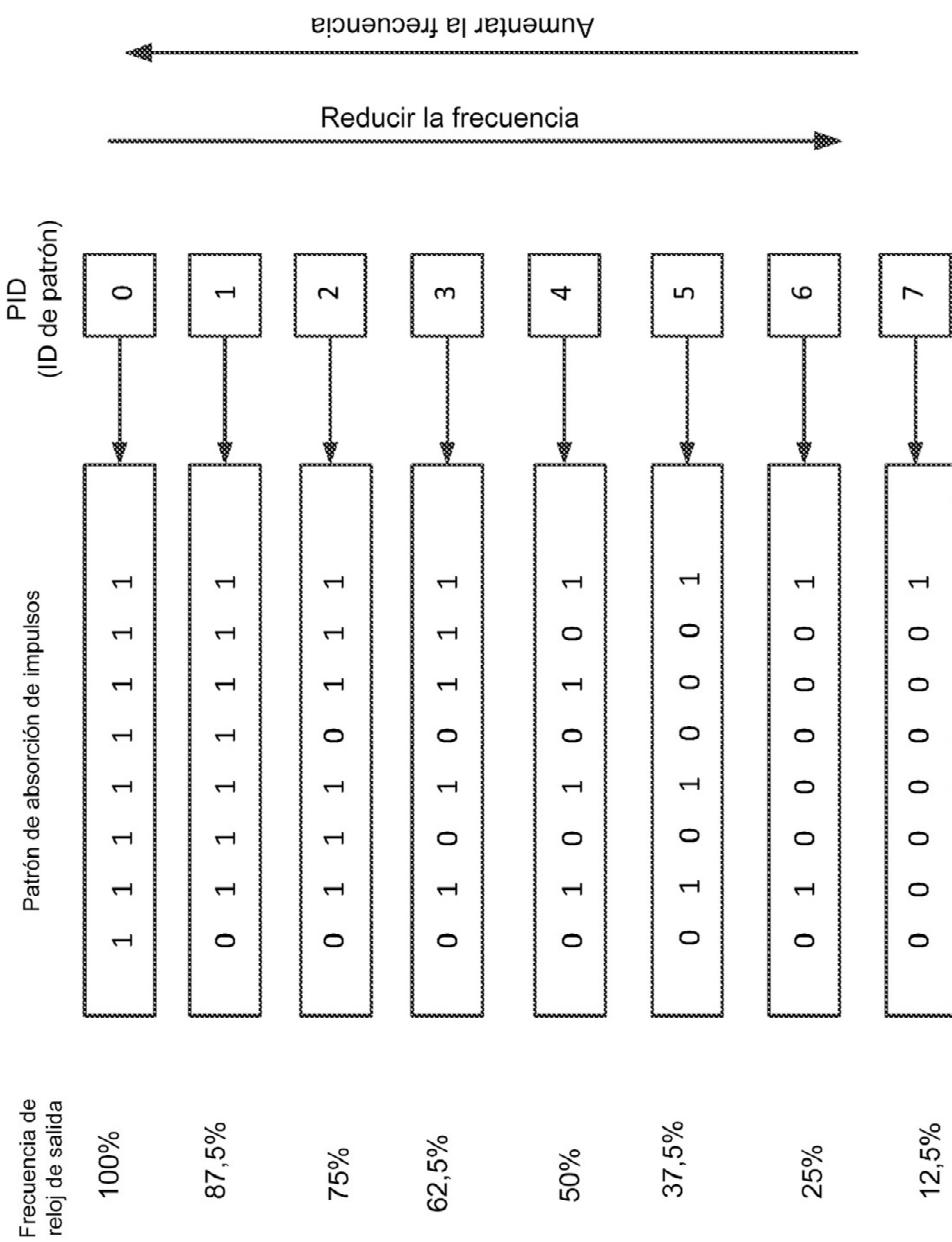

La FIG. 8 muestra patrones de absorción de impulsos a modo de ejemplo de acuerdo con un modo de realización de la presente divulgación.

40 La FIG. 9 muestra un índice de reloj a modo de ejemplo de acuerdo con un modo de realización de la presente divulgación.

45 La FIG. 10 muestra un índice de reloj a modo de ejemplo de acuerdo con otro modo de realización de la presente divulgación.

La FIG. 11 muestra un sistema a modo de ejemplo que comprende un gestor de energía de acuerdo con un modo de realización de la presente divulgación.

50 La FIG. 12 muestra un procedimiento a modo de ejemplo para cambiar un procesador entre un modo activo y un modo inactivo de acuerdo con un modo de realización de la presente divulgación.

La FIG. 13 muestra un sistema a modo de ejemplo con mitigación de temperatura de acuerdo con un modo de realización de la presente divulgación.

55 La FIG. 14 muestra patrones de absorción de impulsos a modo de ejemplo para mitigación de temperatura de acuerdo con un modo de realización de la presente divulgación.

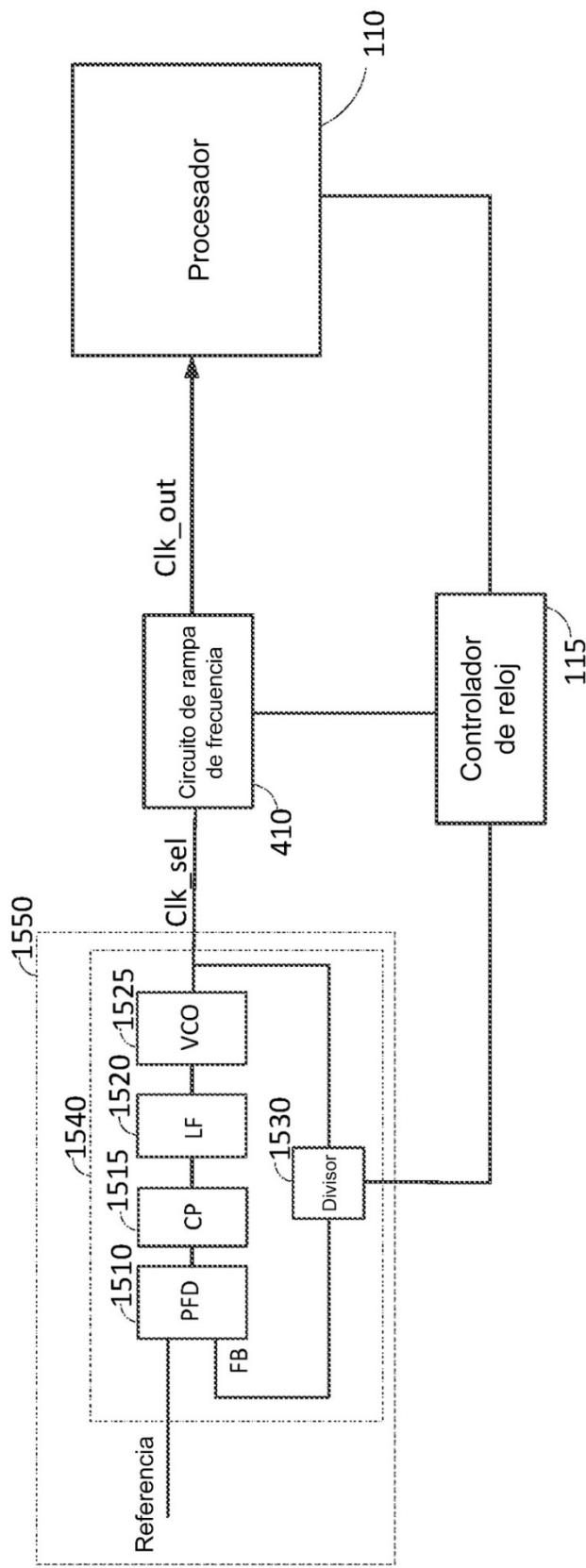

60 La FIG. 15 muestra un circuito de reloj de acuerdo con un modo de realización de la presente divulgación.

## DESCRIPCIÓN DETALLADA

65 [0012] La descripción detallada expuesta a continuación, en relación con los dibujos adjuntos, está concebida como una descripción de diversas configuraciones y no está concebida para representar las únicas configuraciones en las cuales pueden llevarse a la práctica los conceptos descritos en el presente documento. La descripción detallada incluye detalles específicos con el fin de proporcionar un entendimiento exhaustivo de los diversos conceptos. Sin

embargo, resultará evidente para los expertos en la materia que estos conceptos pueden llevarse a la práctica sin estos detalles específicos. En algunos ejemplos, se muestran estructuras y componentes bien conocidos en forma de diagrama de bloques para evitar oscurecer dichos conceptos.

5 [0013] El escalado de frecuencia dinámico se usa ampliamente para cambiar dinámicamente la frecuencia de reloj de un procesador basándose en casos de uso. Por ejemplo, la frecuencia de reloj del procesador puede incrementarse cuando el procesador se está usando para una aplicación de alta velocidad, y puede reducirse cuando el procesador se está usando para una aplicación de baja velocidad para ahorrar energía.

10 [0014] La FIG. 1A muestra un ejemplo de un sistema 100 con escalado de frecuencia dinámico. El sistema 100 comprende un procesador (por ejemplo, CPU, GPU, DSP, etc.) 110, un controlador de reloj 115 y un circuito de reloj 140. El procesador 110 puede alimentarse mediante una fuente de alimentación a través de una red de distribución de energía (PDN) (no mostrada). La fuente de alimentación puede comprender un circuito integrado de gestión de energía (PMIC) u otra fuente de alimentación. Otros circuitos (por ejemplo, uno o más procesadores diferentes) 15 también pueden estar acoplados a la PDN.

20 [0015] El circuito de reloj 140 está configurado para proporcionar una señal de reloj (denominada "Clk\_sel") al procesador 110, y para establecer la señal de reloj en cualquiera de una pluralidad de frecuencias de reloj seleccionables bajo el control del controlador de reloj 115, como se analiza más adelante. En el ejemplo de la FIG. 1A, el circuito de reloj 140 comprende un multiplexor 120 configurado para recibir una pluralidad de señales de reloj de entrada Clk\_a a Clk\_d que tienen diferentes frecuencias de reloj a través de las líneas de reloj 122-1 a 122-4, respectivamente, y para enviar de manera selectiva una de las señales de reloj de entrada Clk\_a a Clk\_d al procesador 110 bajo el control del controlador 115. El multiplexor 120 envía la señal de reloj seleccionada Clk\_sel al procesador 110 a través de una línea de reloj 125.

25 [0016] Las señales de entrada de reloj Clk\_a a Clk\_d se pueden proporcionar mediante diversas fuentes de reloj. En este sentido, la FIG. 1B muestra un ejemplo de un sistema 150 en el que el circuito de reloj 155 comprende un bucle de enganche de fase (PLL) 130, y primer, segundo y tercero divisores de frecuencia 135-1, 135-2 y 135-3. En este ejemplo, la señal de reloj de entrada Clk\_a se proporciona mediante el PLL 130. El PLL 130 puede generar la señal de reloj de entrada Clk\_a multiplicando la frecuencia de una señal de reloj de referencia de un oscilador de cristal (no mostrado) por una cierta cantidad. En el ejemplo de la FIG. 1B, el primer divisor de frecuencia 135-1 divide la frecuencia de la señal de reloj de entrada Clk\_a por una primera cantidad para generar la señal de reloj de entrada Clk\_b, el segundo divisor de frecuencia 135-2 divide la frecuencia de la señal de reloj de entrada Clk\_a por una segunda cantidad para generar la señal de reloj de entrada Clk\_c, y el tercer divisor de frecuencia 135-3 divide la frecuencia de la señal de reloj de entrada Clk\_a por una tercera cantidad para generar la señal de reloj de entrada Clk\_d. En este ejemplo, la señal de reloj de entrada Clk\_a es la señal de reloj de frecuencia más alta.

30 [0017] La FIG. 1C muestra otro ejemplo de un sistema 160 en el que el circuito de reloj 165 comprende un primer PLL 140-1, un segundo PLL 140-2, un primer divisor de frecuencia 145-1 y un segundo divisor de frecuencia 145-2. En este ejemplo, la señal de reloj de entrada Clk\_a se proporciona mediante el primer PLL 140-1, y la señal de reloj de entrada Clk\_c se proporciona mediante el segundo PLL 140-2. El primer PLL 140-1 puede generar la señal de reloj de entrada Clk\_a multiplicando la frecuencia de una señal de reloj de referencia de un oscilador de cristal (no mostrado) por una primera cantidad, y el segundo PLL 140-2 puede generar la señal de reloj de entrada Clk\_c multiplicando la frecuencia de la señal de reloj de referencia por una segunda cantidad. En el ejemplo de la FIG. 1C, el primer divisor de frecuencia 145-1 divide la frecuencia de la señal de reloj de entrada Clk\_a por una tercera cantidad para generar la señal de reloj de entrada Clk\_b, y el segundo divisor de frecuencia 145-2 divide la frecuencia de la señal de reloj de entrada Clk\_c por una cuarta cantidad para generar señal de reloj de entrada Clk\_d. En este ejemplo, la señal de reloj de entrada Clk\_a o bien la señal de reloj de entrada Clk\_c es la señal de reloj de frecuencia más alta. El primer y segundo divisores de frecuencia pueden dividir su respectiva señal de reloj por la misma cantidad (por ejemplo, divisor).

40 [0018] Debe apreciarse que la presente divulgación no se limita a los ejemplos mostrados en las FIG. 1B y 1C, y que las señales de reloj de entrada Clk\_a a Clk\_d pueden generarse usando cualquier disposición de PLL, divisores de frecuencia y/u otros componentes. También debe apreciarse que el multiplexor 120 puede multiplexar cualquier 45 número de señales de reloj de entrada, y por lo tanto no está limitado al ejemplo de cuatro señales de reloj de entrada mostradas en las FIG. 1A a 1C.

50 [0019] En operación, el multiplexor 120 selecciona una de las señales de reloj de entrada Clk\_a a Clk\_d a la vez, y envía la señal de reloj seleccionada Clk\_sel al procesador 110 a través de la línea de reloj 125. El procesador 110 usa la señal de reloj seleccionada Clk\_sel para operaciones de conmutación temporal en el procesador 110. Por ejemplo, las puertas lógicas (por ejemplo, transistores) en el procesador 110 pueden conmutar de acuerdo con la frecuencia de la señal de reloj seleccionada Clk\_sel. Cuanto mayor sea la frecuencia de la señal de reloj seleccionada Clk\_sel, más rápida será la conmutación de las puertas lógicas en el procesador 110, lo que se traduce en una velocidad de procesamiento más rápida.

**[0020]** El controlador de reloj 115 está configurado para cambiar dinámicamente la frecuencia de reloj del procesador 110 basándose en casos de uso cambiando la señal de reloj de entrada seleccionada mediante el multiplexor 120. Por ejemplo, el procesador 110 puede determinar una carga de procesamiento del procesador 110, determinar una frecuencia de reloj basándose en la carga de procesamiento determinada, e indicar al controlador de reloj 115 que establezca la frecuencia de la señal de reloj *Clk\_sel* de acuerdo con la frecuencia de reloj determinada. En este ejemplo, el procesador 110 puede indicar al controlador de reloj 115 que cambie la frecuencia del reloj debido, por ejemplo, a un cambio en las cargas de procesamiento. Por ejemplo, si el procesador 110 lanza una aplicación que requiere mayor velocidad, entonces el procesador 110 puede indicar al controlador de reloj 115 que cambie a una frecuencia de reloj más alta. Por tanto, el controlador de reloj 115 puede cambiar las señales de reloj de entrada basándose en las necesidades de procesamiento del procesador 110.

**[0021]** El multiplexor 120 puede generar un fallo cuando el multiplexor 120 cambia entre dos señales de reloj de entrada, especialmente si el multiplexor 120 opera de forma asíncrona con una o ambas señales de reloj. En este ejemplo, se puede generar un fallo si el multiplexor 120 cambia entre las dos señales de reloj de entrada cuando una o ambas señales de reloj son altas, lo que resulta en el recorte de una o ambas de las señales de reloj. Para evitar fallos, el multiplexor 120 puede implementarse uso un multiplexor libre de fallos.

**[0022]** En este sentido, la FIG. 2 muestra un ejemplo de una implementación libre de fallos del multiplexor 120. En este ejemplo, el multiplexor 120 comprende un multiplexor 210, lógica de control de multiplexor 215, un primer sincronizador 220-1, un segundo sincronizador 220-2, un tercer sincronizador 220-3 y un cuarto sincronizador 220-4. Cada uno de los sincronizadores 220-1 a 220-4 comprende tres biestables activados por flanco negativo acoplados en serie, como se muestra en la FIG. 2. Los biestables en el primer sincronizador 220-1 se sincronizan usando la señal de reloj *Clk\_a*, los biestables en el segundo sincronizador 220-2 se sincronizan usando la señal de reloj *Clk\_b*, los biestables en el tercer sincronizador 220-3 se sincronizan usando la señal de reloj *Clk\_c* y los biestables en el cuarto sincronizador 220-4 se sincronizan usando la señal de reloj *Clk\_d*. Aunque no se muestra de manera explícita en la FIG. 2, cada sincronizador puede estar acoplado a la línea de reloj de la señal de reloj respectiva para recibir la señal de reloj respectiva.

**[0023]** La lógica de control 215 está configurada para seleccionar una de las señales de reloj de entrada *Clk\_a* a *Clk\_d* y deseleccionar las señales de reloj de entrada restantes *Clk\_a* a *Clk\_d*. Para hacer esto, la lógica de control 215 envía una señal de selección/deselección para cada una de las señales de reloj de entrada *Clk\_a* a *Clk\_d* al multiplexor 210 a través de uno respectivo de los sincronizadores 220-1 a 220-4. Más concretamente, la lógica de control 215 envía una señal de selección/deselección (denominada "sel\_a/unsel\_a") para la señal de reloj de entrada *Clk\_a* a través del primer sincronizador 220-1, envía una señal de selección/deselección (denominada "sel\_b/unsel\_b") para la señal de reloj de entrada *Clk\_b* a través del segundo sincronizador 220-2, envía una señal de selección/deselección (denominada "sel\_c/unsel\_c") para la señal de reloj de entrada *Clk\_c* a través del tercer sincronizador 220-3, y envía una selección/deselección (denominada "sel\_d/unsel\_d") para la señal de reloj de entrada *Clk\_d* a través del cuarto sincronizador 220-4. Cuando el multiplexor 210 recibe una señal de selección para una señal de reloj de entrada, el multiplexor 210 envía la señal de reloj de entrada al procesador 110. Cuando el multiplexor 210 recibe una señal de deselección para una señal de reloj de entrada, el multiplexor 210 deshabilita el envío de la señal de reloj de entrada. En este ejemplo, una señal de selección puede corresponder al uno lógico y una señal de deselección puede corresponder al cero lógico, o viceversa.

**[0024]** En un momento dado, la lógica de control 215 puede enviar una señal de selección para una seleccionada de las señales de reloj de entrada y enviar señales de deselección para las señales de reloj deseleccionadas restantes. En este sentido, la lógica de control 215 puede recibir una señal de control de reloj del controlador 115 que indica qué señal de reloj de entrada debe seleccionar. En respuesta, la lógica de control 215 puede enviar una señal de selección para la señal de reloj de entrada indicada mediante la señal de control, y enviar señales de deselección para las señales de reloj de entrada restantes.

**[0025]** En un aspecto, la salida 225-1 a 225-4 de cada uno de los sincronizadores 220-1 a 220-4 se retroalimenta a la lógica de control 215, como se muestra en la FIG. 2. Esto permite que la lógica de control 215 determine cuándo el multiplexor 210 deja de enviar una señal de reloj durante el cambio de reloj, como se analiza en detalle más adelante.

**[0026]** Para cambiar la salida del multiplexor 210 de una actual de las señales de reloj de entrada *Clk\_a* a *Clk\_d* a una nueva de las señales de reloj de entrada *Clk\_a* a *Clk\_d*, la lógica de control 215 puede deshabilitar en primer lugar el envío de la señal de reloj de entrada actual enviando una señal de deselección para la señal de reloj actual. La señal de deselección se propaga a través del sincronizador respectivo, que envía la señal de deselección al multiplexor 210. El sincronizador respectivo sincroniza el envío de la señal de deselección con la señal de reloj de entrada actual. El sincronizador respectivo sincroniza el envío de la señal de deselección con la señal de reloj de entrada actual de tal manera que la señal de deselección se envía al multiplexor 210 cuando la señal de reloj de entrada actual es baja. Esto se debe a que los biestables en el sincronizador respectivo se activan por flanco negativo. Como resultado, el multiplexor 210 deshabilita el envío de la señal de reloj de entrada actual cuando la señal de reloj de entrada actual es baja, lo que evita fallos. En este punto, todas las señales de reloj de entrada están deseleccionadas, y el multiplexor 120 deja de enviar una señal de reloj al procesador 110.

5 [0027] La señal de desección enviada mediante el respectivo sincronizador se retroalimenta a la lógica de control 215, indicando a la lógica de control 215 que el envío de la señal de reloj de entrada actual se ha deshabilitado en el multiplexor 210. En respuesta, la lógica de control 215 envía una señal de selección para la señal de reloj de entrada nueva. La señal de selección se propaga a través del sincronizador respectivo, que envía la señal de selección al multiplexor 210. El sincronizador respectivo sincroniza el envío de la señal de selección con la señal de reloj de entrada nueva de tal manera que la señal de selección se envía al multiplexor 210 cuando la señal de reloj de entrada nueva es baja. Esto se debe a que los biestables en el sincronizador respectivo se activan por flanco negativo. Como resultado, el multiplexor 210 habilita el envío de la señal de reloj de entrada nueva cuando la señal de reloj de entrada nueva es baja, lo que evita fallos.

10 10 [0028] En el ejemplo anterior, hay un período inactivo entre el momento en que el envío de la señal de reloj actual se deshabilita en el multiplexor 210 y el momento en que el envío de la señal de reloj nueva se habilita en el multiplexor 210. Durante el período inactivo, el multiplexor 210 no envía una señal de reloj al procesador 110. El período inactivo puede ser aproximadamente igual al retardo de propagación del sincronizador usado para sincronizar la señal de selección para la señal de reloj nueva con la señal de reloj nueva. En el ejemplo de la FIG. 2, el período inactivo puede abarcar al menos tres ciclos de la señal de reloj nueva, ya que la señal de selección para la señal de reloj nueva debe propagarse a través de tres biestables en el sincronizador respectivo para alcanzar el multiplexor 210. El período inactivo también se puede denominar período muerto o con otra terminología.

20 20 [0029] La FIG. 3 muestra un diagrama de tiempo en el que la señal de reloj seleccionada Clk\_sel del multiplexor 210 se cambia de la señal de reloj de entrada Clk\_a a la señal de reloj de entrada Clk\_b. En este ejemplo, el reloj seleccionado Clk\_sel se proporciona (se origina) inicialmente mediante la señal de reloj de entrada Clk\_a. En el tiempo t1, el envío de la señal de reloj Clk\_a se deshabilita en el multiplexor 210. Durante un período inactivo, el multiplexor 210 no envía una señal de reloj. El período inactivo puede abarcar aproximadamente tres ciclos de la señal de reloj Clk\_b para el ejemplo de la FIG. 2. Al final del período inactivo en el tiempo t2, el envío de la señal de reloj Clk\_b se habilita en el multiplexor 210.

30 30 [0030] Debe apreciarse que el multiplexor 120 no está limitado a la implementación a modo de ejemplo mostrada en la FIG. 2, y, por lo tanto, que el multiplexor 120 puede implementarse usando otros circuitos. También debe apreciarse que otras implementaciones libres de fallos del multiplexor 120 también pueden tener un período inactivo (es decir, un período sin envío de reloj) durante el cambio de reloj.

35 35 [0031] El período inactivo durante el cambio de reloj provoca un exceso de voltaje en la PDN cuando el envío de reloj del multiplexor 120 se deshabilita y una caída de voltaje en la PDN cuando el envío de reloj del multiplexor 120 se habilita con la señal de reloj de entrada nueva. La magnitud del exceso depende de la frecuencia de la señal de reloj de entrada actual. Cuanto mayor sea la frecuencia de la señal de reloj de entrada actual, mayor será el exceso. Esto se debe a que una frecuencia de reloj más alta da como resultado una mayor tasa de cambio en la carga actual de la PDN cuando el envío de la señal de reloj de entrada actual se deshabilita en el multiplexor 120. De manera similar, la magnitud de la caída depende de la frecuencia de la señal de reloj de entrada nueva. Cuanto mayor sea la frecuencia de la señal de reloj de entrada nueva, mayor será la caída. Esto se debe a que una frecuencia de reloj más alta resulta en una mayor tasa de cambio en la carga actual de la PDN cuando el envío de la señal de reloj de entrada nueva se habilita en el multiplexor 120. Si el exceso y/o la caída de voltaje son demasiado altos, entonces el exceso y/o la caída pueden hacer que otros circuitos (no mostrados) que están acoplados a la PDN funcionen incorrectamente. Por consiguiente, son deseables técnicas para reducir el exceso y/o la caída en la PDN durante el cambio de reloj.

45 45 [0032] Los modos de realización de la presente divulgación reducen el exceso y/o la caída de voltaje en la PDN durante el cambio de reloj reduciendo la frecuencia de la señal de reloj para el procesador 110 antes de que se deshabilite la señal de reloj de entrada actual y/o aumentando la frecuencia de la señal de reloj para el procesador 110 cuando se habilita la señal de reloj de entrada nueva, como se analiza en detalle más adelante.

50 50 [0033] La FIG. 4 muestra un sistema a modo de ejemplo 400 con escalado de frecuencia dinámico de acuerdo con un modo de realización de la presente divulgación. El sistema 400 comprende un circuito de rampa de frecuencia 410 acoplado entre el circuito de reloj 140 y el procesador 110. El circuito de rampa de frecuencia 410 está configurado para reducir y/o aumentar la frecuencia de la señal de reloj seleccionada Clk\_sel, y enviar la señal de reloj ajustada en frecuencia resultante (denominada "Clk\_out") al procesador 110, como se analiza en detalle más adelante.

60 60 [0034] Cuando la salida del multiplexor 120 cambia de una actual de las señales de reloj de entrada Clk\_a a Clk\_d a una nueva de las señales de reloj de entrada Clk\_a a Clk\_d, el circuito de rampa de frecuencia 410 puede reducir la frecuencia de la señal de reloj de salida Clk\_out antes de que se deshabilite la señal de reloj de entrada actual. Durante la reducción, la señal de reloj de salida se proporciona (se origina) mediante la señal de reloj de entrada actual. El circuito de rampa de frecuencia 410 puede reducir la frecuencia de la señal de reloj de salida Clk\_out usando cualquiera de diversas técnicas, como se analiza en detalle más adelante. Disminuir la frecuencia de la señal de reloj de salida Clk\_out hace que la carga actual en la PDN disminuya a una velocidad más lenta en comparación con la detención brusca de la señal de reloj de salida a frecuencia máxima (es decir, la frecuencia de la señal de reloj de entrada actual), reduciendo así el exceso de voltaje en la PDN.

**[0035]** El circuito de rampa de frecuencia 410 puede aumentar la frecuencia de la señal de reloj de salida Clk\_out cuando se habilita la señal de reloj de entrada nueva. Durante el aumento, la señal de reloj de salida Clk\_out se proporciona (se origina) mediante la señal de reloj de entrada nueva. El circuito de rampa de frecuencia 410 puede aumentar la frecuencia de la señal de reloj de salida Clk\_out usando cualquiera de diversas técnicas, como se analiza en detalle más adelante. Aumentar la frecuencia de la señal de reloj de salida Clk\_out hace que la carga actual en la PDN aumente a una velocidad más lenta en comparación con el envío brusco de la señal de reloj de salida Clk\_out a frecuencia máxima (es decir, la frecuencia de la señal de reloj de entrada nueva), reduciendo así caída de voltaje en la PDN.

5 **[0036]** En un modo de realización, el circuito de rampa de frecuencia 410 puede reducir la frecuencia de la señal de reloj de salida Clk\_out en una o más etapas, en las que la frecuencia de la señal de reloj de salida se reduce en cierta cantidad en cada etapa. La duración temporal de cada etapa puede estar predeterminada. Por ejemplo, si el circuito de rampa de frecuencia 410 reduce la frecuencia de la señal de reloj de salida Clk\_out en una pluralidad de etapas, el circuito de rampa de frecuencia 410 puede reducir la frecuencia de la señal de reloj de salida Clk\_out a una frecuencia más baja en cada etapa.

10 **[0037]** En un modo de realización, el circuito de rampa de frecuencia 410 puede aumentar la frecuencia de la señal de reloj de salida Clk\_out en una o más etapas, en las que la frecuencia de la señal de reloj de salida se aumenta en cierta cantidad en cada etapa. La duración temporal de cada etapa puede estar predeterminada. Por ejemplo, si el circuito de rampa de frecuencia 410 aumenta la frecuencia de la señal de reloj de salida Clk\_out en una pluralidad de etapas, el circuito de rampa de frecuencia 410 puede aumentar la frecuencia de la señal de reloj de salida Clk\_out a una frecuencia más alta en cada etapa.

15 **[0038]** En un ejemplo, el circuito de rampa de frecuencia 410 puede comprender un divisor de frecuencia que reduce la frecuencia de la señal de reloj de salida Clk\_out dividiendo la frecuencia de la señal de reloj seleccionada Clk\_sel introducida en el circuito de rampa 410 por una cantidad controlable. En este ejemplo, la señal de reloj de salida Clk\_out es la señal de reloj seleccionada Clk\_sel dividida en frecuencia. El circuito de rampa de frecuencia 410 puede reducir la frecuencia de la señal de reloj de salida Clk\_out en una cantidad creciente a lo largo del tiempo para la reducción aumentando la cantidad (por ejemplo, el divisor) por la que la frecuencia de la señal de reloj seleccionada Clk\_sel se divide a lo largo del tiempo. Además, el circuito de rampa de frecuencia 410 puede aumentar la frecuencia de la señal de reloj de salida Clk\_out en una cantidad creciente a lo largo del tiempo para el aumento reduciendo la cantidad (por ejemplo, el divisor) por la que la frecuencia de la señal de reloj seleccionada Clk\_sel se divide a lo largo del tiempo. En este ejemplo, la frecuencia máxima de la señal de reloj de salida Clk\_out puede producirse cuando el divisor es uno, en cuyo caso la frecuencia de la señal de reloj de salida Clk\_out es aproximadamente igual a la frecuencia de la señal seleccionada Clk\_sel.

20 **[0039]** En otro ejemplo, el circuito de rampa de frecuencia 410 puede comprender un absorbedor de reloj que reduce la frecuencia de la señal de reloj de salida Clk\_out absorbiendo de manera selectiva impulsos de la señal de reloj seleccionada Clk\_sel introducidos en el circuito de rampa 410. En este ejemplo, la señal de reloj de salida Clk\_out es la señal de reloj seleccionada Clk\_sel con absorción de impulsos. El circuito de rampa de frecuencia 410 puede reducir la frecuencia de la señal de reloj de salida Clk\_out en una cantidad creciente a lo largo del tiempo para la reducción aumentando el porcentaje de impulsos de la señal de reloj seleccionada Clk\_out que se absorben a lo largo del tiempo. Además, el circuito de rampa de frecuencia 410 puede aumentar la frecuencia de la señal de reloj de salida en una cantidad creciente a lo largo del tiempo para el aumento disminuyendo el porcentaje de impulsos de la señal de reloj seleccionada Clk\_sel que se absorben a lo largo del tiempo. En este ejemplo, la frecuencia máxima de la señal de reloj de salida Clk\_out puede producirse cuando no se absorbe ningún impulso de la señal de reloj seleccionada Clk\_sel, en cuyo caso la frecuencia de la señal de reloj de salida Clk\_out es aproximadamente igual a la frecuencia de la señal seleccionada Clk\_sel.

25 **[0040]** La FIG. 5 muestra un procedimiento a modo de ejemplo 500 para la reducción de frecuencia y el aumento de frecuencia durante el cambio de reloj de acuerdo con un modo de realización de la presente divulgación. El procedimiento 500 puede realizarse mediante el controlador 115, el multiplexor 120 y/o el circuito de rampa 410. El procedimiento 500 se puede realizar cuando el envío de reloj al procesador 110 cambia de una actual de las señales de reloj de entrada Clk\_a a Clk\_d a una nueva de las señales de reloj de entrada Clk\_a a Clk\_d.

30 **[0041]** En la etapa 510, la frecuencia de la señal de reloj de salida Clk\_out se reduce. Durante la reducción, la señal de reloj de salida Clk\_out se proporciona (se origina) mediante la señal de reloj de entrada actual. El circuito de rampa de frecuencia 410 puede realizar esta etapa dividiendo en frecuencia la señal de reloj seleccionada Clk\_sel por una cantidad creciente a lo largo del tiempo o absorbiendo un porcentaje creciente de impulsos de reloj de la señal de reloj seleccionada Clk\_sel a lo largo del tiempo.

35 **[0042]** En la etapa 520, se deshabilita la señal de reloj de salida Clk\_out. Por ejemplo, el controlador 115 puede deshabilitar la señal de reloj de salida Clk\_out indicando al multiplexor 120 que deshabilite el envío de la señal de reloj seleccionada Clk\_sel al circuito de rampa cuando el circuito de rampa de frecuencia 410 completa la reducción de la señal de reloj de salida Clk\_out.

**[0043]** En la etapa 530, se habilita la señal de reloj de salida Clk\_out usando la señal de reloj de entrada nueva. Por ejemplo, el multiplexor 120 puede habilitar la señal de reloj de salida habilitando el envío de la señal de reloj seleccionada Clk\_sel al circuito de rampa 410 después de un período inactivo para evitar fallos. En este ejemplo, el multiplexor 120 puede habilitar la señal de reloj de salida usando la señal de reloj de entrada nueva seleccionando la señal de reloj de entrada nueva después de que se deshabilita la señal de reloj de entrada actual.

**[0044]** En la etapa 540, se aumenta la frecuencia de la señal de reloj de salida Clk\_out. Durante el aumento, la señal de reloj de salida Clk\_out se proporciona (se origina) mediante la señal de reloj de entrada nueva. El circuito de rampa de frecuencia 410 puede realizar esta etapa dividiendo en frecuencia la señal de reloj seleccionada Clk\_sel por una cantidad decreciente a lo largo del tiempo o absorbiendo un porcentaje decreciente de impulsos de reloj de la señal de reloj seleccionada Clk\_sel a lo largo del tiempo. En un aspecto, el multiplexor 120 puede enviar una señal al controlador 115 que indica cuándo se habilita la señal de reloj seleccionada Clk\_sel. En respuesta, el controlador 115 puede activar el circuito de rampa 410 para iniciar el aumento.

**[0045]** La FIG. 6 muestra un ejemplo en el que el circuito de rampa de frecuencia 410 en la FIG. 4 comprende un absorbedor de reloj 610. El absorbedor de reloj 610 está configurado para reducir la frecuencia de la señal de reloj de salida Clk\_out en una cantidad variable absorbiendo de manera selectiva impulsos de la señal de reloj seleccionada Clk\_sel introducida en el circuito de rampa 410, como se ha analizado anteriormente. En este ejemplo, la señal de reloj de salida Clk\_out es la señal de reloj seleccionada Clk\_sel con absorción de impulsos.

**[0046]** Las operaciones ejemplares del absorbedor de reloj 610 se describirán a continuación con referencia a las FIG. 7A y 7B. Las FIG. 7A y 7B muestran diagramas de tiempo a modo de ejemplo de las señales de reloj de entrada Clk\_a y Clk\_b, en las que el multiplexor 120 cambia de la señal de reloj de entrada Clk\_b a la señal de reloj de entrada Clk\_a. Las FIG. 7A y 7B también muestran la señal de reloj seleccionada Clk\_sel introducida en el absorbedor de reloj 610, y la señal de reloj de salida Clk\_out para el procesador 110.

**[0047]** Antes del período inactivo, el absorbedor de reloj 610 reduce la frecuencia de la señal de reloj de salida Clk\_out en cuatro etapas. Durante la reducción, la señal de reloj de salida Clk\_out se proporciona (se origina) mediante la señal de reloj de entrada Clk\_a. En la primera etapa, el absorbedor de reloj 610 absorbe el 20% de los impulsos de la señal de reloj seleccionada Clk\_sel para reducir la frecuencia de la señal de reloj de salida Clk\_out al 80% de la frecuencia de la señal de reloj de entrada Clk\_a, como se muestra en la FIG. 7A. En la segunda etapa, el absorbedor de reloj 610 absorbe el 40% de los impulsos de la señal de reloj seleccionada Clk\_sel para reducir la frecuencia de la señal de reloj de salida Clk\_out al 60% de la frecuencia de la señal de reloj de entrada Clk\_a. En la tercera etapa, el absorbedor de reloj 610 absorbe el 60% de los impulsos de la señal de reloj seleccionada Clk\_sel para reducir la frecuencia de la señal de reloj de salida al 40% de la frecuencia de la señal de reloj de entrada Clk\_a. Finalmente, en la cuarta etapa, el absorbedor de reloj 610 absorbe el 80% de los impulsos de la señal de reloj seleccionada Clk\_sel para reducir la frecuencia de la señal de reloj de salida al 20% de la frecuencia de la señal de reloj de entrada Clk\_a. Por tanto, en cada etapa subsiguiente, el absorbedor de reloj 610 absorbe un mayor porcentaje de impulsos de reloj.

**[0048]** El multiplexor 120 deshabilita entonces la señal de reloj seleccionada Clk\_sel (es decir, deshabilita el envío de la señal de reloj Clk\_a), lo que reduce la frecuencia de la señal de reloj de salida Clk\_out a cero. Por tanto, en este ejemplo, la frecuencia de la señal de reloj de salida Clk\_out (que inicialmente se proporciona mediante la señal de reloj de entrada Clk\_a) se reduce en etapas del 20% en lugar de ir bruscamente a cero. La reducción de frecuencia reduce el exceso de voltaje en la PDN en comparación con deshabilitar bruscamente la señal de reloj de salida Clk\_a a frecuencia máxima, como se muestra en la FIG. 3.

**[0049]** Despues de que se deshabilita la señal de reloj de salida Clk\_out, el multiplexor 120 no envía una señal de reloj durante un período inactivo para evitar fallos, como se muestra en la FIG. 7A. Al final del período inactivo, el multiplexor 130 habilita la señal de reloj seleccionada Clk\_sel con la señal de reloj de entrada Clk\_b. Como se muestra en la FIG. 7B, el absorbedor de reloj 610 aumenta la frecuencia de la señal de reloj de salida Clk\_out a la frecuencia de la señal de reloj de entrada Clk\_b en tres etapas. En la primera etapa, el absorbedor de reloj 610 absorbe el 60% de los impulsos de reloj de la señal de reloj seleccionada Clk\_sel para aumentar la frecuencia de la señal de reloj de salida Clk\_out de cero al 40% de la frecuencia de la señal de reloj Clk\_b, como se muestra en la FIG. 7B. En la segunda etapa, el absorbedor de reloj 610 absorbe el 20% de los impulsos de reloj de la señal de reloj seleccionada Clk\_sel para aumentar la frecuencia de la señal de reloj de salida Clk\_out al 80% de la frecuencia de la señal de reloj Clk\_b. Finalmente, en la tercera etapa, el absorbedor de reloj 610 deja de absorber impulsos de reloj de la señal de reloj seleccionada Clk\_sel, aumentando así la frecuencia de la señal de reloj de salida Clk\_out a la frecuencia máxima de la señal de reloj Clk\_b. Por tanto, en cada etapa subsiguiente, el absorbedor de reloj 610 absorbe un porcentaje menor de impulsos de reloj. El aumento de frecuencia reduce la caída de voltaje en la PDN durante el cambio de frecuencia en comparación con enviar bruscamente la señal de reloj de salida Clk\_out a frecuencia máxima, como se muestra en la FIG. 3. Debe apreciarse que las secuencias de reducción y aumento mostradas en las FIG. 7A y 7B son solo a modo de ejemplo. A continuación se proporcionan otros ejemplos de secuencias de reducción y aumento.

**[0050]** En un modo de realización, el absorbedor de reloj 610 puede usar diferentes secuencias de reducción dependiendo de la frecuencia de la señal de reloj de entrada que proporciona (origina) la señal de reloj de salida. Por ejemplo, la secuencia de reducción para una señal de reloj de entrada de alta frecuencia puede tener más etapas y

reducir la frecuencia en un porcentaje menor en cada etapa en comparación con una secuencia de reducción para un reloj de entrada de frecuencia más baja. Esto se debe a que un reloj de frecuencia más baja corresponde a menos carga actual en la PDN del procesador 110 y, por lo tanto, a menos exceso. Si la frecuencia de la señal de reloj de entrada es lo suficientemente baja, la señal de reloj de salida puede deshabilitarse sin reducción. Esto se debe a que la baja frecuencia de la señal de reloj de entrada puede dar lugar a un exceso relativamente pequeño que está dentro de un límite aceptable. En este caso, el absorbedor de reloj 610 puede no realizar absorción de reloj.

**[0051]** En un modo de realización, el absorbedor de reloj 610 puede usar diferentes secuencias de aumento dependiendo de la frecuencia de la señal de reloj de entrada que proporciona (origina) la señal de reloj de salida. Por ejemplo, la secuencia de aumento para una señal de reloj de entrada de alta frecuencia puede tener más etapas y aumentar la frecuencia en un porcentaje menor en cada etapa en comparación con una secuencia de aumento para un reloj de entrada de frecuencia más baja. Esto se debe a que un reloj de frecuencia más baja corresponde a menos carga actual en la PDN del procesador 110 y, por lo tanto, a menos caída. Si la frecuencia de la señal de reloj de entrada es lo suficientemente baja, la señal de reloj de salida puede habilitarse después del período inactivo sin aumento. Esto se debe a que la baja frecuencia de la señal de reloj de entrada puede dar lugar a una caída relativamente pequeña que está dentro de un límite aceptable. En este caso, el absorbedor de reloj 610 puede no realizar absorción de reloj.

**[0052]** En un modo de realización, el absorbedor de reloj 610 puede configurarse para absorber impulsos de reloj de acuerdo con uno de varios patrones de absorción de impulsos diferentes. En este sentido, la FIG. 8 muestra un ejemplo de ocho patrones de absorción de impulsos, donde cada patrón de absorción de impulsos se identifica mediante un ID de patrón (PID) único. En este ejemplo, cada patrón de absorción de impulsos se define mediante una secuencia de ocho bits, en la que un valor de bit de cero corresponde a una absorción de impulso y un valor de bit de uno corresponde a un paso de impulso. Por ejemplo, el patrón de absorción de impulsos correspondiente al PID 2 tiene dos bits de valor cero y seis bits de valor uno. Por tanto, para este patrón de absorción de impulsos, el absorbedor de reloj 610 absorbe aproximadamente el 25% de los impulsos de reloj de la señal de reloj seleccionada Clk\_sel, lo que corresponde a una reducción de frecuencia del 25%. Como resultado, para este patrón de absorción de impulsos, la frecuencia de la señal de reloj de salida se reduce al 75% de la frecuencia de la señal de reloj de entrada que proporciona (origina) la señal de reloj de salida.

**[0053]** En otro ejemplo, el patrón de absorción de impulsos correspondiente al PID 5 tiene cinco bits de valor cero y tres bits de valor uno. Por tanto, para este patrón de absorción de impulsos, el absorbedor de reloj 610 absorbe aproximadamente el 62,5% de los impulsos de reloj de la señal de reloj seleccionada Clk\_sel, lo que corresponde a una reducción de frecuencia del 62,5%. Como resultado, para este patrón de absorción de impulsos, la frecuencia de la señal de reloj de salida se reduce al 37,5% de la frecuencia de la señal de reloj de entrada que proporciona (origina) la señal de reloj de salida.

**[0054]** En el ejemplo de la FIG. 8, el patrón de absorción de impulsos correspondiente al PID 0 comprende todos los bits de valor uno. Por tanto, para este patrón de absorción de impulsos, el absorbedor de reloj 610 pasa todos los impulsos de reloj de la señal de reloj de salida (es decir, no realiza absorción de reloj).

**[0055]** En un aspecto, el controlador 115 puede indicar al absorbedor de reloj 610 que absorba los impulsos de la señal de reloj seleccionada Clk\_sel de acuerdo con un patrón de absorción de impulsos particular introduciendo el PID correspondiente en el absorbedor de reloj 610. Por ejemplo, si el controlador 115 introduce el PID 6 en el absorbedor de reloj 610, el absorbedor de reloj 610 puede absorber impulsos de acuerdo con el patrón de absorción de impulsos correspondiente mostrado en la FIG. 8. En este ejemplo, el absorbedor de reloj 610 absorbe aproximadamente el 75% de los impulsos de la señal de reloj seleccionada Clk\_sel, lo que reduce la frecuencia de la señal de reloj de salida Clk\_out a aproximadamente el 25% de la frecuencia de la señal de reloj de entrada que proporciona (origina) la señal de reloj de salida Clk\_out.

**[0056]** Cuando el absorbedor de reloj 610 absorbe impulsos de reloj de acuerdo con un patrón de absorción de impulsos, el absorbedor de reloj 610 puede repetir el patrón. Usando el ejemplo de la FIG. 8, el absorbedor de reloj 610 puede repetir el patrón de absorción de impulsos para cada ocho impulsos de la señal de reloj seleccionada Clk\_sel, donde ocho es el número de bits que definen el patrón. Por ejemplo, para el patrón de absorción correspondiente al PID 3 en la FIG. 8, el absorbedor de reloj 610 puede absorber tres impulsos por cada ocho impulsos de la señal de reloj seleccionada Clk\_sel de acuerdo con el patrón.

**[0057]** En un modo de realización, se puede definir una secuencia de reducción para cada señal de reloj de entrada mediante una secuencia correspondiente de PID. La secuencia de PID para una señal de reloj de entrada identifica una secuencia de patrones de absorción de impulsos a usar mediante el absorbedor de reloj 610 para reducir la frecuencia de la señal de reloj de salida Clk\_out cuando la señal de reloj de salida Clk\_out se proporciona (se origina) mediante la señal de reloj de entrada.

**[0058]** En este modo de realización, el absorbedor de reloj 610 puede realizar una reducción de acuerdo con una secuencia de PID realizando de manera secuencial la absorción de reloj de acuerdo con cada PID en la secuencia. Para cada PID en la secuencia, el absorbedor de reloj 610 puede absorber impulsos de reloj de acuerdo con el patrón

de absorción correspondiente al PID. La cantidad de tiempo que gasta el absorbedor de reloj 610 en cada PID durante la reducción puede corresponder a una duración de tiempo predeterminada o a un número predeterminado de repeticiones del patrón de absorción correspondiente. Los PID en la secuencia de reducción se ordenan de tal manera que cada PID subsiguiente en la secuencia corresponde a un porcentaje mayor de absorciones de impulsos de reloj.

5 Por tanto, a medida que el absorbedor de reloj 610 pasa de manera secuencial a través de los PID en la secuencia, el absorbedor de reloj 610 absorbe un porcentaje creciente de impulsos de reloj.

10 [0059] En un modo de realización, el controlador 115 puede incluir una tabla en memoria, en la que la tabla comprende una secuencia de reducción para cada señal de reloj de entrada Clk\_a a Clk\_d. La secuencia de reducción para cada señal de reloj de entrada puede comprender una secuencia de PID que identifica una secuencia de patrones de absorción de impulsos a usar mediante el absorbedor de reloj 610 para reducir la frecuencia de la señal de reloj de salida Clk\_out, como se ha analizado anteriormente. Cuando se cambia la señal de reloj de salida Clk\_out de una señal de reloj actual de las señales de reloj Clk\_a a Clk\_d a una nueva de las señales de reloj Clk\_a a Clk\_b, el controlador 115 puede recuperar la secuencia de reducción para la señal de reloj de entrada actual de la tabla, e indicar al absorbedor de reloj 610 que reduzca la frecuencia de la señal de reloj de salida de acuerdo con la secuencia de reducción recuperada.

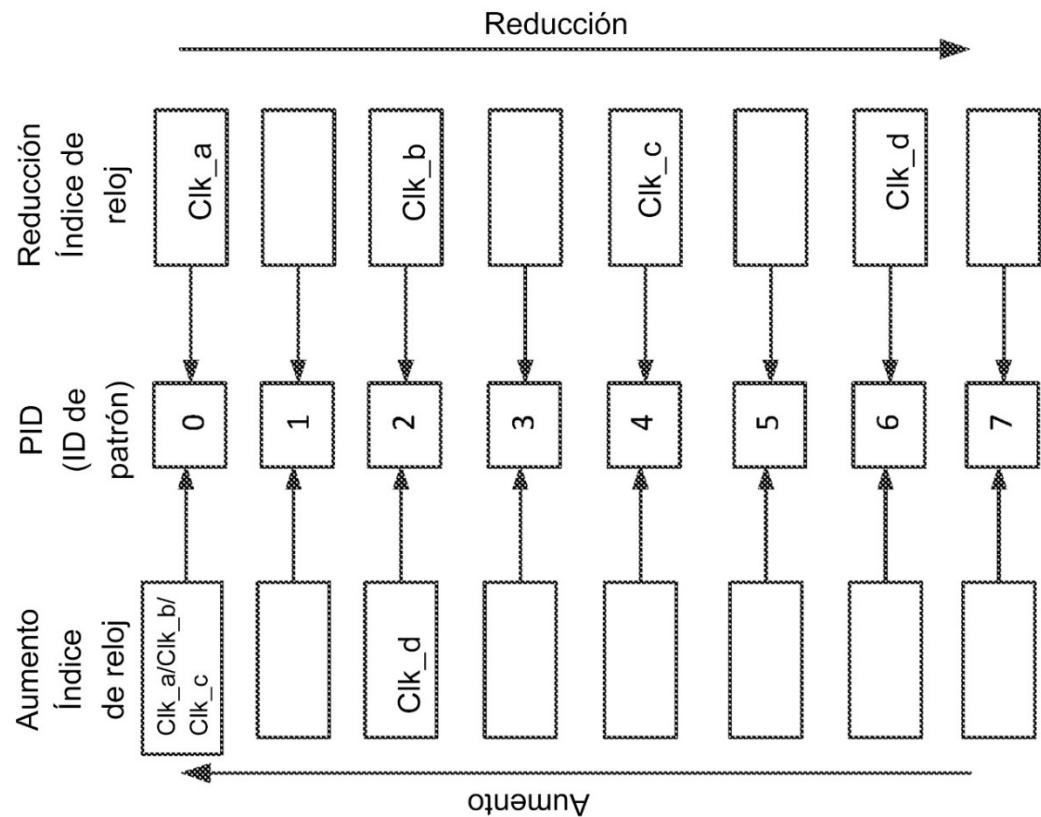

15 [0060] En un modo de realización, la secuencia de reducción para cada señal de reloj de entrada puede definirse mediante un índice de reloj que asigna cada señal de reloj de entrada a uno de los PID. En este modo de realización, la secuencia de reducción para cada señal de reloj de entrada puede saltar del PID 0 al PID asignado en la primera etapa de la secuencia de reducción. Las etapas restantes en la secuencia de reducción se definen mediante los PID restantes en la dirección de reducción. Esto puede explicarse por medio de un ejemplo con referencia a la FIG. 9.

20 [0061] La FIG. 9 muestra un índice de reloj a modo de ejemplo, en el que cada señal de reloj de entrada Clk\_a a Clk\_d se asigna a un PID. En este ejemplo, la secuencia de reducción para cada señal de reloj de entrada salta del PID 0 al PID asignado en la primera etapa de la secuencia de reducción. Las etapas restantes en la secuencia de reducción se definen mediante los PID restantes en la dirección de reducción, lo que se indica mediante la flecha hacia abajo en la FIG. 9.

25 [0062] En el ejemplo de la FIG. 9, la señal de reloj de entrada Clk\_b se asigna al PID 2. Por tanto, la secuencia de reducción para la señal de reloj de entrada Clk\_b se puede indicar como sigue:

PID 0 → PID 2 → PID 3 → PID 4 → PID 5 → PID 6 → PID 7.

30 Además, en este ejemplo, la señal de reloj de entrada Clk\_c se asigna al PID 4. Por tanto, la secuencia de reducción para la señal de reloj de entrada Clk\_c se puede indicar como sigue:

PID 0 → PID4 → PID5 → PID6 → PID7.

35 40 Además, en este ejemplo, la señal de reloj de entrada Clk\_d se asigna al PID 6. Por tanto, la secuencia de reducción para la señal de reloj de entrada Clk\_d se puede indicar como sigue:

PID 0 → PID6 → PID7.

45 50 Finalmente, en este ejemplo, la señal de reloj de entrada Clk\_a se asigna al PID 0. Por tanto, la secuencia de reducción para la señal de reloj de entrada Clk\_a se puede indicar como sigue:

PID 0 → PID 1 → PID 2 → PID 3 → PID 4 → PID 5 → PID 6 → PID 7.

55 60 En este ejemplo, la secuencia de reducción para la señal de reloj de entrada Clk\_a pasa por todos los PID de la FIG. 9 en la dirección de reducción.

[0063] En un modo de realización, se puede definir una secuencia de aumento para cada señal de reloj de entrada mediante una secuencia correspondiente de PID. La secuencia de PID para una señal de reloj de entrada identifica una secuencia de patrones de absorción de impulsos a usar mediante el absorbedor de reloj 610 para aumentar la frecuencia de la señal de reloj de salida Clk\_out cuando la señal de reloj de salida Clk\_out se proporciona (se origina) mediante la señal de reloj de entrada.

[0064] En este modo de realización, el absorbedor de reloj 610 puede realizar un aumento de acuerdo con una secuencia de PID realizando de manera secuencial la absorción de reloj de acuerdo con cada PID en la secuencia. Para cada PID en la secuencia, el absorbedor de reloj 610 puede absorber impulsos de reloj de acuerdo con el patrón de absorción correspondiente al PID. La cantidad de tiempo que gasta el absorbedor de reloj 610 en cada PID durante el aumento puede corresponder a una duración de tiempo predeterminada o a un número predeterminado de repeticiones del patrón de absorción correspondiente. Los PID en la secuencia de aumento se ordenan de tal manera que cada PID subsiguiente en la secuencia corresponde a un porcentaje menor de absorciones de impulsos de reloj.

Por tanto, a medida que el absorbedor de reloj 610 pasa de manera secuencial a través de los PID en la secuencia de PID, el absorbedor de reloj 610 absorbe un porcentaje decreciente de impulsos de reloj.

**[0065]** En un modo de realización, el controlador 115 puede incluir una tabla en memoria, en la que la tabla comprende una secuencia de aumento para cada señal de reloj de entrada Clk\_a a Clk\_d. La secuencia de aumento para cada señal de reloj de entrada puede comprender una secuencia de PID que identifica una secuencia de patrones de absorción de impulsos a usar mediante el absorbedor de reloj 610 para aumentar la frecuencia de la señal de reloj de salida Clk\_out, como se ha analizado anteriormente. Cuando se cambia la señal de reloj de salida Clk\_out de una señal de reloj actual de las señales de reloj Clk\_a a Clk\_d a una nueva de las señales de reloj Clk\_a a Clk\_b, el controlador 115 puede recuperar la secuencia de aumento para la señal de reloj de entrada nueva de la tabla, e indicar al absorbedor de reloj 610 que aumente la frecuencia de la señal de reloj de salida cuanto la señal de reloj de entrada nueva se habilite de acuerdo con la secuencia de aumento recuperada.

**[0066]** En un modo de realización, la secuencia de aumento para cada señal de reloj de entrada puede definirse mediante un índice de reloj que asigna cada señal de reloj de entrada a uno de los PID. En este modo de realización, la secuencia de aumento para cada señal de reloj de entrada puede secuenciarse a través de cada PID que tiene un mayor porcentaje de absorciones de impulsos de reloj que el PID asignado en la dirección de aumento. Después de alcanzar el PID asignado, la secuencia de aumento puede saltar del PID asignado al PID 0. Esto puede explicarse usando el ejemplo de la FIG. 9.

**[0067]** En este ejemplo, la secuencia de aumento para cada señal de reloj de entrada se secuencia a través del PID 7 al PID asignado en la dirección de aumento, lo que se indica mediante la flecha hacia arriba en la FIG. 9. Después de alcanzar el respectivo PID asignado, cada secuencia de aumento puede saltar del PID asignado al PID 0.

**[0068]** En el ejemplo de la FIG. 9, la señal de reloj de entrada Clk\_b se asigna al PID 2. Por tanto, la secuencia de aumento para la señal de reloj de entrada Clk\_b se puede indicar como sigue:

PID 7 → PID 6 → PID 5 → PID 4 → PID 3 → PID 2 → PID 0.

**30** Además, en este ejemplo, la señal de reloj de entrada Clk\_c se asigna al PID 4. Por tanto, la secuencia de aumento para la señal de reloj de entrada Clk\_c se puede indicar como sigue:

PID 7 → PID 6 → PID 5 → PID 4 → PID 0.

**35** Además, en este ejemplo, la señal de reloj de entrada Clk\_d se asigna al PID 6. Por tanto, la secuencia de aumento para la señal de reloj de entrada Clk\_d se puede indicar como sigue:

PID 7 → PID 6 → PID 0.

**40** Finalmente, en este ejemplo, la señal de reloj de entrada Clk\_a se asigna al PID 0. Por tanto, la secuencia de aumento para la señal de reloj de entrada Clk\_a se puede indicar como sigue:

PID 7 → PID 6 → PID 5 → PID 4 → PID 3 → PID 2 → PID 1 → PID 0.

**45** En este ejemplo, la secuencia de aumento para la señal de reloj de entrada Clk\_a pasa por todos los PID de la FIG. 9 en la dirección de aumento. Como en este ejemplo se usa el mismo índice de reloj para la reducción y el aumento, la secuencia de aumento para cada señal de reloj de entrada es la inversa de la secuencia de reducción para la señal de reloj de entrada.

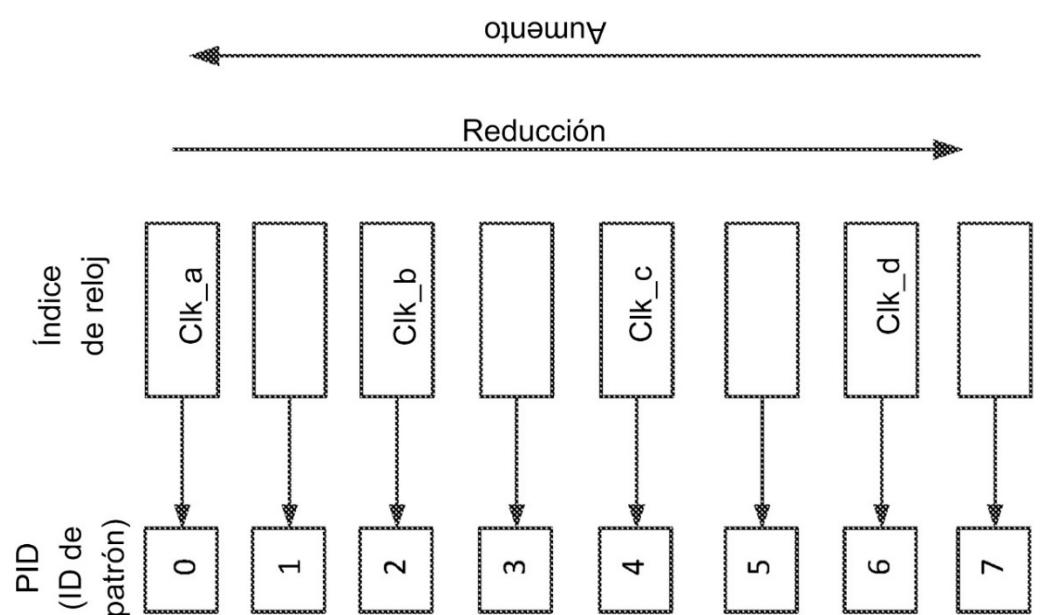

**50** **[0069]** Se debe apreciar que el índice de reloj para la reducción y el aumento puede ser diferente. En este sentido, la FIG. 10 muestra un ejemplo de un índice de reloj para la reducción y un índice de reloj independiente para el aumento. En este ejemplo, el índice de reloj para la reducción es el mismo que el índice de reloj en la FIG. 9. Por lo tanto, las secuencias de reducción para las FIG. 9 y 10 son las mismas. En este ejemplo, el índice de reloj para el aumento asigna cada una de las señales de reloj de entrada Clk\_a, Clk\_b y Clk\_c al PID 0 y asigna la señal de reloj de entrada Clk\_d al PID 2. Por tanto, en este ejemplo, la secuencia de aumento para cada una de las señales de reloj de entrada Clk\_a, Clk\_b y Clk\_c puede indicarse como sigue:

PID 7 → PID 6 → PID 5 → PID 4 → PID 3 → PID 2 → PID 1 → PID 0.

**60** La secuencia de aumento para la señal de reloj de entrada Clk\_d se puede indicar como sigue:

PID 7 → PID 6 → PID 5 → PID 4 → PID 3 → PID 2 → PID 0.

**65** **[0070]** Se debe apreciar que los modos de realización de la presente divulgación no se limitan al cambio de reloj. Por ejemplo, los modos de realización de la presente divulgación se pueden usar para reducir la frecuencia de la señal

de reloj de salida cuando el procesador 110 cambia de un modo activo a un modo inactivo para ahorrar energía, y para aumentar la frecuencia de la señal de reloj de salida cuando el procesador 110 vuelve a cambiar al modo activo.

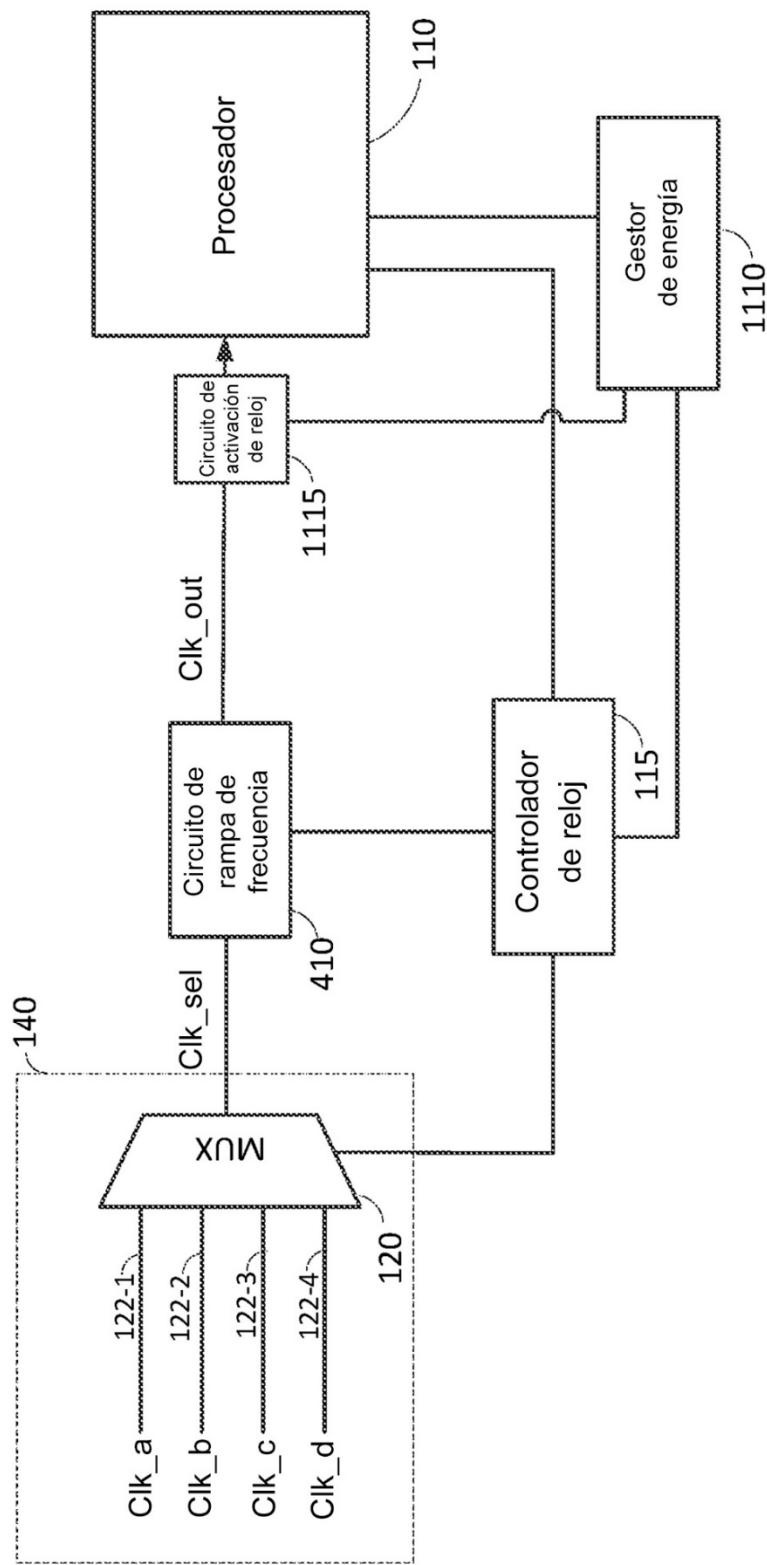

**[0071]** En este sentido, la FIG. 11 muestra un sistema a modo de ejemplo 1100 que comprende además un gestor de energía 1110 configurado para gestionar la energía del procesador 110, y un circuito de activación de reloj 1115 configurado para activar de manera selectiva la señal de reloj para el procesador 110. En un aspecto, el gestor de energía 1110 puede configurarse para colocar el procesador 110 en un modo inactivo para ahorrar energía cuando el procesador no está en uso. Para hacer esto, el gestor de energía 1110 puede desactivar la señal de reloj usando el circuito de activación de reloj 1115. Desactivar la señal de reloj puede detener la mayoría o la totalidad de la actividad de conmutación en el procesador 110, y, por lo tanto, puede reducir significativamente el consumo dinámico de energía mediante el procesador 110. Cuando el procesador 110 se necesita posteriormente (por ejemplo, para ejecutar instrucciones), el gestor de energía 1110 puede volver a colocar el procesador 110 en el modo activo activando la señal de reloj usando el circuito de activación de reloj 1115. Debe apreciarse que el circuito de activación de reloj 1115 puede estar en el procesador 110 y configurarse para desactivar las rutas de reloj internas en el procesador 110 cuando el procesador está en modo inactivo.

**[0072]** En un modo de realización, cuando el gestor de energía 1110 coloca el procesador 110 en el modo inactivo, el gestor de energía 1110 puede enviar una señal de modo inactivo al controlador de reloj 115 que indica al controlador de reloj 115 que reduzca la frecuencia de la señal de reloj de salida *Clk\_out* para el procesador 110. El gestor de energía 1110 puede hacer esto antes de que el circuito de activación del reloj 1115 desactive la señal de reloj en el procesador 110. El controlador de reloj 115 puede reducir la frecuencia de la señal de reloj de salida *Clk\_out* de acuerdo con una secuencia de reducción correspondiente a la señal de reloj de entrada que proporciona (origina) la señal de reloj de salida. La secuencia de reducción puede comprender una o más etapas, en las que la frecuencia de la señal de reloj de salida se reduce en una cantidad creciente en cada etapa subsiguiente. El circuito de rampa 410 puede reducir la frecuencia de la señal de reloj de salida dividiendo la frecuencia de reloj de la señal de reloj seleccionada *Clk\_sel* o absorbiendo impulsos de la señal de reloj seleccionada *Clk\_sel*, como se ha analizado anteriormente.

**[0073]** En este modo de realización, el controlador de reloj 115 puede indicar al circuito de rampa 410 que reduzca la frecuencia de la señal de reloj de salida *Clk\_out* hasta aproximadamente cero hercios o hasta una frecuencia que sea inferior a la señal de reloj de entrada que proporciona (origina) la señal de reloj de salida *Clk\_out*. Una vez que se completa la reducción, el controlador de reloj 115 puede informar al gestor de energía 1110 de que la frecuencia se ha reducido. En respuesta, el gestor de energía 120 puede desactivar la señal de reloj para el procesador 110 para colocar el procesador 110 en el modo inactivo.

**[0074]** La reducción de la frecuencia de la señal de reloj de salida *Clk\_out* puede reducir el exceso de voltaje en la PDN cuando el procesador 110 se coloca en el modo inactivo. Esto se debe a que reducir la frecuencia disminuye la carga actual en la PDN a una velocidad más lenta en comparación con desactivar el reloj para el procesador 110 a frecuencia máxima (es decir, la frecuencia de la señal de reloj de entrada que origina la señal de reloj de salida).

**[0075]** En este modo de realización, el controlador de reloj 115 puede deshabilitar la señal de reloj de salida cuando el procesador 110 está en el modo inactivo. Por ejemplo, el controlador de reloj 115 puede deshabilitar la señal de reloj seleccionada *Clk\_sel* al final de la reducción.

**[0076]** Cuando el gestor de energía 1110 vuelve a cambiar el procesador 110 al modo activo, el gestor de energía 1110 puede enviar una señal de modo activo al controlador de reloj 115, indicando al controlador de reloj 115 que aumente la frecuencia de la señal de reloj de salida *Clk\_out* hasta la frecuencia máxima (es decir, la frecuencia de la señal de reloj de entrada que origina la señal de reloj de salida). El gestor de energía 1110 puede aumentar la frecuencia después de que se activa la señal de reloj para el procesador 110. El controlador de reloj 115 puede aumentar la frecuencia de la señal de reloj de salida *Clk\_out* de acuerdo con una secuencia de aumento correspondiente a la señal de reloj de entrada que proporciona (origina) la señal de reloj de salida. La secuencia de aumento puede comprender una o más etapas, en las que la frecuencia de la señal de reloj de salida aumenta a una frecuencia más alta en cada etapa subsiguiente. El circuito de rampa 410 puede aumentar la frecuencia de la señal de reloj de salida dividiendo la frecuencia de reloj de la señal de reloj seleccionada *Clk\_sel* por una cantidad decreciente a lo largo del tiempo o absorbiendo un porcentaje decreciente de impulsos de la señal de reloj seleccionada *Clk\_sel* a lo largo del tiempo, como se ha analizado anteriormente.

**[0077]** El aumento de la frecuencia de la señal de reloj de salida *Clk\_out* puede reducir la caída de voltaje en la PDN cuando el procesador 110 se coloca en el modo activo. Esto se debe a que aumentar la frecuencia aumenta la carga actual en la PDN a una velocidad más lenta en comparación con activar el reloj para el procesador 110 a frecuencia máxima (es decir, la frecuencia de la señal de reloj de entrada que origina la señal de reloj de salida).

**[0078]** En un modo de realización, el gestor de energía 1110 puede colocar el procesador 110 en el modo inactivo cuando el procesador 110 ejecuta una instrucción de espera de interrupción (WFI), una instrucción de espera de evento (WFE) u otra instrucción. Una vez que el procesador 110 se coloca en el modo inactivo, el gestor de energía 1110 puede volver a cambiar el procesador 110 al modo activo cuando el gestor de energía 1110 recibe una señal de

interrupción u ocurre un evento determinado. La señal de interrupción puede provenir de un dispositivo (por ejemplo, un dispositivo periférico) que necesita el procesador. En otro ejemplo, la señal de interrupción puede provenir de un temporizador. En este ejemplo, el temporizador puede activar un contador cuando el procesador 110 se coloca en el modo inactivo, y enviar la señal de interrupción cuando el valor de recuento del contador alcanza un valor predeterminado.

**[0079]** En otro ejemplo, el procesador 110 (por ejemplo, GPU) puede procesar datos en tramas de tiempo. En este ejemplo, el procesador 110 puede finalizar el procesamiento de datos para una trama de tiempo actual antes de que se reciban los datos para la siguiente trama de tiempo. En este caso, cuando el procesador 110 termina de procesar los datos para la trama de tiempo actual, el procesador 110 puede informar al gestor de energía 1110 de que el procesamiento para la trama actual ha finalizado. En respuesta, el gestor de energía 1110 puede colocar el procesador 110 en el modo inactivo para ahorrar energía. El gestor de energía 1110 puede volver a cambiar el procesador 110 al modo activo al comienzo de la siguiente trama de tiempo. En este ejemplo, el gestor de energía 1110 puede tener un temporizador que siga los límites de las tramas de tiempo. Esto permite al gestor de energía 1110 determinar el inicio de la siguiente trama de tiempo y, por lo tanto, volver a cambiar el procesador 110 al modo activo al comienzo de la siguiente trama de tiempo.

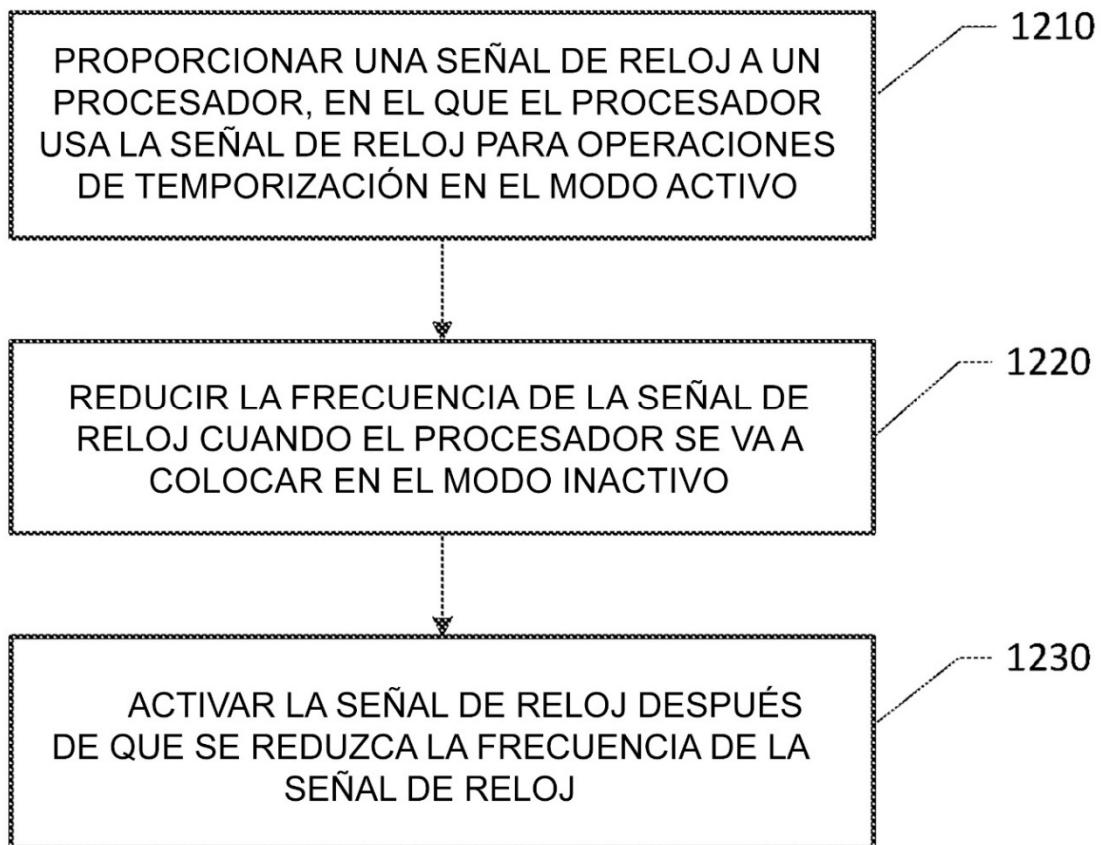

**[0080]** La FIG. 12 muestra un procedimiento a modo de ejemplo 1200 para cambiar un procesador entre un modo activo y un modo inactivo. El procedimiento se puede realizar mediante el gestor de energía 1110, el controlador de reloj 115, el multiplexor 120, el circuito de activación de reloj 1115 y/o el circuito de rampa 410.

**[0081]** En la etapa 1210, se proporciona una señal de reloj al procesador, en la que el procesador usa la señal de reloj para operaciones de temporización en el procesador en el modo activo. Por ejemplo, la señal de reloj puede proporcionarse mediante un multiplexor (por ejemplo, el multiplexor 120) que envía una seleccionada de una pluralidad de señales de reloj de entrada para el procesador (por ejemplo, el procesador 110).

**[0082]** En la etapa 1220, la frecuencia de la señal de reloj se reduce cuando el procesador se coloca en el modo inactivo. Por ejemplo, la frecuencia de la señal de reloj puede reducirse absorbiendo un porcentaje creciente de impulsos de la señal de reloj a lo largo del tiempo o dividiendo la frecuencia de la señal de reloj por una cantidad creciente a lo largo del tiempo. La señal de reloj puede reducirse hasta aproximadamente cero hercios o hasta una frecuencia más baja.

**[0083]** En la etapa 1230, la señal de reloj se desactiva después de reducir la frecuencia de la señal de reloj. Por ejemplo, la señal de reloj se puede desactivar mediante un circuito de activación de reloj (por ejemplo, el circuito de activación de reloj 1115).

**[0084]** El procedimiento puede incluir opcionalmente la activación de la señal de reloj cuando el procesador se debe volver a colocar en el modo activo. Por ejemplo, el procesador se puede volver a colocar en el modo activo en respuesta a una señal de interrupción, como se ha analizado anteriormente. El procedimiento también puede comprender aumentar la frecuencia de la señal de reloj después de que se activa la señal de reloj. Por ejemplo, la frecuencia de la señal de reloj puede aumentarse absorbiendo un porcentaje decreciente de impulsos de la señal de reloj a lo largo del tiempo o dividiendo la frecuencia de la señal de reloj por una cantidad decreciente a lo largo del tiempo.

**[0085]** En un modo de realización, la señal de reloj de salida se puede desactivar mientras el procesador 110 está en el modo inactivo haciendo que el multiplexor 120 deshabilite la señal de reloj de salida mientras el procesador 110 está en el modo inactivo. En este modo de realización, el controlador de reloj 115 puede indicar al multiplexor 120 que deshabilite la señal de reloj seleccionada Clk\_sel al final de la reducción para deshabilitar la señal de reloj de salida Clk\_out. El controlador de reloj 115 puede hacer esto, por ejemplo, deseleccionando todas las señales de reloj de entrada. Cuando el procesador 110 vuelve a cambiar al modo activo, el controlador de reloj 115 puede indicar al multiplexor 120 que habilite la señal de reloj seleccionada Clk\_sel para habilitar la señal de reloj de salida Clk\_out y comenzar el aumento cuando se habilite la señal de reloj seleccionada Clk\_sel. El controlador de reloj 115 puede hacer esto, por ejemplo, seleccionando una de las señales de reloj de entrada. La señal de reloj de entrada seleccionada puede ser la misma que la señal de reloj de entrada que se seleccionó cuando el procesador 110 estuvo por última vez en el modo activo. En este modo de realización, el circuito de activación de reloj 1115 se puede omitir. Además, la señal de reloj se puede desactivar en la etapa 1230 del procedimiento 1200 haciendo que el multiplexor 120 deshabilite el envío de la señal de reloj.

**[0086]** En un modo de realización, el circuito de rampa de frecuencia 410 se puede usar para escalar (regular) la frecuencia de la señal de reloj de salida Clk\_out para la mitigación de temperatura. En este sentido, la FIG. 13 muestra un sistema a modo de ejemplo 1300 que comprende además un controlador de temperatura 1310 y uno o más sensores de temperatura 1320.

**[0087]** El sensor de temperatura 1320 está configurado para medir una temperatura del procesador 110 y enviar la temperatura medida al controlador de temperatura 1310. El sensor de temperatura 1320 puede estar ubicado cerca del procesador 110 o dentro del procesador 110 para obtener una lectura de temperatura precisa del procesador 110.

El controlador de temperatura 1310 está configurado para controlar la frecuencia de la señal de reloj de salida Clk\_out basándose en la temperatura medida, como se analiza en más detalle más adelante.

**[0088]** En un modo de realización, el controlador de temperatura 1310 puede comparar periódicamente la temperatura medida con un umbral de temperatura. Cuando la temperatura medida está por debajo del umbral, el controlador de temperatura 1310 puede no modificar la frecuencia de la señal de reloj de salida. Cuando la temperatura medida aumenta por encima del umbral, el controlador de temperatura 1310 puede iniciar la mitigación de temperatura para bajar la temperatura. Por ejemplo, el controlador de temperatura 1310 puede enviar un comando al controlador de reloj 115 para reducir la frecuencia de la señal de reloj de salida Clk\_out. En respuesta, el controlador de reloj 115 puede indicar al circuito de rampa de frecuencia 410 que reduzca la frecuencia dividiendo la frecuencia de la señal de reloj seleccionada Clk\_sel por una cierta cantidad o absorbiendo un cierto porcentaje de impulsos de reloj de la señal de reloj seleccionada Clk\_sel.

**[0089]** Después de que se reduce la frecuencia, el controlador de temperatura 1310 puede continuar comparando periódicamente la temperatura medida con el umbral de temperatura. Si la temperatura medida aún está por encima del umbral, el controlador de temperatura 1310 puede enviar un comando al controlador de reloj 115 para reducir aún más la frecuencia de la señal de reloj de salida. La reducción de la frecuencia de la señal de reloj de salida hace que la temperatura del procesador 110 caiga al reducir la disipación de energía dinámica en el procesador 110.

**[0090]** Cuando la temperatura medida cae por debajo del umbral de temperatura, el controlador de temperatura 1310 puede ordenar al controlador de reloj 115 que aumente la frecuencia de la señal de reloj de salida Clk\_out si la frecuencia de la señal de reloj de salida está por debajo de una frecuencia objetivo (por ejemplo, la frecuencia de la señal de reloj de entrada que origina la señal de reloj de salida). En respuesta, el controlador de reloj 115 puede aumentar la frecuencia indicando al circuito de rampa 410 que divida la frecuencia de la señal de reloj seleccionada Clk\_sel por una cantidad menor o que absorba un porcentaje menor de impulsos de reloj de la señal de reloj seleccionada Clk\_sel. La frecuencia de la señal de reloj de salida se aumenta cuando la temperatura cae por debajo del umbral para recuperar el rendimiento que se pierde debido a la reducción de frecuencia de la señal de reloj de salida.

**[0091]** En general, cuando la temperatura medida aumenta por encima del umbral, el controlador de temperatura 1310 puede reducir la frecuencia de la señal de reloj de salida para reducir la temperatura del procesador 110, como se ha analizado anteriormente. Cuando la temperatura medida cae por debajo del umbral de temperatura y la frecuencia de la señal de reloj de salida es inferior a la frecuencia objetivo, el controlador de temperatura 1310 puede aumentar la frecuencia de la señal de reloj de salida para aumentar el rendimiento del procesador 110.

**[0092]** Como se ha analizado anteriormente, el circuito de rampa 410 puede comprender un absorbedor de reloj que escala la frecuencia de la señal de reloj de salida absorbiendo de manera selectiva impulsos de la señal de reloj seleccionada Clk\_sel. En este ejemplo, el controlador de reloj 115 puede indicar al circuito de rampa 410 que absorba impulsos de reloj de acuerdo con uno de una pluralidad de patrones de absorción de impulsos. En este sentido, la FIG. 14 muestra un ejemplo de ocho patrones de absorción de impulsos que puede usar el controlador de reloj 115 para la mitigación térmica. En este ejemplo, cada patrón de absorción puede corresponder a un PID único. Aunque los patrones de absorción para la mitigación térmica mostrados en la FIG. 14 son similares a los patrones de absorción para el cambio de reloj mostrados en la FIG. 8, se debe apreciar que este no es necesariamente el caso. Para cada patrón de absorción, la FIG. 14 muestra la frecuencia correspondiente de la señal de reloj de salida como un porcentaje de la señal de reloj de entrada que origina la señal de reloj de salida.

**[0093]** Antes de que se inicie la mitigación térmica, el controlador de reloj 115 puede introducir el PID 0 en el circuito de rampa 410, en cuyo caso la señal de reloj de salida Clk\_out está a frecuencia máxima (es decir, la frecuencia de la señal de reloj de entrada que origina la señal de reloj de salida). Cuando la temperatura medida aumenta por encima del umbral, el controlador de temperatura 1310 puede iniciar la mitigación térmica y ordenar al controlador de reloj 115 que reduzca la frecuencia de la señal de reloj de salida. En respuesta, el controlador de control 115 puede cambiar el patrón de absorción del circuito de rampa 410 a PID 1. Esto hace que el circuito de rampa 410 reduzca la frecuencia de la señal de reloj de salida al 87,5% de la frecuencia de la señal de reloj de entrada en el ejemplo de la FIG. 14. Si la temperatura medida continúa excediendo el umbral de temperatura, el controlador de reloj 115 puede recibir comandos subsiguientes del controlador de temperatura 1310 para reducir aún más la frecuencia de la señal de reloj de salida. Cada vez que el controlador de reloj 115 recibe un comando para reducir la frecuencia de la señal de reloj de salida, el controlador de reloj 115 puede cambiar el patrón de absorción actual que está usando el circuito de rampa 410 al siguiente patrón de absorción mostrado en la FIG. 14 en la dirección descendente (indicada mediante la flecha hacia abajo en la FIG. 14). Por ejemplo, si el patrón de absorción actual corresponde al PID 1, el controlador de reloj 115 puede cambiar el circuito de rampa 410 al patrón de absorción correspondiente al PID 2.

**[0094]** Si la temperatura medida cae por debajo del umbral de temperatura, el controlador de temperatura 1310 puede ordenar al controlador de reloj 115 que aumente la frecuencia de la señal de reloj de salida Clk\_out. En respuesta, el controlador de reloj 115 puede cambiar el patrón de absorción actual al siguiente patrón de absorción mostrado en la FIG. 14 en la dirección ascendente (indicada mediante la flecha hacia arriba en la FIG. 14). Por ejemplo,

si el patrón de absorción actual corresponde al PID 3, el controlador de reloj 115 puede cambiar el circuito de rampa 410 al patrón de absorción correspondiente al PID 2.

**[0095]** Por tanto, el controlador de reloj 115 puede cambiar el patrón de absorción del circuito de rampa 410 para reducir o aumentar la frecuencia de la señal de reloj de salida bajo el control del controlador de temperatura 1310. Se debe apreciar que los patrones de absorción mostrados en la FIG. 14 son sólo a modo de ejemplo. Por ejemplo, los patrones de absorción pueden definirse usando un número mayor de bits. Esto aumenta el número de posibles patrones de absorción que puede usar el circuito de rampa 410 y, por lo tanto, permite que el controlador del reloj ajuste la frecuencia de la señal de reloj de salida con una granularidad más fina.

**[0096]** En un aspecto, el controlador de reloj 115 puede omitir uno o más patrones de absorción para una frecuencia de reloj de entrada dada (es decir, la frecuencia de la señal de reloj de entrada que origina la señal de reloj de salida). Esto se debe a que, para una frecuencia de reloj de entrada dada, un patrón de absorción particular puede dar como resultado una frecuencia de reloj de salida que excita la resonancia de la PDN y/o causa emisiones que interfieren con uno o más componentes (por ejemplo, el receptor). Por ejemplo, si el patrón de absorción correspondiente al PID 2 da como resultado una señal de reloj de salida que excita la resonancia de la PDN para la señal de reloj de entrada Clk\_a, el controlador de reloj 115 puede omitir este patrón de absorción durante la mitigación térmica cuando la señal de reloj de salida se origina mediante la señal de reloj de entrada Clk\_a.

**[0097]** Un patrón de absorción que se omite para la mitigación térmica para una señal de reloj de entrada dada se puede usar para la reducción o el aumento durante el cambio de reloj para la señal de reloj de entrada dada. Esto se debe a que la señal de reloj de salida puede permanecer en una frecuencia que excita la resonancia de PDN durante un período de tiempo mucho más corto durante la reducción o el aumento, y, por lo tanto, puede ser menos preocupante para la reducción o el aumento.