(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년02월04일

(11) 등록번호 10-1229249

(24) 등록일자 2013년01월29일

(51) 국제특허분류(Int. Cl.)

*H01L 29/786* (2006.01) *H01L 21/336* (2006.01)

(21) 출원번호 10-2012-0035149(분할)

(22) 출원일자 2012년04월04일

심사청구일자 2012년04월04일

(65) 공개번호 10-2012-0046137

(43) 공개일자 2012년05월09일

(62) 원출원 특허 10-2003-0083083

원출원일자 2003년11월21일

심사청구일자 2008년11월20일

(30) 우선권주장 JP-P-2002-339952 2002년11월22일 일본(JP)

(56) 선행기술조사문현 EP01122794 A2

EP01256983 A2

KR1020010078229 A

US06445005 B1

전체 청구항 수 : 총 5 항

심사관 : 설관식

(54) 발명의 명칭 반도체 디바이스, 디스플레이 디바이스, 및 발광 디바이스 제조 방법

**(57) 요 약**

얇고 경량이고 플렉서블하고 굴곡이 있는 표면을 갖는 구조 외에, 외부로부터 수분, 산소 등이 침투하는 것을 방지할 수 있는 구조를 갖는 반도체 디바이스. 본 발명에서, 얇고 경량이고 플렉서블하고 굴곡이 있는 표면을 갖고, 게다가 수분, 산소 등이 침투하는 것을 방지할 수 있는 구조는 구조가 디바이스 형성층이 불소 수지막으로 덮이게 형성되고 디바이스 형성층에 포함된 TFT들이 섬형 반도체막으로 형성됨으로써 실현된다.

**대 표 도 - 도1**

(72) 발명자

**추루메 타쿠야**

일본, 카나가와켄 243-0036, 아추기시, 하세, 398,

가부시키가이샤한도오따이 에네루기 켄큐쇼(내)

**고토 유우고**

일본, 카나가와켄 243-0036, 아추기시, 하세, 398,

가부시키가이샤한도오따이 에네루기 켄큐쇼(내)

## 특허청구의 범위

### 청구항 1

반도체 디바이스를 제조하는 방법에 있어서,

제 1 기판 상에 다수의 박막 트랜지스터를 포함하는 디바이스 형성층을 형성하는 단계와,

상기 디바이스 형성층과 접촉하여 제 1 접착층을 형성하는 단계와,

제 2 기판을 상기 제 1 접착층과 접합하고, 상기 제 1 기판과 상기 제 2 기판 사이에 상기 디바이스 형성층을 샌드위칭하는 단계와,

물리적 수단에 의해 상기 제 1 기판을 상기 디바이스 형성층에서 분리하고 제거하는 단계와,

스퍼터링에 의해 노출된 표면상에 제 1 불소 수지막을 형성하는 단계와,

제 3 기판을 상기 제 1 불소 수지막에 그 사이에 삽입된 제 2 접착층을 사용하여 접합하는 단계와,

상기 제 1 접착층과 상기 제 2 기판을 상기 디바이스 형성층에서 분리하고 제거하는 단계와,

스퍼터링에 의해 상기 디바이스 형성층의 노출된 표면상에 제 2 불소 수지막을 형성하는 단계와,

상기 제 2 접착층과 상기 제 3 기판을 상기 디바이스 형성층에서 분리하고 제거하는 단계를 포함하는, 반도체 디바이스 제조 방법.

### 청구항 2

반도체 디바이스를 제조하는 방법에 있어서,

제 1 기판 상에 금속층을 형성하는 단계와,

상기 금속층상에 산화물층을 형성하는 단계와,

상기 산화물층상에 베이스 절연막을 형성하는 단계와,

상기 베이스 절연막 상에 수소를 함유하는 비정질 반도체막을 형성하는 단계와,

수소를 확산하기 위해 반도체막을 가열하는 단계와,

상기 반도체막을 사용하는 다수의 박막 트랜지스터들을 포함하는 디바이스 형성층을 형성하는 단계와,

상기 디바이스 형성층과 접촉하여 제 1 접착층을 형성하며, 제 2 기판을 상기 제 1 접착층에 접합하고, 상기 제 1 기판과 상기 제 2 기판 사이에 상기 디바이스 형성층을 샌드위칭하는 단계와,

물리적 수단에 의해 상기 제 1 기판과 상기 금속층을 상기 디바이스 형성층에서 분리하고 제거하는 단계와,

스퍼터링에 의해 상기 디바이스 형성층의 노출된 표면상에 제 1 불소 수지막을 형성하는 단계와,

제 3 기판을 상기 제 1 불소 수지막에 그 사이에 삽입된 제 2 접착층을 사용하여 접합하는 단계와,

상기 제 1 접착층과 상기 제 2 기판을 상기 디바이스 형성층에서 분리하고 제거하는 단계와,

스퍼터링에 의해 상기 디바이스 형성층의 노출된 표면상에 제 2 불소 수지막을 형성하는 단계와,

상기 제 2 접착층과 상기 제 3 기판을 상기 디바이스 형성층에서 분리하고 제거하는 단계를 포함하는, 반도체 디바이스 제조 방법.

### 청구항 3

제 1 항 또는 제 2 항에 있어서,

상기 제 1 접착층과 상기 제 2 접착층은 그 접착력이 빛 조사 또는 물에 녹기 쉬운 재료에 의해 떨어지는 재료를 사용하는, 반도체 디바이스 제조 방법.

**청구항 4**

디스플레이 디바이스를 제조하는 방법에 있어서,

제 1 기판 상에 금속층을 형성하는 단계와,

상기 금속층상에 산화물층을 형성하는 단계와,

상기 산화물층 상에 베이스 절연막을 형성하는 단계와,

상기 베이스 절연막상에 수소를 함유하는 비정질 반도체막을 형성하는 단계와,

수소를 확산하기 위해 상기 반도체막을 가열하는 단계와,

상기 반도체막을 사용하여 박막 트랜지스터를 형성하는 단계와,

총간 절연막을 통해 상기 박막 트랜지스터에 전기적으로 접속된 제 1 전극을 형성하는 단계와,

상기 제 1 전극과 접촉하여 제 1 접착층을 형성하는 단계와,

제 2 기판을 상기 제 1 접착층에 접합하는 단계와,

물리적 수단에 의해 상기 제 1 기판과 상기 금속층과 상기 베이스 절연막 사이의 계면에서 분리하고 제거하는 단계와,

스퍼터링에 의해 노출된 표면상에 제 1 불소 수지막을 형성하는 단계와,

제 3 기판을 상기 제 1 불소 수지막에 그 사이에 삽입된 제 2 접착층을 사용하여 접합하는 단계와,

상기 제 1 접착층과 상기 제 2 기판을 상기 제 1 전극의 표면에서 분리하고 제거하는 단계와,

상기 제 1 전극의 노출된 표면상에 제 1 전극을 포함하는 디바이스를 형성하는 단계와,

스퍼터링에 의해 상기 디바이스 상에 제 2 불소 수지막을 형성하는 단계와,

상기 제 2 접착층과 상기 제 3 기판을 상기 제 1 불소 수지막에서 분리하고 제거하는 단계를 포함하는, 디스플레이 디바이스 제조 방법.

**청구항 5**

발광 디바이스를 제조하는 방법에 있어서,

제 1 기판 상에 금속층을 형성하는 단계와,

상기 금속층 상에 산화물층을 형성하는 단계와,

상기 산화물층상에 베이스 절연막을 형성하는 단계와,

상기 베이스 절연막 상에 수소를 함유하는 비정질 반도체막을 형성하는 단계와,

수소를 확산하기 위해 상기 반도체막을 가열하는 단계와,

상기 반도체막을 사용하여 박막 트랜지스터를 형성하는 단계와,

총간 절연막을 통해 상기 박막 트랜지스터에 전기적으로 접속된 제 1 전극을 형성하는 단계와,

상기 제 1 전극과 접촉하여 제 1 접착층을 형성하는 단계와,

제 2 기판을 상기 제 1 접착층에 접착하는 단계와,

물리적 수단에 의해 상기 제 1 기판과 상기 금속층과 상기 베이스 절연막 사이의 계면에서 분리하고 제거하는 단계와,

스퍼터링에 의해 노출된 표면상에 제 1 불소 수지막을 형성하는 단계와,

제 3 기판을 상기 제 1 불소 수지막에 그 사이에 삽입된 제 2 접착층을 사용하여 접합하는 단계와,

상기 제 1 접착층과 상기 제 2 기판을 상기 제 1 전극의 표면에서 분리하고 제거하는 단계와,

상기 제 1 전극의 노출된 표면상에 전계 발광막을 형성하는 단계와,

상기 전계 발광막 상에 제 2 전극을 형성하는 단계와,

스팍터링에 의해 상기 제 2 전극상에 제 2 불소 수지막을 형성하는 단계와,

상기 제 2 접착층과 상기 제 3 기판을 상기 제 1 불소 수지막에서 분리하고 제거하는 단계를 포함하는, 발광 디바이스 제조 방법.

## 명세서

### 기술분야

[0001]

본 발명은 유기 박막으로 덮인 다수의 박막 트랜지스터들(하기에서, TFT)로 각각이 이루어진 반도체 디바이스, 디스플레이 디바이스, 및 발광 디바이스의 디바이스들 및 그것을 제조하는 방법에 관한 것이다. 본 발명에 따른 반도체 디바이스는 CPU(중앙 처리 장치), MPU(마이크로 처리 장치), 메모리, 마이크로컴퓨터 및 이미지 처리 기기를 포함한다. 본 발명에 따른 디스플레이 디바이스는 액정 디스플레이 디바이스, PDP(플라즈마 디스플레이 패널), FED(전계 방출 디스플레이) 등을 포함한다.

### 배경기술

[0002]

최근에, 절연 표면을 갖는 기판 위에 형성된 반도체 박막(대략 수 nm 내지 수백 nm의 두께를 가짐)을 사용하여 TFT를 형성하는 기술들이 주의를 끌고 있다. TFT는 IC, 광학 디바이스 등과 같은 전자 디바이스에 폭넓게 사용된다.

[0003]

이 TFT들을 형성하기 위한 기판으로서, 유리 기판 또는 석영 기판이 지금은 광범위하게 사용되고 있지만, 이들 기판들은 부서지기 쉽고 무겁다는 몇 가지 단점들을 갖는다. 또한, 이들 기판들을 대형화하는데 어려움이 있기 때문에 이들 기판들은 대량 생산에 적합하지 않다. 그러므로 TFT들로 이루어진 디바이스는 가요성(flexibility)을 갖는 기판, 대표적으로 플렉서블(flexible) 플라스틱막 위에 형성되게 된다.

[0004]

그러나, 플라스틱막의 열 저항이 낮기 때문에 처리 최고 온도를 낮춰야 하며, 그 결과 유리 기판 위에 형성된 TFT의 전기 특성들보다 양호한 전기 특성들을 갖는 TFT가 형성될 수 없다. 따라서, 기판 위에 직접 형성된 TFT를 포함하는 반도체 디바이스, 디스플레이 디바이스, 또는 발광 디바이스는 아직 실현되지 않았다.

[0005]

동시에, 유리 기판 또는 석영 기판 위에 박막 디바이스를 형성하고, 기판으로부터 박막 디바이스를 벗겨내고(피전사체(exfoliated body)) 그 다음 플라스틱 기판 등과 같은 전사체(transferred body)로 전사하는 기술들이 공개되어 있다(예를 들어, 심사되지 않은 특허 공보 번호 10-125929).

[0006]

반도체 디바이스, 디스플레이 디바이스, 또는 발광 디바이스가 플라스틱막과 같은 가요성을 갖는 기판 위에 제조될 수 있다면, 이들 디바이스들은 얇고 경량이고 플렉서블하고 굴곡이 있는 디스플레이에 이용될 수 있으므로, 응용 범위가 넓어질 수 있다.

[0007]

상술된 전사 기술을 이용함으로써, 양호한 전기 특성들을 갖는 TFT를 각각 갖는 반도체 디바이스(CPU, MPU, 메모리, 마이크로 컴퓨터, 영상 처리기 등), 디스플레이 디바이스(액정 디스플레이 디바이스, PDP, FED 등) 또는 발광 디바이스를 포함하는 층(하기에서, 디바이스 형성층)이 플라스틱 등과 같은 전사체 위에서 제조될 수 있다. 그러나, 유기 물질로 형성된 플라스틱과 같은 전사체가 수분, 산소 등을 투과할 수 있으므로, 이러한 전사체는 피전사체를 밀봉하는데 적합하지 않다.

### 발명의 내용

#### 해결하려는 과제

[0008]

상술된 것을 고려하면, 본 발명의 목적은 얇고 경량이고 굴곡이 있고 플렉서블한 구조에 더하여, 외부로부터 수분, 산소 등이 디바이스 형성층으로 침투하는 것을 방지할 수 있는 구조를 각각 갖는 반도체 디바이스, 디스플레이 디바이스, 및 발광 디바이스의 디바이스들 및 그들을 제조하는 방법을 제공하는 것이다.

[0009] 반도체 디바이스, 디스플레이 디바이스, 또는 발광 디바이스가 본 발명에 따라 제조되는데, 여기서 디바이스 형성층은 불소 수지막(불소 탄소 수지막)으로 덮이며; 디바이스 형성층에 포함된 TFT는 얇고 경량이고 플렉서블하고 굴곡이 있는 표면을 갖도록 섬형 반도체막들로 형성되며; 수분, 산소 등이 그 디바이스로 침투하지 못한다.

### 과제의 해결 수단

[0010] 본 발명을 구성하는 특정 구조가 다음과 같이 제공된다: 다수의 박막 트랜지스터들을 포함하는 디바이스 형성층을 갖는 반도체 디바이스, 디스플레이 디바이스 또는 발광 디바이스에 있어서, 상기 반도체 디바이스는 디바이스 형성층에 접촉하여 형성된 불소 수지막으로 덮이는, 반도체 디바이스, 디스플레이 디바이스 또는 발광 디바이스.

[0011] 상기된 구조에서, 불소 수지막은 디바이스 형성층 위에 형성되며, 디바이스 형성층에 형성된 TFT들과 TFT들에 접속하여 형성된 발광 디바이스가 수분 또는 산소와 같은 기체로 인해 품질저하되는 것을 방지하는 기능을 갖는다. 게다가, 그 구조에서 열 전도층은 디바이스 형성층의 한쪽 또는 두 쪽 표면들에 접촉하여 형성되며, 디바이스 형성층은 불소 수지막으로 덮인다.

[0012] 본 발명을 구성하는 다른 구조가 다음과 같이 제공된다: 제 1 절연막 위에 형성된 소스 영역, 드레인 영역 및 채널 형성 영역을 포함하는 섬형 반도체막; 게이트 절연막을 통해 반도체막 위에 형성되고, 게이트 전극을 포함하는 박막 트랜지스터; 박막 트랜지스터의 소스 영역 또는 드레인 영역에 전기적으로 접속된 배선을 포함하는 디바이스 형성층을 갖는 반도체 디바이스, 디스플레이 디바이스, 또는 발광 디바이스에 있어서, 상기 반도체 디바이스, 디스플레이 디바이스 또는 발광 디바이스는,

디바이스 형성층을 덮도록 형성된 제 2 절연막과;

[0014] 제 1 절연막과 제 2 절연막에 접촉하여 형성된 불소 수지막을 포함하는, 반도체 디바이스, 디스플레이 디바이스, 또는 발광 디바이스.

[0015] 상기 디스플레이 디바이스에 관한 다른 구조가 다음과 같이 제공된다: 제 1 절연막 위에 형성된 소스 영역, 드레인 영역 및 채널 형성 영역을 포함하는 섬형 반도체막; 게이트 절연막을 통해 반도체막 위에 형성되고 게이트 전극을 포함하는 박막 트랜지스터; 박막 트랜지스터의 소스 영역 또는 드레인 영역에 전기적으로 접속된 배선을 포함하는 디바이스 형성층을 갖는 디스플레이 디바이스에 있어서, 상기 디스플레이 디바이스는,

디바이스 형성층을 덮도록 형성된 제 2 절연막과;

[0017] 제 1 절연막과 제 2 절연막에 접촉하여 형성된 불소 수지막을 포함하는, 디스플레이 디바이스.

[0018] 상기 디스플레이 디바이스에 관한 다른 구조가 다음과 같이 제공된다: 층간 절연막을 통해 제 1 절연막 위에 형성된 박막 트랜지스터에 전기적으로 접속된 제 1 전극; 제 1 전극 위에 형성된 전계 발광막; 및 전계 발광막 위에 형성된 제 2 전극을 포함하는 발광 디바이스를 갖는 발광 디바이스에 있어서, 상기 발광 디바이스는,

[0019] 제 1 절연막과 제 2 전극에 접촉하여 형성된 불소 수지막을 포함하는, 발광 디바이스.

[0020] 상기 각 구조에서, 불소 수지막이 불소 수지막의 가요성에 반하지 않고 소스 영역, 드레인 영역 및 채널 형성 영역을 갖는 섬형 반도체막 위에 형성된다는 사실로부터 그 반도체막을 덮는 불소 수지막이 형상들의 변화들에 적응될 수 있으므로, 불소 수지막은 품질저하되지 않으면서 다양한 형상들의 응용에 적용될 수 있음을 알 수 있다.

[0021] 게다가, TFT들 및 TFT들로 이루어진 반도체 디바이스(CPU, MPU, 메모리, 마이크로컴퓨터, 또는 이미지 처리기); 디스플레이 디바이스(액정 디바이스, PDP, 또는 FED); 또는 TFT들로 각각 이루어진 발광 디바이스(하기에서 디바이스 형성층)가 디바이스 형성층을 이용하여 제조될 수 있다.

[0022] 상기 각 구조에서, 디바이스 형성층은 반도체 디바이스, 디스플레이 디바이스 또는 발광 디바이스에서 최대 50  $\mu\text{m}$ 의 두께를 갖는다.

[0023] 본 발명에 따른 불소 수지막은 불소를 함유한 폴리에틸렌, 불소를 함유한 폴리프로필렌, 또는 불소를 함유한 폴리비닐렌(polyvinylene) 또는 이들 화합물의 공중합체(copolymer)와 같은 화학적 화합물로부터 선택된 한 타입으로 형성된다.

- [0024] 상기 각 구조에서, 제조된 반도체 디바이스, 디스플레이 디바이스, 또는 발광 디바이스는 선불 카드, 신용 카드, 자동차 운전 면허증 또는 착용 가능한 컴퓨터에 이용될 수 있다.

- [0025] 본 발명에 따른 상기 구조를 얻기 위한 구조가 다음과 같이 제공된다; 반도체 디바이스를 제조하는 방법에 있어서,

- [0026] 제 1 기판 위에 다수의 박막 트랜지스터들을 포함하는 디바이스 형성층을 형성하는 단계와,

- [0027] 상기 디바이스 형성층에 접촉하여 제 1 접착층을 형성하는 단계와,

- [0028] 제 2 기판을 상기 제 1 접착층에 접합하고, 상기 제 1 기판과 제 2 기판 사이에 상기 디바이스 형성층을 개재하는 단계와,

- [0029] 물리적 수단에 의해 상기 제 1 기판을 상기 디바이스 형성층에서 분리하고 제거하는 단계와,

- [0030] 스퍼터링에 의해 노출된 표면 위에 제 1 불소 수지막을 형성하는 단계와,

- [0031] 상기 제 1 불소 수지막에 접촉하여 제 2 접착층을 형성하는 단계와,

- [0032] 제 3 접착층을 제 2 접착층에 접합하는 단계와,

- [0033] 상기 제 1 접착층과 상기 제 2 기판을 상기 디바이스 형성층에서 분리하고 제거하는 단계와,

- [0034] 스퍼터링에 의해 노출된 표면 위에 제 2 불소 수지막을 형성하는 단계와,

- [0035] 상기 제 2 접착층과 상기 제 3 기판을 상기 디바이스 형성층에서 분리하고 제거하는 단계를 포함하는, 반도체 디바이스 제조 방법.

- [0036] 상기 각 구조에서, 물리적 수단에 의해 상기 제 1 기판을 분리하고 제거하기 위해,

- [0037] 제 1 기판 위에 금속층을 형성하는 단계와,

- [0038] 상기 금속층 위에 산화물층을 형성하는 단계와,

- [0039] 상기 산화물층 위에 제 1 절연막을 형성하는 단계와,

- [0040] 상기 제 1 절연막 위에 수소를 함유하는 비정질 구조의 반도체막을 형성하는 단계와,

- [0041] 수소를 확산하기 위해 상기 반도체막을 열 처리하는 단계와,

- [0042] 다수의 박막 트랜지스터들을 포함하는 디바이스 형성층을 형성하는 단계로서, 상기 박막 트랜지스터 일부는 상기 반도체막을 가지는, 상기 형성 단계를 포함한다.

- [0043] 본 발명에 있어서, 디스플레이 디바이스를 제조하는 방법에 있어서, TFT들에 전기적으로 접속하는 디바이스는 디바이스 형성층의 픽셀부에 형성되며,

- [0044] 제 1 기판 위에 금속층을 형성하는 단계와,

- [0045] 상기 금속층 위에 산화물층을 형성하는 단계와,

- [0046] 상기 산화물층 위에 제 1 절연막을 형성하는 단계와,

- [0047] 상기 제 1 절연막 위에 수소를 함유하는 비정질 구조의 반도체막을 형성하는 단계와,

- [0048] 수소를 확산하기 위해 상기 반도체막을 열처리하는 단계와,

- [0049] 다수의 박막 트랜지스터들을 형성하는 단계로서, 상기 박막 트랜지스터의 일부는 상기 반도체막을 갖는, 상기 형성 단계와,

- [0050] 층간 절연막을 통해 상기 박막 트랜지스터에 전기적으로 접속된 제 1 전극을 형성하는 단계와,

- [0051] 상기 제 1 전극에 접촉하여 제 1 접착층을 형성하는 단계와,

- [0052] 제 2 기판을 상기 제 1 접착층에 접합하는 단계와,

- [0053] 상기 제 1 기판과 상기 금속층을 상기 금속층과 상기 제 1 절연막 사이의 계면에서 분리하고 제거하는 단계와,

- [0054] 노출된 표면 위에 제 1 불소 수지막을 형성하는 단계와,

- [0055] 상기 제 1 불소 수지막에 접촉하여 제 2 접착층을 형성하는 단계와,

- [0056] 제 3 기판을 상기 제 2 접착층에 접합하는 단계와,

- [0057] 상기 제 1 접착층과 상기 제 2 기판을 상기 제 1 전극의 표면에서 분리하고 제거하는 단계와,

- [0058] 상기 제 1 전극의 노출된 표면상에 제 1 전극을 포함하는 디바이스를 형성하는 단계와,

- [0059] 상기 디바이스 위에 제 2 불소 수지막을 형성하는 단계와,

- [0060] 상기 제 2 접착층과 상기 제 3 기판을 상기 제 1 불소 수지막에서 분리하고 제거하는 단계를 포함하는, 디스플레이 디바이스 제조 방법.

- [0061] 본 발명에 있어서, 발광 디바이스를 제조하는 방법에 있어서, TFT들에 전기적으로 접속하는 디바이스는 디바이스 형성층의 괜셀부에 형성되며,

- [0062] 제 1 기판 위에 금속층을 형성하는 단계와,

- [0063] 상기 금속층 위에 산화물층을 형성하는 단계와,

- [0064] 상기 산화물층 위에 제 1 절연막을 형성하는 단계와,

- [0065] 상기 제 1 절연막 위에 수소를 함유하는 비정질 구조의 반도체막을 형성하는 단계와,

- [0066] 수소를 확산하기 위해 상기 반도체막을 열처리하는 단계와,

- [0067] 다수의 박막 트랜지스터들을 형성하는 단계로서, 상기 박막 트랜지스터의 일부는 상기 반도체막을 갖는, 상기 형성 단계와,

- [0068] 층간 절연막을 통해 상기 박막 트랜지스터에 전기적으로 접속된 제 1 전극을 형성하는 단계와,

- [0069] 상기 제 1 전극에 접촉하여 제 1 접착층을 형성하는 단계와,

- [0070] 제 2 기판을 상기 제 1 접착층에 접합하는 단계와,

- [0071] 상기 제 1 기판과 상기 금속층을 상기 금속층과 상기 제 1 절연막 사이의 계면에서 분리하고 제거하는 단계와,

- [0072] 노출된 표면 위에 제 1 불소 수지막을 형성하는 단계와,

- [0073] 상기 제 1 불소 수지막과 접하여 제 2 접착층을 형성하는 단계와,

- [0074] 제 3 기판을 상기 제 2 접착층에 접합하는 단계와,

- [0075] 상기 제 1 접착층과 상기 제 2 기판을 상기 제 1 전극의 표면에서 분리하고 제거하는 단계와,

- [0076] 상기 제 1 전극의 노출된 표면상에 전계 발광막을 형성하는 단계와,

- [0077] 상기 전계 발광막 위에 제 2 전극을 형성하는 단계와,

- [0078] 상기 제 2 전극상에 제 2 불소 수지막을 형성하는 단계와,

- [0079] 상기 제 2 접착층과 상기 제 3 기판을 상기 제 1 불소 수지막에서 분리하고 제거하는 단계를 포함하는, 발광 디바이스 제조 방법.

- [0080] 상기 각 구조에서, 제 1 불소 수지막 또는 제 2 불소 수지막은 스퍼터링 또는 스펀 코팅과 같은 코팅에 의해 형성된다.

- [0081] 상기 각 구조에서, 제 1 불소 수지막에 접촉하여 제 2 접착층을 형성하기 전에 막 형성의 특성을 향상시키기 위해 제 1 불소 수지막은 역스퍼터링될 수 있다.

- [0082] 이 경우에, 불소 수지막은 20 내지 500sccm으로 된 Ar 기체를 주입하면서 0.6 내지 150Pa의 스퍼터링 압력 조건들 하에서 역스퍼터링될 수 있다. 역스퍼터링은 다음과 같은 조건들하에서 방전을 여기하기 위해 1 내지 20분 동안 행해지는 것이 바람직하다; 즉 20kV 내지 120MV의 고주파수 파워가 인가되고; 사용된 RF 파워가 0.06 내지 3.18W/cm<sup>2</sup>이며, 기판 온도가 실내 온도 내지 200°C이다.

- [0083] 상기된 바와 같이, 반도체 디바이스, 디스플레이 디바이스 또는 발광 디바이스 각각은 얇고 경량이고 플렉서블하고 굴곡이 있는 표면을 갖는 구조뿐만 아니라, 외부로부터 수분, 산소 등이 디바이스 형성층으로 침투하는 것

을 방지하는 구조를 갖는다.

### 발명의 효과

[0084] 본 발명을 구현함으로써, 박막의 반도체 디바이스, 디스플레이 디바이스 또는 발광 디바이스는 경량이고 플렉서블하고 굴곡이 있는 표면을 갖도록 형성될 수 있다. 또한, 외부로부터 수분, 산소 등이 디바이스 형성층으로 침투하는 것을 방지할 수 있으며, 따라서 디바이스 특성들의 품질저하가 방지될 수 있다.

### 도면의 간단한 설명

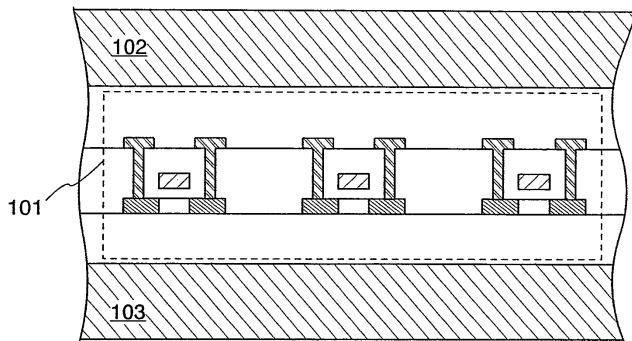

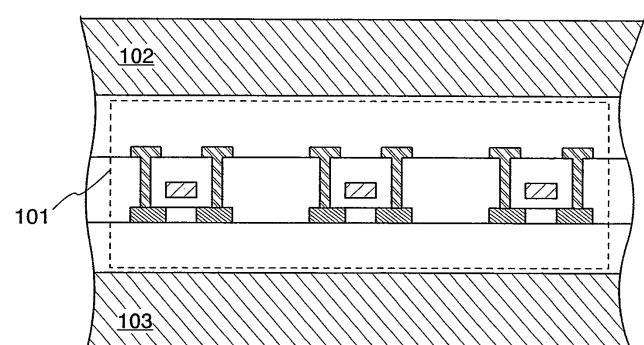

[0085] 도 1은 본 발명에 따른 반도체 디바이스의 구조를 도시하는 설명도.

도 2a 내지 도 2c는 본 발명에 따라 반도체 디바이스를 제조하는 방법을 도시하는 설명도.

도 3a 내지 도 3c는 본 발명에 따라 반도체 디바이스를 제조하는 방법을 도시하는 설명도.

도 4a 내지 도 4c는 본 발명에 따라 반도체 디바이스를 제조하는 방법을 도시하는 설명도.

도 5a 내지 도 5d는 TFT를 제조하는 공정(process)을 도시하는 설명도.

도 6a 내지 도 6d는 TFT를 제조하는 공정을 도시하는 설명도.

도 7a 내지 도 7c는 본 발명에 따른 반도체 디바이스의 외부 접속의 구조를 도시하는 설명도.

도 8a 내지 도 8b는 본 발명에 따른 발광 디바이스를 도시하는 설명도.

도 9a 내지 도 9g는 본 발명에 따른 반도체 디바이스 등을 사용하는 응용 제품을 도시하는 설명도.

도 10a 내지 도 10d는 불소 수지막의 ESCA 측정 결과들을 도시하는 설명도.

도 11a 내지 도 11d는 불소 수지막의 ESCA 측정 결과들을 도시하는 설명도.

도 12는 불소 수지막의 IR 측정 결과들을 도시하는 설명도.

도 13은 본 발명에 따라 반도체 디바이스의 구조를 도시하는 설명도.

### 발명을 실시하기 위한 구체적인 내용

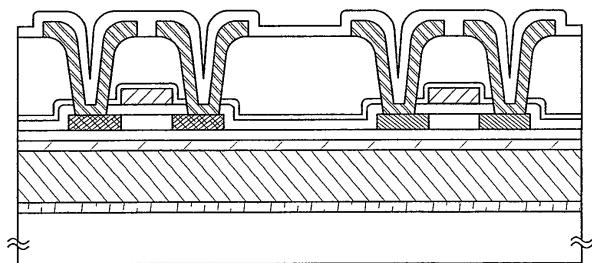

[0086] 도 1은 본 발명에 따라 제조된 반도체 디바이스의 구조를 도시한 도면이다. 따라서, 반도체 디바이스는 다수의 TFT들의 조합을 포함하는 디바이스 형성층(101)이 불소 수지막들(102 및 103)에 의해 덮인 구조를 갖는다. 이러한 반도체 디바이스를 제조하는 방법은 도 2 내지 도 4를 참조하여 보다 상세히 설명될 것이다.

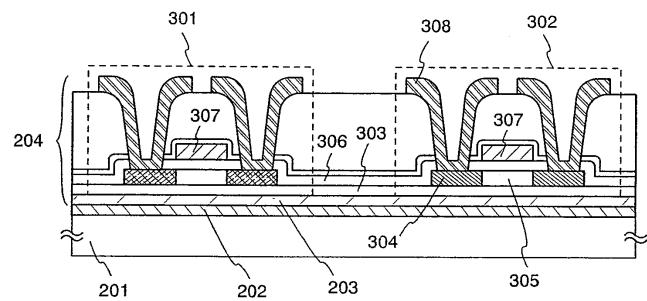

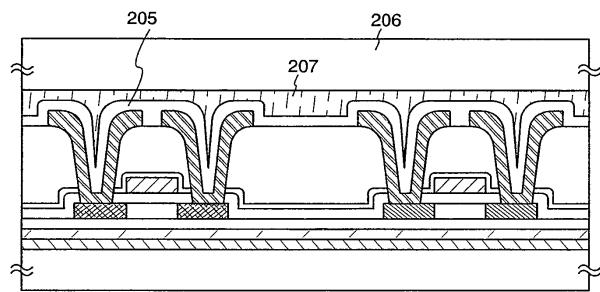

[0087] 도 2a는 제 1 기판(201) 위에 금속층(202) 및 산화물층(203)이 순차적으로 형성되며, 그 위에 디바이스 형성층(204)이 형성된 상태를 도시한 도면이다.

[0088] 제 1 기판(201)으로서, 유리 기판, 석영 기판, 세라믹 기판 등이 사용될 수 있다. 게다가, 실리콘 기판, 금속 기판, 또는 스테인레스 기판도 사용될 수 있다.

[0089] 제 1 기판(201)상에 형성된 금속층(202)용 물질들로서는, W, Ti, Ta, Mo, Nd, Ni, Co, Zr, Zn, Ru, Rh, Pd, Os, Ir 및 Pt로 이루어진 그룹에서 선택된 원소; 또는 주성분으로서 그 원소들을 함유하는 합금 물질 또는 화합물질로 형성된 단층; 또는 단층들로 된 적층; 또는 질화물, 예를 들어 티타늄 질화물, 텉스텐 질화물, 탄탈 질화물, 또는 몰리브덴 질화물로 형성된 단층 또는 적층을 이용하면 좋다. 금속층(202)은 10 내지 200nm의 두께를 갖도록 형성되며, 바람직하게는 50 내지 75nm의 두께를 갖도록 형성되면 좋다.

[0090] 스퍼터링에 의해 금속층(202)을 형성하는 경우에, 그 주변부 근처에서 제 1 기판(201)의 두께는 제 1 기판(201)이 고정되기 때문에, 불균일(inhomogeneous)하게 되는 경향이 있다. 그러므로, 주변부만이 건식 애칭에 의해 제거되는 것이 바람직하다. 이 점에 있어서는, 제 1 기판(201)이 애칭되지 않도록 기판(201)과 금속층(202) 사이에 산화질화 실리콘막으로 형성된 절연막이 약 100nm의 두께를 갖도록 형성될 수 있다.

[0091] 금속층(202) 위에 형성된 산화물층(203)은 실리콘 산화물, 실리콘 산화질화물, 및 금속 산화물 물질들을 사용하여 스퍼터링에 의해 형성된다. 산화물층(203)의 두께는 금속층(202)의 두께보다 2배 이상 큰 것이 바람직하다. 예를 들어, 실리콘 산화막은 실리콘 산화물 타겟들을 사용하여 스퍼터링에 의해 150 내지 200nm의 두께를 갖도록 형성되는 것이 바람직하다.

- [0092] 산화물층(203) 위에 형성된 디바이스 형성층(204)은, TFT들(p-채널 TFT(301) 및 n-채널 TFT(302))을 적절하게 조합함으로써 반도체 디바이스, 디스플레이 디바이스, 또는 발광 디바이스가 형성되는 층이다. p-채널 TFT(301) 및 n-채널 TFT(302) 각각은 베이스막(303), 반도체막의 일부에 형성된 불순물 영역(304), 및 채널 형성 영역(305) 외에, 게이트 절연막(306), 게이트 전극(307) 및 배선(308)으로 이루어져 있다.

- [0093] 디바이스 형성층(204)을 형성하는 공정에서, 적어도 수소를 함유하는 재료막(반도체막 또는 금속막)을 형성한 후 수소를 확산하기 위해 열 처리가 행해진다. 적어도 410°C에서 열처리가 행해질 수 있다. 열처리는 디바이스 형성층(204)을 형성하는 공정과는 별도로 행해지거나 공정들을 간략화하기 위해 동시에 행해질 수 있다. 예를 들어, 재료막으로서 수소를 함유하는 비정질 실리콘막을 사용하고, 폴리실리콘막을 형성하기 위해 비정질 실리콘막을 가열하는 경우, 폴리실리콘막을 형성하기 위해 비정질 실리콘막을 결정화하는 동시에, 비정질 실리콘막 내의 수소가 적어도 500°C의 열처리에 의해 확산될 수 있다.

- [0094] 그 다음, 질화물층(205)은 디바이스 형성층(204) 위에 형성된다. 여기서, 질화물층(205)은 스퍼터링에 의해 대략 50nm의 두께를 갖도록 형성된다.

- [0095] 디바이스 형성층(204)과 질화물층(205)을 고정시키기 위한 지지체(support medium)인 제 2 기판(206)이 제 1 접착층(207)에 접합되어 있다(도 2). 제 2 기판(206)으로는, 유리 기판, 석영 기판, 세라믹 기판, 또는 플라스틱 기판 외에 스테인레스 기판을 대표하는 금속 기판 또는 실리콘 기판을 대표하는 반도체 기판이 사용될 수 있다. 제 2 기판(206)은 제 1 기판(201)의 강성(rigidity)보다 강한 강성을 갖는 것이 바람직하다.

- [0096] 제 1 접착층(207)용 재료로서는, 광 경화(photo-curing) 접착제, 예를 들어, 반응 경화(reaction-curing) 접착제, 열 경화 접착제, 또는 UV 경화 접착제, 또는 협기 접착제와 같은 다양한 경화 접착제들이 사용될 수 있다. 게다가, 이 접착제들은 물 또는 유기 용매에 녹기 쉽고, 낮은 감광성, 즉 접착제가 광 조사에 의해 접착성이 약해지는 재료로 형성되는 것이 바람직하다. 이 접착제들의 구성으로서는, 예를 들어 에폭시 베이스, 아크릴 베이스, 실리콘 베이스 등이 적용될 수 있다. 게다가, 제 1 접착층(207)은 코팅 등에 의해 형성된다. 제 1 접착층(207)은 다음 공정에서 제거될 것이다.

- [0097] 이 실시예 모드에서, 제 1 접착층(207)용 재료로서는, 물 또는 유기 용매에 녹기 쉬운 접착층이 사용된다.

- [0098] 그러나, 그에 한정되는 것은 아니고, 양면 테이프(낮은 감광성, 즉 광 조사에 의해 양면 테이프의 접착성이 약해짐) 또는 상기 접착제와 양면 테이프의 조합이 제 1 접착층(207)용 재료로서 사용될 수 있다.

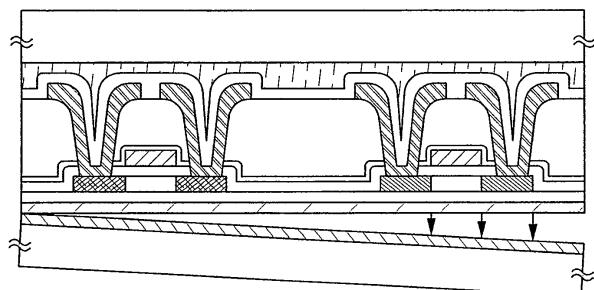

- [0099] 금속층(202)에 제공되는 제 1 기판(201)은 분리된다(도 2c). 산화물층(203)과 금속층(202)의 막 응력(membrane stress)이 서로 다르기 때문에 제 1 기판(201)은 비교적 작은 힘에 의해 분리될 수 있다.

- [0100] 이에 따라, 산화물층(203) 상에 형성된 디바이스 형성층(204)이 제 1 기판(201)과 금속층(202)으로부터 분리될 수 있다.

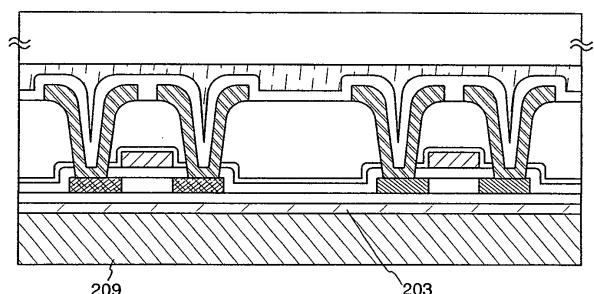

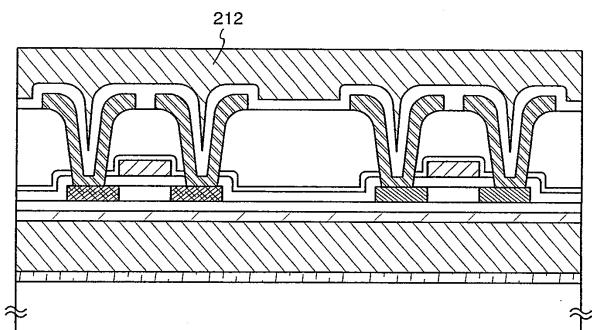

- [0101] 다음에, 불소 수지막(209)이 분리에 의해 노출된 산화물층(203)의 표면상에 스퍼터링에 의해 형성될 수 있다(도 3a). 질화물층(208)은 불소 수지막(209)이 형성되기 전에 형성될 수 있다.

- [0102] 불소 수지막(209)을 스퍼터링에 의해 침착하는 조건들로는, 공정 기체로서 사용된 Ar 기체는 30sccm이며(5sccm O<sub>2</sub> 기체가 Ar 기체 외에 사용될 수 있다), 사용된 스퍼터링 압력은 0.4Pa이며, 전력은 400W이고, 기판 온도는 300°C이다. 불소 수지막(209)이 1 내지 100μm의 두께를 갖도록 형성된다.

- [0103] 본 발명에 따라 불소 수지막(209)을 형성하기 위해서, 폴리테트라 플루오르에틸렌, 테트라플루오르에틸렌-헥사플루오르프로필렌 공중합체, 폴리클로르트리플루오르에틸렌, 테트라플루오르에틸렌-에틸렌 공중합체, 폴리비닐 플루오르화물, 폴리비닐리덴 플루오르화물 등이 사용된다.

- [0104] 스펜 코팅과 같은 코팅에 의해 불소 수지막(209)을 형성하는 경우에, 용매로서 물을 사용하는 불소 수지 용액(액체 불소 수지 코팅)이 사용될 수 있다.

- [0105] 불소 수지막(209)의 형성은 디바이스 형성층(204)에 포함된 TFT들(도시되지 않았지만, 발광 디바이스를 갖는 경우에는 발광 디바이스일 것이다)의 디바이스 특성들에 유익하게 영향을 미치며, 품질저하를 야기시키는 수분이나 산소와 같은 기체의 침투를 막는다.

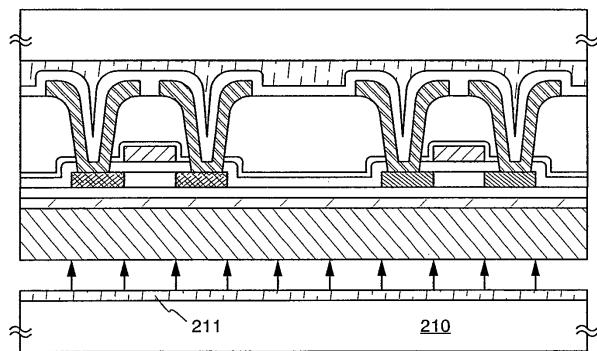

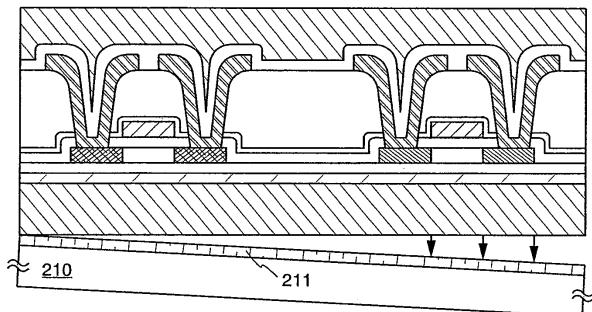

- [0106] 제 3 기판(210)은 제 2 접착층(211)을 사용하여 불소 수지막(209)에 접합된다(도 3b). 제 3 기판(210)용 재료로서는, 제 2 기판(206)의 재료와 동일한 재료가 사용될 수 있다. 제 2 접착층(211)용 재료로서는, 제 1 접착

층(207)의 재료와 동일한 재료가 사용될 수 있다. 제 2 접착층(211)으로서, 낮은 감광성, 즉 광 조사에 의해 양면 테이프의 접착성이 약해지는 양면 테이프가 제 3 기판(210)을 불소 수지막(209)에 접합시키는데 사용된다.

[0107] 그 다음, 제 2 기판(206) 및 제 1 접착층(207)이 제거된다(도 3c). 제 1 접착층(207)에 사용되는 접착제가 물 또는 유기 용매에 녹기 쉬운 경우, 접착제는 물 또는 유기 용매로 세척함으로써 제거되며, 그 다음 제 2 기판(206)이 분리된다. 제 1 접착층에 사용되는 접착제가 감광성(photosensitivity) 즉, 광 조사에 의해 약해지는 접착성을 갖는 경우, 제 2 기판(206)이 분리된다. 또한, 양면 테이프와 수용성 접착제의 조합이 사용되는 경우, 첫째로, 광이 양면 테이프의 접착성을 약해지게 하기 위해서 조사될 수 있으며, 둘째로, 제 2 기판(206), 디바이스 형성층(204) 등이 분리될 수 있으며, 셋째로, 디바이스 형성층(204) 등 위에 남아있는 수용성 접착제가 물 세척에 의해 제거될 수 있다.

[0108] 불소 수지막(212)은 제 2 기판과 제 1 접착층(207)을 제거함으로써 노출되는 질화물층(205) 상에 스퍼터링에 의해 형성된다(도 4a). 불소 수지막(212)은 불소 수지막(209)의 재료와 동일한 재료를 사용함으로써 및 불소 수지막(209)의 방법과 동일한 방법을 사용함으로써 형성될 수 있다.

[0109] 도 4c에 도시된 구조를 갖는 반도체 디바이스는 광을 제 3 기판(210)의 측면으로부터 조사함으로써 양면 테이프의 접착성을 약하게 하는 것에 의해 또는 디바이스 형성층(204)으로부터 제 3 기판(210) 및 제 2 접착층(211)을 분리시킴으로써 제조된다.

[0110] 실시예들

[0111] 본 발명의 실시예들은 하기에 기술될 것이다.

[0112] [실시예 1]

[0113] 본 발명의 실시예들은 도 5 및 도 6을 참조하여 기술될 것이다. 한 기판 위에 n-채널 TFT 및 p-채널 TFT를 동시에 형성하는 방법이 하기에 기술될 것이다.

[0114] 석영 기판, 반도체 기판, 세라믹 기판, 금속 기판 등이 기판(500)으로서 사용될 수 있다. 이 실시예에서, 유리 기판(#1737)이 기판(500)으로 사용된다. 우선, 실리콘 산화질화물층이 질화물층(501)으로서 PCVD에 의해 기판(500) 위에 100nm의 두께를 갖도록 형성된다.

[0115] 이어서, 텅스텐층이 금속층(502)으로서 스퍼터링에 의해 50nm의 두께를 갖도록 형성되며, 200nm의 두께를 갖도록 산화물층(503)이 대기애 노출되지 않고 실리콘 산화물층으로서 스퍼터링에 의해 연속적으로 형성된다. 실리콘 산화물층은 다음과 같은 조건하에서 형성된다; 즉 RF 스퍼터링 디바이스를 사용하여; 실리콘 산화물 타겟(직경 30.5cm)을 사용하여; 기판을 가열하기 위해 가열된 아르곤 기체를 30sccm의 유량으로 흐르게 하여; 기판 온도를 300°C로 설정하여; 막 형성 압력은 0.4Pa로; 전력은 3kW로; 아르곤 유량/산소 유량=10sccm/30sccm으로 한다.

[0116] 이어서, 기판의 주변 또는 에지들에서 텅스텐층이 O<sub>2</sub> 애싱(ashing)을 사용하여 제거된다.

[0117] 이어서, 재료 기체들로서 SiH<sub>4</sub> 및 N<sub>2</sub>O로 형성된 실리콘 산화질화물막(조성비율: Si=32%, O=59%, N=7%, H=2%)이 플라즈마 CVD에 의해 300°C의 침착 온도에서 100nm의 두께를 갖도록 쌓여진다. 또한, 비정질 구조를 갖는 반도체막(이 경우에, 비정질 실리콘막)이 플라즈마 CVD에 의해 300°C의 침착 온도에서 침착 기체로서 SiH<sub>4</sub>를 사용하여 대기애 노출 없이 54nm의 두께를 갖도록 형성된다. 이 비정질 실리콘막은 수소를 포함하며, 그 수소는 다음의 열처리에 의해 확산될 것이며, 비정질 실리콘막은 물리적 수단에 의해 산화물층에서 또는 산화물층의 계면에서 벗겨질 수 있다.

[0118] 그 다음, 중량으로 10ppm의 니켈을 함유하는 초산 니켈염 용액(nickel acetate salt solution)이 스피너(spinner)를 사용하여 코팅된다. 코팅 대신에, 스퍼터링에 의해 니켈 원소들을 전체 표면에 산포하는(spray) 방법이 또한 사용될 수 있다. 그 다음, 결정화를 위해 열 처리가 행해져 결정화 구조를 갖는 반도체막을 형성한다(여기서, 폴리실리콘층이 형성된다). 여기서, 탈수소화를 위해 열 처리(1시간 동안 500°C)가 행해지고 결정화를 위해 열 처리(4시간 동안 550°C)가 행해진 후, 결정화 구조를 갖는 실리콘막이 형성된다. 또한, 탈수소화를 위한 열 처리(1시간 동안 500°C)는 비정질 실리콘층에 함유된 수소를 텅스텐막과 실리콘 산화물층과의 계면으로 확산하는 기능을 갖는다. 또한, 실리콘의 결정화를 촉진하는 금속 원소로서 니켈을 사용하는 결정화 기술이 여기에 사용된다 하더라도, 다른 공지된 결정화 기술들, 예를 들어, 고상(solid-phase) 성장법 및 레이저

결정화법이 사용될 수 있음에 유념하라.

[0119] 다음에, 결정화 구조를 갖는 실리콘막의 표면 상의 산화물막이 묽은 불소 수소산 등에 의해 제거된 후, 레이저빔(XeCl: 파장 308nm)이 대기에서 또는 산소 분위기에서 결정화 속도를 높이고 결정립(crystal grain)에 남아 있는 결함들을 보수하기 위해 조사된다. 레이저빔으로서는 400nm 이하의 파장을 갖는 엑시머 레이저빔과 YAG 레이저의 제 2 고조파 또는 제 3 고조파가 사용된다. 입의의 경우에, 대략 10 내지 1000Hz의 반복 주파수를 갖는 펄스 레이저빔이 사용되며, 펄스 레이저빔은 광학 시스템에 의해 100 내지 500mJ/cm<sup>2</sup>로 집중되며, 90 내지 95%의 오버랩 비율로 조사가 수행되며, 그것에 의해 실리콘막 표면이 스캔될 수 있다. 여기서, 레이저빔은 30 Hz의 반복 주파수와 470mJ/cm<sup>2</sup>의 에너지 밀도로 대기에서 조사된다.

[0120] 레이저빔이 대기에서 또는 산소 분위기에서 조사되기 때문에 산화막이 표면위에 형성됨에 유념하라. 펄스 레이저를 사용하는 예가 여기에 도시되어있지만, 연속 발진 레이저가 또한 사용될 수 있다. 비정질 반도체막의 결정화가 행해질 때, 큰 입자(grain) 크기로 결정을 얻기 위해 연속 발진을 할 수 있는 고체 레이저를 사용함으로써 기본파의 제 2 고조파 내지 제 4 고조파를 적용하는 것이 바람직하다. 전형적으로, Nd:YVO<sub>4</sub> 레이저(기본파 1064nm)의 제 2 고조파(두께 532nm) 또는 제 3 고조파(두께 355nm)를 적용할 수 있는 것이 바람직하다. 특히, 10W의 출력을 갖는 연속 발진형 YVO<sub>4</sub> 레이저로부터 방출된 레이저빔들이 비선형 광학 소자들을 사용하여 고조파로 변환된다. 또한, 공진기에 YVO<sub>4</sub>의 결정과 비선형 광학 소자들을 적용함으로써 고조파를 방출하는 방법이 적용될 수 있다. 그 다음, 보다 바람직하게, 레이저빔들이 광학 시스템에 의해 직사각형 형상 또는 타원 형상을 갖도록 형성되며, 물질이 레이저빔에 노출된다. 이 때, 대략 0.01 내지 100MW/cm<sup>2</sup>의 에너지 밀도가 요구된다(0.1 내지 10MW/cm<sup>2</sup>가 바람직함). 반도체막은 레이저빔에 노출되기 위해 레이저빔들에 따라 상대적으로 대략 10 내지 2000cm/s 속도로 이동된다.

[0121] 이 레이저빔 조사에 의해 형성된 산화막 외에, 총 1 내지 5nm의 두께를 갖기 위해 오존 물로 표면을 120초 동안 처리함으로써 산화막이 배리어층으로서 형성된다. 배리어층이 여기서 오존 물을 사용하여 형성되지만, 산소 분위기에서 자외선 광 조사 또는 결정 구조를 갖는 반도체막의 표면을 산화시키기 위한 산화물 플라즈마 처리와 같은 다른 방법이 사용될 수 있다. 게다가, 배리어층을 형성하는 다른 방법으로서, 대략 1 내지 10nm의 두께를 갖는 산화막이 플라즈마 CVD, 스퍼터링 방법, 증착 방법 등에 의해 침착될 수 있다. 또한, 배리어층을 형성하기 전에, 레이저빔 조사에 의해 형성된 산화막이 제거될 수 있다.

[0122] 배리어층 위에, 게터링 사이트(gettering site)로서 역할을 하는 아르곤 원소들을 함유하는 비정질 실리콘막이 스퍼터링에 의해 10 내지 400nm의 두께를 갖도록 형성되며, 이 실시예에서는 100nm의 두께를 갖도록 형성된다. 이 실시예에서, 아르곤을 함유하는 비정질 실리콘막은 실리콘 타겟을 사용하며 아르곤을 포함하는 분위기 하에서 형성된다. 플라즈마 CVD에 의해 아르곤 원소들을 함유하는 비정질 실리콘막을 형성하는 경우에, 다음과 같은 조건하에서 형성된다; 즉, 아르곤에 대한 모노시레인(monosilane)의 유속은 1/99로 되며; 침착 동안의 압력은 6.665Pa(0.05Torr)이며; 침착 동안의 RF 파워 밀도는 0.087W/cm<sup>2</sup>이며; 침착 온도는 350°C이도록 제어된다.

[0123] 그 다음, 650°C에서 가열된 오븐은 게터링하기 위해 3분 동안 열처리하는데 사용되며, 결정 구조를 갖는 반도체막에서 니켈 농도를 저하시킨다. 램프 어닐링 장치는 오븐 대신에 사용될 수 있다.

[0124] 이어서, 게터링 사이트로서 역할을 하는 아르곤 원소들을 함유하는 비정질 실리콘막은 에칭 스텁퍼(etching stopper)로서 배리어층을 사용하여 선택적으로 제거되며, 그 다음 그 배리어층은 묽은 불소 수소산에 의해 선택적으로 제거된다. 니켈은 게터링 동안 높은 산소 농도를 갖는 영역쪽으로 이동하는 경향이 있으며, 따라서, 산화막으로 형성된 배리어층이 게터링후에 제거되는 것이 바람직함을 유념하라.

[0125] 그 다음, 얇은 산화막이 결정 구조를 갖는 획득된 실리콘막(또한 폴리실리콘막으로 불림)의 표면상에 오존 물을 사용하여 형성된 후, 레지스트로 형성된 마스크가 형성되고, 그 다음 섬 형상들로 분리된 섬형 반도체층들(505 및 506)이 원하는 형상들을 갖도록 에칭함으로써 형성된다. 반도체층들(505 및 506)을 형성한 후, 레지스트로 형성된 마스크가 제거된다.

[0126] 상기 공정들을 통해, 질화물층(501), 금속층(502), 산화물층(503) 및 베이스 절연막(504)이 기판(500) 상에 형성되며, 결정 구조를 갖는 반도체막이 형성되고, 그 다음 섬 형상들로 분리된 반도체층들(505 및 506)은 원하는 형상들을 갖도록 에칭함으로써 형성된다.

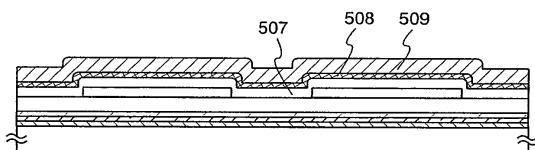

[0127] 그 다음, 산화막이 불소 수소산을 함유하는 에천트(etchant)로 제거되고, 동시에, 실리콘막의 표면이 세척된다. 그 후, 게이트 절연막(507)으로서 역할을 하는, 그 주성분으로서 실리콘을 함유하는 절연막이 형성된다. 이 실

시예에서, 실리콘 산화질화막(조성비율 : Si=32%, O=59%, N=7%, H=2%)이 플라즈마 CVD에 의해 115nm의 두께를 갖도록 형성된다(도 5b).

[0128] 그 다음, 20 내지 100nm의 두께를 갖는 제 1 도전막(508)과 100 내지 400nm의 두께를 갖는 제 2 도전막(509)이 게이트 절연막(507) 위에 쌓이게 된다. 이 실시예에서, 50nm의 두께를 갖는 탄탈 질화물막과 370nm의 두께를 갖는 텉스텐막이 이어서 게이트 절연막(507) 위에 쌓이게 된다.

[0129] 제 1 도전막(508) 및 제 2 도전막(509)을 형성하기 위한 도전 재료로서는, 그 주성분으로서 Ta, W, Ti, Mo, Al, 및 Cu, 또는 상기 원소들을 함유하는 합금 재료 또는 화합물 재료로 이루어진 그룹으로부터 선택된 원소가 사용된다. 또한, 제 1 도전막(508) 및 제 2 도전막(509)으로서는, AgPdCu 합금 또는 인과 같은 불순물 원소가 첨가된 다결정 실리콘막으로 대표되는 반도체막이 사용될 수 있다. 또한, 본 발명은 2층 구조에 한정되지 않는다. 예를 들어, 두께가 50nm인 텉스텐막, 두께가 500nm인 알루미늄과 실리콘(Al-Si)의 합금막, 두께가 30nm인 티타늄 질화물막이 이어서 쌓이게 되는 3층 구조도 채택될 수 있다. 게다가, 3층 구조의 경우에, 텉스텐 질화물이 제 1 도전막의 텉스텐 대신에 사용될 수 있으며, 알루미늄과 티타늄(Al-Ti)의 합금막이 제 2 도전막의 알루미늄과 실리콘(Al-Si)의 합금막 대신에 사용될 수 있고, 티타늄막이 제 3 도전막의 티타늄 질화물막 대신에 사용될 수 있다. 게다가, 단일층 구조도 또한 채택될 수 있다.

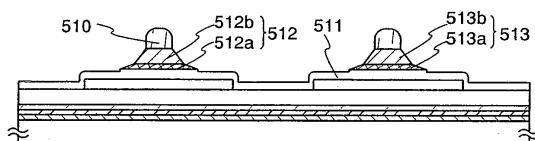

[0130] 다음에, 레지스트 마스크들(510)이 도 5c에 도시된 바와 같이 광 노출 공정으로 형성된다. 그 다음, 제 1 에칭 처리가 게이트 전극들과 배선들을 형성하기 위해 행해진다. 제 1 에칭 처리가 제 1 및 제 2 에칭 조건들하에서 행해진다. ICP(inductively coupled plasma; 유도 결합형 플라즈마) 에칭이 사용되는 것이 바람직하다. 막들은 ICP 에칭을 사용함으로써 그리고 에칭 조건들(코일형 전극에 인가된 파워의 양, 기판 측면상의 전극에 인가된 파워의 양, 기판 측면 상의 전극의 온도, 등)을 적절하게 조절함으로써 원하는 테이퍼(taper) 형상들을 갖도록 에칭될 수 있다. 기체 에칭으로서는, Cl<sub>2</sub>, BC<sub>l</sub><sub>3</sub>, SiCl<sub>4</sub> 또는 CCl<sub>4</sub>로 대표되는 염소 기반 기체, CF<sub>4</sub>, SF<sub>6</sub>, 또는 NF<sub>3</sub>, 또는 O<sub>2</sub>로 대표되는 불소 기반 기체가 적절하게 사용될 수 있다.

[0131] 이 실시예에서, 150W의 RF(13.56MHz) 파워가 또한 실질적으로 음의 자기 바이어스 전압을 인가하기 위해 기판(샘플 스테이지)에 인가된다. 기판 측면의 전극 영역은 12.5cm×12.5cm이며, 코일 형상 전극 영역(여기에는 코일이 형성된 석영 디스크가 기술된다)은 직경이 25cm인 디스크이다. W막은 제 1 에칭 조건들 하에서 테이퍼 형상으로 제 1 도전층의 에지부들을 형성하기 위해서 에칭된다. W에 대한 에칭 속도는 200.39nm/min이며, TaN에 대한 에칭 속도는 80.32nm/min이며, TaN에 대한 W의 선택비율은 제 1 에칭 조건들 하에서 대략 2.5이다. 또한, W의 테이퍼 각은 제 1 에칭 조건들 하에서 대략 26° 가 된다. 그 후, 제 1 에칭 조건들은 레지스트로 형성된 마스크들(510)을 제거하지 않고 제 2 에칭 조건들으로 변화된다. CF<sub>4</sub> 및 Cl<sub>2</sub>은 에칭 기체들로서 사용되며, 기체의 유량은 30/30sccm으로 설정되며, 플라즈마를 발생시키기 위해 1Pa의 압력으로 코일 형상 전극에 500W의 RF(13.56MHz) 파워가 인가되고, 그것에 의해 약 30초 동안 에칭이 행해진다. 20W의 RF(13.56MHz) 파워가 또한 실질적으로 음의 자기-바이어스 전압을 인가하기 위해 기판 측면(샘플 스테이지)에 인가된다. W막 및 TaN막 둘다 CF<sub>4</sub> 및 Cl<sub>2</sub>가 혼합되는 제 2 에칭 조건들 하에서 동일한 레벨로 에칭된다. 제 2 에칭 조건들 하에서 W에 대한 에칭 속도는 58.97nm/min이며, TaN에 대한 에칭 속도는 66.43nm/min이다. 게이트 절연막 위에 잔여물을 남기지 않고 에칭하기 위해 대략 10 내지 20% 에칭 시간이 증가될 수 있음에 유념하라.

[0132] 상술된 바와 같은 제 1 에칭 처리에서, 레지스트로 형성된 마스크의 형상은 적절한 형상으로 형성되며, 그것에 의해 제 1 도전층의 에지부와 제 2 도전층의 에지부 각각이 기판 측면에 인가된 바이어스 전압의 효과로 인해 테이퍼된 형상을 갖도록 형성된다. 테이퍼된 부분의 각은 15° 내지 45° 의 범위로 설정될 수 있다.

[0133] 따라서, 제 1 도전층 및 제 2 도전층으로 구성된 제 1 형상의 도전층들(512 및 513)(제 1 도전층들(512a 및 513a) 및 제 2 도전층들(512b 및 513b))이 제 1 에칭 처리에 의해 형성된다. 이에 따라, 게이트 절연막으로서 역할을 하는 절연막(507)의 대략 10 내지 20nm가 에칭되며, 제 1 형상의 도전층들(512 및 513)로 덮인 영역이 박막으로 에칭되는 것을 제외하고는 게이트 절연막(507)으로 형성된다.

[0134] 다음에, 제 2 에칭 처리가 다음의 조건들 하에서 마스크들을 제거하지 않고 25초 동안 행해진다; 즉, SF<sub>6</sub>, Cl<sub>2</sub> 및 O<sub>2</sub>가 에칭 기체로서 사용되며, 기체의 유량은 24/12/24sccm으로 설정되며, 플라즈마를 발생시키기 위해

1.3Pa의 압력으로 코일 형상 전극에 700W인 RF(13.56MHz) 파워가 인가된다. 10W인 RF(13.56MHz) 파워는 또한 실질적으로 음의 자기 바이어스 전압을 인가하기 위해 기판 측면(샘플 스테이지)에 인가된다. 제 2 에칭 처리에서, W에 대한 에칭 속도는 227.3nm/min이며, TaN에 대한 에칭 속도는 32.1nm/min이며, TaN에 대한 W의 선택비율은 7.1이고, 절연막(507)으로서 역할을 하는 SiON에 대한 에칭 속도는 33.7nm/min이고, SiON에 대한 W의 선택비율은 6.83이다. SF<sub>6</sub>가 에칭 기체로서 사용되는 경우에, 절연막(507)에 대한 선택비율은 상기된 바와 같이 높다. 따라서, 막 두께에 있어서의 감소가 억제될 수 있다. 이 실시예에서, 절연막(507)의 막 두께는 대략 8nm만큼만 감소된다.

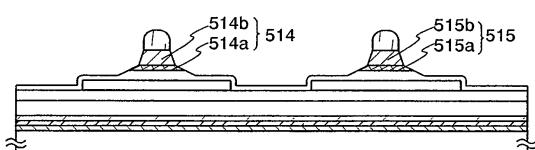

[0135] 제 2 에칭 처리를 통해, W의 테이퍼 각은 70° 가 되게 형성될 수 있다. 제 2 에칭 처리를 통해, 제 2 도전층들(514b 및 515b)이 형성된다. 반대로, 제 1 도전층들은 거의 에칭되지 않고, 제 1 도전층들(514a, 515a)로 형성된다. 제 1 도전층들(514a, 515a)은 제 1 도전층들(512a, 513a)의 크기와 실질적으로 동일한 크기를 가짐에 유념하라. 실제로, 제 1 도전층의 폭은 제 2 에칭 처리가 적용되기 전의 제 1 도전층과 비교하면, 대략 0.3μm 정도, 즉, 전체적으로 대략 0.6μm 정도 감소될 수 있다. 제 1 도전층의 크기에 있어서는 거의 변화가 없다.

[0136] 또한, 2층 구조 대신에, 두께가 50nm인 텅스텐막, 두께가 500nm인 알루미늄과 실리콘(Al-Si)의 합금막, 두께가 30nm인 티타늄 질화물막이 이어서 쌓이게 되는, 3층 구조가 채택는 경우에는, 제 1 에칭 처리가 다음의 조건들 하에서 117초 동안 행해질 수 있다; 즉, BC<sub>l</sub><sub>3</sub>, Cl<sub>2</sub> 및 O<sub>2</sub>가 원료 기체들(raw material gases)로서 사용되며; 기체들의 유량은 65/10/5(sccm)으로 설정되고; 300W의 RF(13.56MHz) 파워가 기판 측면(샘플 스테이지)에 인가되고; 플라즈마를 발생시키기 위해 1.2Pa의 압력으로 코일 형상 전극에 450W의 RF(13.56MHz) 파워가 인가된다. 제 1 에칭 처리에 있어서 제 2 에칭 조건들에 대해서는 다음과 같다; 즉, CF<sub>4</sub>, Cl<sub>2</sub> 및 O<sub>2</sub>가 사용되며; 기체들의 유량은 25/25/10sccm으로 설정되고; 20W의 RF(13.56MHz) 파워가 또한 기판 측면(샘플 스테이지)에 인가되고; 플라즈마를 발생시키기 위해 1Pa의 압력으로 코일 형상 전극에 500W의 RF(13.56MHz) 파워가 인가된다. 제 1 에칭 처리는 제 2 에칭 조건들 하에서 대략 30초 동안 행해질 수 있다. 제 2 에칭 처리는 다음과 같은 조건들 하에서 행해질 수 있다; 즉, BC<sub>l</sub><sub>3</sub> 및 Cl<sub>2</sub>가 사용되며; 기체들의 유량은 20/60sccm으로 설정되고; 100W의 RF(13.56MHz) 파워가 기판 측면(샘플 스테이지)에 인가되고; 플라즈마를 발생시키기 위해 1.2Pa의 압력으로 코일 형상 전극에 600W의 RF(13.56MHz) 파워가 인가된다.

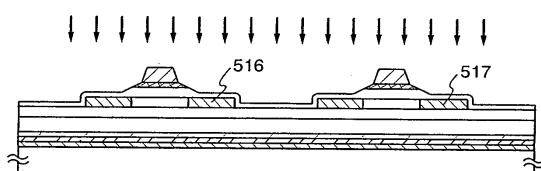

[0137] 다음에, 레지스트로 형성된 마스크들이 제거되며, 제 1 도핑 공정이 도 6a의 상태를 얻기 위해 행해진다. 도핑 공정은 이온 도핑 또는 이온 주입에 의해 행해질 수 있다. 이온 도핑은 다음과 같은 조건들 하에서 행해진다; 도우즈(dosage)는  $1.5 \times 10^{14}$  atoms/cm<sup>2</sup>이고, 가속 전압은 60 내지 100keV이다. n형 도전성을 제공하는 불순물 원소로서는, 인(P) 또는 비소(As)가 통상적으로 사용된다. 이러한 경우에, 제 1 도전층들과 제 2 도전층들(514, 515)은 n형 도전성을 제공하는 불순물 원소들에 대하여 마스크들로서 역할을 하며, 제 1 불순물 영역들(516, 517)은 자기 정렬 방식으로 형성된다. n형 도전성을 제공하는 불순물 원소는  $1 \times 10^{16}$  내지  $1 \times 10^{17}/cm^2$ 의 농도 범위에서 제 1 불순물 영역들(516, 517)에 첨가된다. 여기서, 제 1 불순물 영역과 동일한 농도 범위를 갖는 영역은 또한 n-- 영역으로 불린다.

[0138] 제 1 도핑 공정이 이 실시예에서 레지스트로 형성된 마스크들을 제거한 후에 행해지지만, 제 1 도핑 공정이 레지스트로 형성된 마스크들을 제거하지 않고도 행해질 수 있음에 유념하라.

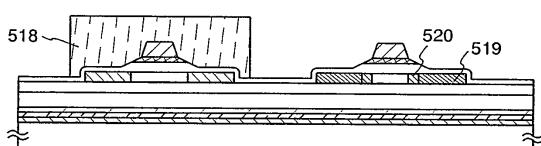

[0139] 이어서, 도 6b에 도시된 바와 같이, 레지스트로 형성된 마스크(518)가 형성되고 제 2 도핑 공정이 행해진다. 마스크(518)는 p-채널 TFT를 형성하는 반도체층의 채널 형성 영역과 그 주변을 보호한다.

[0140] 인(P)으로 이루어진 제 2 도핑 공정이 다음의 조건들 하에서 행해진다; 즉, 도우즈는  $1.5 \times 10^{15}$  atoms/cm<sup>2</sup>이고, 가속 전압은 60 내지 100keV이다. 여기서, 불순물 영역들이 각 반도체층들 내에 마스크들로서의 제 2 도전층들(514b, 515b)로 자기 정렬 방식으로 형성된다. 물론, 인은 마스크(518)로 덮인 영역들에 첨가되지 않는다. 따라서, 제 2 불순물 영역(519) 및 제 3 불순물 영역(520)이 형성된다. n형 도전성을 제공하는 불순물 원소들은  $1 \times 10^{20}$  내지  $1 \times 10^{21}/cm^2$ 의 농도 범위에서 제 2 불순물 영역들(519)에 첨가된다. 여기서, 제 2 불순물 영역과 동일한 농도 범위를 갖는 영역은 또한 n+ 영역으로 불린다.

[0141] 또한, 제 3 불순물 영역(520)은 제 1 도전층(515a)의 영향에 의해 제 2 불순물 영역(519)에서의 농도보다 더 낮은 농도를 갖도록 형성되며,  $1 \times 10^{18}$  내지  $1 \times 10^{19}/cm^2$ 의 농도 범위에서 n형 도전성을 제공하는 불순물 원소들이 첨가된다. 제 3 불순물 영역(520)이 테이퍼된 부분의 예지부로 갈수록 불순물 농도가 높아지는 농도 기울기를

생성하도록 제 3 불순물 영역(520)이 제 1 도전층의 테이퍼된 부분을 통해 도핑됨에 유념하라. 여기서, 제 3 불순물 영역의 농도 범위와 동일한 농도 범위를 갖는 영역은 n- 영역으로 불린다.

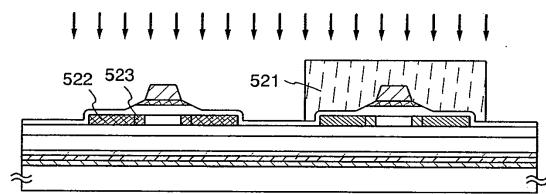

[0142] 다음에, 레지스트로 형성된 마스크(518)가 제거된 후, 레지스트로 형성된 마스크(521)가 새로 형성되고, 제 3 도핑 공정이 도 6c에 도시된 바와 같이 행해진다.

[0143] 상기된 제 3 도핑 공정이 행해지며, p형 도전성을 제공하는 불순물 원소들이 첨가되는 제 4 불순물 영역(522)과 제 5 불순물 영역(523)이 반도체층에 형성된다.

[0144] 또한, p형 도전성을 제공하는 불순물 원소는  $1 \times 10^{20}$  내지  $1 \times 10^{21}/\text{cm}^2$ 의 농도 범위에서 제 4 불순물 영역(522)에 첨가된다. 제 4 불순물 영역(522)에서, 선행 단계(n- 영역)에서 인(P)이 첨가되지만, p형 도전성을 제공하는 불순물 원소는 인의 농도의 1.5 내지 3배로 첨가됨에 유념하라. 따라서, 제 4 불순물 영역(522)은 p형 도전성을 갖는다. 여기서, 제 4 불순물 영역(522)과 동일한 농도 범위를 갖는 영역은 또한 p+ 영역으로 불린다.

[0145] 또한, 제 5 불순물 영역(523)은 제 1 도전층(515a)의 테이퍼된 부분을 오버랩하는 영역들에 형성되며,  $1 \times 10^{18}$  내지  $1 \times 10^{20}/\text{cm}^2$ 의 농도 범위에서 p형 도전성을 제공하는 불순물 원소가 첨가된다. 여기서, 제 5 불순물 영역(523)과 동일한 농도 범위를 갖는 영역은 또한 p- 영역으로 불린다.

[0146] 상기 단계들을 통해, n형 또는 p형 도전성을 갖는 불순물 영역들이 각 반도체층들에 형성된다. 도전층들(514, 515)은 TFT의 게이트 전극들이 된다.

[0147] 다음에, 실질적으로 전체 표면을 덮는 절연막(524)이 형성된다. 이 실시예에서, 실리콘 산화막이 플라즈마 CVD에 의해 50nm의 두께를 갖도록 형성된다. 물론, 절연막은 실리콘 산화막에 한정되지 않으며, 실리콘을 함유하는 다른 절연막들은 단일층 또는 적층 구조에 사용될 수 있다.

[0148] 그 다음, 각 반도체층들에 첨가된 불순물 원소에 대한 활성화 처리 공정이 행해진다. 이 활성화 공정에서, 램프 광원을 사용하는 RTA(rapid thermal annealing)법, 뒷면에서부터의 YAG 레이저 또는 액시머 레이저에서 방출된 광을 조사하는 방법, 용광로(furnace)를 사용하는 열 처리, 또는 그들의 조합이 사용된다.

[0149] 또한, 절연막이 활성화전에 형성되는 예가 이 실시예에 기술되어있지만, 절연막은 활성화가 행해진 후 형성될 수 있다.

[0150] 다음에, 실리콘 절화물막으로 형성된 제 1 층간 절연막(525)이 형성되고, 1 내지 12시간 동안 300 내지 550°C의 온도에서 열 처리되고, 그 다음, 반도체층들의 수소화(hydrogenation) 공정이 행해진다(도 6d). 수소화는 제 1 층간 절연막(525)에 함유된 수소에 의해 반도체층들의 댕글링 본드들(dangling bonds)을 종료시키기 위해 행해진다. 반도체층들은 실리콘 산화막으로 형성된 절연막(524)의 존재에 상관없이 수소화될 수 있다. 부수적으로, 이 실시예에서, 그 주성분으로 알루미늄을 함유하는 재료는 제 2 도전층에 사용되며, 따라서, 제 2 도전층이 견딜 수 있는 열 처리의 조건들 하에서 수소화가 행해지는 것이 중요하다. 수소화를 위한 다른 수단으로서, 플라즈마 수소화(플라즈마에 의해 여기된 수소를 사용하는)가 채택될 수 있다.

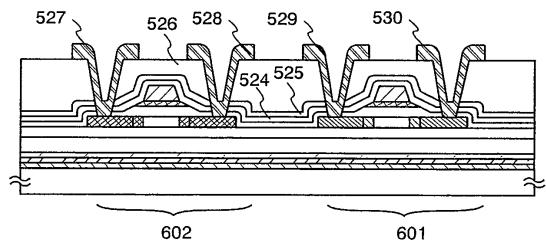

[0151] 다음에, 유기 절연 재료로 형성된 제 2 층간 절연막(526)이 제 1 층간 절연막(525) 상에 형성된다. 이 실시예에서,  $1.6\mu\text{m}$ 의 두께를 갖는 아크릴 수지막이 형성된다. 그 다음, 각 불순물 영역들에 도달하는 콘택트 홀들이 형성된다. 이 실시예에서, 다수의 에칭 처리들이 이어서 행해진다. 이 실시예에서, 제 1 층간 절연막(525)을 에칭 스텝퍼로 하여 제 2 층간 절연막(526)이 에칭되고, 절연막(524)을 에칭 스텝퍼로 하여 제 1 층간 절연막(525)이 에칭되고, 그 다음 절연막(524)이 에칭된다.

[0152] 그 후, 배선들(524, 528, 529 및 530)이 Al, Ti, Mo, W 등을 사용하여 형성된다.

[0153] 이에 따라, n-채널 TFT(601) 및 p-채널 TFT(602)가 한 기판 위에 형성된다(도 6).

[0154] 또한, CMOS 회로는 n-채널 TFT(601) 및 p-채널 TFT(602)를 접속함으로써 상보적 구조를 갖도록 형성될 수 있다.

[0155] 게이트 전극과 불순물 영역의 일부가 서로 오버랩되는 구조(GOLD 구조)를 갖는 실시예에 도시된 TFT를 사용하는 경우에, 얇은 게이트 절연막으로 인해 기생 용량이 증가되지만, 게이트 전극(제 1 도전층)의 테이퍼 부분의 일부 크기를 감소시킴으로써 기생 용량이 감소되면, 주파수 특성들이 향상되고, 고속 동작 및 충분한 신뢰할 수 있는 TFT가 실현될 수 있다.

- [0156] 상기된 바와 같이, 본 발명의 이 실시예 모드에 기술된 공정은, 이 TFT들을 포함하는 디바이스 형성층이 불소 수지막으로 덮인 구조를 갖는 본 발명에 따른 반도체 디바이스가 제조될 수 있도록 n-채널 TFT(601) 및 p-채널 TFT(602)가 기판(500) 위에 형성된 후 행해진다.

- [0157] 이 실시예에 따라 형성된 TFT를 포함하는 디바이스 형성층은  $50\mu\text{m}$  이하의 두께를 갖는다.

- [0158] [실시예 2]

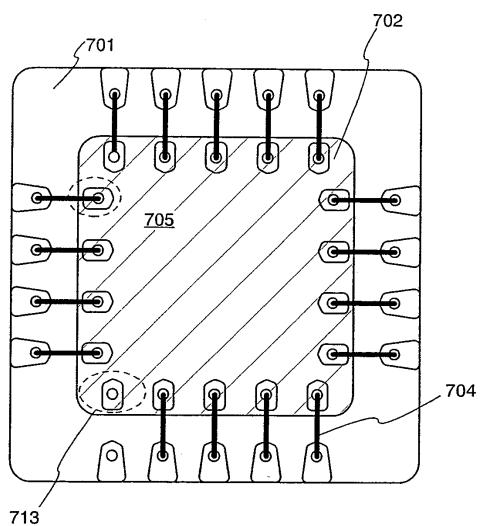

- [0159] CPU가 본 발명에 따른 반도체 디바이스로서 제조되는 경우가 이 실시예에서 도 7을 참조하여 기술될 것이다.

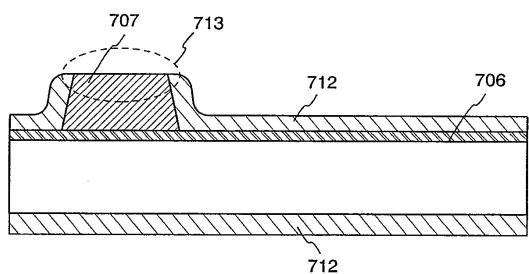

- [0160] 도 7에 도시된 바와 같이, 다수의 TFT들의 조합으로 형성된 CPU(705)는 불소 수지막(701) 위에 제조된다. 또한, 불소 수지막(702)은 CPU(705) 위에 형성된다. CPU(705)가 이 불소 수지막들(701, 702)로 완전히 덮이는 구조가 설명된다. 이러한 구조를 채택하면, CPU(705)는 외부로부터 완전히 차단되어 외부로부터의 수분, 산소 등의 침투가 방지될 수 있다.

- [0161] 그러나, CPU(705)가 본딩 배선(704) 등을 통해 외부와 접속할 필요가 있기 때문에 CPU(705)는 내부에 형성된 배선과 전기적으로 접속하기 위한 구조를 가질 필요가 있다.

- [0162] 이 실시예에서, 도 7b에 도시된 이러한 구조를 채택하면, CPU(705) 내부의 배선(706)은 외부 접속부(713) 내의 본딩 배선(704)과 접속된다. 이러한 경우에, 도전성을 갖는 금속 재료로 형성된 금속(707)은 불소 수지막(712)이 형성되기 전에 형성되며, 불소 수지막(712)은 본 발명의 실시예 모드에 기재된 제조 방법을 통해 형성된다.

- [0163] 외부 접속부(713)는 금속(707) 위에 형성된 불소 수지막(712)의 일부를 제거함으로써 형성될 수 있다.

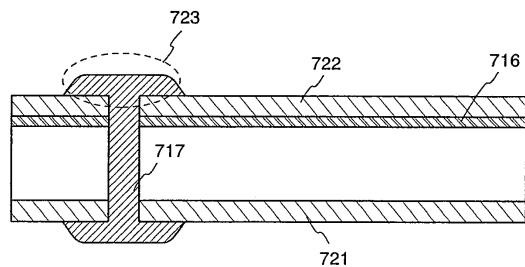

- [0164] 다른 구조로서, 도 7c에 도시된 구조가 채택될 수 있다. 이 경우에, 배선(716)과 전기적인 접속을 갖는 외부 접속부(723)가 불소 수지막들(721, 722)로 덮인 CPU(705)에 물리적 수단을 사용함으로써 개구부들을 형성하고 그 개구부들을 금속(717)으로 채우는 것에 의해 형성될 수 있다.

- [0165] 이 실시예에 기술된 외부 접속부의 구조는 단지 예로서 바람직하다. 본 발명에 따른 반도체 디바이스의 외부 접속부는 이에 한정되지 않는다. 그러므로 외부 접속부로서 역할을 하는 배선 위에만 불소 수지막이 형성되지 않는 공정을 선택하는 것도 가능하다.

- [0166] [실시예 3]

- [0167] 본 발명에 따른 반도체 디바이스는 얇고 경량이고 플렉서블 구조를 가지므로, 다수의 반도체 디바이스들이 한 기판 위에 서로 조합하여 사용될 수 있다. 여기서 사용된 바와 같이, 용어 "기판"은 유리 또는 석영 외에 플라스틱막과 같은 플렉서블 기판을 포함한다.

- [0168] 따라서, 반도체 디바이스가 CPU인 경우, 다수의 CPU들은 한 기판 위에 집적되어 조합될 수 있다.

- [0169] 게다가, 다수의 반도체 디바이스들이 한 기판 위에 집적될 때, 본 발명에 따른 반도체 디바이스의 불소 수지막으로 형성된 표면은 표면이 함몰부(depression)들 및 돌출부(projection)들을 갖도록 역스퍼터링될 수 있으며, 기판에 각 반도체 디바이스가 접착제로 접합될 수 있다.

- [0170] [실시예 4]

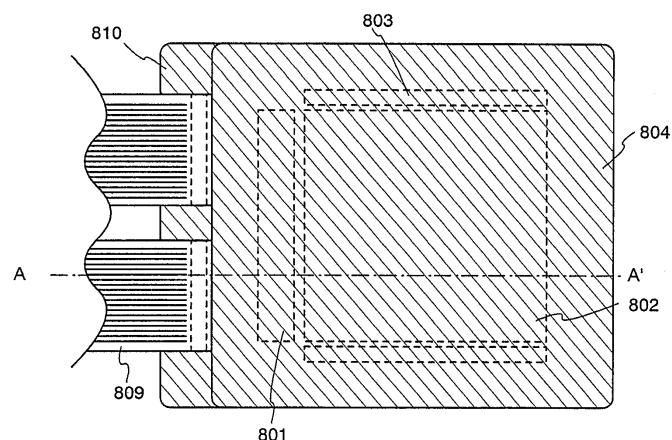

- [0171] 실시예 4에서, 활성 매트릭스형 발광 디바이스의 외형도가 도 8을 참조하여 기술될 것이다. 도 8a는 발광 디바이스의 상면도이며, 도 8b는 도 8a의 A-A'선을 따라 취해진 단면도이다. 점선으로 표시된 도면 부호 801은 드라이버 회로부(소스측 드라이버 회로)이며, 802는 픽셀부이고, 803은 드라이버 회로부(게이트측 드라이버 회로)이며, 804는 불소 수지막이다.

- [0172] 도면 부호 808은 소스측 드라이버 회로(801)와 게이트측 드라이버 회로(803)에 입력되는 신호들을 전송하기 위한 배선이다. 배선(808)은 외부 입력 단자로서 역할을 하는 FPC(flexible printed circuit)(809)에서 비디오 신호, 클록 신호, 스타트 신호, 리셋 신호 등을 수신한다. 여기에는 FPC만이 도시되어있지만, PWB(a print wiring board; 인쇄 배선 기판)이 FPC에 첨부될 수 있다. 명세서에서 발광 디바이스는 발광 디바이스 본체뿐만 아니라 FPC 또는 PWB에 첨부되어 있는 상태의 발광 디바이스를 포함한다.

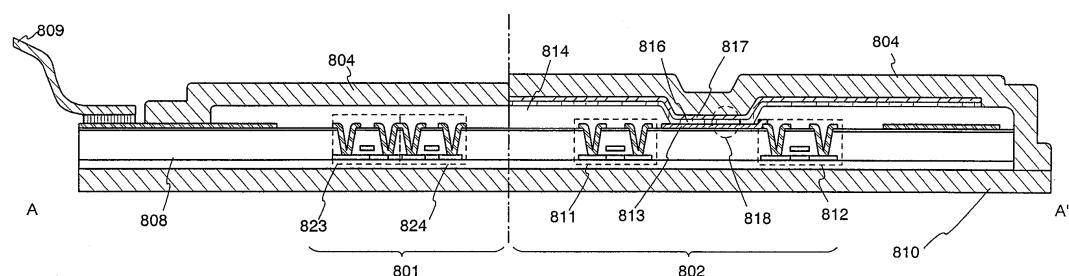

- [0173] 다음에, 발광 디바이스의 단면 구조가 도 8b를 참조하여 기술될 것이다. 여기서, 드라이버 회로부로서 역할을

하는 소스측 드라이버 회로(801)부와 픽셀부(802)는 불소 수지막(810) 위에 형성된다. 불소 수지막(810)이 스퍼터링에 의해 형성되며, 특히, 폴리테트라 플루오르에틸렌, 테트라플루오르에틸렌-헥사플루오르프로필렌 공중합체, 폴리클로르트리플루오르에틸렌, 테트라플루오르에틸렌-에틸렌 공중합체, 폴리비닐 플루오르화물, 폴리비닐리덴 플루오르화물 등과 같은 불소 수지막이 불소 수지막(810)을 형성하는데 사용될 수 있다.

[0174] 소스측 드라이버 회로(801)는 n-채널 TFT(823) 및 p-채널 TFT(824)를 조합함으로써 형성된 CMOS 회로이다. 드라이버 회로를 형성하기 위한 TFT는 공지된 CMOS 회로, PMOS 회로, 또는 NMOS 회로로 형성될 수 있다. 드라이버 회로가 불소 수지막 위에 형성된 드라이버 일체형이 이 실시예에 기술되지만, 이에 한정되지 않으며, 드라이버 회로는 외부에 형성될 수 있다.

[0175] 픽셀부(802)는 스위칭 TFT(811), 전류 제어 TFT(812), 및 전류 제어 TFT(812)의 드레인에 전기적으로 접속되는 제 1 전극(813)을 포함하는 다수의 픽셀들을 포함한다. 절연체(814)는 제 1 전극(813)의 에지부를 덮도록 형성된다. 여기서, 절연체(814)는 포지티브형 감광성 아크릴 수직막으로 형성된다.

[0176] 커버리지(coverage)를 향상시키기 위해, 절연체(814)의 상부 에지부 또는 하부 에지부는 곡률을 갖는 굴곡이 있는 표면을 갖도록 형성된다. 예를 들어, 포지티브형 감광성 아크릴이 절연체(814)용 재료로서 사용되는 경우에, 절연체(814)의 상부 에지부만이 곡률 반경(0.2 내지 3 $\mu\text{m}$ )을 갖는 굴곡이 있는 표면을 갖도록 형성된다. 감광성 재료가 노출된 광에 의해 에칠퐁에 녹지 않는 재료로 되는 네가티브형 또는 감광성 재료에 대한 광에 의해 에칠퐁에 분해될 수 있는 재료로 되는 포지티브형이 절연체(814)로서 사용될 수 있다.

[0177] 전계 발광층(816) 및 제 2 전극(817)이 제 1 전극(813) 위에 각각 형성된다. 여기서, 제 1 전극(813)을 형성하기 위한 재료로서, 큰 일함수 재료들을 사용하는 것이 바람직하다. 예를 들어, 티타늄 질화물막, 크롬막, 텉스텐막, Zn막, 또는 Pt막과 같은 단층; 티타늄 질화물막과 그 주성분으로서 알루미늄을 함유하는 막의 적층; 또는 티타늄 질화물막, 그 주성분으로서 알루미늄을 함유하는 막, 티타늄 질화물막의 3층의 적층이 제 1 전극(813)에 유용하다. 적층 구조를 갖도록 제 1 전극을 형성함으로써, 배선과 같은 저항이 낮아질 수 있으며, 양호한 옴 접촉 특성들이 획득될 수 있고, 제 1 전극이 애노드로서 역할을 할 수 있다.

[0178] 전계 발광층(816)은 증착 마스크 또는 잉크 제팅(ink-jetting)을 사용하여 기상 침착(vapor deposition)에 의해 형성될 수 있다.

[0179] 전계 발광층(816) 위에 형성된 제 2 전극(캐소드)(817)용 재료로서, 작은 일함수 재료(Al, Ag, Li, Ca 또는 이 재료들의 합금 예를 들어 MgAg, MgIn, AlLi, CaF<sub>2</sub> 또는 CaN)가 유용하다. 여기서, 제 2 전극(캐소드)(817)은 광이 제 2 전극을 통과하도록 하기 위해 얇은 금속막, 투명한 도전막(인듐-주석-산화물(ITO), 인듐 산화물-아연 산화물(In<sub>2</sub>O<sub>3</sub>-ZnO), 아연 산화물(ZnO) 등)의 적층으로 형성된다.

[0180] 제 2 전극(817)은 전체 픽셀들에 공통으로 배선으로서 역할을 하며, 접속 배선(808)을 통해 FPC(809)에 전기적으로 접속된다.

[0181] 불소 수지막(804)은 제 2 전극(817) 위에서 스퍼터링에 의해 형성된다. 불소 수지막(804)은 상기된 불소 수지막(810)의 재료와 동일한 재료를 사용하여 형성된다.

[0182] 무기 절연막은 불소 수지막(804)을 형성하기 전에 형성될 수 있다. 스퍼터링, CVD 또는 기상 침착에 의해 형성된 실리콘 질화물막, 실리콘 산화막, 실리콘 산화질화물막(SiNO막(조성비율 N>0) 또는 SiON막(조성비율 N<0) 또는 그 주성분으로서 탄소를 함유하는 박막(예를 들어, DLC막, CN막 등))이 무기 절연막에 유용할 수 있다.

[0183] 따라서, 본 발명에 따른 발광 디바이스는 불소 수지막들(804, 810)이 발광 디바이스의 표면을 덮는 구조를 갖는다. 특히, 발광 디바이스(818) 사이의 전계 발광층은 수분 또는 산소로 인해 품질저하되기 쉽다. 이 이유로, 수분 또는 산소 등과 같은 기체가 발광 디바이스로 침투되는 것을 방지할 수 있기 때문에 발광 디바이스(818)는 불소 수지막들(804, 810)로 덮이게 된다는 이점이 있다. 그 결과, 신뢰성이 높은 발광 디바이스가 얻어질 수 있다.

[0184] 이 실시예는 본 발명의 실시예 모드에 기술된 바와 같이 불소 수지막으로 디바이스 형성층을 덮는 방법 및 제 1 실시예에 기술된 바와 같이 TFT를 제조하는 방법을 자유롭게 조합함으로써 구현될 수 있다. 또한, 이 실시예는 FPC의 접속부에서 실시예 2에 기술된 접속 방법을 통해 구현될 수 있다.

[0185] [실시예 5]

- [0186] 본 발명에 따른 반도체 장치, 디스플레이 장치, 또는 발광 디바이스(이 실시예에서, 반도체 디바이스 등으로 불림)는 유리 기판, 석영 기판 등과 같은 기판 대신에 불소 수지막으로 그 표면이 덮인다. 구조는 반도체 디바이스가 유리 기판, 석영 기판 등 위에 형성되는 통상적인 구조와는 상이하다. 본 발명에 따른 구조는 외부로부터 수분, 산소등이 침투하지 못하게 하고 얇고 경량이고 플렉서블한 구조를 실현하는 이로운 효과를 가진다. 그러므로, 본 발명에 따른 반도체 디바이스 등을 이용함으로써 다양한 응용 제품이 완성될 수 있다.

- [0187] 본 발명에 따른 반도체 디바이스 등을 이용하여 제조된 응용 제품의 예로서는 선불 카드, 신용 카드, 자동차 운전 면허증, 착용할 수 있는 컴퓨터(고글형 디스플레이, 또는 헤드 장착 디스플레이), 게임기, 또는 기록 매체를 재생할 수 있고 휴대용 정보 단말기(모바일 컴퓨터, 셀룰러 폰, 휴대용 게임기, 전자북 등)와 같은 상술된 디바이스들의 이미지를 디스플레이할 수 있는 디스플레이 디바이스를 갖는 장치가 제공된다. 응용 제품들의 구체적인 예들은 도 9a 내지 도 9g에 도시된다.

- [0188] 도 9a는 선불 카드를 도시하며, 그 선불 카드는 본체(2001)에 본 발명에 따른 반도체 디바이스 등을 이용함으로써 제조될 수 있다. 특히, 반도체 디바이스는 카드의 사용을 관리할 수 있다. 게다가, 본 발명에 따른 반도체 디바이스 등을 얇고 경량이고 플렉서블하고 이동성(portability)을 제공하기 때문에 선불 카드에 적합하다.

- [0189] 도 9b는 자동차 운전 면허증을 도시하며, 그 자동차 운전 면허증은 본체(2201)에 본 발명에 따른 반도체 디바이스 등을 이용함으로써 제조될 수 있다. 특히, 반도체 디바이스는 소유자의 자동차 운전 기록을 관리할 수 있다. 게다가, 본 발명에 따른 반도체 디바이스 등을 얇고 경량이고 플렉서블하고 이동성을 제공하기 때문에 자동차 운전 면허증에 적합하다.

- [0190] 도 9c는 본체(2101), 디스플레이부(2102), 이미지 수신부(2103), 조작키(2104), 외부 접속 포트(2105), 셔터(2106) 등을 포함하는 디지털 스틸 카메라를 도시한다. 본 발명에 따른 반도체 디바이스는 디스플레이부(2102)에 사용될 수 있다.

- [0191] 도 9d는 본체(2301), 디스플레이부(2302), 스위치(2303), 조작키(2304), 적외선 포트(2305) 등을 포함하는 모바일 컴퓨터를 도시한다. 본 발명에 따른 반도체 디바이스는 디스플레이부(2302)에 사용될 수 있다.

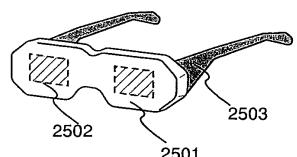

- [0192] 도 9e는 본체(2501), 디스플레이부(2502), 암부(arm portion)(2503)를 포함하는 고글형 디스플레이(헤드 장착 디스플레이)를 도시한다. 본 발명에 따른 반도체 디바이스는 디스플레이부(2502)에 사용될 수 있다.

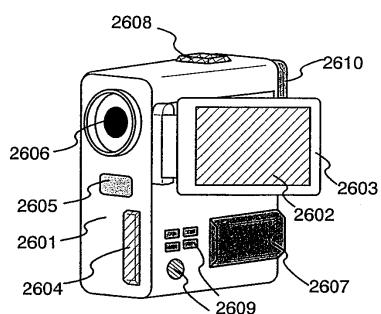

- [0193] 도 9f는 본체(2601), 디스플레이부(2602), 케이싱(2603), 외부 접속 포트(2604), 원격 제어 수신부(2605), 이미지 수신부(2606), 배터리(2607), 사운드 입력부(2608), 조작키(2609), 접안 렌즈부(2610) 등을 포함하는 비디오 카메라를 도시한다. 본 발명에 따른 반도체 디바이스는 디스플레이부(2602)에 사용될 수 있다.

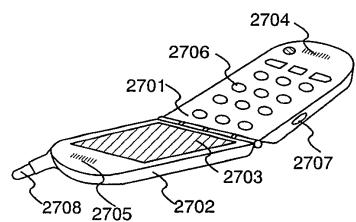

- [0194] 도 9g는 본체(2701), 케이싱(2702), 디스플레이부(2703), 사운드 입력부(2704), 사운드 출력부(2705), 조작키(2706), 외부 접속 포트(2707), 안테나(2708) 등을 포함하는 셀룰러 폰을 도시한다. 본 발명에 따른 반도체 디바이스는 디스플레이부(2703)에 사용될 수 있다.

- [0195] 상기에 설명된 바와 같이, 본 발명에 따라 제조된 반도체 디바이스는 매우 얕은 적용 범위를 가지므로, 본 발명에 따른 반도체 디바이스는 다양한 분야의 응용 제품에 이용될 수 있다.

- [0196] [실시예 6]

- [0197] 실시예 6에서는, 본 발명에 사용된 불소 수지막의 특성들에 대해 측정된 결과들이 기술될 것이다. 측정에 사용된 막은 다음의 조건들 하에서 스퍼터링에 의해 폴리테트라플루오르에틸렌의 타겟을 사용함으로써 100nm의 두께를 갖도록 형성된 불소 수지막이다; 그 조건들은, 즉 공정 기체로 사용된 Ar 기체가 30sccm이며, 사용된 스퍼터링 압력이 0.4Pa이며, 전력은 400W이고, 기판 온도는 300°C이다.

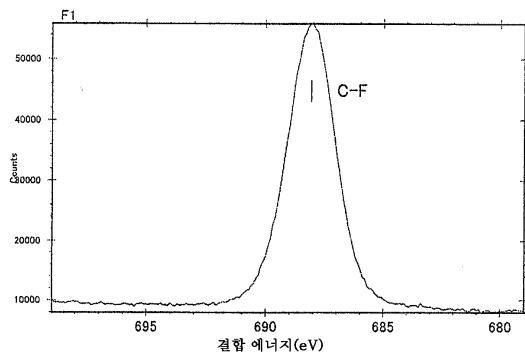

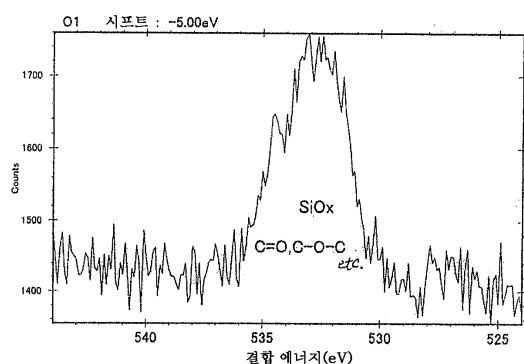

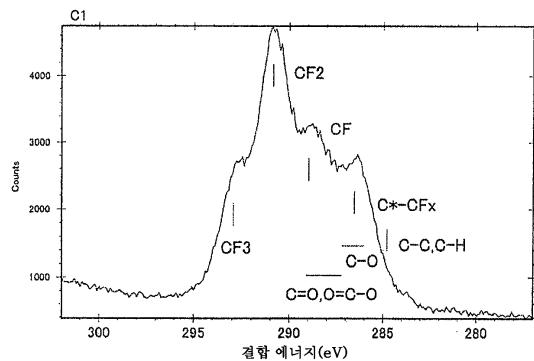

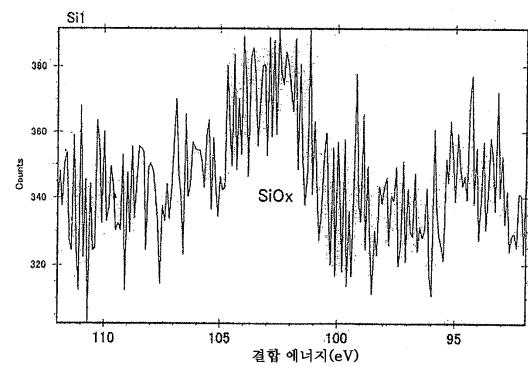

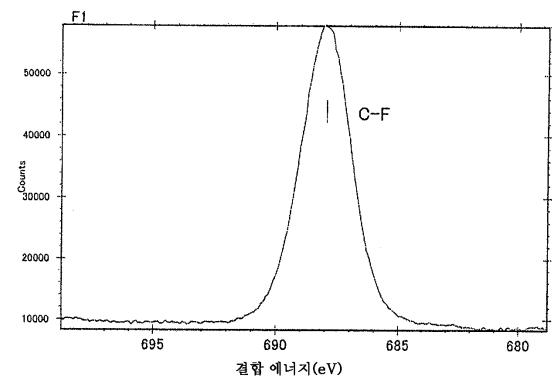

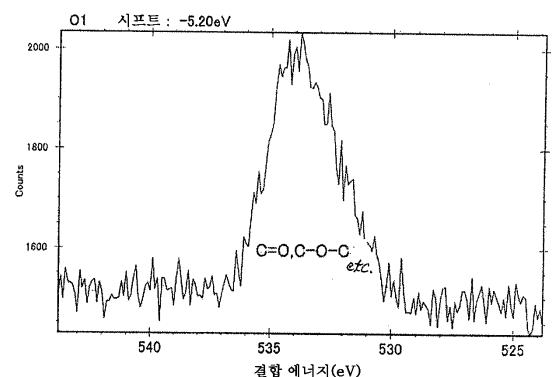

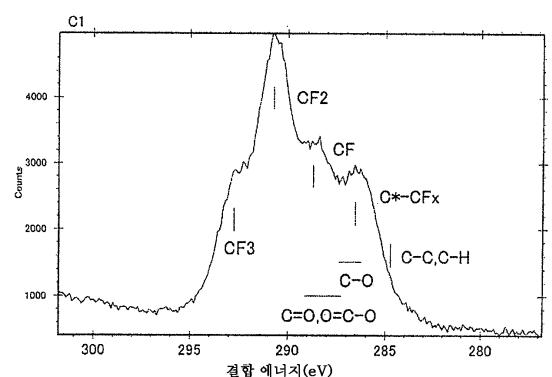

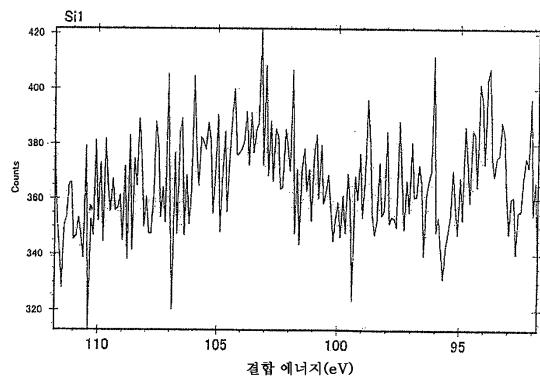

- [0198] 도 10a 내지 10d는 ESCA(photoelectron spectroscopy for chemical analysis)의 스펙트럼들을 도시하는 도면이다. 샘플에서 불소(F), 산소(O), 탄소(C) 및 실리콘의 화학적 조성비율은 61:1:38이다. 실리콘(Si)은 검출되지 않는다.

- [0199] 상이한 침착 조건에서 동일한 측정 방법에 의해 형성된 막의 측정 결과가 도 11a 내지 도 11d에 도시된다. 이 경우에, 30sccm Ar 기체 및 5sccm O<sub>2</sub> 기체가 주입된다. 조성비율은 도 10a 내지 도 10d에 도시된 조건과 동일하다.

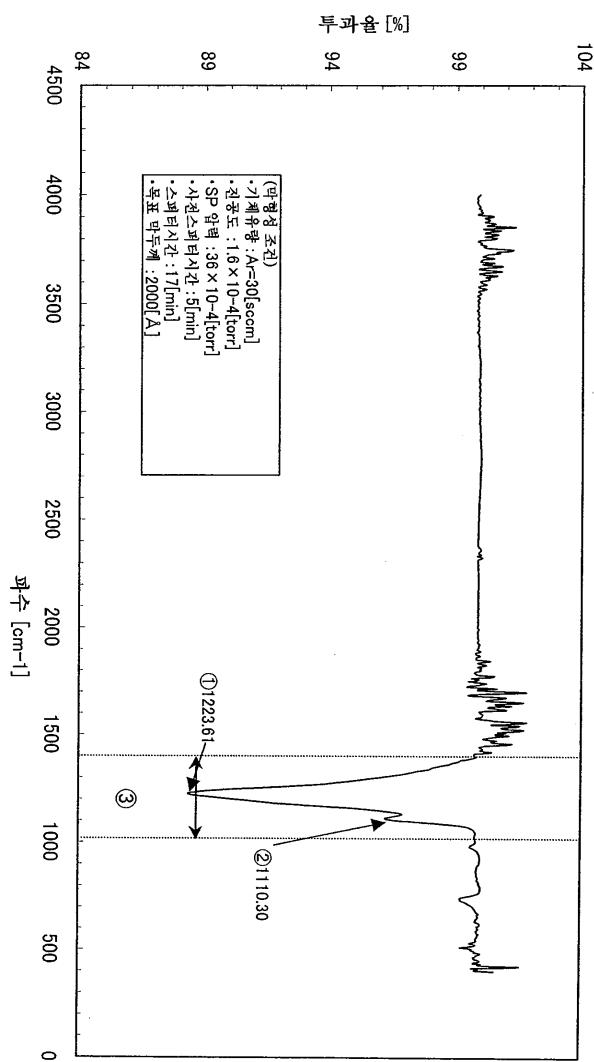

- [0200] 도 12는 퓨리에 변환 적외 분광법(FT-IR)에 의한 정성(qualitative) 분석 결과들을 도시하는 그래프이다. 도

12에서 도면 부호 ①, ②, 및 ③은 CF(1100 내지 1000  $\text{cm}^{-1}$ ),  $\text{CF}_2$ (1250 내지 1070  $\text{cm}^{-1}$ ),  $\text{CF}_3$ (1360 내지 1150  $\text{cm}^{-1}$ )에서 도출된 피크들(peaks)을 표시한다고 고려된다. 도면 부호 ②로 표시된 피크가 특징적이므로, 불소 수지를 함유하는 막에서  $\text{CF}_2$ 가 높은 속도로 포함된다고 생각될 수 있다.

#### [실시예 7]

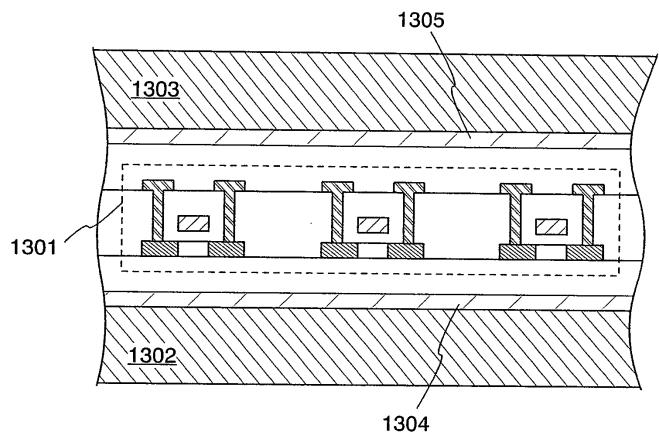

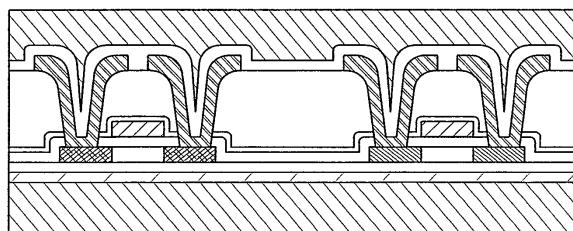

본 명세서에서, 디바이스 형성층(1301)과 각 불소 수지막들(1302, 1303) 사이에 열 전도층들(1304, 1305)이 제공될 수 있다. 열 전도층들은 디바이스 형성층(1301)에서 발생된 열을 방사한다.

도 13에 도시된 바와 같이, 열 전도층들(1304, 1305)은 다수의 TFT들로 구성된 반도체 디바이스, 디스플레이 디바이스, 발광 디바이스를 포함하는 디바이스 형성층(1301)에 접촉하여 형성된다.

열 전도층(1304)은 열 전도성, 특히, 알루미늄 질화물( $\text{AlN}$ ), 알루미늄 질화산화물( $\text{AlN}_{x}\text{O}_{y}(x>y)$ ), 봉소 인화물( $\text{BP}$ ), 봉소 질화물( $\text{BN}$ ) 또는 다이아몬드형 탄소( $\text{DLC}$ )를 갖는 막으로 형성된다. 또는 열 전도층(1304)은 이 막들의 적층으로 형성될 수 있다.

열 전도층(1304)을 형성하는 방법으로는 스퍼터링, 기상 침착, CVD 등이 사용될 수 있다.

예를 들어,  $\text{AlN}$ (알루미늄 질화물)로 열 전도층(1304)을 형성하는 경우에, 층은 아르곤 기체 및 질소 기체의 혼합 기체로 구성된 분위기 하에서  $\text{AlN}$  타겟을 사용하여 침착된다. 게다가, 층은 질소 기체 분위기 하에서 알루미늄( $\text{Al}$ ) 타겟을 사용하여 침착될 수 있다.

열 전도층들(1304, 1305)의 형성에 대하여, 열 전도층(1304)은 불소 수지막(1302)을 형성하기 직전에 형성되며, 열 전도층(1305)은 불소 수지막(1303)을 형성하기 직전에 형성된다.

열 전도층들(1304, 1305)에 디바이스 형성층(1301)을 개재하도록 형성되는 경우가 기술되어있지만, 열 전도층은 디바이스 형성층의 어느 한 측면에 형성될 수 있다.

#### 부호의 설명

101 : 디바이스 형성층

102, 103 : 불소 수지막

#### 도면

##### 도면1

도면2a

도면2b

도면2c

도면3a

도면3b

도면3c

도면4a

도면4b

도면4c

도면5a

도면5b

도면5c

도면5d

도면6a

도면6b

도면6c

도면6d

도면7a

도면7b

도면7c

도면8a

도면8b

도면9a

도면9b

도면9c

도면9d

도면9e

도면9f

도면9g

도면10a

도면10b

도면10c

도면10d

도면11a

도면11b

도면11c

도면11d

도면12

도면13