(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5173503号

(P5173503)

(45) 発行日 平成25年4月3日(2013.4.3)

(24) 登録日 平成25年1月11日(2013.1.11)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 27/146 | (2006.01) |

| HO 4 N 5/357  | (2011.01) |

| HO 4 N 5/374  | (2011.01) |

| HO 4 N 5/378  | (2011.01) |

| HO 1 L        | 27/14     |

| HO 4 N        | 5/335 570 |

| HO 4 N        | 5/335 740 |

| HO 4 N        | 5/335 780 |

請求項の数 16 (全 21 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2008-66736 (P2008-66736)    |

| (22) 出願日  | 平成20年3月14日 (2008.3.14)        |

| (65) 公開番号 | 特開2009-224524 (P2009-224524A) |

| (43) 公開日  | 平成21年10月1日 (2009.10.1)        |

| 審査請求日     | 平成23年3月14日 (2011.3.14)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】撮像装置及び撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素が行方向及び列方向に配列され、複数の列信号線へ信号を出力する画素配列と、

前記列方向における前記画素配列の両側のうち一方の側に配置され、前記複数の列信号線を介して伝達された信号をそれぞれ保持する複数の第1の保持容量と、

前記列方向における前記画素配列の前記両側のうち前記一方の側に配置され、前記複数の列信号線を介して伝達された他の信号をそれぞれ保持する複数の第2の保持容量と、

前記複数の第1の保持容量のための第1の基準電源パターンと、

前記複数の第2の保持容量のための第2の基準電源パターンと、

10

前記第1の基準電源パターンの少なくとも一部は、前記複数の第1の保持容量の基準電源電極が配列された第1の領域に配され、

前記第2の基準電源パターンの少なくとも一部は、前記複数の第2の保持容量の基準電源電極が配列された第2の領域に配され、

前記第1の領域及び前記第2の領域を含む領域の内側において、少なくとも前記第1の領域と前記第2の領域との間で、前記第1の基準電源パターンと前記第2の基準電源パターンとが分離されている

ことを特徴とする撮像装置。

## 【請求項 2】

20

前記複数の第1の保持容量の前記基準電源電極のそれぞれと前記第1の基準電源パターンとは、前記第1の領域において電気的に接続され、

前記複数の第2の保持容量の前記基準電源電極のそれぞれと前記第2の基準電源パターンとは、前記第2の領域において電気的に接続されたことを特徴とする請求項1に記載の撮像装置。

**【請求項3】**

前記第1の領域及び前記第2の領域を含む領域の外側において前記第1の基準電源パターンと前記第2の基準電源パターンとを電気的に接続する共通基準電源パターンをさらに備え、

前記共通基準電源パターンは、基準電源パッドに電気的に接続されていることを特徴とする請求項1又は2に記載の撮像装置。

**【請求項4】**

前記共通基準電源パターンの幅は、前記第1の基準電源パターンの幅及び前記第2の基準電源パターンの幅のいずれよりも広いことを特徴とする請求項3に記載の撮像装置。

**【請求項5】**

前記第1の基準電源パターンは、第1の基準電源パッドに電気的に接続され、

前記第2の基準電源パターンは、第2の基準電源パッドに電気的に接続されたことを特徴とする請求項1又は2に記載の撮像装置。

**【請求項6】**

前記複数の第1の保持容量と前記複数の第2の保持容量とは、行方向に交互に並ぶよう配された

ことを特徴とする請求項1から5のいずれか1項に記載の撮像装置。

**【請求項7】**

前記複数の第1の保持容量と前記複数の第2の保持容量とは、列方向に並ぶように配された

ことを特徴とする請求項1から5のいずれか1項に記載の撮像装置。

**【請求項8】**

第1導電型の半導体領域と、

前記半導体領域内に配された、前記第1導電型と反対導電型である第2導電型のウエルをさらに備え、

前記複数の第1の保持容量のそれぞれは、

前記伝達された信号が入力される第1の電極と、

前記ウエル内に配され、前記基準電源電極として機能する前記第1導電型の第1の半導体領域と、

前記第1の電極と前記第1の半導体領域との間に配置された絶縁膜と、

を含み、

前記複数の第2の保持容量のそれぞれは、

前記伝達された他の信号が入力される第2の電極と、

前記ウエル内に前記第1の半導体領域と分離して配され、前記基準電源電極として機能する前記第1導電型の第2の半導体領域と、

前記第2の電極と前記第2の半導体領域との間に配置された絶縁膜と、

を含む

ことを特徴とする請求項1から7のいずれか1項に記載の撮像装置。

**【請求項9】**

第1導電型の半導体領域と、

前記半導体領域内に配された、前記第1導電型と反対導電型である第2導電型の第1のウエルと、

前記半導体領域内に前記第1のウエルと分離して配された前記第2導電型の第2のウエルと、

10

20

30

40

50

をさらに備え、

前記複数の第1の保持容量のそれぞれは、

前記伝達された信号が入力される第1の電極と、

前記第1のウエル内に配され、前記基準電源電極として機能する前記第1導電型の第1の半導体領域と、

前記第1の電極と前記第1の半導体領域との間に配置された絶縁膜と、を含み、

前記複数の第2の保持容量のそれぞれは、

前記伝達された他の信号が入力される第2の電極と、

前記第2のウエル内に配され、前記基準電源電極として機能する前記第1導電型の第2の半導体領域と、

前記第2の電極と前記第2の半導体領域との間に配置された絶縁膜と、

を含む

ことを特徴とする請求項1から7のいずれか1項に記載の撮像装置。

#### 【請求項10】

前記複数の第1の保持容量と前記複数の第2の保持容量との間に配され、前記複数の第1の保持容量に保持された信号をそれぞれ増幅する複数の増幅器をさらに備え、

前記複数の第2の保持容量は、前記複数の増幅器により増幅された信号を前記他の信号としてそれぞれ保持し、

前記複数の第2の保持容量が保持した前記他の信号が出力線へそれぞれ読み出されることを特徴とする請求項1から9のいずれか1項に記載の撮像装置。

#### 【請求項11】

前記出力線を介して伝達された信号を出力する出力部をさらに備え、

前記複数の第1の保持容量のそれぞれの容量値は、前記複数の第2の保持容量のそれぞれの容量値より小さく、

前記出力部には、前記第2の保持容量の容量値と前記出力線の容量値とに基づいて、前記第2の保持容量に保持された他の信号が読み出される

ことを特徴とする請求項10に記載の撮像装置。

#### 【請求項12】

前記複数の列信号線へ出力された信号をそれぞれ増幅する複数の他の増幅器をさらに備え、

前記複数の他の増幅器のそれぞれの基準電源パターンと、前記第1の基準電源パターンとは、前記第1の領域において電気的に接続され、

前記複数の増幅器のそれぞれの基準電源パターンと、前記第2の基準電源パターンとは、前記第2の領域において電気的に接続されている

ことを特徴とする請求項10又は11に記載の撮像装置。

#### 【請求項13】

前記複数の第1の保持容量が信号を保持している間に、前記複数の第2の保持容量により保持された他の信号が読み出される

ことを特徴とする請求項1から12のいずれか1項に記載の撮像装置。

#### 【請求項14】

前記複数の第1の保持容量と前記複数の第2の保持容量とによって互いに異なる行の画素の信号が保持される

ことを特徴とする請求項13に記載の撮像装置。

#### 【請求項15】

前記複数の第2の保持容量は、前記複数の第1の保持容量に信号が保持された後に、当該信号に応じた信号を前記他の信号として保持する

ことを特徴とする請求項13に記載の撮像装置。

#### 【請求項16】

請求項1から15のいずれか1項に記載の撮像装置と、

前記撮像装置の撮像面へ像を形成する光学系と、

10

20

30

40

50

前記撮像装置から出力された信号を処理して画像データを生成する信号処理部と、を備えたことを特徴とする撮像システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像装置及び撮像システムに関する。

【背景技術】

【0002】

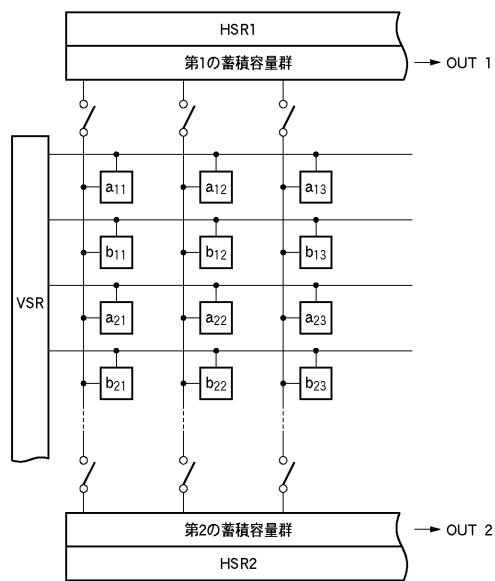

特許文献1の技術では、複数の画素が行方向及び列方向に配列された画素配列において、行方向に伸びた複数の行制御線により駆動するための信号が各画素に供給され、列方向に伸びた複数の列信号線を介して各画素の信号が読み出される。各列信号線の一端と他端とにはそれぞれ蓄積容量が接続され、2つの蓄積容量のいずれか一方の信号が読み出されているとき、画素から出力された信号が2つの蓄積容量の他方に蓄積される(図21参照)。あるいは、各列信号線の一端にそれぞれ2つの蓄積容量が並列接続され、2つの蓄積容量のいずれか一方の信号が読み出されているとき、画素から出力された信号が2つの蓄積容量の他方に蓄積される(図22参照)。これにより、特許文献1によれば、プランギング期間(センサ出力のない期間)が短縮され、総読み出し時間を短縮できる。

10

【0003】

特許文献2の技術では、複数の列信号線のそれぞれに、2つの蓄積容量と2つのアンプとが交互に接続され、2つの蓄積容量の一方に蓄積された信号が2つのアンプの一方により増幅されて2つの蓄積容量の他方に蓄積される。その2つの蓄積容量の他方に蓄積された信号は、2つのアンプの他方により増幅されて後段の出力線へと読み出される。

20

【特許文献1】特開2001-45378号公報

【特許文献2】特開平11-150255号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

特許文献1及び特許文献2の技術では、2つの蓄積容量における信号が入力される電極と対向する基準電源電極についての詳細な記載がない。例えば、どのような基準電源パターン(グランドパターン)により基準電源電圧(グランド電圧)を供給するのかについても記載がない。

30

【0005】

仮に、2つの蓄積容量(保持容量)の基準電源電極(グランド電極)に対して1つの基準電源パターンにより基準電源電圧を供給する場合を考える。2つの蓄積容量のいずれか一方の蓄積容量に画素から信号が転送されているとき、その蓄積容量の基準電源電極の電位が変動することがある。その電位の変動は、1つの基準電源パターンを介して他方の蓄積容量の基準電源電極にも伝達され得る。他方の蓄積容量の基準電源電極の電位が変動すると、その変動は、他方の蓄積容量から読み出される信号にノイズとして混入する可能性がある。

【0006】

40

本発明の目的は、列信号線を介して異なるタイミングで伝達された信号を保持するための2つの保持容量における一方の保持容量に画素から信号が転送される際に他方の保持容量の基準電源電極の電位が変動することを抑制することにある。

【課題を解決するための手段】

【0007】

本発明の第1の側面に係る撮像装置は、複数の画素が行方向及び列方向に配列され、複数の列信号線へ信号を出力する画素配列と、前記列方向における前記画素配列の両側のうち一方の側に配置され、前記複数の列信号線を介して伝達された信号をそれぞれ保持する複数の第1の保持容量と、前記列方向における前記画素配列の前記両側のうち前記一方の側に配置され、前記複数の列信号線を介して伝達された他の信号をそれぞれ保持する複数

50

の第2の保持容量と、前記複数の第1の保持容量のための第1の基準電源パターンと、前記複数の第2の保持容量のための第2の基準電源パターンと、を備え、前記第1の基準電源パターンの少なくとも一部は、前記複数の第1の保持容量の基準電源電極が配列された第1の領域に配され、前記第2の基準電源パターンの少なくとも一部は、前記複数の第2の保持容量の基準電源電極が配列された第2の領域に配され、前記第1の領域及び前記第2の領域を含む領域の内側において、少なくとも前記第1の領域と前記第2の領域との間で、前記第1の基準電源パターンと前記第2の基準電源パターンとが分離されている。

#### 【0008】

本発明の第2側面に係る撮像システムは、上記の撮像装置と、前記撮像装置の撮像面へ像を形成する光学系と、前記撮像装置から出力された信号を処理して画像データを生成する信号処理部とを備えたことを特徴とする。 10

#### 【発明の効果】

#### 【0009】

本発明によれば、列信号線を介して異なるタイミングで伝達された信号を保持するための2つの保持容量における一方の保持容量に画素から信号が転送される際に他方の保持容量の基準電源電極の電位が変動することを抑制することができる。

#### 【発明を実施するための最良の形態】

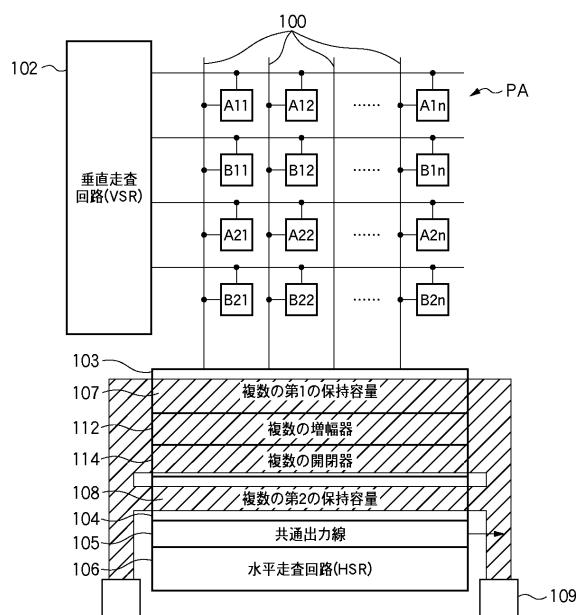

#### 【0010】

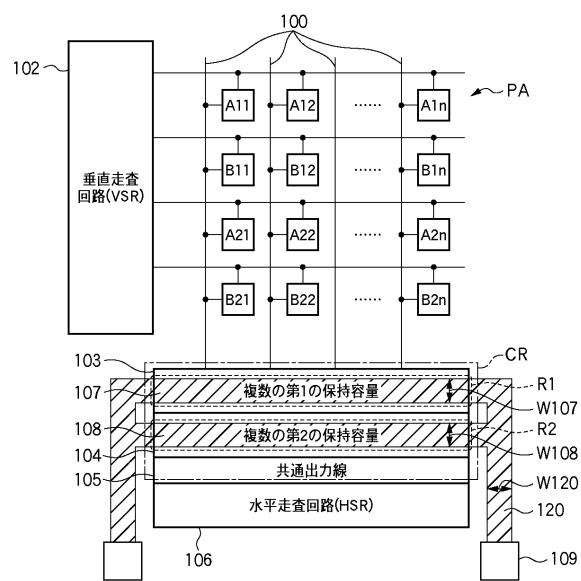

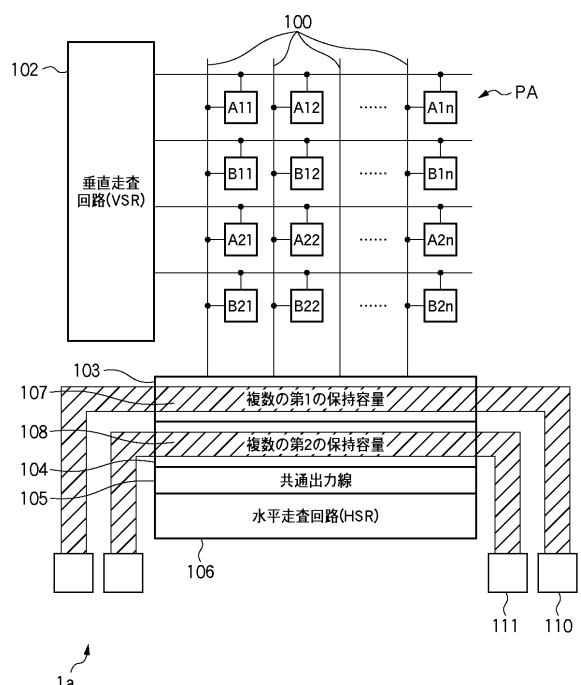

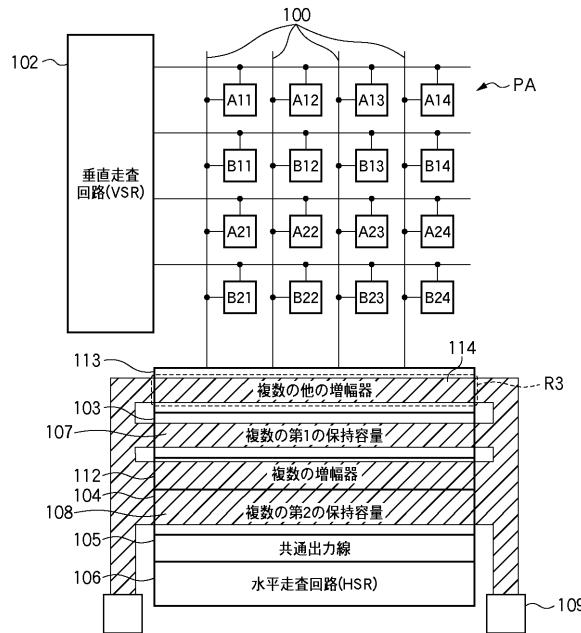

本発明の第1実施形態に係る撮像装置1の構成を、図1を用いて説明する。図1は、本発明の第1実施形態に係る撮像装置1の概略構成図である。 20

#### 【0011】

撮像装置1は、画素配列PA、垂直走査回路102、複数の第1の保持容量103、複数の第2の保持容量104、水平走査回路106、第1の基準電源パターン107、第2の基準電源パターン108、及び共通基準電源パターン120を備える。

#### 【0012】

画素配列PAでは、複数の画素A11～B2nが行方向及び列方向に配列されている。各画素A11～B2nは、光電変換部PD、転送部M1、電荷電圧変換部FD、及び出力部M2を含む(図3参照)。光電変換部は、入射光に応じて発生した電荷を蓄積する。光電変換部は、例えば、フォトダイオードである。転送部M1は、アクティブな転送信号TXが垂直走査回路102から供給された際に、光電変換部PDで発生した電荷を電荷電圧変換部FDへ転送する。転送部M1は、例えば、転送MOSトランジスタである。電荷電圧変換部FDは、転送された電荷を電圧に変換し、変換した電圧を出力部M2へ入力する。電荷電圧変換部FDは、例えば、フローティングディフュージョンである。出力部M2は、入力された電圧に応じた信号を列信号線100へ出力する。出力部M2は、例えば、ソースフォロア回路を構成する増幅MOSトランジスタである。なお、複数の列信号線100は、それぞれ、列方向に延びており、各列の画素から出力された信号を伝達する。 30

#### 【0013】

垂直走査回路(VSR)102は、画素配列PAを垂直方向(列方向)に走査することにより、信号を列信号線100へ出力するように各画素A11～B2nを駆動する。

#### 【0014】

複数の第1の保持容量103のそれぞれは、列信号線100を介して各列の画素に接続されている。複数の第1の保持容量103は、複数の列信号線100を介して伝達された信号をそれぞれ保持する。各第1の保持容量は、後述のように、信号が入力される信号電極(第1の電極)と、その信号電極に対向する基準電源電極とを含む。複数の第1の保持容量103は、第1の領域R1に配されている。 40

#### 【0015】

複数の第2の保持容量104のそれぞれは、列信号線100を介して各列の画素に接続されている。複数の第2の保持容量104は、複数の列信号線100を介して伝達された他の信号をそれぞれ保持する。各第2の保持容量は、後述のように、信号が入力される信号電極(第2の電極)と、その信号電極に対向する基準電源電極とを含む。複数の第2の 50

保持容量 104 は、第 2 の領域 R2 に配されている。

**【0016】**

水平走査回路 (HSR) 106 は、複数の第 1 の保持容量 103 及び複数の第 2 の保持容量 104 をそれぞれ水平方向に走査する。これにより、第 1 の保持容量に保持された信号と第 2 の保持容量に保持された他の信号とがそれぞれ共通出力線 105 へ読み出される。

**【0017】**

第 1 の基準電源パターン 107 は、第 1 の保持容量のためのパターンであり、その一部が第 1 の領域 R1 に配されている。第 1 の基準電源パターン 107 は、各第 1 の保持容量の基準電源電極に電気的に接続されている。

10

**【0018】**

第 2 の基準電源パターン 108 は、第 2 の保持容量のパターンであり、その一部が第 2 の領域 R2 に配されている。第 2 の基準電源パターン 108 は、各第 2 の保持容量の基準電源電極に電気的に接続されている。

**【0019】**

共通基準電源パターン 120 は、第 1 の領域 R1 及び第 2 の領域 R2 を含む領域 CR の外側において第 1 の基準電源パターン 107 と第 2 の基準電源パターン 108 とを電気的に接続する。共通基準電源パターン 120 は、基準電源パッド 109 に電気的に接続されている。共通基準電源パターン 120 の幅 W120 は、第 1 の基準電源パターン 107 の幅 W107 及び第 2 の基準電源パターン 108 の幅 W108 のいずれよりも広い。このため、共通基準電源パターン 120 の配線抵抗は、第 1 の基準電源パターン 107 の配線抵抗及び第 2 の基準電源パターン 108 の配線抵抗のいずれよりも低い。

20

**【0020】**

ここで、第 1 の領域 R1 及び第 2 の領域 R2 を含む領域 CR の内側において、少なくとも第 1 の領域 R1 と第 2 の領域 R2 との間で、第 1 の基準電源パターン 107 と第 2 の基準電源パターン 108 とが分離されている。これにより、第 1 の保持容量に画素から信号が転送される際に第 1 の保持容量の基準電源電極の電位が変動したとしても、その電位の変動は、第 1 の基準電源パターン 107 から第 2 の基準電源パターン 108 へ直接伝達されにくい。このため、第 2 の保持容量の基準電源電極の電位が変動しにくい。すなわち、列信号線を介して異なるタイミングで伝達された信号を保持するための 2 つの保持容量における一方の保持容量に画素から信号が転送される際に他方の保持容量の基準電源電極の電位が変動することを抑制することができる。

30

**【0021】**

また、第 1 の保持容量の基準電源電極の電位が変動した場合、その電位の変動は、第 1 の基準電源パターン 107 から共通基準電源パターン 120 に伝達される。このとき、共通基準電源パターン 120 の配線抵抗が第 2 の基準電源パターン 108 の配線抵抗より低いので、その電位の変動は、共通基準電源パターン 120 から容易に基準電源パッド 109 経由で外部へ排出され得る。この点からも、第 1 の保持容量の基準電源電極の電位の変動は、第 2 の保持容量の基準電源電極に伝達されにくい。

40

**【0022】**

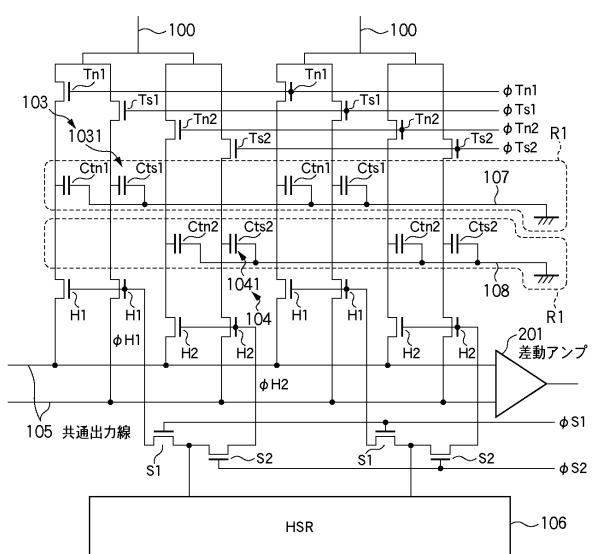

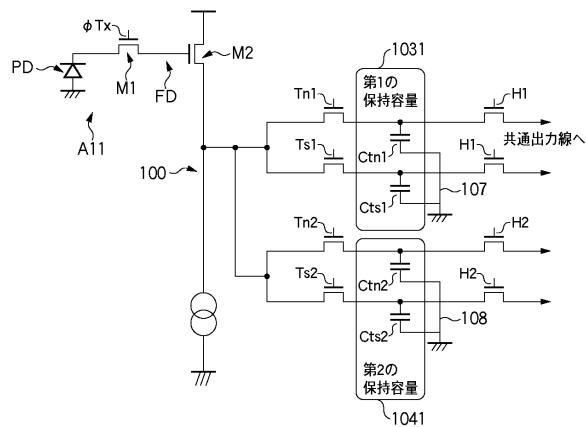

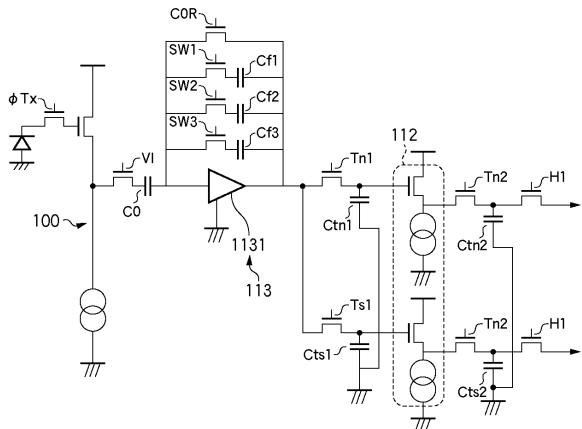

次に、本発明の第 1 実施形態に係る撮像装置 1 の回路構成例を、図 2 及び図 3 を用いて説明する。図 2 は、本発明の第 1 実施形態に係る撮像装置 1 の回路構成例を示す図である。図 3 は、図 2 を簡略化した回路図である。

**【0023】**

第 1 の保持容量 1301 は、容量 Ctn1 又は容量 Cts1 である。容量 Ctn1 は、第 1 の画素（例えば、画素 A11）から出力された基準信号成分（ノイズレベルの N 信号）を保持するための容量である。容量 Cts1 は、第 1 の画素から出力された画素信号成分（光信号レベルの S 信号）を保持するための容量である。容量 Ctn1 及び容量 Cts1 は、第 1 の領域 R1 に配されている。容量 Ctn1 の基準電源電極及び容量 Cts1 の基準電源電極は、第 1 の基準電源パターン 107 に接続されている。

50

## 【0024】

スイッチ素子 T<sub>n</sub>1 は、アクティブな制御パルス T<sub>n</sub>1 を受けた際に、オンして、列信号線 100 と容量 C<sub>t n</sub>1 とを導通させる。容量 C<sub>t n</sub>1 は、列信号線 100 により伝達された第 1 の画素の N 信号を蓄積する。スイッチ素子 T<sub>n</sub>1 は、ノンアクティブな制御パルス T<sub>n</sub>1 を受けた際に、オフして、列信号線 100 と容量 C<sub>t n</sub>1 とを遮断する。容量 C<sub>t n</sub>1 は、N 信号を保持する。

## 【0025】

スイッチ素子 T<sub>s</sub>1 は、アクティブな制御パルス T<sub>s</sub>1 を受けた際に、オンして、列信号線 100 と容量 C<sub>t s</sub>1 とを導通させる。容量 C<sub>t s</sub>1 は、列信号線 100 により伝達された第 1 の画素の S 信号を蓄積する。スイッチ素子 T<sub>s</sub>1 は、ノンアクティブな制御パルス T<sub>s</sub>1 を受けた際に、オフして、列信号線 100 と容量 C<sub>t s</sub>1 とを遮断する。容量 C<sub>t s</sub>1 は、S 信号を保持する。

## 【0026】

第 2 の保持容量 1401 は、容量 C<sub>t n</sub>2 又は容量 C<sub>t s</sub>2 である。容量 C<sub>t n</sub>2 は、第 2 の画素（例えば、画素 B11）から出力された基準信号成分（ノイズレベルの N 信号）を保持するための容量である。容量 C<sub>t s</sub>2 は、第 2 の画素から出力された画素信号成分（光信号レベルの S 信号）を保持するための容量である。容量 C<sub>t n</sub>2 及び容量 C<sub>t s</sub>2 は、第 2 の領域 R<sub>2</sub> に配されている。容量 C<sub>t n</sub>2 の基準電源電極及び容量 C<sub>t s</sub>2 の基準電源電極は、第 2 の基準電源パターン 108 に接続されている。

## 【0027】

スイッチ素子 T<sub>n</sub>2 は、アクティブな制御パルス T<sub>n</sub>2 を受けた際に、オンして、列信号線 100 と容量 C<sub>t n</sub>2 とを導通させる。容量 C<sub>t n</sub>2 は、列信号線 100 により伝達された第 2 の画素の N 信号を蓄積する。スイッチ素子 T<sub>n</sub>2 は、ノンアクティブな制御パルス T<sub>n</sub>2 を受けた際に、オフして、列信号線 100 と容量 C<sub>t n</sub>2 とを遮断する。容量 C<sub>t n</sub>2 は、N 信号を保持する。

## 【0028】

スイッチ素子 T<sub>s</sub>2 は、アクティブな制御パルス T<sub>s</sub>2 を受けた際に、オンして、列信号線 100 と容量 C<sub>t s</sub>2 とを導通させる。容量 C<sub>t s</sub>2 は、列信号線 100 により伝達された第 2 の画素の S 信号を蓄積する。スイッチ素子 T<sub>s</sub>1 は、ノンアクティブな制御パルス T<sub>s</sub>2 を受けた際に、オフして、列信号線 100 と容量 C<sub>t s</sub>2 とを遮断する。容量 C<sub>t s</sub>2 は、S 信号を保持する。

## 【0029】

スイッチ素子 H<sub>1</sub> は、水平走査回路 106 が第 1 の列（例えば、画素 A11 ~ B21 の列）を選択しており制御信号 S<sub>1</sub> がアクティブな第 1 の期間に、オンする。これにより、容量 C<sub>t n</sub>1 に保持された第 1 の画素の N 信号と、容量 C<sub>t s</sub>1 に保持された第 1 の画素の S 信号とは、共通出力線へ読み出されて差動アンプ 201 へ供給される。

## 【0030】

差動アンプ 201 は、第 1 の画素の N 信号と S 信号との差分を演算する（CDS 处理を行う）ことにより、ノイズ成分が除去された第 1 の画素の画像信号を出力する。

## 【0031】

スイッチ素子 H<sub>2</sub> は、水平走査回路 106 が第 1 の列を選択しており制御信号 S<sub>2</sub> がアクティブな第 2 の期間に、オンする。これにより、容量 C<sub>t n</sub>2 に保持された第 2 の画素の N 信号と、容量 C<sub>t s</sub>2 に保持された第 2 の画素の S 信号とは、共通出力線へ読み出されて差動アンプ 201 へ供給される。

## 【0032】

差動アンプ 201 は、第 2 の画素の N 信号と S 信号との差分を演算する（CDS 处理を行う）ことにより、ノイズ成分が除去された第 2 の画素の画像信号を出力する。

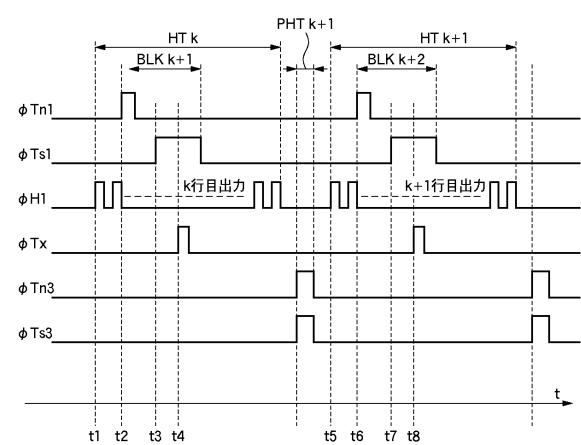

## 【0033】

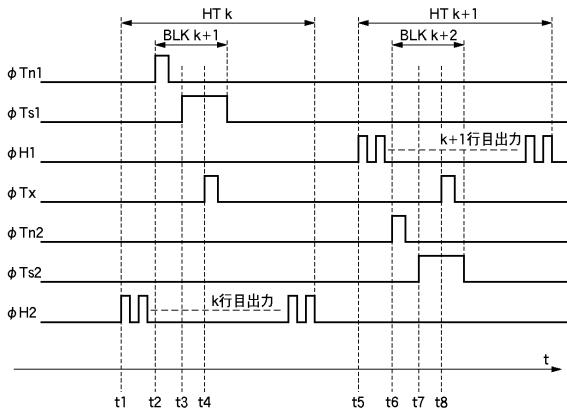

次に、本発明の第 1 実施形態に係る撮像装置 1 の動作を、図 4 を用いて説明する。図 4 は、本発明の第 1 実施形態に係る撮像装置 1 の動作を示すタイミングチャートである。図

10

20

30

40

50

4に示す制御信号  $T_x$  は、垂直走査回路 102 から画素配列 PA の各画素へ供給される。制御信号  $H_1$ 、 $H_2$  は、水平走査回路 106 及びスイッチ素子 S1, S2 から、スイッチ素子  $H_1$ ,  $H_2$  へそれぞれ供給される。他の制御信号は、垂直走査回路 102 又は水平走査回路 106 から供給される。

#### 【0034】

時刻  $t_1$  より開始される  $k$  行目の水平転送期間  $HT_k$  中に、各列の制御信号  $H_2$  が順次にアクティブになるので、各列のスイッチ素子  $H_2$  が順次にオンする。これにより、各列の容量  $C_{tn2}$ ,  $C_{ts2}$  から  $k$  行目の画素の N 信号, S 信号が共通出力線 105 へ読み出される。

#### 【0035】

水平転送期間  $HT_k$  中の時刻  $t_2$  において、制御信号  $T_{n1}$  がアクティブになるので、スイッチ素子  $T_{n1}$  は、オンし、 $k+1$  行目の画素の N 信号を容量  $C_{tn1}$  に転送する。

#### 【0036】

水平転送期間  $HT_k$  中の時刻  $t_3$  において、制御信号  $T_{s1}$  がアクティブになるので、スイッチ素子  $T_{s1}$  は、オンする。

#### 【0037】

水平転送期間  $HT_k$  中の時刻  $t_4$  において、制御信号  $T_x$  がアクティブになるので、転送部（転送 MOS ロジック）M1 は、オンして、 $k+1$  行目の画素の S 信号が  $C_{ts1}$  へと転送される。

#### 【0038】

このように、水平転送期間  $HT_k$  において、 $k$  行目の画素の信号が共通出力線へ読み出される動作と、 $k+1$  行目の画素の信号が保持容量へ転送される動作とは、並行して行われる。すなわち、 $k$  行目の画素の信号の水平転送期間  $HT_k$  と、 $k+1$  行目の画素の信号の垂直ブランディング期間  $BLK_{k+1}$  とは、重なっている。

#### 【0039】

時刻  $t_5$  より開始する水平転送期間  $HT_{k+1}$  中に、各列の制御信号  $H_1$  が順次にアクティブになるので、各列のスイッチ素子  $H_1$  が順次にオンする。これにより、各列の容量  $C_{tn1}$ ,  $C_{ts1}$  から  $k+1$  行目の画素の N 信号, S 信号が共通出力線 105 へ読み出される。

#### 【0040】

水平転送期間  $HT_{k+1}$  中の時刻  $t_6$  において、制御信号  $T_{n2}$  がアクティブになるので、スイッチ素子  $T_{n2}$  は、オンし、 $k+2$  行目の画素の N 信号を容量  $C_{tn2}$  に転送する。

#### 【0041】

水平転送期間  $HT_{k+1}$  中の時刻  $t_7$  において、制御信号  $T_{s2}$  がアクティブになるので、スイッチ素子  $T_{s2}$  は、オンする。。

#### 【0042】

水平転送期間  $HT_{k+1}$  中の時刻  $t_8$  において、制御信号  $T_x$  がアクティブになるので、転送部（転送 MOS ロジック）M1 は、オンして、 $k+2$  行目の画素の S 信号が  $C_{ts2}$  へと転送される。

#### 【0043】

このように、水平転送期間  $HT_{k+1}$  において、 $k+1$  行目の画素の信号が共通出力線へ読み出される動作と、 $k+2$  行目の画素の信号が保持容量へ転送される動作とは、並行して行われる。すなわち、 $k+1$  行目の画素の信号の水平転送期間  $HT_{k+1}$  と、 $k+2$  行目の画素の信号の垂直ブランディング期間  $BLK_{k+2}$  とは、重なっている。

#### 【0044】

上述の通り、 $BLK$  期間を前行の水平転送期間に重ねることにより、読み出し時間が短縮され、単位時間あたりの撮像枚数が向上するという利点がある。しかしながら、従来は従来技術の課題の項で述べたように、 $BLK$  期間と水平走査期間が重複することにより、

10

20

30

40

50

出力信号にノイズを重畠することがあった。以下で、本発明の効果として、このノイズの重畠が抑制される機構を説明する。

#### 【0045】

図3において、水平走査回路102の駆動によってスイッチ素子H1の水平転送が行なわれている期間に、スイッチ素子Tn2をオンすることにより、所定の画素の電荷電圧変換部FDに保持されていた基準信号成分を第2の保持容量Ctn2へと転送する。このとき、スイッチ素子Tn2のオンによって電荷の移動が生じノイズが生じる場合がある。しかし、転送される信号と転送前に容量Ctn2に保持されていた信号とがともに基準信号成分であるので、スイッチ素子Tn2がオンした際の信号電極の電位の変動は小さい。

#### 【0046】

次に、スイッチ素子Ts2をオンし、重ねて所定の画素の転送部（転送MOSトランジスタ）M1をオンすることで、画素信号が容量Ctss2へと転送される。このとき、特に光照射時において、前のフレームで容量Ctss2には大きな信号成分が保持されているような場合、スイッチ素子Ts2をオンするタイミングで電荷の移動が生じる。基準電源パターンには抵抗成分（配線抵抗）が存在するため、このような電荷の移動が生じると基準電源パターンにより伝達される基準電源電位が変動する。

#### 【0047】

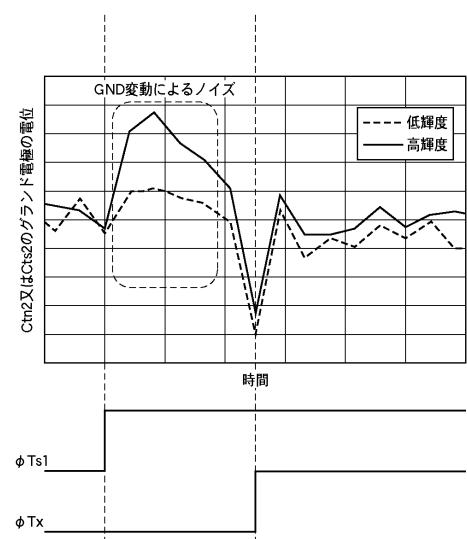

ここで、仮に、第1の保持容量103（Ctn1、Ctss1）と第2の保持容量104（Ctn2、Ctss2）とが1つの基準電源パターンに接続されている場合を考える。この場合、BLK動作と水平走査期間とが重複させた際に、一方の保持容量の基準電源電位の変動が他方の保持容量の基準電源電位をも変動させてるので、他方の保持容量が保持しようとする信号にノイズが重畠する。ノイズが重畠する様子を図20に示す。図20は、第1の保持容量と第2の保持容量とが1つの基準電源パターンに接続されると仮定した場合におけるスイッチ素子Ts1をオンさせた際の容量Ctn2又はCtss2の基準電源電極の電位の変動を示す図である。図19に示されるように、スイッチ素子Tsをオンするタイミングで、第2の保持容量の基準電源電極の電位が変動する為、第2の保持容量が保持する信号が安定するまでに時間を要する。また、被写体の低輝度信号と高輝度信号とでは保持容量に保持された電荷量が異なるため、混入するノイズのレベルが異なる。このように、一定の期間にわたってレベルが変動する、かつ、輝度によってレベルが異なる性質をもつノイズは補正が困難となる。

#### 【0048】

その1つの基準電源パターンの幅を大きくすることによりその配線抵抗を下げれば、このようなノイズを低減できるようにも考えられる。しかし、1つの基準電源パターンの抵抗を下げる対策は大きな面積を必要とするので、近年における画素や保持容量を形成する領域を微細化する要求が高い状況では、そのような対策と取ることは困難である。

#### 【0049】

それに対して、本実施形態では、第1の保持容量1031（Ctn1、Ctss1）と第2の保持容量1041（Ctn2、Ctss2）との基準電源電極を、それぞれ、第1の基準電源パターン107と第2の基準電源パターン108とに接続する。これにより、第1の保持容量1031（Ctn1、Ctss1）と第2の保持容量1041（Ctn2、Ctss2）との基準電源電極を互いに電気的に分離している。そのため、Ctss2の基準電源電極の電位が変動しても、Ctn1、Ctss1の基準電源電極の電位の変動は小さい（図20に示す場合に比較してノイズの振幅は約1/10になる）。その結果、BLK期間と水平走査期間とが時間的に重なりをもつ場合においても、基準電源電位の変動により発生するノイズの重畠を抑制できる。

#### 【0050】

本実施形態で開示する通り、保持容量の基準電源電極を電気的に分離することは面積の増大を最小限にしながら、ノイズを著しく低減できる。画素や保持容量を形成する領域の外側においては、基準電源パターンの幅を広くすることが比較的容易である。したがって、そのような領域では、第1の保持容量と第2の保持容量との基準電源パターンを必ずし

10

20

30

40

50

も分離しなくともよい。本実施形態では、図1に示すように、領域CRの内側において、第1の保持容量103の第1の基準電源パターン107と第2の保持容量104の第2の基準電源パターン108とを電気的に分離している。領域CRの外側において、面積の大きな配線が形成できるので、幅の広い共通基準電源パターン120へ第1の基準電源パターン107と第2の基準電源パターン108とを接続し、パッド数の増大を防止している。パッド数の増大を許せば、撮像装置1aが図5に示す構成をしていても良い。すなわち、第1の基準電源パターン107と第2の基準電源パターン108とは、それぞれ、第1の基準電源パッド110、第2の基準電源パッド111に接続されることにより、パッドにいたるまで電気的に分離されていてもよい。

## 【0051】

10

なお、基準電源パターンにより保持容量Ctの基準電源電極へ供給する基準電源電圧は、グランド電圧でも良いし、基準となる他の固定電圧でもよい。

## 【0052】

また、回路構成は、第1、第2の保持容量を備え、水平転送期間中にBLK動作の行える回路構成となっていれば、本実子形態の回路構成と異なっていても良い。

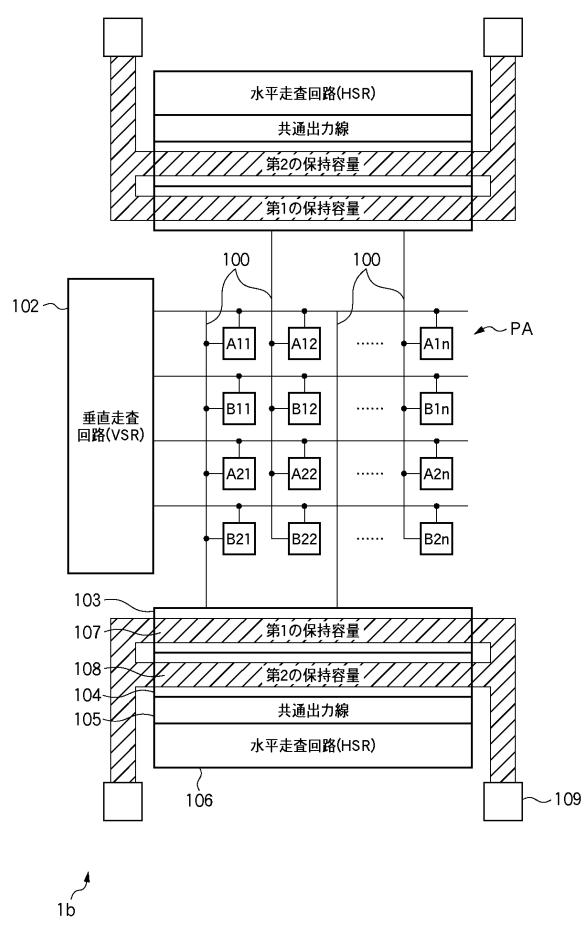

## 【0053】

また、本実施形態においては、画素配列PAの片側のみに第1、第2保持容量を備えた例を示したが、撮像装置1bが図6に示す構成をしていても良い。すなわち、画素配列PAを他方の側に同じく第1、第2の保持容量、共通出力線、及び水平走査回路を備えている。この場合には、画素信号を列ごとに上下に振り分けて読み出すことができ、さらに高速読み出しが可能となる。

20

## 【0054】

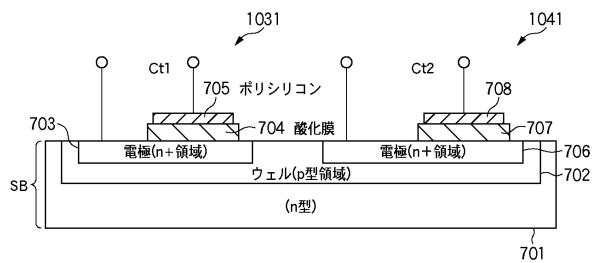

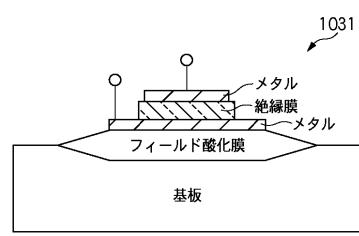

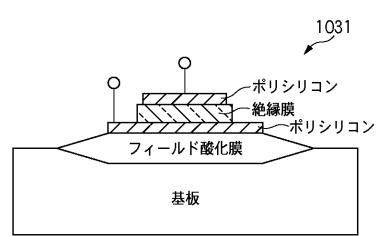

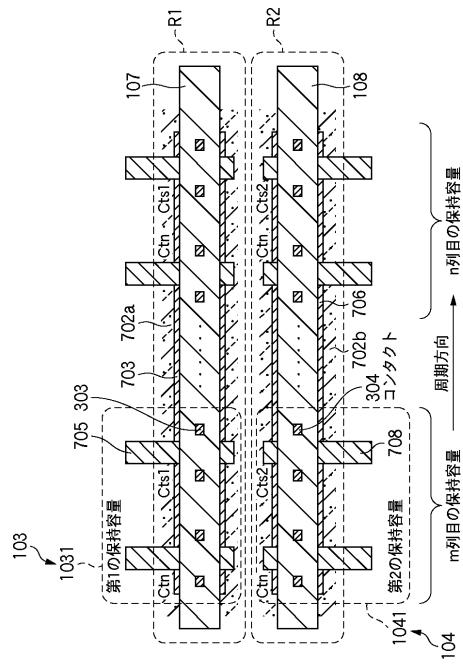

次に、第1の保持容量及び第2の保持容量の断面構成例を、図7を用いて説明する。図7は、第1の保持容量及び第2の保持容量の断面構成例を示す断面図である。

## 【0055】

半導体基板SBにおけるn型（第1導電型）の半導体領域701には、n型（第1導電型）と反対導電型であるp型（第2導電型）のウエル702が形成されている。さらに、ウエル702内（ウエル内）には、第1の保持容量1031の基準電源電極として機能するn型の第1の半導体領域703を形成している。第1の半導体領域703の上部に、酸化膜704を介してポリシリコン層705を堆積させる。ポリシリコン層705を信号電極、第1の半導体領域703を基準電源電極として、第1の保持容量1031が形成されている。本実施形態においては、n型の半導体領域701内（半導体領域内）に設けたp型のウエル702の電位は基準電源電位であり、また、ウエル702内に形成された第1の半導体領域703も基準電源パターンにより基準電源電位へと接続されている。一方、上部のポリシリコン層705には信号が書き込まれる。

30

## 【0056】

また、ウエル702内には、第2の保持容量1041の基準電源電極となるn型の第2の半導体領域706を形成している。第2の半導体領域706の上部に、酸化膜707を介してポリシリコン層708を堆積させる。ポリシリコン層708は、第2の保持容量1041の信号電極として機能し、第2の半導体領域706は、第2の保持容量1041の基準電源電極として機能する。本実施形態においては、n型の半導体領域701内に設けたp型のウエル702の電位は基準電源電位であり、また、ウエル702内に形成された第2の半導体領域706も基準電源パターンにより基準電源電位へと接続されている。一方、上部のポリシリコン層708には信号が書き込まれる。

40

## 【0057】

ここで、第2の半導体領域706は、ウエル702内に第1の半導体領域703と電気的に分離して配されている。これにより、第1の保持容量の基準電源電極の電位の変動が第2の保持容量の基準電源電極へ伝達されにくくなっている。

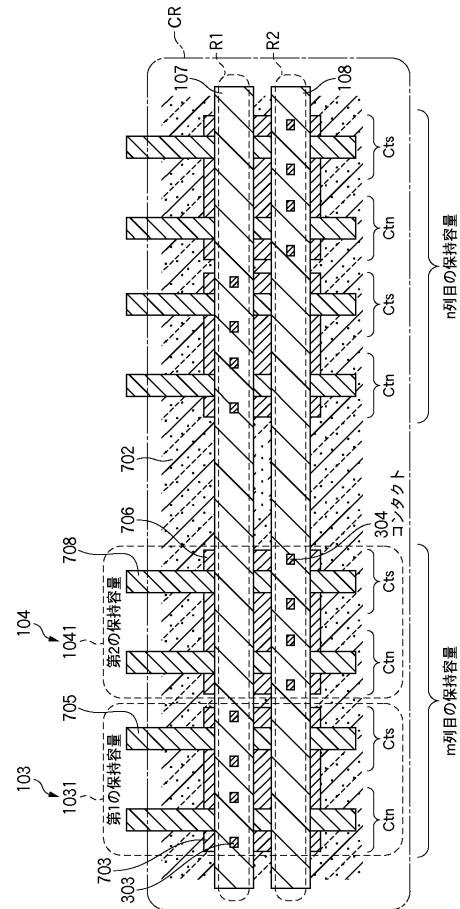

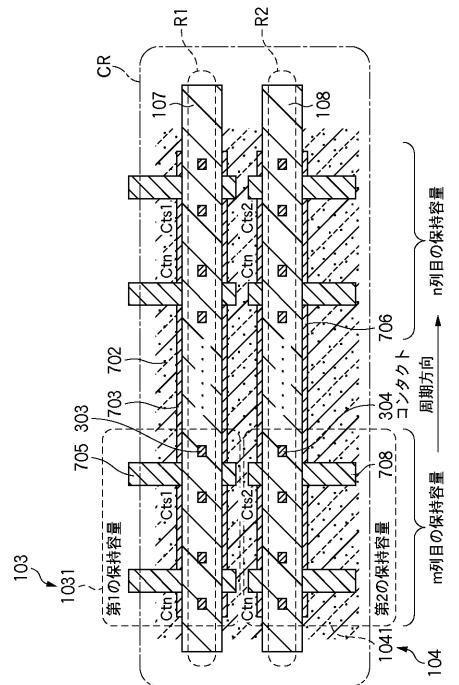

## 【0058】

次に、第1の保持容量及び第2の保持容量のレイアウト構成例を、図8を用いて説明す

50

る。図8は、第1の保持容量及び第2の保持容量のレイアウト構成例を示す図である。

【0059】

ポリシリコン層705とウエル302内の第1の半導体領域703により第1の保持容量1031が形成される。ポリシリコン層708とウエル302内の第2の半導体領域706により第2の保持容量1041が形成される。第1の保持容量1031と第2の保持容量1041とが水平方向(行方向)に配された組は、さらに水平方向(行方向)に繰り返し配列されている。すなわち、複数の第1の保持容量103と複数の第2の保持容量104とは、第1の領域R1及び第2の領域R2を含む領域CRの内側において、行方向に交互に並ぶように配されている。複数の第1の保持容量103のそれぞれと第1の基準電源パターン107とは、コンタクト303を介して、第1の領域R1において電気的に接続されている。複数の第2の保持容量104のそれぞれと第2の基準電源パターン108とは、コンタクト304を介して、第2の領域R2において電気的に接続されている。図8に示すレイアウト構成により、列信号線と共に出力線との間に第1の保持容量と第2の保持容量とを並列に設けた回路構成(図2参照)を容易に実現できる。

10

【0060】

なお、図8に示すレイアウト構成は、列信号線と共に出力線との間に第1の保持容量と第2の保持容量とを直列に設けた回路構成(図15参照)を実現するのに用いられても良い。

【0061】

また、保持容量の構成は必ずしもMOSキャパシタなくともよく、図9に示すメタル/絶縁膜/メタルで構成される容量でよく、図10に示すポリシリコン/絶縁膜/ポリシリコンで構成される容量でよい。少なくとも、第1の保持容量の基準電源電極と第2の保持容量の基準電源電極とが互いに電気的に分離されなければならない。

20

【0062】

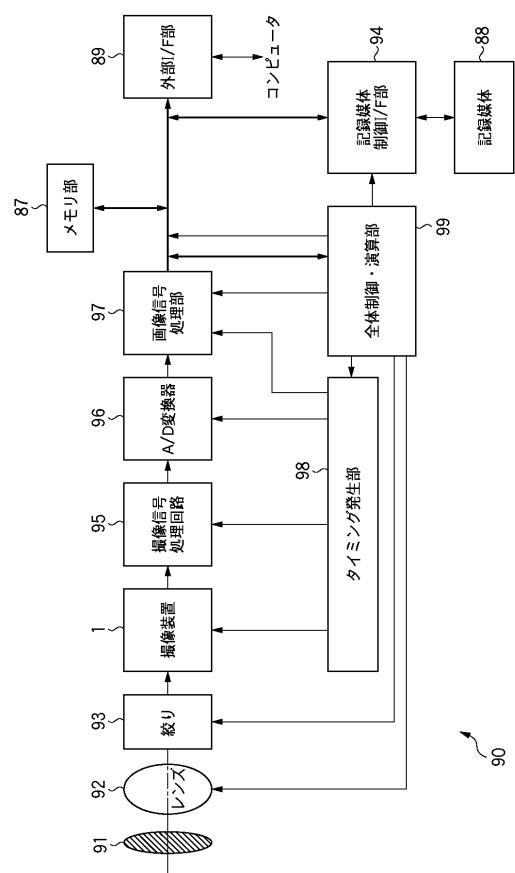

次に、本発明の撮像装置を適用した撮像システムの一例を図11に示す。

【0063】

撮像システム90は、図11に示すように、主として、光学系、撮像装置1及び信号処理部を備える。光学系は、主として、シャッター91、撮影レンズ92及び絞り93を備える。信号処理部は、主として、撮像信号処理回路95、A/D変換器96、画像信号処理部97、メモリ部87、外部I/F部89、タイミング発生部98、全体制御・演算部99、記録媒体88及び記録媒体制御I/F部94を備える。なお、信号処理部は、記録媒体88を備えなくても良い。

30

【0064】

シャッター91は、光路上において撮影レンズ92の手前に設けられ、露出を制御する。

【0065】

撮影レンズ92は、入射した光を屈折させて、撮像装置1の画素配列(撮像面)に被写体の像を形成する。

【0066】

絞り93は、光路上において撮影レンズ92と撮像装置1との間に設けられ、撮影レンズ92を通過後に撮像装置1へ導かれる光の量を調節する。

40

【0067】

撮像装置1は、画素配列に形成された被写体の像を画像信号に変換する。撮像装置1は、その画像信号を画素配列から読み出して出力する。

【0068】

撮像信号処理回路95は、撮像装置1に接続されており、撮像装置1から出力された画像信号を処理する。

【0069】

A/D変換器96は、撮像信号処理回路95に接続されており、撮像信号処理回路95から出力された処理後の画像信号(アナログ信号)をデジタル信号へ変換する。

50

**【0070】**

画像信号処理部97は、A/D変換器96に接続されており、A/D変換器96から出力された画像信号（デジタル信号）に各種の補正等の演算処理を行い、画像データを生成する。この画像データは、メモリ部87、外部I/F部89、全体制御・演算部99及び記録媒体制御I/F部94などへ供給される。

**【0071】**

メモリ部87は、画像信号処理部97に接続されており、画像信号処理部97から出力された画像データを記憶する。

**【0072】**

外部I/F部89は、画像信号処理部97に接続されている。これにより、画像信号処理部97から出力された画像データを、外部I/F部89を介して外部の機器（パソコン等）へ転送する。10

**【0073】**

タイミング発生部98は、撮像装置1、撮像信号処理回路95、A/D変換器96及び画像信号処理部97に接続されている。これにより、撮像装置1、撮像信号処理回路95、A/D変換器96及び画像信号処理部97へタイミング信号を供給する。そして、撮像装置1、撮像信号処理回路95、A/D変換器96及び画像信号処理部97がタイミング信号に同期して動作する。

**【0074】**

全体制御・演算部99は、タイミング発生部98、画像信号処理部97及び記録媒体制御I/F部94に接続されており、タイミング発生部98、画像信号処理部97及び記録媒体制御I/F部94を全体的に制御する。20

**【0075】**

記録媒体88は、記録媒体制御I/F部94に取り外し可能に接続されている。これにより、画像信号処理部97から出力された画像データを、記録媒体制御I/F部94を介して記録媒体88へ記録する。

**【0076】**

以上の構成により、撮像装置1において良好な画像信号が得られれば、良好な画像（画像データ）を得ることができる。

**【0077】**

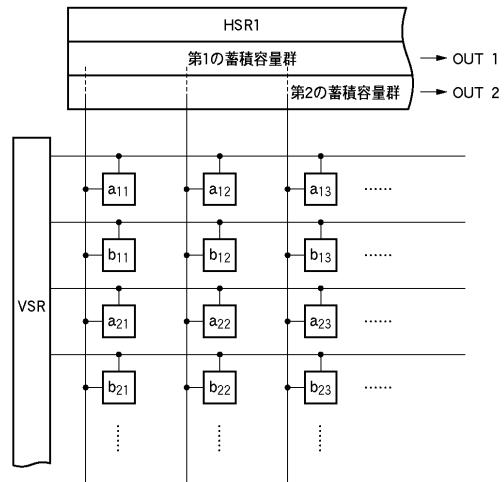

次に、本発明の第2実施形態に係る撮像装置について、図12を用いて説明する。図12は、本発明の第2実施形態に係る撮像装置のレイアウト構成例を示す図である。30

**【0078】**

本実施形態に係る撮像装置の構成は、次の点で第1実施形態と異なる。第1の保持容量1031と第2の保持容量1041とが垂直方向（列方向）に配された組は、さらに水平方向（行方向）に繰り返し配列されている。すなわち、複数の第1の保持容量103と複数の第2の保持容量104とは、第1の領域R1及び第2の領域R2を含む領域CRの内側において、列方向に並ぶように配されている。図12に示すレイアウト構成により、列信号線と共に出力線との間に第1の保持容量と第2の保持容量とを直列に設けた回路構成（図15参照）を容易に実現できる。40

**【0079】**

なお、図12に示すレイアウト構成は、列信号線と共に出力線との間に第1の保持容量と第2の保持容量とを並列に設けた回路構成（図2参照）を実現するのに用いられても良い。

**【0080】**

また、図13に示すように、撮像装置は、ウエル702の代わりに第1のウエル702a及び第2のウエル702bを備えても良い。第1のウエル702aは、第1の領域R1において半導体領域701内に配されたp型の領域である。第2のウエル702bは、第2の領域R2において半導体領域701内に第1のウエル702aと分離して配されたp型の領域である。第1の保持容量1031の基準電源電極となる第1の半導体領域70350

が第1のウエル702a内(第1のウエル内)に配されている。第2の保持容量1032の基準電源電極となる第2の半導体領域706が第2のウエル702b内(第2のウエル内)に配されている。これにより、第1の保持容量1031の基準電源電極の電位の変動が、さらに、第2の保持容量1032の基準電源電極へ伝達されにくくなっている。

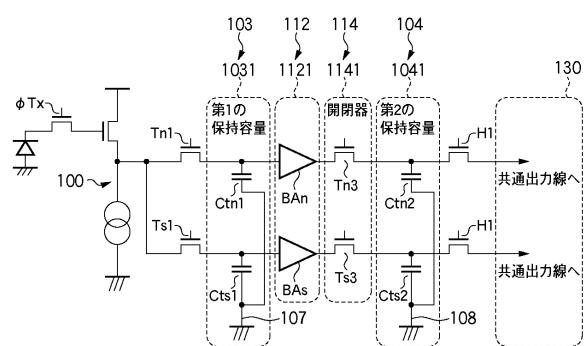

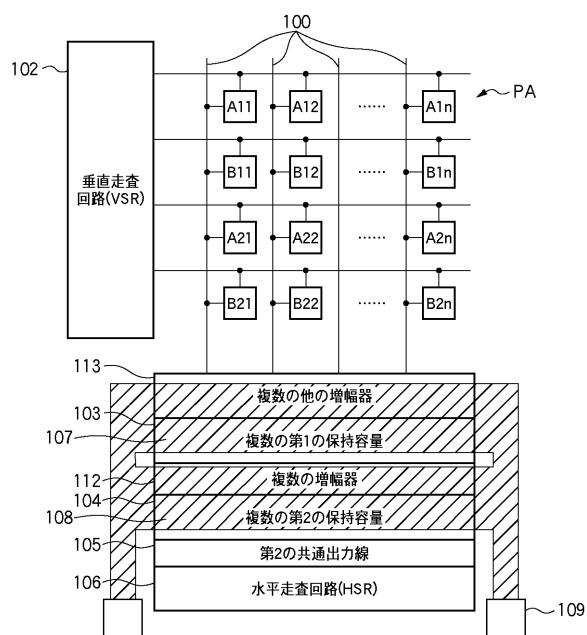

#### 【0081】

本発明の第3実施形態に係る撮像装置について、図14及び図15を用いて説明する。図14は、本発明の第3実施形態に係る撮像装置の構成図である。図15は、本発明の第3実施形態に係る撮像装置の回路構成例を示す図である。

#### 【0082】

本実施形態に係る撮像装置の構成は、次の点で第1実施形態と異なる。列信号線100と共通出力線105との間に第1の保持容量1031と第2の保持容量1041とが直列に設けられている。第1の保持容量1031と第2の保持容量1041との間には、増幅器1121と開閉器1141とが配されている。増幅器1121は、例えば、バッファアンプBAn, BAsである。開閉器1141は、例えば、スイッチ素子Tn3, Ts3である。

#### 【0083】

すなわち、複数の第1の保持容量103により保持された信号は、複数の増幅器112へそれぞれ出力される。複数の増幅器112は、複数の第1の保持容量103に保持された信号をそれぞれ増幅する。複数の第2の保持容量104は、複数の増幅器112により増幅された信号を他の信号としてそれぞれ保持し、その後、保持した他の信号を共通出力線105へそれぞれ読み出される。

#### 【0084】

出力部130は、共通出力線105を介して伝達された信号を出力する。ここで、複数の第1の保持容量103のそれぞれの容量値は、複数の第2の保持容量104の容量値より小さくてもよい。これは、第1の保持容量と第2の保持容量との間に設けた増幅器1121により、信号を増幅できるためであり、また面積も小さくすることが可能である。

#### 【0085】

出力部130には、第2の保持容量1041の容量値と共に出力線105の容量値に基づいて、第2の保持容量に保持された他の信号が読み出される。このとき、複数の第2の保持容量104のそれぞれの容量値が複数の第1の保持容量103のそれぞれの容量値より大きいので、ゲインを低下させずに共通出力線へ他の信号が読み出されるようにできる。この容量値とは例えば、同一構造からなる保持容量であれば、その電極面積で比較することが可能である。

#### 【0086】

また、本実施形態に係る撮像装置の動作は、図16に示すように、次の点で第1実施形態と異なる。

#### 【0087】

時刻t1より開始されるk行目の水平転送期間HTk中に、各列の制御信号H1が順次にアクティブになるので、各列のスイッチ素子H1が順次にオンする。

#### 【0088】

k行目の水平転送期間HTkとk+1行目の水平転送期間HTk+1との間におけるk+1行目の予備的な水平転送期間PHTk+1中に、制御信号Tn3, Ts3がそれぞれアクティブになるので、スイッチ素子Tn3, Ts3は、それぞれオンする。これにより、各列の容量Ctn1, Cts1からk+1行目の画素のN信号, S信号が各列の容量Ctn1, Cts1へそれぞれ転送される。

#### 【0089】

なお、第1の保持容量と第2の保持容量との接続に関しては回路形式を限定しない、ゲインをかける構成でもよく、またはボルテージフォロワやソースフォロワ等の回路形式でもよい。

10

20

30

40

50

**【0090】**

本発明の第4実施形態に係る撮像装置について、図17及び図18を用いて説明する。図17は、本発明の第4実施形態に係る撮像装置の構成図である。図18は、本発明の第4実施形態に係る撮像装置の回路構成例を示す図である。

**【0091】**

本実施形態に係る撮像装置の構成は、次の点で第1実施形態と異なる。列信号線100と複数の第1の保持容量103との間に複数の他の増幅器113が設けられている。列信号線100と他の増幅器1131との間には、列信号線100と容量C0とをショートもしくはオープンするスイッチVLが設けられている。また、他の増幅器1131の入力端子と出力端子との間には、増幅器の帰還回路をショートもしくはオープンするスイッチC0Rと、スイッチSW1～SW3及び容量Cf1～Cf3とが並列接続されている。

10

**【0092】**

この構成により、他の増幅器1131は、C0/(Cf1～Cf3)のうち選択されたものの和)の比のゲインをかけることができる。Cf1～Cf3は、直列に接続されるスイッチSW1～SW3がオンするにより選択される。すなわち、帰還容量を変化させることができ、ゲインが可変となる構成となっている。

**【0093】**

複数の増幅器112のそれぞれと第2の基準電源パターン108とは、図17に示すように、第2の領域R2において電気的に接続されている。

**【0094】**

複数の他の増幅器113のそれぞれと第3の基準電源パターン114とは、第3の領域R3において電気的に接続されている。第3の領域R3は、画素配列PAと第1の領域R1との間に配された領域である。

20

**【0095】**

なお、図19に示すように、複数の他の増幅器113のそれぞれと第1の基準電源パターン107とが、第1の領域R1において電気的に接続されていてもよい。

**【図面の簡単な説明】****【0096】**

【図1】本発明の第1実施形態に係る撮像装置1の概略構成図。

【図2】本発明の第1実施形態に係る撮像装置1の回路構成例を示す図。

30

【図3】図2を簡略化した回路図。

【図4】本発明の第1実施形態に係る撮像装置1の動作を示すタイミングチャート。

【図5】本発明の第1実施形態の変形例に係る撮像装置1aの概略構成図。

【図6】本発明の第1実施形態の別の変形例に係る撮像装置1bの概略構成図。

【図7】第1の保持容量及び第2の保持容量の断面構成例を示す断面図(変形例)。

【図8】第1の保持容量及び第2の保持容量のレイアウト構成例を示す図(変形例)

【図9】保持容量の断面図(変形例)。

【図10】保持容量の断面図(変形例)。

【図11】第1実施形態に係る撮像装置を適用した撮像システムの構成図。

【図12】本発明の第2実施形態に係る撮像装置のレイアウト構成例を示す図。

40

【図13】保持容量のレイアウト構成例を示す図(変形例)。

【図14】本発明の第3実施形態に係る撮像装置の構成図。

【図15】本発明の第3実施形態に係る撮像装置の回路構成例を示す図。

【図16】本発明の第3実施形態に係る撮像装置の動作を示すタイミングチャート。

【図17】本発明の第4実施形態に係る撮像装置の構成図。

【図18】本発明の第4実施形態に係る撮像装置の回路構成例を示す図。

【図19】本発明の第4実施形態の変形例に係る撮像装置の構成図。

【図20】本発明の課題を説明するための図。

【図21】背景技術を説明するための図。

【図22】背景技術を説明するための図。

50

## 【符号の説明】

【0097】

1, 1a, 1b 撮像装置

90 撮像システム

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(72)発明者 領木 達也

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 小泉 徹

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 小倉 正徳

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 石坂 博明

(56)参考文献 特開平11-191891(JP,A)

特開2005-079942(JP,A)

特開2002-151672(JP,A)

特許第3536517(JP,B2)

特開2001-045375(JP,A)

特開2004-153682(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/339、27/14、

27/144-27/148、29/762

H04N 5/30-5/378