(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4832185号

(P4832185)

(45) 発行日 平成23年12月7日(2011.12.7)

(24) 登録日 平成23年9月30日(2011.9.30)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| H05K 3/20    | (2006.01) |

| H05K 3/28    | (2006.01) |

| H01L 21/336  | (2006.01) |

| H01L 29/786  | (2006.01) |

| H01L 21/3205 | (2006.01) |

| HO5K 3/20    | B         |

| HO5K 3/28    | F         |

| HO1L 29/786  | 627D      |

| HO1L 21/3205 | B         |

請求項の数 6 (全 28 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2006-179052 (P2006-179052) |

| (22) 出願日     | 平成18年6月29日 (2006.6.29)       |

| (65) 公開番号    | 特開2007-43118 (P2007-43118A)  |

| (43) 公開日     | 平成19年2月15日 (2007.2.15)       |

| 審査請求日        | 平成21年6月12日 (2009.6.12)       |

| (31) 優先権主張番号 | 特願2005-200756 (P2005-200756) |

| (32) 優先日     | 平成17年7月8日 (2005.7.8)         |

| (33) 優先権主張国  | 日本国 (JP)                     |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 丸山 純矢<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 青木 智幸<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

審査官 西村 泰英

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板上に、導電性を示すパターンを形成し、

前記導電性を示すパターンの曲面形状を有する表面上に、電解めつき処理により導電膜を形成し、

前記導電膜に基板を貼り付け、

前記第1の基板及び前記導電性を示すパターンを分離することにより、表面が前記曲面形状を有する前記導電膜を前記基板上に設け、

第2の基板上に設けられたICチップ上に、前記ICチップと電気的に接続する導電性樹脂を形成し、

前記導電性樹脂の表面と、前記導電膜の前記曲面形状を有する表面とを接触させることにより、前記導電性樹脂を介して、前記導電膜と前記ICチップとを電気的に接続することを特徴とする半導体装置の作製方法。

## 【請求項 2】

請求項1において、

前記導電膜と前記ICチップとを電気的に接続した後に、前記基板を前記導電膜から除去することを特徴とする半導体装置の作製方法。

## 【請求項 3】

請求項1又は請求項2において、

液滴を微小径の開いた細管から吐出する方法、又は、粘性を有する材料あるいは液滴を

細管から乾燥気体を用いて押し出す方法によって、前記導電性を示すパターンを前記第1の基板上に形成することを特徴とする半導体装置の作製方法。

**【請求項4】**

請求項1乃至請求項3のいずれか一項において、

前記導電性を示すパターンは、断面形状が、弓形、又は、部分的に弧を描いた形状であることを特徴とする半導体装置の作製方法。

**【請求項5】**

請求項1乃至請求項4のいずれか一項において、

前記導電性を示すパターンは、Fe、Al、Cu、Ag、Ni、W、Ti、Mg、Nb、又はSnを含むことを特徴とする半導体装置の作製方法。

10

**【請求項6】**

請求項1乃至請求項5のいずれか一項において、

前記導電膜は、AgとAuとの合金、CuとAuとの合金、NiとAuとの合金、CdとAuとの合金、CoとAuとの合金、Cu、Ni、Sn、Pb、Cr、Au、Ag、Rh、Co、又はCdを含むことを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、様々な形状を有する配線基板を作製するための方法及び当該配線基板を利用した半導体装置の作製方法に関する。

20

**【背景技術】**

**【0002】**

近年、有価証券、商品の管理など、自動認識が必要なあらゆる分野を対象に、非接触でデータの授受が行えるRFID (Radio Frequency Identification) 搭載カードや、RFID搭載タグの必要性が高まっている。RFIDを搭載したカードは、データの授受を行う際に使用する周波数帯に適応した形状のアンテナを介して、外部の機器と非接触でデータの読み書きをするようになされる。また、RFIDを搭載したカードは、磁気記録方式によりデータを記録する磁気カードに比べて記憶容量が大きく、セキュリティ性に優れているため、最近では様々な分野への利用できる形態が提案されている。

30

**【0003】**

一般的に、RFIDなどの半導体装置はアンテナとICチップとから構成され、アンテナはICチップ上に直接形成される場合と、ICチップとは別に形成され、その後ICチップと接続される場合がある。後者の場合、一般的にアンテナパターンはリジッド基板と呼ばれるPCB (Print Circuit Board、ガラスエポキシ樹脂) 基板や、フレキ基板と呼ばれるFPC (Flexible Print Circuit、ポリイミド樹脂) 基板上に形成されている。また、従来、アンテナパターンは、PCB基板やFPC基板上に銅箔を形成し、エッチング法やフォトリソグラフィ法にて銅箔をパターンングすることにより形成している(例えば、特許文献1、特許文献2)。

**【0004】**

40

また、半導体素子の微細な配線を形成するために導電性材料からなる配線パターン上に電解めっき処理により形成された電解めっき膜を配線として利用する方法が知られている(例えば、特許文献3)。

**【特許文献1】特開2001-284521号公報**

**【特許文献2】特開2004-282487号公報**

**【特許文献3】特開2004-87597号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0005】**

しかし、前述のように銅箔をパターンングすることによりアンテナを形成する場合、パ

50

ターンとして残らない領域の銅は廃棄物として処理する必要があり、原材料の利用効率が悪い。また、パターンとして残らない領域の銅は廃棄物として処理しなければならないため、環境に優しいとはいえない。

#### 【0006】

また、例えば、フォトリソグラフィ法によって銅箔パターンを加工する場合、フォトレジスト、露光装置、現像装置、銅のエッチング処理設備、フォトレジストの除去装置、乾燥装置等が必要である。従って、アンテナを製造するために高額の設備投資が必要となり、アンテナの製造コストの低下を妨げている。

#### 【0007】

また、従来のように電解めっき処理により微細な配線を作製する場合、配線パターンと電解めっき膜とを配線として用いているが、電解めっき膜のみを配線として利用して配線パターン部分を再利用できれば、配線パターンである導電材料の使用量の削減につながり、半導体素子の低コスト化及び作製工程における環境への悪影響を少なくすることが可能であると考えられる。10

#### 【0008】

上記課題を鑑み、本発明は、低成本で環境への悪影響が少ない配線基板の形成方法及び半導体装置の作製方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0009】

本発明の配線基板の作製方法は、基板上に導電性を示すパターンを形成し、前記パターン上に電解めっき処理により導電膜を形成し、前記パターンと前記導電膜とを分離することを特徴とする。20

#### 【0010】

本発明の配線基板の作製方法は、基板上に導電性を示すパターンを形成し、前記パターン上に電解めっき処理により導電膜を形成し、前記導電膜上に基体を貼り付け、前記基体を前記基板から剥がすことにより、前記パターンと前記導電膜とを分離することを特徴とする。

#### 【0011】

本発明の半導体装置の作製方法は、第1の基板上に導電性を示すパターンを形成し、前記パターン上に電解めっき処理により導電膜を形成し、前記パターンと前記導電膜とを分離し、第2の基板上に少なくとも1つの薄膜トランジスタを有するICチップを形成し、前記導電膜とICチップとを電気的に接続することを特徴とする。30

#### 【0012】

本発明の半導体装置の作製方法は、第1の基板上に導電性を示すパターンを形成し、前記パターン上に電解めっき処理により導電膜を形成し、前記パターンと前記導電膜とを分離し、第2の基板上に少なくとも1つの薄膜トランジスタを有するICチップを形成し、前記導電膜とICチップとを電気的に接続し、前記第2の基板と前記ICチップとを剥離し、前記ICチップと前記導電膜とを第3の基板で覆うことを特徴とする。

#### 【0013】

前記第3の基板は、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニル、繊維質な材料からなる紙、又は帯電防止フィルムであることを特徴とする。40

#### 【0014】

前記第3の基板は、ポリエステル、ポリアミド、無機蒸着フィルム、又は紙類及びアクリル系合成樹脂、又はエポキシ系合成樹脂からなる接着性合成樹脂との積層フィルムであることを特徴とする。

#### 【0015】

前記パターンは、鉄(Fe)、アルミニウム(Al)、銅(Cu)、銀(Ag)、ニッケル(Ni)、タンクステン(W)、チタン(Ti)、マグネシウム(Mg)、ニオブ(Nb)、若しくは錫(Sn)を含む材料であることを特徴とする。

#### 【0016】

50

前記導電膜は、銀(Ag)と金(Au)との合金、銅(Cu)と金(Au)との合金、ニッケル(Ni)と金(Au)との合金、カドミウム(Cd)と金(Au)との合金、コバルト(Co)と金(Au)との合金、銅(Cu)、ニッケル(Ni)、錫(Sn)、鉛(Pb)、クロム(Cr)、金(Au)、銀(Ag)、ロジウム(Rh)、カドミウム(Cd)、又はコバルト(Co)を含むことを特徴とする。

#### 【発明の効果】

#### 【0017】

本発明の配線基板の作製方法を用いることで、多数回の複雑な工程を行うことなく、簡易なプロセスで、低成本に配線基板を作製することが可能である。さらに、本発明の作製方法において、配線基板を形成するための導電性樹脂パターン及び電解めっき浴の再利用が可能であり、環境への悪影響を低減し、低成本で配線基板を作製することができる。

10

#### 【0018】

本発明により作製された配線基板を用いることにより、多数回の複雑な工程を行うことなく、簡易なプロセスで、低成本な半導体装置を作成することができる。

#### 【発明を実施するための最良の形態】

#### 【0019】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々なに変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

20

#### 【0020】

#### (実施の形態1)

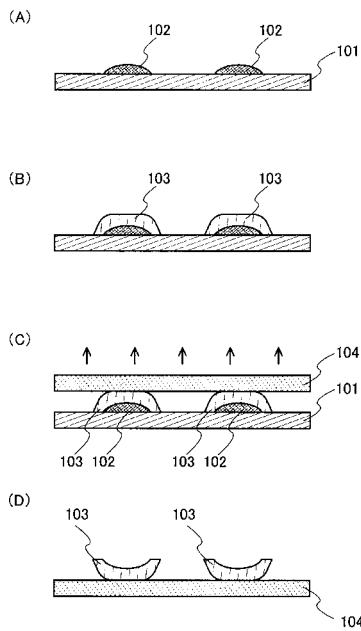

本実施例では、電解めっき処理による配線基板の形成方法について説明する。図1は、本実施の形態における配線基板の作製工程の断面図である。

#### 【0021】

まず、図1(A)に示すように、基板101上に導電性材料からなるパターン102を形成する。基板101としては、バリウムホウケイ酸ガラスや、アルミニウムホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板、シリコン基板等を用いることができる。他にも、ポリエチレンテレフタート(PE T)、ポリエチレンナフタート(PE N)、ポリエーテルサルファン(PE S)に代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板を用いることも可能である。

30

#### 【0022】

パターン102は、スクリーン印刷法、真空蒸着法、スパッタ法、ガラス基板全面に導電性材料を形成した後、レーザー光にて不要な部分を除去する方法、インクジェット法に代表される液滴を微小径の開いた細管から吐出する方法、ディスペンス法に代表される粘性を有する材料あるいは液滴を数ミリメートル程度以下の径を持つ細管から乾燥気体にて押し出すことで形成する手法等を用いて形成することができる。また、パターン102の形状を変化させることで様々な形状の導電膜を作製することができる。なお、図1においてパターン102は表面に曲面を有する形状とした。つまり、パターン102の断面形状が弓形となるように形成した。しかし、パターン102の表面及び断面形状はこの形状に限定されない。例えば、断面形状が半円等の部分的に弧を描いた形状であってもよいし、三角形や四角形等の多角形としてもよい。

40

#### 【0023】

パターン102の材料として例えば、鉄(Fe)、アルミニウム(Al)、銅(Cu)、銀(Ag)、ニッケル(Ni)、タンゲステン(W)、チタン(Ti)、マグネシウム(Mg)、ニオブ(Nb)、若しくは錫(Sn)等の単体金属であってもよいし、鉄(Fe)、アルミニウム(Al)、銅(Cu)、銀(Ag)、ニッケル(Ni)、タンゲステン(W)、チタン(Ti)、マグネシウム(Mg)、ニオブ(Nb)、若しくは錫(Sn)

50

)を主成分とし、他の元素を微量に含んだ化合物であってもよい。また、鉄(Fe)、アルミニウム(Al)、銅(Cu)、銀(Ag)、ニッケル(Ni)、タンゲステン(W)、チタン(Ti)、マグネシウム(Mg)、ニオブ(Nb)、若しくは錫(Sn)を主成分とする合金材料であってもよい。また、金属樹脂中に鉄(Fe)、アルミニウム(Al)、銅(Cu)、銀(Ag)、ニッケル(Ni)、タンゲステン(W)、チタン(Ti)、マグネシウム(Mg)、ニオブ(Nb)、又は錫(Sn)が分散された材料を用いてよい。

#### 【0024】

次に、パターン102が形成された基板101を洗浄する。基材表面に付着した油脂類の汚れを除去することを目的として行う処理で、溶剤脱脂法、エマルジョン脱脂法、アルカリ脱脂法、電解脱脂法、又は超音波脱脂法などがあり、これらを適宜繰り返して脱脂洗浄する。

10

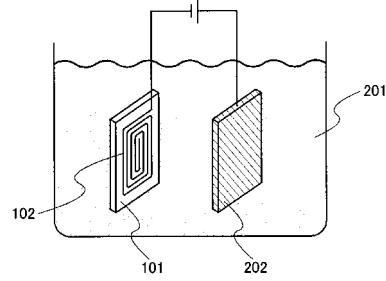

#### 【0025】

次に、洗浄された基板101に対して電解めっき処理を行い、パターン102上に導電膜103を形成する(図1(B)参照)。図2に電解めっき処理のときの模式図を示す。電解めっき処理は、図2に示すように電解めっき浴201中に基板101と金属板202とを浸し、基板101上のパターン102を陰極に、金属板202を陽極としてパターン102と金属板202間に電流を流すことで、パターン102上に当該金属板と同様の導電性を有する導電膜が形成される。金属板として、銅(Cu)、ニッケル(Ni)、錫(Sn)、鉛(Pb)、クロム(Cr)、金(Au)、銀(Ag)、ロジウム(Rh)、コバルト(Co)、若しくはカドミウム(Cd)等の単体金属や、Ag、Cu、Ni、カドミウム(Cd)、若しくはコバルト(Co)等とAuとの合金等を用いることができる。本実施の形態で示した金属板202の材料とパターン102の材料とは、剥がれやすい組み合わせであれば適宜自由に組み合わせて用いることができる。なお、パターン102と金属板202とは、電気的に接続されればどのように接続してもよい。電解めっき終了後、基板101を電解めっき浴より取り出し、純水を用いて基板を洗浄する。

20

#### 【0026】

その後、導電膜103上に転置用基体104を貼り付けて、転置用基体104を基板101から剥がすことで導電膜103とパターン102とを分離する(図1(C)、(D)参照)。つまり、転置用基体104上に導電膜103を転置する。なお、パターン102上に形成された導電膜103の全てを剥がして転置用基体104に転置する必要はなく、必要に応じて導電膜103の一部分をパターン102と分離して転置用基体104に転置してもよい。このようにパターン102と分離した導電膜103を配線基板とよぶ。なお、導電膜103のパターン102と接していた側の表面は、パターン102の導電膜103と接していた側の表面と同様の形状を有している。つまり、導電膜103の断面形状は、パターン102の断面形状と部分的に同じである。転置用基体104として例えば、微粘着はく離テープ、熱はく離テープ、紫外線はく離テープなどを用いることができる。ここでパターン102と分離された導電膜103は、アンテナや素子と素子とを接続する配線などの各種配線として用いることができる。例えば、本実施の形態において作製された導電膜103をICチップと接続することで導電膜103を半導体装置のアンテナとして用いることができる。また、本実施の形態において作製された導電膜103を半導体素子の配線として用いることができる。なお、本実施の形態において、電界めっき処理で導電膜103を形成しているため、基板101と導電膜103とは接着されていない。従って、電界めっき処理の際の金属板202(導電膜103)の材料とパターン102の材料として、剥がれやすい組み合わせの材料を用いることで、パターン102と導電膜103とを簡単に剥がすことができる。

30

40

#### 【0027】

本実施の形態において、電解めっき処理という容易な工程で配線基板を形成することができる。さらに、パターンの形状を変えることで容易に様々な形状の配線基板を形成することができる。例えば、アンテナとして用いる場合、ダイポール、輪状(例えば、ループ

50

アンテナ)、直方体で平坦なもの(例えば、パッチアンテナ)など様々な形状のアンテナを形成することができる。また、本実施の形態の作製方法において、配線基板を形成するための、基板101及びその上に形成されたパターン102並びに電解めっき浴201の再利用が可能であるので、低コストで配線基板を作製することができる。

#### 【0028】

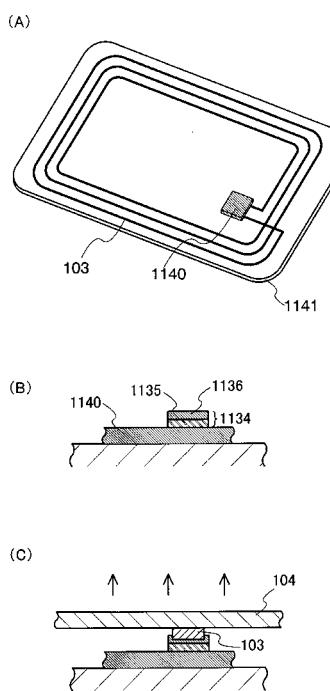

##### (実施の形態2)

本実施の形態では、実施の形態1により作製された配線基板とICチップとを接続する方法の一形態について説明する。本実施の形態では、図3(A)に示すように、基板1141上に複数の薄膜トランジスタ群を有するICチップ1140と導電膜103とが設けられた半導体装置について説明する。なお、導電膜とICチップとを接続することにより、導電膜103は、ICチップ1140に含まれる少なくとも1つの薄膜トランジスタと電気的に接続する。また、当該半導体装置は、導電膜103を介して、非接触でICチップと外部の機器(リーダ/ライタ)との間でデータのやりとりを行うことができる。なお、本明細書において、無線通信によりデータを交信することができる素子を半導体装置と呼ぶ。このような半導体装置は、ICタグ、IDタグ、RF(Radio Frequency)タグ、RFID(Radio Frequency Identification)、無線タグ、電子タグ、無線プロセッサ、無線メモリ、無線チップ等と呼ばれることがある。

#### 【0029】

まず、図3(B)に示すようにICチップ1140上に、ICチップ1140と導電膜103とを接合するためのバンプ1134を形成する。バンプ1134は、スクリーン印刷法、スパッタ法、ガラス基板全面に導電性材料を形成した後、レーザー光にて不要な部分を除去する方法、インクジェット法に代表される液滴を微小径の開いた細管から空気流にて吐出する方法、ディスペンス法に代表される粘性を有する材料あるいは液滴を数ミリメートル程度以下の径を持つ細管から乾燥気体にて押し出すことで形成する手法等を用いて形成することができる。本実施の形態では、スクリーン印刷法で形成する場合の形成方法を説明する。

#### 【0030】

まず、印刷版上に導電性樹脂1135を乗せ、スクレッパによりバンプのパターン形成部に開口された印刷版の開口部および全面に導電性樹脂(導電性ペースト)1135を塗布する。ここで、印刷版として例えばメッシュ数#40~#400を使用し、導電性樹脂として例えば銀を含む樹脂(日本アチソン(株)、品名Electrodag427SS、バインダーとしてポリエステル系樹脂使用)を用いることができる。ここで、メッシュ数は1インチあたりのライン数をあらわしている。また、導電性樹脂として銀を含む樹脂を用いる場合、スクレッパと印刷版は非接触の位置で、スクレッパ移動速度3~300mm/secとして銀を含む樹脂を塗布するとよい。

#### 【0031】

次に、スキージを用いて導電性樹脂1135を基材に塗布する。このとき、スキージは印刷版に接触させ、押し込み圧力は圧縮空気を用いて0.14~0.175MPaとし、移動速度3~300mm/secとして塗布するとよい。印刷後、樹脂の凹凸を取る為に印刷物のレベルリングを例えば5分間行い、その後、75~120で15分間~45分間焼成することによりバンプが形成される。焼成は間接加熱雰囲気で行うとよい。

#### 【0032】

続いて、導電性樹脂1135上に異方性導電性樹脂1136をスクリーン印刷により形成する。例えば、スクリーン印刷版としてメッシュ数#80~#165を使用し、印刷版上に異方性導電性樹脂1136として例えばACP((株)スリーボンド製、3373C)を乗せ、スクレッパによりバンプのパターン形成部に相当する印刷版開口部および全面に異方性導電性樹脂1136を塗布する。その際、スクレッパと印刷版の距離は非接触で、スクレッパ移動速度は3~300mm/secで行うとよい。次に、スキージで異方性導電性樹脂を印刷版開口部より基材に塗布する。スキージは印刷版に接触させ、押し込み

10

20

30

40

50

圧力は圧縮空気を用いて0.14～0.175 MPaとし、速度30～300 mm/sで行うとよい。印刷後、120～160で5分間焼成する。焼成は間接加熱雰囲気で行うとよい。

#### 【0033】

この後、実施の形態1において作製した転置用基体104によって保持されている導電膜103とICチップ1141とを貼り合わせる(図3(C)参照)。本実施の形態では、異方性導電性樹脂が140になるような状態で基板101に圧力147Nを加え、20秒間保持することにより、ICチップ1141と導電膜103を接合する。

#### 【0034】

この後、転置用基体104をICチップ1140から剥がすことにより、導電膜103と転置用基体104とを剥離することができる。その後、導電膜103上にポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、繊維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)と接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルムなどの保護フィルムを形成する。それにより、図3(A)に示す半導体装置を作製することができる。

#### 【0035】

実施の形態1により作製された配線基板を半導体装置に用いることで、多数回の複雑な工程を行うことなく、簡易なプロセスで、低コストな半導体装置を作成することができる。なお、スクリーン印刷法で導電性樹脂又は異方性導電性樹脂を形成する条件は本実施の形態で示した条件に限定されず、所望の導電性樹脂又は異方性導電性樹脂が形成されればどのような条件で行ってもよい。なお、本実施の形態は他の実施の形態と自由に組み合わせて行うことができる。つまり、他の実施の形態で示した材料や形成方法は、本実施の形態でも自由に組み合わせて利用することができる。

#### 【0036】

##### (実施の形態3)

本実施の形態では、上記実施の形態で示した導電膜を半導体装置に利用する一形態について図面を用いて詳しく説明する。より詳しくは、少なくとも1つの薄膜トランジスタ及び少なくとも1つの記憶素子を有するICチップとアンテナとを有する半導体装置の作製方法について図面を参照して説明する。なお、本実施の形態において薄膜トランジスタは、非同期カウンタ、電源回路等の半導体装置を構成する各回路を構成する素子である。

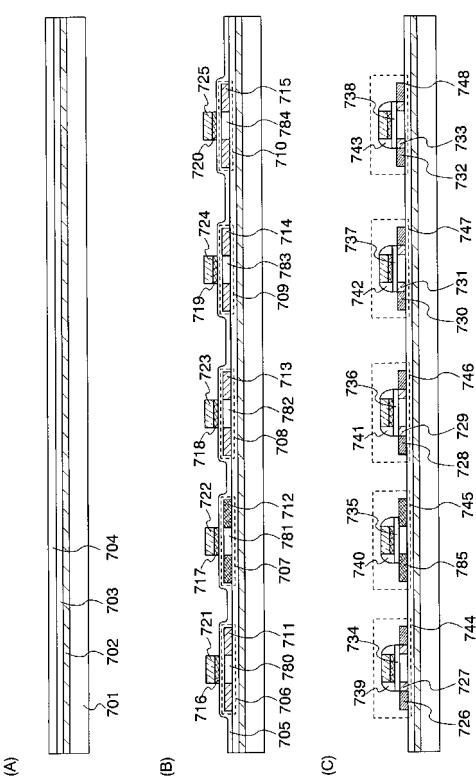

#### 【0037】

基板701(基体ともよぶ)の一表面に、剥離層702を形成する(図4(A)参照)。基板701は、絶縁表面を有する。基板701としては、バリウムホウケイ酸ガラスや、アルミニノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板、シリコン基板、またはステンレスを含む金属基板等を用いることができる。他にも、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)に代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板を用いることも可能である。基板701がガラスからなる場合は、その面積や形状に大きな制限はない。そのため、基板701として、例えば、1辺が1メートル以上であって、矩形状のものを用いれば、生産性を格段に向上させることができる。また、基板701がプラスチックからなる場合、作製工程の処理温度に耐えうる耐熱性のプラスチックを用いる必要がある。なお、好適には、ガラスからなる基板701上に少なくとも1つの薄膜トランジスタを設けた後、当該薄膜トランジスタを剥離して、プラスチックからなる基板上に設けてよい。

#### 【0038】

なお、本工程では、剥離層702は、基板701の全面に設けているが、必要に応じて、基板701の全面に剥離層を設けた後に、フォトリソグラフィ法によりパターニングして、選択的に設けてよい。また、基板701に接するように剥離層702を形成しているが、必要に応じて、基板701に接するように下地となる絶縁層を形成し、当該絶縁層

10

20

30

40

50

に接するように剥離層 702 を形成してもよい。

**【0039】**

剥離層 702 は、スパッタリング法やプラズマ CVD 法等により、タンゲステン (W) 、モリブデン (Mo) 、チタン (Ti) 、タンタル (Ta) 、ニオブ (Nb) 、ニッケル (Ni) 、コバルト (Co) 、ジルコニウム (Zr) 、亜鉛 (Zn) 、ルテニウム (Ru) 、ロジウム (Rh) 、パラジウム (Pd) 、オスミウム (Os) 、イリジウム (Ir) 、珪素 (Si) 等から選択された元素または前記元素を主成分とする合金材料若しくは化合物材料からなる層を、単層又は積層して形成する。珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれの場合でもよい。

**【0040】**

次に、剥離層 702 を覆うように、下地となる絶縁層 703 を形成する。絶縁層 703 は、スパッタリング法やプラズマ CVD 法等により、珪素の酸化物又は珪素の窒化物を含む層を、単層又は積層で形成する。珪素の酸化物材料とは、珪素 (Si) と酸素 (O) を含む物質であり、酸化珪素、窒素を含む酸化珪素等が該当する。珪素の窒化物材料とは、珪素と窒素 (N) を含む物質であり、窒化珪素、酸素を含む窒化珪素等が該当する。下地となる絶縁層は、基板 701 からの不純物の侵入を防止するプロッキング膜として機能する。

10

**【0041】**

次に、絶縁層 703 上に、非晶質半導体層 704 を形成する。非晶質半導体層 704 は、スパッタリング法、LPCVD 法、プラズマ CVD 法等により形成する。続いて、非晶質半導体層 704 をレーザ結晶化法、RTA 又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法、又は結晶化を助長する金属元素を用いる熱結晶化法とレーザ結晶化法を組み合わせた方法等により結晶化して、結晶質半導体層を形成する。その後、得られた結晶質半導体層を所望の形状にパターニングして、結晶質半導体層 706 ~ 710 を形成する(図 4 (B) 参照)。

20

**【0042】**

ここで、結晶質半導体層 706 ~ 710 の作成工程の一例について以下に説明する。まず、プラズマ CVD 法を用いて、非晶質半導体層 704 を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体層上に保持させた後、非晶質半導体層に脱水素化の処理(500、1 時間)と、熱結晶化の処理(550、4 時間)を行って結晶質半導体層を形成する。その後、必要に応じてレーザ光を照射し、フォトリソグラフィ法を用いたパターニング処理によって結晶質半導体層 706 ~ 710 を形成する。

30

**【0043】**

非晶質半導体膜の結晶化にレーザ結晶化法を用いる場合、連続発振型のレーザビーム(CW レーザビーム) やパルス発振型のレーザビーム(パルスレーザビーム) を用いることができる。ここで用いることができるレーザビームは、Ar レーザ、Kr レーザ、エキシマレーザなどの気体レーザ、単結晶の YAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶(セラミック)の YAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub> に、ドーパントとして Nd、Yb、Cr、Ti、Ho、Er、Tm、Ta のうち 1 種または複数種添加されているものを媒質とするレーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti : サファイアレーザ、銅蒸気レーザまたは金蒸気レーザのうち一種または複数種から発振されるものを用いることができる。このようなレーザビームの基本波、及びこれらの基本波の第 2 高調波から第 4 高調波のレーザビームを照射することで、大粒径の結晶を得ることができる。例えば、Nd : YVO<sub>4</sub> レーザ(基本波 1064 nm) の第 2 高調波(532 nm) や第 3 高調波(355 nm) を用いることができる。このときレーザのエネルギー密度は 0.01 ~ 100 MW/cm<sup>2</sup> 程度(好ましくは 0.1 ~ 10 MW/cm<sup>2</sup>) が必要である。そして、走査速度を 10 ~ 2000 cm/sec 程度として照射する。

40

**【0044】**

50

なお、単結晶のYAG、 $\text{YVO}_4$ 、フォルステライト( $\text{Mg}_2\text{SiO}_4$ )、 $\text{YAlO}_3$ 、 $\text{GdVO}_4$ 、若しくは多結晶(セラミック)のYAG、 $\text{Y}_2\text{O}_3$ 、 $\text{YVO}_4$ 、 $\text{YAlO}_3$ 、 $\text{GdVO}_4$ に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、Arイオンレーザ、またはTi:サファイアレーザは、連続発振をさせることができ、Qスイッチ動作やモード同期などを行うことによって10MHz以上の発振周波数でパルス発振をさせることも可能である。10MHz以上の発振周波数でレーザビームを発振させると、半導体膜がレーザによって溶融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波数が低いパルスレーザを用いる場合と異なり、半導体膜中において固液界面を連続的に移動させることができ、走査方向に向かって連続的に成長した結晶粒を得ることができる。連続発振レーザ若しくは10MHz以上の周波数で発振するレーザビームを照射することで、結晶化された半導体膜の表面を平坦なものとすることができる。それにより、後に形成するゲート絶縁膜を薄膜化することも可能であり、また、ゲート絶縁膜の耐圧を向上させることに寄与することができる。

#### 【0045】

媒質としてセラミック(多結晶)を用いると、短時間かつ低コストで自由な形状に媒質を形成することが可能である。単結晶を用いる場合、通常、直径数mm、長さ数十mmの円柱状の媒質が用いられているが、セラミックを用いる場合はさらに大きいものを作ることが可能である。

#### 【0046】

発光に直接寄与する媒質中のNd、Ybなどのドーパントの濃度は、単結晶中でも多結晶中でも大きくは変えられないため、濃度を増加させることによるレーザの出力向上にはある程度限界がある。しかしながら、セラミックの場合、単結晶と比較して媒質の大きさを著しく大きくすることができ、大幅な出力向上が期待できる。

#### 【0047】

さらに、セラミックの場合では、平行六面体形状や立方体形状の媒質を容易に形成することが可能である。このような形状の媒質を用いて、発振光を媒質の内部でジグザグに進行させると、発振光路を長くとることができる。そのため、增幅が大きくなり、大出力で発振させることができ。また、このような形状の媒質から射出されるレーザビームは射出時の断面形状が四角形状であるため、丸状のビームと比較すると、線状ビームに整形するのに有利である。このように射出されたレーザビームを、光学系を用いて整形することによって、短辺の長さ1mm以下、長辺の長さ数mm~数mの線状ビームを容易に得ることが可能となる。また、励起光を媒質に均一に照射することにより、線状ビームは長辺方向にエネルギー分布の均一なものとなる。

#### 【0048】

この線状ビームを半導体膜に照射することによって、半導体膜の全面をより均一にアニールすることができる。線状ビームの両端まで均一なアニールが必要な場合は、その両端にスリットを配置し、エネルギーの減衰部を遮光するなどの工夫が必要となる。このようにして得られた強度が均一な線状ビームを用いて結晶化された半導体膜を用いて電子機器を作製すると、その電子機器の特性は、良好かつ均一である。

#### 【0049】

なお、結晶化を助長する金属元素を用いて非晶質半導体層の結晶化を行うと、低温で短時間の結晶化が可能となるうえ、結晶の方向が揃うという利点がある一方、金属元素が結晶質半導体層に残存するためにオフ電流が上昇し、特性が安定しないという欠点がある。そこで、結晶質半導体層上に、ゲッタリングサイトとして機能する非晶質半導体層を形成するとよい。ゲッタリングサイトとなる非晶質半導体層には、リンやアルゴンの不純物元素を含有させる必要があるため、好適には、アルゴンを高濃度に含有させることができ、スパッタリング法で形成するとよい。その後、加熱処理(RTA法やファーネスアニール炉を用いた熱アニール等)を行って、非晶質半導体層中に金属元素を拡散させ、続いて、当該金属元素を含む非晶質半導体層を除去する。そうすると、結晶質半導体層中の金属元

10

20

30

40

50

素の含有量を低減又は除去することができる。

#### 【0050】

次に、結晶質半導体層706～710を覆うゲート絶縁層705を形成する。ゲート絶縁層705は、プラズマCVD法やスパッタリング法により、珪素の酸化物又は珪素の窒化物を含む層を、単層又は積層して形成する。

#### 【0051】

なお、ゲート絶縁層705を形成する前に、結晶質半導体膜706～710の表面に高密度プラズマ処理によって酸化膜または窒化膜を形成してもよい。例えば、結晶質半導体膜706～710としてSiを用いた場合、半導体膜表面に、酸化珪素(SiO<sub>x</sub>)または窒化珪素(SiNx)が形成される。また、高密度プラズマ処理により半導体膜を酸化させた後に、再度プラズマ処理を行うことによって窒化させてもよい。この場合、半導体膜に接して酸化珪素(SiO<sub>x</sub>)が形成され、当該酸化珪素の表面に窒化酸化珪素(SiNxOy)(x > y)が形成される。10

#### 【0052】

なお、プラズマ処理により半導体膜を酸化する場合には、酸素雰囲気下(例えば、酸素(O<sub>2</sub>)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下または酸素と水素(H<sub>2</sub>)と希ガス雰囲気下または一酸化二窒素と希ガス雰囲気下)でプラズマ処理を行う。一方、プラズマ処理により半導体膜を窒化する場合には、窒素雰囲気下(例えば、窒素(N<sub>2</sub>)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下または窒素と水素と希ガス雰囲気下またはNH<sub>3</sub>と希ガス雰囲気下)でプラズマ処理を行う。希ガスとしては、例えばArを用いることができる。また、ArとKrを混合したガスを用いてもよい。そのため、プラズマ処理により形成された絶縁膜は、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでいる。例えば、Arを用いた場合にはプラズマ処理により形成される絶縁膜にはArが含まれている。この場合のプラズマの励起は、マイクロ波の導入により行うと、低電子温度で高密度のプラズマを生成することができる。この高密度プラズマで生成された酸素ラジカル(OHラジカルを含む場合もある)や窒素ラジカル(NHラジカルを含む場合もある)によって、半導体膜の表面を酸化又は窒化することができる。20

#### 【0053】

また、高密度プラズマ処理は、上記ガスの雰囲気中において、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上であり、プラズマの電子温度が1.5eV以下で行う。より詳しくいうと、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下で、プラズマの電子温度が0.5eV以上1.5eV以下で行う。プラズマの電子密度が高密度であり、基板上に形成された被処理物(ここでは、半導体膜)付近での電子温度が低いため、被処理物に対するプラズマによる損傷を防止することができる。また、プラズマの電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上と高密度であるため、プラズマ処理を用いて、被照射物を酸化または窒化することによって形成される酸化膜または窒化膜は、CVD法やスパッタ法等により形成された膜と比較して膜厚等が均一性に優れ、且つ緻密な膜を形成することができる。また、プラズマの電子温度が1.5eV以下と低いため、従来のプラズマ処理や熱酸化法と比較して低温度で酸化または窒化処理を行うことができる。たとえば、ガラス基板の歪点よりも100度以上低い温度でプラズマ処理を行っても十分に酸化または窒化処理を行うことができる。なお、プラズマを形成するための周波数としては、マイクロ波(2.45GHz)等の高周波を用いることができる。なお、以下に特に断らない場合は、プラズマ処理として上記条件を用いて行うものとする。3040

#### 【0054】

このような高密度プラズマを用いた処理により、1～20nm、代表的には5～10nmの絶縁膜が半導体膜に形成される。この場合の反応は、固相反応であるため、当該絶縁膜と半導体膜との界面準位密度はきわめて低くすることができる。このような、高密度プラズマ処理は、半導体膜(結晶性シリコン、或いは多結晶シリコン)を直接酸化(若しくは窒化)するため、形成される絶縁膜の厚さは理想的には、ばらつきをきわめて小さくす50

ることができる。加えて、結晶性シリコンの結晶粒界でも酸化が強くされることはないとため、非常に好ましい状態となる。すなわち、ここで示す高密度プラズマ処理で半導体膜の表面を固相酸化することにより、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶縁膜を形成することができる。

#### 【0055】

なお、半導体膜をプラズマ処理して酸化または窒化することによって形成された絶縁膜の膜厚が十分である場合には、ゲート絶縁層705は必ずしも設ける必要はなく、プラズマ処理により半導体膜表面に形成された当該絶縁膜をゲート絶縁膜として用いることも可能である。さらに、ゲート絶縁膜は、高密度プラズマ処理によって形成される絶縁膜のみを用いても良いし、それにプラズマや熱反応を利用したCVD法で酸化シリコン、酸窒化シリコン、窒化シリコンなどの絶縁膜を堆積し、積層させても良い。いずれにしても、高密度プラズマで形成した絶縁膜をゲート絶縁膜の一部又は全部に含んで形成されるトランジスタは、特性のばらつきを小さくすることができる。10

#### 【0056】

また、半導体膜の結晶化の際に半導体膜に対し、連続発振レーザ若しくは10MHz以上の周波数で発振するレーザビームを照射しながら一方向に走査して結晶化させて得られた半導体膜は、そのビームの走査方向に結晶が成長する特性がある。その走査方向をチャネル長方向（チャネル形成領域が形成されたときにキャリアが流れる方向）に合わせてトランジスタを配置し、上記高密度プラズマにより形成されたゲート絶縁層を組み合わせることで、特性ばらつきが小さく、しかも電界効果移動度が高いトランジスタ（TFT）を得ることができる。20

#### 【0057】

次に、ゲート絶縁層705上に、第1の導電層と第2の導電層を積層して形成する。第1の導電層は、プラズマCVD法やスパッタリング法により、20~100nmの厚さで形成する。第2の導電層は、100nm~400nmの厚さで形成する。第1の導電層と第2の導電層は、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、等から選択された元素又はこれらの元素を主成分とする合金材料若しくは化合物材料で形成する。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成する。第1の導電層と第2の導電層の組み合わせの例を挙げると、窒化タンタルからなる層とタンゲステンからなる層、窒化タンゲステンからなる層とタンゲステンからなる層、窒化モリブデンからなる層とモリブデンからなる層等が挙げられる。タンゲステンや窒化タンタルは、耐熱性が高いため、第1の導電層と第2の導電層を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2層構造ではなく、3層構造の場合は、モリブデンからなる層とアルミニウムからなる層とモリブデンからなる層の積層構造を採用するとよい。30

#### 【0058】

次に、フォトリソグラフィ法により、レジストからなるマスクを形成し、ゲート電極とゲート線を形成するためのエッチング処理を行って、ゲート電極として機能する導電層716~725を形成する。40

#### 【0059】

次に、フォトリソグラフィ法により、レジストからなるマスクを形成し、結晶質半導体層706、708~710に、イオンドープ法又はイオン注入法により、N型を付与する不純物元素を低濃度に添加して、不純物領域711、713~715とチャネル形成領域780、782~784を形成する。N型を付与する不純物元素は、15族に属する元素を用いれば良く、例えばリン(P)、砒素(As)を用いる。

#### 【0060】

次に、フォトリソグラフィ法により、レジストからなるマスクを形成し、結晶質半導体層707に、P型を付与する不純物元素を添加して、不純物領域712とチャネル形成領域781を形成する。P型を付与する不純物元素は、例えばボロン(B)を用いる。50

## 【0061】

次に、ゲート絶縁層705と導電層716～725を覆うように、絶縁層を形成する。絶縁層は、プラズマCVD法やスパッタリング法により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む層や、有機樹脂などの有機材料を含む層を、単層又は積層して形成する。次に、絶縁層を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、導電層716～725の側面に接する絶縁層（サイドウォールともよぶ）739～743を形成する（図4（C）参照）。また、絶縁層739～743の作成とともに、絶縁層705をエッチングして、絶縁層734～738を形成する。絶縁層739～743は、後にLDD（Lightly Doped drain）領域を形成する際のドーピング用のマスクとして用いる。

10

## 【0062】

次に、フォトリソグラフィ法により、レジストからなるマスクを形成し、そのレジストマスクと絶縁層739～743をマスクとして用いて、結晶質半導体層706、708～710にN型を付与する不純物元素を添加して、第1の不純物領域（LDD領域ともよぶ）727、729、731、733と、第2の不純物領域726、728、730、732とを形成する。第1の不純物領域727、729、731、733の不純物元素の濃度は、第2の不純物領域726、728、730、732の不純物元素の濃度よりも低い。上記工程を経て、Nチャネル型の薄膜トランジスタ744、746～748と、Pチャネル型の薄膜トランジスタ745が完成する。

20

## 【0063】

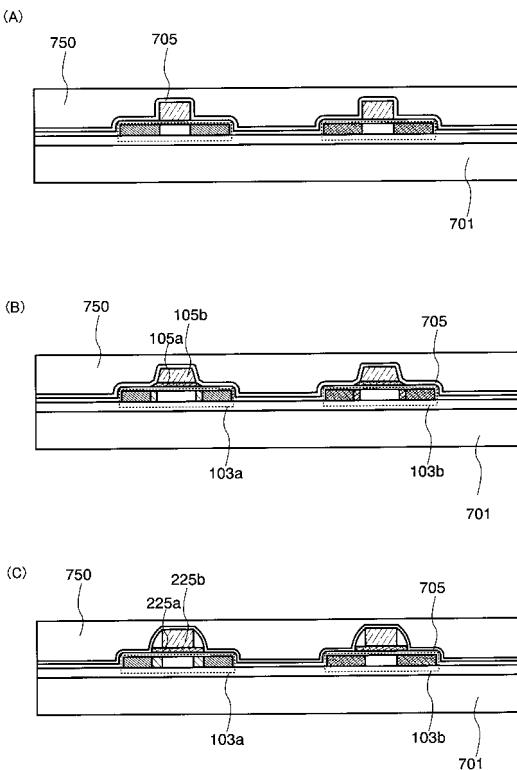

なお、薄膜トランジスタの構造は上記に記載に制約されない。シングルドレイン構造、オフセット構造、LDD構造、GOLD（Gate Overlapped Lightly Doped drain）構造等のどのような構造でもよい。例えば、全てのトランジスタにLDD領域を設けた構成としてもよいし、全てのトランジスタにLDD領域およびサイドウォールを設けない構造（図10（A）参照）とすることも可能である。また、薄膜トランジスタの構造として上述した構造に限られず、チャネル形成領域が1つ形成されるシングルゲート構造でもよいし、2つ形成されるダブルゲート構造または3つ形成されるトリプルゲート構造等の複数のチャネル形成領域を有するマルチゲート構造のTFTを用いることもできる。また、ボトムゲート型（逆スタガ型）としてもよいし、チャネル形成領域の上下にゲート絶縁膜を介して配置された2つのゲート電極を有するデュアルゲート型としてもよい。また、ゲート電極を積層構造で設けてもよい。ゲート電極を積層で設ける場合、図10（B）に示すようにゲート電極下方に形成される第1の導電膜105aと当該第1の導電膜105a上に形成される第2の導電膜105bで設け、当該第1の導電膜をテーパー状で形成し、第1の導電膜にのみ重なるようにソースまたはドレイン領域として機能する不純物領域より低い濃度の不純物領域を設ける構造で設けることもできる。また、ゲート電極を積層構造で設ける場合に、ゲート電極の下方に形成される第1の導電膜225aと当該第1の導電膜225a上に形成される第2の導電膜225bで設け、当該第2の導電膜225bの側壁に接し且つ導電膜225aの上方に形成されるようにサイドウォールを設ける構造（図10（C））とすることも可能である。なお、上記構成において、半導体膜103a、103bのソースまたはドレイン領域として機能する不純物領域をNi、Co、W等のシリサイドで設けることも可能である。

30

## 【0064】

続いて、薄膜トランジスタ744～748を覆うように、絶縁層を単層又は積層して形成する（図5（A）参照）。薄膜トランジスタ744～748を覆う絶縁層は、SOG法、液滴吐出法等により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ、シロキサン等の有機材料等により、単層又は積層で形成する。シロキサンとは、Si-O-Si結合を含む樹脂に相当する。シロキサンは、シリコン（Si）と酸素（O）との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられる。また、置換基として、フルオロ基を用いてもよい。

40

50

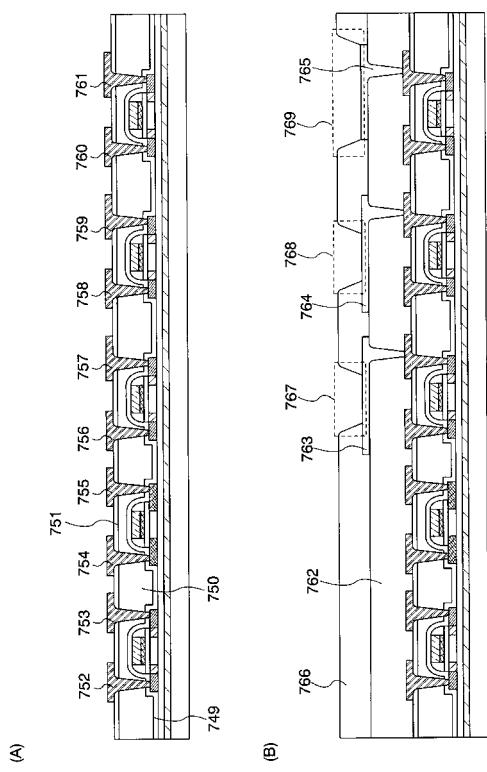

**【0065】**

例えば、薄膜トランジスタ 744～748 を覆う絶縁層が 3 層構造の場合、1 層目の絶縁層 749 として酸化珪素を含む層を形成し、2 層目の絶縁層 750 として樹脂を含む層を形成し、3 層目の絶縁層 751 として窒化珪素を含む層を形成するとよい。

**【0066】**

なお、絶縁層 749～751 を形成する前、又は絶縁層 749～751 のうちの 1 つ又は複数を形成した後に、半導体層の結晶性の回復や半導体層に添加された不純物元素の活性化、半導体層の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザアニール法又は R T A 法などを適用するとよい。

**【0067】**

次に、フォトリソグラフィ法により、絶縁層 749～751 をエッチングして、第 2 の不純物領域 726、728、730、732、不純物領域 712 を露出させる開口部を形成する。続いて、開口部を充填するように、導電層を形成し、当該導電層をパターン加工して、ソース配線又はドレイン配線として機能する導電層 752～761 を形成する。

**【0068】**

導電層 752～761 は、プラズマ CVD 法やスパッタリング法により、チタン (Ti)、アルミニウム (Al)、ネオジウム (Nd) 等から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、アルミニウムを主成分とし珪素を含む材料、アルミニウムを主成分とし、ニッケル、炭素及び珪素から選択された 1 種又は複数種とを含む材料に相当する。導電層 752～761 は、例えば、バリア層と珪素を含むアルミニウム層とバリア層の積層構造、バリア層と珪素を含むアルミニウム層と窒化チタン層とバリア層の積層構造を採用するとよい。なお、アルミニウムシリコンが含むシリコンは、0.1 wt %～5 wt % とする。また、バリア層とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムや珪素を含むアルミニウムは、抵抗値が低く、安価であるため、導電層 752～761 を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムや珪素を含むアルミニウムのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア層を形成すると、結晶質半導体層上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元するため、結晶質半導体層とバリア層の接続不良の発生を抑制することができる。

**【0069】**

次に、導電層 752～761 を覆うように、絶縁層 762 を形成する（図 5 (B) 参照）。絶縁層 762 は、SOG 法、液滴吐出法等を用いて、無機材料又は有機材料により、単層又は積層で形成する。絶縁層 762 は、好適には、0.75 μm～3 μm の厚さで形成する。

**【0070】**

続いて、フォトリソグラフィ法により、絶縁層 762 をエッチングして、導電層 757、759、761 を露出させる開口部を形成する。続いて、開口部を充填するように、導電層を形成する。導電層は、プラズマ CVD 法やスパッタリング法を用いて、導電性材料により形成する。次に、導電層をパターン加工して、導電層 763～765 を形成する。なお、導電層 763～764 は、記憶素子が含む一対の導電層のうちの一方の導電層となる。従って、好適には、導電層 763～765 は、チタン、又はチタンを主成分とする合金材料若しくは化合物材料により、単層又は積層で形成するとよい。チタンは、抵抗値が低いため、記憶素子のサイズの縮小につながり、高集積化を実現することができる。また、導電層 763～765 を形成するためのフォトリソグラフィ工程においては、下層の薄膜トランジスタ 744～748 にダメージを与えないために、ウエットエッチング加工を行うとよく、エッチング剤にはフッ化水素又はアンモニア過水を用いるとよい。

**【0071】**

次に、導電層 763～765 を覆うように、絶縁層 766 を形成する。絶縁層 766 は

10

20

30

40

50

、SOG法、液滴吐出法等を用いて、無機材料又は有機材料により、単層又は積層で形成する。また、絶縁層766は、好適には、0.75μm～3μmの厚さで形成する。続いて、フォトリソグラフィ法により、絶縁層766をエッティングして、導電層763～765を露出させる開口部767～769を形成する。

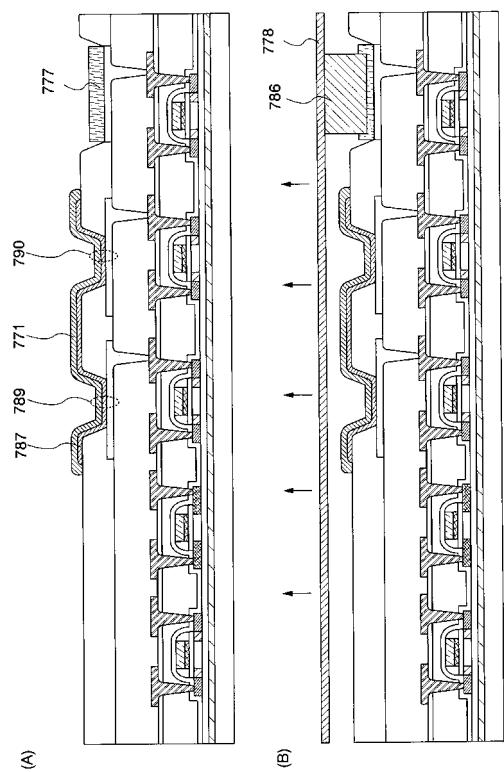

#### 【0072】

次に、導電層763、764に接するように有機化合物を含む層787を形成する(図6(A)参照)。有機化合物を含む層787は、液滴吐出法や蒸着法等により形成する。続いて、有機化合物を含む層787に接するように、導電層771を形成する。導電層771は、スパッタリング法や蒸着法等により形成する。

#### 【0073】

以上の工程を経て、導電層763、有機化合物を含む層787及び導電層771の積層体からなる記憶素子789と、導電層764、有機化合物を含む層787及び導電層771の積層体からなる記憶素子790が完成する。本工程により、半導体装置を構成するICチップを形成することができる。なお、記憶素子の形態は本実施の形態に限定されず、必要がなければ必ずしも記憶素子を設ける必要はない。

#### 【0074】

次に、導電層765上に異方性導電性樹脂777を形成する。そして、異方性導電性樹脂777上に上記実施の形態と同様に作製した導電膜786が設けられた支持体778を設ける。なお、ここで導電膜786はアンテナとして機能する配線基板である。そして、支持体778を取り除くことで支持体778と導電膜786とを剥離することができる(図6(B)、図7(A)参照)。

#### 【0075】

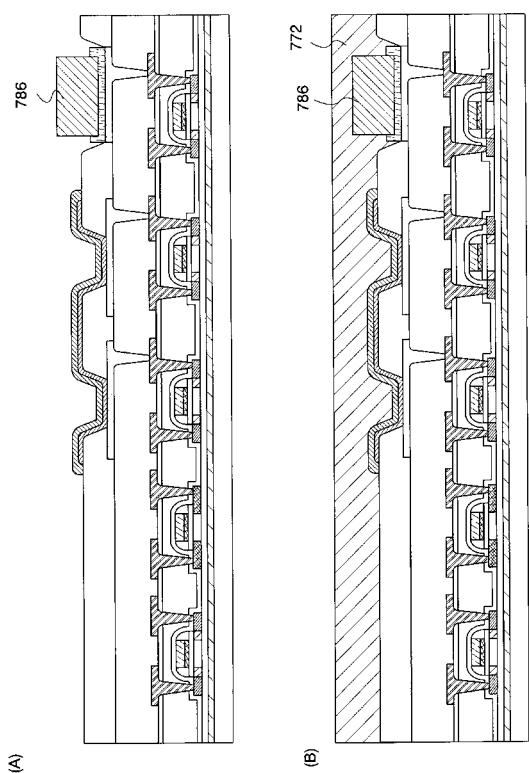

次に、記憶素子789、790、導電層786を覆うように、SOG法、液滴吐出法等により、保護層として機能する絶縁層772を形成する(図7(B)参照)。絶縁層772は、DLC(ダイヤモンドライクカーボン)などの炭素を含む層、窒化珪素を含む層、窒化酸化珪素を含む層、有機材料(好ましくはエポキシ樹脂)により形成する。

#### 【0076】

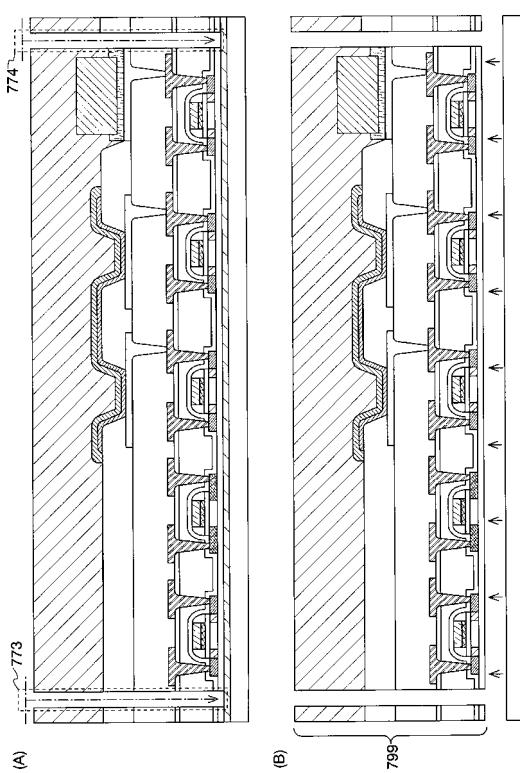

次に、剥離層702の一部が露出するように、絶縁層703、749、750、751、762、766、772をエッティングして、開口部773、774を形成する(図8(A)参照)。開口部773、774は、フォトリソグラフィ法やレーザを用いて不要な部分を除去する方法により形成することができる。本実施の形態では、紫外線レーザから射出されるレーザビームを照射して、開口部773、774を形成する。

#### 【0077】

次に、薄膜トランジスタ744～748と、記憶素子789、790の素子群と、導電層786とを含む薄膜集積回路部799を、基板701から剥離する。剥離の方法としては、エッティング等によって剥離層702を除去する化学的剥離と、外部からの作用によって薄膜集積回路部799と剥離層702とを分離する物理的剥離とに大別されるが、これらに限定されない。本実施の形態では、化学的剥離を用い、開口部773、774にエッティング剤を導入して、剥離層702を除去する(図8(B)参照)。エッティング剤は、フッ化ハロゲンを含む気体又は液体を使用する。例えば、三フッ化塩素(ClF<sub>3</sub>)、三フッ化窒素(NF<sub>3</sub>)、三フッ化臭素(BrF<sub>3</sub>)、フッ化水素(HF)がある。なお、エッティング剤として、フッ化水素を使用する場合は、剥離層702として、酸化珪素からなる層を用いる。なお、剥離層702を化学的に除去せず、薄膜集積回路部799を外部から引っ張る等の物理的手法により剥離してもよい。開口部773、774をレーザーで形成した場合、剥離層702と薄膜集積回路部799とが剥がれやすくなり、薄膜集積回路部799を引っ張るだけで容易に薄膜集積回路部799と剥離層とを分離することができる。このような物理的手法を用いると、高価な薬品を用いる必要がないため、低コストな半導体装置を作製することができる。

#### 【0078】

薄膜集積回路部799が剥離された基板701は、コストの削減のために、再利用する

10

20

30

40

50

とよい。また、絶縁層 772 は、剥離層 702 を除去した後に、薄膜集積回路が飛散しないように、設けたものである。薄膜集積回路は小さく薄く軽いために、剥離層 702 を除去した後は、基板 701 に密着していないために飛散しやすい。しかしながら、薄膜集積回路上に絶縁層 772 を形成することで、薄膜集積回路に重みが付き、基板 701 からの飛散を防止することができる。また、薄膜集積回路単体では薄くて軽いが、絶縁層 772 を形成することで、巻かれた形状になることがなく、ある程度の強度を確保することができる。

#### 【 0079 】

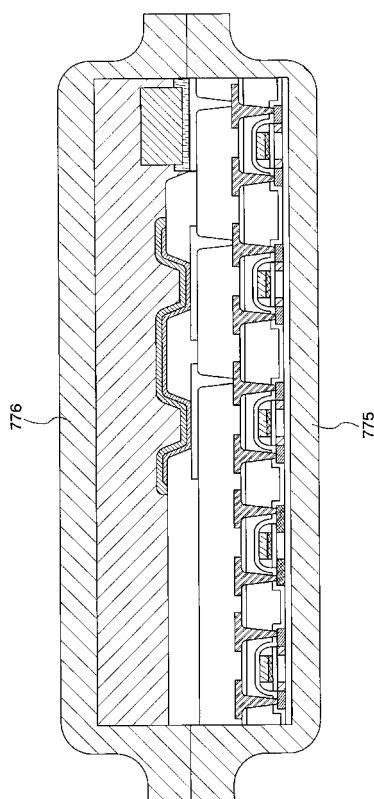

次に、薄膜集積回路の一方の面を、第 1 の基板 776 に接着させて、基板 701 から完全に剥離する（図 9 参照）。続いて、薄膜集積回路の他方の面を、第 2 の基板 775 に接着させ、その後加熱処理と加圧処理の一方又は両方を行って、薄膜集積回路を、第 1 の基板 776 と第 2 の基板 775 により封止することにより半導体装置が完成する。

10

#### 【 0080 】

第 1 の基板 776 と第 2 の基板 775 は、帯電防止対策を施したフィルム（帯電防止フィルム）、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、繊維質な材料からなる紙、基材フィルム（ポリエステル、ポリアミド、無機蒸着フィルム、紙類等）と接着性合成樹脂フィルム（アクリル系合成樹脂、エポキシ系合成樹脂等）との積層フィルムなどに相当する。帯電防止対策を施したフィルムとしては、帯電防止可能な材料を樹脂中に分散させたフィルム、帯電防止可能な材料が貼り付けられたフィルム等が挙げられる。帯電防止可能な材料が貼り付けられたフィルムは、片面に帯電防止可能な材料を貼り付けられたフィルムであってもよいし、両面に帯電防止可能な材料を貼り付けられたフィルムであってもよい。また、片面に帯電防止可能な材料が貼り付けられたフィルムは、帯電防止可能な材料が貼り付けられた面をフィルムの内側になるように貼り付けてよいし、フィルムの外側になるように貼り付けてよい。また、帯電防止可能な材料はフィルムの全面、あるいは一部に貼り付けてあればよい。なお、帯電防止可能な材料としては、アルミなどの金属、インジウムと錫を含む酸化物（ITO）、両性界面活性剤金属塩、イミダゾリン型両性界面活性剤、側鎖にカルボキシル基および 4 級アンモニウム塩基をもつ架橋性共重合体高分子を含む樹脂材料などが挙げられる。帯電防止フィルムを第 1 の基板 776 と第 2 の基板 775 として用いることで、外部からの静電気によって集積回路に悪影響が及ぶことを防止することができる。

20

#### 【 0081 】

第 1 の基板 776 と第 2 の基板 775 は、熱圧着により、被処理体と加熱処理と加圧処理が行われて被処理体と接着する。加熱処理と加圧処理を行う際には、第 1 の基板 776 と第 2 の基板 775 の最表面に設けられた接着層か、又は最外層に設けられた層（接着層ではない）を加熱処理によって溶かし、加圧により接着する。また、第 1 の基板 776 と第 2 の基板 775 の表面には接着層が設けられていてもよいし、接着層が設けられていないてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、酢酸ビニル樹脂系接着剤、ビニル共重合樹脂系接着剤、エポキシ樹脂系接着剤、ウレタン樹脂系接着剤、ゴム系接着剤、アクリル樹脂系接着剤等の接着剤を含む層に相当する。

30

#### 【 0082 】

第 1 の基板 776 と第 2 の基板 775 がプラスチックからなる場合、薄型、軽量で、曲げることが可能であるためデザイン性に優れ、フレキシブルな形状への加工が容易である。また、耐衝撃性に優れ、様々な物品に貼り付けたり、埋め込んだりすることが容易であり、多種多様な分野で活用することができる。

40

#### 【 0083 】

上記の構成において、記憶素子 789、790 は、一対の導電層間に、有機化合物を含む層が設けられた素子であり、データの書き込みは、一対の導電層を短絡させることにより行う。データの読み出しこそは、記憶素子 789、790 の抵抗値の相違を読み取ることにより行う。記憶素子 789、790 は、不揮発性である点、データの書き換えが不可能である点、データの書き込みを行っていない記憶素子がある限り、データの追記が可能である。

50

る点を特徴とする。また、3層の積層体からなるため、作製が簡単である点を特徴とする。また、積層部分の面積を縮小が容易であるため、高集積化を容易に実現することができる点を特徴とする。

#### 【0084】

実施の形態1により作製された配線基板を半導体装置に用いることで、多数回の複雑な工程を行うことなく、簡易なプロセスで、低コストな半導体装置を作成することができる。なお、本実施の形態は他の実施の形態、実施例と自由に組み合わせて行うことができる。つまり、他の実施の形態、実施例で示した材料や形成方法は、本実施の形態でも自由に組み合わせて利用することができる。

#### 【0085】

10

#### (実施の形態4)

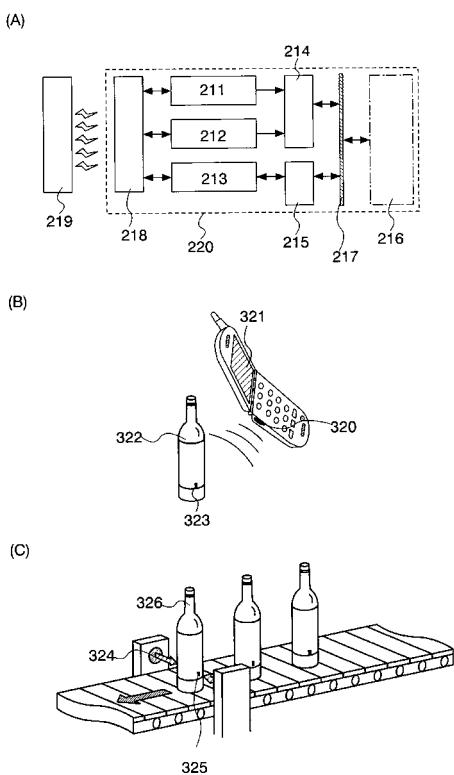

上記実施の形態で示した半導体装置を非接触でデータの送受信が可能であるRFIDとして利用した場合の一実施形態に関して図11を用いて説明する。

#### 【0086】

RFID220は、非接触でデータを交信する機能を有し、電源回路211、クロック発生回路212、データ復調/変調回路213、他の回路を制御する制御回路214、インターフェース回路215、メモリ216、データバス217、本発明の作製方法により形成されたアンテナ218を有する(図11(A))。

#### 【0087】

20

電源回路211は、アンテナ218から入力された交流信号を基に、半導体装置の内部の各回路に供給する各種電源を生成する回路である。クロック発生回路212は、アンテナ218から入力された交流信号を基に、半導体装置内の各回路に供給する各種クロック信号を生成する回路である。データ復調/変調回路213は、リーダライタ219と交信するデータを復調/変調する機能を有する。制御回路214は、メモリ216を制御する機能を有する。アンテナ218は、電磁波或いは電波の送受信を行う機能を有する。リーダライタ219は、半導体装置との交信、制御及びそのデータに関する処理を制御する。なお、RFIDは上記構成に制約されず、例えば、電源電圧のリミッタ回路や暗号処理専用ハードウェアといった他の要素を追加した構成であってもよい。

#### 【0088】

30

また、RFIDは、各回路への電源電圧の供給を電源(バッテリ)を搭載せず電波により行うタイプとしてもよいし、各回路への電源電圧の供給をアンテナの代わりに電源(バッテリ)を搭載させて行うタイプとしてもよいし、電波と電源により電源電圧を供給するタイプとしてもよい。

#### 【0089】

本発明の半導体装置をRFID等に利用した場合、非接触で通信を行う点、複数読み取りが可能である点、データの書き込みが可能である点、様々な形状に加工可能である点、選択する周波数によっては、指向性が広く、認識範囲が広い点等の利点を有する。また、実施の形態1により作製された配線基板を半導体装置に用いることで、多数回の複雑な工程を行うことなく、簡易なプロセスで、低コストな半導体装置を作成することができる。RFIDは、非接触による無線通信で人や物の個々の情報を識別可能なICタグ、ラベル加工を施して目標物への貼り付けを可能としたラベル、イベントやアミューズメント向けのリストバンド等に適用することができる。また、RFIDを樹脂材料により成型加工してもよいし、無線通信を阻害する金属に直接固定してもよい。さらに、RFIDは、入退室管理システムや精算システムといった、システムの運用に活用することができる。

40

#### 【0090】

次に、本発明の半導体装置をRFIDとして実際に使用するときの一形態について説明する。表示部321を含む携帯端末の側面には、リーダライタ320が設けられ、品物322の側面にはRFID323が設けられる(図11(B))。品物322が含むRFID323にリーダライタ320をかざすと、表示部321に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、更に商品の説明等の商品に関する情報が表示さ

50

れる。また、商品 326 をベルトコンベアにより搬送する際に、リーダライタ 324 と、商品 326 に設けられた R F I D 325 を用いて、該商品 326 の検品を行うことができる（図 11（C））。このように、システムに R F I D を活用することで、情報の取得を簡単に行うことができ、高機能化と高付加価値化を実現する。

#### 【0091】

実施の形態 1 により作製された配線基板を半導体装置に用いることで、多数回の複雑な工程を行うことなく、簡易なプロセスで、低コストな半導体装置を作成することができる。なお、本実施の形態は他の実施の形態、実施例と自由に組み合わせて行うことができる。つまり、他の実施の形態、実施例で示した材料や形成方法は、本実施の形態でも自由に組み合わせて利用することができる。

10

#### 【0092】

##### (実施の形態 5 )

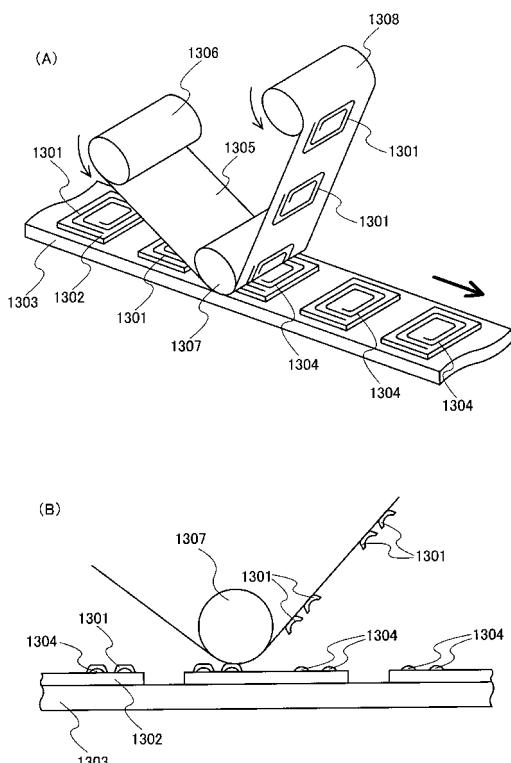

本実施の形態では、上記実施の形態で示した配線基板の大量生産方法の一形態について図面を用いて説明する。具体的には、複数のガラス基板それぞれの上に形成されたパターン上に電解めっき処理により形成された導電膜をロールトゥロール工法によりフィルム上に移し替える方法を説明する。本実施の形態では、図 12（A）、（B）に模式的に示すロールトゥロール型転写装置を用いて電解めっき処理により形成された導電膜をフィルム上に移し替える方法を説明する。図 12（B）は、図 12（A）に示した装置の断面の模式図である。

#### 【0093】

20

本実施の形態のロールトゥロール型転写装置は、図 12（A）に示すように、フィルム 1305 が巻かれた第 1 のロール 1306、第 2 のロール 1307、第 3 のロール 1308 を回転させることで、フィルム 1305 が第 3 のロール 1308 に巻かれる構成となっている。

#### 【0094】

まず、導電膜 1301 が形成されたガラス基板 1302 を移動手段 1303 上に設置する（図 12（A）、（B）参照）。本実施の形態において、移動手段 1303 はガラス基板 1302 を矢印方向に移動させるものとする。ここで、導電膜 1301 は、実施の形態 1 と同様に電解めっき処理を用いてパターン 1304 上に形成されている。ガラス基板 1302 として、無アルカリガラス、ソーダガラス、鉛ガラス、ホウケイ酸ガラス、合成石英、溶融石英、シリコンウェハー、その他セラミックス基板等を使用すれば良い。

30

#### 【0095】

また、パターン 1304 は、スクリーン印刷法、ガラス基板全面に導電性材料を形成した後、レーザー光にて不要な部分を除去する方法、インクジェット法に代表される液滴を微小径の開いた細管から空気流にて吐出する方法、ディスペ ns 法に代表される粘性を有する材料あるいは液滴を数ミリメートル程度以下の径を持つ細管から乾燥気体にて押し出すことで形成する手法等のどのような方法を用いても良い。ガラス基板の大きさは、所望の配線基板の大きさ以上であれば当該パターンの形成方法で対応できる範囲で、適宜選択することができる。大量生産を行うことにより安価にアンテナパターンを得ようとすれば、所望のパターンを出来るだけ多く配置出来るようなより大きなガラス基板を用いればよい。また、パターンが形成された基板を電界めっき浴に浸し、電解めっき処理によりパターン上に導電膜を形成するとき、電解めっき処理により形成される導電膜は、Cu に限らず、Ni、Sn、Pb、Cr、Au、Ag、ロジウム等の単体金属や、Ag、Cu、Ni、Cd、Co 等と Auとの合金であっても良い。

40

#### 【0096】

次に、複数のガラス基板 1302 を移動させ、第 1 のロール 1306、第 2 のロール 1307、第 3 のロール 1308 を回転させることで、それぞれのガラス基板 1302 上に形成された導電膜 1301 をフィルム 1305 上に移すことができる。つまり、ガラス基板 1302 上に形成された導電膜 1301 と第 2 のロール 1307 とをフィルム 1305 を介して接触させることで、導電膜 1301 がパターン 1304 から剥離し、導電膜 13

50

01のみがフィルム1305に転写される。フィルム1305は、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)に代表されるプラスチック、又はアクリル等の可撓性を有する合成樹脂からなる基体上に、熱可塑性樹脂等の接着性あるいは粘着性を有した層を塗布したものを用いることができる。もちろんフィルム1305の材料はこれらに限定されず、接着性を有する可撓性基体であれば特に限定されない。本実施の形態のロールトゥロール型転写装置において、ロールの径、配置角度、ロールフィルムの走行速度、使用するフィルム材料、フィルムの厚み、フィルムの幅、フィルムの長さは、所望のアンテナパターンが転写出来ればどのようなものを使用しても良い。

## 【0097】

10

本実施の形態では、導電膜1301を転写した後フィルム1305は第3のロール1308に巻き取られ、ガラス基板1302上に形成されたパターン1304を再利用することができる。

## 【0098】

なお、本実施の形態は他の実施の形態、実施例と自由に組み合わせて行うことができる。つまり、他の実施の形態、実施例で示した材料や形成方法は、本実施の形態でも自由に組み合わせて利用することができる。

## 【0099】

## (実施の形態6)

本実施の形態では、配線基板の大量生産方法について実施の形態5に示す方法とは異なる一形態について図面を用いて説明する。

20

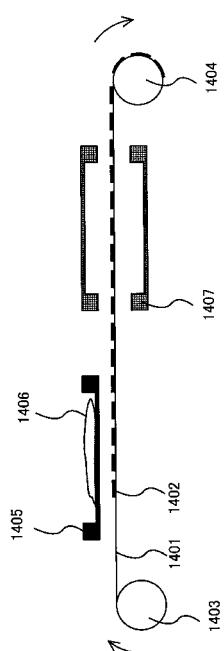

## 【0100】

本実施の形態では、図13に示すロールトゥロールスクリーン印刷装置を用いて、ロール1403に巻き付けられた第1のフィルム1401上にアンテナパターン1402を形成する。このとき第1のロール1403、第2のロール1404に巻き付けて使用する第1のフィルム1401は、可撓性を有し、その後の製造プロセスでの最高処理温度に耐えられるものであればよい。第1のフィルムとして、例えばポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)、ポリカーボネート(PC)、ナイロン、ポリエーテルエーテルケトン(PEEK)、ポリスルホン(PSF)、ポリエーテルイミド(PEI)、ポリアリレート(PAR)、ポリブチレンテレフタレート(PBT)、ポリイミドなどのプラスチック基板や、アクリル等の可撓性を有する合成樹脂からなる基板等が挙げられる。当該基板はその形状・面積に大きな制限が無く、例えば一本のロールで最大数キロメートルの基板を巻き付けることが出来るため、非常に生産性が良い。この点はフレキシブル性に劣る基板、例えばシリコン基板・ガラス基板・セラミック基板等と比較すると大きな優位点となる。

30

## 【0101】

まず、第1のフィルム1401を第2のロール1404によって巻き取りながら、印刷板1405上にアンテナパターン材料1406を塗布してアンテナパターン1402を形成する。そして、乾燥炉1407においてアンテナパターン1402を乾燥させ、第1のフィルム1401上に固定する。

40

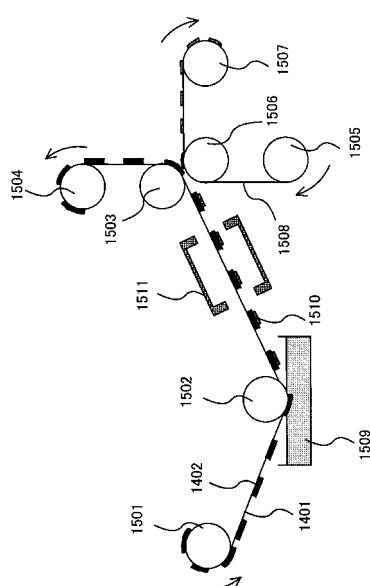

## 【0102】

続いて、第2のロール1404に巻き取られたアンテナパターン1402が形成された第1のフィルム1401を、図14に示す第3～第6のロール1501～1504に設置する。この際、第3～第6のロール1501～1504に均一に張力をかけることで、導電膜の膜厚と電気特性の均一化を図ることが可能となり、製品作製の歩留まりを向上することが可能である。図14は、電解めっき処理による導電膜形成、乾燥、導電膜の分離・剥離を連続的に行うロールトゥロール転写装置の模式図である。ロールトゥロール転写装置を用いてこれらの工程を連続的に行うことにより、個々に行う場合と比べてコストの低減・タクト向上の面で大きな優位点がある。また、本実施の形態では、第1のフィルム1401上にアンテナパターン1402を形成する工程を別の装置で行ったが、電解めっき

50

処理による導電膜形成、乾燥、導電膜の分離・剥離工程と同一の装置を用いて形成してもよい。

#### 【0103】

続いて、第2のフィルム1508を第7～第9のロール1505～1507に設置する。本実施の形態では第2のフィルムとして熱可塑性樹脂付き基材を使用する。第2のフィルムとしては熱可塑性樹脂に限らず、表面に接着性あるいは粘着性を有した層があるものであればよい。

#### 【0104】

続いて、第3～第9のロール1501～1507を回転させて第1のフィルム1401を移動させて電解めっき処理を行う。本実施の形態では、電解めっき浴1509中にアンテナパター1402を浸して電解めっき処理を行い、アンテナパター1402上に導電膜1510を形成する。その後、乾燥炉1511において導電膜1510を乾燥させる。

10

#### 【0105】

次に、第5のロール1503上の導電膜1510と、第8のロール1506上の第2のフィルム1508とを接触させることにより、導電膜1510をアンテナパター1402から分離・剥離する。つまり、第2のフィルム1508上に導電膜1510を転置する。導電膜1510が転置された第2のフィルム1508は、第9のロール1507により巻き取られる。第2のフィルム1508上に形成された導電膜1510をICチップ等と接続することにより、第2のフィルム1508を半導体装置として利用することができる。また、導電膜1510が剥離された第1のフィルム1401は、第6のロール1504により巻き取られる。巻き取られた第1のフィルム1401を再びめっき浴に連結されたロールトゥロール転写装置へ再び設置することで、アンテナパター1402を再利用して導電膜を形成することが可能である。第1のフィルム1401の再利用回数を増やすれば増やすほどアンテナ形成のコストの低減が可能となる。

20

#### 【0106】

なお、本実施の形態は他の実施の形態、実施例と自由に組み合わせて行うことができる。つまり、他の実施の形態、実施例で示した材料や形成方法は、本実施の形態でも自由に組み合わせて利用することができる。

#### 【0107】

##### (実施の形態7)

本発明のアンテナは半導体装置に利用することが可能であり、例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。これらの例に関して図15、図16を用いて説明する。

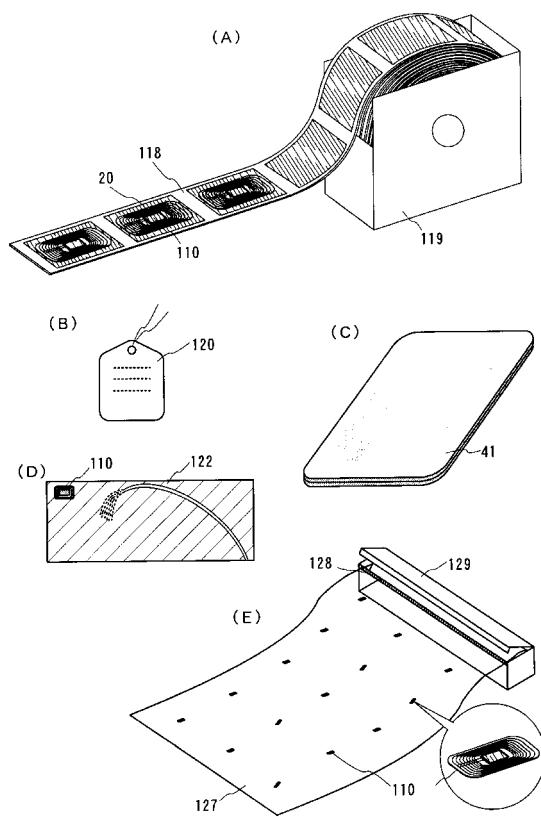

#### 【0108】

図15(A)は、本発明に係るIDラベルの完成品の状態の一例である。ラベル台紙(セパレート紙)118上に、ICチップ110を内蔵した複数のIDラベル20が形成されている。IDラベル20は、ボックス119内に収納されている。また、IDラベル上には、その商品や役務に関する情報(商品名、ブランド、商標、商標権者、販売者、製造者等)が記されており、一方、内蔵されているICチップには、その商品(又は商品の種類)固有のIDナンバーが付されており、偽造や、商標権、特許権等の知的財産権侵害、不正競争等の不法行為を容易に把握することができる。また、ICチップ内には、商品の容器やラベルに明記しきれない多大な情報、例えば、商品の产地、販売地、品質、原材料、効能、用途、数量、形状、価格、生産方法、使用方法、生産時期、使用時期、賞味期限、取扱説明、商品に関する知的財産情報等を入力しておくことができ、取引者や消費者は、簡易なリーダによって、それらの情報にアクセスすることができる。また、生産者側からは容易に書換え、消去等も可能であるが、取引者、消費者側からは書換え、消去等ができる仕組みになっている。

40

#### 【0109】

図15( B )は、ICチップを内蔵したIDタグ120を示している。IDタグを商品に備え付けることにより、商品管理が容易になる。例えば、商品が盗難された場合に、商品の経路を辿ることによって、その犯人を迅速に把握することができる。このように、IDタグを備えることにより、所謂トレーサビリティ( traceability ; 複雑化した製造、流通の各段階で問題が生じた場合に、経路を辿ることによって、その原因を迅速に把握できる態勢を整えること。)に優れた商品を流通させることができる。

#### 【0110】

図15( C )は、本発明に係るIDカード41の完成品の状態の一例である。上記IDカードとしては、キャッシュカード、クレジットカード、プリペイドカード、電子乗車券、電子マネー、テレフォンカード、会員カード等のあらゆるカード類が含まれる。

10

#### 【0111】

図15( D )は、本発明に係る無記名債券122の完成品の状態の一例である。上記無記名債券類には、切手、切符、チケット、入場券、商品券、図書券、文具券、ビール券、おこめ券、各種ギフト券、各種サービス券等が含まれるが、勿論これらに限定されるものではない。また、無記名債権に限らず小切手、証券、約束手形等の有価証券類、運転免許証、住民票等の証書類等に設けることもできる。

#### 【0112】

図15( E )は、ICチップ110を内蔵した商品を包装するための包装用フィルム類127を示している。包装用フィルム類127は、例えば、下層フィルム上に、ICチップを任意にばらまき、上層フィルムで覆うことによって作製することができる。包装用フィルム類127は、ボックス129に収納されており、所望の量だけカッター128で切り離して利用することができる。なお、包装用フィルム類127としての素材は特に制限されない。例えば、薄膜樹脂、アルミ箔、紙等を用いることができる。

20

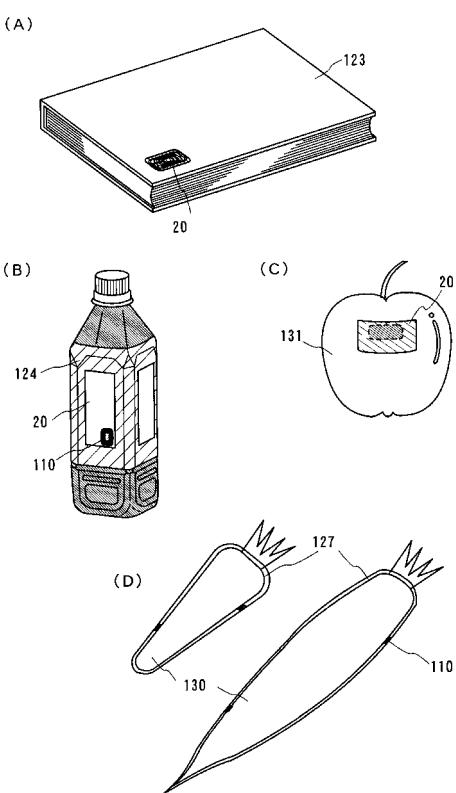

#### 【0113】

図16( A )、( B )は、本発明に係るIDラベル20を貼付した書籍123、ペットボトル124を示している。なお、もちろんこれらに限定されず、お弁当等の包装紙等の包装用容器類、DVDソフト、ビデオテープ等の記録媒体、自転車等の車両、船舶等の乗物類、鞄、眼鏡等の身の回り品、食料品、飲料等の食品類、衣服、履物等の衣類、医療器具、健康器具等の保健用品類、家具、照明器具等の生活用品類、医薬品、農薬等の薬品類、液晶表示装置、EL表示装置、テレビジョン装置(テレビ受像機、薄型テレビ受像機)、携帯電話等の電子機器等様々な物品に設けることができる。本発明に用いられるICチップは非常に薄いため、上記書籍等の物品に薄膜集積回路を搭載しても、機能、デザイン性を損ねることがない。更に、非接触型薄膜集積回路装置の場合、アンテナをチップとを一体形成でき、曲面を有する商品に直接転写することが容易になる。

30

#### 【0114】

図16( C )は、果物類131の生鮮食品に、直接IDラベル20を貼り付けた状態を示している。また、図16( D )は、ICチップ110を内蔵した包装用フィルム類127によって、野菜類130の生鮮食品を包装した一例を示している。また、なお、IDラベルを商品に貼り付けた場合、剥がされる可能性があるが、包装用フィルム類によって商品をくるんだ場合、包装用フィルム類を剥がすのは困難であるため、防犯対策上多少のメリットはある。

40

#### 【0115】

紙幣、硬貨、有価証券類、証書類、無記名債券類等にRFIDを設けることにより、偽造を防止することができる。また、包装用容器類、書籍類、記録媒体等、身の回り品、食品類、生活用品類、電子機器等にRFIDを設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。乗物類、保健用品類、薬品類等にRFIDを設けることにより、偽造や盗難の防止、薬品類ならば、薬の服用の間違いを防止することができる。RFIDの設け方としては、物品の表面に貼ったり、物品に埋め込んだりして設ける。例えば、本ならば紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりするとよい。

50

## 【0116】

このように、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等にRFIDを設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。また乗物類にRFIDを設けることにより、偽造や盗難を防止することができる。また、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物にRFIDを埋め込むことによって、生まれた年や性別または種類等を容易に識別することが可能となる。

## 【0117】

以上のように、本発明の配線基板を用いた半導体装置は物品あればどのようなものにでも設けて使用することができる。本発明を用いることで、多数回の複雑な工程を行うことなく、簡易なプロセスで、低コストな半導体装置を作成することができる。なお、本実施の形態は、他の実施の形態、実施例と自由に組み合わせて行うことができる。10

## 【実施例1】

## 【0118】

本実施例では、実施の形態1で示した配線基板の作製結果について説明する。

## 【0119】

まず、スクリーン印刷にてガラス基板上に導電性樹脂を形成した。本実施例において、スクリーン印刷版はメッシュ数#250を使用し、導電性樹脂として印刷版上に約100g程の銀を含む樹脂（日本アチソン（株）、Electrodag427SS、バインダーとしてポリエステル系樹脂を使用）を乗せ、スクレッパによりパターン形成部に相当する印刷版開口部および全面に銀を含む樹脂の塗布を行った。その際、スクレッパと印刷版の距離は非接触で、スクレッパを速度80mm/sec移動させた。次に、スキージで銀を含む樹脂を印刷版開口部より基材に塗布した。スキージは印刷版に接触しスピード100mm/secとした。スキージの押し込み圧力は圧縮空気を用いて行い、0.150MPaとした。銀を含む樹脂を基材に塗布した後、樹脂の凹凸を取る為に印刷物のレベリングを5分行い、200度30分間焼成した。焼成は間接加熱雰囲気で行った。20

## 【0120】

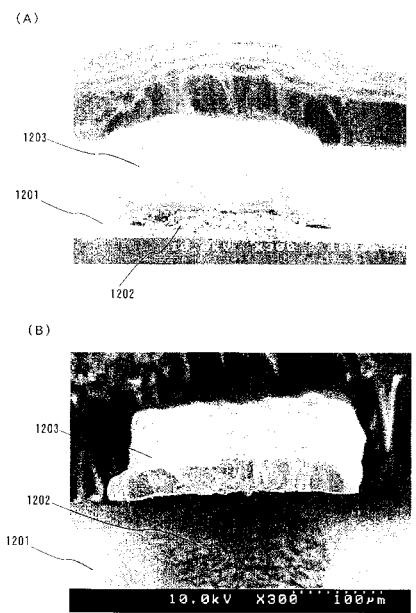

その後、銀を含む樹脂が形成された基板に対して、銅(Cu)の電解めっき処理を行った。本実施例において使用した電解めっき浴は、水500ml中に硫酸銅5水和物146.38g、濃硫酸15ml、平均分子量2000のポリエチレングリコール150mgを使用した。始めに硫酸銅5水和物146.38gと水500mlをビーカーに入れ、スターラーにて攪拌させながら、濃硫酸15ml、ポリエチレングリコール150mgを加え、全てを溶解させた。その後、基板上の銀を含む樹脂を陰極に、銅板（リン含有）を陽極にセットし、電解めっき浴を攪拌しながら、6分間0.03Aの電流を流すことで、基板上に形成された銀を含む樹脂上に銅の膜が形成された。電解めっき処理のときの電流密度は約1.0A/cm<sup>2</sup>とした。電解めっき終了後、基板を電解浴より取り出し、純水を用いて基板を洗浄した。図17(A)に、本実施例によりガラス基板上1201に形成された銀を含む樹脂1202上に、電解めっき処理により銅の膜1203が形成されたときのSEM(走査型電子顕微鏡)写真を示す。30

## 【0121】

その後、銅の膜上に転置用基体を貼り付けて、転置用基体を基板から剥がすことで銅の膜と銀を含む樹脂とを剥離する。図17(B)に示すように、銅の膜と銀を含む樹脂とははがれやすいため、容易に銅の膜を作製することができる。このように、パターンと電解めっきにより形成された導電膜とが剥がれやすくなる理由は、電解めっき処理により形成された導電膜の成長に伴い生成される導電膜の応力に対して、パターンと導電膜との界面での密着力が相対的に低下したため、分離・剥離につながったと考えられる。パターンと導電膜との界面での密着力は、パターンの形状、パターンの表面の形状（凹凸具合）、パターンの材質、パターンの電気的特性、パターンの機械的特性、電解めっき処理により形成された導電膜の材質、電解めっき処理により形成された導電膜の電気的特性、電解めっき処理により形成された導電膜の機械的特性、又はパターンと電解めっき浴との塗れ性（4050

表面特性)等に影響を受けると考えられる。

【図面の簡単な説明】

【0122】

- 【図1】本発明の配線基板の作製方法を示す図。

- 【図2】本発明の配線基板の作製方法を示す図。

- 【図3】本発明の半導体装置の作製方法を示す図。

- 【図4】本発明の半導体装置の作製方法を示す図。

- 【図5】本発明の半導体装置の作製方法を示す図。

- 【図6】本発明の半導体装置の作製方法を示す図。

- 【図7】本発明の半導体装置の作製方法を示す図。

- 【図8】本発明の半導体装置の作製方法を示す図。

- 【図9】本発明の半導体装置の作製方法を示す図。

- 【図10】薄膜トランジスタの形態を示す図。

- 【図11】本発明の半導体装置の使用形態を示す図。

- 【図12】本発明の配線基板の作製工程を示す図。

- 【図13】本発明の配線基板の作製工程を示す図。

- 【図14】本発明の配線基板の作製工程を示す図。

- 【図15】本発明の半導体装置の使用形態を示す図。

- 【図16】本発明の半導体装置の使用形態を示す図。

- 【図17】本発明の配線基板の作製結果を示す図。

10

20

【符号の説明】

【0123】

- 101 基板

- 102 パターン

- 103 導電膜

- 104 転置用基体

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(56)参考文献 特開2001-127409(JP,A)

特開2001-284521(JP,A)

特開2004-282487(JP,A)

特開2004-087597(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |               |

|--------|---------------|

| H 05 K | 3 / 2 0       |

| H 01 L | 2 1 / 3 2 0 5 |

| H 01 L | 2 1 / 3 3 6   |

| H 01 L | 2 9 / 7 8 6   |

| H 05 K | 3 / 2 8       |