## (19) United States

## (12) Patent Application Publication Walmsley

# (10) Pub. No.: US 2009/0268246 A1

#### Oct. 29, 2009 (43) Pub. Date:

### (54) METHOD OF ENABLING OR DISABLING **VERIFICATION PROCESS**

Simon Robert Walmsley, Balmain (75) Inventor:

> Correspondence Address: SILVERBROOK RESEARCH PTY LTD

393 DARLING STREET **BALMAIN 2041 (AU)**

(73) Assignee: Silverbrook Research Pty Ltd

(21) Appl. No.: 12/501,457 (22) Filed: Jul. 12, 2009

### Related U.S. Application Data

Continuation of application No. 12/436,133, filed on May 6, 2009, which is a continuation of application No. 10/854,519, filed on May 27, 2004, now Pat. No. 7,557,941.

## **Publication Classification**

(51) Int. Cl. (2006.01)G06F 15/00

#### (57)**ABSTRACT**

A method is provided of enabling or disabling a verification process of a first entity in response to a predetermined event. The first entity has at least one associated bit-pattern and at least one variant key. Each variant key has been generated by applying a one way function to: a base key; and one or more of the at least one bit-patterns, respectively; or one or more alternative bit patterns. Each alternative bit-pattern is based on one of the at least one bit-patterns. In the method, it is determined that the predetermined event has happened, and at least one of the first variant keys is enabled or disabled in response to the predetermined event.

F1G. 1

F1G. 5

FIG. 8

FIG. 9

FIG. 10

FIG. 12

FIG. 13

FIG. 14

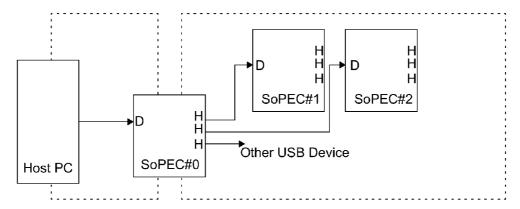

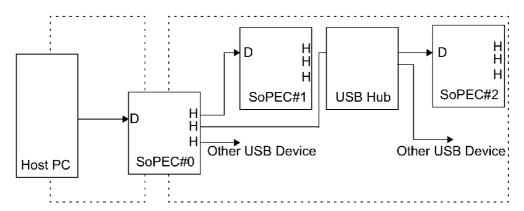

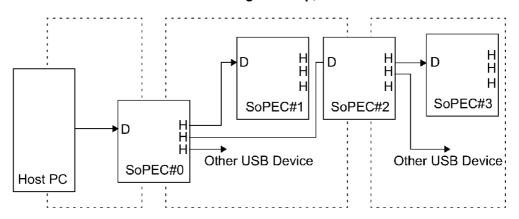

Case 1: One Printer USB Bus with no Hub chips, up to 3 Devices on the bus

Case 2: One Printer USB Bus including Hub chip, more than 3 Devices on the bus

Case 3: Two Printer USB Busses, up to 3 devices on each bus

FIG. 15

FIG. 16

FIG. 17

FIG. 19

FIG. 20

FIG. 21

FIG. 23

FIG. 27

## ROLLBACK

FIG. 28

# METHOD OF ENABLING OR DISABLING VERIFICATION PROCESS

# CROSS REFERENCE TO RELATED APPLICATION

**[0001]** This application is a continuation of U.S. application Ser. No. 12/436,133 filed on May 6, 2009, which is a continuation of U.S. application Ser. No. 10/854,519 filed May 27, 2004, now issued U.S. Pat. No. 7,557,941, all of which are herein incorporated by reference.

### FIELD OF THE INVENTION

[0002] The present invention relates to the field of secure communication.

[0003] The invention has been developed primarily to enable communication between various integrated circuits in a printer, including cartridges for use with the printer, and will be described with reference to this application. However, it will be appreciated that the invention has broad application in the general field, including use in software, hardware and combinations of the two.

### CO-PENDING APPLICATIONS

[0004] Various methods, systems and apparatus relating to the present invention are disclosed in the following co-pending applications filed by the applicant or assignee of the present invention simultaneously with the present application:

| 7,374,266                           | 7,427,117                            | 7,448,707                             | 7,281,330                | 10/854,503               |

|-------------------------------------|--------------------------------------|---------------------------------------|--------------------------|--------------------------|

| 7,328,956                           | 10/854,509                           | 7,188,928                             | 7,093,989                | 7,377,609                |

| 10/854,495                          | 10/854,498                           | 10/854,511                            | 7,390,071                | 10/854,525               |

| 10/854,526                          | 7,549,715                            | 7,252,353                             | 10/854,515               | 7,267,417                |

| 10/854,505                          | 7,517,036                            | 7,275,805                             | 7,314,261                | 10/854,490               |

| 7,281,777<br>7,549,718<br>7,266,661 | 7,290,852<br>10/854,520<br>7,243,193 | 7,484,831<br>10/854,514<br>10/854,518 | 10/854,523<br>10/854,499 | 10/854,527<br>10/854,501 |

[0005] The disclosures of these co-pending applications are incorporated herein by cross-reference.

### CROSS-REFERENCES

[0006] Various methods, systems and apparatus relating to the present invention are disclosed in the following co-pending applications filed by the applicant or assignee of the present invention. The disclosures of all of these co-pending applications are incorporated herein by cross-reference.

| 7,249,108  | 6,566,858  | 6,331,946  | 6,246,970  | 6,442,525  |

|------------|------------|------------|------------|------------|

| 7,346,586  | 09/505,951 | 6,374,354  | 7,246,098  | 6,816,968  |

| 6,757,832  | 6,334,190  | 6,745,331  | 7,249,109  | 7,509,292  |

| 10/636,283 | 7,416,280  | 7,252,366  | 7,488,051  | 7,360,865  |

| 10/727,181 | 10/727,162 | 7,377,608  | 7,399,043  | 7,121,639  |

| 7,165,824  | 7,152,942  | 10/727,157 | 7,181,572  | 7,096,137  |

| 7,302,592  | 7,278,034  | 7,188,282  | 10/727,159 | 10/727,180 |

| 10/727,179 | 10/727,192 | 10/727,274 | 10/727,164 | 7,523,111  |

| 10/727,198 | 10/727,158 | 10/754,536 | 10/754,938 | 10/727,160 |

| 6,795,215  | 6,859,289  | 6,977,751  | 6,398,332  | 6,394,573  |

| 6,622,923  | 6,747,760  | 6,921,144  | 7,454,617  | 7,194,629  |

### -continued

| 10/791,792 | 7,182,267 | 7,025,279 | 6,857,571 | 6,817,539 |

|------------|-----------|-----------|-----------|-----------|

| 6,830,198  | 6,992,791 | 7,038,809 | 6,980,323 | 7,148,992 |

| 7,139,091  | 6,947,173 |           |           |           |

### **BACKGROUND**

[0007] It is often desirable to enable at least one-way, and preferably two-way, secure communication between three or more entities. One way of doing this is by using a digital signature.

**[0008]** To create a digital signature, the data to be signed (d) is passed together with a secret key (k) through a key dependent one-way hash function (SIG). i.e. signature= $SIG_k(d)$ . The key dependent one-way hash function used throughout the QA Chip Logical Interface is HMAC-SHA1, although any key dependent one-way hash function could be used.

[0009] Signatures are only of use if they can be validated. For example, QA Device A produces a signature for data and QA Device B can check if the signature is valid for that particular data. This implies that A and B must share some secret information so that they can generate equivalent signatures.

[0010] Common key signature generation is when QA Device A and QA Device B share the exact same key i.e. key  $K_A$ =key  $K_B$ . Thus the signature for a message produced by A using  $K_A$  can be equivalently produced by B using  $K_B$ . In other words  $SIG_{KA}(d)$ = $SIG_{KB}(d)$  because key  $K_A$ =key  $K_B$ .

[0011] However, common key authentication has some disadvantages. For example, if a first entity wants to communicate with a series of other entities, it can share a single common key with all of them. However, this means that each of the entities will be able to authenticate (and emulate) messages from each other. One way around this is to give each of the other entities its own key, and store a copy of each of the keys in the first entity. However, where large numbers of entities are involved, an unacceptable number of keys may need to be stored in the first entity.

[0012] The problem is exacerbated when it is desirable to enable a second entity to communicate with a third entity, where the third entity has a key to enable communication, but the second entity does not.

[0013] It would be desirable to provide a method of authenticated communication that addressed at least some of the problems of the prior art.

### SUMMARY OF THE INVENTION

[0014] In a first aspect the present invention provides a method of enabling or disabling a verification process of a first entity in response to a predetermined event, the first entity having at least one associated bit-pattern and at least one variant key, each of the variant keys having been generated by applying a one way function to: a base key; and one or more of the at least one bit-patterns, respectively; or one or more alternative bit patterns, each of the alternative bit-patterns being based on one of the at least one bit-patterns, the method comprising:

- (a) determining that the predetermined event has happened; and

- (b) enabling or disabling at least one of the first variant keys in response to the predetermined event.

[0015] Optionally, step (a) includes disabling at least one of the variant keys, such that the disabled at least one variant key can no longer be used to digitally sign information in that entity.

[0016] Optionally, step (a) includes disabling at least one of the variant keys, such that the disabled at least one variant key can no longer be used to verify information signed by one or more respective base keys related to the disabled at least one variant key in that entity.

[0017] Optionally, the step of disabling the at least one variant key includes modifying a status of a flag associated with that at least one variant key.

[0018] Optionally, the step of disabling the at least one variant key includes deleting that at least one variant key.

[0019] Optionally, the step of disabling the at least one variant key includes modifying that at least one variant key

[0020] Optionally, the event is a predetermined point in time being reached or passed.

[0021] Optionally, the first entity includes a plurality of the variant keys, the plurality of variant keys being based on the result of a one way function applied to: a respective one of a corresponding plurality of base keys; and one of the at least one bit-patterns or one of the at least one alternative bit-patterns, the method comprising:

[0022] determining that a predetermined event related to one of the variant keys has happened; and

[0023] enabling or disabling at least one of the plurality of variant keys with which the predetermined event is associated.

[0024] Optionally, each base key has a corresponding sequence of predetermined events associated with them, the method including the steps of:

(a) determining that one of the predetermined event has happened; and

(b) enabling or disabling the variant key in the sequence corresponding to predetermined event that is determined to have happened.

[0025] Optionally, the variant keys are disabled in the order of the sequence of predetermined events.

[0026] Optionally, the sequence of events is chronological.

[0027] Optionally, each of the events includes a time being reached.

[0028] Optionally, the step of determining that one of the events has happened includes receiving a time from a trusted source.

[0029] Optionally, the time is a date.

[0030] Optionally, the date is determined with a resolution of a month.

[0031] Optionally, the predetermined event includes detection of compromise of one or more of the variant keys, the method comprising disabling the one or more variant keys detected as compromised.

[0032] Optionally, the predetermined event includes suspect compromise of one or more of the variant keys, the method comprising disabling the one or more variant keys suspected of being compromised.

[0033] In a second aspect the present invention provides a method of manufacturing second entities for use in the verification process with a first entity, each of the first entities including at least first and second variant key, the first variant key having been generated by applying a one way function to a first base key and a first bit-pattern, and the second variant

key having been generated by applying a one way function to a second base key and a second bit-pattern, the method comprising the steps of:

[0034] manufacturing a plurality of second entities for use with the first entities, each of the second entities including at least the first base key; and

[0035] upon the first variant key being disabled in response to one of the predetermined event, manufacturing a plurality of third entities for use with the first entities, each of the third entities including at least the second base key.

[0036] Optionally, the first variant key is automatically disabled in response to a predetermined event.

[0037] Optionally, the method further includes the step of causing the first variant key to be disabled.

[0038] Optionally, the first variant key is disabled in response to a time being reached.

[0039] Optionally, at least some of the first entities have one or more further variant keys, each of the respective further variant keys having been generated by applying a one way function to respective further base keys and bit-patterns, each of the variant keys being enabled or disabled in response to respective predetermined events, the method comprising the step of manufacturing a sequence of sets of second entities, each set of the second entities being manufactured such that the variant key corresponding to its base key is enabled for the verification process during the life of that set.

[0040] Optionally, the predetermined events are selected such that the variant keys corresponding with the base keys of more than one of the sets are enabled at once.

[0041] Optionally, the method includes using a first entity configured to authenticate a digital signature supplied by a second entity, wherein one of the entities includes a base key and the other of the entities includes a variant key and a bit-pattern, the variant key being based on the result of applying a one way function to the base key and the bit-pattern, the digital signature having been generated by the second entity using its key to digitally signing at least part of data to be authenticated, the first entity being configured to:

- (a) receive the digital signature from the second entity;

- (b) receive the data; and

- (c) authenticate the digital signature based on the received data and the first entity's key.

[0042] Optionally, the method includes using a first entity including:

[0043] a first bit-pattern;

[0044] a non-volatile memory storing resource data;

[0045] a first base key for use with at least a first variant key;

[0046] a second variant key for use with a second base key, the second variant key being the result of a one way function applied to: the second base key; and the first bit-pattern or a modified bit-pattern based on the first bit-pattern.

[0047] Optionally, the method includes using a system for enabling authenticated communication between a first entity and at least one other entity, the system including a second entity, wherein:

[0048] the first entity and the second entity share transport keys; and

[0049] the second entity includes at least one authentication key configured to be transported from the second entity to the first entity using the transport keys, the authentication key being usable to enable the authenticated communication by the first entity.

[0050] Optionally, the method includes storing a first bitpattern in non-volatile memory of a device, the method comprising:

(a) applying a one way function to a second bit-pattern associated with the device, thereby to generate a first result;

(b) applying a second function to the first result and the first bit-pattern, thereby to generate a second result; and

(c) storing the second result in the memory, thereby indirectly storing the first bit-pattern.

[0051] Optionally, the method includes storing a bit-pattern in each of a plurality of devices, each of the devices having a memory, the method comprising, for each device:

(a) determining a first memory location; and

(b) storing the bit-pattern at the first memory location;

[0052] wherein the first memory locations are different in at least a plurality of the respective devices.

[0053] Optionally, the method includes storing at least one functionally identical code segment in each of a plurality of devices, each of the devices having a memory, the method comprising, for each device:

(a) determining a first memory location; and

(b) storing a first of the at least one code segments in the memory at the first memory location;

[0054] wherein the first memory location is different in at least a plurality of the respective devices.

[0055] Optionally, the method includes providing a sequence of nonces  $(R0, R1, R2, \dots)$  commencing with a current seed of a sequence of seeds  $(x1, x2, x3, \dots)$ , the method comprising:

(a) applying a one-way function to the current seed, thereby to generate a current nonce;

(b) outputting the current nonce;

(c) using the current seed to generate a next seed in a sequence of seeds, the seed so generated becoming the current seed; and

(c) repeating steps (a) to (c) as required to generate further nonces in the sequence of nonces.

[0056] Optionally, the method includes storing multiple first bit-patterns in non-volatile memory of a device, the method comprising, for each of the first bit-patterns to be stored:

(a) applying a one way function to a third bit-pattern based on a second bit-pattern associated with the device, thereby to generate a first result;

(b) applying a second function to the first result and the first bit-pattern, thereby to generate a second result; and

(c) storing the second result in the memory, thereby indirectly storing the first bit-pattern;

[0057] wherein the third bit-patterns used for the respective first bit-patterns are relatively unique compared to each other.

### BRIEF DESCRIPTION OF THE DRAWINGS

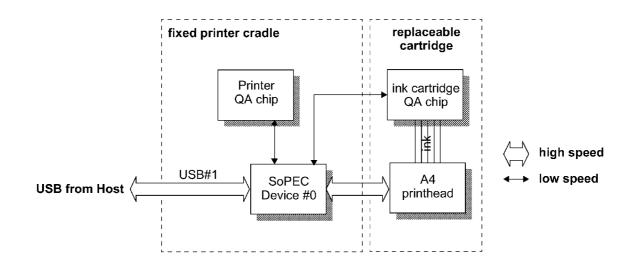

[0058] FIG. 1. Single SoPEC A4 Simplex system

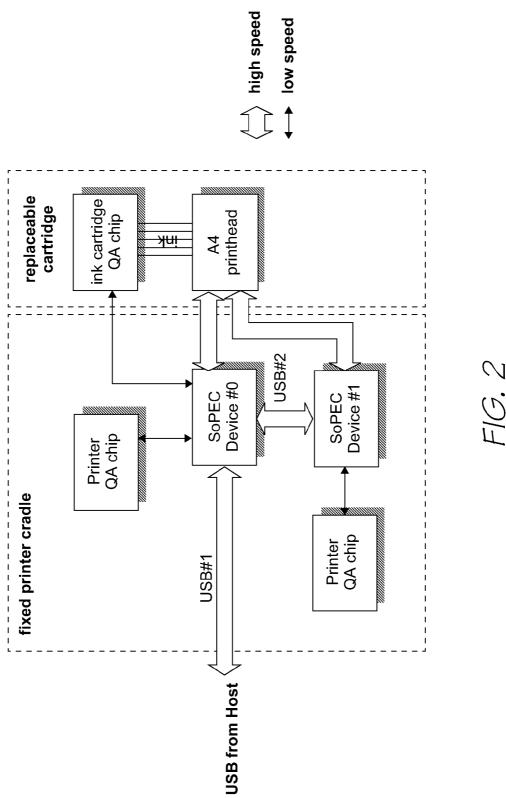

[0059] FIG. 2. Dual SoPEC A4 Simplex system

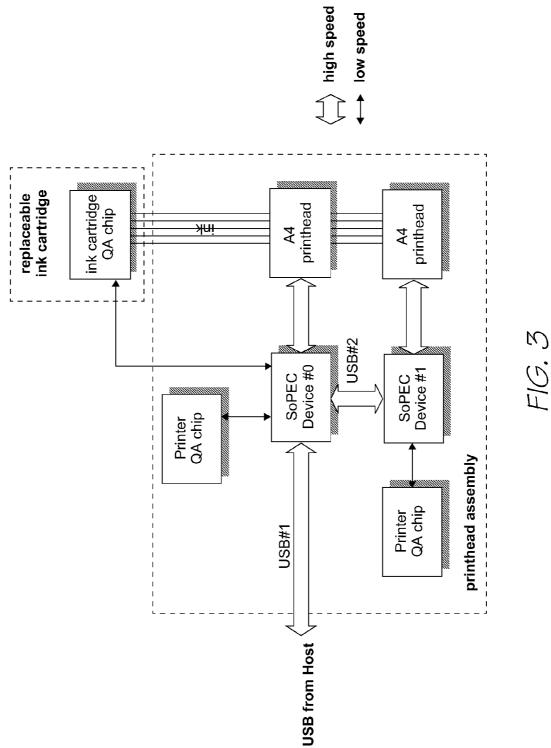

[0060] FIG. 3. Dual SoPEC A4 Duplex system

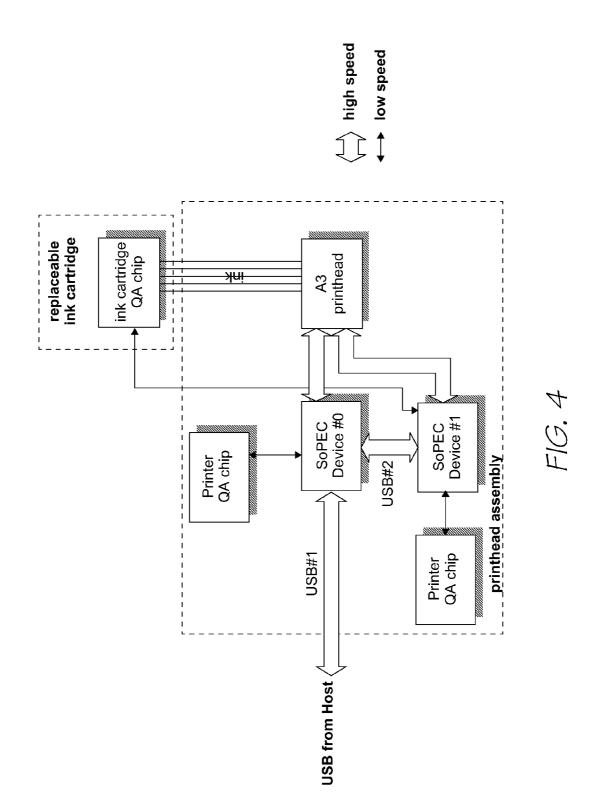

[0061] FIG. 4. Dual SoPEC A3 simplex system

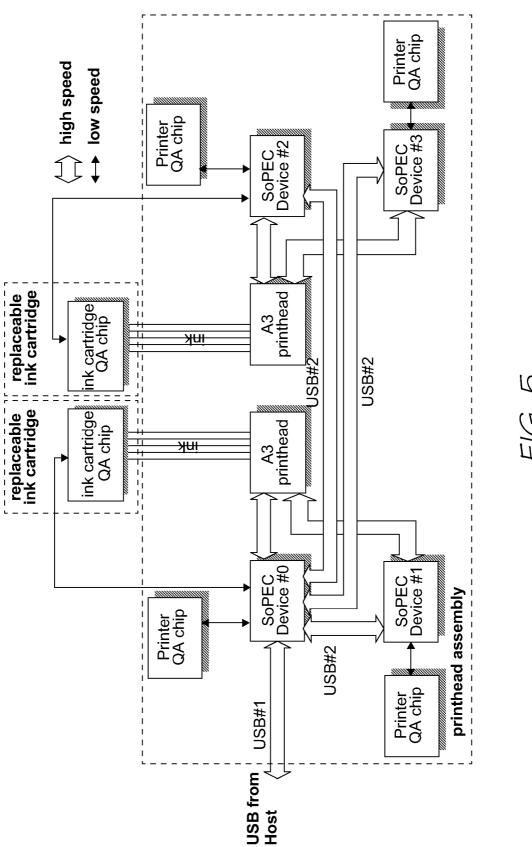

[0062] FIG. 5. Quad SoPEC A3 duplex system

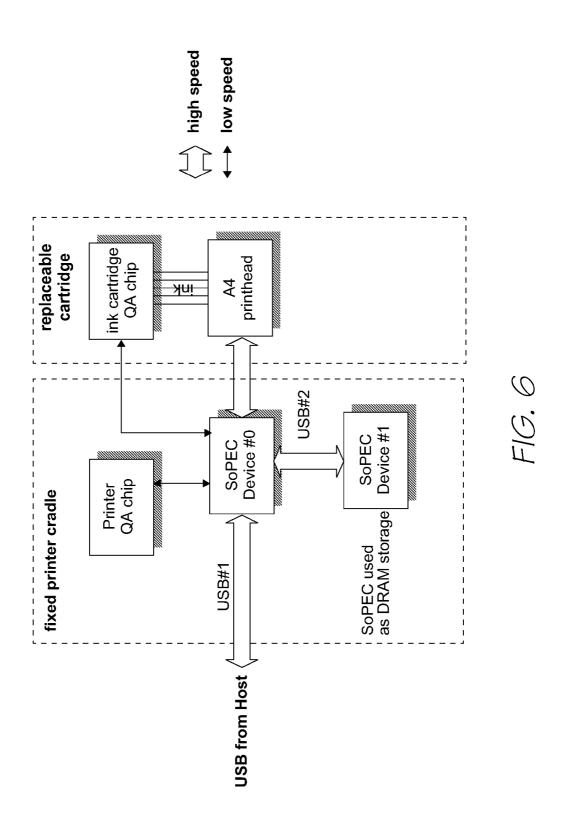

[0063] FIG. 6. SoPEC A4 Simplex system with extra SoPEC used as DRAM storage

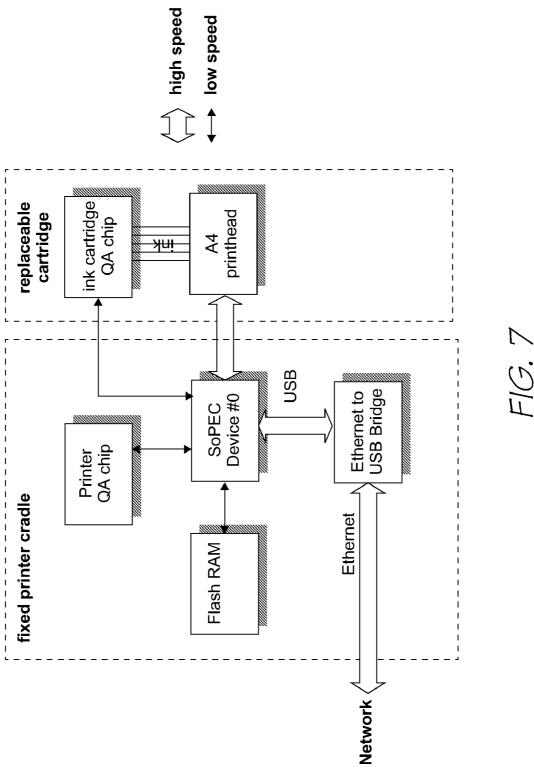

$\cite{Model}$  FIG. 7. SoPEC A4 Simplex system with network connection to Host PC

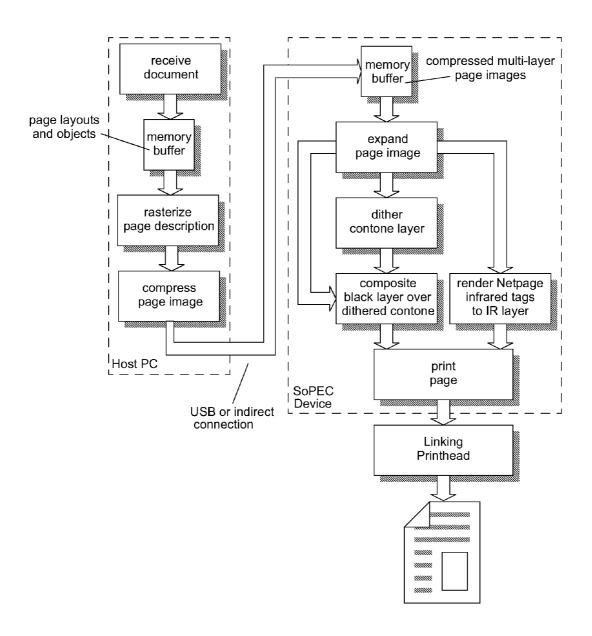

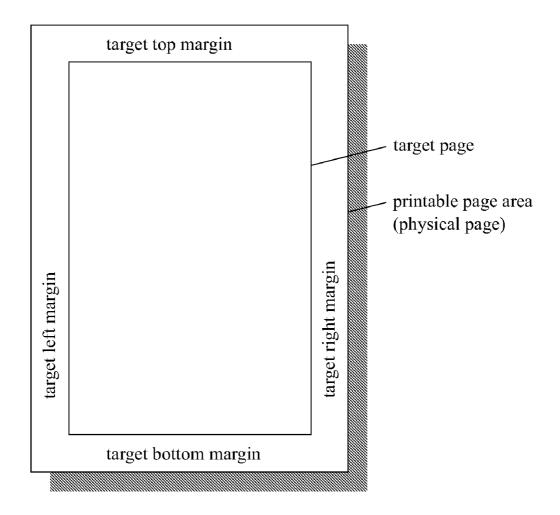

[0065] FIG. 8. Document data flow

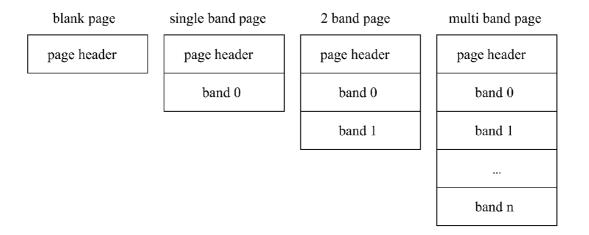

[0066] FIG. 9. Pages containing different numbers of bands

[0067] FIG. 10. Contents of a page band

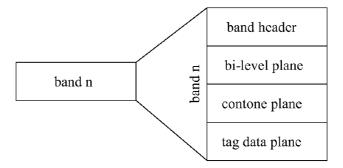

[0068] FIG. 11. Page data path from host to SoPEC

[0069] FIG. 12. Page structure

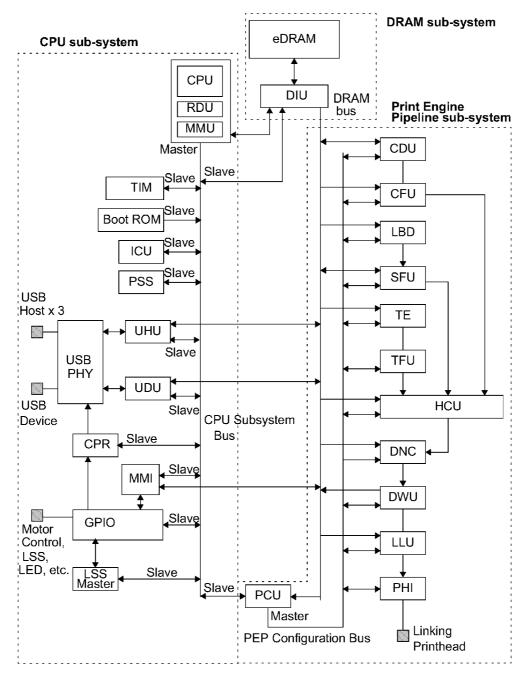

[0070] FIG. 13. SoPEC System Top Level partition

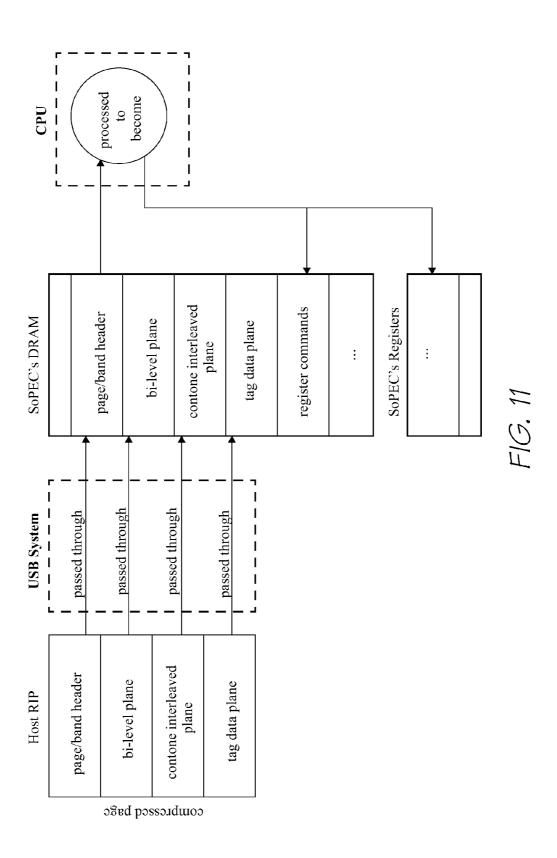

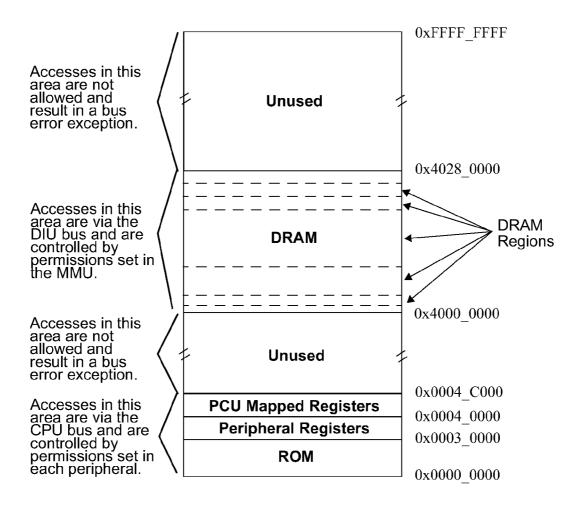

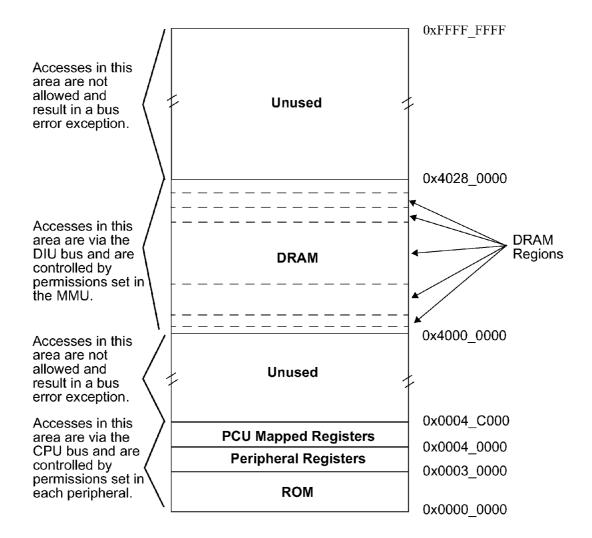

[0071] FIG. 14. Proposed SoPEC CPU memory map (not to scale)

[0072] FIG. 15. Possible USB Topologies for Multi-SoPEC systems

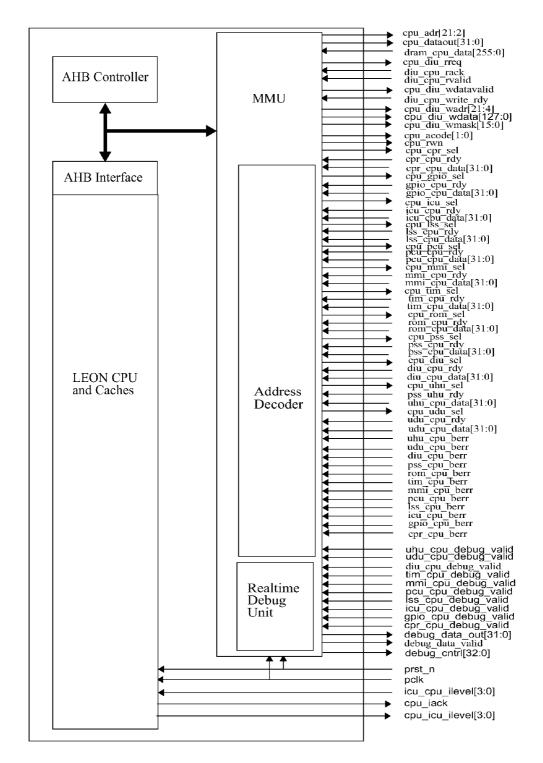

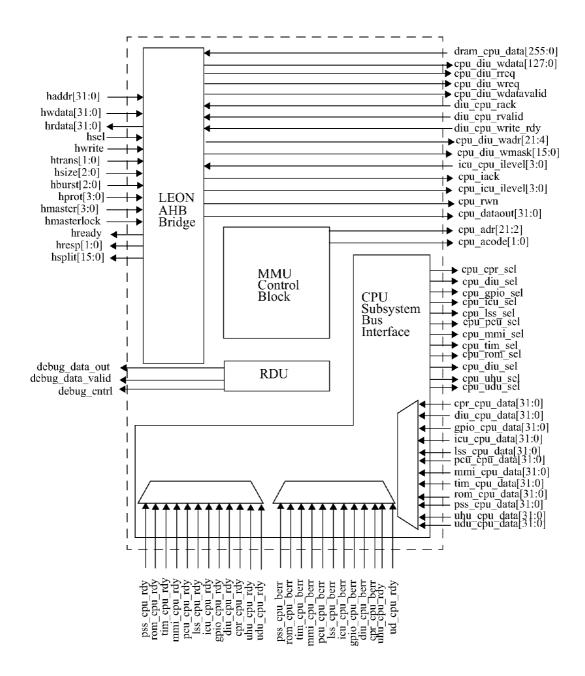

[0073] FIG. 16. CPU block diagram

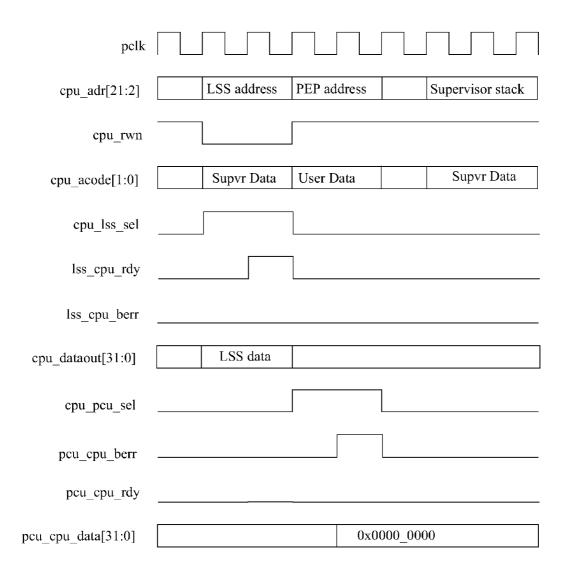

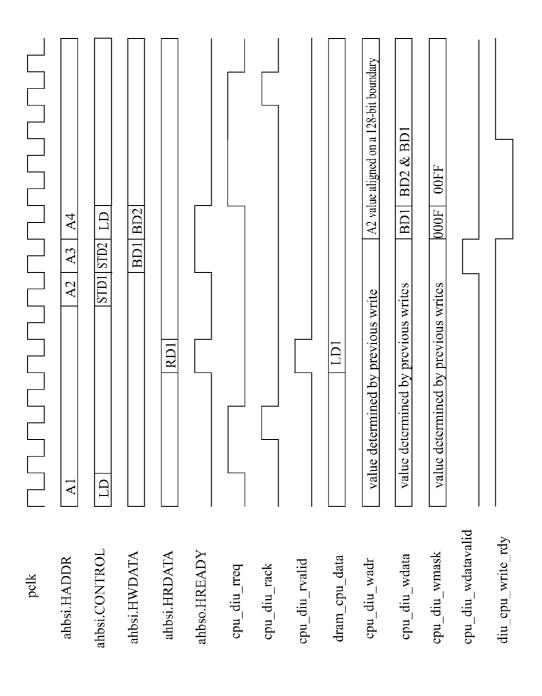

[0074] FIG. 17. CPU bus transactions

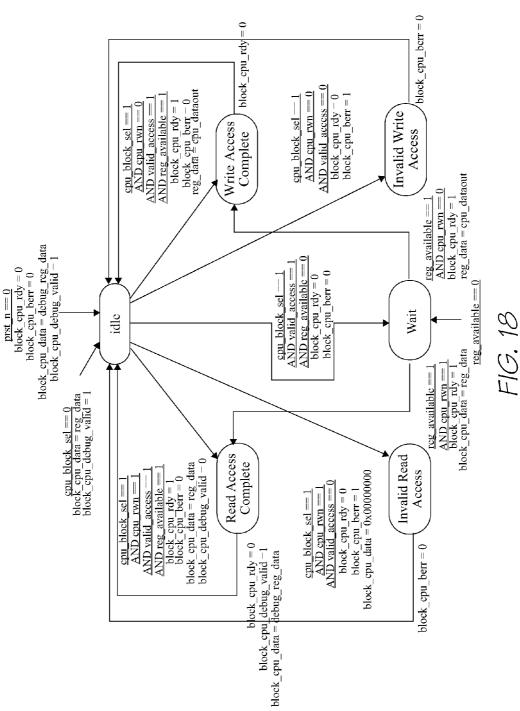

[0075] FIG. 18. State machine for a CPU subsystem slave

[0076] FIG. 19. Proposed SoPEC CPU memory map (not to scale)

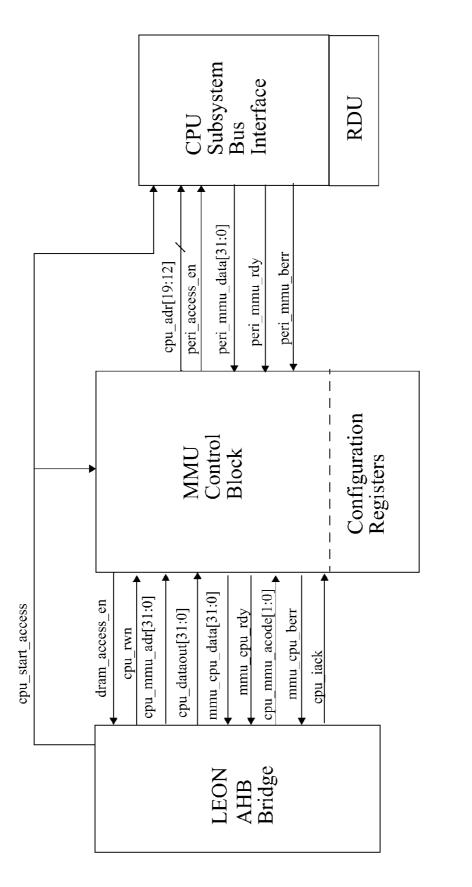

[0077] FIG. 20. MMU Sub-block partition, external signal view

[0078] FIG. 21. MMU Sub-block partition, internal signal view

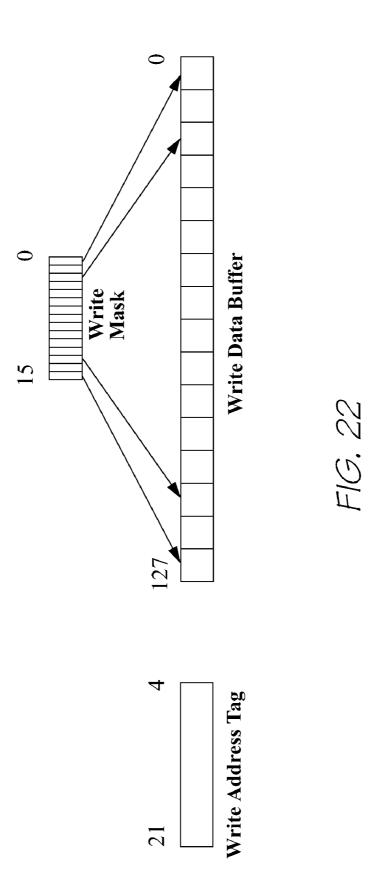

[0079] FIG. 22. DRAM Write buffer

[0080] FIG. 23. DIU waveforms for multiple transactions

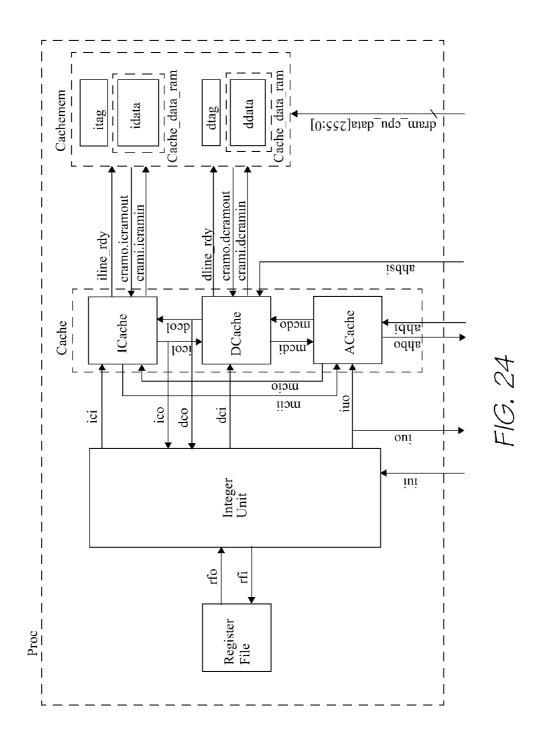

[0081] FIG. 24. SoPEC LEON CPU core

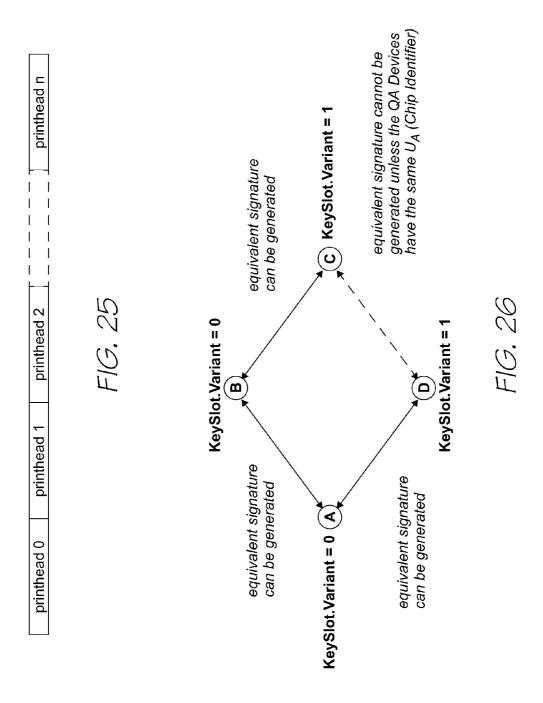

[0082] FIG. 25. Linking Printhead Concept

[0083] FIG. 26. Equivalent signature generation

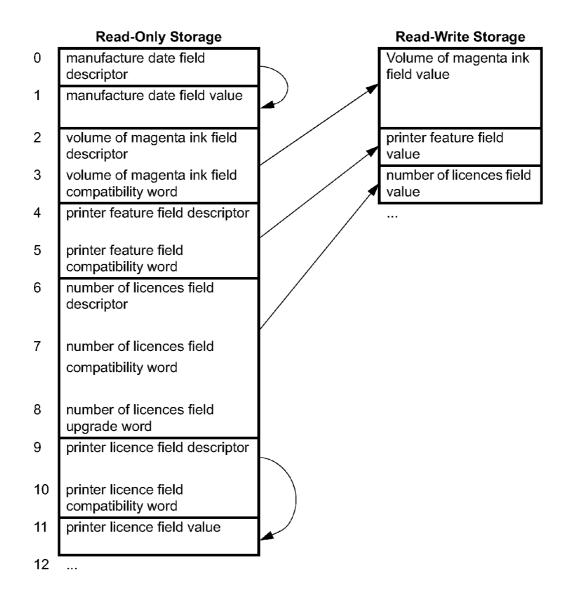

[0084] FIG. 27. An allocation of words in memory vectors

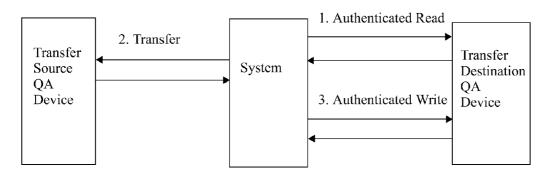

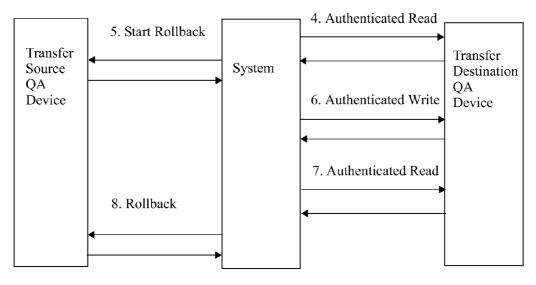

[0085] FIG. 28. Transfer and rollback process

## DETAILED DESCRIPTION OF PREFERRED EMBODIMENT

[0086] Also throughout this description, "printhead module" and "printhead" are used somewhat interchangeably. Technically, a "printhead" comprises one or more "printhead modules", but occasionally the former is used to refer to the latter. It should be clear from the context which meaning should be allocated to any use of the word "printhead".

[0087] A SoPEC ASIC (Small office home office Print Engine Controller) suitable for use in price sensitive SoHo printer products is described. The SoPEC ASIC is intended to be a relatively low cost solution for linking printhead control, replacing the multichip solutions in larger more professional systems with a single chip. The increased cost competitiveness is achieved by integrating several systems such as a modified PEC1 printing pipeline, CPU control system, peripherals and memory sub-system onto one SoC ASIC, reducing component count and simplifying board design. SoPEC contains features making it suitable for multifunction or "all-in-one" devices as well as dedicated printing systems. [0088] Basic features of the preferred embodiment of SoPEC include:

[0089] Continuous 30 ppm operation for 1600 dpi output at A4/Letter.

[0090] Linearly scalable (multiple SoPECs) for increased print speed and/or page width.

[0091] 192 MHz internal system clock derived from lowspeed crystal input

[0092] PEP processing pipeline, supports up to 6 color channels at 1 dot per channel per clock cycle

[0093] Hardware color plane decompression, tag rendering, halftoning and compositing

[0094] Data formatting for Linking Printhead

[0095] Flexible compensation for dead nozzles, printhead misalignment etc.

[0096] Integrated 20 Mbit (2.5 MByte) DRAM for print data and CPU program store

[0097] LEON SPARC v8 32-bit RISC CPU

[0098] Supervisor and user modes to support multithreaded software and security [0099] 1 kB each of I-cache and D-cache, both direct mapped, with optimized 256-bit fast cache update.

[0100] 1×USB2.0 device port and 3×USB2.0 host ports (including integrated PHYs)

[0101] Support high speed (480 Mbit/sec) and full speed (12 Mbit/sec) modes of USB2.0

[0102] Provide interface to host PC, other SoPECs, and external devices e.g. digital camera

[0103] Enable alternative host PC interfaces e.g. via external USB/ethernet bridge

[0104] Glueless high-speed serial LVDS interface to multiple Linking Printhead chips

[0105] 64 remappable GPIOs, selectable between combinations of integrated system control components:

[0106] 2×LSS interfaces for QA chip or serial EEPROM

[0107] LED drivers, sensor inputs, switch control outputs

[0108] Motor controllers for stepper and brushless DC motors

[0109] Microprogrammed multi-protocol media interface for scanner, external RAM/Flash, etc.

[0110] 112-bit unique ID plus 112-bit random number on each device, combined for security protocol support

[0111] IBM Cu-11 0.13 micron CMOS process, 1.5V core supply, 3.3V IO.

[0112] 208 pin Plastic Quad Flat Pack

[0113] The SoPEC device can be used in several printer configurations and architectures.

[0114] In the general sense, every preferred embodiment SoPEC-based printer architecture will contain:

[0115] One or more SoPEC devices.

[0116] One or more linking printheads.

[0117] Two or more LSS busses.

[0118] Two or more QA chips.

[0119] Connection to host, directly via USB2.0 or indirectly.

[0120] Connections between SoPECs (when multiple SoPECs are used).

[0121] The Host PC rasterizes and compresses the incoming document on a page by page basis. The page is restructured into bands with one or more bands used to construct a page. The compressed data is then transferred to the SoPEC device directly via a USB link, or via an external bridge e.g. from ethernet to USB. A complete band is stored in SoPEC embedded memory. Once the band transfer is complete the SoPEC device reads the compressed data, expands the band, normalizes contone, bi-level and tag data to 1600 dpi and transfers the resultant calculated dots to the linking printhead.

[0122] The SoPEC device can print a full resolution page with 6 color planes. Each of the color planes can be generated from compressed data through any channel (either JPEG compressed, bi-level SMG4 fax compressed, tag data generated, or fixative channel created) with a maximum number of 6 data channels from page RIP to linking printhead color planes.

[0123] The mapping of data channels to color planes is programmable. This allows for multiple color planes in the printhead to map to the same data channel to provide for redundancy in the printhead to assist dead nozzle compensation.

[0124] Also a data channel could be used to gate data from another data channel. For example in stencil mode, data from the bilevel data channel at 1600 dpi can be used to filter the

contone data channel at 320 dpi, giving the effect of 1600 dpi edged contone images, such as 1600 dpi color text.

[0125] The SoPEC device typically stores a complete page of document data on chip. The amount of storage available for compressed pages is limited to 2 Mbytes, imposing a fixed maximum on compressed page size. SoPEC would not be capable of printing worst case pages unless they are split into bands and printing commences before all the bands for the page have been downloaded. The page sizes in the table are shown for comparison purposes and would be considered reasonable for a professional level printing system. The SoPEC device is aimed at the consumer level and would not be required to print pages of that complexity. If a document with more complex pages is required, the page RIP software in the host PC can determine that there is insufficient memory storage in the SoPEC for that document. In such cases the RIP software can take two courses of action:

[0126] It can increase the compression ratio until the compressed page size will fit in the SoPEC device, at the expense of print quality, or

[0127] It can divide the page into bands and allow SoPEC to begin printing a page band before all bands for that page are downloaded.

**[0128]** Once SoPEC starts printing a page it cannot stop; if SoPEC consumes compressed data faster than the bands can be downloaded a buffer underrun error could occur causing the print to fail. A buffer underrun occurs if a line synchronisation pulse is received before a line of data has been transferred to the printhead.

[0129] Other options which can be considered if the page does not fit completely into the compressed page store are to slow the printing or to use multiple SoPECs to print parts of the page. Alternatively, a number of methods are available to provide additional local page data storage with guaranteed bandwidth to SoPEC, for example a Storage SoPEC.

[0130] The SoPEC is a page rendering engine ASIC that takes compressed page images as input, and produces decompressed page images at up to 6 channels of bi-level dot data as output. The bi-level dot data is generated for the Memjet linking printhead. The dot generation process takes account of printhead construction, dead nozzles, and allows for fixative generation.

[0131] A single SoPEC can control up to 12 linking printheads and up to 6 color channels at >10,000 lines/sec, equating to 30 pages per minute. A single SoPEC can perform full-bleed printing of A4 and Letter pages. The 6 channels of colored ink are the expected maximum in a consumer SOHO, or office Memjet printing environment:

[0132] CMY, for regular color printing.

[0133] K, for black text, line graphics and gray-scale printing.

[0134] IR (infrared), for Netpage-enabled applications.

[0135] F (fixative), to enable printing at high speed. Because the Memjet printer is capable of printing so fast, a fixative may be required on specific media types (such as calendared paper) to enable the ink to dry before the page touches a previously printed page. Otherwise the pages may bleed on each other. In low speed printing environments, and for plain and photo paper, the fixative is not be required.

[0136] SoPEC is color space agnostic. Although it can accept contone data as CMYX or RGBX, where X is an optional 4th channel (such as black), it also can accept contone data in any print color space. Additionally, SoPEC pro-

vides a mechanism for arbitrary mapping of input channels to output channels, including combining dots for ink optimization, generation of channels based on any number of other channels etc. However, inputs are typically CMYK for contone input, K for the bi-level input, and the optional Netpage tag dots are typically rendered to an infra-red layer. A fixative channel is typically only generated for fast printing applications

[0137] SoPEC is resolution agnostic. It merely provides a mapping between input resolutions and output resolutions by means of scale factors. The expected output resolution is 1600 dpi, but SoPEC actually has no knowledge of the physical resolution of the linking printhead.

[0138] SoPEC is page-length agnostic. Successive pages are typically split into bands and downloaded into the page store as each band of information is consumed and becomes free

[0139] SoPEC provides mechanisms for synchronization with other SoPECs. This allows simple multi-SoPEC solutions for simultaneous A3/A4/Letter duplex printing. However, SoPEC is also capable of printing only a portion of a page image. Combining synchronization functionality with partial page rendering allows multiple SoPECs to be readily combined for alternative printing requirements including simultaneous duplex printing and wide format printing.

[0140] The required printing rate for a single SoPEC is 30 sheets per minute with an inter-sheet spacing of 4 cm. To achieve a 30 sheets per minute print rate, this requires:

[0141] 300 mm×63 (dot/mm)/2 sec=105.8 seconds per line, with no inter-sheet gap.

[0142] 340 mm×63 (dot/mm)/2 sec=93.3 seconds per line, with a 4 cm inter-sheet gap.

[0143] A printline for an A4 page consists of 13824 nozzles across the page. At a system clock rate of 192 MHz, 13824 dots of data can be generated in 69.2 seconds. Therefore data can be generated fast enough to meet the printing speed requirement.

[0144] Once generated, the data must be transferred to the printhead. Data is transferred to the printhead ICs using a 288 MHz clock (½ times the system clock rate). SoPEC has 6 printhead interface ports running at this clock rate. Data is 8b/10b encoded, so the throughput per port is 0.8×288=230.4 Mb/sec. For 6 color planes, the total number of dots per printhead IC is 1280×6=7680, which takes 33.3 seconds to transfer. With 6 ports and 11 printhead ICs, 5 of the ports address 2 ICs sequentially, while one port addresses one IC and is idle otherwise. This means all data is transferred on 66.7 seconds (plus a slight overhead). Therefore one SoPEC can transfer data to the printhead fast enough for 30 ppm printing

[0145] From the highest point of view the SoPEC device consists of 3 distinct subsystems

[0146] CPU Subsystem

[0147] DRAM Subsystem

[0148] Print Engine Pipeline (PEP) Subsystem

[0149] See FIG. 13 for a block level diagram of SoPEC.

[0150] The CPU subsystem controls and configures all aspects of the other subsystems. It provides general support for interfacing and synchronising the external printer with the internal print engine. It also controls the low speed communication to the QA chips. The CPU subsystem contains various peripherals to aid the CPU, such as GPIO (includes motor control), interrupt controller, LSS Master, MMI and general timers. The CPR block provides a mechanism for the CPU to

powerdown and reset individual sections of SoPEC. The UDU and UHU provide high-speed USB2.0 interfaces to the host, other SoPEC devices, and other external devices. For security, the CPU supports user and supervisor mode operation, while the CPU subsystem contains some dedicated security components.

[0151] The DRAM subsystem accepts requests from the CPU, UHU, UDU, MMI and blocks within the PEP subsystem. The DRAM subsystem (in particular the DIU) arbitrates the various requests and determines which request should win access to the DRAM. The DIU arbitrates based on configured parameters, to allow sufficient access to DRAM for all requesters. The DIU also hides the implementation specifics of the DRAM such as page size, number of banks, refresh rates etc.

[0152] The Print Engine Pipeline (PEP) subsystem accepts compressed pages from DRAM and renders them to bi-level dots for a given print line destined for a printhead interface that communicates directly with up to 12 linking printhead ICs.

[0153] The first stage of the page expansion pipeline is the CDU, LBD and TE. The CDU expands the JPEG-compressed contone (typically CMYK) layer, the LBD expands the compressed bi-level layer (typically K), and the TE encodes Netpage tags for later rendering (typically in IR, Y or K ink). The output from the first stage is a set of buffers: the CFU, SFU, and TFU. The CFU and SFU buffers are implemented in DRAM.

[0154] The second stage is the HCU, which dithers the contone layer, and composites position tags and the bi-level spot0 layer over the resulting bi-level dithered layer. A number of options exist for the way in which compositing occurs. Up to 6 channels of bi-level data are produced from this stage. Note that not all 6 channels may be present on the printhead. For example, the printhead may be CMY only, with K pushed into the CMY channels and IR ignored. Alternatively, the position tags may be printed in K or Y if IR ink is not available (or for testing purposes).

[0155] The third stage (DNC) compensates for dead nozzles in the printhead by color redundancy and error diffusing dead nozzle data into surrounding dots.

[0156] The resultant bi-level 6 channel dot-data (typically CMYK-IRF) is buffered and written out to a set of line buffers stored in DRAM via the DWU.

[0157] Finally, the dot-data is loaded back from DRAM, and passed to the printhead interface via a dot FIFO. The dot FIFO accepts data from the LLU up to 2 dots per system clock cycle, while the PHI removes data from the FIFO and sends it to the printhead at a maximum rate of 1.5 dots per system clock cycle.

[0158] Manufacturers of systems that require consumables (such as laser printers that require toner cartridges) have addressed the problem of authenticating consumables with varying levels of success. Most have resorted to specialized packaging that involves a patent. However this does not stop home refill operations or clone manufacture in countries with weak industrial property protection. The prevention of copying is important to prevent poorly manufactured substitute consumables from damaging the base system. For example, poorly filtered ink may clog print nozzles in an ink jet printer, causing the consumer to blame the system manufacturer and not admit the use of non-authorized consumables.

[0159] In addition, some systems have operating parameters that may be governed by a license. For example, while a

specific printer hardware setup might be capable of printing continuously, the license for use may only authorise a particular print rate. The printing system would ideally be able to access and update the operating parameters in a secure, authenticated way, knowing that the user could not subvert the license agreement.

[0160] Furthermore, legislation in certain countries requires consumables to be reusable. This slightly complicates matters in that refilling must be possible, but not via unauthorized home refill or clone refill means.

[0161] To address these authentication problems, this document defines the QA Chip Logical Interface, which provides authenticated manipulation of a system's operating and consumable parameters. The interface is described in terms of data structures and the functions that manipulate them, together with examples of use. While the descriptions and examples are targeted towards the printer application, they are equally applicable in other domains. The QA Chip Logical Interface is now described.

[0162] The QA Chip Logical Interface is a logical interface, and is therefore implementation independent. Although this document does not cover implementation details on particular platforms, expected implementations include:

[0163] Software only

[0164] Off-the-shelf cryptographic hardware

[0165] ASICs, such as SBR4320 [2] and SOPEC [5] for physical insertion into printers and ink cartridges

[0166] Smart cards

[0167] An instance of a QA Chip Logical Interface (on any platform) is a QA Device.

[0168] QA Devices cannot talk directly to each other. A System is a logical entity which has one or more QA Devices connected logically (or physically) to it, and calls the functions on those QA Devices.

[0169] From the point of view of a QA Device receiving commands, System cannot inherently be trusted i.e. a given QA Device cannot tell if the System is trustworthy or not. System can, however, be constructed within a trustworthy environment (such as a SoPEC or within another physically secure computer system), and in these cases System can trust itself

[0170] Digital signatures are used throughout the authentication protocols of the QA Chip Logical Interface. A signature is produced by passing data plus a secret key through a keyed hash function. The signature proves that the data was signed by someone who knew the secret key.

[0171] The signature function used throughout the QA Chip Logical Interface is HMAC-SHA1.

[0172] When a System is constructed within a physically/ logically secure environment, then System itself is trusted, and any software/hardware running within that secure environment is trusted. A Trusted QA Device is simply a QA Device that resides within the same secure environment that System also resides in, and can therefore be trusted by System. This means that it is not possible for an attacker to subvert the communication between the System and the Trusted QA Device, or to replace the functionality of a QA Device by some other functionality. A Trusted QA Device enables a System to extend trust to external QA Devices. An example of a Trusted QA Device is a body of software inside a digitally signed program.

[0173] An External untrusted QA Device is a QA Device that resides external to the trusted environment of the system and is therefore untrusted. The purpose of the QA Chip Logi-

cal Interface is to allow the external untrusted QA Devices to become effectively trusted. This is accomplished when a Trusted QA Device shares a secret key with the external untrusted QA Device, or with a Translation QA Device (see below).

[0174] In a printing application, external untrusted QA Devices would typically be instances of SBR4320 implementations located in a consumable or the printer.

[0175] A Translation QA Device is used to translate signatures between QA Devices and extend effective trust when secret keys are not directly shared between QA Devices.

[0176] As an example, if a message is sent from QA Device A to QA Device C, but A and C don't share a secret key, then under normal circumstances C cannot trust the message because a signature generated by A cannot be verified by C. However if A and B share secret 1, and B and C share secret 2, and B is allowed to translate signatures for certain messages sent between secret 1 and secret 2, then B can be used as a Translation QA Device to allow those messages to be sent between A and C.

[0177] A Consumable QA Device is an external untrusted QA Device located in a consumable. It typically contains details about the consumable, including how much of the consumable remains.

[0178] In a printing application the consumable QA Device is typically found in an ink cartridge and is referred to as an Ink QA Device, or simply Ink QA since ink is the most common consumable for printing applications. However, other consumables in printing applications include media and impression counts, so consumable QA Device is more generic.

[0179] An Operating Parameter QA Device is an external untrusted device located within the infrastructure of a product, and contains at least some of the operating parameters of the application. Unlike the Trusted QA Device, an Operating Parameter QA Device is in a physically/logically untrusted section of the overall hardware/software.

**[0180]** An example of an Operating Parameter QA Device in a SoPEC-based printer system is the PrinterQA Device (or simply PrinterQA), that contains the operating parameters of the printer. The PrinterQA contains OEM and printer model information that indirectly specifies the non-upgradeable operating parameters of the printer, and also contains the upgradeable operating parameters themselves.

[0181] A Value Upgrader QA Device contains the necessary functions to allow a system to write an initial value (e.g. an ink amount) into another QA Device, typically a consumable QA Device. It also allows a system to refill/replenish a value in a consumable QA Device after use.

[0182] Whenever a value upgrader QA Device increases the amount of value in another QA Device, the value in the value upgrader QA Device is correspondingly decreased. This means the value upgrader QA Device cannot create value—it can only pass on whatever value it itself has been issued with. Thus a value upgrader QA Device can itself be replenished or topped up by another value upgrader QA Device.

[0183] An example of a value upgrader is an Ink Refill QA Device, which is used to fill/refill ink amount in an Ink QA Device.

[0184] A Parameter Upgrader QA Device contains the necessary functions to allow a system to write an initial parameter value (e.g. a print speed) into another QA Device, e.g. an

Operating Parameter QA Device. It also allows a system to change that parameter value at some later date.

[0185] A parameter upgrader QA Device is able to perform a fixed number of upgrades, and this number is effectively a consumable value. Thus the number of available upgrades decreases by 1 with each upgrade, and can be replenished by a value upgrader QA Device.

[0186] Secret transport keys are inserted into QA Devices during instantiation (e.g. manufacture). These keys must be replaced by the final secret keys when the purpose of the QA Device is known. The Key Replacement QA Device implements all necessary functions for replacing keys in other QA Devices.

[0187] An Authenticated Read is a read of data from a non-trusted QA Device that also includes a check of the signature. When the System determines that the signature is correct for the returned data (e.g. by asking a Trusted QA Device to test the signature) then the System is able to determine that the data has not been tampered en route from the read, and was actually stored on the non-trusted QA Device.

[0188] An authenticated write is a write to the data storage area in a QA Device where the write request includes both the new data and a signature. The signature is based on a key that has write access permission to the region of data in the QA Device, and proves to the receiving QA Device that the writer has the authority to perform the write. For example, a Value Upgrader Refilling Device is able to authorize a system to perform an authenticated write to upgrade a Consumable QA Device (e.g. to increase the amount of ink in an Ink QA Device).

[0189] The QA Device that receives the write request checks that the signature matches the data (so that it hasn't been tampered with en route) and also that the signature is based on the correct authorization key.

[0190] An authenticated write can be followed by an authenticated read to ensure (from the system's point of view) that the write was successful.

[0191] A non-authenticated write is a write to the data storage area in a QA Device where the write request includes only the new data (and no signature). This kind of write is used when the system wants to update areas of the QA Device that have no access-protection.

[0192] The QA Device verifies that the destination of the write request has access permissions that permit anyone to write to it. If access is permitted, the QA Device simply performs the write as requested.

[0193] A non-authenticated write can be followed by an authenticated read to ensure (from the system's point of view) that the write was successful.

[0194] Authorized modification of data refers to modification of data via authenticated writes.

[0195] The primary purpose of a QA Device is to securely hold application-specific data. For example if the QA Device is a Consumable QA Device for a printing application it may store ink characteristics and the amount of ink remaining.

[0196] For secure manipulation of data:

[0197] Data must be clearly identified (includes typing of data).

[0198] Data must have clearly defined access criteria and permissions.

[0199] Data must be able to be transferred securely from one QA Device to another, through a potentially insecure environment. **[0200]** In addition, each QA Device must be capable of storing multiple data elements, where each data element is capable of being manipulated in a different way to represent the intended use of that data element. For convenience, a data element is referred to as a field.

[0201] Each QA Device requires an identifier that allows unique identification of that QA Device by external systems, ensures that messages are received by the correct QA Device, and ensures that the same device can be used across multiple transactions.

[0202] Strictly speaking, the identifier only needs to be unique within the context of a key, since QA Devices only accept messages that are appropriately signed. However it is more convenient to have the instance identifier completely unique, as is the case with this design.

[0203] In certain circumstances it is useful for a Trusted QA Device to assume the instance identifier of an external untrusted QA Device in order to build a local trusted form of the external QA Device. It is the responsibility of the System to ensure that the correct device is used for particular messages. As an example, a Trusted QA Device in a SoPEC-based printing system has the same instance identifier as the external (untrusted) Printer QA so that the System can access functionality in the Trusted QA instead of the external untrusted Printer QA. The identifier functionality is provided by ChipId.

[0204] ChipId is the unique 64-bit QA Device identifier. The ChipId is set when the QA Device is instantiated, and cannot be changed during the lifetime of the QA Device.

[0205] A 64-bit ChipId gives a maximum of 1844674 trillion unique QA Devices.

[0206] Each QA Device contains a number of secret keys that are used for signature generation and verification. These keys serve three basic functions:

[0207] For reading, where they are used to verify that the read data came from the particular

[0208] QA Device and was not altered en route.

[0209] For writing, where they are used to authorise modification of data.

[0210] For transporting keys, where they are used in the process of encrypting and transporting new keys into the OA Device.

[0211] All of these functions are achieved by signature generation; a key is used to generate a signature for subsequent transmission from the device, and to generate a signature to compare against a received signature. The transportation function is additionally achieved by encryption.

[0212] The number of secret keys in a QA Device is given by NumKeys, and has a maximum value of 256, i.e. the number of keys for a particular implementation may be less than this. For convenience, we refer to a QA Device as having NumKeys keyslots, where each keyslot contains a single key. Thus the nth keyslot contains the nth key (where n has the range 0 to NumKeys-1). The keyslot concept is useful because a keyslot contains not only the bit-pattern of the secret key, but also additional information related to the secret key and its use within the QA Device. The term Keyslot[n]. xxx is used to describe the element named xxx within Keyslot n.

[0213] Each key is referred to as K, and the subscripted form  $K_n$  refers to the key in the nth keyslot. Thus  $K_n$ =Keyslot [n] K

[0214] The length of each key is 160 bits. 160 bits was chosen because the output signature length from the signature

generation function (HMAC-SHA1) is 160 bits, and a key longer than 160-bits does not add to the security of the function.

[0215] The security of the digital signatures relies upon keys being kept secret. To safeguard the security of each key, keys should be generated in a way that is not deterministic. Ideally the bit pattern representing a particular key should be a physically generated random number, gathered from a physically random phenomenon. Each key is initially programmed during QA Device instantiation.

[0216] For the convenience of the System, each key has a corresponding 18-bit KeyId which can be read to determine the identity or label of the key without revealing the value of the key itself. Since the relationship between keys and Keylds is 1:1 (they are both stored in the same keyslot), a system can read all the Keylds from a QA Device and know what key is stored in each of the keyslots. A KeyId of INVALID\_KEYID (=0) is the only predefined id, and indicates that the key is invalid and should not be used, although the QA Device itself will not specifically prevent its use. From a system perspective, the bit pattern of a key is undefined when KeyId=INVALID\_KEYID, and so cannot be guaranteed to match another key whose Keyld is also INVALID\_KEYID. The bit pattern for such a key should be set to a random bit pattern for the physical security of any other keys present in the QA Device.

**[0217]** To create a digital signature, the data to be signed (d) is passed together with a secret key (k) through a key dependent one-way hash function (SIG). i.e. signature= $SIG_k(d)$ . The key dependent one-way hash function used throughout the QA Chip Logical Interface is HMAC-SHA1, although from a theoretical sense any key dependent one-way hash function could be used.

[0218] Signatures are only of use if they can be validated i.e. QA Device A produces a signature for data and QA Device B can check if the signature is valid for that particular data. This implies that A and B must share some secret information so that they can generate equivalent signatures.

**[0219]** Common key signature generation is when QA Device A and QA Device B share the exact same key i.e. key  $K_A$ =key  $K_B$ . Thus the signature for a message produced by A using  $K_A$  can be equivalently produced by B using  $K_B$ . In other words  $SIG_{KA}(d)=SIG_{KB}(d)$  because key  $K_A$ =key  $K_B$ .

**[0220]** Variant key signature generation is when QA Device B holds a base key, and QA Device A holds a variant of that key such that  $K_A = \text{owf}(K_B, U_A)$  where owf is a one-way function based upon the base key  $(K_B)$  and a unique number in A  $(U_A)$ . A one-way function is required to create  $K_A$  from  $K_B$  or it would be possible to derive  $K_B$  if  $K_A$  were exposed. Thus A can produce  $SIG_{KA}$  (message), but for B to produce an equivalent signature B must produce  $K_A$  by being told  $V_A$  from A and using B's base key  $V_B$ .  $V_A$  is referred to as a variant key and  $V_A$  is referred to as the base key. Therefore, B can produce equivalent signatures from many QA Devices, each of which has its own unique variant of  $V_A$ . Since ChipId is unique to a given QA Device, we conveniently use that as  $V_A$ .

**[0221]** Common key signature generation is used when A and B are effectively equally available<sup>1</sup> to an attacker. Variant key signature generation is used when B is not readily available to an attacker, and A is readily available to an attacker. If an attacker is able to determine  $K_4$ , they do not know  $K_4$  for

any other QA Device of class A, and they are not able to determine  $K_B$ .

<sup>1</sup> The term "equally available" is relative. It typically means that the ease of availability of both are the effectively the same, regardless of price (e.g. both A and B are commercially available and effectively equally easy to come by).

**[0222]** When two or more devices share  $U_A$  (in our implementation,  $U_A$  is ChipId), then their variant keys can be effectively treated as common keys for signatures passed between them, but as variant keys when passed to other devices.

[0223] The QA Device producing or testing a signature needs to know if it must use the common or variant means of signature generation. Likewise, when a key is stored in a QA Device, the status of the key (whether it is a base or variant key) must be stored in the keyslot along with the key for future reference.

[0224] Therefore each keyslot contains a 1-bit Variant flag to hold the status of the key in that keyslot:

[0225] Variant=0 means the key in the keyslot is a base/common key

[0226] Variant=1 means the key in the keyslot is a variant key

[0227] The QA Device itself doesn't directly use the Variant setting. Instead, the System reads the value of variant from the desired keyslots in the two QA Devices (one QA Device will produce the signature, the other will check the signature) and informs the signature generation function and signature checking functions whether or not to use base or variant signature generation for a particular operation.

[0228] It is assumed in equivalent signature generation between 4 QA Devices A, B, C that each device has a single keyslot. KeySlot.KeyId of all four keys are the same i.e KeySlot[A].KeyId=KeySlot[B].KeyId=KeySlot[C].

KeyId=KeySlot[D].KeyId.

**[0229]** If KeySlot[A]. Variant=0 and KeySlot[B]. Variant=0, then a signature produced by A, can be equivalently produced by B because  $K_A = K_B$ .

[0230] If KeySlot[B]. Variant=0 and KeySlot[C]. Variant=1, then a signature produced by C, can be equivalently produced by B because  $K_C = f(K_B, ChipId_C)$ . Note that B must be told ChipId<sub>C</sub> for this to be possible.

**[0231]** If KeySlot[C]. Variant=1 and KeySlot[D]. Variant=1, then a signature produced by C, cannot be equivalently produced by D unless both QA Devices have the same  $U_A$  (i.e. they must share the same Chip Identifier) While C and D will typically not share a ChipId, in certain circumstances the System can read a QA Device's Chip Identifier and install it into another QA Device. Then, using key transport mechanisms, the two QA Devices can come to share a common variant key, and can thence generate and check signatures with each other.

**[0232]** If KeySlot[D].Variant=1 and KeySlot[A].Variant=0, then a signature produced by D, can be equivalently produced by A because  $K_D = f(K_A, \text{ChipId}_D)$ .

[0233] While it is theoretically possible that a system could permit each key to be used to perform all of these tasks, in most cases it is a security risk to allow this.

[0234] If any key can be used to transport any other key out of a QA Device, then a compromise of a single key means a compromise of all keys. The reason is that the compromised key can be used by an attacker to transport all other keys out of a QA Device. Some QA Devices (such as Key Replacement QA Devices) are specifically required to transport keys, while others (such as those devices used in consumables) should not ever transport their keys out.

[0235] During manufacture it is not always possible to know the final intended application for a given QA Device. For example, one may end up at OEM1 while another is

destined for OEM2. To decouple manufacture from installation of QA Devices, it is useful to place temporary batch keys into the QA Devices. Each of these keys should be replaceable by a different batch key or a final application key, but during their temporary existence these keys must not be capable of authenticating signatures writes of data. Thus they act as a transport key.

[0236] Likewise, in the Key Replacement QA Device, there is a need to differentiate between final use for a key in a QA Device, and storage of a key in one QA Device for subsequent injection into another. For example, a key may be a transport key when stored in QA Device A, and although we want to store that same key in a Key Replacement QA Device B for future injection into A, we do not want that key to be used to transport keys from B. Thus, if a key is not in its final intended keyslot, then it should have no abilities in that QA Device other than being transported out, and the intended use of the key (for example whether or not it will be a transport key when installed in its final destination) needs to be associated with that key.

[0237] From a security point of view there should be a time when a key in a given keyslot can be guaranteed to be in its final intended form i.e. it cannot be replaced later. If a key could be replaced at any time, attackers could potentially launch a denial of service attack by replacing keys with garbage, or could replace a key with one of their own choice. As an example, suppose keys k1 and k2 are both used to read value from a QA Device, write value to the QA Device, and to transport new keys into the QA Device. If either k1 or k2 is compromised, then the compromised key could be used to transport keys of choice to replace both keys and create value in the QA Device.

[0238] Therefore each keyslot contains 3 1-bit flags as follows:

[0239] KeyType: whether the key is a TransportKey (0) to be used for key transport and signing reads of key meta-information, or if it is a DataKey (1) to be used for signing data as well as key meta-information

[0240] TransportOut: whether or not the key can be transported out from this QA Device

[0241] UseLocally: whether or not the key is for use locally within this QA Device or not. For transport keys this means whether or not the transport key can be used to transport another key out from this QA Device.

[0242] The following examples assume 3 bits xyz are interpreted as:

[0243] x=KeyType [0244] y=TransportOut

[0245] z=UseLocally

[0246] A freshly manufactured QA Device A will most likely have the 3 bits for each keyslot set to 000 so that all the keys are replaceable.

[0247] To replace one of A's keys (k1) by another batch key (k2), key replacement QA Device B is required where B typically contains k1 with 3 bits set to 001, and k2 with 3 bits set to 010. After k2 has been transferred into A, the 3 bits within A will be now set to 000. Thus k2 cannot be used or replaced within B, but can be replaced within A.

[0248] To replace one of A's keys (k1) by a final use data key (k2), key replacement QA Device B is required where B typically contains k1 with 3 bits set to 001, and k2 with 3 bits set to 110. After k2 has been transferred into A, the 3 bits within A will be now set to 101. Thus k2 can be used within A but not B, and cannot be transported out of A.

[0249] Although there are KeyNum keyslots in a QA Device, not all keyslots may be required for a given application. For example, a QA Device may supply 256 keyslots, but only 2 keys may be required for a particular application. The remaining keyslots need to be invalidated so they cannot be used as a reference for signature checking or signature generation.

[0250] When QA Device A has a keyslot with KeyType, TransportOut, and UseLocally set to 000, then the key in that keyslot can be replaced.

[0251] To invalidate the keyslot in A where k1 is currently residing so that no further keys can ever be stored in that keyslot, key replacement QA Device B is required where B typically contains:

[0252] k1 with 3 bits set to 001

[0253] a base key k2 with 3 bits set to 110 and a KeyId of 0 [0254] After k2 has been transferred into A as a variant key, the 3 bits within A will be now set to 100. Thus k2 cannot be used within A, cannot be transported out of A, and cannot be replaced. Moreover, being a variant key in A, k2 will be different for each instance of A and will therefore be contribute to the entropy of A. Any system reading the Keylds that are present in A will see that the keyslot contains a key whose keyId is 0 (and is therefore invalid) and whose 2-bits specify that the key cannot be used.

[0255] Over the lifetime of a product, it may be desirable to retire a given key from use, either because of compromise or simply because it has been used for a specific length of time (and therefore to reduce the risk of compromise). Therefore the key in a keyslot needs to be invalidated by some means so that it cannot be used any more as a reference for signature checking or signature generation. From an audit-trail point of view, although a key has been retired from use, it is convenient to retain the key meta-information so that a System can know which keys have been retired.

[0256] In theory, a special command could be available in each QA Device to allow the caller to transform the KeyType, TransportOut, and UseLocally settings for a keyslot from some value to 100. The key in that slot would then be nontransportable non-usable, and therefore invalid. However it would not be possible to know the previous setting for the 3 bits once the key had become invalid.

[0257] It is therefore desirable to have a boolean in each keyslot that can be set to make a particular key invalid. If a key has been marked as invalid, then TransportOut and UseLocally are ignored and treated as 0, and the key cannot be replaced.

[0258] However, a single bit representation of this boolean over-complicates 4320-based implementations of QA Devices in that it is not possible to set a single bit in shadowed mode on a 4320 device (to change a key from valid to invalid). Instead, the page containing the key would need to be erased and the key reconstructed, tasks which need to take place during initial key replacement during manufacture, but which should not need to take place after the keys are all finalised. [0259] Therefore each keyslot contains a 4-bit boolean (which should be nybble-aligned within the keyslot data structure) referred to as Invalid, where 0000 represents a valid key in the keyslot, and non-zero represents an invalid key. A specific command (Invalidate Key) exists in the QA Logical Interface to allow a caller to invalidate a previously valid key. [0260] If Invalid is set to a non-zero value, then the key is

not used regardless of the settings for KeyType, TransportOut, and UseLocally.

[0261] In general each QA Device contains a number of data elements (each element referred to as a field), each of which can be operated upon by one or more keys. In the general case of an arbitrary device containing keys and fields, it is useful to have a set of permissions for each key on each field. For example, key 1 may have read-only permissions on field 1, but read/write permissions on field 2 and read/decrement-only permissions on field 3.

[0262] Although it can cater for all possibilities, a general scheme has size and complexity difficulties when implemented on a device with low storage capacity. In addition, the complexity of such a scheme is increased, if the device has to operate correctly with power-failures e.g. an operation must not create a logical inconsistency if power is removed partway through the operation.

[0263] Since the actual number of keys that can be stored in a low storage capacity QA Device depends on the complexity of the program code and the size of the data structures, it is useful to minimise the functional complexity and minimise the size of the structures while not knowing the final number of keys.

[0264] In particular, the scheme must cope with multiple keys having the same permissions for a field to support the following situations:

each of the various users of the QA Device has access to a different key, such that different users can be individually included or excluded from access

only a subset of keys are in use at any one time

[0265] The concept that supports this requirement is the keygroup. A keygroup contains a number of keys, and each field has a set of permissions with respect to the keygroups. Thus keygroup 1 (containing some number of keys) may have read-only permissions on field 1, but read/write permissions on field 2 and read/decrement-only permissions on field 3.

**[0266]** In the limit case of 1 key per keygroup, with an arbitrary number of keygroups, the storage requirements for the permissions on each field would be the same as the general case without keygroups, but by limiting the number of keygroups, the storage requirements for the permissions on each field can be pre-known, constant, and is decoupled from the actual number of keys in the device.

[0267] The number of keygroups in a QA Device is 4. This allows for 2 different keygroups that can transfer value into the QA Device, and for 2 different keygroups that can transfer value out of a QA Device, where each of the 4 keygroups is independent of the others. Note that transport keys do not need to be allocated a keygroup since they cannot be used to authorise reads or writes of data.

[0268] Thus each keyslot contains a 2-bit KeyGroup identifier. The value of KeyGroup is relevant only when the KeyType=DataKey.

[0269] For security concerns it is important that a field not be created until all the keys for a keygroup have been created. Otherwise an attacker may be able to add a known new key to an existing keygroup and thereby subvert the value associated with the field.

[0270] However it is not possible to simply not allow the creation of fields until all of the keys have been created. It may be that two distinct phases of programming occur, with creation of keys and data based on each phase. For example a stamp franking system may contain value in the form of ink plus a dollar amount. The keys and fields relating to ink may

be injected at one physical location, while the keys and fields relating to dollars may be injected at a separate location some time later.

[0271] It is therefore desirable to have a boolean indicator that indicates whether a particular keygroup is locked. Once a keygroup is locked, then no more keys can be added to that keygroup. The boolean indicator is accessible per keyslot rather than as a single indicator for each keygroup in order that someone reading the keyslot information can know:

whether they can add any more keys to a keygroup whether they can create fields with write-permissions for the keygroup

[0272] When a key is replaced, the keygroup for that key can be locked at the same time. This will cause the QA Device to change the status of all keys with the same KeyGroup value from keygroup-unlocked to keygroup-locked, thereby preventing the addition of any more keys in the keygroup.

[0273] However, a single bit representation of this boolean over-complicates 4320-based implementations of QA Devices in that it is not possible to set a single bit in shadowed mode on a 4320 device (to change a locked status from unlocked to locked). Instead, the page containing the key would need to be erased and the key reconstructed, and this would need to take place per key (where the KeyGroup matched).

[0274] Therefore each keyslot contains a 4-bit boolean (which should be nybble-aligned within the keyslot data structure) referred to as KeyGroupLocked, where 0000 represents that the keygroup to which the key in the keyslot belongs is unlocked (i.e. more keys can be added to the keygroup), and non-zero represents that the keygroup to which the key in the keyslot belongs is locked (i.e. more keys cannot be added to the keygroup).

[0275] It is finally worth noting that a Key Replacement QA Device does not need to check whether or not there are fields on the target device with write permissions related to a particular keygroup. The reason is that the target QA Device only allows field creation related to a keygroup if the keygroup is locked. Therefore if there was such a field in the target device one of the following is true:

the target QA Device is a fake one created by an attacker. If so, and if the attacker does not know the original key, then the replaced key will be of no value. If the attacker does know the original key, then they can determine the replacement key (since the replacement key is encrypted using the original key for transport) without creating a fake QA, and can therefore generate fake value as desired.

the target QA Device has come under physical attack (it's a real QA Device). If an attacker can do this, it's easier to allow the key replacement first, and then create a fake field. This situation cannot ever be detected by the Key Replacement QA Device

[0276] In an ideal world (for the owner of a secret key at least), a given secret key will remain secret forever. However it is prudent to minimise the loss that could occur should a key be compromised.

[0277] This is further complicated in a system where all of the components of a system are stored at the user site, potentially without direct connection to a central server that could appropriately update all components after a particular time period or if a compromise is known to have occurred.

[0278] To create rolling keys, two QA Devices A and B are required such that A and B are intended to work together via a conceptual key k. While a single key could be used for k, it

is more secure to limit the lifetime of any particular key, and to have a plan in place to remove a key from use should it be compromised.

[0279] Rolling keys are where multiple keys are stored in at least one of A and B such that different keys can be used at different times during the life of A and B, different instances of A and B at differing manufacture times can be programmed with different keys yet still work together, and keys can be retired from use in A and/or B.

[0280] In the simplest example of the problem, suppose A is embedded in a printer system that works with ink cartridges containing B. If A contains a single key k for working with B, then k is required for all Bs as long as A is deployed. A compromise of k lasts for the lifetime of A.

**[0281]** A rolling key example system for this example is where A contains multiple keys  $k_1, k_2 \ldots kn$ , each with a different KeyId, where each of these keys has the same permissions on datafields within A (typically they will all belong to the same keygroup in A). At initial manufacture, B contains a single key  $k_1$  (that is also present in A). For a given time period  $k_1$  can be used between A and B. At some later time (or if  $k_1$  is compromised), Bs are manufactured only containing  $k_2$ , and new As are manufactured only containing  $k_3, k_4 \ldots k_n$ ,  $k_{n+1}$ . At a later time, Bs are manufactured only containing  $k_3$  and new As are manufactured only containing  $k_3, k_4 \ldots k_n$ ,  $k_{n+1}, k_{n+2}$  etc.

[0282] Note that if the keys shared by A and B are all common keys, then a compromise of keys from A will compromise all future value in Bs. However if A contains the variant key form and B contains a base form of each key, then compromise of keys in A does not permit an attacker to know future keys in B and the attacker can therefore not create clone Bs until a real B is released and the base key is obtained from B. This means that the more variant keys that can be injected into A the more changes in B can be coped with out any loss of security.

**[0283]** In the example above, note that if  $k_1$  is compromised, an attacker can still manufacture clone Bs that will work on older As. It is therefore desirable to somehow invalidate  $k_1$  on older As at some point to reduce the impact of clone Bs. However it is not usually the case that an immediate cut-off point can be introduced. For example, once Bs are being manufactured with  $k_2$ , existing Bs containing  $k_1$  may still be in use and are still valid. Just because  $k_2$  is used with A doesn't mean that  $k_1$  should be invalidated in A immediately. Otherwise a valid user could not then use an older valid B in A after using a newer B in A. Likewise, new As typically need to be able to work with valid old Bs. Our example assumes that newer As won't work with older Bs.

[0284] Therefore if overlapping timing is required, then several valid keys in use at a time instead of having only a single valid key in use at a time. Once valid Bs are known to be out of circulation (e.g. due to an expiry date associated with a B) then a key can be officially retired from being included in the manufacture of new As, and can be invalidated in old As. The more keys that can be used, the finer-grained the resolution of timing for invalidating a particular key, and hence the greater the reduction in exposure.

[0285] For example, B may be an ink cartridge that has a use-by date of 12 months while A is a printer that must last for 5 years:

[0286] If A contains 5 keys, B is issued with a new key each year, and a new A is released each year, then k<sub>1</sub> will be in B during year1, k<sub>2</sub> will be in B during year2 etc. As

produced in year 2 will need to contain  $k_1$  since old Bs from the previous year are still valid. Only in year 3 can As be manufactured without  $k_1$ , and old As can have their  $k_1$  invalidated. Clone Bs can therefore be manufactured by an attacker causing loss during year 1 and 2. After year 2, those clone Bs won't work on new As, but will continue to work on old As until  $k_1$  has been invalidated on the old As.

[0287] If A contains 10 keys, B is issued with a new key every 6 months, and a new A is released every 6 months, then k<sub>1</sub> will be in B during the first 6 months, k<sub>2</sub> will be in B during the second six months etc. As produced in the second and third 6-months will need to contain k<sub>1</sub> since old Bs from the previous year are still valid. Only in the fourth 6-month can As be manufactured without k1, and old As can have their k<sub>1</sub> invalidated. Clone Bs can therefore be manufactured by an attacker causing loss during year 1 and the first half of year 2. After this time, those clone Bs won't work on new As, but will continue to work on old As until k, has been invalidated on the old As. Thus the addition of keys in A and the changing of keys at a faster rate (every 6 months compared to every year) has reduced the exposure of a compromised key without increasing any risk due to exposure of keys in A.

[0288] Of course if A is used with B and a B-like entity called C, then A can have 1 set of rolling keys with B, and can have a different set of rolling keys with C. This requires 1 key in B, 1 key in C, and two sets of multiple keys in A.

[0289] The rolling key structure can be extended to work with value hierarchy. Suppose A uses value from B, and value in B is replenished by C, then A and B can have one set of rolling keys, and B and C can have a different set of rolling keys and each set of rolling keys can roll at different times and rates. In this example:

[0290] A contains multiple variants for use with B

[0291] B contains 1 base key for use with A, and multiple variants for use with C

[0292] C contains 1 base key for use with B

[0293] A compromise of key(s) in a A does not allow an attacker to manufacture clone Bs

[0294] A compromise of key(s) in B does not allow an attacker to manufacture clone Cs

[0295] A compromise of the keys in A allows free B resources on that particular A only—no other As are affected

[0296] A compromise of the base key in B has a limited exposure of effect—free B resources are available to attackers for a limited time, and with each new release of A and C, the amount of exposure is reduced.

[0297] A compromise of the base key in C has a limited exposure of effect—free C resources are available to attackers for a limited time, and with each new release of B the amount of exposure is reduced.

[0298] In the general case, each of the keys in a set of rolling keys has exactly the same purpose as the others in the set, and is used in the same way in the same QA Devices, but at different times in a product's life span. Each of the keys has a different Keyld. Typically when a set of rolling keys is held in a QA Device, they all belong to the same keygroup.

[0299] When the variant/base form of rolling keys is used, at any given time, only one base key is injected during manufacture. This is the current manufactured instance of the rolling key. Several of the key instances can be used in manufac-

ture, in their variant forms. One by one, the current manufactured instance of the rolling key is replaced by subsequent instances of the rolling key.

[0300] After a period, or after the discovery of a key compromise, a particular current manufactured instance of a key is replaced by the next instance in the rolling key set in all of the QA Devices where it is used.

[0301] A set of rolling keys has the following characteristics:

[0302] The number of instances in the set of rolling keys, N. The rolling key instances are from 0 to N-1.

[0303] The current manufactured instance of the rolling key. This is the rolling key instance which is currently being inserted into manufactured products, in base form. The current manufactured instance is rolled to the next instance when a suitable length of time has elapsed, or there is the discovery of a key compromise.

[0304] The first and last valid instances of the rolling key set. There is likely to be a number of valid key instances either side of the current manufactured instance at any given time.

[0305] Rolling key instances which are before the first valid instance are considered to be invalid, and they should be invalidated in any manufactured product in the field whenever they are found. The question is how to enforce the eradication process, especially if the QA Devices are not in direct contact with a central authority of some kind.

[0306] The QA Logical Interface allows a particular key in a keyslot to be invalidated. An external entity needs to know which keys are invalid (for example by knowing the invalid keys' Keylds). Assuming that the entity can read the Keylds present in a QA Device the entity can invalidate the appropriate keys in the QA Device. The entity could refuse to operate on a QA Device until the appropriate keys have been invalidated.