(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6437674号

(P6437674)

(45) 発行日 平成30年12月12日(2018.12.12)

(24) 登録日 平成30年11月22日(2018.11.22)

(51) Int.Cl.

H01L 21/822 (2006.01)

H01L 27/04 (2006.01)

F 1

H01L 27/04

H01L 27/04H

C

請求項の数 20 (全 14 頁)

(21) 出願番号 特願2017-564018 (P2017-564018)

(86) (22) 出願日 平成27年7月30日 (2015.7.30)

(65) 公表番号 特表2018-521504 (P2018-521504A)

(43) 公表日 平成30年8月2日 (2018.8.2)

(86) 國際出願番号 PCT/US2015/042798

(87) 國際公開番号 WO2016/200411

(87) 國際公開日 平成28年12月15日 (2016.12.15)

審査請求日 平成30年3月13日 (2018.3.13)

(31) 優先権主張番号 14/736,882

(32) 優先日 平成27年6月11日 (2015.6.11)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 318007085

アンペア・コンピューティング・エルエル

シー

アメリカ合衆国・カリフォルニア・950

54・サンタ・クララ・グレート・アメリ

カ・パークウェイ・4555・シックスス

フロア

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100110364

弁理士 実広 信哉

(74) 代理人 100133400

弁理士 阿部 達彦

最終頁に続く

(54) 【発明の名称】高効率の半交差結合デカップリングキャパシタ

## (57) 【特許請求の範囲】

## 【請求項1】

第1のpチャンネル電界効果トランジスタ(PFET)と、

第1のnチャンネル電界効果トランジスタ(NFET)と、

少なくとも1つの容量性デバイスとを備えるデカップリングキャパシタ回路であって、

前記第1のPFETの第1のPFETソースおよび第1のPFET本体は、電圧源に接続され、

前記第1のNFETの第1のNFETソースおよび第1のNFET本体は、接地に接続され、

前記少なくとも1つの容量性デバイスは、前記第1のPFETの第1のPFETゲートまたは前記

第1のNFETの第1のNFETゲートのうちの少なくとも1つに接続され、

前記少なくとも1つの容量性デバイスを含むことにより、前記デカップリングキャパシタ回路の周波数応答を変えることなく、前記デカップリングキャパシタ回路の面積効率を

増加させる、デカップリングキャパシタ回路。

## 【請求項2】

前記第1のPFETの第1のPFETドレインは、前記第1のNFETの前記第1のNFETゲートに接続され、

前記第1のNFETの第1のNFETドレインは、前記第1のPFETの前記第1のPFETゲートに接続される、請求項1に記載のデカップリングキャパシタ回路。

## 【請求項3】

前記少なくとも1つの容量性デバイスは、第2のPFETを備える、請求項2に記載のデカップリングキャパシタ回路。

10

20

**【請求項 4】**

前記第2のPFETの第2のPFETドレイン、第2のPFETソース、および第2のPFET本体は、前記電圧源に接続され、

前記第2のPFETの第2のPFETゲートは、前記第1のPFETの前記第1のPFETゲートに接続される、請求項3に記載のデカップリングキャパシタ回路。

**【請求項 5】**

前記少なくとも1つの容量性デバイスは、第2のNFETを備える、請求項2に記載のデカップリングキャパシタ回路。

**【請求項 6】**

前記第2のNFETの第2のNFETドレイン、第2のNFETソース、および第2のNFET本体は、接地に接続され、10

前記第2のNFETの第2のNFETゲートは、前記第1のNFETの前記第1のNFETゲートに接続される、請求項5に記載のデカップリングキャパシタ回路。

**【請求項 7】**

前記第2のPFETの第2のPFETソースおよび第2のPFETドレインは、接地に接続され、

前記第2のPFETの第2のPFET本体は、前記電圧源に接続され、

前記第2のPFETの第2のPFETゲートは、前記第1のNFETの前記第1のNFETゲートに接続される、請求項3に記載のデカップリングキャパシタ回路。

**【請求項 8】**

前記第2のNFETの第2のNFETドレイン、および第2のNFETソースは、前記電圧源に接続され、20

前記第2のNFETの第2のNFET本体は、接地に接続され、

前記第2のNFETの第2のNFETゲートは、前記第1のPFETの前記第1のPFETゲートに接続される、請求項5に記載のデカップリングキャパシタ回路。

**【請求項 9】**

前記電圧源は、電力配電ネットワークの電圧源である、請求項1に記載のデカップリングキャパシタ回路。

**【請求項 10】**

前記電力配電ネットワークを備えた超大規模集積(VLSI)システムのオンチップコンポーネントである、請求項9に記載のデカップリングキャパシタ回路。30

**【請求項 11】**

前記電力配電ネットワークを備えた超大規模集積(VLSI)システムのオフチップコンポーネントである、請求項9に記載のデカップリングキャパシタ回路。

**【請求項 12】**

電源ノイズを抑制するための方法であって、

第1のpチャンネル電界効果トランジスタ(PFET)の第1のソースおよび第1の本体を電圧源に接続するステップと、

nチャンネル電界効果トランジスタ(NFET)の第2のソースおよび第2の本体を接地に接続するステップと、

前記第1のPFETの第1のドレインを前記NFETの第1のゲートに接続するステップと、40

前記NFETの第2のドレインを前記第1のPFETの第2のゲートに接続するステップと、

第2のPFETの第3のドレイン、第3のソース、および第3の本体を前記電圧源に接続するステップと、

前記第2のPFETの第3のゲートを前記第1のPFETの前記第2のゲートに接続するステップとを含む方法。

**【請求項 13】**

前記NFETは、第1のNFETを備え、前記方法は、

第2のNFETの第4のドレイン、第4のソース、および第4の本体を接地に接続するステップと、

前記第2のNFETの第4のゲートを前記第1のNFETの前記第1のゲートに接続するステップと50

をさらに含む、請求項12に記載の方法。

【請求項14】

前記第1のPFETの前記第1のソースおよび前記第1の本体を前記電圧源に接続する前記ステップは、電力配電ネットワークの電圧源に接続するステップを含む、請求項12に記載の方法。

【請求項15】

電源ノイズを抑制するためのシステムであって、

第1のpチャンネル電界効果トランジスタ(PFET)であって、前記第1のPFETの第1のPFETソースおよび第1のPFET本体は、電圧源に接続される、第1のpチャンネル電界効果トランジスタ(PFET)と、

第1のnチャンネル電界効果トランジスタ(NFET)であって、前記第1のNFETの第1のNFETソースおよび第1のNFET本体は、接地に接続される、第1のnチャンネル電界効果トランジスタ(NFET)と、

第2のNFETと

を備え、

前記第1のPFETの第1のPFETドレインは、前記第1のNFETの第1のNFETゲートに接続され、

前記第1のNFETの第1のNFETドレインは、前記PFETの第1のPFETゲートに接続され、

前記第2のNFETの第2のNFETドレイン、第2のNFETソース、および第2のNFET本体は、接地に接続され、

前記第2のNFETの第2のNFETゲートは、前記第1のNFETの前記第1のNFETゲートに接続される、システム。

【請求項16】

第2のPFETをさらに備え、

前記第2のPFETの第2のPFETドレイン、第2のPFETソース、および第2のPFET本体は、前記電圧源に接続され、

前記第2のPFETの第2のPFETゲートは、前記第1のPFETの前記第1のPFETゲートに接続される、請求項15に記載のシステム。

【請求項17】

前記第2のNFETを含むことにより、前記第1のPFETおよび前記第1のNFETのチャンネル長さを増加させることなく、前記システムの面積効率を増加させる、請求項15に記載のシステム。

【請求項18】

前記電圧源は、超大規模集積(VLSI)システムの電力配電ネットワークの電圧源である、請求項15に記載のシステム。

【請求項19】

前記VLSIシステムのオンチップコンポーネントである、請求項18に記載のシステム。

【請求項20】

前記VLSIシステムのオフチップコンポーネントである、請求項18に記載のシステム。

【発明の詳細な説明】

【技術分野】

【0001】

この開示は一般に、高動作周波数および高面積効率を提供する、電源ノイズを抑制するためのデカップリングキャパシタ回路設計に関する。

【背景技術】

【0002】

デカップリングキャパシタ(DCAP)は、超大規模集積(VLSI)設計のための電力配電ネットワーク(PDN)の重要なコンポーネントである。これらのデカップリングキャパシタは、キャパシタを通じてアクティブ回路素子によって引き起こされる電源ノイズを分流し、それによってアクティブになろうとしている回路の他の素子によって観察される電源ノイズを抑制する。

10

20

30

40

50

## 【0003】

高い面積効率、堅固な電気特性、および適切に目標とされる動作周波数を含む、いくつかの考慮すべき事柄が、DCAP設計にとって重要である。しかしながら、いくつかのDCAP設計は、特にトランジスタ設計が、超ディープサブミクロンおよびフィンFETプロセスノードに入るにつれて、静電放電(ESD)事象(event)から損傷を受けやすい。その上、DCAPをESD損傷に対してより耐性があるようにすることを目的とする設計は、しばしば高面積効率と高周波数動作との間の固有のトレードオフによって妨げられる。

## 【発明の概要】

## 【課題を解決するための手段】

## 【0004】

一実施形態では、面積効率を犠牲にすることなく高動作周波数をもたらすデカップリングキャパシタ(DCAP)回路が、提供される。高い動作周波数および面積効率の相反することもある設計要件を切り離すために、pチャンネル電界効果トランジスタ(PFET)およびnチャンネル電界効果トランジスタが、半交差結合(HCC)様式で接続され、結果として得られるHCC回路は、少なくとも1つの面積効率の良いキャパシタンス(AEC)デバイスによって補完される。半交差結合FETは、高周波数設計要件に対処し、一方AECデバイスは、高面積効率要件に対処する。結果として、HCC FETのサイズは、回路の動作周波数を面積効率とは無関係に設定することができ、一方AECデバイスのサイズは、面積効率を動作周波数とは無関係に設定することができる。それ故に、本明細書で述べられるDCAP設計は、いくつかの従来のDCAP設計に固有の動作周波数と面積効率との間の望ましくないトレードオフを除去する。

10

## 【0005】

一実施形態は、第1のpチャンネル電界効果トランジスタ(PFET)と、第1のnチャンネル電界効果トランジスタ(NFET)と、少なくとも1つの容量性デバイスとを備えるデカップリングキャパシタ回路を提供し、第1のPFETの第1のPFETソースおよび第1のPFET本体は、電圧源に接続され、第1のNFETの第1のNFETソースおよび第1のNFET本体は、接地に接続され、少なくとも1つの容量性デバイスは、第1のPFETの第1のPFETゲートまたは第1のNFETの第1のNFETゲートのうちの少なくとも1つに接続され、少なくとも1つの容量性デバイスを含むことにより、デカップリングキャパシタ回路の周波数応答を変えることなくデカップリングキャパシタ回路の面積効率を増加させる。

20

## 【0006】

第1のpチャンネル電界効果トランジスタ(PFET)の第1のソースおよび第1の本体を電圧源に接続するステップと、nチャンネル電界効果トランジスタ(NFET)の第2のソースおよび第2の本体を接地に接続するステップと、第1のPFETの第1のドレインをNFETの第1のゲートに接続するステップと、NFETの第2のドレインを第1のPFETの第2のゲートに接続するステップと、第2のPFETの第3のドレイン、第3のソース、および第3の本体を電圧源に接続するステップと、第2のPFETの第3のゲートを第1のPFETの第2のゲートに接続するステップとを含む、電源ノイズを抑制するための方法が、提供される。

30

## 【0007】

一実施形態は、第1のpチャンネル電界効果トランジスタ(PFET)であって、第1のPFETの第1のPFETソースおよび第1のPFET本体は、電圧源に接続される、第1のpチャンネル電界効果トランジスタ(PFET)と、第1のnチャンネル電界効果トランジスタ(NFET)であって、第1のNFETの第1のNFETソースおよび第1のNFET本体は、接地に接続される、第1のnチャンネル電界効果トランジスタ(NFET)と、第2のNFETとを備える、電源ノイズを抑制するためのシステムを提供し、第1のPFETの第1のPFETドレインは、第1のNFETの第1のNFETゲートに接続され、第1のNFETの第1のNFETドレインは、PFETの第1のPFETゲートに接続され、第2のNFETの第2のNFETドレイン、第2のNFETソース、および第2のNFET本体は、接地に接続され、第2のNFETの第2のNFETゲートは、第1のNFETの第1のNFETゲートに接続される。

40

## 【図面の簡単な説明】

## 【0008】

50

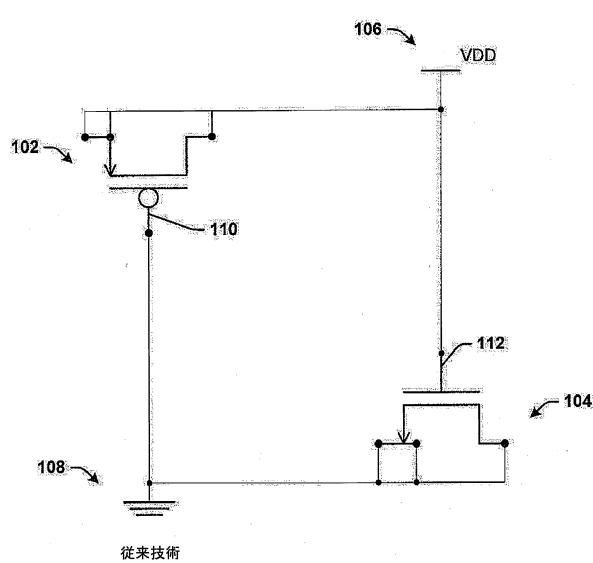

【図1】DCAP設計への例示的な手法を示す回路図である。

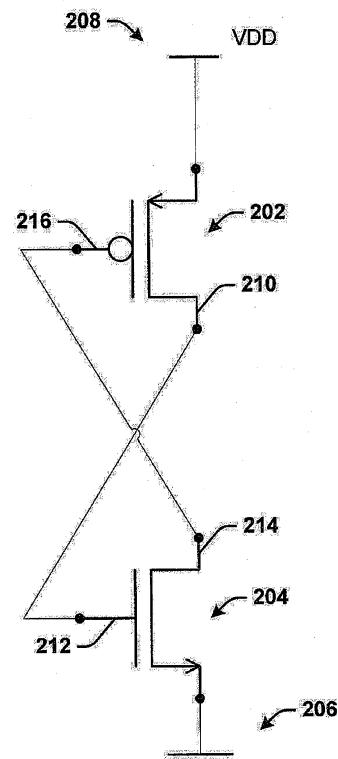

【図2】例示的な半交差結合DCAP設計手法を示す回路図である。

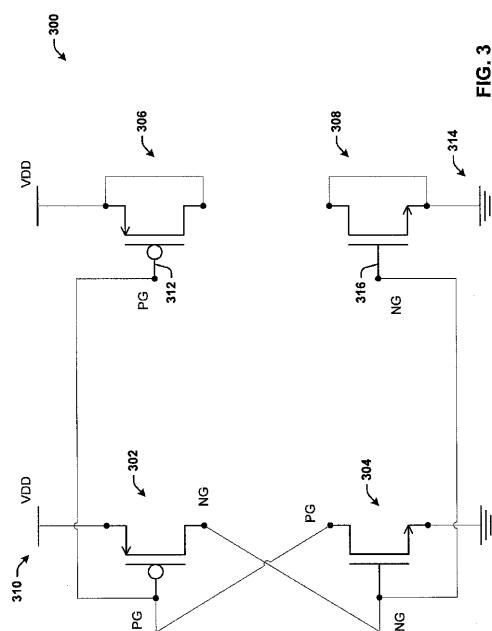

【図3】高面積効率および高周波数動作を提供する例示的なDCAP設計の回路図である。

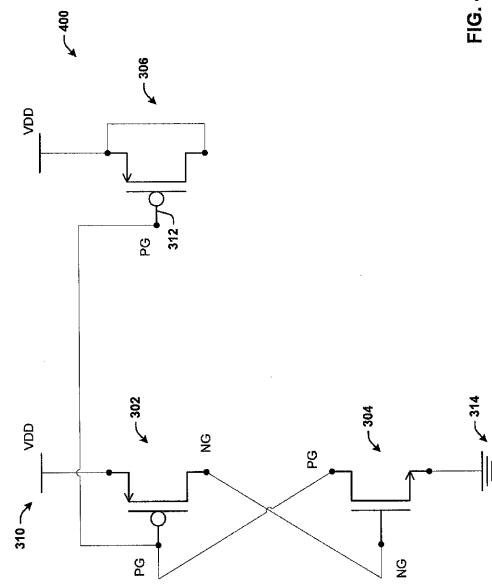

【図4】単一のPFET AECデバイスを使用する例示的なDCAP設計の回路図である。

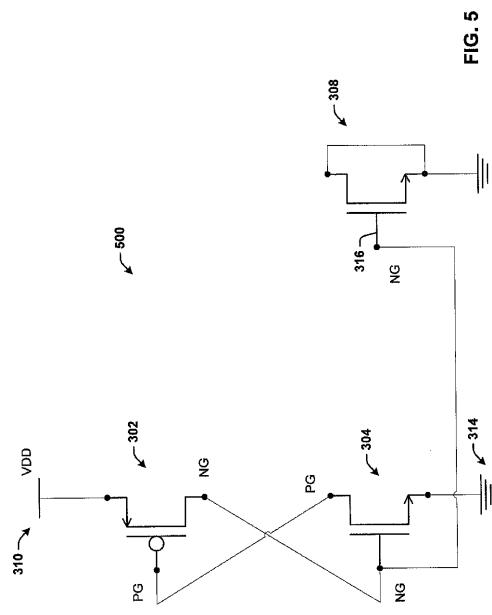

【図5】単一のNFET AECデバイスを使用する例示的なDCAP設計の回路図である。

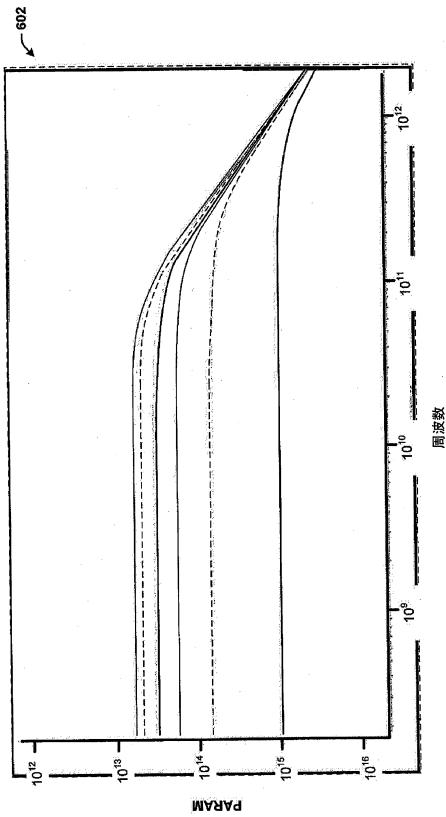

【図6】AECデバイスの様々なサイズのための図3のDCAP回路についての周波数応答を例示するグラフである。

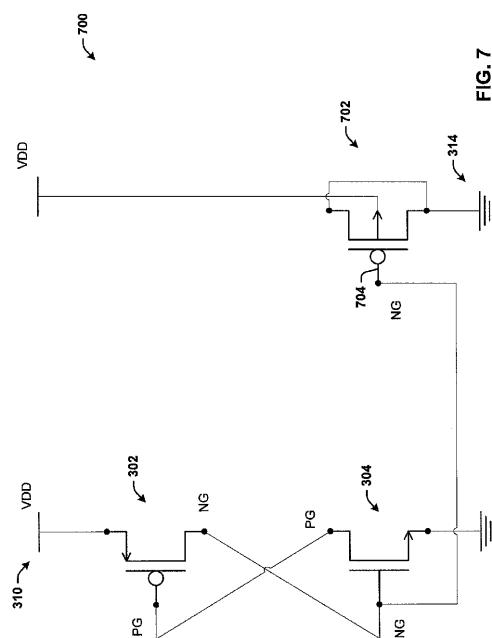

【図7】NGノードに結び付けられたゲート、接地に結び付けられたソースおよびドレイン、ならびにVDDに結び付けられた本体を有するPFETを備えるAECデバイスを含む例示的なDCAP設計の回路図である。

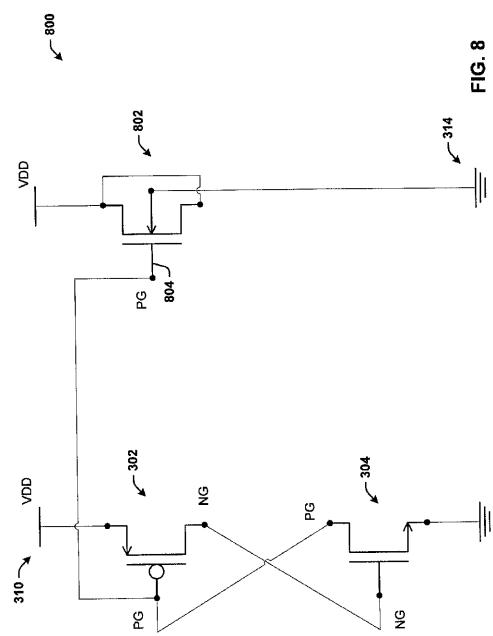

【図8】ノードPGに結び付けられたゲート、VDDに結び付けられたドレインおよびソース、ならびに接地に結び付けられた本体を有するNFETを備えるAECデバイスを含む例示的なDCAP設計の回路図である。

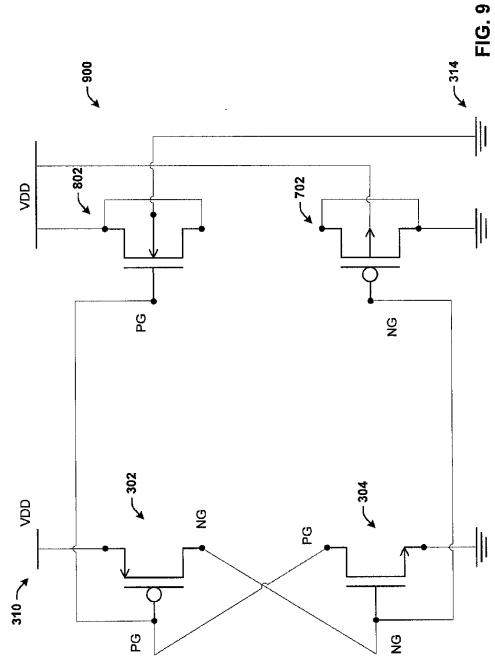

【図9】図7のPFET AECデバイスおよび図8のNFET AECデバイスを含む例示的なDCAP設計の回路図である。

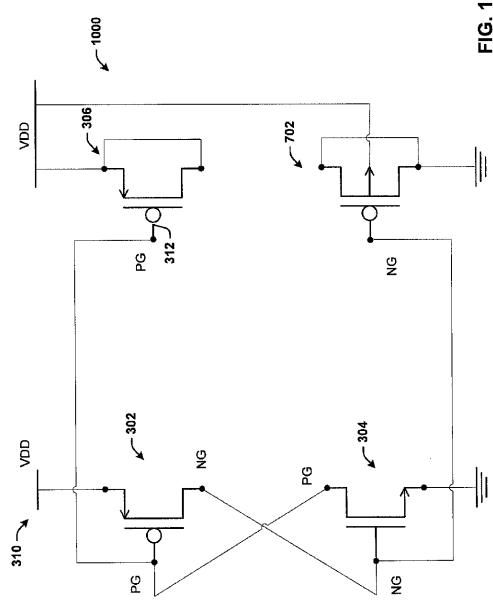

【図10】図4の第1のPFET AECデバイスおよび図7の第2のPFET AECデバイスを含む例示的なDCAP設計の回路図である。

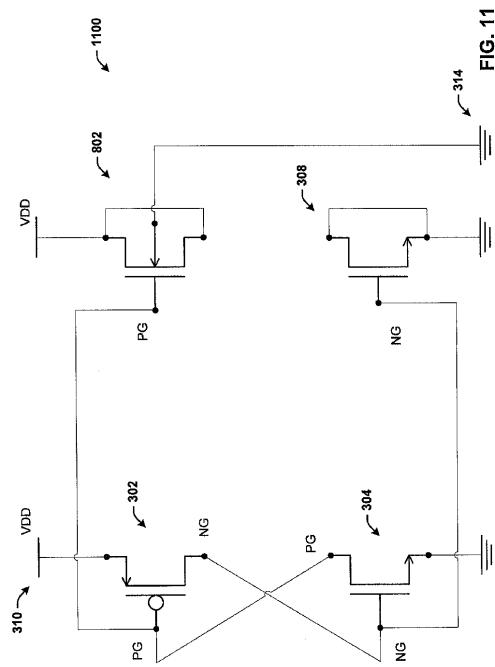

【図11】図5の第1のNFET AECデバイスおよび図8の第2のNFET AECデバイスを含む例示的なDCAP設計の回路図である。

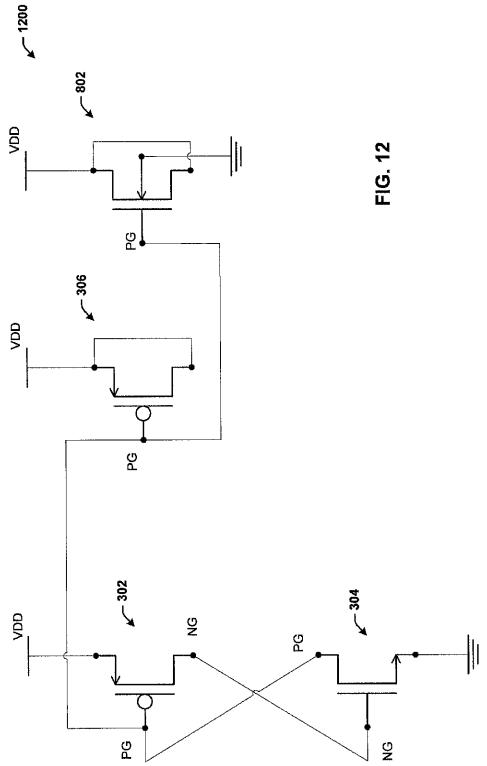

【図12】図4のPFET AECデバイスおよび図8のNFET AECデバイスを含む例示的なDCAP設計の回路図である。

【図13】図5のNFET AECデバイスおよび図7のPFET AECデバイスを含む例示的なDCAP設計の回路図である。

【図14】デカップリングキャパシタ(DCAP)回路を製造するための一実施形態の流れ図を例示する図である。

#### 【発明を実施するための形態】

##### 【0009】

DCAPはしばしば、アクティブ回路素子によって誘発される電圧源ノイズまたはリップルを抑制するためにVLSIシステムの電力配電ネットワークにおいて使用され、それによって素子を損傷するまたはそれらの機能を妨げることもある電源電圧変動から回路の他の素子をシールドする。堅固なDCAP設計は、高い面積効率、堅固な電気特性、および適切に目標とされる動作周波数によって特徴付けられる。オンダイのDCAP設計の場合は、目標とされる動作周波数は、その設計における動作周波数からゲートのスイッチングスルー(switching slew)に及び、それ故に電力配電ネットワークに使用されるDCAPの高動作周波数を構成する。

##### 【0010】

図1は、DCAP設計への1つの手法を例示する回路図である。この設計手法によると、pチャンネル電界効果トランジスタ(PFET)102のドレイン、ソース、および本体は、供給電圧106に直接結び付けられ、nチャンネル電界効果トランジスタ(NFET)104のドレイン、ソース、および本体は、接地に結び付けられる。PFET102のゲート110は、接地に結び付けられ、NFET104のゲート112は、供給電圧106に結び付けられる。この設計は、面積効率が良いまま、高い動作周波数まで電源ノイズを切り離すことができる。しかしながら、トランジスタ設計が、超ディープサブミクロンおよびフィンFETプロセスノードに入るために、ゲート酸化物は、極めて薄くなる。その結果、図1での設計は、静電放電(ESD)事象に対して弱くなる可能性があり、それは、ゲート酸化物に損傷を引き起こし、電源および接地ノードをショートさせることもある。ゲート110および112は、電源および接地ノードに直接接続されるので、図1での設計は、ESDクランプの存在下でさえ、極度のESD事象に耐えることができないこともある。ポリシリコンよりもむしろ金属ゲート材料を使用する設計は、特にこの問題の影響を受けやすい。

##### 【0011】

10

20

30

40

50

図2は、PFETおよびNFETのドレインおよびゲートノードを半交差結合(HCC)様式で接続しながら、PFET202のソースおよび本体を供給電圧208に結び付け、NFET204のソースおよび本体を接地206に結び付けることによってこの問題に対処しようとする別のDCAP設計手法を例示する回路図である。すなわち、PFET202のドレイン210は、NFET204のゲート212に接続され、一方NFET204のドレイン214は、PFET202のゲート216に接続される。この設計は、供給電圧および接地ノードからゲートへのデバイスチャンネルを通じての抵抗経路を提供し、それによってESDクランプが、過剰な電荷を分流することができるまで、ESD事象の間ゲート酸化物を保護する。

#### 【 0 0 1 2 】

しかしながら、図2での設計を使用すると、高面積効率および高周波数動作の両方を達成することは、困難である。これは、HCC接続性が、これらの2つの設計目標を直接対立する状態に置くからである。例えば、高面積効率を達成するために、PFET202およびNFET204は、ゲート面積を最大にするために大きいチャンネルを必要とするということになる。しかしながら、これらの大きいチャンネルは、抵抗をデカップリング経路に追加するということになり、それによってキャパシタ回路が達成することができる高周波数デカップリングの種類を制限する。もしチャンネル長さが、この関心事に対処するためにPFET202およびNFET204において低減されるならば、面積効率は、不利益をこうむるということになる。

#### 【 0 0 1 3 】

その上、図2に描かれる設計のための大きいチャンネルは、高い立ち上がり時間をもたらすことになる。この高い立ち上がり時間は、HCCノードが、DCAPを機能させるために必要とする値と相反する状態に持ち上げられる、「デッド」ゾーンに起因し、その設計は、正しい状態値を設定するための2つのFET202および204のデバイス漏れ(device leakage)に依存する。大きいチャンネルは、このデバイス漏れを低減することになり、DCAPが有効となる前に立ち上がり時間の大きな増加をもたらす。

#### 【 0 0 1 4 】

これらの問題および他の問題に対処するために、本明細書で述べられる1つまたは複数の実施形態は、高面積効率もまた達成しながら、HCC DCAPの電気特性によって提示される高周波数動作を持続するDCAP回路設計を提供する。図3は、高面積効率および高周波数動作を提供する、例示的なDCAP回路300の回路図である。この設計は、HCC構成に接続されるPFET302およびNFET304、ならびに面積効率の良いデカップリングキャパシタとしての役割を果たす面積効率の良いキャパシタンス(AEC)デバイス306および308を含む。AECデバイス306および308は、例えば第2のPFETおよび第2のNFETをそれぞれ備えることができる。AECデバイス306および308を適所に有すると、HCCデバイスは、高面積効率の相反する設計要件によって制限されることなく、高周波数応答を提供するために最適化されてもよい。

#### 【 0 0 1 5 】

この設計によると、PFET AECデバイス306のドレイン、ソース、および本体は、供給電圧310に接続され、一方ゲート312は、HCC接続によって作成されるPGノードに接続される。NFET AECデバイス308のドレイン、ソース、および本体は、接地314に接続され、一方ゲート316は、HCC接続によって作成されるNGノードに接続される。

#### 【 0 0 1 6 】

図3に描かれる回路300は、HCCデバイス(PFET302およびNFET304)のデバイスチャンネル長さが、それ故にPFETおよびNFETを通るデカップリング経路の対応する抵抗が低く保たれることを可能にし、それによって高周波数電源ノイズデカップリングを提供する。デバイスチャンネル長さを低く保つことはまた、HCCデバイスでの漏れも増加させ、それによってHCC接続性が、正しくない状態に初期化されるシナリオについて立ち上がり時間を低く保つ。

#### 【 0 0 1 7 】

HCCデバイス302および304が、高周波数動作を達成する一方で、AECデバイス306および308は、高面積効率を提供するために最適化されてもよい。この関連で、AECデバイス306お

10

20

30

40

50

より308は、PFET302およびNFET304を通るデカップリング経路のチャンネル長さ(および抵抗)を変えることなく、それ故に回路300の動作周波数を変えることなく、高面積効率を提供するようなサイズにされてもよい。場合によっては、AECデバイス306および308を高面積効率のために最適化することは、大きい長さ(L)を有することに対応する。HCCデバイス302および304を使用して高周波数動作要件を満たし、AECデバイス306および308を使用して高面積効率要件を満たすことによって、図3に描かれる設計は、高周波数コンポーネントを面積効率の良いコンポーネントから効果的に解き放ち、設計が面積効率を犠牲にすることなく高周波数応用に対処するために最適化されることを可能にする。

#### 【 0 0 1 8 】

回路300は、PFET302およびNFET304にそれぞれ対応する2つのAECデバイス306および308を含むけれども、いくつかの実施形態は、1つだけのAECデバイスを含んでもよい。図4は、PFET AECデバイス306だけが、HCC回路に接続される(NFET AECデバイス308を省略する)実施形態を例示し、一方図5は、NFET AECデバイス308だけが、接続される(PFET AECデバイス306を省略する)実施形態を例示する。

10

#### 【 0 0 1 9 】

図6は、AECデバイス306および308の様々なサイズのための回路300についての周波数応答を例示するグラフ602である。グラフ602の各プロットは、AECデバイス306および308の所与のサイズについての周波数応答を表し、HCCデバイス302および304のサイズは、各プロットについて一定に保たれている。各シナリオについて、ロールオフ周波数 、すなわち回路300のキャパシタンスがその有効性を失う周波数は、 $1/(RC)$ によって特徴付けられ、ただしRは、HCCデバイス302および304のサイズによって決定されるデカップリング経路の抵抗であり、Cは、AECデバイス306および308のサイズによって決定されるキャパシタンスである。AECデバイス306および308のキャパシタンスが、増加するにつれて、ロールオフ周波数 は、減少する。一般設計考察として、AECデバイス306および308のサイズが、増加するにつれて、HCCデバイス302および304がまた、AECデバイスの増加するキャパシタンスについていくために増加されてもよく、それによって高周波数電源ノイズデカップリングを持続する。一般に、AECデバイス306および308上のキャパシタンスに対するHCCデバイス302および304のサイズ間の比は、高周波数動作の程度を決定する。

20

#### 【 0 0 2 0 】

AECデバイス306および308に加えて、他の種類のAECデバイスもまた、この開示の1つまたは複数の実施形態の範囲内である。例えば、図7は、NGノードに結び付けられたゲート704、接地314に結び付けられたソースおよびドレイン、ならびにVDD310に結び付けられた本体を有するPFETを備えるAECデバイス702を含む、例示的なDCAP回路700の回路図である。図8は、ノードPGに結び付けられたゲート804、VDD310に結び付けられたドレインおよびソース、ならびに接地314に結び付けられた本体を有するNFETを備えるAECデバイス802を含む、例示的なDCAP回路800の回路図である。図9は、AECデバイス702および802の両方を含む、例示的なDCAP回路900の回路図である。

30

#### 【 0 0 2 1 】

AECデバイス306、308、702、および802は、DCAP回路をもたらすために任意の順列に組み合わされてもよい。例えば、図10は、AECデバイス702およびAECデバイス306を含む、例示的なDCAP回路1000の回路図であり、一方図11は、AECデバイス802およびAECデバイス308を含む、例示的なDCAP回路1100の回路図である。

40

#### 【 0 0 2 2 】

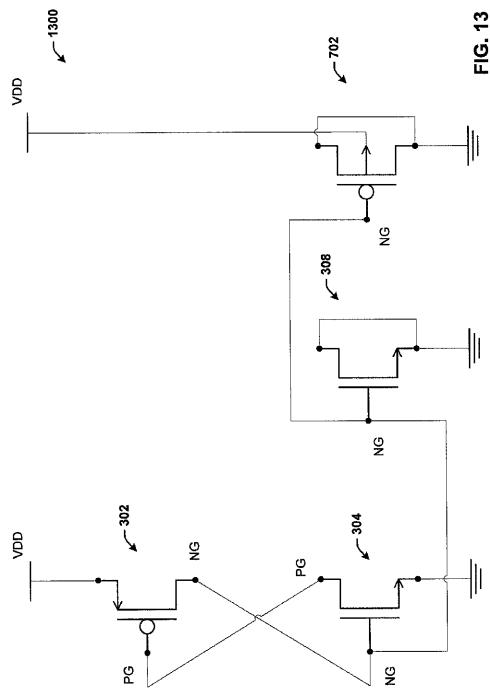

図12は、AECデバイス306および802を含む、別の例示的なDCAP回路1200の回路図である。この例では、両方のAECデバイスのゲートは、PGノードに接続される。図13は、AECデバイス308および702を含む、なお別の例示的なDCAP回路1300の回路図である。この例では、両方のAECデバイスのゲートは、NGノードに接続される。

#### 【 0 0 2 3 】

上で述べられ、図3～図5および図7～図13に例示されるデカップリングキャパシタ回路は、任意の適切なFET実施を使用して具体化されてもよい。例えば、回路300、400、500、

50

700、800、900、1000、1100、1200、および/または1300のいずれかは、VLSIシステムの電力配電ネットワークのための電源ノイズ抑制を提供するために使用されてもよい集積回路として具体化されてもよい。回路300、400、500、700、800、900、1000、1100、1200、または1300のいずれかは、そのようなVLSIシステムのオンチップコンポーネントとして、または別個のチップ上にあるVLSIシステムのための電源ノイズ抑制を提供する、専用の集積回路上に具体化されるオフチップコンポーネントとして実施されてもよい。他の実施形態では、回路300、400、500、700、800、900、1000、1100、1200、または1300のいずれかは、固体コンポーネントを使用して構成されてもよい。

#### 【0024】

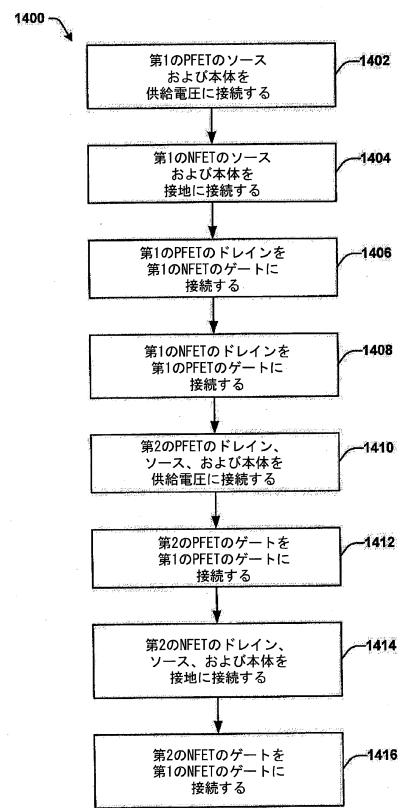

図14は、1つまたは複数の実施形態による手順を例示する。本明細書で示される手順は、一連の行為として示されるが、いくつかの行為は、それに従って、本明細書で図示され、述べられるそれと異なる順番および/または他の行為と同時に起こってもよいので、本革新は、行為の順番によって制限されない。例えば、当業者は、手順が別法として、状態図などでの、一連の相互に関連する状態または事象と表されることもあり得ることを理解し、認識するであろう。その上、すべての例示される行為が、本革新による手順を実施するために必要とされるとは限らない。さらに、相互作用図は、完全に異なる実体が、手順の完全に異なる部分を規定するとき、主題の開示による手順、または方法を表してもよい。さらになお、開示される例示的な方法の2つ以上は、本明細書で述べられる1つもしくは複数の特徴または利点を成し遂げるために、互いに組み合わせて実施されてもよい。

#### 【0025】

図14は、デカップリングキャパシタ(DCAP)回路を組み立てるための実施形態の流れ図である。DCAP回路は、例えば電力配電ネットワーク(PDN)のコンポーネントとして使用されてもよい。方法1400は、ブロック1402から始まり、ここで第1のpチャンネル電界効果トランジスタ(PFET)のソースおよび本体は、供給電圧(例えば、電源ノイズ抑制を必要とする電力配電ネットワークまたは他のシステムの供給電圧)に接続される。ブロック1404において、第1のnチャンネル電界効果トランジスタ(NFET)のソースおよび本体は、接地に接続される。ブロック1406において、第1のPFETのドレインは、第1のNFETのゲートに接続される。ブロック1408において、第1のNFETのドレインは、第1のPFETのゲートに接続される。

#### 【0026】

ブロック1410において、第2のPFETのドレイン、ソース、および本体は、供給電圧に接続される。ブロック1412において、第2のPFETのゲートは、第1のPFETのゲートに接続される。ブロック1414において、第2のNFETのドレイン、ソース、および本体は、接地に接続される。ブロック1416において、第2のNFETのゲートは、第1のNFETのゲートに接続される。ブロック1402～1416によってもたらされる回路は、電源ノイズを抑制するために使用されてもよく、高面積効率ならびに高周波数動作を達成することができる。

#### 【0027】

いくつかの実施形態では、第2のPFETまたは第2のNFETのどちらかは、回路から省略されてもよい(例えば、図4および図5を参照)。すなわち、いくつかの実施形態では、ブロック1410および1412は、省略されてもよく、一方他の実施形態では、ブロック1414および1416が、省略されてもよい。

#### 【0028】

開示される主題は、開示される主題を実施するための電子デバイスを制御するためにハードウェア、ファームウェア、ソフトウェア、またはそれらの任意の適切な組み合わせを作成するための典型的な製造、プログラミングまたはエンジニアリング技法を使用する製造の方法、装置、または物品として実施されてもよい。コンピュータ可読媒体は、ハードウェア媒体、ソフトウェア媒体、非一時的媒体、または輸送媒体を含むことができる。

#### 【符号の説明】

#### 【0029】

102 pチャンネル電界効果トランジスタ(PFET)

104 nチャンネル電界効果トランジスタ(NFET)

10

20

30

40

50

|      |                                      |    |

|------|--------------------------------------|----|

| 106  | 供給電圧                                 |    |

| 110  | PFETのゲート                             |    |

| 112  | NFETのゲート                             |    |

| 202  | PFET                                 |    |

| 204  | NFET                                 |    |

| 206  | 接地                                   |    |

| 208  | 供給電圧                                 |    |

| 210  | PFETのドレイン                            | 10 |

| 212  | NFETのゲート                             |    |

| 214  | NFETのドレイン                            |    |

| 216  | PFETのゲート                             |    |

| 300  | DCAP回路                               |    |

| 302  | PFET、HCCデバイス                         |    |

| 304  | NFET、HCCデバイス                         |    |

| 306  | 面積効率の良いキャパシタンス(AEC)デバイス、PFET AECデバイス |    |

| 308  | 面積効率の良いキャパシタンス(AEC)デバイス、NFET AECデバイス |    |

| 310  | 供給電圧、VDD                             |    |

| 312  | AECデバイス306のゲート                       |    |

| 314  | 接地                                   |    |

| 316  | AECデバイス308のゲート                       | 20 |

| 400  | 回路                                   |    |

| 500  | 回路                                   |    |

| 602  | 回路300についての周波数応答を例示するグラフ              |    |

| 700  | DCAP回路                               |    |

| 702  | AECデバイス                              |    |

| 704  | PFETのゲート                             |    |

| 800  | DCAP回路                               |    |

| 802  | AECデバイス                              |    |

| 804  | AECデバイスのゲート                          |    |

| 900  | DCAP回路                               | 30 |

| 1000 | DCAP回路                               |    |

| 1100 | DCAP回路                               |    |

| 1200 | DCAP回路                               |    |

| 1300 | DCAP回路                               |    |

| 1400 | 方法                                   |    |

【図1】

従来技術

【図2】

従来技術

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

【図10】

【図11】

【図12】

FIG. 9

FIG. 12

【図13】

【図14】

---

フロントページの続き

(72)発明者 アルフレッド・イエン

アメリカ合衆国・カリフォルニア・94536-3467・フリーモント・ブレア・ブレイス・3

6078

(72)発明者 ローネン・コーハン

アメリカ合衆国・カリフォルニア・94087-4111・サニーヴェール・ジャスパー・ドライ

ヴ・1586

審査官 棚田 一也

(56)参考文献 特開2007-067207(JP, A)

米国特許出願公開第2009/0207552(US, A1)

特開2009-246062(JP, A)

特開2004-342924(JP, A)

特開平11-186497(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 27/04