(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4763206号

(P4763206)

(45) 発行日 平成23年8月31日(2011.8.31)

(24) 登録日 平成23年6月17日(2011.6.17)

(51) Int.Cl.

F 1

H03H 11/08 (2006.01)

H03H 11/34 (2006.01)H03H 11/08

H03H 11/34

請求項の数 6 (全 10 頁)

(21) 出願番号 特願2001-548523 (P2001-548523)

(86) (22) 出願日 平成12年12月22日 (2000.12.22)

(65) 公表番号 特表2003-518863 (P2003-518863A)

(43) 公表日 平成15年6月10日 (2003.6.10)

(86) 國際出願番号 PCT/IB2000/001975

(87) 國際公開番号 WO2001/048918

(87) 國際公開日 平成13年7月5日 (2001.7.5)

審査請求日 平成19年12月17日 (2007.12.17)

(31) 優先権主張番号 1013951

(32) 優先日 平成11年12月24日 (1999.12.24)

(33) 優先権主張国 オランダ (NL)

(73) 特許権者 598036300

テレフォンアクチーボラゲット エル エ

ム エリクソン (パブル)

スウェーデン国 ストックホルム エスー

164 83

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

最終頁に続く

(54) 【発明の名称】多相フィルタ

## (57) 【特許請求の範囲】

## 【請求項 1】

所望のフィルタ特性を有するとともに、第1と第2の入力端子を有し、かつ、I入力信号( $I_I$ )を受け取る入力( $31_I, 102_I$ )、及び第1と第2の出力端子を有し、かつ、I出力信号( $I_I$ )を供給する出力( $32_I, 103_I$ )を有する第1のフィルタ・チャネル( $30_I; 101_I$ )と、

前記第1のフィルタ・チャネル( $30_I; 101_I$ )とほぼ同一であり、第3と第4の入力端子を有し、かつ、I入力信号( $I_I$ )に対して $90^\circ$ シフトされているQ入力信号( $Q_Q$ )を受け取る入力( $31_Q; 102_Q$ )、及び第3と第4の出力端子を有し、かつ、I出力信号( $I_I$ )に対して $90^\circ$ シフトされているQ出力信号( $Q_Q$ )を供給する出力( $32_Q, 103_Q$ )を有する第2のフィルタ・チャネル( $30_Q; 101_Q$ )とを備えた多相フィルタ( $20; 100$ )であって、

前記第1のフィルタ・チャネル( $30_I; 101_I$ )において、前記第1の入力端子及び前記第1の出力端子とが一方と接続され、前記第2の入力端子及び前記第2の出力端子とが他方と接続された第1容量性フィルタ部品( $C_I, C_{i_I}$ )と、

前記第2のフィルタ・チャネル( $30_Q; 101_Q$ )において、前記第3の入力端子及び前記第3の出力端子とが一方と接続され、前記第4の入力端子及び前記第4の出力端子とが他方と接続され、前記第1容量性フィルタ部の容量値とほぼ等しい容量値を有する第2容量性フィルタ部品( $C_Q, C_{i_Q}$ )と、

前記第1のフィルタ・チャネル( $30_I; 101_I$ )において前記第1容量性フィルタ

10

20

部品 (C<sub>I</sub>、C<sub>iI</sub>) と並列に接続され、電流を出力する第 1 電圧制御電流源 (41<sub>I</sub>) と、前記第 2 のフィルタ・チャネル (30<sub>Q</sub>; 101<sub>Q</sub>) において前記第 2 容量性フィルタ部品 (C<sub>Q</sub>、C<sub>iQ</sub>) と並列に接続され、かつ、検出した電圧を該第 1 電圧制御電流源 (41<sub>I</sub>) に出力する第 1 電圧検出器 (42<sub>Q</sub>) とを有する第 1 電流源結合 (40<sub>QI</sub>) と、

前記第 2 のフィルタ・チャネル (30<sub>Q</sub>; 101<sub>Q</sub>) において前記第 2 容量性フィルタ部品 (C<sub>Q</sub>、C<sub>iQ</sub>) と並列に接続され、電流を出力する第 2 電圧制御電流源 (41<sub>Q</sub>) と、前記第 1 のフィルタ・チャネル (30<sub>I</sub>; 101<sub>I</sub>) において前記第 1 容量性フィルタ部品 (C<sub>I</sub>、C<sub>iI</sub>) と並列に接続され、かつ、検出した電圧を該第 2 電圧制御電流源 (41<sub>Q</sub>) に出力する第 2 電圧検出器 (42<sub>I</sub>) とを有する第 2 電流源結合 (40<sub>IQ</sub>) と、をさらに備え、 10

前記第 1 電圧検出器 (42<sub>Q</sub>) は、前記第 2 電圧制御電流源 (41<sub>Q</sub>) と並列に接続され、

前記第 2 電圧検出器 (42<sub>I</sub>) は、前記第 1 電圧制御電流源 (41<sub>I</sub>) と並列に接続され、

前記第 1 電流源結合 (40<sub>QI</sub>) は、第 1 電圧検出器 (42<sub>Q</sub>) によって出力された電圧を入力として、前記第 1 のフィルタ・チャネル (30<sub>I</sub>; 101<sub>I</sub>) に電流を出力し、

前記第 2 電流源結合 (40<sub>IQ</sub>) は、第 2 電圧検出器 (42<sub>I</sub>) によって出力された電圧を入力として、前記第 2 のフィルタ・チャネル (30<sub>Q</sub>; 101<sub>Q</sub>) に電流を出力することを特徴とする多相フィルタ。 20

### 【請求項 2】

前記第 1 及び第 2 電圧制御電流源 (41<sub>I</sub>、41<sub>Q</sub>) は、電流値が

$I_{41,I} = V_{cQ} / (c \cdot C)$ 、 $I_{41,Q} = V_{cI} / (c \cdot C)$

をそれぞれ満足する電流 ( $I_{41,I}$ 、 $I_{41,Q}$ ) を提供するように適応されていることを特徴とする請求項 1 に記載の多相フィルタ。

### 【請求項 3】

前記第 1 及び第 2 のフィルタ・チャネル (101<sub>I</sub>、101<sub>Q</sub>) は、前記第 1 電流源結合 (40<sub>QI</sub>) 及び前記第 2 電流源結合 (40<sub>IQ</sub>) を含むジャイレータ (105<sub>iI</sub>、105<sub>iQ</sub>) と、該ジャイレータの入力及び出力に接続された前記第 1 容量性フィルタ部品及び前記第 2 容量性フィルタ部品 (C<sub>iI</sub> 及び C<sub>[i+1]I</sub>、C<sub>iQ</sub> 及び C<sub>[i+1]Q</sub>) の組合せを少なくとも 1 つ備えていることを特徴とする請求項 1 又は 2 に記載の多相フィルタ。 30

### 【請求項 4】

前記組合せにおいて、

前記第 1 のフィルタ・チャネル (101<sub>I</sub>) の 1 つ目の前記第 1 容量性フィルタ部品 (C<sub>[i+1]I</sub>) と、対応する前記第 2 のフィルタ・チャネル (101<sub>Q</sub>) の 1 つ目の前記第 2 容量性フィルタ部品 (C<sub>[i+1]Q</sub>) とは、比例係数 (G<sub>iI</sub> 及び G<sub>iQ</sub>) が常に  $1 / (c \cdot C_{iI})$  に等しい対称的なジャイレータ (106<sub>I</sub>) に接続され、

前記第 1 のフィルタ・チャネル (101<sub>I</sub>) の 2 つ目の前記第 1 容量性フィルタ部品 (C<sub>iI</sub>) と、対応する第 2 のフィルタ・チャネル (101<sub>Q</sub>) の 2 つ目の前記第 2 容量性フィルタ部品 (C<sub>iQ</sub>) とは、比例係数 (G<sub>[i+1]I</sub> 及び G<sub>[i+1]Q</sub>) が常に  $1 / (c \cdot C_{[i+1]I})$  に等しい対称的なジャイレータ (106<sub>[i+1]</sub>) に接続されていることを特徴とする請求項 3 に記載の多相フィルタ。 40

### 【請求項 5】

前記第 1 のフィルタ・チャネル (30<sub>I</sub>; 101<sub>I</sub>) は、複数の前記第 1 容量性フィルタ部品 (C<sub>iI</sub>) を有し、

前記第 2 のフィルタ・チャネル (30<sub>Q</sub>; 101<sub>Q</sub>) は、複数の前記第 2 容量性フィルタ部品 (C<sub>iQ</sub>) を有し、

前記第 1 容量性フィルタ部品と対応する前記第 2 容量性フィルタ部品の組合せごとに、前記第 1 電流結合 (40<sub>QI</sub>) と前記第 2 電流結合 (40<sub>IQ</sub>) とが設けられることを 50

特徴とする請求項 1 乃至 4 の何れか 1 項に記載の多相フィルタ。

**【請求項 6】**

個々のフィルタ・チャネル ( $30_I$ 、 $30_Q$ ； $101_I$ 、 $101_Q$ ) は、それぞれローパス・フィルタ特性を有し、前記多相フィルタ ( $20$ ； $100$ ) は、前記第 1 及び第 2 電流源結合 ( $40_{QI}$ 、 $40_{IQ}$ ； $106i$ ) により発生されるバンドパス・フィルタ特性を有する請求項 1 乃至 5 の何れか 1 項に記載の多相フィルタ。

**【発明の詳細な説明】**

**【0001】**

本発明は、一般的に、多相バンドパス・フィルタに関する。

**【0002】**

このようなフィルタは、それ自体、例えば米国特許第 4、914、408 号により知られており、また例えば無線応用、テレビジョン応用又は電話応用の受信機回路に適用することが例え可能である。このようなフィルタは、更に、異なる応用も知られているが、ここでは、このようなフィルタの可能な応用を受信機回路の背景においてより詳細に説明する。

10

**【0003】**

米国特許第 4、914、408 号に説明されているフィルタの大きな欠点は、2 フィルタ・チャネル間の結合が抵抗により影響されることである。従って、本発明の重要な目的は、このようなカップリング抵抗を除去した多相バンドパス・フィルタを提供することである。

20

**【0004】**

図面を参照して、本発明による多相バンドパス・フィルタの好ましい実施例の下記説明によって、これらと共にその他の構成、特徴及び効果を更に詳細に説明する。図面において、同一参照番号は、同一又は同様の部分を表している。

**【0005】**

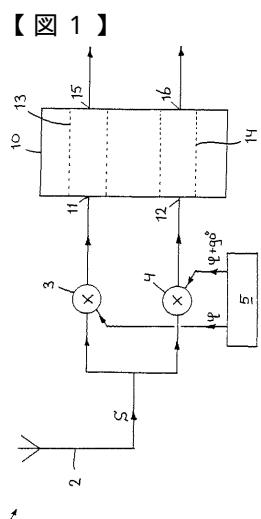

図 1 は、既知の受信機回路 1 を概要的に示しており、アンテナ 2 から来る受信機信号  $S$  は、第 1 の混合段 3 において、ローカル発振器 5 から供給される信号  $f_1$  と混合され、かつ受信機信号  $S$  は、第 2 の混合段 4 において、ローカル発振器 5 から供給され、第 1 の信号に対して  $90^\circ$  シフトされている第 2 の信号と混合される。同様に、位相同相信号によって示される第 1 の混合段 3 の出力信号は、フィルタ 10 の第 1 の入力 11 に供給され、同様に、直角位相信号によって示される第 2 の混合段 4 の出力信号は、フィルタ 10 の第 2 の入力 12 に供給される。フィルタ 10 は、それぞれ実質的に同一方法により、第 1 の入力 11 の同相信号及び第 2 の入力 12 の直角信号をそれぞれ処理する 2 フィルタ・チャネル 13 及び 14 を有し、また、同相出力信号及び直角出力信号をそれぞれ供給する出力 15 及び 16 をそれぞれ有する。第 2 の出力の直角出力信号は、第 1 の出力の同相出力信号に対して  $90^\circ$  シフトされている。フィルタ・チャネル 13 及び 14 は、互いに同一のフィルタ特性、例えば帯域通過特性を有する。

30

**【0006】**

以下において、ローカル発振器信号の周波数は、 $f_1$  により示される。受信機信号  $S$  には、多くの周波数が存在する。以下において、受信回路 1 が同調すべき同調周波数は、 $f_2$  により表される。この周波数は、ローカル周波数  $f_1$  より高いものと、即ち  $f_2 = f_1 + f$  と仮定する。

40

**【0007】**

一般的に、異なる周波数  $f_1$  及び  $f_2$  を有する 2 信号が混合されると、信号成分は、異なる周波数  $f = f_2 - f_1$  を発生する。しかしながら、受信機信号  $S$  には、更に  $f_3 = f_1 - f$  を満足させる周波数  $f_3$  が存在する。更に、この成分は、究極的に混合信号に、即ち異なる周波数  $f_3 - f_1 = -f$  を有する仮想ミラー信号成分を発生させることに、寄与している。フィルタ 10 は、このようなミラー信号成分を抑圧することが望まれている。

**【0008】**

更に、中心周波数  $f_c$  に対してほぼ対称となる帯域通過特性を有することが望まれている

50

。

## 【0009】

周波数特性が中心周波数  $\omega_c > 0$  に対して対称であり、かつミラー信号成分を効果的に抑圧するバンドパス・フィルタを設計する既知の方法は、特性が設計しようとするバンドパス・フィルタの所望特性に対応するローパス・フィルタから開始する。

## 【0010】

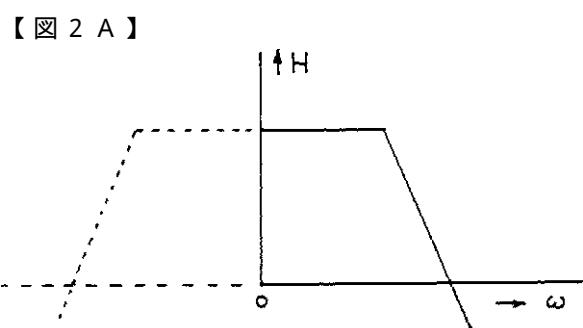

図2Aは、ローパス・フィルタの伝達特性を概要的に示す。周波数  $\omega$  は水平軸上に示され、また伝達関数  $H$  は垂直軸上に示される。実際には、周波数が 0 より高い信号のみが発生し、この部分の周波数特性を実線により示す。しかしながら、周波数特性は、周波数の符号に関係なく、図2Aに点線により示すように、 $\omega = 0$  に対して対称となることを意味する。10

## 【0011】

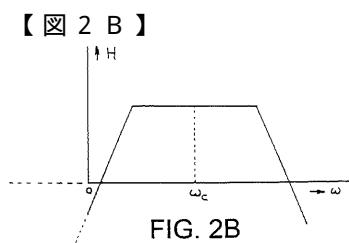

ローパス・フィルタは、前記ローパス・フィルタの設計によって、所望の特性、例えば1次、2次、又は更に高次、ベッセル形、バターワース形等を有することができる。所望の特性を有するローパス・フィルタから開始すると、フィルタ特性を高い周波数へ変換即ちシフトすることにより、帯域フィルタを導き出すことができる。図2Bは、距離  $\omega_c$  だけ高い周波数へシフトした図2Aの特性を示す。この帯域フィルタの同調周波数  $H_{BDF}$  ( $\omega_c$ ) は、次式を満足する。

## 【0012】

## 【数1】

20

$$H_{BDF}(\omega) = H_{LPF}(\omega - \omega_c) \quad (1)$$

## 【0013】

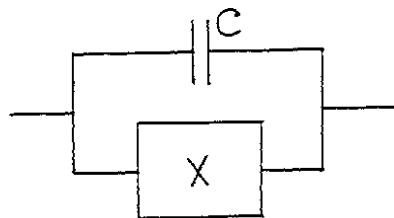

フィルタ特性の所望シフトは、想像軸上の互いに同一距離で全ての極及び全てのゼロのシフトに対応する。周波数に依存したインピーダンスを有する部品が専らコンデンサである。フィルタ設計では、前記容量性フィルタ部品に対して並列の複素部品  $X$  をスイッチングすることにより、これを達成可能であり、そのアドミッタンス  $Y_X$  は、次式により、一定の複素数となる。30

## 【0014】

## 【数2】

$$Y_X(\omega) = -j \cdot \omega_c \cdot C \quad (2)$$

## 【0015】

図2Cは、コンデンサ  $C$  とこのような複素部品  $X$  との並列接続を概要的に示す。容量値  $C$  を有する周波数に依存したコンデンサの従属アドミッタンス  $Y_C$  に対して、次式は、理想コンデンサの場合に成立する。40

## 【0016】

## 【数3】

$$Y_C(\omega) = j \cdot \omega \cdot C \quad (3)$$

## 【0017】

図2Cの並列接続の周波数に依存したアドミッタンス  $Y$  に対して、以下は有効である。

## 【数4】

$$Y(\omega) = Y_C(\omega) + Y_X(\omega) = j \cdot \omega \cdot C - j \cdot \omega_C \cdot C = j \cdot (\omega - \omega_C) \cdot C \quad (4)$$

## 【0018】

従って、周波数  $\omega$  を有する信号の場合に、この並列回路の動作は、周波数  $\omega - \omega_C$  におけるコンデンサ  $C$  の動作と同一である。従って、フィルタの全ての容量性フィルタ部品をこのような並列回路によって置換することにより、周波数  $\omega$  における総合的なフィルタの動作は、周波数  $\omega - \omega_C$  における元のフィルタの動作と同一となる。

10

## 【0019】

以上の演繹は、単一フィルタに既に適用している。そこで、このようにして帯域フィルタを実現するときの問題は、アドミッタンス（又は逆：インピーダンス）が一定の複素数となる部品を得ることの問題に移行する。これは、それ自体可能であるが、多相フィルタでは、信号が互いに同一であるが、信号が互いに  $90^\circ$  シフトされている、互いに同一の 2 つのフィルタ・チャネルが存在するという、都合のよい方法に使用することができる。そこで、このようなフィルタでは、各チャネルにおいて、アドミッタンスが実数であるが、その入力で他のチャネルから  $90^\circ$  シフトされて受信する部品を使用することにより、複素部品  $X$  の動作を獲得できる。

## 【0020】

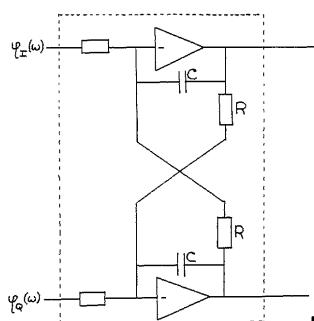

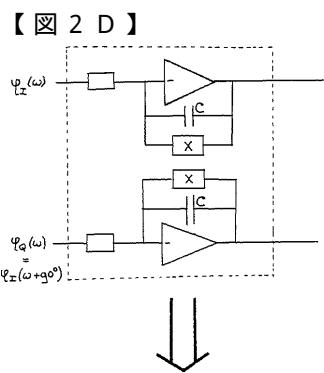

多相帯域フィルタを構築するこのような解決方法は、米国特許第 4,914,408 号において既に説明されていた。そこでは、2 つのフィルタ・チャネル間の実結合が図 2 D に示すように、抵抗により実施される。その場合、各抵抗は、抵抗値  $R = \omega_C \cdot C$  を有する。

20

## 【0021】

しかしながら、既知の解決方法は、チップ上にフィルタを実現するときに得に問題となるいくつかの難点がある。プロセスのばらつきを原因として、フィルタの抵抗及びコンデンサは、比較的に大きな許容誤差を示す。従って、コンデンサ及び抵抗は、製造後、設定可能でなければならない。しかしながら、これは実現するのが困難である。

## 【0022】

本発明の概要的な目的は、前述の欠点を克服することである。

30

## 【0023】

特に、本発明の目的は、所望の周波数シフトを達成するために必要とする 2 つのフィルタ・チャネル間の結合を抵抗なしで実現する多相帯域フィルタを提供することである。

## 【0024】

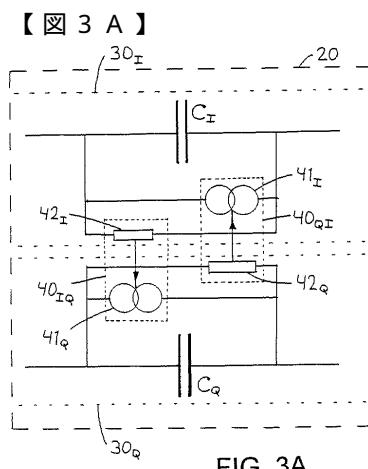

本発明の重要な構成によれば、2 フィルタ・チャネル間の結合は、電圧制御電流源により、実施される。本発明によるこの原理を図 3 A に示す。図 3 A において、多相フィルタは、参照番号 20 により概略的に示す。フィルタ 20 は、互いに区別するために、それぞれ I 及び Q により示す互いに同一の 2 つのフィルタ・チャネル 30 を有する。各フィルタ・チャネル 30<sub>I</sub>、30<sub>Q</sub> は、1 入力及び 1 出力を有する。フィルタ・チャネル 30<sub>I</sub>、30<sub>Q</sub> の設計は、適当とする任意の設計が可能であると同時に、フィルタ・チャネルに関する種々の構造それ自体が公知なので、図 3 A に、フィルタ・チャネル 30 の完全な設計は、示していない。

40

## 【0025】

以下の説明のために、図 3 A には、同相フィルタ・チャネル 30<sub>I</sub> の 1 容量性フィルタ部品  $C_I$  を示し、かつ対応する直交フィルタ・チャネル 30<sub>Q</sub> の容量性フィルタ部品  $C_Q$  を示す。2 つの容量性フィルタ部品  $C_I$  及び  $C_Q$  は、逆並列に接続された 2 つの電流源結合 40<sub>QI</sub> 及び 40<sub>IQ</sub> により互いに接続されている。第 1 の電流源結合 40<sub>QI</sub> は第 1 の電圧制御電流源 41<sub>I</sub> を備え、その出力は、同相フィルタ・チャネル 30<sub>I</sub> における容量性フィルタ部品  $C_I$  に並列に接続され、一方、第 2 の電流源結合 40<sub>IQ</sub> は第 2 の電圧制御電流源 41<sub>Q</sub> を

50

備え、その出力は、直交フィルタ・チャネル 3 0<sub>Q</sub>における容量性フィルタ部品 C<sub>Q</sub>に並列に接続されている。

#### 【0026】

第 1 の電圧制御電流源 4 1<sub>I</sub> は、第 1 の電圧検出器 4 2<sub>Q</sub> の出力信号により制御されており、その入力は、容量性フィルタ部品 C<sub>Q</sub> と並列に接続されている。同様に、第 2 の電圧制御電流源 4 1<sub>Q</sub> は、第 2 の電圧検出器 4 2<sub>I</sub> により制御されており、その入力は、容量性フィルタ部品 C<sub>I</sub> と並列に接続されている。

#### 【0027】

従って、第 1 の電圧制御電流源 4 1<sub>I</sub> は、値が第 2 のフィルタ・チャネル 3 0<sub>Q</sub> における容量性フィルタ部品 C<sub>Q</sub> 上の電圧に従った電流を第 1 のフィルタ・チャネル 3 0<sub>I</sub> に加算し、一方、第 2 の電圧制御電流源 4 1<sub>Q</sub> は、値が第 1 のフィルタ・チャネル 3 0<sub>I</sub> における容量性フィルタ部品 C<sub>I</sub> 上の電圧に従った電流を第 2 のフィルタ・チャネル 3 0<sub>Q</sub> に加算する。

10

#### 【0028】

2 つの第 1 の電流源結合 4 0<sub>QI</sub> 及び 4 0<sub>IQ</sub> は、必須ではないが、互いに同一である。重要なことは、両電流源結合 4 0<sub>QI</sub> 及び 4 0<sub>IQ</sub> に関して、電圧検出器 4 2 により検出された電圧と電流源 4 1 により発生した電流との間の比例係数が互いに同一ということだけである。換言すれば、重要なことは、2 つの電流源結合 4 0<sub>QI</sub> 及び 4 0<sub>IQ</sub> が互いに同一の伝達関数を有することだけである。これは、各電流源結合 4 0<sub>QI</sub> 及び 4 0<sub>IQ</sub> がそれぞれ電圧制御電流源 4 1<sub>I</sub> 及び 4 1<sub>Q</sub> がそれぞれ電流 I<sub>41,I</sub> 及び I<sub>41,Q</sub> を発生するように設計されることを意味し、その電流値は、それぞれ次式に従ってそれぞれ電圧検出器 4 2<sub>Q</sub> 及び 4 2<sub>I</sub> によりそれぞれ検出された電圧 V<sub>CQ</sub> 及び V<sub>CI</sub> に従う。

20

#### 【0029】

#### 【数 5】

$$I_{41,I} = V_{CQ} / (\omega_c \cdot C) \quad \text{及び} \quad I_{41,Q} = V_{CI} / (\omega_c \cdot C)$$

#### 【0030】

ただし、C はそれぞれ容量性フィルタ部品 C<sub>I</sub> 及び C<sub>Q</sub> の容量値であり、また ω<sub>c</sub> は、帯域フィルタの所望中心周波数である。

30

#### 【0031】

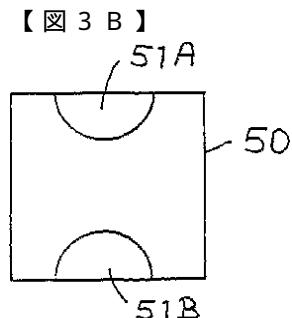

以下において、逆並列に接続された 2 つの電流源結合は、位相「ジャイレータ」により表され、また図 3B に示すシンボル 50 により表される。ジャイレータ 50 は、2 つの端子 51A 及び 51B を有する。51A から 51B へ接続する場合、ジャイレータ 50 は、図 3B に示していない第 1 の電流源結合を備え、その端子 51A は電圧入力であり、またその端子 51B は電流出力である。51B から 51A へ接続する場合、ジャイレータ 50 は、図 3B に示していない第 2 の電流源結合を備え、その端子 51B は電圧入力であり、またその端子 51A は電流出力である。2 つの電流源結合は、入力電圧により分流された出力電流として定義された比例係数 G<sub>AB</sub> 及び G<sub>BA</sub> をそれぞれ有する。両比例係数が互いに等しいとき、又は少なくとも同一特性を有するときは、ジャイレータを対称ジャイレータとして示す。両電流源結合が同一であれば、これを達成することができるが、必須ではない。

40

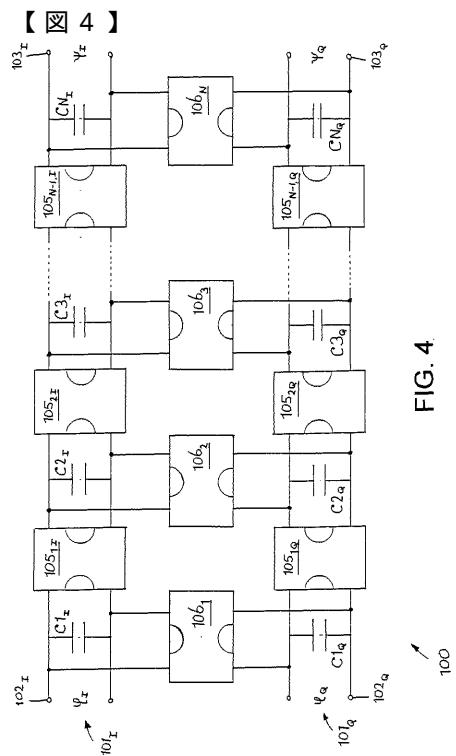

#### 【0032】

図 4 は、本発明による多相フィルタ 1 0 0 の実施例を示す。多相フィルタ 1 0 0 は、同相チャネル 1 0 1<sub>I</sub> 及び直交チャネル 1 0 1<sub>Q</sub> を備えており、これらは互にほぼ同一である。チャネル 1 0 1<sub>I</sub> 及び 1 0 1<sub>Q</sub> は、同相入力信号 I<sub>I</sub> 及び直交入力信号 I<sub>Q</sub> を受け取る入力 1 0 2<sub>I</sub>、1 0 2<sub>Q</sub> をそれぞれ有する。チャネル 1 0 1<sub>I</sub> 及び 1 0 1<sub>Q</sub> は、更に同相出力信号 I<sub>I</sub> 及び直交出力信号 I<sub>Q</sub> を出力する出力 1 0 3<sub>I</sub>、1 0 3<sub>Q</sub> をそれぞれ有する。入力 1 0 2<sub>I</sub>、1 0 2<sub>Q</sub> は、電流入力である。即ち、入力信号 I<sub>I</sub> 及び I<sub>Q</sub> は電流信号である。フィルタ 1 0 0 が電圧信号を受け取りたいときは、入力 1 0 2<sub>I</sub>、1 0 2<sub>Q</sub> の前の電圧・電流変換器

50

を切り換えることができる。これには、それ自体公知の電圧・電流変換器を使用することができる、ここで、これらをこれ以上説明しない。出力  $103_1$  及び  $103_Q$  は、電圧出力である。即ち、出力信号  $_1$  及び  $_Q$  は、電圧信号である。フィルタ  $100$  が電流信号を出力したいときは、出力  $103_1$ 、 $103_Q$  の後の電圧・電流変換器を切り換えることができる。これには、それ自体公知の電圧・電流変換器を使用する能够で、ここでも、これらをこれ以上説明しない。

#### 【0033】

チャネル  $101_1$  及び  $101_Q$  は、複数の N コンデンサ  $C_{11}$ 、 $C_{21}$ 、 $C_{31}$ 、…  $C_{N1}$ 、及び  $C_{1Q}$ 、 $C_{2Q}$ 、 $C_{3Q}$ 、…  $C_{NQ}$  をそれぞれ備えている。ただし、 $N \geq 2$ 。

#### 【0034】

同相チャネル  $101_1$  において、連続する 2 つのコンデンサ  $C_{i1}$  及び  $C_{[i+1]1}$  は、ジャイレータ  $105_{i1}$  により常に接続されている。同様に、直交チャネル  $101_Q$  において、連続する 2 つのコンデンサ  $C_{iQ}$  及び  $C_{[i+1]Q}$  は、ジャイレータ  $105_{iQ}$  により常に接続されている。対応するジャイレータ  $105_{i1}$  及び  $105_{iQ}$  は、互いに同一である。ここで、「順方向」比例係数  $G(i - i + 1)$  及び「逆方向」比例係数  $G(i + 1 - i)$  は、互いに同一である必要性はない。

#### 【0035】

対応するコンデンサ  $C_{i1}$  及び  $C_{iQ}$  は、常に、互いに同一容量値  $C_i$  を有する。異なる値の  $i$  の場合、容量値  $C_i$  は異なっていてもよい。対応するコンデンサ  $C_{i1}$  及び  $C_{iQ}$  は、常に、対称ジャイレータ  $106_{i1}$  により相互に接続されている。各ジャイレータ  $106_{i1}$  の比例係数  $G_{i1Q}$  及び  $G_{iQ1}$  は、常に  $1 / (\pi \cdot C_i)$  に等しい。

#### 【0036】

従って、本発明は、I - 入力信号  $_1$  及び Q - 入力信号  $_Q$  をそれぞれ処理するフィルタ・チャネル  $30_1$ 、 $30_Q$ ； $101_1$ 、 $101_Q$  を有する多相フィルタ  $20$ 、 $100$  を提供する。このフィルタは、2 つのフィルタ・チャネル  $30_1$ 、 $30_Q$ ； $101_1$ 、 $101_Q$  において互いに対応する少なくとも 2 つの容量性フィルタ部品  $C_1$ 、 $C_Q$ ； $C_{i1}$ 、 $C_{iQ}$  を有し、これら 2 つの容量性フィルタ部品  $C_1$ 、 $C_Q$ ； $C_{i1}$ 、 $C_{iQ}$  の容量値  $C$ ； $C_i$  は、互いにほぼ等しい。前記 2 つの容量性フィルタ部品  $C_1$ 、 $C_Q$ ； $C_{i1}$ 、 $C_{iQ}$  は、逆並列にスイッチングされるほぼ等しい特性を有する 2 つの電流源結合  $40_{Q1}$ 、 $40_{1Q}$ ； $106_1$  により互いに接続されている。従って、更に高い周波数方向へ距離  $c$  だけフィルタ特性を遷移させることができ達成される。

#### 【0037】

本発明の範囲が以上で説明した例に限定されることないことは、当該技術分野に習熟する者にとって、明らかである。

#### 【図面の簡単な説明】

【図 1】 既知の受信機回路を概要的に示す。

【図 2 A】 ローパス・フィルタの伝送特性を概要的に示す。

【図 2 B】 図 2 A の伝送特性から導き出したバンドパス・フィルタの伝送特性を概要的に示す。

【図 2 C】 コンデンサ及び複素部品の並列接続を概要的に示す。

【図 2 D】 2 つのフィルタ・チャネルを結合する既知の方法を概要的に示す。

【図 3 A】 本発明によるカップリング原理を示す。

【図 3 B】 図 3 A のカップリング・スケジュールの置換表示を示す。

【図 4】 本発明による多相フィルタの一実施例の基本スケジュールである。

FIG. 1

FIG. 2A

FIG. 2B

FIG. 2C

FIG. 3A

FIG. 3B

FIG. 4

100

---

フロントページの続き

(74)代理人 100091339

弁理士 清水 邦明

(74)代理人 100094673

弁理士 林 銘三

(72)発明者 エッシング、ベレンド、ヘンドリク

オランダ国 エンシェデ、プランディユゼルホーク、12

審査官 佐藤 聰史

(56)参考文献 国際公開第99/016179 (WO, A1)

特開平10-070482 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03H 11/00-11/54