(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6205014号

(P6205014)

(45) 発行日 平成29年9月27日(2017.9.27)

(24) 登録日 平成29年9月8日(2017.9.8)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G09G 3/36

G09G 3/20 (2006.01)

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

624B

611J

622B

623B

請求項の数 2 (全 15 頁)

(21) 出願番号

特願2016-111710 (P2016-111710)

(22) 出願日

平成28年6月3日(2016.6.3)

(62) 分割の表示

特願2015-100679 (P2015-100679)

の分割

原出願日

平成13年4月27日(2001.4.27)

(65) 公開番号

特開2016-186644 (P2016-186644A)

(43) 公開日

平成28年10月27日(2016.10.27)

審査請求日

平成28年6月20日(2016.6.20)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 浅見 宗広

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 長尾 祥

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 棚田 好文

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 西島 篤宏

最終頁に続く

(54) 【発明の名称】表示装置

(57) 【特許請求の範囲】

【請求項 1】

画素と、駆動回路と、を有し、

前記駆動回路は、第1乃至第8のトランジスタを有し、

前記第1乃至前記第8のトランジスタの導電型は、同じであり、

前記第2のトランジスタのゲートは、第1の配線と電気的に接続され、

前記第1の配線は、第1の信号を供給する機能を有し、

前記第2のトランジスタのゲートは、前記第4のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのゲートは、前記第5のトランジスタのゲートと電気的に接続され、

前記第6のトランジスタのゲートは、前記第8のトランジスタのゲートと電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第3のトランジスタのゲートと電気的に接続され、

前記第1のトランジスタは、前記第3のトランジスタをオンにする電位の前記第3のトランジスタのゲートへの供給を制御する機能を有し、

前記第2のトランジスタは、前記第3のトランジスタをオフにする電位の前記第3のト

10

前記第2のトランジスタは、前記第3のトランジスタをオフにする電位の前記第3のト

20

ランジスタのゲートへの供給を制御する機能を有し、

前記第3のトランジスタは、前記第6のトランジスタをオンにする電位の前記第6のトランジスタのゲートへの供給を制御する機能を有し、

前記第4のトランジスタは、前記第6のトランジスタをオフにする電位の前記第6のトランジスタのゲートへの供給を制御する機能を有し、

前記第5のトランジスタは、前記第7のトランジスタをオンにする電位の前記第7のトランジスタのゲートへの供給を制御する機能を有し、

前記第6のトランジスタは、前記第7のトランジスタをオフにする電位の前記第7のトランジスタのゲートへの供給を制御する機能を有し、

前記第7のトランジスタは、第1の電位の前記第8のトランジスタのソース又はドレインの一方への供給を制御する機能を有し、 10

前記第8のトランジスタは、第2の電位の前記第7のトランジスタのソース又はドレインの一方への供給を制御する機能を有し、

前記第7のトランジスタのソース又はドレインの一方からの出力信号に応じた電位が、前記画素に入力されることを特徴とする表示装置。

【請求項2】

画素と、駆動回路と、を有し、

前記駆動回路は、第1乃至第8のトランジスタを有し、

前記画素は、第9のトランジスタを有し、

前記第1乃至第9のトランジスタの導電型は、同じであり、 20

前記第2のトランジスタのゲートは、第1の配線と電気的に接続され、

前記第1の配線は、第1の信号を供給する機能を有し、

前記第2のトランジスタのゲートは、前記第4のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのゲートは、前記第5のトランジスタのゲートと電気的に接続され、

前記第6のトランジスタのゲートは、前記第8のトランジスタのゲートと電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、 30

前記第1のトランジスタのソース又はドレインの他方は、前記第3のトランジスタのゲートと電気的に接続され、

前記第1のトランジスタは、前記第3のトランジスタをオンにする電位の前記第3のトランジスタのゲートへの供給を制御する機能を有し、

前記第2のトランジスタは、前記第3のトランジスタをオフにする電位の前記第3のトランジスタのゲートへの供給を制御する機能を有し、

前記第3のトランジスタは、前記第6のトランジスタをオンにする電位の前記第6のトランジスタのゲートへの供給を制御する機能を有し、

前記第4のトランジスタは、前記第6のトランジスタをオフにする電位の前記第6のトランジスタのゲートへの供給を制御する機能を有し、 40

前記第5のトランジスタは、前記第7のトランジスタをオンにする電位の前記第7のトランジスタのゲートへの供給を制御する機能を有し、

前記第6のトランジスタは、前記第7のトランジスタをオフにする電位の前記第7のトランジスタのゲートへの供給を制御する機能を有し、

前記第7のトランジスタは、第1の電位の前記第8のトランジスタのソース又はドレインの一方への供給を制御する機能を有し、

前記第8のトランジスタは、第2の電位の前記第7のトランジスタのソース又はドレインの一方への供給を制御する機能を有し、

前記第7のトランジスタのソース又はドレインの一方からの出力信号に応じた電位が、前記第9のトランジスタのゲートに入力されることを特徴とする表示装置。 50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置の駆動回路に関する。さらに本発明は、前記表示装置の駆動回路を用いて作製された電子機器を含む。なお本明細書中、表示装置とは、画素に液晶素子を用いてなる液晶表示装置および、有機エレクトロルミネッセンス(EL)素子を始めとした自発光素子を用いてなる発光表示装置を含むものとする。駆動回路とは、表示装置に配置された画素に映像信号を入力し、映像の表示を行うための処理を行う回路を指し、シフトレジスタ等を始めとするパルス回路や、アンプ等を始めとする增幅回路を含むものとする。

10

**【背景技術】****【0002】**

近年、絶縁体上、特にガラス基板上に半導体薄膜を形成した表示装置、特に薄膜トランジスタ(以下、TFTと表記)を用いたアクティブマトリクス型表示装置の普及が顕著となっている。TFTを使用したアクティブマトリクス型表示装置は、マトリクス状に配置された数十万から数百万の画素を有し、各画素に配置されたTFTによって各画素の電荷を制御することによって映像の表示を行っている。

**【0003】**

さらに最近の技術として、画素を構成する画素TFTの他に、画素部の周辺領域にTFTを用いて駆動回路を同時形成するポリシリコンTFTに関する技術が発展してきており、装置の小型化、低消費電力化に大いに貢献し、それに伴って、近年その応用分野の拡大が著しいモバイル情報端末の表示部等に、表示装置は不可欠なデバイスとなってきている。

20

**【0004】**

表示装置の駆動回路としては、N型TFTとP型TFTを組み合わせたCMOS回路が一般的に使用されている。CMOS回路の特徴として、論理が変わる(Hi電位からLo電位へ、あるいはLo電位からHi電位へ)瞬間にのみ電流が流れ、ある論理の保持中には電流が流れない(実際には微小なリーク電流の存在がある)ため、回路全体での消費電流を低く抑えることが可能な点や、高速駆動に有利な点が挙げられる。

**【0005】**

30

液晶や自発光素子を用いた表示装置の需要は、モバイル電子機器の小型化、軽量化に伴って急速にその需要が増加しているが、歩留まり等の面から、その製造コストを十分に低く抑えることが難しい。今後の需要はさらに急速に増加することは容易に予測され、そのため表示装置をより安価に供給できるようにすることが望まれている。

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

絶縁体上に駆動回路を作製する方法としては、複数のフォトマスクを用いて、活性層、配線等のパターンを露光、エッチングを行って作りこんでいく方法が一般的であるが、このときの工程数の多さが製造コストに直接影響しているため、可能な限り少ない工程数で製造することが理想的である。そこで、従来CMOS回路によって構成されていた駆動回路を、N型もしくはP型のいずれか一方の導電型のみのTFTを用いて構成する。この方法により、イオンドーピング工程の一部を省略することが出来、さらにフォトマスクの枚数も削減することが出来る。

40

**【0007】**

(本発明以前の技術の問題点)

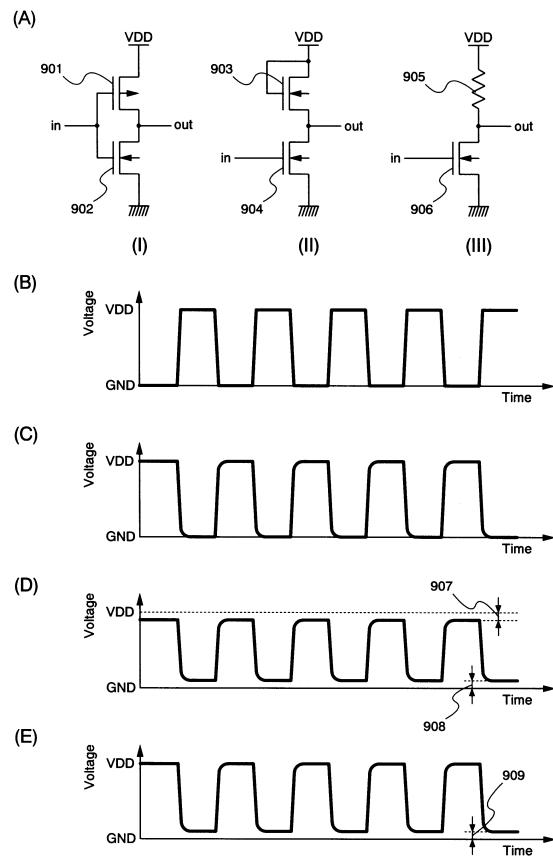

図9(A)は、従来一般的に用いられているCMOSインバータ(I)と、一極性のみのTFTを用いて構成したインバータ(II)(III)の例を示している。(II)はTFT負荷型のインバータ、(III)は抵抗負荷型のインバータである。以下に、それぞれの動作について述べる。

50

## 【0008】

図9(B)は、インバータに入力する信号の波形を示している。ここで、入力信号振幅はVDD - GND間( $GND < VDD$ )とする。具体的には $GND = 0[V]$ として考える。

## 【0009】

回路動作について説明する。なお、説明を明確かつ簡単にするため、回路を構成するN型TFTのしきい値電圧は、そのばらつきがないものとして一律( $V_{thN}$ )とする。また、P型TFTについても同様に、一律( $V_{thP}$ )とする。

## 【0010】

CMOSインバータに図9(B)のような信号が入力されると、入力信号の電位がHi( $VDD$ )のとき、P型TFT901はOFFし、N型TFT902がONすることにより、出力ノードの電位はLo( $GND$ )となる。逆に、入力信号の電位がLoのとき、P型TFT901がONし、N型TFT902がOFFすることにより、出力ノードの電位はHiとなる(図9(C))。

## 【0011】

続いて、TFT負荷型インバータ(II)の動作について説明する。同じく図9(B)に示すような信号が入力される場合を考える。まず、入力信号がLoのとき、N型TFT904はOFFする。一方、負荷TFT903は常に飽和動作していることから、出力ノードの電位はHi方向に引き上げられる。一方、入力信号がHiのとき、N型TFT904はONする。ここで、負荷TFT903の電流能力よりも、N型TFT904の電流能力を十分に高くしておくことにより、出力ノードの電位はLo方向に引き下げられる。

## 【0012】

抵抗負荷型インバータ(III)についても同様に、N型TFT906のON抵抗値を、負荷抵抗905の抵抗値よりも十分に低くしておくことにより、入力信号がHiのときは、N型TFT906がONすることにより、出力ノードはLo方向に引き下げられる。入力信号がLoのときは、N型TFT906はOFFし、出力ノードはHi方向に引き上げられる。

## 【0013】

ただし、TFT負荷型インバータや抵抗負荷型インバータを用いる際、以下のような問題点がある。図9(D)は、TFT負荷型インバータの出力波形を示したものであるが、出力がHiのときに、907で示す分だけVDDよりも電位が低くなる。負荷TFT903において、出力ノード側の端子をソース、電源VDD側の端子をドレインとすると、ゲート電極とドレイン領域が接続されているので、このときのゲート電極の電位はVDDである。また、この負荷TFTがONしているための条件は、(TFT903のゲート-ソース間電圧 $> V_{thN}$ )であるから、出力ノードの電位は、最大でも( $VDD - V_{thN}$ )までしか上昇しない。つまり、907は $V_{thN}$ に等しい。さらに、負荷TFT903とN型TFT904の電流能力の比によっては、出力電位がLo電位のとき、908で示す分だけGNDよりも電位が高くなる。これを十分にGNDに近づけるためには、負荷TFT903に対し、N型TFT904の電流能力を十分に大きくする必要がある。同様に、図9(E)は抵抗負荷型インバータの出力波形を示したものであるが、負荷抵抗905の抵抗値とN型TFT906のON抵抗の比によっては、909で示す分だけ電位が高くなる。つまり、ここに示した一極性のみのTFTを用いて構成したインバータを用いると、入力信号の振幅に対し、出力信号の振幅減衰が生ずることになる。駆動回路を構成するには、振幅が減衰することなく出力が得られなければならない。

## 【0014】

本発明は、以上のような課題を鑑見てなされたものであり、一極性のみのTFTを用いて製造工程を削減することにより低コストで作製が可能であり、かつ振幅減衰のない出力を得ることが出来る表示装置の駆動回路を提供することを目的とする。

## 【課題を解決するための手段】

## 【0015】

10

20

30

40

50

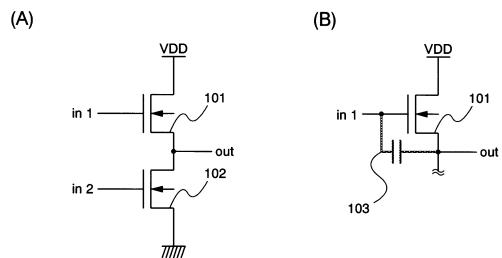

先程の図9(A)の(II)に示したTFT負荷型インバータにおいて、出力信号の振幅が正常にVDD-GNDを取るための条件を考える。第1に、図1(A)のような回路において、出力信号の電位がLoとなるとき、その電位を十分にGNDに近づけるためには、電源VDD-出力ノード間の抵抗値に対し、電源GND-出力ノード間の抵抗値が十分に低くなつていればよい。すなわち、N型TFT102がONしている期間、N型TFT101がOFFしていればよい。第2に、出力信号の電位がHiとなるとき、その電位がVDDに等しくなるには、N型TFT101のゲート-ソース間電圧の絶対値が、VthNを常に上回つていればよい。つまり、出力ノードのHi電位がVDDとなる条件を満たすには、N型TFT101のゲート電極の電位は( $VDD + VthN$ )よりも高くなる必要がある。回路に供給される電源はVDD、GNDの2種類のみであるから、VDDよりも電位の高い第3の電源がない限り、条件を満たすことは出来ない。

#### 【0016】

そこで、本発明では以下のような手段を講じた。図1(B)に示すように、N型TFT101のゲート-ソース間に容量103を設ける。N型TFT101のゲート電極がある電位をもつて浮遊状態となつたとき、出力ノードの電位を上昇させると、この容量103による容量結合によって、出力ノードの電位上昇分に伴つて、N型TFT101のゲート電極の電位も持ち上げられる。この効果を利用すれば、N型TFT101のゲート電極の電位をVDDよりも高く(正確には、 $VDD + VthN$ よりも高く)することが可能となる。よつて出力ノードの電位を十分にVDDまで引き上げることが可能となる。

#### 【0017】

なお、図1(B)において示した容量103は、実際に容量部分を作製しても良いし、TFT101のゲート-ソース間に寄生する容量を利用するようにしても良い。

#### 【0018】

本発明の構成を以下に記す。

#### 【0019】

請求項1の記載によると、本発明の表示装置の駆動回路は、第1の不純物領域が第1の電源と電気的に接続された、第1のトランジスタと、第1の不純物領域が第2の電源と電気的に接続された、第2のトランジスタと、第1の不純物領域が第1の電源と電気的に接続された、第3のトランジスタと、第1の不純物領域が第2の電源と電気的に接続された、第4のトランジスタと、容量とを有する表示装置の駆動回路であつて、前記第1乃至第4のトランジスタはいずれも同一導電型であり、前記第1のトランジスタの第2の不純物領域と、前記第2のトランジスタの第2の不純物領域とはいずれも前記容量の一方の端子と電気的に接続され、前記第3のトランジスタの第2の不純物領域と、前記第4のトランジスタの第2の不純物領域と、前記第1のトランジスタのゲート電極とは、いずれも前記容量の他の一方の端子と電気的に接続され、前記第2のトランジスタのゲート電極と、前記第4のトランジスタのゲート電極は、入力信号線と電気的に接続され、前記第3のトランジスタのゲート電極は、前記第1の電源と電気的に接続されていることを特徴としている。

#### 【0020】

請求項2の記載によると、本発明の表示装置の駆動回路は、第1の不純物領域が第1の電源と電気的に接続された、第1のトランジスタと、第1の不純物領域が第2の電源と電気的に接続された、第2のトランジスタと、第1の不純物領域が第1の電源と電気的に接続された、第3のトランジスタと、第1の不純物領域が第2の電源と電気的に接続された、第4のトランジスタと、容量とを有する表示装置の駆動回路であつて、前記第1乃至第4のトランジスタはいずれも同一導電型であり、前記第1のトランジスタの第2の不純物領域と、前記第2のトランジスタの第2の不純物領域とはいずれも前記容量の一方の端子と電気的に接続され、前記第3のトランジスタの第2の不純物領域と、前記第4のトランジスタの第2の不純物領域と、前記第1のトランジスタのゲート電極とは、いずれも前記容量の他の一方の端子と電気的に接続され、前記第2のトランジスタのゲート電極と、前記第4のトランジスタのゲート電極は、第1の入力信号線と電気的に接続

10

20

30

40

50

され、前記第3のトランジスタのゲート電極は、第2の入力信号線と電気的に接続されていることを特徴としている。

【0021】

請求項3の記載によると、本発明の表示装置の駆動回路は、請求項2において、前記第2の入力信号線は、前記第1の入力信号線に入力される信号の反転信号が入力される信号線であることを特徴としている。

【0022】

請求項4の記載によると、本発明の表示装置の駆動回路は、請求項1もしくは請求項2において、前記容量は、前記第1のトランジスタのゲート電極と、前記不純物領域のうちいずれか一方との間の容量を用いることを特徴としている。

10

【0023】

請求項5の記載によると、本発明の表示装置の駆動回路は、請求項1もしくは請求項2において、前記容量は、活性層材料、ゲート電極を構成する材料、あるいは配線材料のうちのいずれか2つの材料を用いて構成された容量であることを特徴としている。

【0024】

請求項6の記載によると、本発明の表示装置の駆動回路は、請求項1乃至請求項5のいずれか1項において、前記一導電型とは、Nチャネル型であることを特徴としている。

【0025】

請求項7の記載によると、本発明の表示装置の駆動回路は、請求項1乃至請求項5のいずれか1項において、前記一導電型とは、Pチャネル型であることを特徴としている。

20

【0026】

請求項8の記載によると、本発明の表示装置の駆動回路は、請求項6において、前記入力信号がHi電位のときの電位は第3の電源電位に等しく、Lo電位のときの電位は第4の電源電位に等しいとき、第2の電源電位 第4の電源電位 < 第3の電源電位 第1の電源電位を満たすことを特徴としている。

【0027】

請求項9の記載によると、本発明の表示装置の駆動回路は、請求項7において、前記入力信号がHi電位のときの電位は第3の電源電位に等しく、Lo電位のときの電位は第4の電源電位に等しいとき、第1の電源電位 第4の電源電位 < 第3の電源電位 第2の電源電位を満たすことを特徴としている。

30

【0028】

請求項10の記載によると、本発明の表示装置の駆動回路は、請求項1乃至請求項9のいずれか1項において、前記表示装置の駆動回路は、インバータ、バッファ、あるいはレベルシフタであること、あるいはインバータ、バッファあるいはレベルシフタの構成要件となっていることを特徴としている。

【発明の効果】

【0029】

本発明の表示装置の駆動回路によって、表示装置の駆動回路および画素部を、一導電型のTFTのみによって構成することが可能となり、表示装置の作製工程を削減することによって、低コスト化、歩留まりの向上に寄与し、より安価に表示装置の供給が可能となる。

40

【図面の簡単な説明】

【0030】

【図1】本発明の表示装置の駆動回路の動作原理を説明する図。

【図2】本発明の表示装置の駆動回路の基本的一形態であるインバータとその入出力信号の波形を示す図。

【図3】本発明の表示装置の駆動回路の基本的一形態であるインバータを複数段接続して用いる場合の接続例を示す図。

50

【図4】本発明の表示装置の駆動回路の実施例として示したレベルシフタとその入出力信号の波形を示す図。

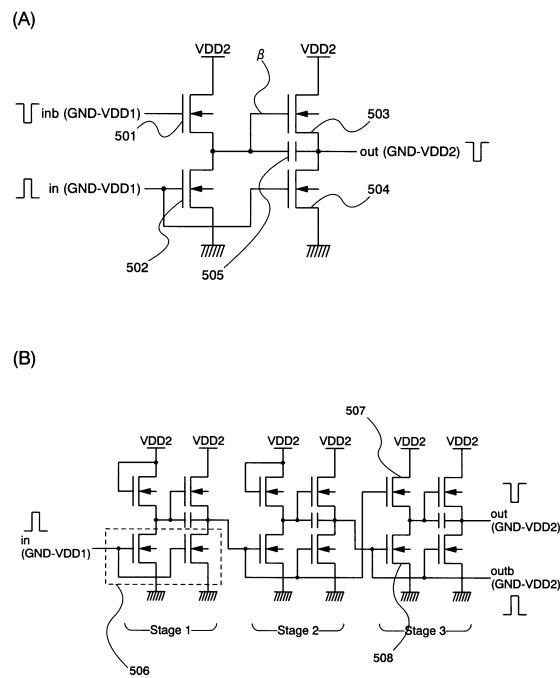

【図5】レベルシフタの動作についての説明図およびレベルシフタの構成例を示す図。

【図6】反転信号を有する場合の2入力型レベルシフタの構成例を示す図。

【図7】本発明を適用して作製した表示装置の概略図。

【図8】本発明の表示装置の駆動回路の電子機器への適用例を示す図。

【図9】従来型CMOSインバータと負荷型インバータの構成と、それぞれの入出力信号の波形を示す図。

【図10】4 TFT型のインバータと3 TFT型のインバータにおける入力信号と回路動作を説明する図。

10

【発明を実施するための形態】

【0031】

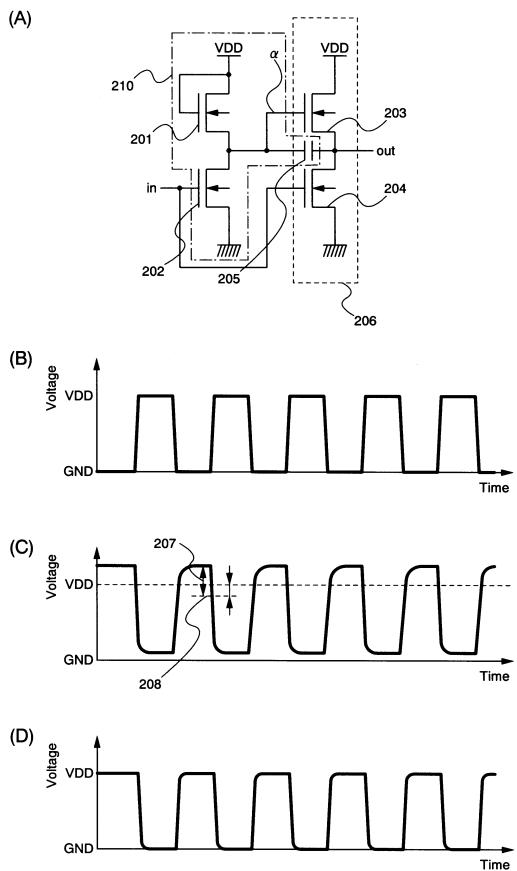

図2(A)は、本発明の表示装置の駆動回路の1形態を示したものであり、インバータとして機能する回路である。N型TFT201～204および容量205によって構成されており、点線枠206で囲われた部分が、図1(A)に示した回路に相当する。点線枠210で囲われた部分が、出力振幅補償回路を構成している。出力振幅補償回路210は、N型TFT203のゲート電極に浮遊状態を作り出すことを目的としたものであり、同一の機能を有する限り、図2(A)の構成に限定しない。

【0032】

20

図2(A)の回路において、入力信号はN型TFT202およびN型TFT204のゲート電極に入力される。N型TFT201は負荷として機能し、N型TFT201、202によって構成される回路からの出力(図2(A)中、このノードをとおく)が、N型TFT203のゲート電極に入力される。

【0033】

30

回路の動作詳細について順を追って説明する。なお、電源電位はVDDおよびGND、入力信号の振幅もVDD(Hi) - GND(Lo)とする。まず、入力信号の電位がHiのとき、N型TFT202、204がONする。ここで、N型TFT201はゲート電極とドレイン領域とが接続されているため飽和動作しているが、N型TFT202の電流能力をN型TFT201の電流能力よりも十分に高くすることによって、ノードの電位はGND側に引き下げられる。これにより、N型TFT203がOFFし、出力ノードにはLo電位が出力される。

【0034】

続いて、入力信号の電位がLoのとき、N型TFT202、204がOFFする。これにより、ノードの電位は、VDD側に引き上げられ、その電位が(VDD - VthN)となったところで一旦浮遊状態となる。一方、ノードの電位が上昇を始めると、やがてN型TFT203がONし、出力ノードの電位がVDD側に引き上げられる。ノードが浮遊状態となったとき、依然出力ノードの電位は上昇を続けているため、N型TFT203のゲート - ソース間容量205の存在によって、出力ノードの電位上昇に伴い、浮遊状態にあるノードの電位も上昇する。これにより、ノードの電位が、(VDD + VthN)よりも高い電位となることが出来る。よって、出力ノードにはHi電位が出力され、このときの電位はVDDに等しくなる。

40

【0035】

以上のような動作により、出力信号の振幅は、入力信号の振幅に対して減衰なく得られる。このように、2点間の容量結合を利用して電位を引き上げる方法をブーストストラップ法という。図2(B)は、図2(A)に示した回路の入力信号の波形を示したものであり、図2(C)は、ノードにおける電位の波形を示したものであり、図2(D)は出力信号の波形を示したものである。図2(C)中、208で示される電位は、VDDよりもVthNだけ低下した電位であり、ブーストストラップによって、207で示す分だけ、ノードの電位が引き上げられる。結果、図2(D)に示すように、出力ノードがHi電位の

50

とき、その電位はVDDまで上昇し、VDD-GND間の振幅を有する出力信号を得ることが出来る。

【0036】

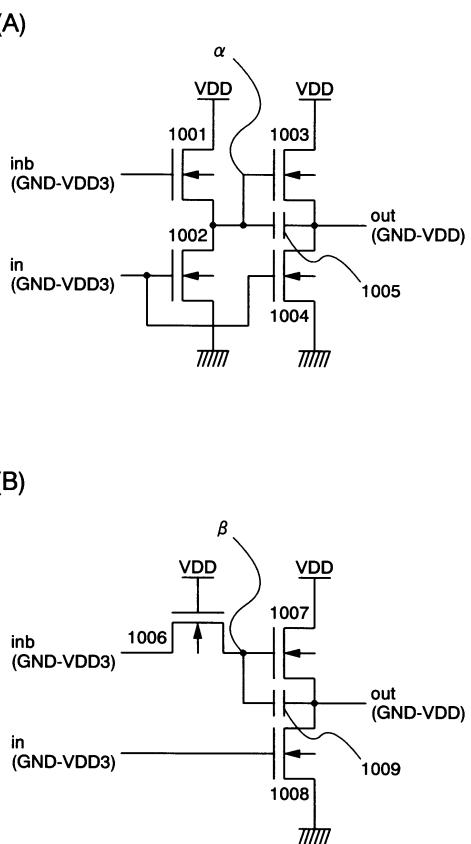

ところで、本発明の表示装置の駆動回路においては、ブートストラップ法による出力信号の振幅補償を動作の基本としているが、そのとき、容量結合を利用するTFTのゲート電極が浮遊状態となっていることが前提となる。図10は、ブートストラップ法を利用した回路の構成例を挙げているが、図10(A)は本発明の表示装置の駆動回路の基本構成を示しているが、ノード<sub>1</sub>が浮遊状態となっていることにより、TFT1003のゲート-ソース間の容量1005を利用してノード<sub>1</sub>の電位を引き上げ、それによって出力信号の振幅を補償する。図10(B)は3個のTFTからなる回路を示しているが、こちらについても同様に、ノード<sub>1</sub>が浮遊状態となっていることにより、TFT1007のゲート-ソース間容量1009を利用してノード<sub>1</sub>の電位を引き上げ、それによって出力信号の振幅を補償する。

【0037】

続いて、入力信号の振幅と電源電位について考える。今、高電位側の電源電位はVDD、低電位側の電源電位はGNDであり、入力信号(in)の振幅はVDD-GNDであり、inbは入力信号の反転信号である。ここで、in、inbの振幅がそれぞれVDD3-GND(ただし、GND < VthN < VDD3 < VDD-GND)である場合のノード<sub>1</sub>、ノード<sub>2</sub>の状態について考える。図10(A)において、inbがHiのとき、N型TFT1001のゲート電極電位はVDD3となる。VthN < VDD3であるから、N型TFT1001はONし、ノード<sub>1</sub>の電位はVDD側に引き上げられ、その電位が(VDD3-VthN)となったところで浮遊状態となる。つまり、inbのHi電位がVthNを上回っていれば、ノード<sub>1</sub>は確実に浮遊状態となることが出来、ブートストラップによってN型TFT1003のゲート電極電位を引き上げる動作が可能となる。一方、図10(B)においては、N型TFT1006のゲート電極電位は常にVDDであるから、inbがHiのとき、ノード<sub>1</sub>の電位はVDD3まで引き上げられる。ただし今、VDD3 < VDD-GNDであるから、N型TFT1006は入力信号の電位に関わらず常にONの状態を取る。よってノード<sub>1</sub>は浮遊状態とはならない。故に、ブートストラップによってノード<sub>1</sub>の電位を引き上げることが出来ないことになる。つまり、図10(B)に示した回路の場合、ノード<sub>1</sub>が浮遊状態となるためには、inbのLo電位がGNDであるとき、少なくともHi電位が(VDD-GND)以上にあるという最低条件があるため、低電圧駆動やTFTの特性ばらつきの面を考えると不利である。

【0038】

このように、入力信号の振幅が電源電圧よりも小さい場合の、ある特定の条件下では、図10(B)のような構成ではノード<sub>1</sub>に浮遊状態を与えない可能性が考えられるのに対し、本発明で示した図10(A)の構成であれば、確実にノード<sub>1</sub>を浮遊状態に出来るメリットがある。

【0039】

以下に、本発明の実施例について記載する。

【実施例1】

【0040】

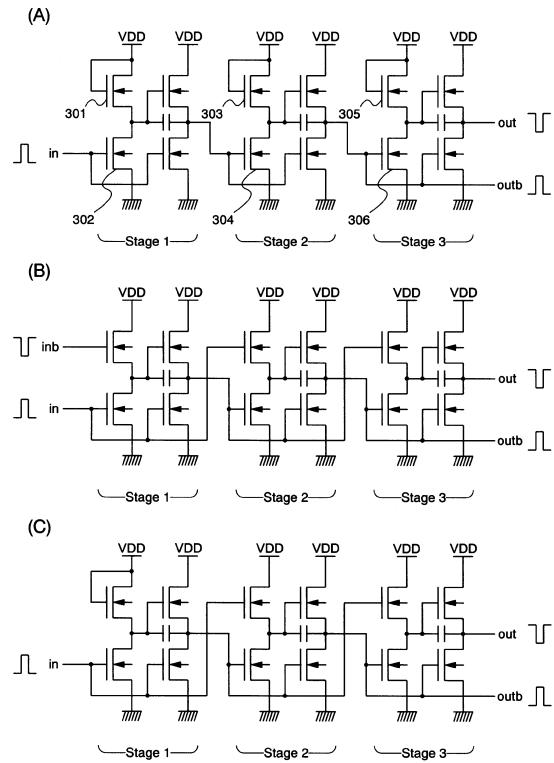

図3(A)は、本発明の表示装置の駆動回路の一形態であるインバータを複数段接続した回路を示している。表示装置の駆動回路等においては、このような回路をバッファとして用いることが多い。ここで、図3(A)のような回路を用いる場合、以下のようなデメリットが挙げられる。

【0041】

図3(A)において、入力信号がHiのとき、N型TFT302がONする。

ここで、N型TFT301は、ゲート-ドレイン間を短絡した負荷として機能しており、常に飽和動作しているため、N型TFT302がONすることによって、VDD-GND間に貫通電流が流れる。これは、各段のTFT303、304および305、306にお

10

20

30

40

50

いても同様であり、消費電流が大きくなってしまう。

【0042】

このような問題を回避するための例として、図3(B)に示すような、2入力型のインバータを用いる方法が挙げられる。このような回路の場合、VDD-GND間に配置されているTFTは、入力信号の極性が常に逆であることから、排他的動作をするため、貫通電流が流れない。

【0043】

ただし、図3(B)の回路を用いる場合、入力信号として、反転、非反転の2相の信号を用意する必要がある。

【0044】

そこで、双方を組み合わせた形として、図3(C)に示すように、先頭段には本発明の1入力型インバータを用い、2段目以降は2入力型インバータを用いる。2段目の入力は、一方には前段の出力信号を、もう一方には前段の入力信号を入力すればよい。これにより、1入力型であり、かつ貫通電流を最小限に抑えたバッファとして用いることが出来る。

【実施例2】

【0045】

本発明の表示装置の駆動回路は、回路に供給する電源電位として、入力信号の振幅電位と異なる電位を与えることにより、レベルシフタとして機能させることも容易である。以下にその例を示す。

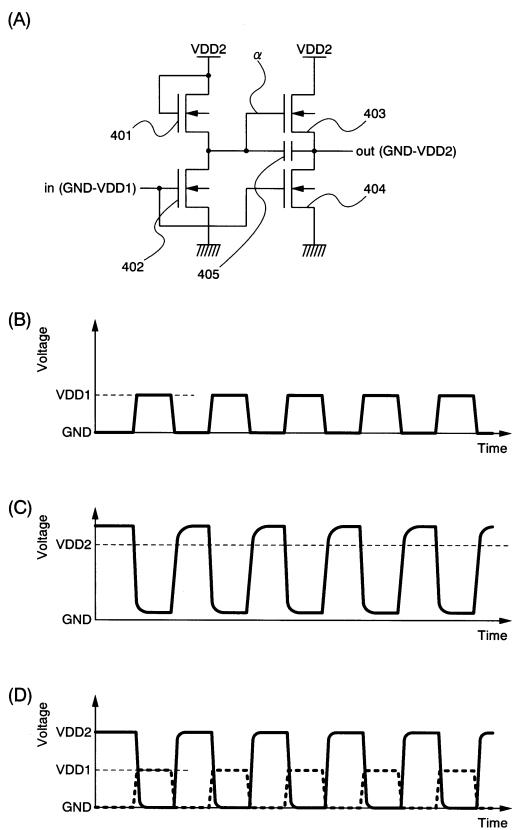

【0046】

まず、電源電位として、GND、VDD1、VDD2の3電位を考え、それぞれの大小関係は、GND < VDD1 < VDD2とする。このとき、GND-VDD1間の振幅を有する信号を入力し、GND-VDD2間の振幅に変換して取り出す場合を例として考える。

【0047】

図4(A)に例を示す。回路の構成は実施形態および実施例1と同様で良い。入力信号の振幅がGND-VDD1間であり、N型TFT401、403の不純物領域の一端に接続される電源の電位をVDD2としている。

【0048】

回路の動作について説明する。入力信号の波形を図4(B)に示す。GND-VDD1間の振幅をもった信号が、N型TFT402および404のゲート電極に入力される。入力信号がHi電位であるとき、N型TFT402、404がONし、ノードにおける電位がGND側に引き下げられ、N型TFT403はOFFする。よって出力ノードにおける電位はLo電位となる。

【0049】

入力信号がLo電位であるとき、N型TFT402、404がOFFし、ノードにおける電位がVDD2側に引き上げられる。したがってN型TFT403がONし、出力ノードの電位が上昇する。一方、ノードにおいては、その電位が(VDD2 - N型TFT403のしきい値電圧の絶対値)となったところで浮遊状態となる。その後、出力ノードの電位上昇に伴い、N型TFT403のゲート-ソース間に存在する容量結合405によってノードの電位はさらに引き上げられ、VDD2よりも高い電位をとる(図4(C))。よって、出力ノードの電位はHi電位となり、GND-VDD2間の振幅を持った信号が出力される(図4(D)実線)。

【0050】

本実施例で示した回路がレベルシフタとして容易に扱うことが出来る理由として、高電位側電源(VDD2)に接続されたTFT401、403のゲート電極には、低電圧振幅の信号入力がない点が挙げられる。図5(A)に示す2入力型の回路において、高電位側電源(VDD2)に接続されたTFT501に低電圧振幅の信号を入力しても、ノードの電位はVDD1付近までしか上昇することができない。したがってTFT503もまた

10

20

30

40

50

、十分にONすることが出来ず、容量結合を用いてTFT503のゲート電極電位を持ち上げることが出来ないため、正常動作が望めない。

【0051】

よって、本実施例にて示したレベルシフタの直後にかかる負荷が大きく、バッファ等の構成を必要とする場合には、図5(B)のように、1入力型の回路を2段用いて、その後の入力信号の振幅を全て高電圧振幅とする必要がある。図5(B)においては、低電圧振幅の信号が入力されるTFTは、点線枠506で囲まれた部分のTFTに限られ、1入力型の回路を2段重ねることによって、3段目の2入力(TFT507、508のゲート電極への入力)はいずれも高電圧振幅の信号が入力されるため、正常に動作することが出来る。

10

【0052】

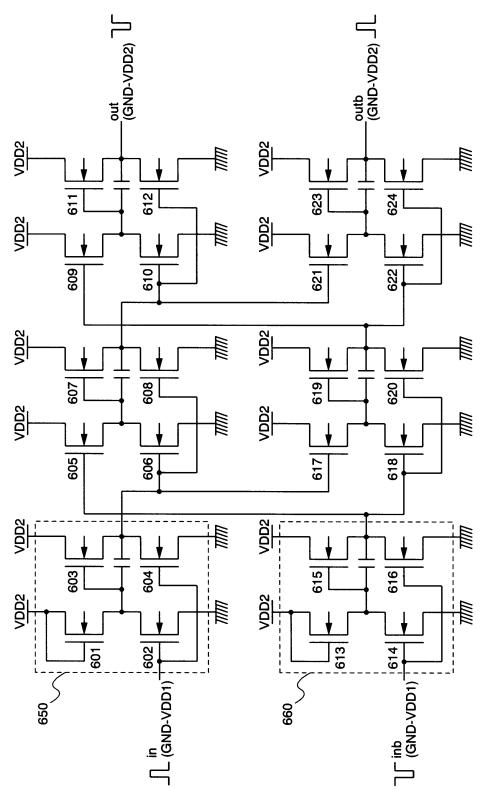

また、振幅変換を行う信号が反転信号を有している場合、互いの出力信号を、次段の反転入力として用いる構成としても良い。図6に例を示す。入力信号はin、inbであり、それぞれTFT602、614のゲート電極に入力される。

レベルシフタ1段目650の出力は、2段目のTFT606、617に入力され、660の出力は、2段目のTFT605、618に入力される。2段目への入力信号は、いずれも高電圧振幅の信号であるから、以後は正常にバッファとして機能し、最終段より、出力信号Out、outbを得る。

20

【実施例3】

【0053】

本実施例においては、本発明の表示装置の駆動回路を用いて表示装置を作製した例について説明する。

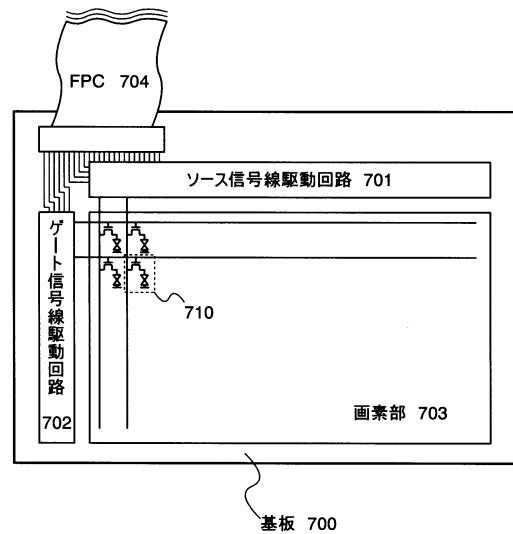

【0054】

図7は、表示装置の概略図である。基板700上に、ソース信号線駆動回路701、ゲート信号線駆動回路702および画素部703を一体形成にて作製している。画素部において、点線枠710で囲まれた部分が1画素である。図の例では、液晶表示装置の画素を示しており、1個のTFT(以後、画素TFTと表記する)によって液晶素子の一電極に印加される電荷の制御を行っている。ソース信号線駆動回路701、ゲート信号線駆動回路702への信号入力は、フレキシブルプリント基板(Flexible Print Circuit: FPC)704を介して、外部より供給される。

30

【0055】

本実施例にて示す表示装置は、本発明の表示装置の駆動回路を用いて構成することにより、画素部を含む表示装置全体を構成する駆動回路を、画素TFTと同一の極性を有する一極性のTFT(例えばN型TFT)のみを用いて作製している。これにより、半導体層にP型を付与するイオンドーピング工程を省略することが可能となり、製造コストの削減や歩留まり向上等に寄与することができる。

【0056】

なお、本実施例の表示装置を構成したTFTの極性はN型であるが、P型TFTのみを用いて駆動回路および画素TFTを構成することも、本発明によってもちろん可能となる。この場合は、省略されるイオンドーピング工程は、半導体層にN型を付与する工程であることを付記する。また、本発明は液晶表示装置のみならず、絶縁体上に駆動回路を一体形成して作製する装置ならばいずれの物にも適用が可能である。

40

【実施例4】

【0057】

本発明の表示装置の駆動回路は、様々な電子機器に用いられている表示装置の作製に適用が可能である。このような電子機器には、携帯情報端末(電子手帳、モバイルコンピュータ、携帯電話等)、ビデオカメラ、デジタルカメラ、パーソナルコンピュータ、テレビ、携帯電話等が挙げられる。それらの一例を図8に示す。

【0058】

図8(A)は液晶ディスプレイ(LCD)であり、筐体3001、支持台3002、表

50

示部 3 0 0 3 等により構成されている。本発明の表示装置の駆動回路は、表示部 3 0 0 3 の作製に適用が可能である。

【 0 0 5 9 】

図 8 ( B ) はビデオカメラであり、本体 3 0 1 1 、表示部 3 0 1 2 、音声入力部 3 0 1 3 、操作スイッチ 3 0 1 4 、バッテリー 3 0 1 5 、受像部 3 0 1 6 等により構成されている。本発明の表示装置の駆動回路は、表示部 3 0 1 2 の作製に適用が可能である。

【 0 0 6 0 】

図 8 ( C ) はノート型のパーソナルコンピュータであり、本体 3 0 2 1 、筐体 3 0 2 2 、表示部 3 0 2 3 、キーボード 3 0 2 4 等により構成されている。本発明の表示装置の駆動回路は、表示部 3 0 2 3 の作製に適用が可能である。

10

【 0 0 6 1 】

図 8 ( D ) は携帯情報端末であり、本体 3 0 3 1 、スタイルス 3 0 3 2 、表示部 3 0 3 3 、操作ボタン 3 0 3 4 、外部インターフェイス 3 0 3 5 等により構成されている。本発明の表示装置の駆動回路は、表示部 3 0 3 3 の作製に適用が可能である。

【 0 0 6 2 】

図 8 ( E ) は音響再生装置、具体的には車載用のオーディオ装置であり、本体 3 0 4 1 、表示部 3 0 4 2 、操作スイッチ 3 0 4 3 、3 0 4 4 等により構成されている。本発明の表示装置の駆動回路は表示部 3 0 4 2 の作製に適用が可能である。また、本実施例では車載用オーディオ装置を例に挙げたが、携帯型もしくは家庭用のオーディオ装置に用いても良い。

20

【 0 0 6 3 】

図 8 ( F ) はデジタルカメラであり、本体 3 0 5 1 、表示部 ( A ) 3 0 5 2 、接眼部 3 0 5 3 、操作スイッチ 3 0 5 4 、表示部 ( B ) 3 0 5 5 、バッテリー 3 0 5 6 等により構成されている。本発明の表示装置の駆動回路は、表示部 ( A ) 3 0 5 2 および表示部 ( B ) 3 0 5 5 の作製に適用が可能である。

【 0 0 6 4 】

図 8 ( G ) は携帯電話であり、本体 3 0 6 1 、音声出力部 3 0 6 2 、音声入力部 3 0 6 3 、表示部 3 0 6 4 、操作スイッチ 3 0 6 5 、アンテナ 3 0 6 6 等により構成されている。本発明の表示装置の駆動回路は、表示部 3 0 6 4 の作製に適用が可能である。

【 0 0 6 5 】

30

なお、本実施例に示した例はごく一例であり、これらの用途に限定しないことを付記する。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(56)参考文献 特開平05-303354(JP,A)

特開平5-224629(JP,A)

特開昭55-156427(JP,A)

特許第4785271(JP,B2)

特許第4860765(JP,B2)

特許第5493023(JP,B2)

特許第6167133(JP,B2)

米国特許第03506851(US,A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 36

G 09 G 3 / 20