(12) NACH DEM VERTRAG ÜBER DIE INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES

PATENTWESENS (PCT) VERÖFFENTLICHTE INTERNATIONALE ANMELDUNG

(19) Weltorganisation für geistiges Eigentum

Internationales Büro

(43) Internationales Veröffentlichungsdatum

29. November 2007 (29.11.2007)

(10) Internationale Veröffentlichungsnummer

**WO 2007/134581 A1**

(51) Internationale Patentklassifikation:

**H01L 21/58** (2006.01)

(81) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare nationale Schutzrechtsart): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) Internationales Aktenzeichen: PCT/DE2007/000897

(22) Internationales Anmeldedatum:

16. Mai 2007 (16.05.2007)

(25) Einreichungssprache: Deutsch

(26) Veröffentlichungssprache: Deutsch

(30) Angaben zur Priorität:

10 2006 023 683.1 19. Mai 2006 (19.05.2006) DE

10 2006 028 692.8 22. Juni 2006 (22.06.2006) DE

(84) Bestimmungsstaaten (soweit nicht anders angegeben, für jede verfügbare regionale Schutzrechtsart): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), eurasisches (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), europäisches (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(71) Anmelder (für alle Bestimmungsstaaten mit Ausnahme von US): **OSRAM OPTO SEMICONDUCTORS GMBH** [DE/DE]; Wernerwerkstrasse 2, 93049 Regensburg (DE).

**Veröffentlicht:**

- mit internationalem Recherchenbericht

- vor Ablauf der für Änderungen der Ansprüche geltenden Frist; Veröffentlichung wird wiederholt, falls Änderungen eintreffen

Zur Erklärung der Zwei-Buchstaben-Codes und der anderen Abkürzungen wird auf die Erklärungen ("Guidance Notes on Codes and Abbreviations") am Anfang jeder regulären Ausgabe der PCT-Gazette verwiesen.

(74) Anwalt: **EPPING HERMANN FISCHER PATENTANWALTSGESELLSCHAFT MBH**; Ridlerstrasse 55, 80339 München (DE).

(54) Title: ELECTRICALLY CONDUCTING CONNECTION WITH INSULATING CONNECTION MEDIUM

(54) Bezeichnung: ELEKTRISCH LEITENDE VERBINDUNG MIT ISOLIERENDEM VERBINDUNGSMEDIUM

(57) Abstract: Device with a first component (5) with a first surface (6), a second component (8) with a second surface (9), and a connecting layer (7) between the first surface (6) of the first component (5) and the second surface (9) of the second component (8), in which the connecting layer (7) comprises an electrically insulating adhesive, and an electrically conducting contact exists between the first surface (6) of the first component (5) and the second surface (9) of the second component (8).

(57) Zusammenfassung: Vorrichtung mit einem ersten Bauteil (5) mit einer ersten Oberfläche (6), einem zweiten Bauteil (8) mit einer zweiten Oberfläche (9) und einer Verbindungsschicht (7) zwischen der ersten Oberfläche (6) des ersten Bauteils (5) und der zweiten Oberfläche (9) des zweiten Bauteils (8), wobei die Verbindungsschicht (7) einen elektrisch isolierenden Klebstoff umfasst und ein elektrisch leitender Kontakt zwischen der ersten Oberfläche (6) des ersten Bauteils (5) und

des zweiten Bauteils (8) besteht.

WO 2007/134581 A1

## Beschreibung

### Elektrisch leitende Verbindung mit isolierendem Verbindungsmedium

Die vorliegende Erfindung betrifft eine Vorrichtung mit einem ersten Bauteil mit einer ersten Oberfläche, einem zweiten Bauteil mit einer zweiten Oberfläche und einer Verbindungsschicht zwischen der ersten Oberfläche des ersten Bauteils und der zweiten Oberfläche des zweiten Bauteils, und ein Verfahren zur Herstellung einer solchen Vorrichtung.

Um zwei Bauteile mechanisch, elektrisch und/oder thermisch miteinander zu verbinden, können beispielsweise Methoden mit einer Verbindungsschicht, etwa aus einem Lot oder einem Klebstoff, angewendet werden. Wie beispielsweise in der Druckschrift EP 0905797 A2 beschrieben, wird in der Regel ein elektrisch leitender Klebstoff oder ein metallisches Lot verwendet, wenn eine elektrisch leitende Verbindung angestrebt ist, während für elektrisch isolierende Verbindungen ein elektrisch isolierender Klebstoff eingesetzt wird. Die Verwendung von Lot ist jedoch aufgrund der relativ hohen Verarbeitungstemperaturen nicht immer möglich. Weiterhin ist der Einsatz von elektrisch leitendem Klebstoff aufgrund der Füllstoffe gegenüber elektrisch isolierenden Klebstoffen in der Regel aufwändig.

Eine Aufgabe der vorliegenden Erfindung ist es daher, eine Vorrichtung mit einer elektrisch isolierenden Verbindungsschicht zwischen zwei Bauteilen anzugeben, wobei eine elektrisch leitende Verbindung zwischen den zwei Bauteilen vorliegt. Eine weitere Aufgabe der vorliegenden

Erfindung ist es, ein Verfahren zur Herstellung einer solchen Verbindung anzugeben.

Diese Aufgaben werden durch eine Vorrichtung mit den Merkmalen des Patentanspruchs 1 gelöst. Vorteilhafte Ausgestaltungen der Vorrichtung sowie ein Verfahren sind Gegenstand weiterer Ansprüche.

Eine Vorrichtung weist gemäß einer Ausführungsform der Erfindung insbesondere ein erstes Bauteil mit einer ersten Oberfläche und ein zweites Bauteil mit einer zweiten Oberfläche auf, wobei

- zumindest eine der ersten und zweiten Oberfläche topographische Oberflächenstrukturen aufweist,

- die erste Oberfläche (6) des ersten Bauteils (5) mit der zweiten Oberfläche (9) des zweiten Bauteils (8) über eine elektrisch isolierende Verbindungsschicht (7) verbunden ist und

- ein elektrisch leitender Kontakt zwischen der ersten Oberfläche (6) des ersten Bauteils (5) und der zweiten Oberfläche (9) des zweiten Bauteils (8) über die topographischen Oberflächenstrukturen besteht.

Es sei an dieser Stelle darauf hingewiesen, dass mit dem Begriff „Bauteil“ nicht nur fertige Bauelemente wie beispielsweise Leuchtdioden (LEDs) oder Laserdioden gemeint sind, sondern auch Substrate oder Epitaxieschichtenfolgen, so dass das erste Bauteil und das zweite Bauteil verbunden durch die Verbindungsschicht ein übergeordnetes drittes Bauteil bilden bzw. Teil eines solchen sind.

Dabei kann eine Oberfläche mit einer topographischen Oberflächenstruktur ein mikroskopisches und/oder ein

makroskopisches Höhenprofil aufweisen. Ein Höhenprofil kann sich dabei regelmäßig oder unregelmäßig in eine oder in zwei Richtungen parallel zur Oberfläche über die gesamte Oberfläche oder über einen oder mehrere Teilbereiche der Oberfläche erstrecken.

Weiterhin kann es möglich sein, dass sowohl die erste als auch die zweite Oberfläche topographische Oberflächenstrukturen aufweist. Die topographischen Oberflächenstrukturen können dabei zumindest in einem Teilbereich gleich, ähnlich oder verschieden sein.

Bei einer Ausführungsform der Vorrichtung sind die topographischen Oberflächenstrukturen durch die Rauigkeit der ersten und/oder zweiten Oberfläche bedingt. Das kann insbesondere beispielsweise bedeuten, dass topographische Oberflächenstrukturen, die die erste Oberfläche aufweist, verschieden von topographischen Oberflächenstrukturen sind, die die zweite Oberfläche aufweist, beispielsweise aufgrund unterschiedlicher Rauigkeiten der ersten und zweiten Oberfläche. Bevorzugt können die topographischen Oberflächenstrukturen der ersten Oberfläche und die topographischen Oberflächenstrukturen der zweiten Oberfläche gleich oder ähnlich sein. Das kann insbesondere bedeuten, dass die Rauigkeiten und Rautiefe der ersten und zweiten Oberflächen gleich oder zumindest ähnlich sind.

Bei einer Ausführungsform der Vorrichtung kann durch die elektrisch isolierenden Verbindungsschicht vorteilhafterweise eine wesentlich dünnerne Verbindungsschicht zwischen den beiden Oberflächen der Bauteile erzielt werden als durch eine elektrisch leitende Verbindungsschicht. Insbesondere kann dies möglich sein, wenn die elektrisch isolierende

Verbindungsschicht einen elektrisch isolierenden Klebstoff aufweist. Das kann weiterhin bedeuten, dass die elektrisch isolierende Verbindungsschicht aus einem elektrisch isolierenden Klebstoff oder einer Mischung aus elektrisch isolierenden Klebstoffen oder aus einer Mischung eines elektrisch isolierenden Klebstoffes mit weiteren elektrisch isolierenden Zusätzen besteht. Ein elektrisch isolierender Klebstoff oder eine Mischung aus elektrisch isolierenden Klebstoffen oder eine Mischung eines elektrisch isolierenden Klebstoffes mit weiteren elektrisch isolierenden Zusätzen kann im Vergleich zur Verwendung einer elektrisch leitenden Klebstoffes beispielsweise dadurch vorteilhaft sein, dass der elektrisch isolierende Klebstoff beispielsweise keine elektrisch leitenden Füllstoffe aufweist. Aufgrund der Füllstoffe in elektrisch leitenden Klebstoffen sind bei der Verwendung elektrisch leitender Klebstoffe Klebedicken im Bereich von einigen 10 µm erforderlich. Durch eine sehr dünne Verbindungsschicht hingegen, wie sie beispielsweise mit einem elektrisch isolierenden Klebstoff möglich ist, kann es möglich sein, dass vorteilhafterweise der thermische Widerstand der Verbindungsschicht gegenüber einer Verbindungsschicht mit größerer Dicke verringert wird. So können beispielsweise elektrisch isolierende Verbindungsschichten, die beispielsweise elektrisch isolierende Klebstoffe aufweisen, mit Dicken von 100 nm bei einer planaren, vollflächigen Anbindung und Wärmebelastung weniger als 1 K/W zum Wärmeübergangswiderstand beitragen. Somit kann eine gute thermische Ankopplung zwischen dem ersten und dem zweiten Bauteil gewährleistet sein. Insbesondere kann ein elektrisch isolierender Klebstoff eine Wärmeleitfähigkeit im Bereich von 0,2 bis 0,4 W/mK, insbesondere von 0,293 W/mK bei 24°C, 0,310 W/mK bei 45°C und 0,324 W/mK bei 66°C aufweisen.

Bei einer weiteren Ausführungsform der Vorrichtung weist die elektrisch isolierende Verbindungsschicht einen elektrisch isolierenden Klebstoff auf, was insbesondere bedeuten kann, dass die Verbindungsschicht keine elektrisch leitenden Füllstoffe aufweist. Im Vergleich zur elektrischen Kontaktierung beispielsweise eines Halbleiterchips mittels elektrisch leitenden Klebstoffen mit Füllstoffen kann es daher möglich sein, dass bei der Verwendung einer elektrisch isolierenden Verbindungsschicht ohne elektrisch leitende Füllstoffe keine Vorkehrung gegen eine mögliche Migration der Füllstoffe oder deren Bestandteile getroffen werden muss. Dies kann insofern vorteilhaft sein, da insbesondere bei der Verwendung von Füllstoffen, die Silber aufweisen, durch die Migration des Silbers in die funktionellen Schichten des Halbleiterchips die Funktionsfähigkeit des Halbleiterchips eingeschränkt werden kann. Weiterhin kann die Verwendung einer elektrisch isolierenden Verbindungsschicht ohne elektrisch leitende Füllstoffe vorteilhaft sein, da beispielsweise goldgefüllter elektrisch leitender Klebstoff die Prozesskosten erhöhen kann. Zusätzlich sind die üblichen elektrisch leitenden Klebstoffe oft nicht mit Prozesschemikalien, wie sie z.B. in der Dünnfilm-LED-Herstellung eingesetzt werden, verträglich.

Gegenüber der Verwendung von Loten kann die Verwendung von elektrisch isolierenden Verbindungsschichten, die beispielsweise elektrisch isolierenden Klebstoff aufweisen, insbesondere den Vorteil bieten, dass elektrisch isolierende Verbindungsschichten bei im Vergleich zu Lötprozessen deutlich geringeren Temperaturen verarbeitet werden können. So erfordern Lotverbindungen oft Prozesstemperaturen von mehr als 200°C zur Herstellung einer metallurgischen Verbindung,

die nicht unbedingt mit den Anforderungen der zu verbindenden Bauteile vereinbar sind. Zusätzlich kann es möglich sein, dass eine elektrisch isolierende Verbindungsschicht, die beispielsweise einen elektrisch isolierenden Klebstoff aufweist, keinen zusätzlichen Aufwand hinsichtlich der Separation und zum Schutz von Funktionsschichten zum Beispiel durch Diffusionssperren erforderlich macht, wie es bei Lötverbindungen mitunter erforderlich ist.

Das erste Bauteil oder das zweite Bauteil oder beide können beispielsweise ein Substrat, ein Wafer, ein Glasträger, eine Wärmesenke, eine Epitaxieschichtenfolge, ein Halbleiterchip wie ein Leuchtdiodenchip oder ein Laserdiodenchip oder auch ein optoelektronisches Bauelement wie eine organische Leuchtdiode (OLED) oder eine Leuchtdiode auf Halbleiterbasis sein. Die laterale Ausdehnung der Verbindungsschicht kann daher von der Größe von Wafern bis zur Größe von Chipkontakte und kleiner reichen.

Insbesondere kann als erstes Bauteil eine Epitaxieschichtenfolge mit einer aktiven Zone, in der im Betrieb elektromagnetische Strahlung erzeugt wird, und als zweites Bauteil ein Träger wie ein Glassubstrat oder ein Wafer verwendet werden. Die Verbindung dieser beiden Bauteile miteinander ist beispielsweise bei der Herstellung eines Dünnfilm-Halbleiterchips zweckmäßig.

Dünnfilm-Halbleiterchips zeichnen sich insbesondere durch mindestens eines der folgenden charakteristischen Merkmale aus:

- An einer zu einem Träger hin gewandten ersten Hauptfläche einer strahlungserzeugenden Epitaxieschichtenfolge ist eine reflektierende Schicht aufgebracht oder ausgebildet, die

zumindest einen Teil der in der Epitaxieschichtenfolge erzeugten elektromagnetischen Strahlung in diese zurückreflektiert;

- die Epitaxieschichtenfolge weist eine Dicke im Bereich von 20µm oder weniger, insbesondere im Bereich von 10 µm auf; und

- die Epitaxieschichtenfolge enthält mindestens eine Halbleiterschicht mit zumindest einer Fläche, die eine Durchmischungsstruktur aufweist, die im Idealfall zu einer annähernd ergodischen Verteilung der Strahlung in der Epitaxieschichtenfolge führt, d.h. sie weist ein möglichst ergodisch stochastisches Streuverhalten auf.

Ein Grundprinzip eines Dünnschicht-Leuchtdiodenchips ist beispielsweise in I. Schnitzer et al., Appl. Phys. Lett. 63 (16), 18. Oktober 1993, 2174 - 2176 beschrieben, deren Offenbarungsgehalt insofern hiermit durch Rückbezug aufgenommen wird.

Bei einem Dünnfilm-Halbleiterchip kann das Wachstumssubstrat der strahlungserzeugenden Epitaxieschichtenfolge in der Regel entfernt oder gedünnt sein und die Epitaxieschichtenfolge kann auf einen anderen Träger übertragen sein. Da die Verbindung zwischen Träger und Epitaxieschichtenfolge elektrisch leitend sein sollte, kann die vorliegend vorgeschlagene Verbindung insbesondere für einen Dünnfilm-Halbleiterchip geeignet sein um den Dünnfilm-Halbleiterchip über den Träger kontaktieren zu können. Weiterhin kann sich daraus der Vorteil ergeben, dass eine elektrisch isolierende Verbindungsschicht dünn genug sein kann, so dass sie einen geringen Wärmewiderstand aufweisen kann, um die Wärme von der Epitaxieschichtenfolge effektiv ableiten zu können, die beim Betrieb in dieser entstehen kann. Insbesondere kann es sein, dass bei einer elektrisch nichtleitenden Verbindung zwischen

dem Träger und der Epitaxieschichtenfolge eine Kontaktierungsmöglichkeit von der dem Träger abgewandten Seite der Epitaxieschichtefolge notwendig ist, was aber einen Mehrverbrauch an Epitaxiefläche und eine damit verbundene geringere Wirtschaftlichkeit zu Folge hätte.

Weiterhin kann das erste Bauteil eine Halbleiterschichtenfolge, etwa eine Epitaxieschichtenfolge, umfassen, die auf einer Seite wenigstens zwei elektrische Kontaktflächen aufweisen kann. Das zweite Bauteil kann ein Träger, beispielsweise ein Substrat oder ein Leiterrahmen, sein der ebenfalls wenigstens zwei elektrische Kontaktflächen aufweisen kann. Die jeweils wenigstens zwei elektrischen Kontaktflächen des ersten beziehungsweise des zweiten Bauteils können dabei dieselbe oder verschiedenen elektrische Polaritäten aufweisen. Beispielsweise kann es sich bei dem ersten Bauteil um eine strukturierte Epitaxieschichtenfolge für einen oben beschriebenen Dünnfilm-Halbleiterchip handeln oder um einen Halbleiterchip zur so genannten Flip-Chip-Montage, der auf einer Seite mittels zweier elektrischer Kontaktflächen mit unterschiedlicher elektrischer Polarität elektrisch an ein zweites Bauteil angeschlossen werden kann.

Weiterhin können gemäß der hier vorgeschlagenen Verbindung auch optoelektronische Halbleiterchips wie Leuchtdiodenchips oder Laserdiodenchips auf einer Wärmesenke oder einem Bauelementgehäuse befestigt werden.

Bei einer bevorzugten Ausführungsform weist die erste Oberfläche oder die zweite Oberfläche Vertiefungen auf. Dabei können die Vertiefungen nur auf der ersten Oberfläche des ersten Bauteils oder nur auf der zweiten Oberfläche des

zweiten Bauteils oder auf beiden zu verbindenden Oberflächen vorhanden sein.

Bei einer weiteren Ausführungsform weisen die erste Oberfläche des ersten Bauteils und/oder die zweite Oberfläche des zweiten Bauteils einen Fügebereich auf, innerhalb dem elektrisch isolierender Klebstoff angebracht sein kann, der die elektrisch leitende Verbindungsschicht bilden kann. Die Vertiefungen in der ersten und/oder zweiten Oberfläche sind dabei bevorzugt um den jeweiligen Fügebereich angeordnet. Bevorzugt können die Vertiefungen als Auffangreservoirs für den Klebstoff dienen. Dadurch kann es möglich sein, dass überschüssig aufgebrachter Klebstoff, der aus dem Fügebereich verdrängt wird, in die Auffangreservoirs abfließen und dort verbleiben kann. Die Vertiefungen können dabei weiterhin regelmäßig oder unregelmäßig beabstandet angeordnet sein.

Bei einer bevorzugten Ausführungsform weisen die Vertiefungen oder Aufnahmereservoirs eine gleichmäßige Anordnung auf. Eine gleichmäßige oder regelmäßige Anordnung kann beispielsweise vorteilhaft sein, da es möglich sein kann, dass die Vertiefungen mithilfe von im Herstellungsprozess von Epitaxieschichtenfolgen üblichen Photomasken herstellbar sind, und da es möglich sein kann, dass durch eine gleichmäßige oder regelmäßige Anordnung eine Verminderung der Epitaxiefläche vermieden werden kann.

Vorteilhafterweise kann zumindest eine der Oberflächen eine strukturierte Oberfläche aufweisen. Die Strukturierung kann dabei beispielsweise durch eine Mikroprismenstrukturierung oder Mikroreflektorenstrukturierung gegeben sein. Dabei können Vertiefungen oder Auffangreservoirs aufgrund von

Mikoprismen oder Mikroreflektoren ausgebildet sein, die beispielsweise durch Ätzen erzeugt werden können.

Vertiefungen oder Auffangreservoirs können beispielsweise als Mesagräben oder als Teile von Mesagräben ausgeführt sein, die beispielsweise eine gesamte Epitaxieschichtenfolge oder einen Teil davon durchschneiden können. Dabei kann die Tiefe der Vertiefungen der Dicke der Epitaxieschichtenfolge entsprechen oder geringer als diese sein. Die Vertiefungen können weiterhin eine Breite aufweisen, die durch die Breite der Mesagräben gegeben sein kann, welche wiederum beispielsweise durch spätere Verarbeitungsschritte wie etwa Vereinzeln vorgegeben sein kann. Es kann dabei vorteilhaft sein, wenn die Vertiefungen ein Volumen aufweisen, dass groß genug ist, um den gesamten verdrängten Klebstoff aufnehmen zu können. Andererseits kann durch das Volumen der Vertiefungen oder Auffangreservoirs und die angestrebte Dicke der Verbindungsschicht eine Bedingung für die maximal aufzutragende Klebstoffschicht ergeben. Beispielsweise kann es vorteilhaft sein, wenn die Vertiefungen beziehungsweise Auffangreservoirs durch Mesagräben gebildet sind, die einen Abstand von etwa 1000 µm und eine Grabenbreite von etwa 40 µm aufweisen und deren Tiefe beispielsweise der Dicke der Epitaxieschichtenfolge von etwa 7 µm entspricht. Dadurch kann sich eine Dicke von etwa 0,5 µm für eine Klebstoffschicht zum Auftragen als vorteilhaft erweisen.

Bei einer weiteren Ausführungsform können Vertiefungen oder Auffangreservoirs durch die Vertiefungen gegeben sein, die durch die Rauhigkeit einer Oberfläche oder eines Bereichs einer Oberfläche gegeben sind.

Bei einer weiteren bevorzugten Ausführungsform ist die mittlere Dicke der Verbindungsschicht in der Größenordnung der topographischen Oberflächenstrukturen der ersten und/oder der zweiten Oberfläche. Das kann insbesondere bedeuten, dass die mittlere Dicke der Verbindungsschicht in der Größenordnung der Rauhigkeit oder Rautiefe der ersten Oberfläche und/oder der zweiten Oberfläche ist.

Als Rauhigkeit kann der rms-Wert der Höhenvariationen einer Oberfläche bezeichnet werden, der als Wurzel aus dem mittleren quadratischen Abstand eines Höhenprofils einer Oberfläche von einer mittleren Höhe der Oberfläche definiert ist. Das Höhenprofil der Oberfläche kann beispielsweise mittels eines Rasterkraftmikroskops bestimmt werden, indem innerhalb eines oder mehrerer Ausschnitte der Oberfläche Höhenprofile aufgenommen werden. Von dem beispielsweise mittels Rasterkraftmikroskopie, Tastschnittprofilometrie oder Weißlichtinterferometrie erhaltenen Höhenprofil der Oberfläche kann eine mittlere Höhe bestimmt werden, die das arithmetische Mittel des Höhenprofils darstellt. Mithilfe der mittleren Höhe und des ermittelten Höhenprofils kann der rms-Wert als Wert für die Rauhigkeit der Oberfläche bestimmt werden.

Die Dicke der Verbindungsschicht wird als der Abstand zwischen der mittleren Höhe der ersten Oberfläche und der mittleren Höhe der zweiten Oberfläche definiert.

Die Rauhigkeit einer Oberfläche oder eines Bereichs einer Oberfläche kann dabei der natürlichen Rauhigkeit entsprechen, die sich bei der Abscheidung von Metallschichten, etwa elektrischen Metall-Halbleiter-Kontaktschichten oder metallischen reflektierenden Schichten, ergibt.

Die Rauigkeit einer Oberfläche oder eines Bereichs einer Oberfläche kann beispielsweise durch Verfahren etwa wie durch photolithographische Strukturierung oder Sandstrahlen erhöht werden. Weiterhin kann eine erhöhte Rauigkeit durch die Wahl geeigneter Abscheidebedingungen wie etwa eine langsame Aufdampfrate und/oder hohe Substrattemperaturen erreicht werden.

Eine hinreichend dünne Verbindungsschicht kann damit einen elektrisch leitenden Kontakt zwischen den Oberflächen der Bauteile insbesondere dadurch gewährleisten, dass beispielsweise erhöhte Bereiche der topographischen Oberflächenstrukturen der ersten Oberfläche mit der zweiten Oberfläche in direktem Kontakt stehen und/oder umgekehrt. Insbesondere können erhöhte Bereich der topographischen Oberflächenstrukturen der ersten Oberfläche mit erhöhten Bereichen der topographischen Oberflächenstrukturen der zweiten Oberfläche in direktem Kontakt stehen. Sind die topographischen Oberflächenstrukturen der ersten und/oder zweiten Oberfläche durch die Rauigkeit der ersten und/oder zweiten Oberfläche gegeben, so können die erhöhten Bereiche der topographischen Oberflächenstrukturen insbesondere die Rauigkeitsspitzen der ersten Oberfläche und/oder die Rauigkeitsspitzen der zweiten Oberfläche umfassen oder sein, und es kann weiterhin sein, dass Rauigkeitsspitzen der ersten Oberfläche mit Rauigkeitsspitzen der zweiten Oberfläche in direktem Kontakt miteinander stehen.

Bei einer besonders bevorzugten Ausführungsform beträgt die Rauigkeit der ersten Oberfläche und/oder der zweiten Oberfläche zumindest innerhalb des Fügebereichs mindestens einige Nanometer.

Bei einer weiteren Ausführungsform sind die erste Oberfläche und die zweite Oberfläche zumindest teilweise elektrisch leitend ausgebildet. Insbesondere kann bevorzugt zumindest ein Teil des Fügebereichs elektrisch leitend ausgebildet sein. Weiterhin können insbesondere auch zumindest Teilbereiche der topographischen Oberflächenstrukturen elektrisch leitend ausgebildet sein.

Eine elektrisch leitend ausgebildete erste Oberfläche und/oder zweite Oberfläche ist/sind beispielsweise metallisch. Die erste und/oder zweite Oberfläche kann/können, damit sie elektrisch leitend ausgebildet ist/sind, aber auch ein leitfähiges transparentes Oxid (TCO) aufweisen oder aus diesem bestehen.

Bei einer weiteren Ausführungsform ist der elektrisch isolierende Klebstoff, der die Verbindungsschicht bildet, lösungsmittelbeständig gegen Lösungsmittel wie beispielsweise N-Methyl-Pyrrolidon (NMP), beispielsweise 1-Methyl-2-Pyrrolidinon, Aceton, Isopropanol, Ethanol und/oder Methanol. Weiterhin kann eine Laugen- beziehungsweise Säurebeständigkeit gegenüber Kaliumhydroxid (KOH), Natriumhydroxid (NaOH) und/oder Phosphorsäure vorteilhaft sein.

Weiterhin kann der elektrisch isolierende Klebstoff bevorzugt vakuumtauglich hinsichtlich eines typischen Prozessvakuum zwischen 0,1 Millibar und einigen hundert Millibar, vorzugsweise etwa 100 Millibar, sein und/oder temperaturstabil bei Temperaturen von über 200°C. Solche Merkmale können in der Regel vorteilhaft hinsichtlich der Anforderungen bei den folgenden Prozessschritten und/oder der

späteren Verwendung der Bauteile sein. Insbesondere sollte die anzuwendende Verbindungstechnik kompatibel mit den gängigen Prozessschritten und Chemikalien sein, die in der Herstellungskette der Vorrichtung ihre Anwendung finden. Daneben sollten durch die Verbindungsschicht keine nachteiligen Einflüsse auf die Funktionsweise der Vorrichtung oder der einzelnen Bauteile entstehen. Insbesondere kann es vorteilhaft sein, wenn keine nachteiligen Effekte durch Ausgasungen von Lösungsmitteln, Weichmachern oder anderen Komponenten hervorgerufen werden.

Bei einer weiteren Ausführungsform ist der elektrisch isolierende Klebstoff UV-aushärtbar. Dies kann vorteilhaft sein, wenn die Verbindungsschicht von mindestens einer Seite optisch zugänglich ist, so zum Beispiel wenn ein Bauteil transparent ist, so dass die Verbindungsschicht von der Seite des transparenten Bauteils her mit UV-Licht beleuchtet werden kann.

Bei einer besonders bevorzugten Ausführungsform umfasst der elektrisch isolierende Klebstoff Bisbenzocyclobuten (BCB) oder besteht aus BCB. Verarbeitungseigenschaften von BCB sind in der Druckschrift T. Takahashi, Proc. 3rd Japan International SAMPE Symposium (1993), pp. 826-833 beschrieben, deren Offenbarungsgehalt diesbezüglich durch Rückbezug aufgenommen wird. BCB bietet den Vorteil, dass es ohne die Erzeugung von Nebenprodukten wie zum Beispiel Wasser aushärtet und daher eine nur sehr geringe Schrumpfung aufweist.

Ein Verfahren zur Herstellung einer elektrisch leitfähigen Verbindung zwischen einem ersten Bauteil mit einer ersten Oberfläche und einem zweiten Bauteil mit einer zweiten

Oberfläche wobei zumindest eine der ersten und zweiten Oberfläche topographische Oberflächenstrukturen aufweist, umfasst in einer Ausführungsform die Schritte:

- Aufbringen einer elektrisch isolierenden Verbindungs-schicht auf die erste und/oder zweite Oberfläche,

- Positionieren der ersten Oberfläche und der zweiten Oberfläche (9) zueinander, und

- Beaufschlagen des ersten Bauteils (5) und/oder des zweiten Bauteils (8) mit einer Kraft (10) solange bis ein elektrisch leitender Kontakt zwischen der ersten und zweiten Oberfläche über die topographischen Oberflächenstrukturen zustande kommt.

Bei einer Ausführungsform des Verfahrens weisen die erste Oberfläche und die zweite Oberfläche topographische Strukturen auf.

Bei einer weiteren Ausführungsform des Verfahrens werden topographische Strukturen durch Verfahren wie beispielsweise Ätzen oder Schleifen erzeugt.

Bei einer weiteren Ausführungsform des Verfahrens wird die Herstellung der Vertiefungen auf zumindest einer der zu verbindenden ersten und zweiten Oberfläche durch abtragende Strukturierungsverfahren, wie beispielsweise Ätzen oder Schleifen, und/oder durch verformende Strukturierungsverfahren, wie beispielsweise Prägen, vorgenommen. Dabei können verschiedene Vertiefungen auf einem Bauteil oder auf beiden Bauteilen durch verschiedene Verfahren hergestellt werden.

Bei einer weiteren Ausführungsform des Verfahrens wird die elektrisch isolierende Verbindungsschicht, etwa ein

elektrisch isolierender Klebstoff, strukturiert aufgetragen. Dies kann beispielsweise durch Druckverfahren wie etwa Tintenstrahldruck oder Siebdruck erfolgen. Dabei kann es vorteilhaft sein, wenn eine Verbindungsschicht mit einer Dicke von mindestens etwa 10 µm durch Siebdruck, eine Verbindungsschicht von weniger als etwa 10 µm durch Tintenstrahldruck aufgetragen wird. Weiterhin können beispielsweise Stempelverfahren genutzt werden.

Alternativ kann die elektrisch isolierende Verbindungsschicht, etwa ein elektrisch isolierender Klebstoff, auch unstrukturiert, beispielsweise durch Spin-Coating oder durch Abscheidung aus der Dampfphase, aufgetragen werden. Bei einer weiteren Ausführungsform wird die unstrukturiert aufgetragene Verbindungsschicht nach dem Auftragen strukturiert. Eine Strukturierung kann beispielsweise dadurch möglich sein, dass zumindest Teilbereiche zumindest einer Oberfläche oder zumindest von Bereichen davon unterschiedliche Benetzungseigenschaften hinsichtlich der Verbindungsschicht aufweisen. Unterschiedliche Benetzungseigenschaften können etwa durch eine Modifikation von Teilbereichen zumindest einer Oberfläche oder zumindest von Bereichen davon erreicht werden. Alternativ oder zusätzlich kann es vorteilhaft sein, wenn die Verbindungsschicht beispielsweise durch Licht strukturierbar ist. Eine Belichtung kann beispielsweise durch eine Photomaske erfolgen. Alternativ kann es auch möglich sein, eine Verbindungsschicht durch trocken- oder nasschemisches Ätzen mithilfe einer Lackmaske zu strukturieren.

Bei einer zweckmäßigen Ausführungsform weist die Verbindungsschicht nach dem Auftragen eine Dicke zwischen 10

nm und 100  $\mu\text{m}$  auf. Es kann weiterhin vorteilhaft sein, wenn die Verbindungsschicht nach dem Auftragen eine Dicke zwischen 100 nm und 10  $\mu\text{m}$  aufweist. Besonders vorteilhaft kann es sein, wenn die Verbindungsschicht nach dem Auftragen eine Dicke zwischen 500 nm und 5  $\mu\text{m}$  aufweist. Die Dicke der Verbindungsschicht nach dem Auftragen kann dabei von der Viskosität und/oder der Strukturierung der Verbindungsschicht und/oder von der Rauigkeit der ersten und/oder der zweiten Oberfläche abhängen.

Bei einer besonders bevorzugten Ausführungsform des Verfahrens wird die Dicke der Verbindungsschicht durch Beaufschlagen mit einer Kraft auf zumindest ein Bauteil oder auf beide Bauteile so reduziert, dass nach dem Beaufschlagen die Dicke der Verbindungsschicht in der Größenordnung der Rauigkeit oder der Rautiefe der ersten und/oder der zweiten Oberfläche ist. Dies bedeutet insbesondere, dass sich nach dem Beaufschlagen mit einer Kraft die Dicke der Verbindungsschicht so weit reduziert hat, dass sich zumindest die Rauigkeitsspitzen der zu verbindenden Oberflächen berühren.

Bei einer Ausführungsform des Verfahrens wird eine Kraft in einem Bereich von 1 bis 40 kN auf eine Fläche von 20 bis 78  $\text{cm}^2$  beaufschlagt.

Weitere Vorteile und vorteilhafte Ausführungsformen und Weiterbildungen der Erfindung ergeben sich aus den im folgenden in Verbindung mit den Figuren beschriebenen Ausführungsbeispielen.

Es zeigen:

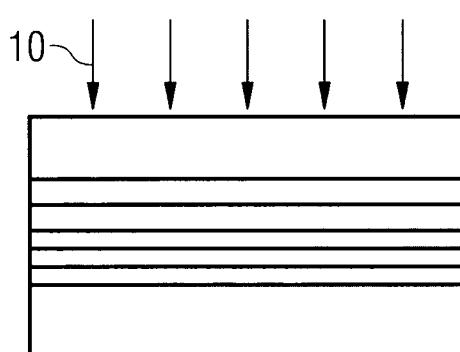

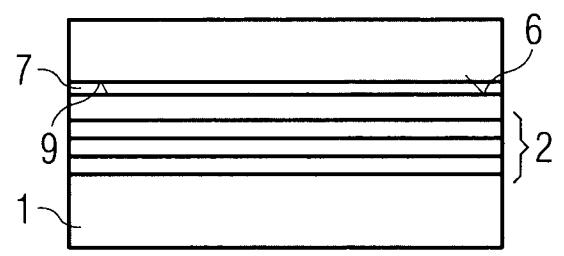

Figuren 1A bis 1F, schematische Schnittdarstellungen einer Vorrichtung bei verschiedenen Stadien des erfindungsgemäßen Verfahrens,

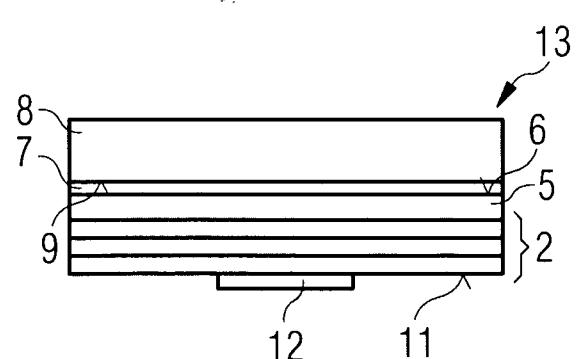

Figur 2, eine schematische Schnittdarstellung eines Ausschnitts einer Vorrichtung gemäß einem ersten Ausführungsbeispiel,

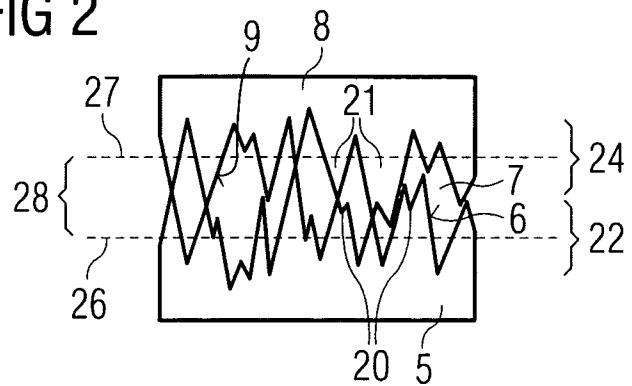

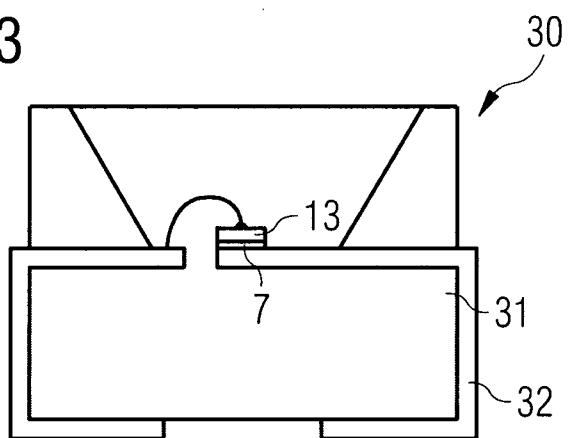

Figur 3, eine schematische Schnittdarstellung einer Vorrichtung gemäß einem zweiten Ausführungsbeispiel,

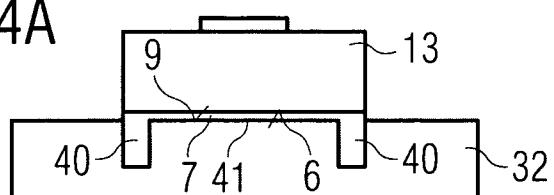

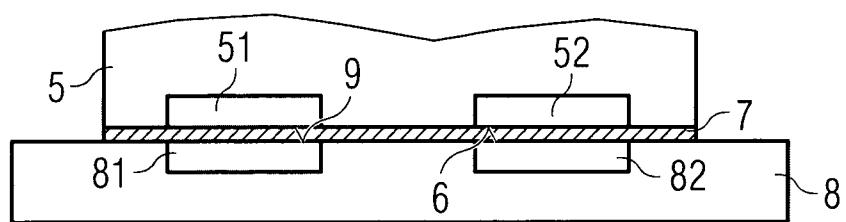

Figur 4a, eine schematische Schnittdarstellung einer Vorrichtung gemäß einem dritten Ausführungsbeispiel,

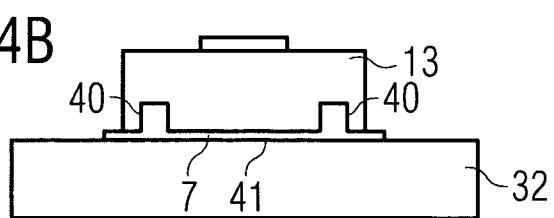

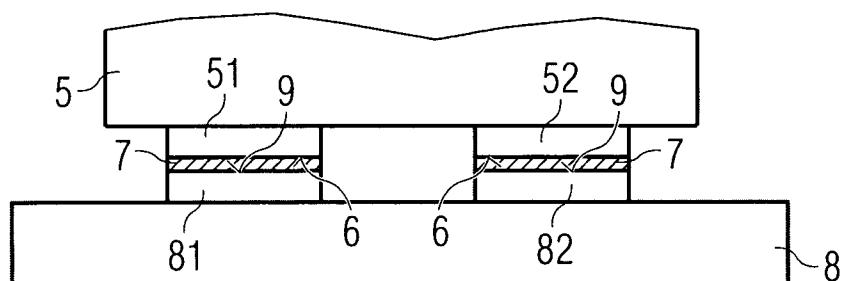

Figur 4b, eine schematische Schnittdarstellung einer Vorrichtung gemäß einem vierten Ausführungsbeispiel,

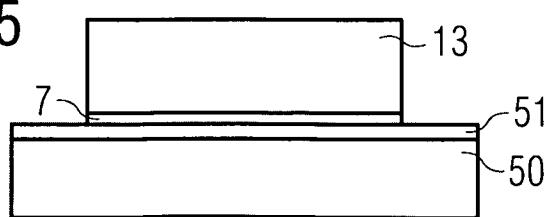

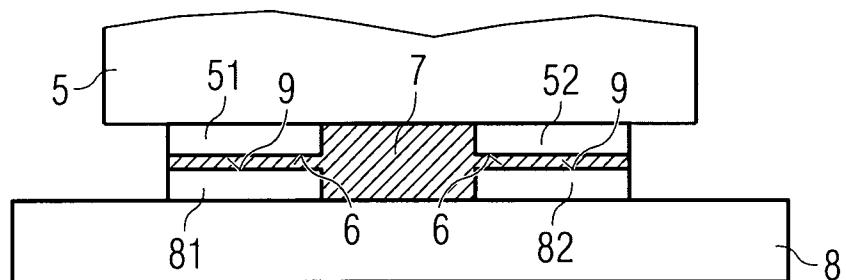

Figur 5, eine schematische Schnittdarstellung einer Vorrichtung gemäß einem fünften Ausführungsbeispiel und

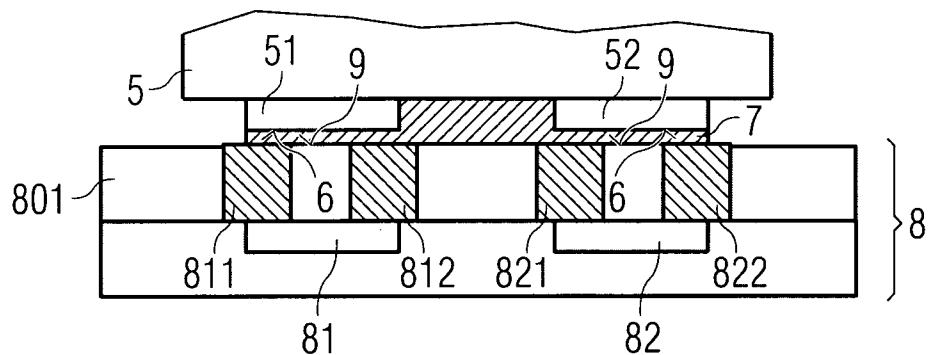

Figuren 6A bis 6E, schematische Schnittdarstellungen weiterer Vorrichtungen gemäß weiterer Ausführungsbeispiele.

In den Ausführungsbeispielen und Figuren sind gleiche oder gleich wirkende Bestandteile jeweils mit den gleichen Bezugszeichen versehen. Die dargestellten Elemente und deren Größenverhältnisse untereinander sind grundsätzlich nicht als maßstabsgerecht anzusehen, vielmehr können einzelne Elemente wie zum Beispiel Schichtdicken oder Rauhigkeiten zur besseren Darstellbarkeit und/oder zum besseren Verständnis übertrieben groß dargestellt sein.

Bei dem Ausführungsbeispiel gemäß der Figuren 1A bis 1F wird innerhalb der Prozessfolge zur Herstellung eines Dünnfilm-Halbleiterchips eine Epitaxieschichtenfolge als ein erstes Bauteil mit einem Trägerwafer als ein zweites Bauteil mittels einer Verbindungsschicht verbunden.

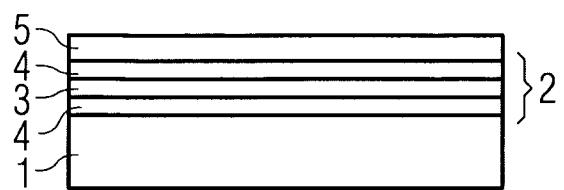

Zur Herstellung von strahlungsemittierenden Dünnfilm-Halbleiterchips gemäß Figur 1A wird auf einem geeigneten Wachstumssubstrat 1, etwa einem SiC-Substrat oder einem Saphir-Substrat, eine Epitaxieschichtenfolge 2 epitaktisch gewachsen. Die Epitaxieschichtenfolge umfasst eine aktive Zone 3, in der im Betrieb Strahlung erzeugt wird, und weitere funktionelle Schichten 4. Zur Strahlungserzeugung weist die aktive Zone 3 zum Beispiel einen pn-Übergang, eine Doppelheterostruktur, einen Einfach-Quantentopf oder einen Mehrfach-Quantentopf (MQW) auf. Die Bezeichnung Quantentopfstruktur beinhaltet hierbei keine Angabe über die Dimensionalität der Quantisierung. Sie umfasst somit u.a. Quantentröge, Quantendrähte und Quantenpunkte und jede Kombination dieser Strukturen. Beispiele für MQW-Strukturen sind in den Druckschriften WO 01/39282, US 5,831,277, US 6,172,382 B1 und US 5,684,309 beschrieben, deren Offenbarungsgehalt insofern hiermit durch Rückbezug aufgenommen wird.

Weiterhin wird auf die von dem Wachstumssubstrat 1 abgewandte Seite der Epitaxieschichtenfolge 2 eine reflektierende Schicht 5 aufgebracht, die in der aktiven Zone 3 erzeugte Strahlung, die auf der vom Wachstumssubstrat 1 abgewandten Seite aus der Epitaxieschichtenfolge 2 austreten würde, wieder in die Epitaxieschichtenfolge 2 zurückreflektiert. Die reflektierende Schicht 5 weist dabei Au, Al oder Ag oder eine Legierung aus diesen Metallen auf und kann als Einzelschicht

oder als Schichtenfolge mit Schichten aus anderen Materialien vorliegen. Die Gesamtdicke einer Epitaxieschichtenfolge 2 eines herkömmlichen Dünnfilm-Halbleiterchips liegt im Bereich von einigen Mikrometern bis einigen zehn Mikrometern.

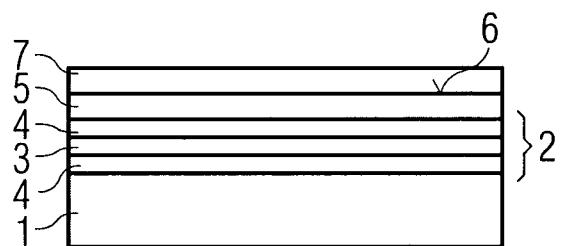

In einem weiteren Schritt gemäß Figur 1B wird auf der dem Wachstumssubstrat 1 abgewandten Seite 6 der reflektierenden Schicht 5, die vorliegend als erste Oberfläche des ersten Bauteils dient, eine Verbindungsschicht 7 aufgebracht. Dabei kann eine Mikroprismenstrukturierung auf der dem Wachstumssubstrat 1 abgewandten Seite 6 der reflektierenden Schicht 5, wie in der Druckschrift WO 02/13281A1 beschrieben, deren Offenbarungsgehalt insofern hiermit durch Rückbezug aufgenommen wird, vorteilhaft als Vorstrukturierung genutzt werden. Ausnehmungen für Mikroprismen können beispielsweise in eine Halbleiterschicht geätzt werden, über der dann eine reflektierende Schicht 5 abgeschieden werden kann. Um eine Kontaktierung der Epitaxieschichtenfolge 2 durch die reflektierende Schicht 5 zu ermöglichen, ist die reflektierende Schicht 5 vorzugsweise aus einem elektrisch leitenden Material ausgebildet. Da nach dem Verbindungsschritt zahlreiche weitere Prozessschritte erfolgen, wird ein Verbindungsmedium benötigt, das unter anderem lösungsmittelbeständig, vakuumtauglich und/oder temperaturstabil ist und zudem mit allen weiteren Prozess- und Arbeitsschritten verträglich ist. Ein geeignetes Material für die Verbindungsschicht 7 ist beispielsweise BCB (Bisbenzocyclobutene, das beispielsweise unter dem Markennamen Cyclotene 3022-xx bei der Firma Dow Corning erhältlich ist, wobei „xx“ den Anteil an vorpolymerisierten BCB-Monomeren im Lösungsmittel Mesitylen angibt), das vorteilhafterweise wie Fotolack mit gut reproduzierbaren Dicken im Bereich von 0,5 bis zehn Mikrometer aufschleuderbar ist und auf den zu

verbindenden Oberflächen in der Regel gut haftet. Als vorteilhaft kann sich die Verwendung von Cyclotene 3022-35 oder Cyclotene 3022-46 erweisen, mit dem beispielsweise beim Auftragen Schichtdicken von etwa 1,0 bis etwa 2,3  $\mu\text{m}$  beziehungsweise von etwa 2,4 bis etwa 5,5  $\mu\text{m}$  erreicht werden können.

Nach dem Auftragen lässt sich der BCB-Film gegebenenfalls durch reaktives Ionenätzen unter Verwendung einer Titanmaske strukturieren.

Alternativ kann sich auch die Verwendung von Cyclotene 4022-xx, beispielsweise mit xx=35 oder xx=46, erweisen, das photostrukturierbar ist. Es können damit beispielsweise beim Auftragen Schichtdicken von etwa 2,6 bis etwa 5,2  $\mu\text{m}$  beziehungsweise von etwa 7,3 bis etwa 14,2  $\mu\text{m}$  erreicht werden.

Alternativ oder zusätzlich wird die Verbindungsschicht 7 auch auf ein mit der Epitaxieschichtenfolge 2 zu verbindendes Trägersubstrat 8 aufgebracht.

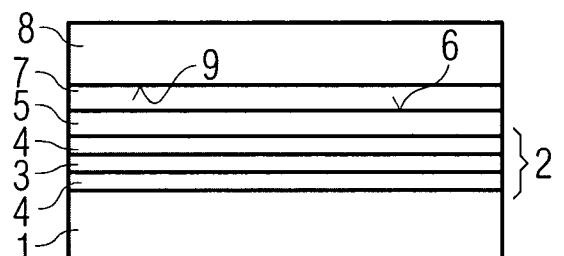

In einem weiteren Herstellungsschritt gemäß Figur 1C wird ein Trägersubstrat 8 als zweites Bauteil mit einer zweiten Oberfläche 9 in einer gewünschten Position relativ zu der Epitaxieschichtenfolge 2 auf der Verbindungsschicht 7 positioniert. Geeignete Materialien für das Trägersubstrat 8 sind elektrisch leitend wie etwa Silizium oder Metall, oder elektrisch isolierend mit einer elektrisch leitenden Oberfläche. Dadurch kann in den weiteren Verfahrensschritten eine einfache elektrische Kontaktierung der Epitaxieschichtenfolge 2 durch das Trägersubstrat 8 erfolgen.

In einem weiteren Herstellungsschritt gemäß Figur 1D wird eine Kraft 10 im wesentlichen senkrecht zu den zu verbindenden Oberflächen 6, 9 der die Epitaxieschichtenfolge 2 abschließenden reflektierende Schicht 5 und des Trägersubstrats 8 beaufschlagt. Dadurch verringert sich die Dicke der Verbindungsschicht 7 soweit, dass gemäß dem Ausführungsbeispiel in Figur 2 ein elektrisch leitender Kontakt durch die Berührung von topographischen Oberflächenstrukturen der Oberflächen 6, 9 der die Epitaxieschichtenfolge 2 abschließenden reflektierende Schicht 5 und des Trägersubstrats 8 hergestellt wird. Die topographischen Oberflächenstrukturen der Oberflächen 6, 9 können dabei vorteilhafte Rauigkeitsspitzen 20, 21 sein, wie im Ausführungsbeispiel der Figur 2 gezeigt.

Die so an Dicke verringerte Verbindungsschicht 7 gemäß Figur 1E wird unter mäßigem Druck durch einen in weiten Grenzen frei wählbaren Temperaturbereich ausgehärtet. Geeignet kann sich dabei eine Kraft von etwa 1 bis etwa 40 kN auf eine Fläche von etwa 20 bis etwa 78 cm<sup>2</sup> erweisen.

BCB kann beispielsweise bei Temperaturen im Bereich von etwa 150 bis etwa 200°C ausgehärtet werden. Besonders vorteilhaft kann sich dabei ein Aushärten bei einer Temperatur von etwa 150°C während etwa 12 Stunden oder bei einer Temperatur von etwa 200°C während etwa 0,5 Stunden erweisen. Weiterhin kann es vorteilhaft sein, bei einer geringeren Temperatur, beispielsweise etwa 150°C während etwa 3 Minuten, vorzuhärten und bei einer höheren Temperatur, beispielsweise etwa 200°C während etwa 2 Minuten, nachzuhärten.

Durch die gute Prozessverträglichkeit hinsichtlich mechanischer Belastbarkeit und Temperaturbeständigkeit der

Verbindungsschicht 7 kann die Vorrichtung weiterverarbeitet werden. Eine gute Prozessverträglichkeit kann sich insbesondere dadurch zeigen, dass durch die Verbindungsschicht weitere Prozessschritte nicht eingeschränkt werden oder nachteilig beeinflusst werden. Beispielsweise kann es durch die Verbindungsschicht möglich sein, dass durch die Abwesenheit von Ausgasungen, die für nachfolgende Prozessschritte im Vakuum nachteilig sein können, durch die Beständigkeit gegenüber Ätzprozessen und durch die Verträglichkeit der Verbindungsschicht mit Temperaturen nachfolgender Prozessschritte kein nachteiliger Effekt auf einen Prozess zur Herstellung beispielsweise eines Halbleiterchips mit einer erfindungsgemäßen Verbindungsschicht entsteht.

Das Wachstumssubstrat 1 wird beispielsweise durch Schleifen gedünnt oder ganz entfernt. Auf der dem Trägersubstrat 8 abgewandten Oberfläche 11 der Epitaxieschichtenfolge 2 wird in einem weiteren Verfahrensschritt ein Bond-Pad 12 zur Kontaktierung der Epitaxieschichtenfolge 2 aufgebracht (siehe Figur 1F). Eine elektrische Kontaktierung des so erhältlichen Halbleiterchips 13 kann durch elektrische Zuführungen ermöglicht werden, die das Trägersubstrat 8 und den Bond-Pad 12 kontaktieren. Die Anordnung des Halbleiterchips 13 auf geeigneten Trägersubstraten wie etwa Leiterrahmen ist in den Ausführungsbeispielen der Figuren 3 bis 5 gezeigt.

Das dargestellte Verfahren kann zur großflächigen Verbindung eines Vierzoll-Epitaxiewafers, der auf einem Aufwachssubstrat die Epitaxieschichtenfolge aufweist, mit einem Trägerwafer genutzt werden.

Durch das in den Figuren 1A bis 1F dargestellte Verfahren und eine Strukturierung der Epitaxieschichtenfolge können beispielsweise auf einem Vierzoll-Trägerwafer in der Regel etwa 50000 Dünnfilm-Halbleiterchips hergestellt werden, deren elektrische Kontaktierung durch den Trägerwafer für jeden Dünnfilm-Halbleiterchip überprüft und verifiziert werden kann.

Es konnte weiterhin durch eine Abschätzung festgestellt werden, dass beispielsweise ein durch ein erfindungsgemäßes Verfahren herstellter Chip mit einer Verbindungsschichtfläche von etwa  $90000 \mu\text{m}^2$  Kontaktstellenfläche von mindestens etwa  $700 \mu\text{m}^2$  aufwies.

Die elektrischen Übergangswiderstände zwischen dem Trägerwafer und den Dünnfilm-Halbleiterchips sind gegenüber den sonst üblichen Lötverbindungen nicht erhöht.

Erfolgt eine elektrische Kontaktierung des Halbleiterchips 13 nicht wie in dem Ausführungsbeispiel gemäß Figur 1F über das Trägersubstrat 8 auf der dem Trägersubstrat 8 zugewandten Seite 6 der reflektierenden Schicht 5 sowie über den Bond-Pad 12 auf der dem Trägersubstrat 8 abgewandte Seite 11 der Epitaxieschichtenfolge 2, sondern über strukturierte elektrische Kontakte auf nur einer Seite der Epitaxieschichtenfolge 2, so erfolgt eine elektrische Kontaktierung der strukturierten elektrischen Kontakte mit strukturierten elektrischen Zuführungen beispielsweise auf einem strukturierten Leiterband mittels einer Verbindungsschicht 7 aus elektrisch isolierendem Klebstoff. Eine solche so genannte Flip-Chip-Montage ist in der Druckschrift EP 0905797 A2 beschrieben, deren Offenbarungsgehalt hiermit insofern durch Rückbezug aufgenommen wird. Dabei wird der zu montierende und zu

kontakterende Dünnschicht-Halbleiterchip 13 mit reflektierend ausgeführten Kontakten 5 auf die elektrischen Zuführungen, beispielsweise auf dem Leiterband, aufgesetzt, wobei durch eine Strukturierung der reflektierend ausgeführten Kontakte 5 geeignete als Aufnahmegräben wirkende Vertiefungen 40 bereitgestellt werden. Als erfindungsgemäße Verbindungsschicht 7 wird elektrisch isolierender Klebstoff verwendet, der den Vorteil bietet, dass Kurzschlüsse durch Schwankungen im Montageprozess grundsätzlich vermieden werden. Es kann beispielsweise möglich sein, dass durch zu viel aufgetragenen Klebstoff, der die Seitenflächen eines Halbleiterchips, also die Chipflanken, bedecken kann, kein Kurzschluss der Epitaxieschichtenfolge hervorgerufen wird.

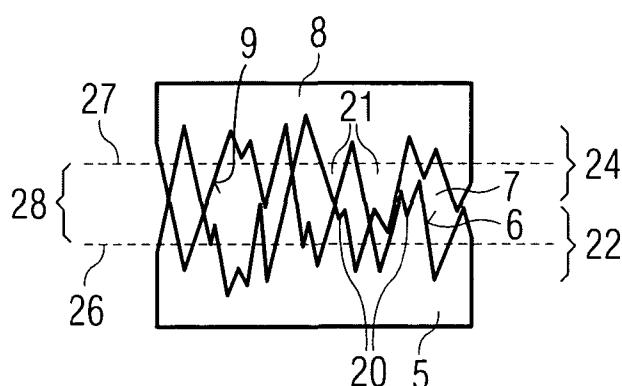

Bei dem Ausführungsbeispiel gemäß der Figur 2 ist ein Ausschnitt einer erfindungsgemäßen Vorrichtung gezeigt. Dabei weisen eine erste Oberfläche 6 eines ersten Bauteils 5 und eine zweite Oberfläche 9 eines zweiten Bauteils 8 jeweils topographische Oberflächenstrukturen 22, 24 auf, die in einer Messung, zum Beispiel mittels Rasterkraftmikroskopie, als Höhenprofil ermittelt werden können. Für die Oberflächen 6, 9 der Bauteile 5, 8 kann eine mittlere Höhenlinie 26 der Oberfläche 22 und eine mittlere Höhenlinie 27 der Oberfläche 24 angegeben werden. Der Abstand der mittleren Höhenlinien 26 und 27 definiert die Dicke 28 der Verbindungsschicht 7. Die Oberflächenstrukturen 22, 24 weisen im gezeigten Ausführungsbeispiel Erhebungen 20, 21 wie etwa Rauhigkeitsspitzen auf, zwischen denen sich Vertiefungen befinden können. Wie gezeigt können die Erhebungen unregelmäßig angeordnet sein, wie etwa bei einem unstrukturierten Rauhigkeitsprofil. Alternativ (nicht gezeigt) können die Erhebungen auch zumindest in Teilbereichen regelmäßig angeordnet sein.

Das erste Bauteil 5 kann beispielsweise die Epitaxieschichtenfolge mit der reflektierenden Schicht aus dem Ausführungsbeispiel 1A sein, wobei die erste Oberfläche die der Epitaxieschichtenfolge abgewandte Seite der reflektierenden Schicht ist, und das zweite Bauteil 8 kann das Trägersubstrat sein. Alternativ kann das erste Bauteil 5 beispielsweise auch ein Halbleiterchip 13 wie etwa ein Dünnfilm-Halbleiterchip gemäß einem der folgenden Ausführungsbeispiele sein, wobei die erste Oberfläche 6 die der Epitaxieschichtenfolge abgewandte Seite des Trägersubstrats sein kann, und das zweite Bauteil 8 kann der Leiterrahmen eines Gehäuses eines oberflächenmontierbaren Bauelements oder eine anderes geeignetes Substrat für den Halbleiterchip 13, wie beispielsweise in den folgenden Figuren gezeigt, sein.

Durch die Kraftbeaufschlagung 10 werden die Bauteile 5, 8 einander so weit genähert, bis sich die Erhebungen 20, 21 der topographischen Oberflächenstrukturen der beiden Oberflächen 6, 9 berühren. Über diese sich berührenden Erhebungen 20, 21 wird ein elektrisch leitender Kontakt zwischen den Oberflächen 6, 9 der beiden Bauteile 5, 8 hergestellt. Der elektrische Kontaktwiderstand ist umso kleiner, je mehr Kontaktstellen hergestellt werden. Die Dicke 28 der Verbindungsschicht kann dabei in etwa dem Höhenprofil der topographischen Oberflächenstrukturen 22, 24, beispielsweise also der Rauhigkeit der Oberflächen 6, 9, entsprechen.

Die Verbindungsschicht 7 kann bei ausgebildetem elektrischem Kontakt zwischen den Bauteilen 5, 8 so ausgeformt sein, dass sich das elektrisch isolierende Verbindungsmedium, das die Verbindungsschicht ausbildet, zwischen den Erhebungen 20, 21

befindet. Dadurch kann ein stoffschlüssiger Kontakt zwischen den Bauteilen 5, 8 gewährleistet werden.

Bei dem Ausführungsbeispiel gemäß der Figur 3 handelt es sich um die Montage eines Halbleiterchips 13, wie zum Beispiel eines nach dem Verfahren 1A bis 1F hergestellten Dünnfilm-Halbleiterchips, der in einem oberflächenmontierbaren Bauelement 30 angebracht wird. Das oberflächenmontierbare Bauelement 30 weist ein Gehäuse 31 auf, beispielsweise aus Kunststoff, und einen Leiterrahmen 32, der eine Montage und eine elektrische Kontaktierung des oberflächenmontierbaren Bauelements 30 zum Beispiel auf einer Leiterplatte ermöglicht. Der Halbleiterchip 13 wird mit einer Seite, im Falle des Dünnfilm-Halbleiterchips gemäß des Ausführungsbeispiels 1F mit der der Epitaxieschichtenfolge 2 abgewandten Seite des Trägersubstrats 8 an dem Leiterrahmen 32 innerhalb des Gehäuses 31 mittels einer Verbindungsschicht 7 aus einem elektrisch isolierenden Klebstoff angebracht und an den Leiterrahmen 32 elektrisch und thermisch angekoppelt. Dabei dient der Leiterrahmen 32 nicht nur als elektrische Zuführung sondern auch als Wärmesenke, um die im Halbleiterchip 13 entstehende Wärme abzuleiten. Durch die Verwendung einer besonders dünnen elektrisch isolierenden Verbindungsschicht 7 ohne die für einen elektrisch leitenden Klebstoff typische Metallfüllung kann die Wärme besonders gut abgeführt werden.

Vorteilweise können Verbindungsschichten aus BCB wie im Zusammenhang mit dem Verfahren gemäß dem Ausführungsbeispiel der Figuren 1A bis 1F mit ähnlichen Verarbeitungsparametern verwendet werden. Das Anheften, also beispielsweise das Aufsetzen eines Halbleiterchips 13 auf einen Leiterrahmen 32,

kann zeitlich und räumlich getrennt vom Aushärten der Verbindungsschicht 7 erfolgen.

Bei dem Ausführungsbeispiel gemäß Figur 4A ist ein Halbleiterchip 13 gezeigt, der auf einem Leiterrahmen 32 montiert wird, wobei der Leiterrahmen 32, typischerweise ein Metallband, durch Prägen derart verformt wurde, dass er Vertiefungen 40 für den elektrisch isolierenden Klebstoff der Verbindungsschicht 7 aufweist. Beim Aufsetzen des Halbleiterchips 13 auf den Leiterrahmen 32 wird durch die Anpresskraft Druck auf den als Verbindungsschicht 7 aufgebrachten Klebstoff ausgeübt, so dass sich die Dicke der Verbindungsschicht 7 verringert. Überschüssiger Klebstoff aus der Verbindungsschicht 7 wird dabei in die als Auffangreservoirs für Klebstoff dienenden Vertiefungen 40 gedrückt. Die Klebstoffdicke im Fügebereich 41 wird dabei so weit verringert, dass ein elektrisch leitender Kontakt zwischen dem Halbleiterchip 13 und dem Leiterrahmen 32 entsteht. Durch die als Auffangreservoirs dienenden Vertiefungen 40 fällt kein verdrängter, überschüssiger Klebstoff um den zu montierenden Halbleiterchip 13 an, was eine saubere Kontaktierung und Montage des Halbleiterchips 13 auf dem Leiterband 32 ermöglicht.

Bei dem Ausführungsbeispiel gemäß der Figur 4B weist der zu montierende Halbleiterchip 13 gemäß dem Ausführungsbeispiel 1F Vertiefungen 40 auf, die als Auffangreservoirs für Klebstoff dienen. Diese Vertiefungen 40 können entweder durch die Strukturierung der der Epitaxieschichtenfolge 2 abgewandten Seite des Trägersubstrats 8 bereitgestellt werden oder durch die Rauigkeit gegeben sein, die durch das Zusammenwirken eines Schleifprozesses mit einem kristallographischen Ätzangriff entsteht.

Eine Kontaktierung des Halbleiterchips 13 gemäß dem Ausführungsbeispiel der Figur 4A oder des Halbleiterchips 13 gemäß dem Ausführungsbeispiel der Figur 4B kann beispielsweise auf der dem Leiterrahmen abgewandten Seite des Halbleiterchips durch ein Bond-Pad 12 erfolgen. Alternativ können bei einer Flip-Chip-Montage auf der dem Leiterband 32 zugewandten Seite des Halbleiterchips Kontaktierungsmöglichkeit für bei Halbleiterchipseiten vorgesehen sein (nicht gezeigt). Die Anbringung eines Bond-Pads 12 kann dann entfallen.

Bei dem Ausführungsbeispiel gemäß Figur 5 ist ein strahlungsemittierender Halbleiterchip 13 auf einem transparenten Substrat 50 montiert, das mit einer Schicht 51 beschichtet ist, die ein transparentes, elektrisch leitendes Oxid (transparent conductive oxide, kurz „TCO“) aufweist oder aus einem solchen besteht. TCOs sind transparente, elektrisch leitende Materialien, in der Regel Metalloxide, wie beispielsweise Zinkoxid, Zinnoxid, Cadmiumoxid, Titanoxid, Indiumoxid oder Indiumzinnoxid (ITO). Neben binären Metallsauerstoffverbindungen, wie beispielsweise  $ZnO$ ,  $SnO_2$  oder  $In_2O_3$  gehören auch ternäre Metallsauerstoffverbindungen, wie beispielsweise  $Zn_2SnO_4$ ,  $CdSnO_3$ ,  $ZnSnO_3$ ,  $MgIn_2O_4$ ,  $GaInO_3$ ,  $Zn_2In_2O_5$  oder  $In_4Sn_3O_{12}$  oder Mischungen unterschiedlicher transparenter leitender Oxide zu der Gruppe der TCOs. Weiterhin entsprechen die TCOs nicht zwingend einer stöchiometrischen Zusammensetzung und können auch p- oder n-dotiert sein. Der Halbleiterchip 13 ist mittels einer Verbindungsschicht 7 aus einem elektrisch isolierenden Klebstoff, der mit UV-Licht ausgehärtet werden kann, auf dem transparenten Substrat 50 befestigt. Dabei ist der Halbleiterchip 13, der gemäß dem Verfahren des

Ausführungsbeispiels der Figuren 1A bis 1F hergestellt sein kann, so auf dem Substrat angeordnet, dass das Trägersubstrat 8 dem Substrat 50 zugewandt ist. Vorteilhafterweise ist das Trägersubstrat transparent ausgeführt und weist Glas oder ein anderes transparentes Material auf oder ist aus diesem. Dadurch kann vom Halbleiterchip 13 emittierte Strahlung durch das Trägersubstrat 8 des Halbleiterchips 13, durch die Verbindungsschicht 7, die Schicht 51 und das transparente Substrat 50 abgestrahlt werden. Nach dem Aufbringen der Verbindungsschicht 7 und dem Positionieren des Halbleiterchips 13 wird durch Anwenden einer Kraft der Abstand zwischen dem Halbleiterchip und der Schicht 51 soweit verringert, dass wie im Ausführungsbeispiel der Figur 2 gezeigt ein elektrisch leitender Kontakt zwischen dem Halbleiterchip 8 und der Schicht 51 durch das Ausbilden von Berührungs punkten zwischen Erhebungen, etwa Rauhigkeitsspitzen, der topographischen Oberflächenstrukturen beider Bauteile ausgebildet wird. Danach kann der elektrisch isolierende Klebstoff beispielsweise mit UV-Licht ausgehärtet werden, das von der Seite des transparenten Substrats 50 her auf die Verbindungsschicht 7 gestrahlt werden kann. Ein elektrischer Kontakt kann beispielsweise über eine Kontaktstelle, die ein oder mehrere Metalle aufweist oder aus einem oder mehreren Metallen ist, erfolgen. Ein solche Kontaktstelle kann etwa neben dem Halbleiterchip 13, insbesondere mit einem geeigneten Abstand zum Halbleiterchip, auf der Schicht 51 angeordnet sein (nicht gezeigt).

Die dem Substrat 50 abgewandte Seite des Halbleiterchips, die beispielsweise eine Mikroprismenstrukturierung aufweisen kann, kann in ähnlicher Weise kontaktiert werden. Dabei kann zusätzlich auf der dem Substrat 50 abgewandten Seite des Halbleiterchips 13 ein weiteres transparentes Substrat 52

angeordnet sein, das beispielsweise Glas aufweist oder aus Glas ist. Das transparente Substrat 52 kann mit einer elektrisch leitenden Schicht 53, die ein TCO aufweist oder aus einem TCO ist, beschichtet sein. Eine elektrisch leitende Verbindung des Halbleiterchips 13 mit der elektrisch leitenden Schicht 53 kann ebenfalls über eine Verbindungsschicht 7 erfolgen. Weiter kann es durch die Verwendung einer Verbindungsschicht 7 aus einem elektrisch isolierenden Material wie etwa einem elektrisch isolierendem Klebstoff möglich sein, dass die Bereiche 54, die an die Seitenflächen 131, 132 des Halbleiterchips 13 angrenzen, mit dem Verbindungsschichtmaterial gefüllt sind. Durch die Verwendung eines elektrisch isolierenden Verbindungsschichtmaterials kann ein Kurzschluss des Halbleiterchips vermieden werden.

Alternativ kann das Substrat 50 nicht transparent sein und das Substrat 52 transparent sein.

In Figur 6A ist ein Ausführungsbeispiel gezeigt, das ein erstes Bauteil 5 mit zwei elektrischen Kontaktbereichen 51, 52 aufweist. Das erste Bauteil 5, das nur in einem Ausschnitt gezeigt ist, ist dabei als Epitaxieschichtenfolge ausgeführt, die über die elektrischen Kontaktbereiche 51, 52 auf einer Seite elektrisch kontaktiert werden kann. Das erste Bauteil 5 weist dazu eine durchgehende erste Oberfläche 6 auf, die durch die elektrischen Kontaktbereiche 51, 52 elektrisch angeschlossen werden kann. Die elektrischen Kontaktbereiche 51, 52 weisen im gezeigten Ausführungsbeispiel unterschiedliche Polaritäten auf. Alternativ können die elektrischen Kontaktbereiche 51, 52 auch die gleiche elektrische Polarität aufweisen, so dass der elektrische Anschluss des ersten Bauteils nur hinsichtlich einer

Polarität über die strukturierten Kontaktbereiche 51, 52 auf der ersten Oberfläche 6 erfolgen kann. Alternativ kann die erste Oberfläche 6 mehr als zwei elektrische Kontaktbereiche mit gleichen oder verschiedenen Polaritäten aufweisen.

Das erste Bauteil 5 ist auf einem zweiten Bauteil 8 angeordnet, das ein Träger mit zwei elektrischen Kontaktbereichen 81, 82 ist. Der Träger kann dabei als Trägersubstrat oder etwa als Leiterrahmen mit einer zweiten Oberfläche 9 ausgeführt sein, die entsprechend der Anzahl der elektrischen Kontaktbereiche 51, 52 auf der ersten Oberfläche 6 elektrische Kontaktbereiche 81, 82 aufweist. Alternativ kann ein elektrischer Kontaktbereich auf der zweiten Oberfläche 9 auch mehr als einen elektrischen Kontaktbereich auf der zweiten Oberfläche kontaktieren oder umgekehrt (nicht gezeigt).

Die Befestigung und elektrische Kontaktierung des ersten Bauteils 5 auf dem zweiten Bauteil 8 erfolgt mittels der Verbindungsschicht 7, die zwischen den Oberflächen 6 und 9 angeordnet ist. Die Verbindungsschicht 7 ist dabei wie bei den vorangegangenen Ausführungsbeispielen ausgeführt und weist einen elektrisch isolierenden Klebstoff, etwa BCB auf.

Durch die Anordnung der elektrischen Kontaktbereiche 51, 52 über den elektrischen Kontaktbereichen 81, 82 und eine Reduzierung der Dicke der Verbindungsschicht 7 soweit, dass sich die jeweiligen Rauigkeitsspitzen der Oberflächen 6 und 9 berühren können, kann ein elektrischer Kontakt zwischen den elektrischen Kontaktbereichen 51 und 81 beziehungsweise 52 und 82 erreicht werden. Dazu kann die Verbindungsschicht 7 wie im gezeigten Ausführungsbeispiel durchgängig und unstrukturiert sein und sich als durchgehende Schicht über

die elektrischen Kontaktbereiche 51, 52, 81, 82 erstrecken. Dadurch, dass die Verbindungsschicht aus einem elektrisch isolierenden Klebstoff ausgeführt ist, kann eine großflächige stoffschlüssige Befestigung des ersten Bauteils 5 am zweiten Bauteil 8 erreicht werden, ohne dass ein Kurzschluss zwischen den elektrischen Kontaktbereichen 51 und 52 beziehungsweise 81 und 82 entstehen würde.

Im Ausführungsbeispiel der Figur 6B weisen das erste Bauteil 5 und das zweite Bauteil 8 jeweils erhabene elektrische Kontaktbereiche 51, 52 beziehungsweise 81, 82 auf. Das erste Bauteil 5 kann etwa ein Halbleiterchip zur Flip-Chip-Montage sein, der auf einem Träger mit Leiterrahmen 81, 82 als zweites Bauteil 8 aufgebracht ist. Die stoffschlüssige Befestigung und der elektrische Anschluss des ersten Bauteils 5 mit dem zweiten Bauteil 8 erfolgt über Verbindungsschichten 7 in der oben beschriebenen Art und Weise, die zwischen den jeweiligen elektrischen Kontaktbereichen 51 und 81 beziehungsweise 52 und 82 aufgebracht sind.

In Figur 6C ist ein weiteres Ausführungsbeispiel gezeigt, in dem die Verbindungsschicht 7 auch zwischen den elektrischen Kontaktbereichen 51, 52, 81, 82 angeordnet ist, um eine bessere stoffschlüssige Befestigung des ersten Bauteils 5 am zweiten Bauteil 8 zu ermöglichen.

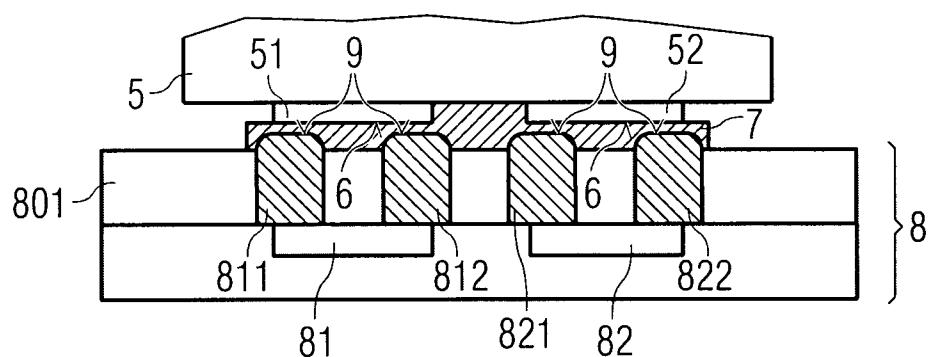

Das Ausführungsbeispiel der Figur 6D zeigt ein zweites Bauteil 8 mit einer zusätzlichen Schicht über den elektrischen Kontaktbereichen 81, 82, die ein isolierendes Material 801, etwa ein Oxid wie  $\text{SiO}_2$ , aufweist, das Metallfüllungen 811, 812, 821, 822 enthält, die jeweils die elektrischen Kontaktbereiche 81 und 82 des zweiten Bauteils 8 kontaktieren. Auf der Schicht mit dem isolierenden Material

801 ist das erste Bauteil 5, etwa eine Epitaxieschichtenfolge mit strukturierten elektrischen Kontaktbereichen 51, 52, angeordnet, die in oben beschriebener Art und Weise mittels einer Verbindungsschicht 7 elektrisch an die Metallfüllungen 811, 812 beziehungsweise 821, 822 angeschlossen sind und damit auch an die elektrischen Kontaktbereiche 81, 82 des zweiten Bauteils 8. Beispielsweise kann das zweite Bauteil 8 als Substrat mit elektrischen Zuleitungen 81, 82 ausgeführt sein, über dem die Schicht mit dem isolierenden Material 801 und den Metallfüllungen 811, 812, 821, 822 angeordnet ist. Alternativ können die Metallfüllungen 811, 812, 821, 822 an den Grenzflächen zum Material 801 von einer Schicht aus einem isolierenden Material umgeben sein, so dass das Material 801 auch elektrisch leitend sein kann.

Im Ausführungsbeispiel der Figur 6E sind die Metallfüllungen 811, 812, 821, 822 über dem Material 801 erhaben, etwa in einer Pilzstruktur, ausgeführt. Der elektrische Kontakt kommt dabei zwischen der zweiten Oberfläche 9 der Metallfüllungen 811, 812, 821, 822 und der ersten Oberfläche 6 der elektrischen Kontaktbereiche 51 und 52 durch eine ausreichende Reduzierung der dicke der Verbindungsschicht 7 zustande.

Durch eine geeignete Verteilung und eine geeignete Dimensionierung, insbesondere den Durchmesser, der Metallfüllungen 811, 812, 821, 822 in den gezeigten Ausführungsbeispielen kann somit eine justagefreie Kontaktierung des ersten Bauteils 5 mit dem zweiten Bauteil 8 erreicht werden. Die Anzahl der Metallfüllungen kann dabei von der gezeigten Anzahl abweichen. Alternativ oder zusätzlich können das erste und/oder das zweite Bauteil Justageelemente wie etwa Führungsteile oder -kanten

aufweisen, so dass die Einschränkungen an die Dimensionierung und die Anordnung der Metallfüllungen entfallen kann.

Die Erfindung ist nicht durch die Beschreibung anhand der Ausführungsbeispiele auf diese beschränkt. Vielmehr umfasst die Erfindung jedes neue Merkmal sowie jede Kombination von Merkmalen, was insbesondere jede Kombination von Merkmalen in den Patentansprüchen beinhaltet, auch wenn dieses Merkmal oder diese Kombination selbst nicht explizit in den Patentansprüchen oder Ausführungsbeispielen angegeben ist.

## Patentansprüche

1. Vorrichtung mit einem ersten Bauteil (5) mit einer ersten Oberfläche (6) und einem zweiten Bauteil (8) mit einer zweiten Oberfläche (9), wobei

- zumindest eine der ersten und zweiten Oberfläche topographische Oberflächenstrukturen aufweist,

- die erste Oberfläche (6) des ersten Bauteils (5) mit der zweiten Oberfläche (9) des zweiten Bauteils (8) über eine elektrisch isolierende Verbindungsschicht (7) verbunden ist und

- ein elektrisch leitender Kontakt zwischen der ersten Oberfläche (6) und der zweiten Oberfläche (9) über die topographischen Oberflächenstrukturen besteht.

2. Vorrichtung nach Anspruch 1, bei der sowohl die erste als auch die zweite Oberfläche topographische Oberflächenstrukturen aufweist.

3. Vorrichtung nach einem der vorherigen Ansprüche, bei der die topographischen Oberflächenstrukturen durch die Rauigkeit der ersten und/oder zweiten Oberfläche bedingt sind.

4. Vorrichtung nach einem der vorherigen Ansprüche, wobei das erste Bauteil (5) und/oder das zweite Bauteil (8) aus der Gruppe gewählt ist, die gebildet wird durch: ein Substrat, einen Wafer, einen Glasträger, eine Wärmesenke, eine Epitaxieschichtenfolge und einen optoelektronischen Halbleiterchip.

5. Vorrichtung nach einem der vorherigen Ansprüche, wobei die erste Oberfläche (6) des ersten Bauteils (5) und/oder die

zweite Oberfläche (9) des zweiten Bauteils (8) Vertiefungen (40) aufweist.

6. Vorrichtung nach dem vorherigen Anspruch, wobei die erste Oberfläche (6) und die zweite Oberfläche (9) einen Fügebereich (41) aufweisen, in dem die Verbindungsschicht (7) angebracht ist und die Vertiefungen (40) in der ersten Oberfläche (6) und/oder zweiten Oberfläche (9) um den Fügebereich (41) angeordnet sind.

7. Vorrichtung nach einem der Ansprüche 5 oder 6, wobei die Vertiefungen (40) als Auffangreservoirs für einen Klebstoff der Verbindungsschicht dienen.

8. Vorrichtung nach einem der Ansprüche 5 bis 7, wobei die Vertiefungen (40) regelmäßig beabstandet angeordnet sind.

9. Vorrichtung nach einem der Ansprüche 5 bis 7, wobei die Vertiefungen (40) unregelmäßig beabstandet angeordnet sind.

10. Vorrichtung nach einem der vorherigen Ansprüche, wobei die mittlere Dicke (28) der Verbindungsschicht (7) in der Größenordnung der Rauhigkeit der ersten Oberfläche (6) und/oder der Rauhigkeit zweiten Oberfläche (9) ist.

11. Vorrichtung nach einem der vorherigen Ansprüche 3 oder 10, wobei die Rauhigkeit der ersten Oberfläche (6) und/oder die Rauhigkeit der zweiten Oberfläche (9) mindestens einige Nanometer beträgt.

12. Vorrichtung nach einem der vorherigen Ansprüche, wobei die erste Oberfläche (6) und die zweite Oberfläche (9) zumindest teilweise elektrisch leitend ausgebildet sind.

13. Vorrichtung nach Anspruch 9, wobei die erste Oberfläche (6) und/oder zweite Oberfläche (9) zumindest teilweise metallisch ausgebildet ist.

14. Vorrichtung nach einem der vorherigen Ansprüche, wobei die Verbindungsschicht einen elektrisch isolierenden Klebstoff umfasst.

15. Vorrichtung nach dem vorherigen Anspruch, wobei der Klebstoff lösungsmittelbeständig, vakuumtauglich, temperaturstabil und/oder UV-aushärtbar ist.

16. Vorrichtung nach Anspruch 14 oder 15, wobei der Klebstoff Bisbenzocyclobuten (BCB) umfasst.

17. Verfahren zur Herstellung einer elektrisch leitfähigen Verbindung zwischen einem ersten Bauteil (5) mit einer ersten Oberfläche (6) und einem zweiten Bauteil (8) mit einer zweiten Oberfläche (9), wobei zumindest eine der ersten und zweiten Oberfläche topographische Oberflächenstrukturen aufweist, mit den Schritten:

- Aufbringen einer elektrisch isolierenden Verbindungs- schicht (7) auf die erste und/oder zweite Oberfläche,

- Positionieren der ersten Oberfläche (6) und der zweiten Oberfläche (9) zueinander, und

- Beaufschlagen des ersten Bauteils (5) und/oder des zweiten Bauteils (8) mit einer Kraft (10) solange bis ein elektrisch leitender Kontakt zwischen der ersten und zweiten Oberfläche über die topographischen Oberflächenstrukturen zustande kommt.

18. Verfahren nach dem vorherigen Anspruch, bei dem die erste Oberfläche (6) und die zweite Oberfläche (9) topographische Strukturen aufweisen.

19. Verfahren nach Anspruch 17 oder 18, bei dem vor dem Aufbringen der Verbindungsschicht die topographischen Oberflächenstrukturen erzeugt werden.

20. Verfahren nach dem vorhergehenden Anspruch, bei dem die topographische Oberflächenstrukturen durch Ätzen, Schleifen, photolithographische Strukturierung und/oder Sandstrahlen erzeugt werden.

21. Verfahren nach einem der Ansprüche 17 bis 20, bei dem ein erstes Bauteil (5) und/oder ein zweites Bauteil (8) verwendet wird, das aus der Gruppe gewählt ist, die gebildet wird durch: ein Substrat, einen Wafer, einen Glasträger, eine Wärmesenke, eine Epitaxieschichtenfolge und einen optoelektronischen Halbleiterchip.

22. Verfahren nach einem der Ansprüche 17 bis 21, bei dem die erste Oberfläche (6) des ersten Bauteils (5) und/oder die zweite Oberfläche (9) des zweiten Bauteils (8) vor dem Aufbringen der elektrisch isolierenden Verbindungsschicht mit Vertiefungen (40) versehen wird.

23. Verfahren nach einem der Ansprüche 17 bis 22, bei dem die erste Oberfläche (6) und die zweite Oberfläche (9) einen Fügebereich (41) aufweisen, in dem die Verbindungsschicht (7) aufgebracht wird, wobei Vertiefungen (40) in der ersten Oberfläche (6) und/oder der zweiten Oberfläche (9) um den Fügebereich (41) angeordnet werden.

24. Verfahren nach einem der Ansprüche 22 oder 23, bei dem die Vertiefungen (40) als Auffangreservoirs für einen Klebstoff der Verbindungsschicht dienen.

25. Verfahren nach einem der Ansprüche 22 bis 24, bei dem die Vertiefungen (40) regelmäßig beabstandet angeordnet werden.

26. Verfahren nach einem der Ansprüche 22 bis 24, bei dem die Vertiefungen (40) unregelmäßig beabstandet angeordnet werden.

27. Verfahren nach einem der Ansprüche 22 bis 26, bei dem die Vertiefungen (40) durch Ätzen, Schleifen, Prägen, photolithographisches Strukturieren und/oder Sandstrahlen hergestellt werden.

28. Verfahren nach Anspruch 17, bei dem die Verbindungsschicht (7) strukturiert aufgetragen wird.

29. Verfahren nach Anspruch 28, bei dem das strukturierte Auftragen durch ein Druckverfahren erfolgt.

30. Verfahren nach Anspruch 17, bei dem die Verbindungsschicht (7) unstrukturiert aufgetragen wird.

31. Verfahren nach Anspruch 30, bei dem das unstrukturierte Auftragen mittels Spin-Coating oder Abscheidung aus der Dampfphase erfolgt.

32. Verfahren nach Anspruch 17, bei dem die Dicke (28) der Verbindungsschicht (7) nach dem Auftragen eine Dicke von 100 nm bis 10 µm umfasst.

- 41 -

33. Verfahren nach Anspruch 32, bei dem die Dicke (28) der Verbindungsschicht (7) nach dem Auftragen durch Beaufschlagen mit einer Kraft (10) so reduziert wird, dass die Dicke (28) der Verbindungsschicht (7) in der Größenordnung der Rauhigkeit der ersten Oberfläche (6) und/oder der Rauhigkeit der zweiten Oberfläche (9) ist.

34. Verfahren nach einem der Ansprüche 17 bis 33, wobei eine elektrisch isolierende Verbindungsschicht verwendet wird, die einen Klebstoff umfasst.

35. Verfahren nach Anspruch 34, wobei ein Klebstoff verwendet wird, der lösungsmittelbeständig, vakuumtauglich, temperaturstabil und/oder UV-aushärtbar ist.

36. Verfahren nach Anspruch 34 oder 35, wobei ein Klebstoff verwendet wird, der Bisbenzocyclobuten (BCB) umfasst.

1/4

FIG 1A

FIG 1B

FIG 1C

FIG 1D

FIG 1E

FIG 1F

2/4

FIG 2

FIG 3

FIG 4A

FIG 4B

FIG 5

FIG 6A

FIG 6B

FIG 6C

FIG 6D

FIG 6E

# INTERNATIONAL SEARCH REPORT

International application No

PCT/DE2007/000897

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H01L21/58

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No.               |

|-----------|------------------------------------------------------------------------------------|-------------------------------------|

| X         | DE 195 29 490 A1 (FRAUNHOFER GES FORSCHUNG [DE]) 13 February 1997 (1997-02-13)     | 1-4,<br>10-21,<br>28-36             |

| Y         | column 3, line 30 – column 6, line 11;<br>figures 1,2<br>-----                     | 5-9,<br>22-27                       |

| X         | JP 60 262430 A (MATSUSHITA ELECTRIC IND CO LTD) 25 December 1985 (1985-12-25)      | 1,2,4,<br>12-21,<br>28-32,<br>34-36 |

| Y         | abstract; figure 1<br>-----                                                        | 5-9,<br>22-27                       |

| A         | -----<br>-----                                                                     | 3,10,11,<br>33                      |

|           |                                                                                    | -/-                                 |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

\*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

\*&\* document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

20 September 2007

01/10/2007

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

Krause, Joachim

## INTERNATIONAL SEARCH REPORT

|                              |

|------------------------------|

| International application No |

| PCT/DE2007/000897            |

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                   | Relevant to claim No.                      |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| X         | US 5 861 678 A (SCHROCK ED A [US])<br>19 January 1999 (1999-01-19)                                                                   | 1,2,4,<br>12-19,<br>21,<br>28-32,<br>34-36 |

| Y         | column 3, line 33 - column 6, line 50;<br>figures 2-5                                                                                | 5-9,<br>22-27                              |

| A         | -----                                                                                                                                | 3,10,11,<br>33                             |

| X         | DE 101 63 799 A1 (MATSUSHITA ELECTRIC<br>WORKS LTD [JP]) 25 July 2002 (2002-07-25)                                                   | 1,2,4,<br>12,13,<br>17-21,<br>30-32        |

| A         | paragraph [0027] - paragraph [0055];<br>figures 1-6                                                                                  | 3,5-11,<br>14-18,<br>22-29,<br>33-36       |

| Y         | US 6 426 565 B1 (BHATT ASHWINKUMAR C [US]<br>ET AL) 30 July 2002 (2002-07-30)                                                        | 5-9,<br>22-27                              |

| A         | column 4, line 36 - column 6, line 43;<br>figures 1,2                                                                                | 1-4,<br>10-21,<br>28-36                    |

| A         | EP 1 143 519 A (LUCENT TECHNOLOGIES INC<br>[US]) 10 October 2001 (2001-10-10)<br>paragraph [0020] - paragraph [0027];<br>figures 4-9 | 1-36                                       |

|           | -----                                                                                                                                |                                            |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/DE2007/000897

| Patent document cited in search report |    | Publication date |                      | Patent family member(s)                               |                                                      | Publication date |

|----------------------------------------|----|------------------|----------------------|-------------------------------------------------------|------------------------------------------------------|------------------|

| DE 19529490                            | A1 | 13-02-1997       | WO<br>US             | 9706557 A1<br>6107118 A                               | 20-02-1997<br>22-08-2000                             |                  |

| JP 60262430                            | A  | 25-12-1985       | JP                   | 1689504 C<br>2007180 B                                | 27-08-1992<br>15-02-1990                             |                  |

| US 5861678                             | A  | 19-01-1999       | US                   | 6221691 B1                                            | 24-04-2001                                           |                  |

| DE 10163799                            | A1 | 25-07-2002       | US                   | 2002121706 A1                                         | 05-09-2002                                           |                  |

| US 6426565                             | B1 | 30-07-2002       | NONE                 |                                                       |                                                      |                  |

| EP 1143519                             | A  | 10-10-2001       | CA<br>CN<br>JP<br>US | 2342726 A1<br>1316657 A<br>2002014264 A<br>6404566 B1 | 03-10-2001<br>10-10-2001<br>18-01-2002<br>11-06-2002 |                  |

# INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/DE2007/000897

**A. KLASSEIFIZIERUNG DES ANMELDUNGSGEGENSTANDES**

INV. H01L21/58

Nach der Internationalen Patentklassifikation (IPC) oder nach der nationalen Klassifikation und der IPC

**B. RECHERCHIERTE GEBIETE**

Recherchierte Mindestprüfstoff (Klassifikationssystem und Klassifikationssymbole )

H01L

Recherchierte, aber nicht zum Mindestprüfstoff gehörende Veröffentlichungen, soweit diese unter die recherchierten Gebiete fallen

Während der internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe)

EPO-Internal, WPI Data

**C. ALS WESENTLICH ANGESEHENE UNTERLAGEN**

| Kategorie* | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile | Betr. Anspruch Nr.                  |

|------------|----------------------------------------------------------------------------------------------------|-------------------------------------|

| X          | DE 195 29 490 A1 (FRAUNHOFER GES FORSCHUNG [DE]) 13. Februar 1997 (1997-02-13)                     | 1-4,<br>10-21,<br>28-36             |

| Y          | Spalte 3, Zeile 30 – Spalte 6, Zeile 11;<br>Abbildungen 1,2                                        | 5-9,<br>22-27                       |

| X          | JP 60 262430 A (MATSUSHITA ELECTRIC IND CO LTD) 25. Dezember 1985 (1985-12-25)                     | 1,2,4,<br>12-21,<br>28-32,<br>34-36 |

| Y          | Zusammenfassung; Abbildung 1                                                                       | 5-9,<br>22-27                       |

| A          | -----                                                                                              | 3,10,11,<br>33                      |

|            | -----                                                                                              | -/-                                 |

Weitere Veröffentlichungen sind der Fortsetzung von Feld C zu entnehmen

Siehe Anhang Patentfamilie

- \* Besondere Kategorien von angegebenen Veröffentlichungen :

- \*A\* Veröffentlichung, die den allgemeinen Stand der Technik definiert, aber nicht als besonders bedeutsam anzusehen ist

- \*E\* älteres Dokument, das jedoch erst am oder nach dem internationalen Anmeldeatum veröffentlicht worden ist

- \*L\* Veröffentlichung, die geeignet ist, einen Prioritätsanspruch zweifelhaft erscheinen zu lassen, oder durch die das Veröffentlichungsdatum einer anderen im Recherchenbericht genannten Veröffentlichung belegt werden soll oder die aus einem anderen besonderen Grund angegeben ist (wie ausgeführt)

- \*O\* Veröffentlichung, die sich auf eine mündliche Offenbarung, eine Benutzung, eine Ausstellung oder andere Maßnahmen bezieht

- \*P\* Veröffentlichung, die vor dem internationalen Anmeldeatum, aber nach dem beanspruchten Prioritätsdatum veröffentlicht worden ist