(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4668892号

(P4668892)

(45) 発行日 平成23年4月13日(2011.4.13)

(24) 登録日 平成23年1月21日(2011.1.21)

(51) Int.Cl.

F 1

|      |        |           |      |           |

|------|--------|-----------|------|-----------|

| GO9G | 3/36   | (2006.01) | GO9G | 3/36      |

| GO2F | 1/1343 | (2006.01) | GO2F | 1/1343    |

| GO2F | 1/1368 | (2006.01) | GO2F | 1/1368    |

| GO2F | 1/133  | (2006.01) | GO2F | 1/133 550 |

| GO9G | 3/20   | (2006.01) | GO2F | 1/133 525 |

請求項の数 6 (全 13 頁) 最終頁に続く

(21) 出願番号

特願2006-347659 (P2006-347659)

(22) 出願日

平成18年12月25日 (2006.12.25)

(65) 公開番号

特開2007-256916 (P2007-256916A)

(43) 公開日

平成19年10月4日 (2007.10.4)

審査請求日

平成19年1月12日 (2007.1.12)

(31) 優先権主張番号

10-2006-0025222

(32) 優先日

平成18年3月20日 (2006.3.20)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者

501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル, ヨンドゥンポーク, ヨ

イドードン 20

(74) 代理人

100094112

弁理士 岡部 譲

(74) 代理人

100064447

弁理士 岡部 正夫

(74) 代理人

100085176

弁理士 加藤 伸晃

(74) 代理人

100096943

弁理士 白井 伸一

(74) 代理人

100101498

弁理士 越智 隆夫

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

垂直及び水平画素列がマトリックス状で定義された液晶パネルと；

前記液晶パネル内で順次に配列された G m、 G m + 1、 G m + 2、 G m + 3 (m は自然数) ゲートラインと；

前記液晶パネル内で前記 G m、 G m + 1、 G m + 2、 G m + 3 ゲートラインと交差するデータラインと；

データ信号、制御信号、電源電圧、クロック、第 1 フリッカーハードウェア、第 2 フリッカーハードウェアを出力するタイミングコントローラと；

前記電源電圧を利用して高電位ゲート電圧を生成し、前記高電位ゲート電圧を前記第 1 フリッカーハードウェアと前記クロックを利用して調節して第 1 及び第 3 調整クロックを出力し、前記高電位ゲート電圧を前記第 2 フリッカーハードウェアと前記クロックを利用して調節して第 2 及び第 4 調整クロックを出力する外部回路と；

前記第 1 乃至第 4 調整クロックを利用して、ゲート信号 V g m、V g m 1、V g m 2、V g m 3 を生成して前記ゲートライン G m、G m + 1、G m 2、G m + 3 それぞれに伝送するゲートドライバと；

前記データ信号及び制御信号を利用して前記データラインに画像信号を伝送するデータドライバとを含み、

前記水平画素列はそれぞれ、前記 G m、G m + 1 ゲートラインそして前記 G m + 2、G m + 3 ゲートライン間に 1 列ずつ配列されて、前記垂直画素列はそれぞれ、前記データ

10

20

インの左右両側に 2 列に配列され、

前記第 1 及び第 2 フリッカー信号は、ハイ期間を 1 周期 (T) として、相互に 1 / 2 周期 (T / 2) 差を有する矩形波であり、

前記ゲート信号  $V_{gm}$ 、 $V_{gm+1}$ 、 $V_{gm+2}$ 、 $V_{gm+3}$  は、それぞれ高電位ゲート電圧と低電位ゲート電圧が順次に繰り返されるパルス形態であり、

前記ゲート信号  $V_{gm}$ 、 $V_{gm+2}$  は、ハイ期間を 1 周期 (T) として、相互に 1 周期 (T) 差を有して、前記ゲート信号  $V_{gm+1}$ 、 $V_{gm+3}$  は相互に 1 周期 (T) 差を有して、前記ゲート信号  $V_{gm}$ 、 $V_{gm+1}$ 、 $V_{gm+2}$ 、 $V_{gm+3}$  は順次に 1 / 2 周期 (T / 2) 差を有し、

前記外部回路は、前記高電位ゲート電圧を生成する PWM ( Pulse Width Modulation ) 部と、前記第 1 フリッカー信号を利用して前記高電位ゲート電圧を調節する第 1 GPM ( Gate Pulse Modulation ) 部と、前記第 2 フリッcker 信号を利用して前記高電位ゲート電圧を調節する第 2 GPM 部とを含み、 10

前記ゲート信号  $V_{gm}$ 、 $V_{gm+2}$  と前記ゲート信号  $V_{gm+1}$ 、 $V_{gm+3}$  は、それぞれ前記高電位ゲート電圧の後段部に前記高電位ゲート電圧より小さくて前記低電位ゲート電圧より高い電圧で構成される調整領域が付与されることを特徴とする液晶表示装置。

#### 【請求項 2】

前記水平画素列は赤 (R)、緑 (G)、青 (B) カラーのサブ画素  $P_{sub}$  が順序通り繰り返されて、前記垂直画素列は同一カラーの前記サブ画素  $P_{sub}$  が配列されることを特徴とする請求項 1 に記載の液晶表示装置。 20

#### 【請求項 3】

前記赤 (R)、緑 (G)、青 (B) カラーのサブ画素  $P_{sub}$  によって画素 P が定義されて、前記画素 P は前記水平画素列それぞれで奇数番目と偶数番目に繰り返し配列されて、

前記奇数番目画素 P の赤 (Ro)、青 (Bo) カラーサブ画素  $P_{sub}$ 、前記偶数番目画素 P の緑 (Ge) カラーサブ画素  $P_{sub}$  は前記 Gm ゲートラインまたは  $Gm + 2$  ゲートラインに接続されて、前記奇数番目画素 P の緑 (Go) カラーサブ画素  $P_{sub}$ 、前記偶数番目画素 P の赤 (Re)、青 (Be) カラーサブ画素  $P_{sub}$  は前記  $Gm + 1$  ゲートラインまたは  $Gm + 3$  ゲートラインに接続されることを特徴とする請求項 2 に記載の液晶表示装置。 30

#### 【請求項 4】

前記奇数番目画素 P の赤 (Ro)、緑 (Go) カラーサブ画素  $P_{sub}$  と、前記奇数番目画素 P の青 (Bo) カラーサブ画素  $P_{sub}$  及び前記偶数番目画素 P の赤 (Re) カラーサブ画素  $P_{sub}$  と、前記偶数番目画素 P の緑 (Ge)、青 (Be) カラーサブ画素  $P_{sub}$  はそれぞれ同じデータラインに接続されることを特徴とする請求項 3 に記載の液晶表示装置。

#### 【請求項 5】

一方向に配列されるゲートライン  $Gm$ 、 $Gm + 1$ 、 $Gm + 2$ 、 $Gm + 3$  と、前記ゲートライン  $Gm$ 、 $Gm + 1$ 、 $Gm + 2$ 、 $Gm + 3$  と交差するデータラインを具備して、垂直及び水平画素列がマトリックス状で定義された液晶表示装置の駆動方法として、 40

高電位ゲート電圧を生成する段階と；

第 1 フリッcker 信号と第 1 及び第 3 調整クロックとを利用して前記高電位ゲート電圧を調節することで生成されるゲート信号  $V_{gm}$ 、 $V_{gm+2}$  を、前記ゲートライン  $Gm$ 、 $Gm + 2$  に伝送する段階と；

第 2 フリッcker 信号と第 2 及び第 4 調整クロックとを利用して前記高電位ゲート電圧を調節することで生成されるゲート信号  $V_{gm+1}$ 、 $V_{gm+3}$  を、前記ゲートライン  $Gm + 1$ 、 $Gm + 3$  に伝送する段階とを含み、

前記水平画素列はそれぞれ、前記  $Gm$ 、 $Gm + 1$  ゲートラインそして前記  $Gm + 2$ 、 $Gm + 3$  ゲートライン間に 1 列ずつ配列されて、前記垂直画素列はそれぞれ、前記データラインの左右両側に 2 列に配列され、 50

前記第1及び第2フリッカー信号は、ハイ期間を1周期(T)として、相互に1/2周期(T/2)差を有する矩形波であり、

前記ゲート信号Vgm、Vgm+1、Vgm+2、Vgm+3は、それぞれ高電位ゲート電圧と低電位ゲート電圧が順次に繰り返されるパルス形態であり、

前記ゲート信号Vgm、Vgm+2は、ハイ期間を1周期(T)として、相互に1周期(T)差を有して、前記ゲート信号Vgm+1、Vgm+3は相互に1周期(T)差を有して、前記ゲート信号Vgm、Vgm+1、Vgm+2、Vgm+3は順次に1/2周期(T/2)差を有し、

前記ゲート信号Vgm、Vgm+2と前記ゲート信号Vgm+1、Vgm+3は、それぞれ前記高電位ゲート電圧の後段部に前記高電位ゲート電圧より小さくて前記低電位ゲート電圧より高い電圧で構成される調整領域が付与されることを特徴とする液晶表示装置の駆動方法。 10

#### 【請求項6】

前記データラインに画像信号を伝送する段階と、

前記ゲートラインGm、Gm+1、Gm+2、Gm+3それに前記ゲート信号Vgm、Vgm+1、Vgm+2、Vgm+3が伝送されている間、前記画像信号を前記ゲートラインGm、Gm+1、Gm+2、Gm+3それに連結されるサブ画素に伝送する段階をさらに含むことを特徴とする請求項5に記載の液晶表示装置の駆動方法。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は液晶表示装置(Liquid Crystal Display device)及びこの画像具現方法に係り、より具体的にはフリッカー信号による調整時に伴うゲート信号歪みによる画質低下現象を防止することができるDGIP(Double pixel Gate In Panel)方式液晶表示装置及びこの画像具現方法に関する。

##### 【背景技術】

##### 【0002】

動画像表示に有利であってコントラスト比(contrast ratio)が大きい特徴を見せてTV、モニター等の分野で最も活発に利用されている液晶表示装置(Liquid Crystal Display device)は液晶の光学的異方性(optical anisotropy)と分極性質(polarization)を利用した画像具現原理を示すので、両基板間に液晶層を介在して対面合着させた液晶パネル(liquid crystal panel)を必須の構成要素にしており、液晶パネル内の電界で液晶分子の配列方向を変化させ、透過率差を発生させて別途のバックライト(back light)を利用して液晶パネルの透過率差を外部に投影させて目的する画像を表示する。 30

##### 【0003】

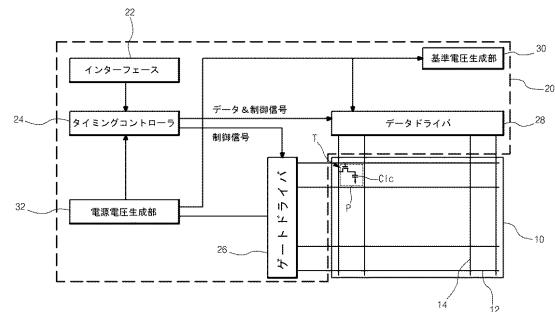

最近には液晶パネル上に画像表現の基本単位である画素をマトリックスで配列して薄膜トランジスタ(TFT)を利用してそれを個別制御するアクティブマトリックス方式(Active Matrix type)が広く利用されるが、添付された図1は一般的な液晶表示装置を示したブロック図である。 40

##### 【0004】

見えるように一般的な液晶表示装置は直接的な画像具現のための液晶パネル10及びこの画像具現に必要な電気的信号を供給する駆動回路部20に区分されることがある。

##### 【0005】

まず、液晶パネル10は液晶層を間に置いて対面合着された第1及び第2基板で構成されて、このうちアレイ基板(array substrate)と呼ばれる第1基板内面には複数のゲートライン12とデータライン14が交差配列され、画素Pが定義されて、これらの交差点毎に薄膜トランジスタTが具備されて各画素Pに実装された画素電極と一 50

対一で対応連結される。

**【0006】**

またカラーフィルタ基板と呼ばれる第2基板内面にはカラー具現のためのカラーフィルタ、一例で各画素に一対一に対応する赤(R)、緑(G)、青(B)カラーフィルタと、液晶層を間に置いて画素電極と対面される共通電極が用意されて、その結果画素電極と共通電極そしてこれら間に介在された液晶層は液晶キャパシタ(C1c)を形成する。

**【0007】**

次に駆動回路部20はインターフェース22と、タイミングコントローラ24と、ゲート及びデータドライバ26、28と、基準電圧生成部30と、電源電圧生成部32等で構成され、このうちインターフェース22はパーソナルコンピューターのような外部駆動システムから入力されるデータ及び制御信号をタイミングコントローラ24に伝達して、タイミングコントローラ24はこれらデータ及び制御信号を適切に処理してゲート及びデータドライバ26、28に供給する。

10

**【0008】**

そしてゲートドライバ26とデータドライバ28にはそれぞれゲートライン12とデータライン14が連結されて、ゲートドライバ26は液晶パネル10上の薄膜トランジスタTをオン/オフ制御することができるようタイミングコントローラ24から入力される制御信号に応答してフレーム別に各ゲートライン12を1水平同期時間ずつ順次にインエーブル(enable)させる。続いて、各ゲートライン12別薄膜トランジスタTをオン/オフ制御して、データドライバ28はタイミングコントローラ24から入力されるデータ及び制御信号に応答して入力データの基準電圧を選択した後、複数のデータライン14に供給する。その結果、各ゲートライン12のゲート信号により各ゲートライン12別に選択された薄膜トランジスタTがオンされればデータライン14のデータ信号がそれぞれの薄膜トランジスタTを介して該画素電極に伝達され、これによって画素電極と共に電極間の電界で液晶が駆動される。

20

**【0009】**

また基準電圧生成部30はデータドライバ28で使われるD A C(Digital To Analog Converter)基準電圧を生成して、電源電圧生成部32は先によく見た駆動回路部20の各構成要素に対する動作電源を供給すると同時に液晶パネル10の共通電極電圧、共通電圧を生成及び供給する。

30

**【0010】**

一方、一般的な液晶に直流電圧が長時間印加されると液晶内のイオン性不純物が電界により固着されて、深化すれば液晶分子のプレチルト(pretilt)値が変化して目的による制御が難しくなる。そのため残像のような画質低下が伴うので、これを防止するために通常液晶に伝達されるデータ信号の極性をフレーム毎に反転させるインバージョン(inversion)方式を採択している。

**【0011】**

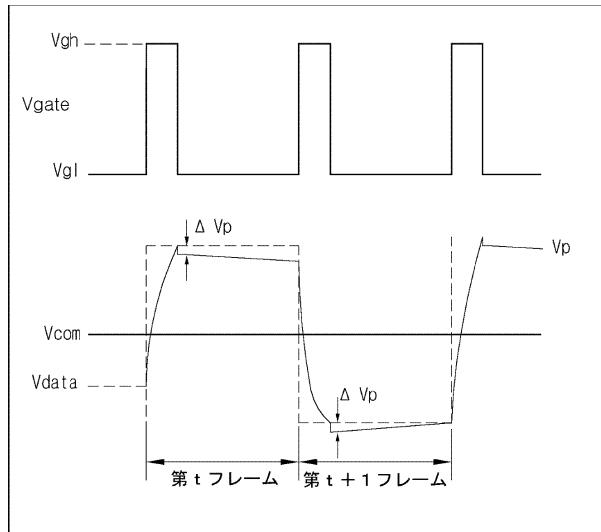

すなわち、添付された図2は一般的な液晶パネルに供給される信号電圧を示した波形図であって、共通電極に共通電圧Vcomが印加されて、ゲート信号Vgateが各ゲートラインに順次に供給されて、データ信号Vdataがデータラインを介して該画素に伝達される。

40

**【0012】**

この時ゲート信号Vgateは薄膜トランジスタのターンオン(turn-on)区間である高電位ゲート電圧Vghと薄膜トランジスタのターンオフ(turn-off)区間である低電位ゲート電圧Vglが繰り返される矩形波を示しており、データ信号Vdataはフレーム別に極性が反転されるインバージョン方式を取るので、任意のtフレームでゲート信号Vgateの高電位ゲート電圧Vghが印加されるターンオン区間では正(+)極性のデータ信号Vdataが画素に供給されて、t+1フレームでゲート信号Vgateの高電位ゲート電圧Vghが印加されるターンオン区間では負(-)極性のデータ信号Vdataが画素に供給される。

50

## 【0013】

そしてこの場合ゲート信号  $V_{gate}$  が高電位から低電位に遷移されるターン オフ区間では画素内の液晶容量、言い換えると画素電圧の電圧降下が現われるのに、これを画素電圧の変動分 ( $V_p$ ) といえば、以下の式 1 で表現することができる。

## [式 1]

$$V_p = \{C_{gd} / (C_{lc} + C_{st} + C_{gd})\} (V_{gh} - V_{gl})$$

## 【0014】

ここで  $C_{lc}$  は液晶容量、 $C_{st}$  は保存容量、 $C_{gd}$  は薄膜トランジスタの寄生容量、 $V_{gh}$ 、 $V_{gl}$  はそれぞれ高電位及び低電位ゲート信号電圧を示す。

## 【0015】

ところがこのような画素電圧の変動分は液晶パネルの位置別に不均一に現れると同時にフレーム別画素電圧を非対称的に歪曲させて輝度偏差を誘発し、結局画面ちらつき等のフリッカー (flicker) 現象に引き継がれて表示品質を大きく低下させる。

## 【0016】

そのため前記のフリッカー現象を解消しようと一定周期を有する矩形波のフリッカー信号に同期してゲート信号  $V_{gate}$  を調整することによって高電位ゲート電圧  $V_{gh}$  の後段一定区間を相対的に低い電位の調整領域に遷移させる方法が提案されて、これを通じて画素電圧の変動分によるフリッcker 現象を低減させることができるようにになった。

## 【0017】

また一方、最近では液晶表示装置の低価格化を達成しようと材料費の大部分を占めるドライバ IC に対する所要費用を減らすことが注目されており、一例では、データラインの数を減らすことによってデータドライバのドライバ IC に対する数量節減を試みる方法が紹介された。

## 【0018】

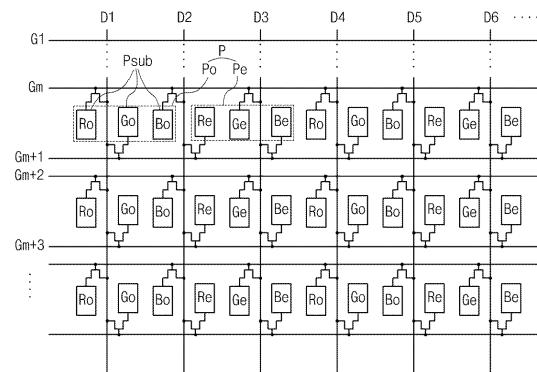

具体的な 1 様態では、データラインの数を半分に減らして各データラインの左右に隣接した 2 画素が一つのデータラインを共有するいわゆる D G I P (Double pixel Gate In Panel) 方式の液晶表示装置を示す。添付された図 3 はこれを説明するため的一般的な D G I P 方式液晶パネルの概要図である。この時、便宜上赤 (R)、緑 (G)、青 (B) 色が発現されるそれぞれの単位領域をサブ画素  $P_{sub}$  と言って、データライン間の相互に隣接した赤、緑、青サブ画素  $P_{sub}$  を一つずつの単位として一画素  $P$  は、各サブ画素  $P_{sub}$  が水平列に沿って赤 (R)、緑 (G)、青 (B) の順で繰り返されて、垂直列に沿って同一カラーで配列されたストライプ (stripe) 状で示すことができる。

## 【0019】

そしてこのような D G I P 方式で一つのデータライン  $D_1$ 、 $D_2$ 、 $D_3$ 、 $\dots$  を水平列の左右 2 サブ画素  $P_{sub}$  が相互に共有して、ゲートライン  $G_1$ 、 $\dots$ 、 $G_m$ 、 $G_{m+1}$ 、 $G_{m+2}$ 、 $\dots$  は最上及び最下の一つずつを除けばそれぞれの水平列間に 2 個ずつ位置するので、図面でのように ( $G_m$ ,  $G_{m+1}$ )、( $G_{m+2}$ ,  $G_{m+3}$ ) ゲートライン間ではそれぞれサブ画素  $P_{sub}$  の水平列が介在されて、( $G_{m+1}$ ,  $G_{m+2}$ ) ゲートラインは相互に隣接している。共にこのような D G I P 方式液晶パネルは最上位から最下位ゲートライン  $G_1$ 、 $\dots$ 、 $G_m$ 、 $G_{m+1}$ 、 $G_{m+2}$ 、 $\dots$  まで順次にゲート信号が印加されることによって各ゲートライン  $G_1$ 、 $\dots$ 、 $G_m$ 、 $G_{m+1}$ 、 $G_{m+2}$ 、 $\dots$  別サブ画素  $P_{sub}$  がオープンされて、データライン  $D_1$ 、 $D_2$ 、 $D_3$ 、 $\dots$  を介して供給されるデータ信号により各サブ画素  $P_{sub}$  が駆動されて該カラーを表示する。

## 【0020】

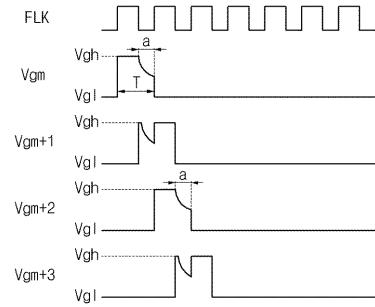

すなわち、添付された図 4 は一般的な D G I P 液晶パネルのゲート信号入力時点を決定するゲート信号  $V_{gm}$ 、 $V_{gm+1}$ 、 $V_{gm+2}$ 、 $V_{gm+3}$  に対する波形図であって、前での図 3 と共に参照すると、任意の  $G_m$ 、 $G_{m+1}$ 、 $G_{m+2}$ 、 $G_{m+3}$  ゲートラインにそれぞれ印加されるゲート信号  $V_{gm}$ 、 $V_{gm+1}$ 、 $V_{gm+2}$ 、 $V_{gm+3}$  を確認す

10

20

30

40

50

ることができる。

#### 【0021】

この場合液晶パネルの左側から各水平列の画素 P を奇数と偶数に区分すれば、G<sub>m</sub> 及び G<sub>m</sub> + 1 ゲートライン間に位置した水平列の画素 P において奇数番目画素 P のうち赤 (R<sub>o</sub>)、青 (B<sub>o</sub>) サブ画素 P<sub>s u b</sub> と偶数番目画素 P のうち緑 (G<sub>e</sub>) サブ画素 P<sub>s u b</sub> はそれぞれゲートライン G<sub>m</sub> のゲート信号 V<sub>g m</sub> により駆動されて、奇数番目画素 P のうち緑 (G<sub>o</sub>) サブ画素 P<sub>s u b</sub> と偶数番目画素 P のうち赤 (R<sub>e</sub>)、青 (B<sub>e</sub>) サブ画素 P<sub>s u b</sub> はそれぞれゲートライン G<sub>m</sub> + 1 のゲート信号 V<sub>g m + 1</sub> により駆動され、ゲートライン G<sub>m</sub> + 2 及び G<sub>m</sub> + 3 間に位置した水平列の画素 P において奇数番目画素 P のうち赤 (R<sub>o</sub>)、青 (B<sub>o</sub>) サブ画素 P<sub>s u b</sub> と偶数番目画素 P のうち緑 (G<sub>e</sub>) サブ画素 P<sub>s u b</sub> はそれぞれゲートライン G<sub>m</sub> + 2 のゲート信号 V<sub>g m + 2</sub> により駆動されて、奇数番目画素 P のうち緑 (G<sub>o</sub>) サブ画素 P<sub>s u b</sub> と偶数番目画素 P のうち赤 (R<sub>e</sub>)、青 (B<sub>e</sub>) サブ画素 P<sub>s u b</sub> はそれぞれゲートライン G<sub>m</sub> + 3 に印加されるゲート信号 V<sub>g m + 3</sub> により駆動される。そしてこのうちゲート信号 V<sub>g m</sub> と V<sub>g m + 2</sub> そして V<sub>g m + 1</sub> と V<sub>g m + 3</sub> はそれぞれ 1 周期 (T) 差を示して、ゲート信号 V<sub>g m</sub>、V<sub>g m + 1</sub>、V<sub>g m + 2</sub>、V<sub>g m + 3</sub> は順に 1 / 2 周期 (T / 2) 差を見せる。

10

#### 【0022】

この時 DGIP 方式の液晶表示装置もフリッカー現象が現われることがあるので、図面に示したようにフリッカー信号 F<sub>L K</sub> を利用してゲート信号を調整するが、下降地点 (falling time) が 1 周期 T と同一な周期を有するフリッcker 信号 F<sub>L K</sub> に同期してゲート信号を調整する場合にゲート信号 V<sub>g m</sub> をはじめとしてこれと 1 周期 (T) 差を見せるゲート信号 V<sub>g m + 2</sub> にも影響を及ぼして、その結果ゲート信号 V<sub>g m</sub>、V<sub>g m + 2</sub> の高電位ゲート電圧 V<sub>g h</sub> 後段にはそれぞれ相対的に低い電位の調整領域 a が付与され、これによってゲートライン G<sub>m</sub>、G<sub>m</sub> + 2 に接続されたサブ画素 P<sub>s u b</sub> に対するフリッcker 現象が抑制ができる。

20

#### 【0023】

しかしこの場合フリッcker 信号 F<sub>L K</sub> はゲート信号 V<sub>g m + 1</sub>、V<sub>g m + 3</sub> にも影響を及ぼすようになるので、ゲート信号 V<sub>g m + 1</sub>、V<sub>g m + 3</sub> はそれぞれゲート信号 V<sub>g m</sub>、V<sub>g m + 2</sub> と 1 / 2 周期 (T / 2) 差を見せているので V<sub>g m + 1</sub>、V<sub>g m + 3</sub> ゲート信号の場合にはそれとの高電位ゲート電圧 V<sub>g h</sub> 前段で信号波形が歪曲される現象が現われる。

30

#### 【0024】

すなわち、図 4 の V<sub>g m + 1</sub>、V<sub>g m + 3</sub> ゲート信号においてフリッcker 信号 F<sub>L K</sub> によりそれぞれの高電位ゲート電圧 V<sub>g h</sub> 前段の信号歪みを確認することができて、このような信号歪みは G<sub>m</sub> + 1、G<sub>m</sub> + 3 ゲートラインそれぞれに接続されたサブ画素 P<sub>s u b</sub> に対する輝度変化を発生させて画質を低下させる問題点を示す。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0025】

これで本発明は前記のような問題点を解決するために案出したものであって、フリッcker 現象を防止するためのフリッcker 信号混入時伴うゲート信号歪みによる画質低下現象を防止することができる DGIP 方式液晶表示装置及びこれの画像具現方法を提供することに目的がある。

40

#### 【課題を解決するための手段】

#### 【0026】

前記のような目的を達成するために本発明は、垂直及び水平画素列がマトリックス状で定義された液晶パネルと、前記液晶パネル内で順次に配列された G<sub>m</sub>、G<sub>m</sub> + 1、G<sub>m</sub> + 2、G<sub>m</sub> + 3 (m は自然数) ゲートラインと、前記液晶パネル内で前記 G<sub>m</sub>、G<sub>m</sub> + 1、G<sub>m</sub> + 2、G<sub>m</sub> + 3 ゲートラインと交差するデータラインと、データ信号、電源電圧、クロック、第 1 フリッcker 信号、第 2 フリッcker 信号を出力するタイミングコントローラと

50

、前記電源電圧を利用して高電位ゲート電圧を生成して、前記高電位ゲート電圧を前記第1フリッカー信号と前記クロックを利用して調節して、前記高電位ゲート電圧を前記第2フリッcker信号と前記クロックを利用して調節することによって調整クロックを出力する外部回路と、前記調整クロックを利用して、ゲート信号Vgm、Vgm1、Vgm2、Vgm3を生成して前記Gm、Gm+1、Gm2、Gm+3ゲートラインそれぞれに伝送するゲートドライバと、前記データ信号及び制御信号を利用して前記データラインに画像信号を伝達するデータドライバとを含む液晶表示装置を提供する。

#### 【0027】

前記水平画素列はそれぞれ、前記ゲートラインGm、Gm+1そして前記ゲートラインGm+2、Gm+3間に1列ずつ配列されて、前記垂直画素列はそれぞれ、前記データラインの左右両側に2列に配列される。 10

#### 【0028】

前記水平画素列は赤(R)、緑(G)、青(B)カラーのサブ画素Psubが順序通り繰り返されて、前記垂直画素列は同一カラーの前記サブ画素Psubが配列される。

#### 【0029】

前記赤(R)、緑(G)、青(B)カラーのサブ画素Psubによって画素Pが定義されて、前記画素Pは前記水平画素列それぞれで奇数番目と偶数番目に繰り返し配列される。

#### 【0030】

前記奇数番目画素Pの赤(Ro)、青(Bo)カラーサブ画素Psub、前記偶数番目画素Pの緑(Ge)カラーサブ画素Psubは前記GmゲートラインまたはGm+2ゲートラインに接続されて、前記奇数番目画素Pの緑(Go)カラーサブ画素Psub、前記偶数番目画素Pの赤(Re)、青(Be)カラーサブ画素Psubは前記Gm+1ゲートラインまたはGm+3ゲートラインに接続される。 20

#### 【0031】

また前記奇数番目画素Pの赤(Ro)、緑(Go)カラーサブ画素Psubと、前記奇数番目画素Pの青(Bo)カラーサブ画素Psub及び前記偶数番目画素Pの赤(Re)カラーサブ画素Psubと、前記偶数番目画素Pの緑(Ge)、青(Be)カラーサブ画素Psubはそれぞれ同じデータラインに接続される。

#### 【0032】

前記ゲート信号Vgm、Vgm+1、Vgm+2、Vgm+3はそれぞれ、高電位ゲート電圧と低電位ゲート電圧が順次に繰り返されるパルス形態である。 30

#### 【0033】

そして前記ゲート信号Vgm、Vgm+2は相互に1周期(T)差を有して、前記Vgm+1、Vgm+3ゲート信号は相互に1周期(T)差を有して、前記Vgm、Vgm+1、Vgm+2、Vgm+3ゲート信号は順次に1/2周期(T/2)差を有する。

#### 【0034】

前記第1及び第2フリッcker信号は相互に1/2周期(T/2)差を有する矩形波であって、前記ゲート信号Vgm、Vgm+2と前記ゲート信号Vgm+1、Vgm+3は、それぞれ前記高電位ゲート電圧の後段部に前記高電位ゲート電圧より小さくて前記低電位ゲート電圧より高い電圧で構成される調整領域が付与される。 40

#### 【0035】

前記外部回路は、前記高電位ゲート電圧を生成するPWM(Pulse Width Modulation)部と、前記第1フリッcker信号を利用して前記高電位ゲート電圧を調節する第1GPM(Gate Pulse Modulation)部と、前記第2フリッcker信号を利用して前記高電位ゲート電圧を調節する第2GPM部を含む。

#### 【0036】

一方、本発明は、一方向に配列されるゲートラインGm、Gm+1、Gm+2、Gm+3と、前記ゲートラインGm、Gm+1、Gm+2、Gm+3と交差するデータラインを具備した液晶表示装置の駆動方法として、高電位ゲート電圧を生成する段階と、第1フリ 50

ツカ－信号を利用して、前記高電位ゲート電圧を調節して前記 G m、G m + 2 ゲートラインに伝送する段階と、第 2 フリッカ－信号を利用して、前記高電位ゲート電圧を調節して前記ゲートライン G m + 1、G m + 3 に伝送する段階とを含む液晶表示装置の駆動方法を提供する。

**【 0 0 3 7 】**

前記ゲート信号 V g m、V g m + 1、V g m + 2、V g m + 3 は順次に 1 / 2 周期 ( T / 2 ) 差を有しており、前記第 1 及び第 2 フリッカ－信号は相互に 1 / 2 周期 ( T / 2 ) 差を有する矩形波である。

**【 0 0 3 8 】**

また液晶表示装置の駆動方法は前記データラインに画像信号を伝送する段階と、前記ゲートライン G m、G m + 1、G m + 2、G m + 3 それに前記ゲート信号 V g m、V g m + 1、V g m + 2、V g m + 3 が伝送されている間、前記画像信号を前記ゲートライン G m、G m + 1、G m + 2、G m + 3 それに連結されるサブ画素に伝送する段階とをさらに含む。 10

**【発明の効果】**

**【 0 0 3 9 】**

以上でよく見たように、本発明による D G I P 液晶表示装置はゲート信号歪みによる画質低下現象を防止することができる長所がある。

**【 0 0 4 0 】**

特に、本発明による D G I P 液晶表示装置は別途の第 1 及び第 2 フリッカ－信号を利用して前記ゲート信号の高電位ゲート電圧にそれぞれ個別的に調整領域を付与するので、この過程中に所望しない信号歪み現象を未然に防止することができて、これを通じてフリッカ－現象をはじめとする画像の局部的な輝度差を解消することができる長所がある。 20

**【発明を実施するための最良の形態】**

**【 0 0 4 1 】**

以下図面を参照して本発明をさらに詳細に説明する。

**【 0 0 4 2 】**

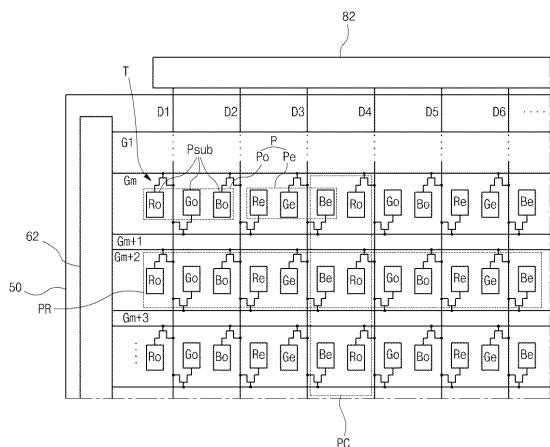

添付された図 5 は本発明による D G I P 方式液晶表示装置の概要図であって、液晶パネル 5 0 をはじめとする駆動回路部の一部が現れている。

**【 0 0 4 3 】**

図面に詳細に表示されていないが、本発明による液晶パネル 5 0 は液晶層を間に置いて対面合着された第 1 及び第 2 基板で構成され、第 1 基板内面には複数のゲートライン G 1、. . . 、G m、G m + 1、G m + 2、G m + 3、. . . とデータライン D 1、D 2、D 3、D 4、. . . が交差配列されて垂直画素列 P C 及び水平画素列 P R を定義して、これらの交差点には薄膜トランジスタ T が具備されて画素電極と対応連結している。共に第 2 基板内面にはカラー具現のためのカラーフィルタと共に通電極が具備され、これによって共通電極と画素電極及びその間に介在した液晶は液晶キャバシタを形成する。 30

**【 0 0 4 4 】**

一方、本発明による液晶パネル 5 0 は D G I P 方式であることがあって、これにより赤 ( R ) 、緑 ( G ) 、青 ( B ) カラーが発現されるそれをサブ画素 P s u b と言う場合に左右に隣接した 2 サブ画素 P s u b が一つのデータライン D 1、D 2、D 3、D 4 . . . を共有する方式を取るので、相互に隣接した赤、緑、青サブ画素 P s u b 一つずつが一画素 P を形成するとすれば、各サブ画素 P s u b は水平画素列 P R に沿って赤 ( R ) 、緑 ( G ) 、青 ( B ) カラー順で繰り返されて、垂直画素列 P C に沿っては同一カラーのサブ画素 P s u b が配列される。 40

**【 0 0 4 5 】**

そして本発明による液晶パネル 5 0 でゲートラインは G 1、. . . 、G m、G m + 1、G m + 2、G m + 3、. . . ( m は自然数 ) の反復配列で構成され、水平画素列 P R のサブ画素 P s u b はそれぞれゲートライン G m、G m + 1 とゲートライン G m + 2、G m + 3 間に 1 列ずつ配列されて、垂直画素列 P C のサブ画素 P s u b はそれぞれのデータライ 50

ン D 1、D 2、D 3、D 4、. . . 左右両側に 2 列に配列される。

#### 【0046】

その結果、各水平画素列 P R 内で画素 P は奇数番目と偶数番目に区分するのに、ゲートライン G m と G m + 1 間に介在された水平画素列 P R のサブ画素 P s u b のうちで奇数番目画素 P の赤 (R o)、青 (B o) カラーサブ画素 P s u b と偶数番目画素 P の緑 (G e) カラーサブ画素 P s u b はそれぞれ G m ゲートラインに接続されて、奇数番目画素 P の緑 (G o) カラーサブ画素 P s u b と偶数番目画素 P の赤 (R e)、青 (B e) カラーサブ画素 P s u b はそれぞれ G m + 1 ゲートラインに接続され、G m + 2 ゲートラインと G m + 3 ゲートライン間に介在された水平画素列 P R のサブ画素 P s u b のうちで奇数番目画素 P の赤 (R o)、青 (B o) カラーサブ画素 P s u b と偶数番目画素 P の緑 (G e) カラーサブ画素 P s u b はそれぞれ G m + 2 ゲートラインに接続されて、奇数番目画素 P の緑 (G o) カラーサブ画素 P s u b と偶数番目画素 P の赤 (R e)、青 (B e) カラーサブ画素 P s u b はそれぞれ G m + 3 ゲートラインに接続される。共に垂直画素列 P C のサブ画素 P s u b のうちで奇数番目画素 P の赤 (R o)、緑 (G o) カラーサブ画素 P s u b はそれぞれ任意に D 1 データラインに接続されて、奇数番目画素 P の青 (B o) カラーサブ画素 P s u b 及び偶数番目画素 P の赤 (R e) カラーサブ画素 P s u b は D 2 データラインに接続され、偶数番目画素 P の緑 (G e)、青 (B e) カラーサブ画素 P s u b は D 3 データラインに接続される。

10

#### 【0047】

そしてこれら複数のゲートライン G 1、. . . 、G m、G m + 1、G m + 2、G m + 3 20 . . . はゲートドライバ 6 2 に連結されて、複数のデータライン D 1、D 2、D 3、D 4、. . . はデータドライバ 8 2 に連結されるので、ゲートライン G 1、. . . 、G m、G m + 1、G m + 2、G m + 3、. . . から伝送されるゲート信号により各ゲートライン G 1、. . . 、G m、G m + 1、G m + 2、G m + 3 . . . 別に選択されたサブ画素 P s u b がオープンされればデータライン D 1、D 2、D 3、D 4、. . . から伝送されるデータ信号が該サブ画素 P s u b に伝達されて駆動される。

#### 【0048】

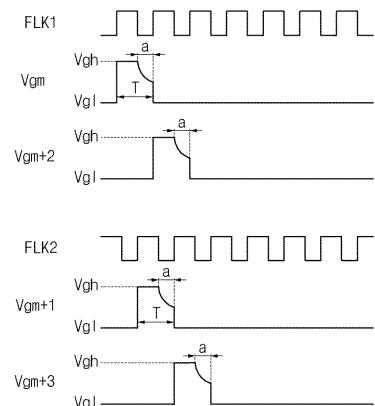

この時添付された図 6 は本発明による D G I P 方式液晶パネルに印加されるゲート信号を示した波形図であって、前での図 5 を共に参照すると、ゲートライン G m、G m + 1、G m + 2、G m + 3 にそれぞれ印加される V g m、V g m + 1、V g m + 2、V g m + 3 30 ゲート信号が現れている。

#### 【0049】

そして、このうちゲート信号 V g m と V g m + 2 そしてゲート信号 V g m + 1 と V g m + 3 はそれぞれ 1 周期 (T) 差を示して、ゲート信号 V g m と V g m + 1、V g m + 1 と V g m + 2、V g m + 2 と V g m + 3 はそれぞれ順に 1 / 2 周期 (T / 2) 差を見せ、これらゲート信号 V g m、V g m + 1、V g m + 2、V g m + 3 は薄膜トランジスタのターンオン区間である高電位ゲート電圧 V g h と薄膜トランジスタのターンオフ区間である低電位ゲート電圧 V g l が順次に繰り返されるパルス形態で構成される。このようなゲート信号はそれぞれ 1 フレーム周期で繰り返される。

40

#### 【0050】

これらゲート信号 V g m、V g m + 1、V g m + 2、V g m + 3 それぞれの高電位ゲート電圧 V g h 後段部は、高電位ゲート電圧 V g h よりは低く低電位ゲート電圧 V g l よりは大きい調整領域 a が付与されているので、このためにタイミングコントローラ (図示せず) から伝送される第 1 及び第 2 フリッカー信号 F L K 1、F L K 2 が使われ、これら第 1 及び第 2 フリッcker 信号 F L K 1、F L K 2 は相互に 1 / 2 周期 (T / 2) だけの差を見せる矩形波でゲート信号 V g m、V g m + 2 は第 1 フリッcker 信号 F L K 1 を利用して調節生成されて、ゲート信号 V g m + 1、V g m + 3 は第 2 フリッcker 信号 F L K 2 を利用して調節生成される。

#### 【0051】

すなわち、本発明による D G I P 方式液晶パネルは相互に 1 / 2 周期 (T / 2) 差を示

50

す 2 個の第 1 及び第 2 フリッカー信号 F L K 1、F L K 2 を用いることを特徴としており、このうち第 1 フリッcker 信号 F L K 1 はゲート信号 V g m、V g m + 2 の生成に使用されそれぞれの高電位ゲート電圧 V g h 後段に相対的に低い電位の調整領域 a を生成して、第 2 フリッcker 信号 F L K 2 はゲート信号 V g m + 1、V g m + 3 の生成に使用されそれぞれの高電位ゲート電圧 V g h 後段に相対的に低い電位の調整領域 a を生成する。言い換えると、第 1 フリッcker 信号 F L K 1 はゲート信号 V g m、V g m + 2 に同期される信号波形であって、相互に 1 周期 (T) 差を見せるゲート信号 V g m、V g m + 2 の生成に使用されそれぞれの高電位ゲート電圧 V g h 後段に調整領域 a が現われるようにして、第 2 フリッcker 信号 F L K 2 はゲート信号 V g m + 1、V g m + 3 に同期される信号波形であって第 1 フリッcker 信号 F L K 1 と 1 / 2 周期 (T / 2) 差を見せ、相互に 1 周期 (T) 差を見せるゲート信号 V g m + 1、V g m + 3 の生成に使用されそれぞれの高電位ゲート電圧 V g h 後段に調整領域 a が現われるようとする。

#### 【 0 0 5 2 】

このような調整領域 a は、各ゲート信号が薄膜トランジスタのターンオン (turn on) 時間の間高電位ゲート電圧 V g h を続けて維持する代わりに後段では高電位ゲート電圧 V g h より小さい電圧を有するようにして V p の値を減少させる役割をする区間である。例えば、調整領域 a は高電位ゲート電圧 V g h と低電位ゲート電圧 V g l より高い電圧を結ぶ曲線、すなわち、電圧値が高電位ゲート電圧 V g h から低電位ゲート電圧 V g l より高い電圧まで非線形的に減少する形態を有することができる。

例えば、調整領域 a は、1 周期 T の 2 / 3 地点 (2 T / 3) から始まり、調整領域 a の一端での電圧は、高電位ゲート電圧 V g h の 2 / 3 の値 (2 V g h / 3) である。

#### 【 0 0 5 3 】

これによって一般的な場合でよく見たように単一フリッcker 信号を利用したゲート信号の調節時にゲート信号間の周期差によって現われることができる一部ゲート信号に対する信号歪みを解消して、全ての水平列に対する輝度差及びフリッcker 現象を解消することができる。

#### 【 0 0 5 4 】

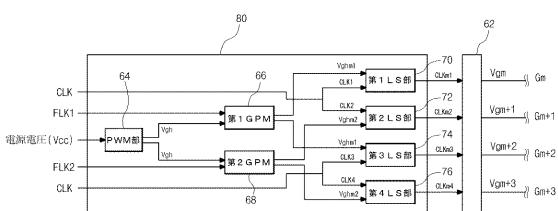

そしてこのような第 1 及び第 2 フリッcker 信号 F L K 1、F L K 2 によるフリッcker 現象を除去するためにゲートドライバ 6 2 は図 7 に示したように構成することができる。

#### 【 0 0 5 5 】

この時図 7 は本発明による D G I P 方式液晶表示装置に適用されることがある外部回路 8 0 及びゲートドライバ 6 2 に対するブロック図であって、便宜上、ゲートライン G m、G m + 1、G m + 2、G m + 3 にだけ限定して示したので、外部回路 8 0 は、印刷回路基板の形態であって、P W M 部 6 4 と第 1 及び第 2 G P M 部 6 6、6 8 そしてゲートライン G m、G m + 1、G m + 2、G m + 3 がそれぞれ連結する第 1 ないし第 4 L S (L e v e l Shift e r) 部 7 0、7 2、7 4、7 6 を含むことができる。

#### 【 0 0 5 6 】

この時 P W M 部 6 4 はタイミングコントローラ (図示せず) から伝送される電源電圧 V c c を適切に処理して、ゲート信号のための高電位ゲート電圧 V g h を生成する。生成された高電位ゲート電圧 V g h は、第 1 G P M 部 6 6 と第 2 G P M 部 6 8 に供給される。

#### 【 0 0 5 7 】

次に第 1 G P M 部 6 6 はタイミングコントローラから伝達される第 1 フリッcker 信号 F L K 1 を利用して P W M 部 6 4 から伝送される高電位ゲート電圧 V g h を調節することによって後端に調整領域(図 6 の a)を有する第 1 調整高電位ゲート電圧 V g h m 1 を生成する。また第 2 G P M 部 6 8 はタイミングコントローラから伝達される第 2 フリッcker 信号 F L K 2 を利用して P W M 部 6 4 から伝送される高電位ゲート電圧 V g h を調節することによって後端に調整領域(図 6 の a)を有する第 2 調整高電位ゲート電圧 V g h m 2 を生成する。

#### 【 0 0 5 8 】

そして第 1 G P M 部 6 6 で生成された第 1 調整高電位ゲート電圧 V g h m 1 は、第 1 及

10

20

30

40

50

び 3 L S 部 7 0、7 4 に供給された後、第 1 及び 3 L S 部 7 0、7 4 でタイミングコントローラから供給される第 1 及び第 3 クロック C L K 1、C L K 3 を利用して適切に調節され第 1 及び第 3 調整クロック C L K m 1、C L K m 3 として出力されゲートドライバ 6 2 に伝達される。また第 2 G P M 部 6 8 で生成された第 2 調整高電位ゲート電圧 V g h m 2 は、第 2 及び第 4 L S 部 7 2、7 6 に供給された後、第 2 及び第 4 L S 部 7 2、7 6 でタイミングコントローラから供給される第 2 及び第 4 クロック C L K 2、C L K 4 を利用して適切に調節され第 2 及び第 4 調整クロック C L K m 2、C L K m 4 として出力されゲートドライバー 6 2 に伝達される。

ゲートドライバー 6 2 は、シフトレジストの場合があって、第 1 ないし第 4 調整クロック C L K m 1、C L K m 2、C L K m 3、C L K m 4 は、シフトレジストによって、図 6 に示したゲート信号 V g m、V g m+1、V g m+2、V g m+3 に変形出力されそれぞれゲートライン G m、G m 1、G m 2、G m 3 に供給される。

10

【図面の簡単な説明】

【0 0 5 9】

【図 1】一般的な液晶表示装置のブロック図。

【図 2】一般的な液晶表示装置のゲート信号に対する波形図。

【図 3】一般的な D G I P 方式液晶パネルの概要図。

【図 4】一般的なフリッカー信号によって調節された D G I P 方式液晶パネルのゲート信号に対する波形図。

20

【図 5】本発明による D G I P 方式液晶パネルに対する概要図。

【図 6】本発明による D G I P 方式液晶パネルのゲート信号に対する波形図。

【図 7】本発明による D G I P 方式液晶パネルの外部回路に対するブロック図。

【符号の説明】

【0 0 6 0】

5 0 : 液晶パネル

6 2 : ゲートドライバ

6 4 : PWM 部

6 6、6 8 : 第 1 及び第 2 G P M 部

7 0、7 2、7 4、7 6 : 第 1 ないし第 4 L S 部

G m、G m + 1、G m + 2、G m + 3 : ゲートライン

30

V g m、V g m + 1、V g m + 2、V g m + 3 : ゲート信号

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 611 E

G 09 G 3/20 621 B

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 イ ミンキュン

大韓民国 718-833 キョンブック チルゴッケン ソクジョクミヨン チュンリ 141

ポンジ プヨン アパート 109-909

審査官 西島 篤宏

(56)参考文献 特開平08-248385 (JP, A)

特開平04-324418 (JP, A)

特開平11-281957 (JP, A)

特開平06-003647 (JP, A)

特開平10-171412 (JP, A)

特開平04-360127 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 00 - 3 / 38

G 02 F 1 / 133 505 - 580