(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7441979号**

**(P7441979)**

(45)発行日 令和6年3月1日(2024.3.1)

(24)登録日 令和6年2月21日(2024.2.21)

(51)国際特許分類

|                        |     |              |   |

|------------------------|-----|--------------|---|

| H 01 L 25/04 (2023.01) | F I | H 01 L 25/04 | Z |

| H 01 L 25/18 (2023.01) |     | H 01 L 23/30 | R |

| H 01 L 23/29 (2006.01) |     |              |   |

| H 01 L 23/31 (2006.01) |     |              |   |

請求項の数 30 (全34頁)

(21)出願番号 特願2022-581735(P2022-581735)

(86)(22)出願日 令和3年6月23日(2021.6.23)

(65)公表番号 特表2023-525403(P2023-525403

A)

(43)公表日 令和5年6月15日(2023.6.15)

(86)国際出願番号 PCT/US2021/038696

(87)国際公開番号 WO2022/005846

(87)国際公開日 令和4年1月6日(2022.1.6)

審査請求日 令和5年2月27日(2023.2.27)

(31)優先権主張番号 16/917,686

(32)優先日 令和2年6月30日(2020.6.30)

(33)優先権主張国・地域又は機関

米国(US)

早期審査対象出願

(73)特許権者 518065991

アデイア セミコンダクター ポンディング テクノロジーズ インコーポレイテッド

アメリカ合衆国 カリフォルニア州 95134 サンノゼ オーチャード パーク

ウェイ 3025

(74)代理人 100094569

弁理士 田中 伸一郎

(74)代理人 100103610

弁理士 吉田 和彦

(74)代理人 100109070

弁理士 須田 洋之

(74)代理人 100098475

弁理士 倉澤 伊知郎

(74)代理人 100130937

最終頁に続く

(54)【発明の名称】 集積デバイスパッケージ

**(57)【特許請求の範囲】****【請求項1】**プロセッサダイと、前記プロセッサダイの上に配置された第1のメモリダイであって、前記プロセッサダイ上に形成された接合層の導電性コンタクトに直接接合された導電性コンタクトを有し、介在する接着剤なしで前記プロセッサダイ上の前記接合層の非導電性領域に直接接合された非導電性領域を有する、前記第1のメモリダイと、介在する接着剤なしで前記プロセッサダイ上の前記接合層に直接接合された第1のダミー素子と、介在する接着剤なしで前記プロセッサダイ上の前記接合層に直接接合された第2のダミー素子と、を備え、前記第1のメモリダイは、前記第1のダミー素子と前記第2のダミー素子との間に横方向に配置され、前記プロセッサダイのフットプリントは、前記第1のメモリダイのフットプリントよりも大きい、電子部品。**【請求項2】**前記プロセッサダイ上に配置された第2のメモリダイをさらに備え、前記第2のメモリダイの導電性コンタクトが、介在する接着剤なしで前記プロセッサダイ上の前記接合層の導電性コンタクトに直接接合されている、請求項1に記載の電子部品。

**【請求項 3】**

前記第1のダミー素子及び前記第2のダミー素子は、前記プロセッサダイに直接接合される導電性コンタクトを含まない、請求項1に記載の電子部品。

**【請求項 4】**

前記第1のダミー素子及び前記第2のダミー素子は、シリコンを含む、請求項1に記載の電子部品。

**【請求項 5】**

前記第1のダミー素子及び前記第2のダミー素子の熱膨張係数(CTE)は、7 ppm/未満である、請求項1に記載の電子部品。

**【請求項 6】**

前記第1のダミー素子及び前記第2のダミー素子は、介在する接着剤なしで前記プロセッサダイ上の前記接合層の対応する非導電性フィールド領域に直接接合された、各々の第1の非導電性接合層及び第2の非導電性接合層を有する、請求項1に記載の電子部品。

10

**【請求項 7】**

前記第1のダミー素子及び前記第2のダミー素子は、前記プロセッサダイ及び前記第1のメモリダイの少なくとも1つに付与される応力を低減するための応力補償素子を含む、請求項1に記載の電子部品。

**【請求項 8】**

さらに、前記プロセッサダイを少なくとも部分的に貫通して延びる複数のピアを備える、請求項1に記載の電子部品。

20

**【請求項 9】**

さらに絶縁封入材を備え、前記第1のメモリダイ、前記第1のダミー素子及び前記第2のダミー素子が少なくとも部分的に前記絶縁封入材に埋め込まれている、請求項1に記載の電子部品。

**【請求項 10】**

前記第1のダミー素子及び前記第2のダミー素子の少なくとも一方は、アクティブ回路を有していない、請求項1に記載の電子部品。

**【請求項 11】**

電子部品であって、

第1の集積デバイスダイと、

30

前記第1の集積デバイスダイの上に取り付けられた第2の集積デバイスダイであって、回路を有する前記第2の集積デバイスダイと、

前記第1の集積デバイスダイの上に取り付けられ、前記電子部品の外側側縁に対して横方向に挿入されるダミー素子と、を備え、

前記ダミー素子及び前記第2の集積デバイスダイは、接着剤なしで前記第1の集積デバイスダイ上の接合層に直接接合され、前記ダミー素子の非導電性領域は、前記第1の集積デバイスダイ上の前記接合層の非導電性領域に直接接合され、

前記第1の集積デバイスダイは、前記第2の集積デバイスダイよりも大きなフットプリントを有する、

電子部品。

40

**【請求項 12】**

前記第1の集積デバイスダイはプロセッサダイを含み、前記第2の集積デバイスダイはメモリダイを含む、請求項11に記載の電子部品。

**【請求項 13】**

前記第1の集積デバイスダイに取り付けられた第2のダミー素子をさらに備え、前記ダミー素子及び前記第2のダミー素子はアクティブ回路を有していない、請求項12に記載の電子部品。

**【請求項 14】**

前記第1の集積デバイスダイに取り付けられた第3の集積デバイスダイをさらに備える、請求項13に記載の電子部品。

50

**【請求項 15】**

前記第3の集積デバイスダイは、第2のメモリダイを含み、前記メモリダイ及び前記第2のメモリダイは、前記ダミー素子と前記第2のダミー素子との間に横方向に配置されている、請求項14に記載の電子部品。

**【請求項 16】**

前記第2の集積デバイスダイの複数の導電性コンタクトが、介在する接着剤なしで前記第1の集積デバイスダイ上の前記接合層の複数の導電性コンタクトに直接接合されている、請求項11に記載の電子部品。

**【請求項 17】**

前記第2の集積デバイスダイの非導電性領域が、接着剤なしで前記第1の集積デバイスダイ上の前記接合層の前記非導電性領域に直接接合されている、請求項16に記載の電子部品。10

**【請求項 18】**

前記ダミー素子の非導電性領域だけが、介在する接着剤なしで、前記第1の集積デバイスダイ上の前記接合層の前記非導電性領域に直接接合されている、請求項11に記載の電子部品。

**【請求項 19】**

前記第1の集積デバイスダイを貫通して延びる複数のビアをさらに備える、請求項11に記載の電子部品。

**【請求項 20】**

さらに絶縁封入材を備え、前記第2の集積デバイスダイ及び前記ダミー素子は、前記絶縁封入材に少なくとも部分的に埋め込まれ、前記絶縁封入材の一部が、前記ダミー素子と前記電子部品の外側側縁との間に配置されている、請求項11に記載の電子部品。20

**【請求項 21】**

前記ダミー素子はシリコンを含む、請求項11に記載の電子部品。

**【請求項 22】**

前記ダミー素子は、前記第1の集積デバイスダイ及び／又は前記第2の集積デバイスダイに付与される応力を低減するための応力補償素子を含む、請求項11に記載の電子部品。

**【請求項 23】**

第1の非導電性フィールド領域と第1の導電性コンタクトとを有するキャリアと、30

前記キャリアに接合された第1の素子であって、前記第1の素子の第2の導電性コンタクトが、接着剤なしで前記キャリアの前記第1の導電性コンタクトに直接接合された、前記第1の素子と、

第2の非導電性フィールド領域を有する第2の素子であって、前記第2の非導電性フィールド領域は、前記第2の非導電性フィールド領域が前記第1の非導電性フィールド領域に接触するように、介在する接着剤なしで前記キャリアの前記第1の非導電性フィールド領域に直接接合され、前記第2の素子は、アクティブ回路を有しないダミー素子を含み、前記第2の素子は、前記キャリアに直接接合された前記第2の素子と前記キャリアとの間の導電性コンタクトを含まない、前記第2の素子と、を備え、

前記キャリアは、前記第1の素子よりも大きなフットプリントを有する、40

電子部品。

**【請求項 24】**

前記第1の素子はメモリダイを含み、前記キャリアはプロセッサダイを含む、請求項23に記載の電子部品。

**【請求項 25】**

さらに絶縁封入材を備え、前記第1の素子及び前記第2の素子は、前記絶縁封入材に少なくとも部分的に埋め込まれている、請求項23に記載の電子部品。

**【請求項 26】**

前記前記第1の素子は、接着剤なしで前記キャリアに直接ハイブリッド接合されており、

前記第1の素子の第3の非導電性フィールド領域が、接着剤なしで前記キャリアの前記第50

1の非導電性フィールド領域に直接接合されている、請求項23に記載の電子部品。

**【請求項27】**

前記第1のダミー素子は、前記電子部品の外側側縁に対して横方向に挿入されている、請求項1に記載の電子部品。

**【請求項28】**

前記第1のメモリダイの前記フットプリントは、前記プロセッサダイの前記フットプリントを超えて延びない、請求項1に記載の電子部品。

**【請求項29】**

前記絶縁封入材の一部が、前記第1のダミー素子と前記電子部品の外側側縁との間に配置されている、請求項9に記載の電子部品。

10

**【請求項30】**

前記第1のメモリダイの少なくとも1つの横方向側縁が、前記第1のダミー素子と交差する平面内にある、請求項1に記載の電子部品。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

(関連出願に対する優先権及び相互参照)

本出願は、2020年6月30日に出願された、米国非仮出願特許出願第16/917,686号に対する優先権を主張し、その全内容は、参照により本明細書に組み込まれる。

**【0002】**

20

**(技術分野)**

本分野は、集積デバイスパッケージ及びこれを形成するための方法に関する。

**【背景技術】**

**【0003】**

様々なパッケージング配置において、パッケージ、例えば、システムインパッケージ(SIP)内に複数の集積デバイスダイを配置することが有利であり得る。例えば、幾つかのパッケージは、パッケージ基板に沿って互いに離間して配置された異なるタイプのアクティブチップ又は集積デバイスダイを含む。また、3次元(3D)集積技術では、2又は3以上の集積デバイスダイを積層して互いに電気的に接続したパッケージを使用することが多い。

30

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

集積デバイスダイの上にモールド化合物又は封入材料を設けることができ、これによりパッケージ内に応力が発生する可能性がある。従って、改良された集積デバイスパッケージに対する継続的な必要性が存在する。

**【0005】**

これらの態様及び他の態様は、好ましい実施形態の以下の説明及び添付図面から明らかになるであろうが、この図面は、本発明を説明するためのものであり、限定するためのものではない。

40

**【図面の簡単な説明】**

**【0006】**

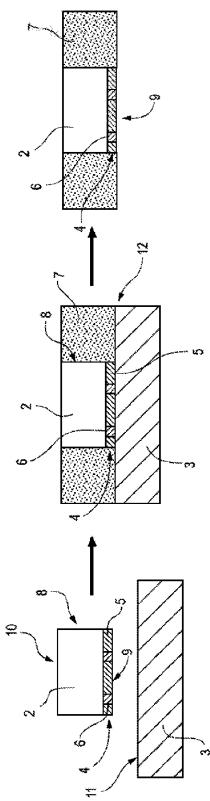

**【図1A】**様々な直接接合プロセスにおける犠牲キャリアの使用を概略的に示す図である。

**【図1B】**様々な直接接合プロセスにおける犠牲キャリアの使用を概略的に示す図である。

**【図1C】**様々な直接接合プロセスにおける犠牲キャリアの使用を概略的に示す図である。

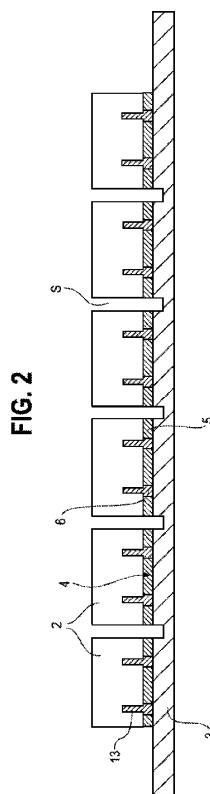

**【図2】**キャリアに直接接合された複数の素子を示す図である。

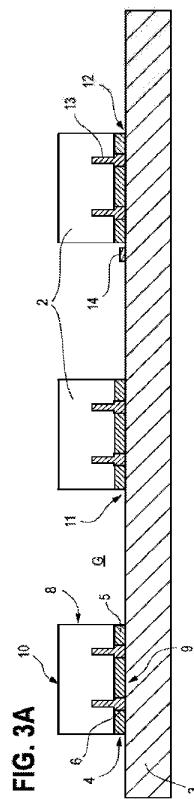

**【図3A】**接着剤を用いて素子がキャリアに直接接合される種々の例を示す図である。

**【図3B】**接着剤を用いて素子がキャリアに直接接合される種々の例を示す図である。

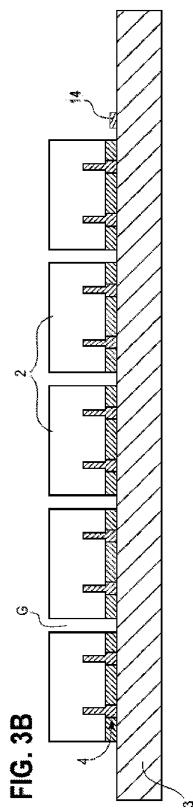

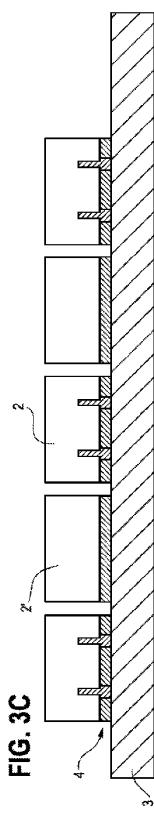

**【図3C】**接着剤を用いて素子がキャリアに直接接合される種々の例を示す図である。

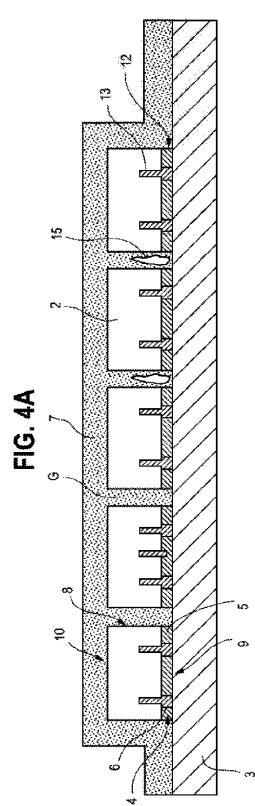

**【図4A】**キャリアに直接接合され、素子の上及び素子間のギャップ内に保護材料が施工

50

された複数の素子の概略側面図である。

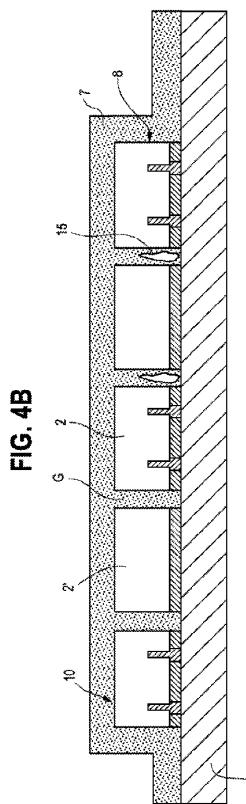

【図 4 B】キャリアに直接接合された 1 又は 2 以上のダミー素子を含む複数の素子の概略側面図である。

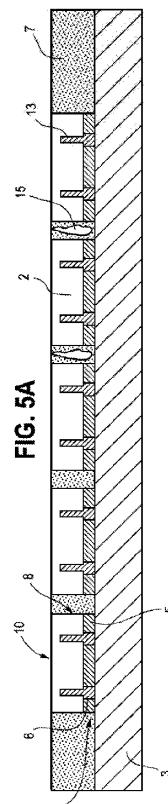

【図 5 A】再構成ウェーハを形成するための一連のプロセスステップを示す図である。

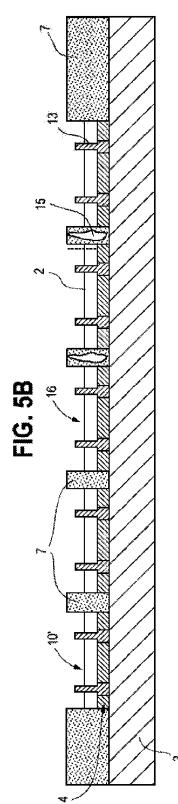

【図 5 B】再構成ウェーハを形成するための一連のプロセスステップを示す図である。

【図 5 C】再構成ウェーハを形成するための一連のプロセスステップを示す図である。

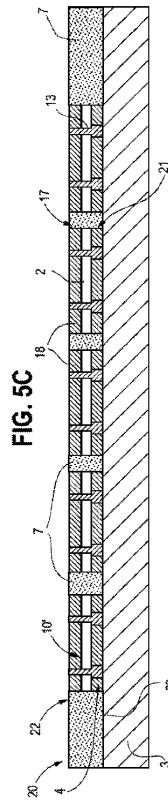

【図 6】別の再構成ウェーハ又は基板に直接接合するように構成された接合層を有する再構成ウェーハの概略側面断面図である。

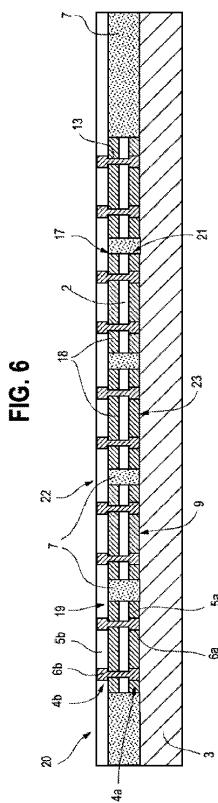

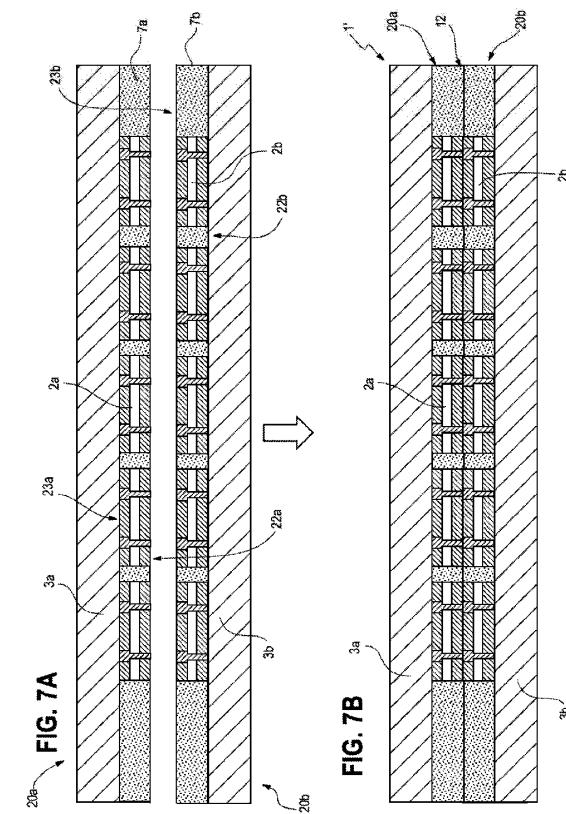

【図 7 A】直接接合する前の 2 つの対向する再構成ウェーハを示す図である。

【図 7 B】互いに直接接合された後の 2 つの対向する再構成ウェーハを示す図である。

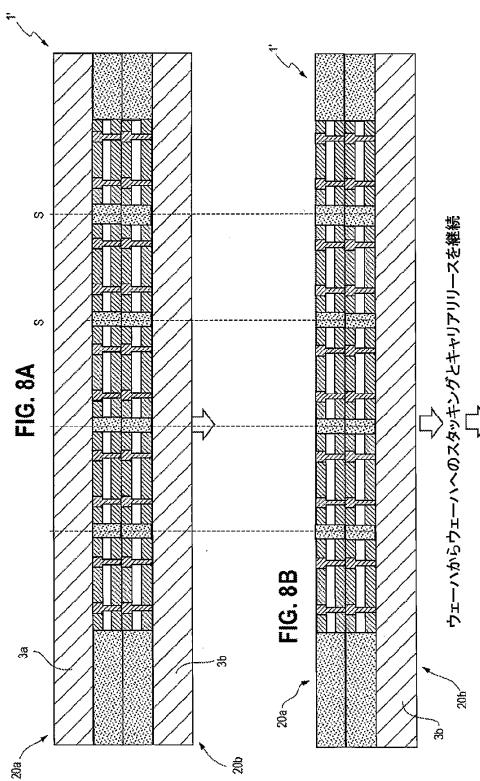

【図 8 A - B】種々の実施形態による、3 以上の再構成ウェーハを積層するための方法及び構造を示す図である。

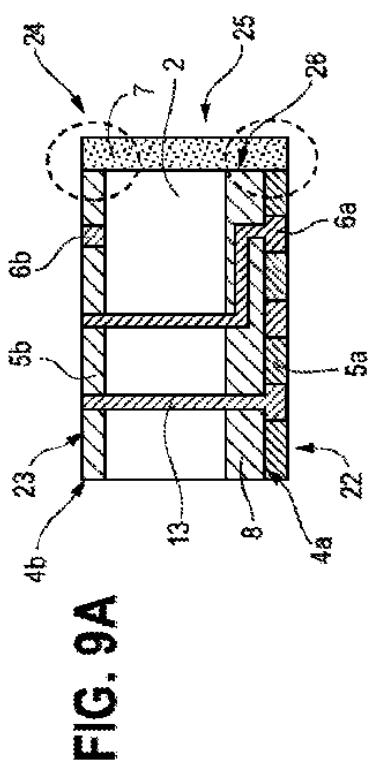

【図 9 A】種々の実施形態による、様々なフェースアップ接合構造を示す図である。

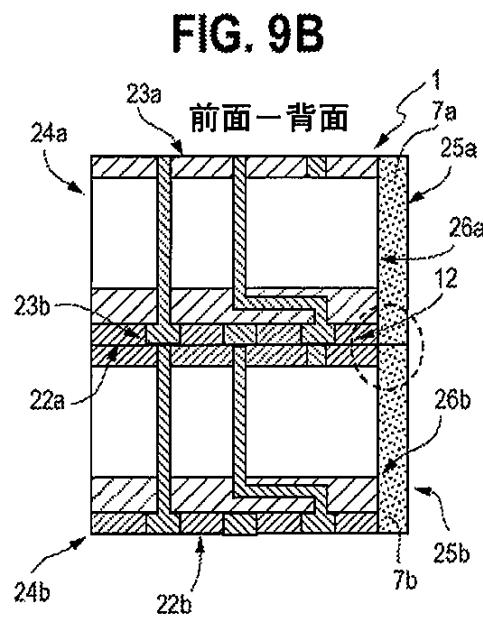

【図 9 B】種々の実施形態による、様々なフェースアップ接合構造を示す図である。

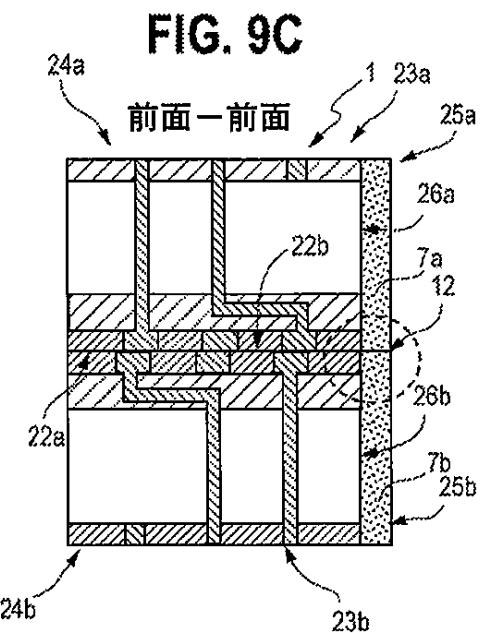

【図 9 C】種々の実施形態による、様々なフェースアップ接合構造を示す図である。

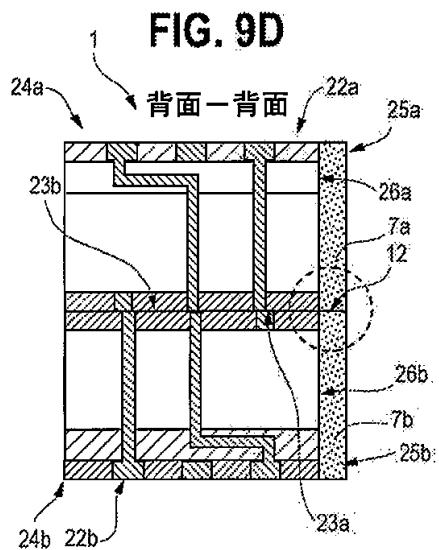

【図 9 D】種々の実施形態による、様々なフェースアップ接合構造を示す図である。

【図 9 E】種々の実施形態による、様々なフェースアップ接合構造を示す図である。

【図 9 F】種々の実施形態による、様々なフェースアップ接合構造を示す図である。

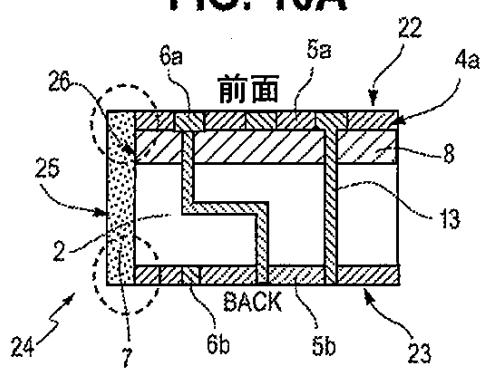

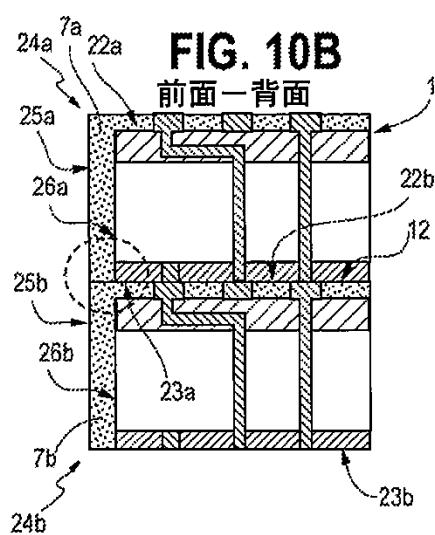

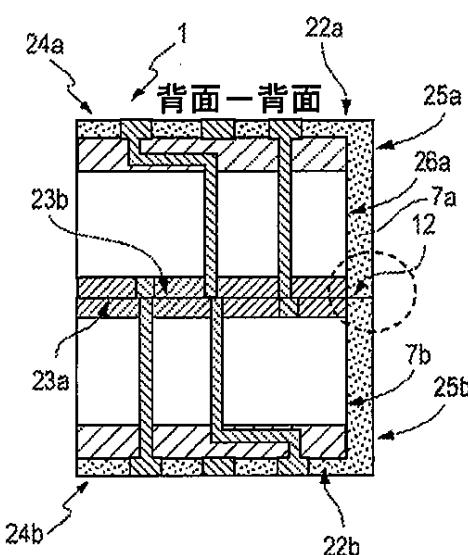

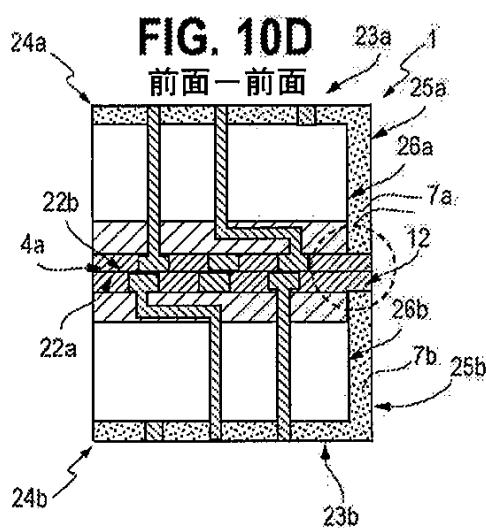

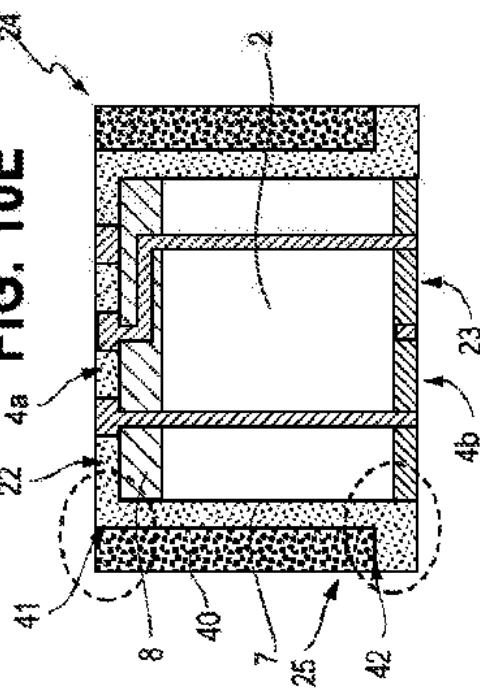

【図 10 A】種々の実施形態による、様々なフェースダウン接合構造を示す図である。

【図 10 B】種々の実施形態による、様々なフェースダウン接合構造を示す図である。

【図 10 C】種々の実施形態による、様々なフェースダウン接合構造を示す図である。

【図 10 D】種々の実施形態による、様々なフェースダウン接合構造を示す図である。

【図 10 E】種々の実施形態による、様々なフェースダウン接合構造を示す図である。

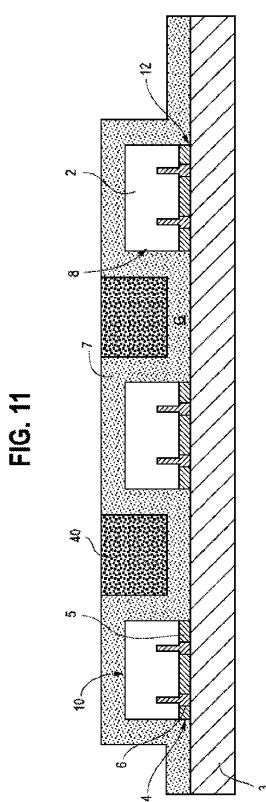

【図 11】追加の充填材料が第 2 の保護材料として機能することができ、隣接する素子間のギャップにおいて共形保護材料上に提供できる、別の実施形態を示す図である。

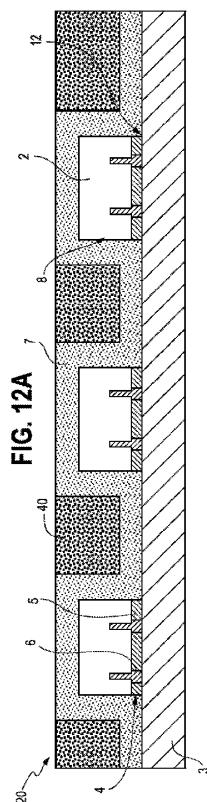

【図 12 A】種々の実施形態による再構成ウェーハを形成するための方法を示す図である。

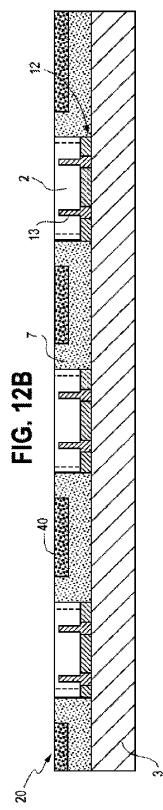

【図 12 B】種々の実施形態による再構成ウェーハを形成するための方法を示す図である。

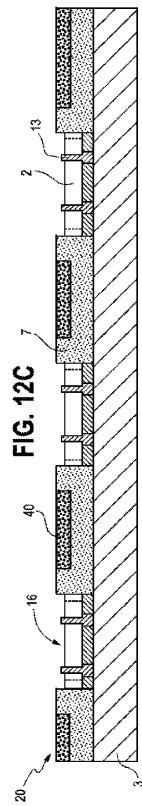

【図 12 C】種々の実施形態による再構成ウェーハを形成するための方法を示す図である。

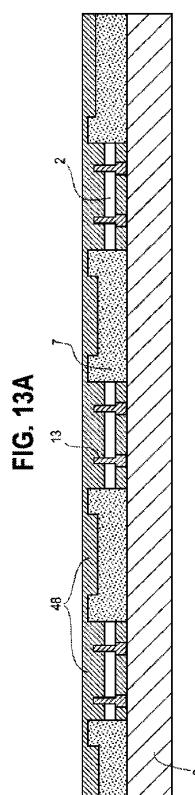

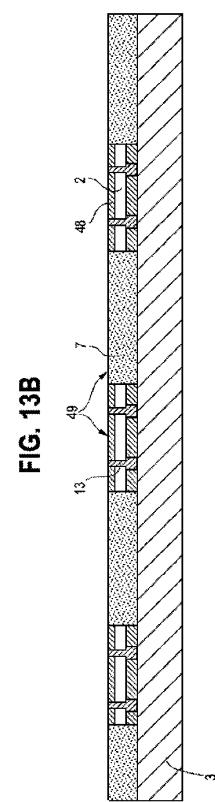

【図 13 A】種々の実施形態による再構成ウェーハを形成するための方法を示す図である。

【図 13 B】種々の実施形態による再構成ウェーハを形成するための方法を示す図である。

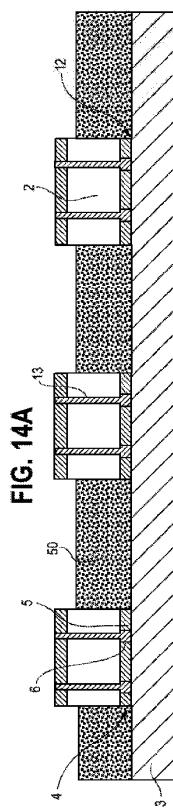

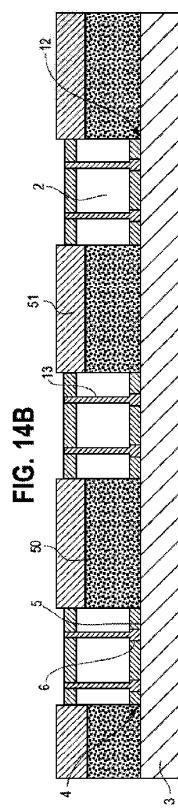

【図 14 A】キャリアに直接接合された隣接する素子間にモールド化合物を設けることができる、モールド化合物上に金属を設けることができる、別の実施形態を示す図である。

【図 14 B】キャリアに直接接合された隣接する素子間にモールド化合物を設けることができる、モールド化合物上に金属を設けることができる、別の実施形態を示す図である。

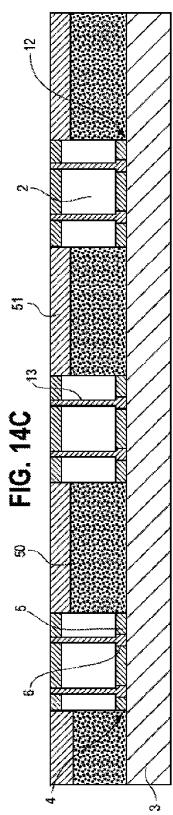

【図 14 C】キャリアに直接接合された隣接する素子間にモールド化合物を設けることができる、モールド化合物上に金属を設けることができる、別の実施形態を示す図である。

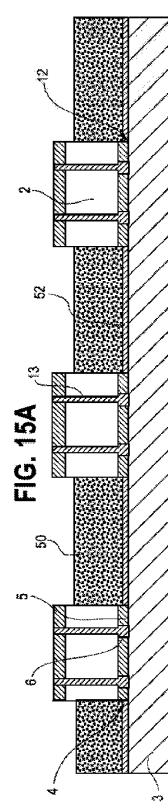

【図 15 A】キャリアに直接接合された隣接する素子間にモールド化合物を設けることができる、モールド化合物の両面に金属を設けることができる他の実施形態を示す図である。

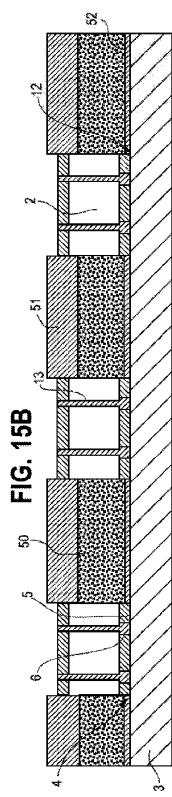

【図 15 B】キャリアに直接接合された隣接する素子間にモールド化合物を設けることができる、モールド化合物の両面に金属を設けることができる他の実施形態を示す図である。

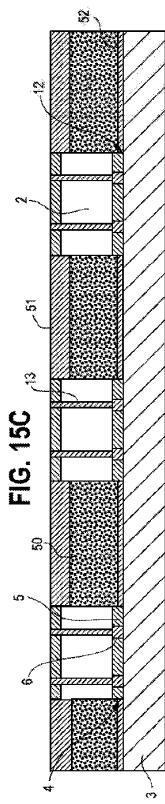

【図 15 C】キャリアに直接接合された隣接する素子間にモールド化合物を設けることができる、モールド化合物の両面に金属を設けることができる他の実施形態を示す図である。

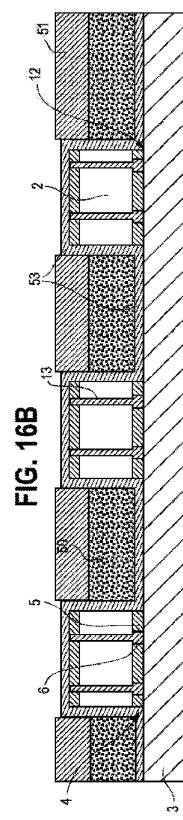

【図 16 A】モールド化合物とキャリアとの間に保護コーティング又は層を設けることができる別の実施形態を示す図である。

【図 16 B】モールド化合物とキャリアとの間に保護コーティング又は層を設けることができる別の実施形態を示す図である。

【図 16 C】モールド化合物とキャリアとの間に保護コーティング又は層を設けることができる別の実施形態を示す図である。

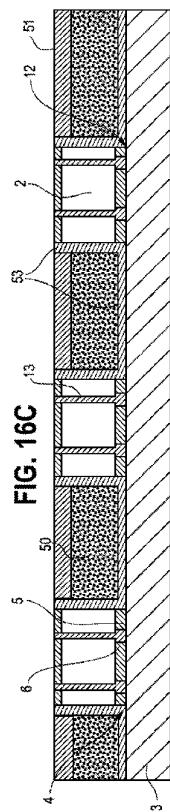

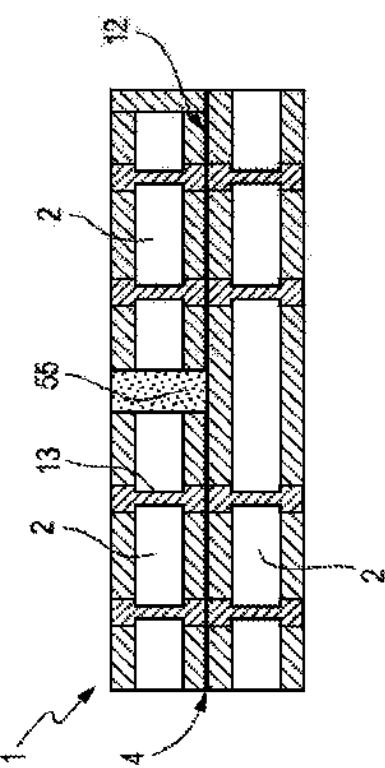

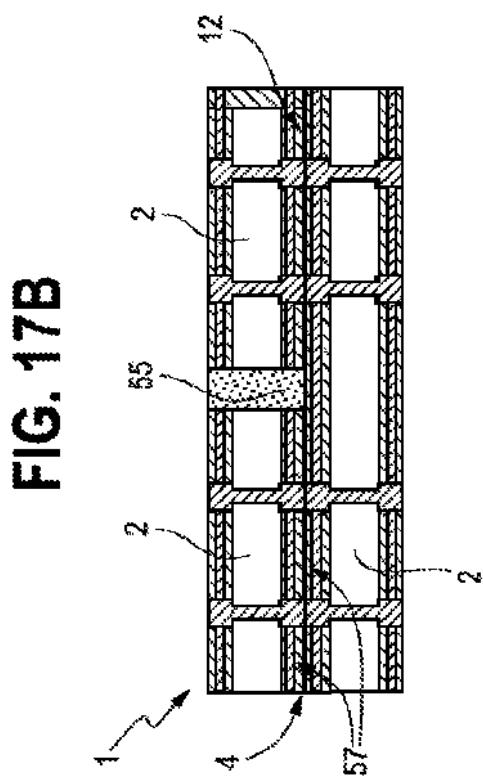

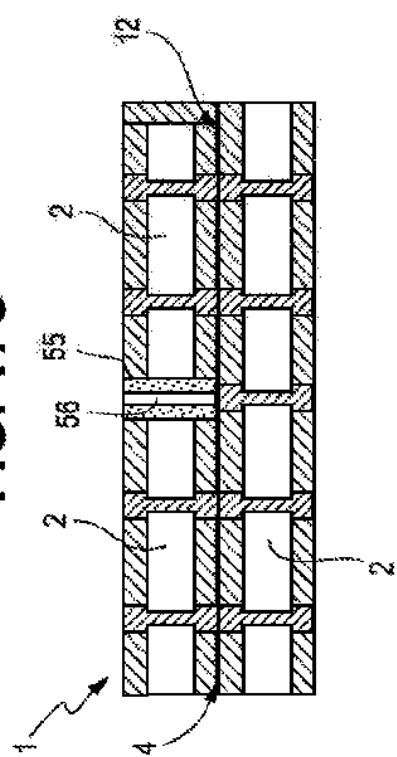

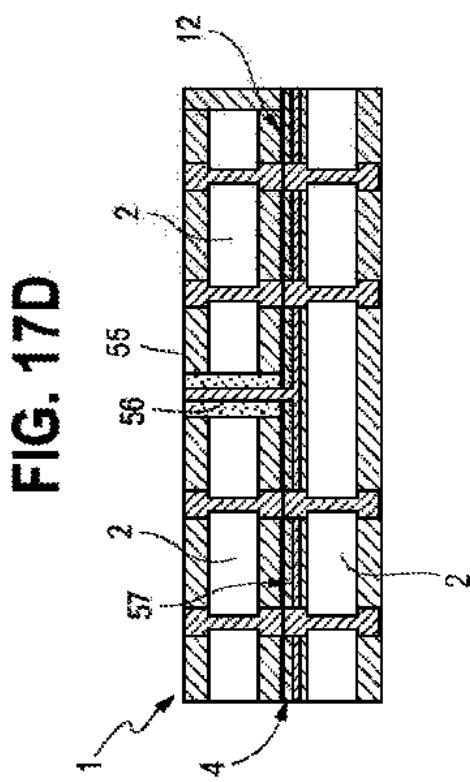

【図 17 A】本明細書に開示される方法で提供することができる追加の接合構造を示す図である。

10

20

30

40

50

【図17B】本明細書に開示される方法で提供することができる追加の接合構造を示す図である。

【図17C】本明細書に開示される方法で提供することができる追加の接合構造を示す図である。

【図17D】本明細書に開示される方法で提供することができる追加の接合構造を示す図である。

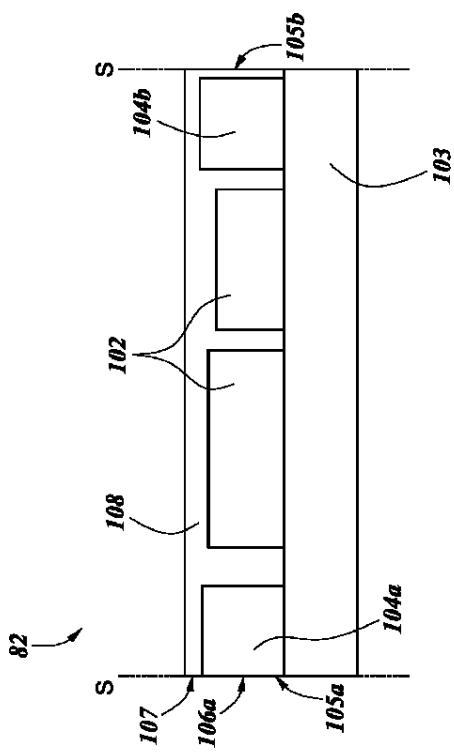

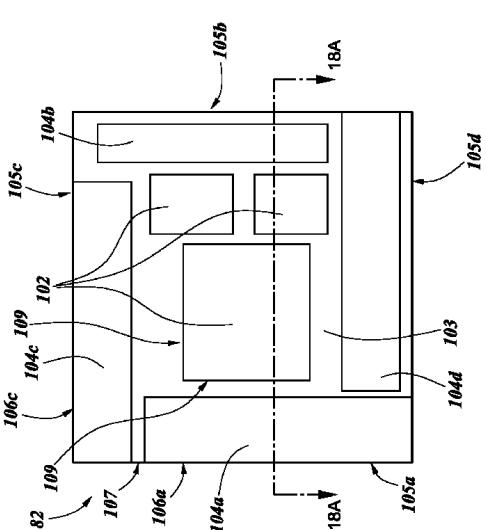

【図18A】別の実施形態による集積デバイスパッケージの概略側断面図である。

【図18B】説明を容易にするためにモールド化合物が隠された、図18Aの集積デバイスパッケージの概略上面図である。

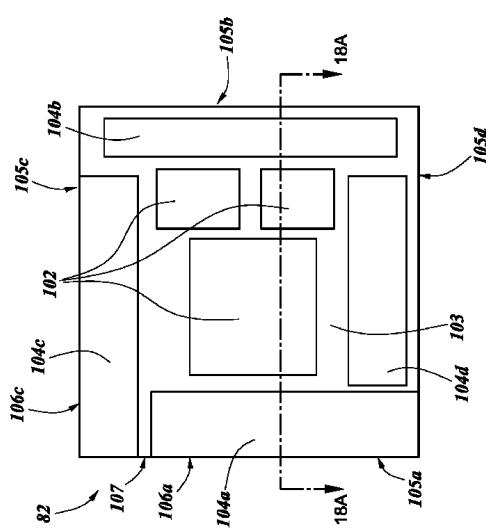

【図18C】応力補償素子間の増加した横方向の重なりを含む集積デバイスパッケージの概略上面図である。 10

【図19】種々の実施形態による、1又は2以上の接合構造を組み込んだシステムの概略図である。

#### 【発明を実施するための形態】

##### 【0007】

本明細書に開示される種々の実施形態は、第1の側面と第1の側面の反対側にある第2の側面とを有する第1の素子（例えば、第1の集積デバイスダイ）を含む接合構造に関する。この接合構造は、第1の側面と、第1の側面の反対側にある第2の側面を有する第2の素子（例えば、第2の集積デバイスダイ）を含むことができる。第2の集積デバイスダイの第1の側面は、接合界面に沿って接着剤を介在させることなく、第1の集積デバイスダイの第1の側面に直接接合することができる。第1及び第2の集積回路ダイの周縁部（例えば、それぞれの側壁）の周りには、保護材料を配置することができる。保護材料は、第1の集積デバイスダイの第2の側面から第2の集積デバイスダイの第2の側面まで延びることができる。種々の実施形態において、保護材料の一部は、隣接する第1の集積デバイスダイ又は素子間のギャップ内に配置することができる。幾つかの実施形態では、保護材料は、二酸化ケイ素、窒化ケイ素、ポリシリコン、アモルファスシリコンなどの無機誘電体を含むことができる。 20

##### 【0008】

本明細書に開示された実施形態は、キャリアとして機能するウェーハ又は基板が、複数の集積デバイスダイと集積デバイスダイ上の保護材料（1又は複数の保護層を含むことができる）とを備えたウェーハレベルプロセスを含むことができる。ダイ及び保護材料は、再構成ウェーハの少なくとも一部を形成することができ、再構成ウェーハは、別の再構成ウェーハに接合（例えば、接着剤なしで直接接合）することができる。接合された再構成ウェーハは、例えば、キャリアを除去した後、複数の接合構造を形成するためにシンギュレーションすることができる。接合構造は、幾つかの実施形態において、パッケージング構造を含むことができる。本明細書で使用されるように、直接接合相互接続（DBI（登録商標））は、高密度に分散した導電性コンタクトが接着剤を介さずに互いに接合された接合構造を含むことができる。様々な実施形態において、周囲の誘電体又は非導電性材料もまた、接着剤を介さずに直接接合することができる。ZiBond（登録商標）プロセスは、接着剤を介さずに非導電性材料間の直接接合を含むことができる。DBIとZiBondのプロセス及び構造の例は、少なくとも米国特許第9,391,143号、第10,141,218号、第10,147,641号、第9,431,368号、及び第7,126,212号に記載されており、これらの各々の内容全体は、あらゆる目的で引用により全体が本明細書に組み込まれる。キャリア上に取り付けられた各シンギュレーションダイは、取り付け前にテストすることができ、再構成ウェーハ内の全てのダイを保証済みの良品ダイ（Known Good Dies（KGD））にすることができる。 40

##### 【0009】

図1A-1Cは、様々な直接接合プロセスにおける犠牲キャリア3の使用を概略的に示している。図示のように、幾つかの実施形態において、素子2は、接着剤なしでキャリア3に直接接合することができる。本願において、素子2（又は本明細書に記載される他

10

20

30

40

50

の任意の素子)は、半導体素子(例えば、集積デバイスダイ)、光学素子など、何れかの好適なタイプの素子を含むことができる。キャリア3は、1又は2以上のロジック又は処理デバイスを有するキャリア、及び/又は処理中のある時点で除去される犠牲キャリア(例えば、アクティブな処理回路を有しないキャリア)など、何れかの好適なタイプのキャリアを含むことができる。

#### 【0010】

素子2は、前面9と、前面9に対向する背面10とを含むことができる。種々の実施形態において、前面9は、素子2内に形成されたアクティブ回路又はデバイスに最も近い表面を含むことができる。第1の前面接合層4は、素子2の前面9に設けることができる。接合層4は、素子2の前面9に示されているが、接合層は、接合のために背面10にも又は代替的に設けることができる。接合層4は、非導電性フィールド領域5内に配置された又は非導電性フィールド領域5によって囲まれた1又は複数のコンタクトパッド6を含むことができる。幾つかの実施形態では、コンタクトパッドは、銅を含むことができるが、他の導電性材料が適している。幾つかの実施形態では、非導電性フィールド領域は、酸化シリコン、窒化シリコンなどの誘電体を含むことができる。背面10は、アクティブ回路又はデバイス含んでもよいし、含まなくてもよい。種々の実施形態において、素子2は、側面8を有する単結晶素子(単結晶デバイスダイのような)を含むことができる。側面8は、例えば、ソウマーキング(Saw Marking)、エッチングパターンなど、シンギュレーションプロセスを示すマーキングを含むことができる。

#### 【0011】

上記で説明し、図1Aに示すように、素子2(例えば、ダイ)は、接合界面12に沿って接着剤を介在させることなく、キャリア3に直接接合することができる。前面接合層4は、上記で説明したように、接合のために調製することができる。例えば、前面接合層4は、極めて低い表面粗さに研磨され、誘電体対誘電体の直接接合を強化するように処理することができる。幾つかの実施形態では、接合される表面は、接合前に、適切な種で終端処理されて活性化することができる。例えば、幾つかの実施形態において、接合される表面は、活性化のために極めて軽くエッチングされて、窒素含有溶液に曝露され、窒素含有種で終端することができる。一例として、接合される表面は、極めて軽いエッチングの後にアンモニア浸漬及び/又は窒素含有プラズマ(別個のエッチングを伴うか又は伴わない)に曝されてもよい。

#### 【0012】

表面が調製されると、素子2の非導電性フィールド領域5をキャリア3の対応する非導電性領域と接触させることができる。活性化された表面の相互作用により、素子2の非導電性領域5は、接着剤を介在させることなく、外部圧力を加えることなく、電圧を加えることなく、室温でキャリア3の対応する非導電性領域と直接接合させることができる。種々の実施形態において、非導電性領域の接着力は、ファンデルワールス接合よりも大きい共有結合とすることができます。幾つかの実施形態では、素子2の非導電性フィールド領域のみが、キャリア3の対応する非導電性領域に直接接合される。しかしながら、他の実施形態では、素子2のコンタクトパッド6をキャリア3の対応する導電性コンタクトに直接接合することができ、非導電性領域5もまたキャリア3の非導電性領域に直接接合することができる。このような実施形態において、コンタクトの直接接合は、キャリア3に対する素子2のアライメントを改善することができる。本明細書に開示される実施形態では、直接接合の使用は、介在する接着剤を利用する実施構成と比較して、組立中の動きを低減することができる。

#### 【0013】

図1Bに示すように、保護材料7は、素子2の少なくとも周縁部又は側面8の周りを含む、素子2の少なくとも一部の上に施工することができる。幾つかの実施形態では、保護材料7は、側面8に沿って及びキャリア3の上面の上に堆積させることができます。保護材料7は、酸化シリコン、窒化シリコン、ポリシリコン、アモルファスシリコン、金属などの1又は2以上の無機層を含む1又は2以上の保護層を含むことができる。

10

20

30

40

50

### 【0014】

図1Cに示すように、キャリア3は、何れかの好適な方法で素子2及び保護材料7から除去することができる。図示された実施形態では、キャリア3は、ナノ酸化物層11を有するシリコン基板又は素子を含むことができ、これは、本明細書で使用する場合、ネイティブシリコン酸化物層及び熱シリコン酸化物層のうちの少なくとも1つを含むことができる。本明細書で開示される実施形態の各々は、ナノ酸化物層11を有するこのようなキャリアを利用することができます。幾つかの実施形態では、キャリア除去プロセスにおいて、キャリア3は、シリコンナノ酸化物層11をエッチングストップとして用いて選択的にエッチングすることができる。幾つかの実施形態では、キャリア3のシリコン基材を除去した後に、ナノ酸化物層11の少なくとも一部を残存させることができる。他の実施形態では、キャリア3の全体（例えば、シリコン基材及びナノ酸化物層11）を除去することができる。ナノ酸化物層11を利用する実施形態では、素子2は、接合のために平坦化することができるが、キャリア3は直接接合の前に平坦化されなくてもよい。他の実施形態では、素子2とキャリア3の両方を直接接合のために平坦化することができる。本明細書に記載の直接接合及びその後のキャリア3の除去は、有利には、追加の直接接合工程を含む所望の更なる処理のために再構成ウェーハに平坦面を残すことができる。これに対し、犠牲接着層や一時接着層（テープやフィルムなど）上に形成された再構成ウェーハは、平坦な表面を確実に提供せず、例えば、その後の積層用のダイの直接接合において、その後のアライメントの問題を引き起こす可能性がある。このような直接接合による積層は、第1の再構成ウェーハ上の個々の第2のダイを直接接合する方法、又は第2の再構成ウェーハ内の複数の第2のダイを同時に接合する方法によることができる。

10

20

### 【0015】

有利なことに、図1A-1Cの実施形態は、改善されたアライメント精度で直接接合するためのウェーハの再構成を可能にすることができる。例えば、図1A-1Cには1つの素子2又はダイのみが示されているが、複数のダイのアレイを提供することができますを理解すべきであり、以下に示される。接着剤を用いて素子2（例えば、ダイ）をキャリア3に接合する他の用途では、例えば、加熱中又は加熱後、或いは接合のための配置中に接着剤が移動又は移行することに起因して素子2又はダイがキャリア3に対してずれることがある。このような位置ずれは、その後で接合される構造に対して位置ずれを生じさせ、接合された構造体の性能に悪影響を与える可能性がある。本明細書に開示される実施形態は、キャリア3との直接的な接合相互接続を提供することによって位置ずれを有利に低減することができ、これは、素子2又はダイを、その後の処理、例えば、素子2の上に保護材料7（無機又は有機）を設けること、又は他の任意の好適な処理のためにキャリア3に対して有效地に固定する役割を果たすことができる。

30

### 【0016】

図2は、ウェーハなどのキャリア3に直接接合された複数の素子2を示す図である。特に断らない限り、図2中の参照数字は、図1A-1Cの同番号の構成要素と同一又はほぼ類似する構成要素を表すことができる。図2において、各素子2は、対応するコンタクトパッド6の背面に接続された1又は2以上の導電性ビア13を含むことができる。図2に示すように、導電性ビアは、当初、コンタクトパッドから上方に延び、素子2の本体内で終端することができる。直接接合後、ダイ又は素子2は、複数のダイシングされた又はシンギュレーションされた素子2にダイシング又はシンギュレーションすることができる。本明細書で説明したように、ナノ酸化物層11を用いたシリコン基板の除去は、その後の直接接合のために実質的に平滑な表面を残すことができる。

40

### 【0017】

図3A-3Cは、接着剤を介さずに素子2（例えば、集積デバイスのダイ）をキャリア3（ナノ酸化膜11付きシリコン基板など）に直接接合した様々な例を示している。図3Aは、素子2間の比較的広い離隔距離又はギャップGを示し、図3Bは、素子2間の比較的狭いギャップGを示している。図3Cは、比較的狭いギャップGを間に有して、アクティブ素子2又はダイの間に配置された追加のダミー素子2'又はダイを示している。図3B

50

及び図3Cの狭いギャップGを設けることで、その後のステップでギャップGを充填するのに使用される保護材料7の量を有益に減らすことができ、ギャップGを共形（conformal）に充填することが可能になる。更に、図3A及び図3Bに示すように、キャリア3の上面には1又は2以上のアライメント特徴部14を設けることができる。アライメント特徴部14は、キャリア3上に選択的に配置されて、素子2の正確な配置を支援することができる。

#### 【0018】

図4Aは、キャリア3に直接接合され、素子2の上及び素子2間のギャップG内に保護材料7が施工された複数の素子2の概略側面図である。図4Aでは、素子2は全てアクティブ集積デバイスダイであるように図示されている。図4Bでは、一部の素子は、半導体材料（例えば、シリコン）の不活性ブロックなどのダミー素子2'を含む。図4A及び図4Bでは、ギャップG内及び素子2の上面（図4A-4Bでは背面10である）上の周縁部（例えば、側面8）の一部の周りを含む、素子2の一部上に保護層7（無機保護層など）を設けることができる。保護材料7には、ボイド又は不連続部などの継ぎ目15が存在してもよい。

10

#### 【0019】

保護層7は、例えば、無機又は有機保護層を含む、1又は複数の保護層を含むことができる。図示の実施形態では、例えば、保護層7は、酸化シリコン、窒化シリコン、ポリシリコン、アモルファスシリコン、又は金属などの無機層を含むことができる。他の実施形態では、保護材料7の少なくとも一部は、モールド化合物又はエポキシなどの有機材料を含むことができる。幾つかの実施形態では、保護材料7は、共形層及びギャップ充填層の両方を含む。有益には、保護材料7は、その後の直接接合プロセス中に素子2がシフトしないように、素子2をキャリア3に取り付けるのを支援することができる。また、保護材料7は、研磨及び他の処理時に素子2を保護し、ダイの損傷（例えば、チッピング）を防止することができる。接合後の薄肉化及び/又はシンギュレーション工程と組み合わせて使用するために、キャリア上に直接接合された隣接するダイの上及び間に保護材料7を設ける構造及び工程の例は、米国特許第10,204,893号に開示されており、その全内容は、引用により全体が本明細書に組み込まれる。

20

#### 【0020】

図5A-5Cは、再構成ウェーハ20を形成するための一連の処理ステップを示す。再構成ウェーハ20は、後続のステップにおいて別の再構成ウェーハに又は他の基板に接合（例えば、直接接合）することができる。図5Aにおいて、共形保護材料7の上面は、例えば、エッティング、ラッピング、研削、研磨等によって除去することができる。幾つかの実施形態では、保護材料7の除去は、素子2の背面10の一部も除去することができる。他の実施形態では、除去ステップは、素子2の背面10で終端させることができる。

30

#### 【0021】

図5Bを見ると、背面10からの素子2の一部は、エッティング、ラッピング、化学機械研磨（CMP）、又は他の何れかの好適な方法によって除去され、素子2の薄化背面10'を形成することができる。図5Aに示すように、この除去ステップにより、素子内に形成された導電性貫通基板ビア（TSV）13又は他の電気的相互接続を露出させることができる。また、この除去ステップにより、素子2の薄化背面10'と保護材料7の側壁とによって少なくとも部分的に定められるキャビティ16を形成することができる。図5Cでは、非導電性層18（例えば、第2の酸化物層）を素子2の薄化背面10'上と露出したビア13の周りに設けることができる。幾つかの実施形態では、設けられた非導電性層18（例えば、酸化シリコン）は、ラッピング又は研磨されて、平坦面を生成し、非導電性層18がビア13及び保護材料の露出した端部に対して略平面的であることを保証することができる。

40

#### 【0022】

図5Cにおいて、再構成ウェーハ20は、他の再構成ウェーハに接合（例えば、直接接合）されるように構成された前面22を含むことができる。再構成ウェーハ20はまた、

50

背面 23 を含むことができる。図 5 C の再構成ウェーハ 20 では、保護材料 7 は、隣接する素子 2 の間に配置することができ、再構成ウェーハ 20 の前面 22 からキャリア 3 の上面まで延びることができる。垂直界面 19 は、素子 2 上の非導電性層 18 と保護材料 7 との間に定めることができる。同様に、垂直界面 21 は、接合層 4 と保護材料 7 との間に定めることができる。

#### 【 0 0 2 3 】

図 6 は、別の再構成ウェーハ又は基板に直接接合するように構成された第 2 の接合層 4 b を有する再構成ウェーハの概略側断面図である。図 6 において、図 1 A - 5 の第 1 の接合層 4 、コンタクト 6 、及び非導電性フィールド領域 5 は、それぞれ参照数字 4 a , 6 a , 5 a として番号が付け直されている。図 6 に示すように、幾つかの実施形態において、第 2 の接合層 4 b 、例えば、交互する導電性コンタクト 6 b 及び非導電性接合部分（例えば、フィールド領域 5 b ）を有する DBI 層を非導電性層 18 ( 例えば、第 2 の酸化物層 ) 上に設けて、必要に応じて追加の接合接続を容易にし、DBI アライメントを助長する接合パッドを提供することができる。従って、図 6 において、第 2 の接合層 4 b は、再構成ウェーハ 20 の複数（例えば、全て）の素子 2 にわたって延びることができる。第 2 の接合層 4 b と非導電性層 18 との間、及び第 2 の接合層 4 b とその下の保護材料 7 との間に水平界面 19 を形成することができる。

#### 【 0 0 2 4 】

図 7 A - 7 B において、2つの対向する再構成ウェーハ 20 a , 20 b を設けることができ、直接接合して接合された再構成ウェーハ 1' のペアを形成することができる。参照数字には、再構成ウェーハ 20 a 又は 20 b とのそれぞれの関連性を示すために、「 a 」又は「 b 」が付されている。図 7 A は、直接接合する前の 2 つの対向する再構成ウェーハ 20 a , 20 b を示す。図 7 B は、互いに直接接合した後の対向する 2 枚の再構成ウェーハ 20 a , 20 b を示している。キャリア 3 a , 3 b に直接接合を用いることで、導電面と非導電面のダイ間直接接合に必要なダイ接合面の平坦性が得られる。しかしながら、他の実施形態では、キャリアを使用しなくてもよく、代わりに再構成ウェーハは、キャリアの使用なしでモールド化合物又は封入材料に少なくとも部分的に埋め込まれた素子（例えば、ダイ）を含むことができる。図 7 B では、非導電性保護層は、接合界面 12 に沿って接着剤なしで互いに直接接合することができる。再構成ウェーハ 20 a , 20 b の他の非導電性フィールド領域（接合層 4 a , 4 b 、非導電層 8 などの非導電性フィールド領域 5 a , 5 b など）は、接着剤で互いに接合することもできる。更に、導電性コンタクト 6 a , 6 b は、接着剤なしで直接接合することができる。幾つかの実施形態では、導電性コンタクト 6 a , 6 b の一部又は全部は、最初は、接合面に対して凹状にすることができる。接合されたウェーハ 20 a , 20 b を加熱して、コンタクト 6 a , 6 b を拡張させ、電気接觸を形成させることができる。加熱後、コンタクト 6 a , 6 b 間の界面は、接合界面 12 と同じ平面上にない場合がある。

#### 【 0 0 2 5 】

図 8 A - 8 B に示すように、追加の再構成ウェーハ 20 a , 20 b を設けて、任意の数の積層再構成ウェーハ I' を提供することができる。積層再構成ウェーハ I' は、シンギュレーションストリート S に沿ってシンギュレーションして、複数の接合構造 1 を提供することができる。何れかの好適な数の再構成ウェーハ 20 a , 20 b を提供して、積層再構成ウェーハ I' を形成することができ、これらもまた、何れかの好適な数の接合構造 1 を形成するためにシンギュレーションすることができる。シンギュレーションは、図示のようにキャリア 3 を除去する前（犠牲の場合）、又はシンギュレーションの後とすることができる。幾つかの実施形態では、図 8 A に示すように、キャリア 3 a , 3 b の両方は、シンギュレーションの前に除去されなくてもよい。幾つかの実施形態では、図 8 B に示されるように、一方のキャリア 3 a は、シンギュレーションの前に除去することができる。他の実施形態では、両方のキャリア 3 a , 3 b は、シンギュレーションの前に除去することができる。本明細書で説明するように、例えばエッチングプロセスを用いてキャリア 3 a 及び / 又は 3 b を除去すると、追加の直接接合を促進するためにナノ酸化物層 11 を残すこ

とができる。

#### 【0026】

図9A - 9F及び10A - 10Eは、本明細書に記載の方法から生じ得る様々なフェースアップ又はフェースダウン接合構造Iを示す。図9A - 9F及び10A - 10Eに示される接合構造Iは、シンギュレーション再構成された集積デバイスダイなどのシンギュレーション再構成素子24を含むことができる。シンギュレーション再構成素子24は、種々の実施形態によるシンギュレーション再構成ウェーハ20からどのような構造が得られるかを示すために、例示の目的で図9A、9E、及び9Fに示されている。図9A - 9F及び10A - 10Eに示すように、アクティブ回路又はデバイスに最も近い表面は、接合構造1の前面22とすることができます、前面22と反対側の表面は、背面23とすることができます。個別にピックアップして配置されたダイ又は素子とは異なり、図示の実施形態の直接接合再構成素子24は、共平面側面を有すると共に、接着剤を介さずに、導電性(例えば金属)面と非導電性(例えば、直接接合を助けるために窒素及び/又はフッ素含有物を含む酸化物のような無機誘電体)面との間の直接接合界面12を有することができる。

#### 【0027】

図9A - 9Fは、フェースダウン接合構造の例を示している。図9Aを見ると、シンギュレーションされた再構成素子24は、素子2と、素子2の薄肉化された背面10'に配置された非導電性層18と、前面22及び背面23にそれぞれある接合層4a, 4bと、を含むことができる。図9Aに示すように、保護材料7は、再構成素子24の背面23から前面22まで延びることができる。従って、図9Aの実施形態では、シンギュレーションされた再構成素子24は、保護材料の外側露出表面によって定められた側壁25を有することができる。保護材料7及び素子2と、非導電性層8と、第1及び第2の接合層4a, 4bとの間に垂直界面26を定めることができる。図9Aの配置では、保護材料7は、これに応じて、保護材料7が提供される前に施工することができる接合層4a, 4bに当接している。他の実施形態では、図6に関連して説明したように、接合層4a, 4bの1又は2以上は、側壁25が保護材料7と接合層4a及び/又は4bの側縁とを含むように保護材料7の上に延びることができる。

#### 【0028】

図9Bは、再構成素子24aの前面22aが接着剤を介在させずに再構成素子24bの背面23bに直接接合されて接合構造1を形成する前面-背面接合配置を示す。図9Bにおいて、保護材料の第1の部分7aは、再構成素子24aの背面23aから接合界面12まで延びることができる。保護材料の第2の部分7bは、接合界面12から再構成素子24bの前面22bまで延びることができる。

#### 【0029】

図9Cは、再構成素子24aの前面22aが接着剤を介在させずに再構成素子24bの前面23aに直接接合されて接合構造1を形成する、前面-前面接合配置を示す。図9Cにおいて、保護材料の第1の部分7aは、再構成素子24aの背面23aから接合界面12まで延びることができる。保護材料の第2の部分7bは、接合界面12から再構成素子24bの背面23bまで延びることができる。

#### 【0030】

図9Dは、再構成素子24aの背面23aが接着剤を介在させずに再構成素子24bの背面23bに直接接合されて接合構造1を形成する、背面-背面接合配置を示す図である。図9Dにおいて、保護材料の第1の部分7aは、再構成素子24aの前面22aから接合界面12まで延びることができる。保護材料の第2の部分7bは、接合界面12から再構成素子24bの前面22bまで延びることができる。

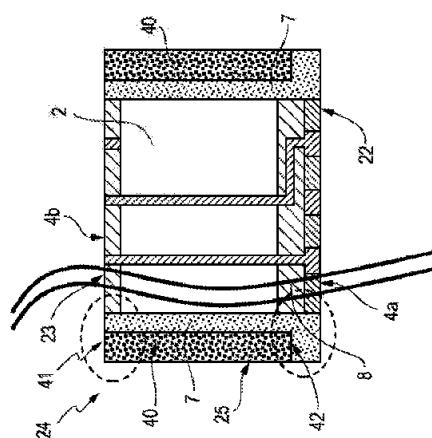

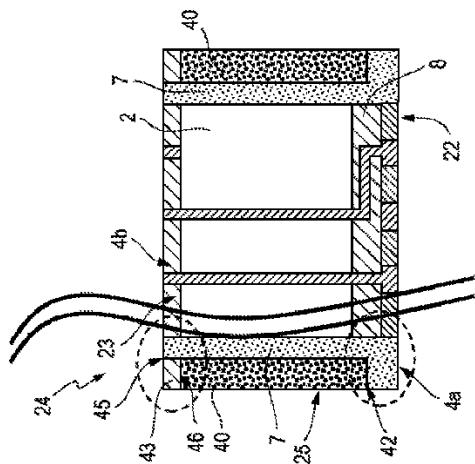

#### 【0031】

図9E及び9Fは、第2の保護層40を利用するシンギュレーションされた再構成素子24の追加の例を示している。図9E及び9Fの再構成素子24を形成する方法に関する追加の詳細は、例えば、図11 - 図12Cにおいて以下に見出すことができる。図9Eの実施形態では、例えば、第2の保護材料40は、保護材料7の上に施工することができる

。図9Eにおいて、第2の保護材料40は、接合層4bに隣接する再構成素子24の背面23で露出することができる。更に、保護材料7は、接合層4aに隣接し且つ第2の保護層40の下にある前面22において露出することができる。従って、図9Eにおいて、側壁25は、第1及び第2の保護材料7, 25の間の水平界面42を含むことができる。更に、背面23において、第1及び第2の保護材料7, 25の間に垂直界面41を設けることができる。

#### 【0032】

図9Fの実施形態では、第2の保護材料40も保護材料7の上に施工することができる。しかしながら、図9Eの実施形態とは異なり、図9Fでは、第3の保護層43を第2の保護材料40の上に設けることができる。第3の保護層43は、再構成素子24の背面23で露出していてもよい。従って、図9Fでは、保護材料7と第3の保護材料43との間に垂直界面45を設けることができる。水平界面46は、第2の保護材料40と第3の保護材料43との間に設けることができる。

10

#### 【0033】

図10A-10Eは、フェースアップ接合構造1の例を示す図である。特に断らない限り、図10A-10Eの参照数字は、図9A-9Fの参照数字と同じ又はほぼ類似した構成要素を指すことができる。図10Aを参照すると、シンギュレーションされた再構成素子24は、フェースアップ方向で示されている。図10B-10Dにおいて、それぞれの再構成素子24a, 24bは、互いに直接接合されて接合構造を形成している。

20

#### 【0034】

図9Bと同様に、図10Bは、再構成素子24aの前面22aが接着剤を介さずに再構成素子24bの背面23bに直接接合されて接合構造1を形成する、前面-背面接合配置を示す。図10Bにおいて、保護材料の第1の部分7aは、再構成素子24aの背面23aから接合界面12まで伸びることができる。保護材料の第2の部分7bは、接合界面12から再構成素子24bの前面22bまで伸びることができる。

#### 【0035】

図10Cは、再構成素子24aの背面23aが接着剤を介在させずに再構成素子24bの背面23bに直接接合されて接合構造1を形成する、背面-背面接合配置を示す。図10Cにおいて、保護材料の第1の部分7aは、再構成素子24aの前面22aから接合界面12まで伸びることができる。保護材料の第2の部分7bは、接合界面12から再構成素子24bの前面22bまで伸びることができる。

30

#### 【0036】

図10Dは、再構成素子24aの前面22aが接着剤を介在させずに再構成素子24bの前面22bに直接接合されて接合構造1を形成する、前面-前面接合配置を示す。図10Dにおいて、保護材料の第1の部分7aは、再構成素子24aの背面23aから接合界面12まで伸びることができる。保護材料の第2の部分7bは、接合界面12から再構成素子24bの背面23bまで伸びることができる。図10Dにおいて、接合層4aは、保護材料7a, 7bの上に伸び、側壁25上に露出させることができる。図6に関連して上記で説明したように、幾つかの実施形態では、接合層4aは、再構成ウェーハがシンギュレーションされるときに、接合層4aが側壁で露出して側壁25で保護材料7と同一平面になるように、保護材料7の上にウェーハを横断して設けることができる。

40

#### 【0037】

図10Eは、保護材料7の側面及び上面上に配置された第2の保護材料40を有する、シンギュレーションされた再構成素子24を示す図である。図9E及び9Fの実施形態とは異なり、図10Eでは、第1の前面接合層4aは、第2の保護材料40と共に平面又は同一平面とすることができます。第2の背面接合層4bは、保護材料7と共に平面であるか又は同一平面上にあることができる。

#### 【0038】

図11は、追加の充填材料が第2の保護材料40として機能することができ、隣接する素子2間のギャップGにおいて共形保護材料7上に設けられ得ることを除いて、上述のも

50

のと同様の別の実施形態を例示している。保護材料 7 は、素子 2 の背面 10 及び側面 8 上、並びにキャリア 3 の上面上に共形に堆積させることができる。共形保護材料 7 は、素子 2 の側面 8 上に配置された保護材料 7 の部分間にギャップ G を有することができる。第 2 の保護材料 40 は、ギャップ G を充填する役割を果たすことができる。第 2 の充填保護材料 40 は、有機材料又は無機材料を含む何れかの好適な材料を含むことができる。

#### 【 0 0 3 9 】

図 12 A - 12 C は、種々の実施形態による、再構成ウェーハ 20 を形成するための方法を示す図である。図 12 A は、第 2 の保護材料 40 の追加の部分が外側素子 2 の端部に設けられることを除いて、図 11 と概ね同様である。図 12 B では、保護材料 7 の一部及び第 2 のフィラー保護材料 40 の一部を除去して、略平面的な面を提供することができる。種々の実施形態において、例えば、フィラー保護材料及び共形保護材料 40, 7 のそれぞれの部分は、エッティング、ラッピング、研削、化学機械研磨 (C M P) 等によって除去することができる。図 12 C では、例えばエッティング、ラッピング、C M P 等によって素子 2 又はダイのバルク半導体材料（例えば、シリコン）の一部を除去して、キャビティ 16 を形成し、導電性ビア 13 を露出させることができる。共形保護材料及び / 又はギャップ充填保護材料は、素子 2（例えば、集積デバイスダイ）の熱膨張係数が 5 p p m / 内である熱膨張係数を有することができる。

#### 【 0 0 4 0 】

図 13 A において、図 12 C に示す構造から第 2 のフィラー保護材料 40 を除去することができ、素子 2 及び露出したビア 13 の上に追加の保護材料 48 を設けることができる。図 13 B において、設けられた追加の保護材料 48 及び保護材料 7 の一部を除去又は平坦化して、上面に露出したビアを有する接合面 49 を形成することができる。

#### 【 0 0 4 1 】

図 14 A - 14 C は、接着剤なしでキャリア 3 に直接接合された隣接する素子 2 の間にモールド化合物 50 を設けることができる別の実施形態を示している。図 14 A では、ビア 13 が背面に露出されているように示されているが、他の実施形態では、上記に例示したように、ビア 13 を埋設することができる。図 14 B に示すように、モールド化合物 51 の上に金属 51（例えば、銅）は、モールド化合物 51 の上に設けることができる。例えば、種々の実施形態において、金属 51 は、無電解メッキプロセス、スパッタリングプロセス、又は任意の他の適切な方法を用いて提供することができる。図 14 C に示すように、金属 51 は、例えば、化学機械研磨 (C M P)、又は任意の他の適切な方法によって平坦化することができる。一部の実施形態では、モールド化合物に有機材料を用いる構造では、C M P による十分な平滑性（例えば、5 nm 未満など）の平坦化が困難な場合がある。金属 51（銅など）をモールド化合物の上に設けることにより、C M P 又は他の平坦化プロセスを用いて、直接接合に充分な滑らかさまで平坦化することができる。

#### 【 0 0 4 2 】

図 15 A - 15 C においてキャリア 3 とモールド化合物 50 との間のキャリア 3 の上に第 2 の金属 52 を設けることができるのを除いて、図 15 A - 15 C は、図 14 A - 14 C と概ね同様である。図 16 A - 16 C は、モールド化合物 50 とキャリア 3 の間に保護コーティング 53 又は層（例えば、酸化ケイ素）を設けることができる別の実施形態を示す。保護コーティングはまた、種々の実施形態において、ダイ配置の後で金属堆積の前に設けることができる。図 16 A では、保護コーティング 53 は、キャリア 3 の上面、及び素子 3 の上面及び側面を共形にコーティングすることができる。モールド化合物 50 は、保護コーティング 53 の上及び素子 2 の間に設けることができる。図 16 B において、金属 51 は、上記で説明したように、モールド化合物 50 の上に設けることができる。図 16 C において、素子 2 の上にある保護コーティング 53 の部分は、ビア 13 を露出させるために、研磨、研削、又はラッピングプロセスを使用して除去することができる。金属 51 及び素子 2 を平坦化して、接合のための滑らかな表面を形成することができる。

#### 【 0 0 4 3 】

図 17 A - 17 D は、本明細書に開示される方法によって提供され得る追加の接合構造

10

20

30

40

50

1を示す図である。図17Aにおいて、接合構造1は、複数の素子2を含むことができ、この素子2は、集積デバイスダイ及びインターポーラの組み合わせを含むことができる。従って、本明細書に開示される方法は、アクティブ及び／又はインアクティブデバイスを使用することができる。更に、図17Aに示すように、上部再構成素子において隣接する素子2を分離するために、絶縁コラム55を設けることができる。図17Bにおいて、接合構造1は、信号を横方向内側又は外側に伝達するための横方向導電性配線トレースを含むことができる1又は2以上の再配線層(RDL)57を含むことができる。RDL57は、外部パッケージ基板に接続するためのファンイン又はファンアウト配置を可能にすることができる。図17Cでは、下部素子2から接合構造1の上面に信号を運ぶために、導電性ピア56を絶縁コラム56に設けることができる。図17Dでは、接合構造1は、絶縁コラム56のピア56とRDL57の両方を含むことができる。当業者であれば、更なる組み合わせが適切であることを理解するであろう。

10

#### 【0044】

##### 集積デバイスパッケージの追加例

集積デバイスパッケージは、トランジスタ及び他のタイプのアクティブデバイスなどのアクティブ回路を有する1又は複数の集積デバイスダイ(例えば、チップ)を含むことができる。集積デバイスダイは、半導体インターポーラ、半導体又は誘電体(例えば、ガラス)基板、別の集積デバイスダイ、再構成ウェーハ又は素子などのキャリアに取り付けることができる。様々な配置において、集積デバイスダイ及びパッケージ基板の露出面の上にモールド化合物又は封入材料を設けることができる。モールド化合物は、エポキシ又はポッティングコンパウンドなどのポリマー材料を含むことができる。モールド化合物の材料は、キャリア及び／又は集積デバイスのダイの熱膨張係数(CTE)とは異なる熱膨張係数(CTE)を有することができる。高温でのプロセスステップでは、モールド化合物とキャリア(及び／又は集積デバイスダイ)間のCTE不整合により、キャリア及び／又は集積デバイスダイに応力が誘起されることがある。例えば、CTE不整合により誘起される応力は、キャリア及び／又は集積デバイスダイにクラック及び／又は反りを生じさせる可能性があり、パッケージの歩留まりを低下させ、及び／又はシステム性能に影響を及ぼす可能性がある。従って、モールド化合物とキャリア(及び／又は集積デバイスダイ)間のCTE不整合に起因する応力を低減する改良されたパッケージに対する継続的な要求が依然としてある。

20

#### 【0045】

図18Aは、種々の実施形態による集積デバイスパッケージ82の概略側断面図である。図18Bは、図18Aの集積デバイスパッケージ82の概略的な上面図である。図18A-18Bに示すように、パッケージ82は、キャリア103と、キャリア103の上面に取り付けられた複数の集積デバイスダイ102とを含むことができる。集積デバイスダイ102は、アクティブ回路を含むことができる。例えば、集積デバイスダイ102は、プロセッサダイ、メモリダイ、センサダイ、マイクロエレクトロメカニカルシステム(MEMS)ダイ、又はアクティブ回路(トランジスタ又は他のアクティブデバイスなど)を含む他の何れかの好適なデバイスを含むことができる。図18Bの上面図には3つの集積デバイスダイ102が示されているが、何れかの好適な数のデバイスダイ102を提供することができることを理解されたい。例えば、1又は2の集積デバイスダイ102をキャリア103に取り付けることができ、或いは、3よりも多い集積デバイスダイ102をキャリアに取り付けることができる。更に、図18A-18Bにおいて、集積デバイスダイ102は、キャリア103に沿って横方向に離間して配置されている。代替的又は追加的に、パッケージのフットプリントを小さくするために、集積デバイスダイ102を垂直方向に積み重ねることができる。

30

#### 【0046】

キャリア103は、集積デバイスダイ102のための何れかの好適な支持構造を含むことができる。例えば、幾つかの実施形態では、キャリア103は、インターポーラ(半導体インターポーラなど)、半導体又は誘電体(例えば、ガラス)基板、別の集積デバイス

40

50

ダイ（例えば、ガラス）基板、別の集積デバイスダイ（例えば、アクティプ電子回路を有するアクティプチップ）、再構成ウェーハ又は素子等を含むことができる。キャリア 103 は、第 1 の CTE を有する材料（例えば、半導体材料、誘電体材料等）を含むことができる。種々の実施形態において、集積デバイスダイ 102 は、キャリア 103 の第 1 の CTE に実質的に類似する CTE を有することができる。幾つかの実施形態では、ダイ 102 の 1 又は 2 以上のバルク材料は、キャリア 103 の対応するバルク材料と同じ材料であつてよい。種々の実施形態において、キャリア 103 は、シリコン、ガラス、又は任意の他の適切な材料を含むことができる。幾つかの実施形態では、キャリア 103 は、ダイ 102 よりも大きな横方向のフットプリントを有する集積デバイスダイ（プロセッサダイなど）を含むことができる。集積デバイスダイ 102 は、何れかの好適な方法でキャリア 103 に取り付けることができる。例えば、ダイ 102 は、本明細書で説明するように、接着剤なしでキャリア 103 に直接ハイブリッド接合することができる。このような実施形態では、ダイ 102 の非導電性フィールド領域は、接着剤なしでキャリア 103 の対応する非導電性フィールド領域に直接接合することができる。更に、ダイ 102 の導電性コンタクトは、接着剤なしでキャリア 103 の対応する導電性コンタクトに直接接合することができる。しかしながら、他の実施形態では、ダイ 102 は、接着剤でキャリア 103 に取り付けることができる。幾つかの実施形態では、キャリア 103 は、キャリア 103 がより大きな電子システム内に存在し続けるように、ダイ 102 に接合されたままであることができる。他の実施形態では、キャリア 103 は、一時的な構造（取り付けテープ又は犠牲基板など）を含むことができ、取り外すことができる。キャリア 103 は、除去される（例えば、剥離され、又はエッチング除去される）一時的な構造体（マウンティングテープや犠牲基板など）を含むことができ、最終的な電子パッケージ又はシステムには存在しない。

#### 【0047】

図 18A に示すように、集積デバイスダイ 102 の上及びキャリア 103 の露出した上面の上にモールド化合物 108 を提供することができる。モールド化合物 108 は、説明を容易にするために、図 18B の上面図では隠されている。集積デバイスダイ 102 は、モールド化合物 108 内に少なくとも部分的に埋め込むことができる（例えば、完全に埋め込むか、又は埋める）。上記で説明したように、モールド化合物 108 は、キャリア 103（及び／又はダイ 102）の第 1 の CTE とは異なる第 2 の CTE を有するポリマー材料（エポキシ又はポッティング化合物など）を含むことができる。例えば、モールド化合物 108 の第 2 の CTE は、キャリア 103 及び／又はダイ 102 に CTE 誘起応力を生じさせるのに十分な量（例えば、CTE 不整合は、幾つかの場合、最大約 12 ppm であり得る）だけキャリア 103（及び／又はダイ 102）の第 1 の CTE と異なることができる。上記で説明したように、高温でのプロセスステップでは、モールド化合物 108 とキャリア 103（及び／又はダイ 102）との間の CTE 不整合が、パッケージ 82 の構成部品に反り、クラック、その他の損傷を引き起こす応力を発生させことがある。

#### 【0048】

モールド化合物 108 とキャリア 103（及び／又はダイ 102）との間の CTE 不整合の影響を低減するために、パッケージ 82 は、キャリア 103 の上面に取り付けられた 1 又は 2 以上の応力補償素子 104a - 104d を含むことができる。図示のように、パッケージ 82 は、応力補償素子 104a - 104d は、集積デバイスダイ 102 の周りに配置することができ、集積デバイスダイ 102 が、応力補償素子 104a - 104d によって囲まれたパッケージ 82 の内部領域内に配置されるようになる。モールド化合物 108 はまた、応力補償素子 104a - 104d の上に設けられるか又は施工することができ、応力補償素子 104a - 104d がモールド化合物 108 に少なくとも部分的に埋め込まれるようになる。応力補償素子 104a - 104d は、モールド化合物 108 の介在部分によって互いから及びダイ 102 から離間して配置することができる。応力補償素子 104a - 104d は、半導体材料（例えば、シリコン）、絶縁材料（例えば、ガラス）、又はキャリア 103 及び／又はダイ 102 の第 2 の CTE に実質的に一致する（又は近い

10

20

30

40

50

) CTE を有する他の適切な材料タイプを含むことができる。幾つかの実施形態では、応力補償素子 104a - 104d は、キャリア 103 及び / 又はダイ 102 と同じ材料を含むことができる。他の実施形態では、応力補償素子 104a - 104d は、キャリア 103 及び / 又はダイ 102 の材料とは異なる材料を含むことができる。各応力補償素子 104a - 104d は、同じ材料を含むことができ、又は一部（又は全て）が異なる材料を含むことができる。種々の実施形態において、応力補償素子 104a - 104d の CTE は、キャリア 103 及び / 又は集積デバイスダイ 102 の第 2 の CTE の 10% 以内、第 2 の CTE の 5% 以内、又は第 2 の CTE の 1% 以内とすることができます。種々の実施形態において、応力補償素子 104a - 104d の CTE は、10 ppm 未満、8 ppm 未満、又は 7 ppm 未満とすることができます。例えば、応力補償素子 104a - 104d の CTE は、3 ppm - 7 ppm の範囲にすることができる。

10

#### 【0049】

有益なことに、応力補償素子 104a - 104d の材料組成は、キャリア 103 及び / 又はダイ 102 のものと実質的に一致する CTE を有するように選択されるので、応力補償素子 104a - 104d は、キャリア 103 及び / 又はダイ 102 に付与される応力を低減させることができる。CTE が一致した応力補償素子 104a - 104d は、キャリア 103 の大面積にわたって提供され、モールド化合物 108 とキャリア 103 及び / 又はダイ 102 との間の CTE 不整合によって誘発されるあらゆる応力を補償又は低減する応力整合充填材料として機能するようにすることができます。例えば、幾つかの実施形態では、応力補償素子 104a - 104d は、キャリア 103 の占有されていない領域の大部分、例えば、少なくとも 20%、少なくとも 50%。キャリア 103 の非占有領域の少なくとも 20%、少なくとも 50%、少なくとも 75%、少なくとも 85%、又は少なくとも 90% を覆うように取り付けることができる（例えば、ダイ 102 又は他の電子部品又はデバイスをサポートしないキャリア 103 の領域）。幾つかの実施形態では、応力補償素子 104a - 104d は、キャリア 103 の占有されていない領域の 20% - 90% の範囲、キャリア 103 の占有されていない領域の 35% - 90% の範囲、又はキャリア 103 の占有されていない領域の 50% - 90% の範囲をカバーするように取り付けることができる。幾つかの実施形態では、図 18B の上面図に示されるように、応力補償素子 104a - 104d は、対向する側縁 105a、105b に垂直な全ての線が少なくとも 1 つの応力補償素子 104a - 104d を通過するか、又は交差することができるよう、横方向に重なり合うことができる。このような配置では、応力補償素子 104a - 104d は、キャリア 103 を通って亀裂が伝播するのを防止又は阻止するように機能することができます。

20

#### 【0050】

更に、図 18B の上面図に示されるように、応力補償素子 104a - 104d は、パッケージ 82 の外側側縁 105a - 105d と集積デバイスダイ 102 との間で、各集積デバイスダイ 102 の少なくとも 1 つの横方向側縁 109 が少なくとも 1 つの応力補償素子 104a - 104d と交差する対応する平面に存在するように配置することができます。幾つかの実施形態では、ダイ 102 の側縁 109 の大部分（又は全て）は、少なくとも 1 つの応力補償素子 104a - 104d と交差するそれぞれの平面に存在することができる。

30

#### 【0051】

図 18C は、応力補償素子 104a - 104d の間の増加した横方向の重なりを含む、集積デバイスパッケージ 82 の概略上面図である。特に断らない限り、図 18C の構成要素は、図 18A - 18B の同じ番号の構成要素と同じで、又はほぼ類似したものとすることができます。図 18C では、応力補償素子 104b は、垂直方向に（上面図に示すように）短縮され、応力補償素子 104a ~ 104d は、図 18B と比較して、水平方向（上面図に示す）に長くなっている。従って、図 18C では、応力補償素子 104d は、側縁 105b まで延び、側縁 105b に沿って露出することができる。図 18C において、各側縁 105a - 105d に垂直な全ての線は、少なくとも 1 つの応力補償素子 104a - 104d を通過するか、又はこれと交差することができ、これにより、亀裂伝播を防止又は

40

10

20

30

40

50

阻止することができる。

#### 【0052】

幾つかの実施形態では、応力補償素子104a - 104dは、アクティブ回路がないダミー応力補償素子を備えることができ、例えば、ダミー応力補償素子にアクティブデバイスが存在しない。このような実施形態では、ダミー応力補償素子は、アクティブ回路を持たない半導体材料（例えば、シリコン）又は誘電体材料（ガラスなど）のダミーピース又はブロックを含むことができる。ダミー素子を使用すると、素子104a - 104dに回路又はデバイスをパターン化又は形成する必要がないので、処理コスト及び複雑さを低減することができ、更なる利点を提供することができる。しかしながら、他の実施形態では、応力補償素子104a - 104dのうちの1又は2以上が、アクティブ回路又はデバイスを有するアクティブ集積デバイスダイを含むことができる。複数の応力補償素子104a - 104dの使用により、パッケージ組立業者が所望の場所、例えば、クラックが発生しやすい場所及び/又はキャリア103上の標的空間にて素子104a - 104dをピックアップして配置することを有利に可能にすることができます。10

#### 【0053】

集積デバイスダイ102と同様に、応力補償素子104a - 104dは、何れかの好適な方法でキャリア103に取り付けることができる。例えば、応力補償素子104a - 104dは、接着剤なしでキャリア103に直接接合することができる。上記で説明したように、応力補償素子104a - 104dは、アクティブ回路を有しないダミー応力補償素子を含むことができる。このような実施形態では、応力補償素子104a - 104dは、接着剤なしで接合界面に沿ってキャリア103の対応する非導電性電界領域に直接接合される非導電性電界領域を備えることができる。更に、幾つかの実施形態において、応力補償素子104a - 04dは、素子104a - 104dとキャリア103との間の接合界面が非導電性 - 非導電性直接接合（例えば、接合界面が導体 - 導体又は金属 - 金属直接接合がない）のみを含むように、直接接合することができる。例えば、アクティブ回路及び/又はコンタクトパッドを有しないダミー応力補償素子を利用する実施形態では、応力補償素子104a - 104dは、非導電性 - 非導電性直接接合のみを利用してキャリア103に直接接合することができ、例えば、素子104a - 104dの非導電性又は誘電性接合層は、接着剤なしでキャリア103の対応する非導電性又は誘電性接合層に直接接合することができる。このような実施形態では、非導電性 - 非導電性直接接合は、接合界面に沿って1つのタイプ又は複数の異なるタイプの非導電性材料を含むことができる。このように、本書で開示される種々の実施形態では、1又は2以上の素子（ダイ102など）は、接着剤なしで接合界面に沿ってキャリア103にハイブリッド直接接合することができ、1又は2以上の素子（例えば、ダイ102）は、キャリア103の対応する非導電性フィールド領域及び導電性コンタクトに直接接合されるようになる。他の1又は2以上の素子（応力補償素子104a - 104dなど）は、接合界面に沿って接着剤なしでキャリア103に直接接合することができ、応力補償素子104a ~ 104dとキャリア103の間の接合界面が、非導電性 - 非導電性接接合のみを含む（例えば、素子104a - 104dとキャリア103の直接接合された誘電体接合層104a ~ 104d及びキャリア103）。例えば、一部の素子104a - 104dは、キャリア103に直接接合される導電性コンタクトを含まない場合がある。ダイ102、応力補償素子104a - 104d、及び/又はキャリア103の非導電性フィールド領域は、無機誘電体材料（例えば、酸化シリコン）を含むことができる。非導電性フィールド領域は、ダイ102、応力補償素子104a - 104d、及び/又はキャリア103のパターン化されていない部分を備えることができる。接合界面は、窒素終端表面、接合界面及び素子の誘電体接合層の上部及び/又は下部界面におけるフッ素ピークなど、直接的な非導電性接合を示すシグネチャを含むことができる。20

#### 【0054】

応力補償素子104a - 104dが回路及びコンタクトパッドを含むような他の実施形態では、応力補償素子104a - 104dの非導電性フィールド領域及びコンタクトパッ30

ドの両方は、キャリア 103 の対応する非導電性フィールド領域及びコンタクトパッドに直接接合することができる。更に他の実施形態では、応力補償素子 104a - 104d は、接着剤でキャリア 103 に接合することができる。幾つかの実施形態では、キャリア 103 は、システムマザーボードなどの外部デバイス又は別の構造に取り付けることができる。他の実施形態では、キャリア 103 は、モールド化合物 108 が施工された後に取り外すことができる一時的なサポート構造を備えることができる。図 18B には、4つの応力補償素子 104a - 104d が示されているが、4つよりも少ない又は4つよりも多い応力補償素子 104a - 104d を設けてもよいことは理解されたい。

#### 【0055】

図 18A - 18B に示すように、パッケージ 82 は、外側側縁 105a - 105d を備えることができる。パッケージ 82 は、より大きなウェーハ又は再構成ウェーハがシンギュレーションストリート S に沿ってシンギュレーションされて、複数のシンギュレーションパッケージ 82 をもたらすシンギュレーションプロセスから形成することができる。幾つかの実施形態において、シンギュレーションは、ソーキングプロセス、エッチングプロセス、又はパッケージ 82 がより大きなウェーハ又は再構成ウェーハから形成することができる任意の他の適切なプロセスを含むことができる。シンギュレーション後、外側側縁 105a - 105d ( 例えは、図 18B に示すように、応力補償素子 104a、104c、キャリア 103、及び / 又はモールド化合物 108 の外側側縁を含む ) は、シンギュレーションプロセスを示すシンギュレーションマーキングを含むことができる。例えば、ソーキングプロセスの場合、シンギュレーションマーキングは、シンギュレーションされた表面の筋のようなソウマーキングを含むことができる。エッチングシンギュレーションプロセスの場合、シンギュレーションマーキングは、エッチング経路を示すマーキング又は微細構造を含むことができる。図 18C の実施形態では、外側側縁 105b は、応力補償素子 104d の外縁部、キャリア 103 の縁部、及びモールド化合物を含むことができ、これらの各々は、シンギュレーションプロセスを示すマーキングを含むことができる。応力補償素子 104a - 104d は、キャリア 103 に沿った任意の場所に配置することを理解されたい。例えは、他の実施形態において、応力補償素子 104a - 104d の一部又は全部は、パッケージ 82 の外側側縁 105a - 105d に対して横方向に挿入されて位置決めすることができ、応力補償素子 104a - 104d はモールド化合物 108 に埋め込まれるようになる。

#### 【0056】

種々の実施形態において、シンギュレーションストリート S は、シンギュレーション時に、モールド化合物 108 及び 1 又は 2 以上の応力補償素子 104a - 104d をパッケージ 82 の 1 又は 2 以上の外側側縁 105a - 105d に沿って露出することができるよう、応力補償素子 104a - 104d のうちの 1 又は 2 以上を通過させることができる。例えは、図 18A - 18B に示すように、応力補償素子 104a, 104c は、パッケージ 82 の対応する外側側縁 105a, 105c で露出される側縁 106a, 106c を含むことができる。更に、モールド化合物 108 の側縁 107 は、パッケージ 82 の外側側縁 105a - 105d に沿って露出させることができる。図示のように、応力補償素子 104a, 104c の露出した側縁 106a, 106c は、応力補償素子 104a, 104c の上にあるモールド化合物 108 の部分及び応力補償素子 104a, 104c に横方向に隣接するモールド化合物 108 の部分を含む、モールド化合物 108 の側縁 107 と同一平面にすることができる。種々の実施形態において、幾つかの応力補償素子 104b, 104d は、パッケージ 82 の外側側縁 105b, 105d に対して横方向に挿入することができ、素子 104b, 104d はモールド化合物 108 に完全に埋め込むことができるようになる。幾つかの実施形態では、応力補償素子 104a - 104d の全てが、外側側縁 105a - 105d に対して横方向に挿入することができる。

#### 【0057】

図 19 は、種々の実施形態による、1 又は 2 以上の集積デバイスパッケージ 82 を組み込んだシステム 80 の概略図である。システム 80 は、例えは、モバイル電子デバイス (

10

20

30

40

50

例えば、スマートフォン、タブレットコンピューティングデバイス、ラップトップコンピュータなど)、デスクトップコンピュータ、自動車又はその部品、ステレオシステム、医療機器、カメラ、又は任意の他の適切なタイプのシステムなど、任意の好適なタイプの電子デバイスを含むことができる。幾つかの実施形態では、電子デバイスは、マイクロプロセッサ、グラフィックプロセッサ、電子記録装置、又はデジタルメモリを含むことができる。システム 80 は、例えば 1 又は 2 以上のマザーボードによって、システム 80 に機械的及び電気的に接続されている 1 又は 2 以上のデバイスパッケージ 82 を含むことができる。各パッケージ 82 は、1 又は 2 以上の集積デバイスダイ及び / 又は接合構造 1 を含むことができる。集積デバイスダイ及び / 又は接合構造は、図 1A - 18B に関連して上記に示され説明された集積デバイスパッケージ及び / 又は接合構造の何れかを備えることができる。

#### 【 0 0 5 8 】

一実施形態では、集積デバイスパッケージが開示される。集積デバイスパッケージは、キャリアと、キャリアの上面の一部を覆うモールド化合物と、を備えることができる。集積デバイスパッケージは、キャリアに取り付けられ且つモールド化合物に少なくとも部分的に埋め込まれた集積デバイスダイを備えることができ、集積デバイスダイは、アクティブ回路を備える。集積デバイスパッケージは、キャリアに取り付けられ且つモールド化合物に少なくとも部分的に埋め込まれた応力補償素子を備え、応力補償素子は集積デバイスダイから離間して配置され、応力補償素子は、アクティブ回路を有していないダミー応力補償素子を含むことができる。応力補償素子及び集積デバイスダイの少なくとも一方は、接着剤なしでキャリアに直接接合することができる。

#### 【 0 0 5 9 】

別の実施形態では、集積デバイスパッケージが開示される。集積デバイスパッケージは、モールド化合物と、モールド化合物に少なくとも部分的に埋め込まれた集積デバイスダイとを含むことができ、集積デバイスダイはアクティブ回路を含む。集積デバイスパッケージは、モールド化合物に少なくとも部分的に埋め込まれた複数のダミー応力補償素子を含むことができ、複数のダミー応力補償素子はアクティブ回路を含まず、複数のダミー応力補償素子はモールド化合物によって互いに離間して配置される。

#### 【 0 0 6 0 】

別の実施形態では、集積デバイスパッケージを形成する方法が開示される。本方法は、集積デバイスダイ及び複数のダミー応力補償素子上にモールド化合物を設けるステップを含むことができ、複数のダミー応力補償素子は、モールド化合物によって互いに離間して配置される。集積デバイスダイは、アクティブ回路を含むことができる。複数のダミー応力補償素子は、アクティブ回路を有していない。

#### 【 0 0 6 1 】

別の実施形態では、集積デバイスパッケージが開示される。集積デバイスパッケージは、モールド化合物と、モールド化合物に少なくとも部分的に埋め込まれた集積デバイスダイとを備えることができ、集積デバイスダイは、アクティブ回路を含む。集積デバイスパッケージは、モールド化合物に少なくとも部分的に埋め込まれ、集積デバイスダイから離間して配置された応力補償素子を含むことができる。モールド化合物及び応力補償素子は、集積デバイスパッケージの外側の側縁で露出させることができる。

#### 【 0 0 6 2 】

別の実施形態では、電子部品が開示される。電子部品は、第 1 の非導電性フィールド領域及び第 1 の導電性コンタクトを有するキャリアを備えることができる。電子部品は、接着剤なしでキャリアに直接ハイブリッド接合された第 1 の素子と、接着剤なしでキャリアの第 1 の非導電性フィールド領域に直接接合された第 1 の素子の第 2 の非導電性フィールド領域と、キャリアの第 1 の導電性コンタクトに直接接合された第 1 の素子の第 2 の導電性コンタクトとを含むことができる。電子部品は、第 2 の素子の第 3 の非導電性フィールド領域のみがキャリアの第 1 の非導電性フィールド領域に直接接合されるように、接着剤を用いずにキャリアに直接接合された第 2 の素子を含むことができる。

**【 0 0 6 3 】**

別の実施形態では、電子部品が開示される。電子部品は、第1の非導電性フィールド領域及び第1の導電性コンタクトを有するキャリアを備えることができる。電子部品は、接着剤なしでキャリアに直接ハイブリッド接合された第1の素子と、接着剤なしでキャリアの第1の非導電性フィールド領域に直接接合された第1の素子の第2の非導電性フィールド領域と、キャリアの第1の導電性コンタクトに直接接合された第1の素子の第2の導電性コンタクトとを含むことができる。電子部品は、接着剤なしでキャリアに直接接合された第2の素子を含むことができ、第2の素子は、キャリアに直接接合される導電性コンタクトを含まない。

**【 0 0 6 4 】**

一実施形態では、接合構造が開示される。接合構造は、第1の素子を含み、第1の接合面を含む第1の側面と、第1の側面と反対側の第2の側面とを有する第1の再構成された素子を含むことができる。第1の再構成素子は、第1の素子の第1の側壁表面の周りに配置された第1の保護材料を含むことができる。接合構造は、第2の素子を含み、第2の接合面を含む第1の側面と第1の側面と反対側の第2の側面とを有する第2の再構成素子を含むことができる。第1の再構成素子は、第2の素子の第2の側壁表面について配置された第2の保護材料を含むことができる。第2の再構成素子の第1の側面の第2の接合面は、接合界面に沿って接着剤を介在させることなく、第1の再構成素子の第1の側面の第1の接合面に直接接合することができる。第1の保護材料は、第1の接合面と面一であることができ、第2の保護材料は、第2の接合面と面一であることができる。

10

**【 0 0 6 5 】**

別の実施形態では、接合構造が開示される。接合構造は、第1の素子を含み、第1の側面と第1の側面と反対側の第2の側面とを有する第1の再構成素子を備えることができる。接合構造は、第2の素子を含み、第1の側面と第1の側面とは反対側の第2の側面とを有する第2の再構成素子を含むことができ、第2の再構成素子の第1の側面は、接合界面に沿って接着剤を介在せずに第1の再構成素子の第1の側面に直接接合される。接合構造は、第1及び第2の素子のそれぞれの第1及び第2の側面の周りに配置された保護材料を含むことができる。接合構造は、第1及び第2の素子の間に配置された非導電層を含むことができ、非導電層は、保護材料と非導電層との間に界面が設けられるように第1及び第2の素子の第1及び第2の側面の少なくとも1つと同一平面上にある。

20

**【 0 0 6 6 】**

別の実施形態では、接合構造が開示される。接合構造は、複数の第1素子を含む第1再構成ウェーハを含むことができる。接合構造は、複数の第2の素子を含む第2の再構成ウェーハを含むことができる。第1再構成ウェーハ及び第2再構成ウェーハは、接着剤なしで互いに直接接合することができる。

30

**【 0 0 6 7 】**

別の実施形態では、接合方法が開示される。接合方法は、第1の再構成ウェーハを形成するために、複数の第1の素子上に第1の保護材料を施工するステップを含むことができる。接合方法は、第2の再構成ウェーハを形成するために、複数の第2の素子上に第2の保護材料を施工するステップを含むことができる。接合方法は、接着剤を用いて、第1の再構成ウェーハを第2の再構成ウェーハに直接接合するステップを含むことができる。

40

**【 0 0 6 8 】**

別の実施形態では、接合方法が開示される。接合方法は、接着剤なしで第1の素子をキャリアに直接接合するステップを含むことができる。キャリアは、シリコンキャリアの表面上に直接配置されたシリコン酸化物層を有するシリコンキャリアを含むことができる。酸化ケイ素層は、第1の素子に直接接合することができる。シリコン酸化物層は、ネイティブ酸化物層又は熱酸化物層を含むことができる。

**【 0 0 6 9 】**

これらの実施形態は全て、本開示の範囲内にあることが意図されている。これらの実施形態及び他の実施形態は、添付図を参照した以下の実施形態の詳細な説明から当業者には

50

容易に明らかになるであろうが、特許請求の範囲は、開示されたあらゆる特定の実施形態にも限定されるものではない。この特定の実施形態及び実施例が本明細書で開示されているが、開示された実施構成は、具体的に開示された実施形態を逸脱して、他の代替の実施形態及び／又は使用並びにこれらの明らかな修正形態及び等価物にまで拡大されることは、当業者には理解されるであろう。更に、幾つかの変形例が図示されて詳細に説明されてきたが、他の修正形態は、本開示に基づいて当業者には容易に明らかであろう。また、実施形態の特定の特徴及び態様の様々な組み合わせ又は部分的組み合わせがなされ、それでもなお範囲内にあることが企図される。開示された実施形態の様々な特徴及び態様は、開示された実施形態の様々な態様を形成するために、互いに組み合わせることができ、又は置換することができることを理解されたい。従って、本明細書に開示された主題の範囲は、上述の特定の開示された実施形態によって限定されるべきではなく、以下の請求項を適正に読むことによってのみ決定されるべきであることが意図される。

10

## 【図面】

【図 1A - 1C】

FIG. 1A

FIG. 1B

FIG. 1C

【図 2】

20

30

40

50

【図 3 A】

【図 3 B】

10

20

【図 3 C】

【図 4 A】

30

40

50

【図 4 B】

【図 5 A】

10

20

【図 5 B】

【図 5 C】

30

40

50

【 四 6 】

FIG. 6

【図7A-7B】

28

【 8 A - B 】

E/G

FIG. 8B

【図 9 A】

FIG. 9A

The diagram illustrates the relationship between the final synchronization and the start of the stacking cycle. It features two downward-pointing arrows originating from the text "最終シンクレーション" (Final Synchronization) on the right. The top arrow points to the text "ウェーハからウェーハへのスタッキングキャリアリースを継続" (Continue the wafer-to-wafer stacking carrier lease). The bottom arrow points to the text "20b".

10

20

30

40

50

【図 9 B】

【図 9 C】

10

20

【図 9 D】

【図 9 E】

30

40

50

【図 9 F】

FIG. 9F

【図 10 A】

FIG. 10A

【図 10 B】

FIG. 10B

【図 10 C】

FIG. 10C

10

20

30

40

50

【図 10D】

【図 10E】

10

20

【図 11】

【図 12A】

30

40

50

【図 1 2 B】

【図 1 2 C】

10

20

【図 1 3 A】

【図 1 3 B】

30

40

50

【図 14 A】

【図 14 B】

10

20

【図 14 C】

【図 15 A】

30

40

50

【図 15B】

【図 15C】

10

20

【図 16A】

【図 16B】

30

40

50

【図 16C】

【図 17A】

【図 17B】

【図 17C】

【図 17D】

FIG. 17D

【図 18A】

FIG. 18A

10

20

30

40

【図 18B】

FIG. 18B

【図 18C】

FIG. 18C

50

【図 1 9】

Fig. 19

10

20

30

40

50

---

フロントページの続き

弁理士 山本 泰史

(74)代理人 100144451

弁理士 鈴木 博子

(74)代理人 100168871

弁理士 岩上 健

(72)発明者 ハーバ ベルガセム

アメリカ合衆国 カリフォルニア州 95134 サンノゼ オーチャード パークウェイ 3025

審査官 河合 俊英

(56)参考文献 米国特許出願公開第2015/0262845(US, A1)

米国特許出願公開第2016/0126634(US, A1)

米国特許出願公開第2018/0138101(US, A1)

特開2007-294724(JP, A)

特開2010-34294(JP, A)

米国特許出願公開第2016/0322330(US, A1)

国際公開第2019/054364(WO, A1)

(58)調査した分野 (Int.Cl., DB名)

H01L 25/04

H01L 23/29