19 RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

**11 N° de publication :**

(à n'utiliser que pour les commandes de reproduction)

2 695 505

(21) N° d'enregistrement national : **93 10652**

51 Int Cl<sup>5</sup> : G 11 C 27/02 , H 03 M 1/44 , 1/36

12

# DEMANDE DE BREVET D'INVENTION

A1

22 Date de dépôt : 08.09.93.

30 Priorité : 08.09.92 GB 9218987.

(71) Demandeur(s) : FUJITSU LIMITED — JP.

43 Date de la mise à disposition du public de la demande : 11.03.94 Bulletin 94/10.

**56** **Liste des documents cités dans le rapport de recherche préliminaire : Ce dernier n'a pas été établi à la date de publication de la demande.**

**60 Références à d'autres documents nationaux apparentés :**

72 Inventeur(s) : Dedic Ian Juso.

73 Titulaire(s) :

**74** **Mandataire : Cabinet Beau de Loménie.**

## 54 Circuits de mémorisation, de sommation et de conversion de tension et convertisseurs analogique-numérique.

57 L'invention concerne les circuits de traitement de tensions analogiques.

Un circuit de mémorisation de tension comprend un élément de commutation d'entrée (1) connecté entre un nœud d'entrée (ENTREE) du circuit et une première armature d'un condensateur de mémorisation (2). L'autre armature est connectée à une borne commune (COM) du circuit. Un élément amplificateur à haute impédance (3) est connecté à la première armature pour fournir sur un nœud de sortie (SORTIE) une tension de sortie ( $V_s$ ) qui dépend du potentiel de la première armature ( $V_1$ ). Un tel circuit évite une charge/décharge du condensateur de mémorisation sous l'effet d'une injection de charge par l'élément amplificateur.

Application aux convertisseurs analogique-numérique rapides de très haute précision.

La présente invention concerne des circuits de mémorisation de tension prévus par exemple pour l'utilisation dans des convertisseurs analogique-numérique, pour mémoriser une valeur analogique appliquée avant la conversion en son équivalent numérique.

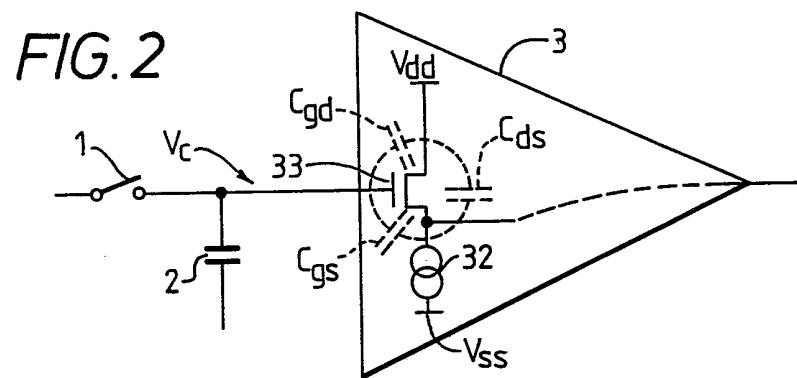

La figure 1 des dessins annexés montre un circuit de mémorisation de tension envisagé précédemment, qui comprend un élément de commutation d'entrée 1, un condensateur de mémorisation 2, et un élément amplificateur 3 ayant une impédance élevée et un gain égal à l'unité. Initialement, lorsque l'élément de commutation 1 est dans la position fermée, une tension d'entrée analogique  $V_i$  qui est appliquée entre les bornes d'entrée du circuit est transmise au condensateur de mémorisation 2, de façon que la différence de potentiel entre les armatures du condensateur de mémorisation suive la tension d'entrée  $V_i$ . A un instant prédéterminé  $t_{comm}$ , l'élément de commutation d'entrée 1 est commuté vers la position ouverte, ce qui fait que la différence de potentiel entre les armatures du condensateur immédiatement après cette commutation est mémorisée jusqu'au moment où l'élément de commutation d'entrée 1 est ouvert à nouveau.

Pendant la période au cours de laquelle l'élément de commutation est dans la position ouverte, la tension mémorisée est reproduite entre les bornes de sortie du circuit, sous la forme d'une tension de sortie  $V_o$ , l'élément amplificateur 3 ayant pour fonction d'éviter que le condensateur de mémorisation ne soit chargé par un circuit qui est connecté aux bornes de sortie.

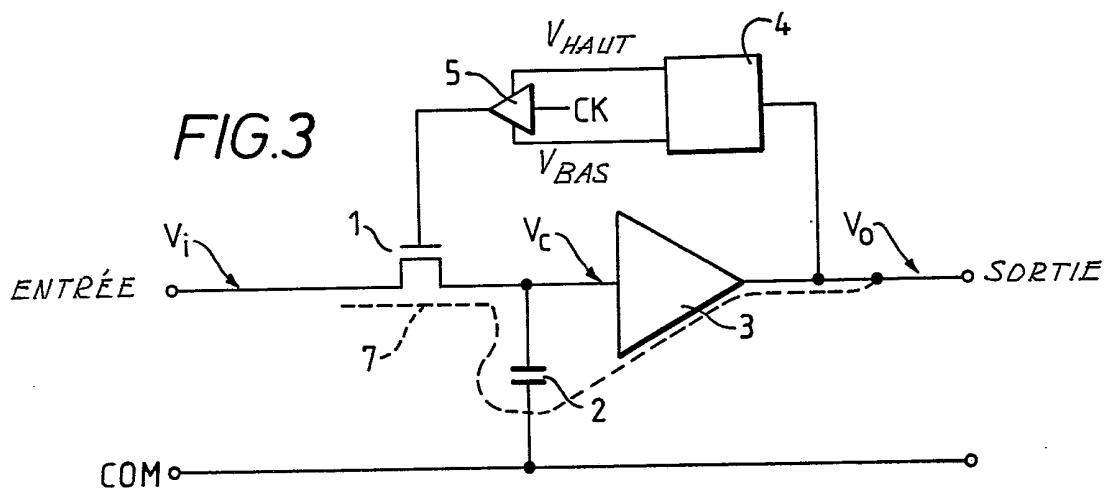

La figure 2 montre de façon plus détaillée une partie d'entrée de l'élément amplificateur 3. Cette partie d'entrée comprend un transistor d'entrée 33 qui est un transistor à effet de champ ayant une électrode de drain connectée à une ligne d'alimentation.

tion positive  $V_{dd}$  de l'élément, une électrode de source connectée par l'intermédiaire d'une source de courant 32 à une ligne d'alimentation négative  $V_{ss}$  de l'élément, et une électrode de grille connectée à une 5 armature (l'armature supérieure sur la figure 1) du condensateur de mémorisation. On notera que le transistor à effet de champ d'entrée 33 est connecté dans ce que l'on appelle la configuration à charge de source.

10 Un circuit supplémentaire, non représenté sur la figure 2, est normalement interposé entre l'électrode de source du transistor à effet de champ d'entrée 33 et une sortie de l'élément pour isoler/amplifier le potentiel de l'électrode de source de 15 façon à produire le potentiel de sortie  $V_o$ .

Dans l'utilisation de l'élément amplificateur 3 de la figure 2, la source de courant 32 fait circuler un courant dans le canal drain-source du transistor à effet de champ d'entrée 33, ce qui fait 20 que le potentiel d'électrode de source  $V_s$  de ce transistor suit le potentiel d'électrode de grille, et par conséquent le potentiel mémorisé  $V_c$  de l'armature supérieure du condensateur de mémorisation 2. Ainsi, 25 la partie d'entrée de l'élément amplificateur 3 a un gain en tension pratiquement égal à l'unité, bien qu'en pratique le potentiel d'électrode de source  $V_s$  soit toujours légèrement inférieur au potentiel  $V_s$  de l'armature supérieure du condensateur de mémorisation 2.

30 Du fait que la partie d'entrée utilise un transistor à effet de champ d'entrée dont le courant de grille est très faible, l'impédance d'entrée de l'élément est très élevée. Par conséquent, après que 35 l'élément de commutation d'entrée 1 du circuit de mémorisation de tension de la figure 1 a été ouvert,

le condensateur de mémorisation n'est pas déchargé d'une manière appréciable par l'élément amplificateur 3.

L'élément amplificateur 3 de la figure 2 présente cependant un inconvénient qui résulte d'une injection de charge dans sa partie d'entrée à partir du condensateur de mémorisation 2 (ou inversement), lorsque le potentiel de l'armature supérieure  $V_c$  du condensateur de mémorisation 2 est changé. Bien 10 qu'après que l'élément de commutation d'entrée 1 a été ouvert, il ne se produise normalement aucun changement de ce type du potentiel de l'armature supérieure, comme on l'expliquera ultérieurement dans la présente description, le potentiel de l'armature supérieure  $V_c$  15 change inévitablement à l'instant  $t_{comm}$  de l'ouverture de l'élément de commutation d'entrée 1, à cause d'une injection de charge à ce moment par l'élément de commutation d'entrée 1 lui-même. Une telle injection de charge par l'élément de commutation d'entrée 1 20 conduit à un changement faible, mais appréciable lorsqu'on travaille avec une précision élevée, dans la tension qui est mémorisée dans le condensateur de mémorisation 2, et par conséquent il provoque un 25 changement dans le potentiel  $V_c$  de l'armature supérieure du condensateur, au moment où l'élément de commutation est ouvert.

On va maintenant expliquer les raisons pour lesquelles une injection de charge se produit dans la partie d'entrée de l'élément amplificateur sous 30 l'effet de changements du potentiel de l'armature supérieure du condensateur de mémorisation 2. Comme le montre la figure 2, le transistor à effet de champ d'entrée 33 a inévitablement de petites capacités parasites entre ses électrodes, et il y a une capacité 35 parasite grille-source  $C_{gs}$  entre les électrodes de

grille et de source, une capacité parasite grille-drain  $C_{gd}$  entre les électrodes de grille et de drain, et une capacité parasite drain-source  $C_{ds}$  entre les électrodes de drain et de source. Chaque fois que les 5 potentiels de ces trois électrodes changent mutuellement, une charge doit entrer dans les capacités parasites ou sortir de celles-ci, et c'est la combinaison de ces circulations de charges qui provoque l'injection de charge dans la partie d'entrée d'élément amplificateur, ou à partir de celle-ci.

10

Dans l'élément amplificateur de la figure 2, du fait que le transistor d'entrée 33 est connecté dans la configuration à charge de source mentionnée ci-dessus, son potentiel grille-source est pratiquement constant, indépendamment du potentiel  $V_c$  de l'armature supérieure du condensateur de mémorisation 2, ce qui fait que l'on peut normalement négliger l'injection de charge qui est due à la capacité parasite grille-source  $C_{gs}$ .

15

20 Cependant, le potentiel grille-drain et le potentiel drain-source du transistor d'entrée 33, qui ont respectivement les valeurs  $V_{dd} - V_c$  et  $V_{dd} - V_s$ , ne sont pas constants et varient sous la dépendance du potentiel  $V_c$  de l'armature supérieure. Par conséquent, 25 chaque fois que  $V_c$  est changé, une charge doit entrer dans la capacité parasite grille-drain  $C_{gd}$  et la capacité parasite drain-source  $C_{ds}$ , ou sortir de ces capacités, ce qui provoque dans chaque cas la circulation d'une charge vers la partie d'entrée de l'élément amplificateur ou à partir de celle-ci.

30

35 Lorsque l'élément de commutation d'entrée est ouvert, la charge qui circule doit charger ou décharger le condensateur de mémorisation 2, en fonction de la direction de circulation. Cette charge ou cette décharge introduit inévitablement une erreur

dans la tension mémorisée entre les armatures du condensateur de mémorisation 2.

Les effets des capacités parasites de la partie d'entrée de l'élément amplificateur sont particulièrement sévères lorsque la capacité du condensateur de mémorisation 2 n'est pas élevée par rapport aux capacités parasites elles-mêmes, ce qui peut être le cas par exemple lorsqu'on désire réduire le temps d'acquisition du circuit de mémorisation de tension.

10 Un premier aspect de la présente invention procure un circuit de mémorisation de tension comprenant :

15 un condensateur de mémorisation dont une première armature est connectée à une borne d'entrée du circuit par l'intermédiaire d'un élément de commutation d'entrée et dont la seconde armature est connectée à une borne commune du circuit, un signal d'entrée à mémoriser étant appliqué entre les bornes d'entrée et commune lorsque le circuit est en cours

20 d'utilisation; et

25 un élément amplificateur, ayant une entrée connectée à la première armature et une sortie connectée à une borne de sortie du circuit, pour fournir un signal de sortie entre la borne de sortie et la borne commune, sous la dépendance de la tension qui est mémorisée dans le condensateur de mémorisation, cet élément amplificateur comprenant un dispositif d'entrée électronique ayant un chemin de courant commandé entre des première et seconde électrodes

30 respectives de chemin de courant du dispositif, et ayant également une électrode de commande à laquelle un potentiel est appliqué pour commander l'intensité du courant dans le chemin de courant, cette électrode de commande étant connectée à la première armature, et

35 les première et seconde électrodes de chemin de

courant étant connectée à des moyens suiveurs de potentiel, de façon que le potentiel de la première électrode de chemin de courant ainsi que le potentiel de la seconde électrode de chemin de courant suivent 5 le potentiel de l'électrode de commande, pendant qu'un courant circule dans le chemin à courant commandé, afin que les potentiels respectifs des première et seconde électrodes de chemin de courant soient maintenus pratiquement fixes par rapport au potentiel de la 10 première armature.

Avec une telle conception de l'élément amplificateur, les potentiels de l'électrode de commande et des première et seconde électrodes de chemin de courant du dispositif d'entrée sont tous dans une 15 relation pratiquement fixe les uns par rapport aux autres et par rapport au potentiel de la première armature, lorsque le circuit est en cours d'utilisation, ce qui fait que les capacités parasites qui existent entre ces électrodes n'affectent pas notable- 20 ment le fonctionnement du circuit. Ceci évite une injection de charge vers l'élément amplificateur ou à partir de celui-ci, avec la charge/décharge résultante du condensateur de mémorisation, à cause du fonctionnement de l'élément amplificateur qui est connecté à 25 la première armature du condensateur de mémorisation. On élimine ainsi une erreur dans la tension mémorisée sous l'effet d'une telle charge/décharge.

Il est préférable que les moyens suiveurs de potentiel comprennent une source de courant, connectée 30 à la première électrode de chemin de courant, pour faire en sorte que le potentiel de la première électrode de chemin de courant suive le potentiel de l'électrode de commande, et un circuit suiveur actif connecté fonctionnellement entre les première et 35 seconde électrodes de chemin de courant, pour que le

potentiel de la seconde électrode de chemin de courant suive le potentiel de la première électrode de chemin de courant.

Dans une telle configuration, la première 5 électrode de chemin de courant suit automatiquement le potentiel de la première armature, ce qui fait que le circuit suiveur actif peut être connecté fonctionnellement entre les première et seconde électrodes de chemin de courant, c'est-à-dire exclusivement du côté 10 de la sortie du dispositif d'entrée, pour réaliser la fonction exigée consistant à suivre la seconde électrode de chemin de courant.

Le dispositif d'entrée électronique est 15 avantageusement un transistor d'entrée à effet de champ, de façon que l'électrode de commande soit l'électrode de grille du transistor d'entrée à effet de champ, la première électrode de chemin de courant soit l'électrode de source du transistor d'entrée à effet de champ, la seconde électrode de chemin de courant soit l'électrode de drain du transistor 20 d'entrée à effet de champ, et le chemin à courant commandé soit constitué par le canal drain-source du transistor d'entrée à effet de champ.

Un tel transistor d'entrée à effet de champ 25 confère une impédance d'entrée élevée à l'élément amplificateur, de façon à éviter une décharge du condensateur de mémorisation après que l'élément de commutation d'entrée a été ouvert, les capacités parasites grille-source, grille-drain et source-drain 30 du transistor à effet de champ d'entrée, qui sont inévitables, n'affectant pas le fonctionnement.

Lorsque le dispositif d'entrée est un 35 transistor à effet de champ, le circuit suiveur actif peut comprendre un transistor à effet de champ en montage cascode avec son canal drain-source en série

avec le canal drain-source du transistor d'entrée à effet de champ, de façon que le potentiel d'électrode de source du transistor en montage cascode suive le potentiel d'électrode de grille de ce transistor, et

5 il peut également comprendre un générateur de polarisation connecté fonctionnellement entre l'électrode de source du transistor d'entrée à effet de champ et l'électrode de grille du transistor en montage cascode, pour maintenir une différence de potentiel

10 pratiquement constante entre ces électrodes.

Une telle configuration cascode est simple mais efficace, la connexion en série du transistor à effet de champ à montage cascode, avec le transistor d'entrée à transistor à effet de champ, garantissant

15 que le potentiel d'électrode de source du transistor à montage cascode suit automatiquement celui de l'électrode de grille.

20 L'élément amplificateur est de préférence constitué par des première et seconde parties de circuit pratiquement identiques, la première partie comprenant le dispositif d'entrée et le circuit suiveur actif, et la seconde partie comprenant la source de courant.

25 Une telle symétrie de circuit peut permettre d'obtenir un fonctionnement très stable et très prévisible de l'élément amplificateur, en particulier en ce qui concerne la relation entre les potentiels d'entrée et de sortie de l'élément amplificateur, et le circuit peut être fabriqué commodément.

30 L'élément de commutation d'entrée est de préférence un élément de commutation d'entrée électronique, fonctionnant sous la dépendance du potentiel présent sur une électrode de commutation de cet élément, le circuit comprenant en outre des moyens

35 d'attaque de commutation qui sont connectés pour faire

en sorte que le potentiel de l'électrode de commutation suive le potentiel de la borne d'entrée lorsque l'élément est dans son état passant, ce qui a pour effet de maintenir le potentiel de l'électrode de commutation pratiquement fixe par rapport au potentiel de la borne d'entrée, et que l'on peut actionner pour faire en sorte que le potentiel de l'électrode de commutation change, par rapport au potentiel de la borne d'entrée, pour que l'élément soit commuté de son état passant à son état bloqué.

Dans un tel circuit, le potentiel de l'électrode de commande est fixe par rapport au potentiel de la borne d'entrée, ce qui fait que la quantité de charge qui est injectée dans l'élément de commutation électronique au moment de la commutation à l'état bloqué est pratiquement indépendante du niveau du signal d'entrée. Par conséquent, l'erreur dans la tension mémorisée qui est due à une telle injection de charge est pratiquement constante, ou au moins linéaire, pour différentes tensions de signal d'entrée, et on peut donc prendre des mesures appropriées pour compenser une telle erreur.

Le potentiel de l'électrode de commutation est avantageusement obtenu à partir du signal de sortie, de façon que ce potentiel puisse être obtenu sans charger ou affecter d'une autre manière le signal d'entrée.

Selon une caractéristique avantageuse, les moyens d'attaque de commutation sont connectés fonctionnellement à la borne de sortie et on peut les faire fonctionner, sous la dépendance d'un signal de commutation qu'ils reçoivent, de façon à appliquer à l'électrode de commutation soit un potentiel d'état passant, pour maintenir l'élément de commutation d'entrée dans son état passant, soit un potentiel

d'état bloqué, pour maintenir l'élément de commutation d'entrée dans son état bloqué, ces potentiels d'état passant et d'état bloqué étant chacun pratiquement fixes par rapport au potentiel de la borne de sortie, 5 mais différant l'un de l'autre d'une quantité pré-déterminée.

Dans cette configuration, les deux potentiels d'état passant et d'état bloqué sont fixes par rapport au potentiel de signal d'entrée, ce qui fait 10 que l'injection de charge par l'élément de commutation d'entrée est pratiquement constante, indépendamment du potentiel du signal d'entrée.

Le circuit de mémorisation de tension peut parfaitement comporter des première et seconde lignes 15 de polarisation respectives, connectées fonctionnellement à la borne de sortie, de façon à être à des potentiels qui sont respectivement fixes par rapport au potentiel de la borne de sortie, le potentiel de la seconde ligne de polarisation étant égal à l'un des 20 potentiels d'état passant et d'état bloqué, et la différence de potentiel entre les première et seconde lignes de polarisation étant supérieure ou égale à la quantité pré-déterminée. Dans ce cas, les moyens 25 d'attaque de commutation peuvent comprendre un condensateur d'amplificateur à réaction du type "bootstrap", dont une première armature est connectée à l'électrode de commutation pour fournir le potentiel de l'électrode de commutation, et ils peuvent également comprendre des moyens de connexion connectés aux deux 30 armatures du condensateur bootstrap et aux lignes de polarisation, et pouvant être commutés, lorsque le potentiel de l'électrode de commutation doit être changé de l'un de ses potentiels d'état passant et d'état bloqué, à l'autre de ces potentiels, de façon à 35 passer d'une configuration de charge, ayant pour

fonction de connecter la première armature du condensateur bootstrap à la seconde ligne de polarisation, et de connecter la seconde armature de ce condensateur à la première ligne de polarisation, à une configuration flottante ayant pour fonction d'isoler la première armature précitée vis-à-vis de la seconde ligne de polarisation, en connectant la seconde armature à la seconde ligne de polarisation, pour que le potentiel sur la première armature précitée change ainsi en passant du potentiel de la seconde ligne de polarisation à un potentiel qui en diffère de la quantité prédéterminée.

Dans une telle configuration, l'un des potentiels d'état passant et d'état bloqué peut, si nécessaire, être à l'extérieur des potentiels des lignes d'alimentation du circuit.

Selon une variante, le circuit de mémorisation de tension peut comporter des première, seconde et troisième lignes de polarisation respectives, connectées fonctionnellement à la borne de sortie, de façon à être à des potentiels qui sont respectivement fixes par rapport au potentiel de la borne de sortie, le potentiel de la troisième ligne de polarisation étant égal à l'un des potentiels d'état passant et d'état bloqué, et la différence de potentiel entre les première et seconde lignes de polarisation étant supérieure ou égale à la quantité prédéterminée. Dans ce cas, les moyens d'attaque de commutation peuvent comprendre un condensateur d'amplificateur à réaction du type "bootstrap", dont une première armature est connectée à l'électrode de commutation pour fournir le potentiel de l'électrode de commutation, et ils peuvent également comprendre des moyens de connexion connectés aux deux armatures du condensateur bootstrap et aux lignes de polarisation, et pouvant être

commutés, lorsque le potentiel de l'électrode de commutation doit être changé de l'un de ses potentiels d'état passant et d'état bloqué, à l'autre de ces potentiels, de façon à passer d'une configuration de charge, ayant pour fonction de connecter la première armature du condensateur bootstrap à la troisième ligne de polarisation, tout en connectant la seconde armature de ce condensateur à la première ligne de polarisation, à une configuration flottante ayant pour fonction d'isoler la première armature vis-à-vis de la troisième ligne de polarisation, tout en connectant la seconde armature à la seconde ligne de polarisation, pour changer le potentiel sur la première armature, de façon qu'il passe du potentiel de la troisième ligne de polarisation à un potentiel qui diffère de ce dernier de la quantité prédéterminée.

Dans cet exemple, le changement exigé dans le potentiel de l'électrode de commande, à partir du potentiel de la borne de sortie lorsque l'élément de commutation est dans l'un de ses états passant et bloqué, vers un potentiel qui diffère de la quantité prédéterminée par rapport au potentiel de la borne de sortie, lorsque l'élément de commutation est dans l'autre de ses états passant et bloqué, peut être réalisé en utilisant des lignes de polarisation internes dont les potentiels ne conviennent pas pour fournir directement les potentiels d'état passant et d'état bloqué, et/ou dont les potentiels diffèrent du potentiel de la borne de sortie avec un écart inférieur à la quantité prédéterminée.

Il est préférable que l'élément de commutation d'entrée électronique soit un transistor MOS à effet de champ, auquel cas l'un des potentiels d'état passant et d'état bloqué peut être pratiquement identique au potentiel de la borne de sortie. Par

exemple, si le transistor MOS à effet de champ est un transistor du type à canal n et à enrichissement, le potentiel d'état bloqué peut être pratiquement identique au potentiel de la borne de sortie. Avec un 5 tel transistor MOS à effet de champ pour l'élément de commutation électronique, la génération de potentiels d'état passant et d'état bloqué peut être simple, comme il est souhaitable, en particulier dans le cas où le potentiel précité parmi les potentiels d'état 10 passant et d'état bloqué peut être obtenu en appliquant simplement directement le potentiel de la borne de sortie à l'électrode de commande.

Il est préférable que le circuit de mémorisation de tension soit formé sur un seul substrat, et 15 que l'élément de commutation d'entrée et le dispositif d'entrée de l'élément amplificateur se trouvent dans un ou plusieurs caissons du type de conductivité opposé à celui du matériau environnant du substrat, des moyens étant incorporés pour faire en sorte que le 20 potentiel de caisson, ou chacun d'eux, suive le potentiel de la première armature. En commandant de cette manière le potentiel du caisson, on peut éliminer par le montage bootstrap les capacités parasites du circuit (comprenant la capacité de l'élément de commutation et 25 toute capacité d'interconnexion). Le caisson peut par exemple être connecté électriquement à la borne de sortie du circuit. Ceci permet au potentiel du caisson de suivre le potentiel de la borne de sortie.

Le condensateur de mémorisation précité peut 30 également se trouver à l'intérieur d'un tel caisson pour compenser par une configuration bootstrap des capacités parasites qui lui sont associées.

Selon une configuration avantageuse, un ou 35 plusieurs blindages conducteurs s'étendent sur la région du caisson ou de chaque caisson, et des moyens

5       sont incorporés pour faire en sorte que le potentiel ou chaque potentiel de blindage suive le potentiel de la première armature. Ceci contribue à éliminer des effets de capacité parasite résiduelle. Dans un tel cas, le blindage conducteur peut également utilement être connecté électriquement à la borne de sortie du circuit, de façon que le potentiel du blindage suive le potentiel de la borne de sortie.

10     Lorsque l'élément amplificateur du circuit de mémorisation de tension comprend deux parties de circuit pratiquement identiques, comme décrit ci-dessus, la première partie de l'élément amplificateur est de préférence placée à l'intérieur du caisson ou des caissons précités et la seconde partie de l'élément amplificateur est formée dans un ou plusieurs caissons supplémentaires, chacun du type de conductivité opposé à celui des régions environnantes du substrat, le potentiel du caisson ou de chaque caisson supplémentaire étant pratiquement fixe par rapport au potentiel d'une 15     ligne d'alimentation du circuit.

20     Le circuit de mémorisation de tension comprend en outre de préférence des moyens de maintien de potentiel d'entrée, intercalés entre la borne d'entrée et le côté d'entrée de l'élément de commutation d'entrée, dans le but de maintenir le potentiel du côté de l'entrée de l'élément de commutation 25     d'entrée, après le passage de cet élément à l'état bloqué, pratiquement fixe par rapport au potentiel de la première armature du condensateur de mémorisation.

30     Ceci peut éviter que l'élément de commutation d'entrée ne commute accidentellement à l'état passant au cas où le potentiel du signal d'entrée change suffisamment par rapport au potentiel de l'électrode de commande après que l'élément a été 35     commuté à l'état bloqué.

Les moyens de maintien de potentiel d'entrée peuvent comprendre un élément de commutation supplémentaire connecté en série avec l'élément de commutation d'entrée précité, et pouvant être actionné, après que l'élément de commutation d'entrée a été commuté à l'état bloqué, de façon à isoler le côté d'entrée de cet élément vis-à-vis de la borne d'entrée. De cette manière, une variation du potentiel du signal d'entrée après l'ouverture de l'élément de commutation supplémentaire n'affecte pas le potentiel du côté d'entrée de l'élément de commutation d'entrée.

Les moyens de maintien de potentiel d'entrée peuvent en outre comprendre un condensateur auxiliaire connecté entre le côté d'entrée de l'élément de commutation d'entrée et la seconde armature du condensateur de mémorisation, et/ou un élément de commutation de réaction connecté entre l'élément amplificateur et le côté d'entrée de l'élément de commutation d'entrée, et pouvant être actionné, lorsque le côté d'entrée de cet élément doit être isolé, de façon à lui appliquer un potentiel qui est obtenu à partir du potentiel de la première armature du condensateur de mémorisation.

Le gain de l'élément amplificateur est de préférence pratiquement égal à l'unité. Dans ce cas, le potentiel de l'électrode de commande et le ou les potentiels de caisson peuvent commodément être portés par une configuration bootstrap au potentiel de la borne de sortie du fait que, lorsque l'élément amplificateur a un gain pratiquement égal à l'unité, le potentiel de la borne de sortie, après amplification/isolement, est pratiquement égal au potentiel de la première armature/potentiel du signal d'entrée. Par conséquent, le potentiel d'électrode de commande qui est exigé peut être obtenu à partir du signal de sortie après isolation/amplification, sans affecter

le signal d'entrée.

Un circuit de mémorisation de tension (dont l'élément amplificateur a un gain égal à l'unité) du type décrit ci-dessus peut utilement être inclus dans un circuit de sommation de tension qui comprend également :

des premier, second et troisième noeuds d'entrée auxquels des premier, second et troisième potentiels sont appliqués lorsque le circuit est en cours d'utilisation;

10 un noeud de sortie connecté à la borne d'entrée du circuit de mémorisation de tension; et

15 des moyens de commutation connectés aux noeuds d'entrée et au circuit de mémorisation de tension et pouvant être commutés d'une configuration d'entrée à une configuration de sortie, après que l'élément de commutation d'entrée du circuit de mémorisation de tension a été commuté à l'état bloqué, la configuration d'entrée ayant pour fonction de connecter les premier et second noeuds d'entrée respectivement à la borne d'entrée et à la borne commune du circuit de mémorisation de tension, pour permettre ainsi la mémorisation de la différence de potentiel entre les premier et second potentiels dans 20 le condensateur de mémorisation du circuit de mémorisation de tension, et la configuration de sortie ayant pour fonction de connecter la borne commune du circuit de mémorisation de tension au troisième noeud d'entrée, pour produire ainsi sur le noeud de sortie 25 un potentiel qui est pratiquement égal à la somme du troisième potentiel et de la différence mémorisée entre les premier et second potentiels.

30 Un tel circuit de sommation de tension est capable d'effectuer une sommation de tension de très grande précision, la précision étant essentiellement

limitée seulement par l'efficacité avec laquelle on peut éliminer les effets de capacités parasites dans le circuit de mémorisation de tension. Lorsque, dans chaque circuit de mémorisation de tension, les diverses capacités parasites du circuit (la capacité de l'élément de commutation, la capacité d'entrée de l'élément amplificateur et toute capacité d'interconnexion) sont éliminées par une configuration bootstrap en utilisant les techniques indiquées ci-dessus, pratiquement la seule limite sur l'annulation d'effets de capacité parasite résulte de l'erreur de gain des éléments amplificateurs. On peut réduire cette erreur de gain à des niveaux très faibles en adoptant des structures appropriées pour l'élément amplificateur.

Des premier et second circuits de mémorisation de tension, chacun d'eux étant du type décrit ci-dessus et chacun d'eux ayant des éléments amplificateurs à gain égal à l'unité, peuvent avantageusement être inclus dans un circuit de sommation de tension qui comprend également :

des premier, second, troisième, quatrième, cinquième et sixième noeuds d'entrée, une première paire de tensions d'entrée étant appliquée aux premier et second noeuds d'entrée, une seconde paire de tensions d'entrée étant appliquée aux troisième et quatrième noeuds d'entrée, et une troisième paire de tensions d'entrée étant appliquée aux cinquième et sixième noeuds d'entrée, lorsque le circuit est en cours d'utilisation;

des premiers et seconds noeuds de sortie, connectés aux bornes de sortie respectives des premier et second circuits de mémorisation de tension; et

des moyens de commutation connectés aux noeuds d'entrée et aux circuits de mémorisation de tension et pouvant être commutés, après que les

éléments de commutation d'entrée respectifs des premier et second circuits de mémorisation de tension ont été commutés dans leur état bloqué, d'une configuration d'entrée vers une configuration de sortie, la 5 configuration d'entrée ayant pour fonction de connecter les premier et second noeuds d'entrée respectivement à la borne d'entrée et à la borne commune du premier circuit de mémorisation de tension, et également de connecter les troisième et quatrième noeuds d'entrée respectivement à la borne d'entrée et à la 10 borne commune du second circuit de mémorisation de tension, pour permettre ainsi la mémorisation, dans le condensateur de mémorisation du premier circuit de mémorisation de tension, d'une première différence de 15 potentiel entre les deux tensions d'entrée de la première paire, et pour permettre la mémorisation, dans le condensateur de mémorisation du second circuit de mémorisation de tension, d'une seconde différence de potentiel entre les deux tensions d'entrée de la seconde paire, et la configuration de sortie ayant 20 pour fonction de connecter les bornes communes respectives des premier et second circuits de mémorisation de tension respectivement aux cinquième et sixième noeuds d'entrée, pour produire ainsi entre les premier et second noeuds de sortie une paire de tensions de 25 sortie ayant entre elles une différence de potentiel qui est pratiquement égale à la somme de différence de potentiel entre les deux tensions d'entrée de la troisième paire, et la différence entre les première 30 et seconde différences de potentiel mémorisées.

Du fait de la connexion en opposition des deux circuits de mémorisation de tension, les quantités de charge individuelles (fixes) qui sont injectées par les éléments de commutation respectifs de ces 35 circuits au moment où ils sont bloqués, sont les mêmes

pour chaque circuit, et par conséquent elles s'annulent mutuellement de façon effective, si l'on tient compte de la nature différentielle de l'entrée et de la sortie des circuits.

5           Dans un autre exemple préféré, des premier et second circuits de mémorisation de tension, qui sont chacun du type décrit ci-dessus et qui ont chacun des éléments amplificateurs à gain égal à l'unité, peuvent être inclus dans un circuit doubleur de tension qui comprend également :

des premier et second noeuds d'entrée entre lesquels une tension d'entrée à doubler est appliquée lorsque le circuit est en cours d'utilisation;

15          des premier et second noeuds d'entrée connectés respectivement aux bornes de sortie respectives des premier et second circuits de mémorisation de tension; et

20          des moyens de commutation connectés aux noeuds d'entrée et aux circuits de mémorisation de tension et pouvant être commutés d'une configuration d'entrée vers une configuration de sortie, après que les éléments de commutation d'entrée respectifs des premier et second circuits de mémorisation de tension ont été commutés à l'état bloqué, la configuration d'entrée ayant pour fonction de connecter le premier noeud d'entrée à la fois à la borne d'entrée du premier circuit de mémorisation de tension et à la borne commune du second circuit de mémorisation de tension, et également de connecter le second noeud d'entrée à la fois à la borne d'entrée du second circuit de mémorisation de tension et à la borne commune du premier circuit de mémorisation de tension, pour faire ainsi en sorte que chacun des condensateurs de mémorisation respectifs des circuits de mémorisation de tension soit chargé à la tension d'entrée,

et la configuration de sortie ayant pour fonction de connecter ensemble les bornes communes respectives des premier et second circuits de mémorisation de tension, de façon que les condensateurs de mémorisation de 5 tension soient connectés mutuellement en série entre les premier et second noeuds de sortie, pour produire ainsi entre ces noeuds de sortie une tension de sortie qui est pratiquement égale au double de la tension d'entrée.

10 Ici encore, la connexion en opposition des deux circuits de mémorisation de tension permet l'annulation de la charge qui est injectée par les éléments de commutation d'entrée, ce qui fait que la tension doublée est très précise. Le circuit présente 15 un compromis vitesse/puissance/bruit considérablement amélioré, peut-être jusque dans un rapport de dix, par rapport à des propositions antérieures comparables.

Un tel circuit doubleur de tension peut être appliqué de façon particulièrement avantageuse dans 20 des convertisseurs analogique-numérique qui accomplissent des opérations de doublement de tension au cours de leurs opérations de conversion. Un tel convertisseur peut comprendre un étage de conversion de tension comprenant :

25 un circuit doubleur de tension du type décrit ci-dessus;

des moyens comparateurs connectés de façon à recevoir une tension de travail égale à la tension d'entrée, ou obtenue à partir de cette 30 dernière, et également connectés de façon à recevoir un potentiel de comparaison, et capables d'effectuer une comparaison entre cette tension de travail et le potentiel de comparaison, et de fournir des données numériques représentatives du résultat de la comparaison; et 35

des moyens de réglage de tension connectés entre les bornes communes respectives des premier et second circuits de mémorisation de tension et capables, après que les moyens de commutation ont été 5 commutés de la configuration d'entrée à la configuration de sortie, d'appliquer entre ces bornes une tension de décalage ayant une valeur sélectionnée, par les données numériques, parmi un ensemble de valeurs prédéterminées possibles, pour produire ainsi entre 10 les noeuds de sortie une tension de conversion analogique qui diffère du double de la tension d'entrée, avec un écart égal à la tension de décalage sélectionnée.

Dans un tel étage de conversion, grâce à 15 l'utilisation d'un circuit doubleur de tension de haute précision, comme décrit ci-dessus, la tension de conversion analogique peut être obtenue avec une précision élevée souhaitable, à partir de la tension d'entrée, sans l'utilisation de structures de commutation complexes pour interconnecter les deux condensateurs de mémorisation. Cette tension de conversion analogique peut être décalée, par rapport au double de 20 la tension d'entrée, d'une tension de décalage parmi un certain nombre de tensions de décalage présélectionnées, qui est sélectionnée sous la dépendance de 25 la valeur absolue de la tension d'entrée, comme c'est par exemple nécessaire dans des convertisseurs analogique-numérique du type utilisant une "logique à trois états". Les moyens de réglage de tension 30 précités sont connectés entre les bornes communes respectives des premier et second circuits de mémorisation de tension, et ils sont capables d'appliquer la tension de décalage entre ces bornes. De cette manière, du fait que les moyens de réglage de tension 35 sont connectés en série avec les deux condensateurs de

5 mémorisation, de façon à établir entre les secondes armatures des condensateurs une différence de potentiel égale à la tension de décalage sélectionnée, et du fait que chaque condensateur de mémorisation a entre ses armatures respectives une différence de potentiel égale à la tension d'entrée, le décalage exigé de la tension de conversion analogique, par rapport au double de la tension d'entrée, est obtenu de façon simple et précise, sans employer des additionneurs de tension analogiques qui sont complexes et sujets à erreurs.

10

15 Les moyens comparateurs accomplissent de préférence la comparaison pendant que les moyens de commutation des circuits de mémorisation de tension sont dans la configuration d'entrée, ce qui procure un fonctionnement à vitesse élevée.

20 Dans un exemple préféré, les moyens comparateurs sont connectés aux premier et second noeuds d'entrée, de façon que la tension d'entrée soit la tension de travail précitée, et ils fournissent des premières données numériques si la tension d'entrée est inférieure ou égale à l'opposé du potentiel de comparaison, ils fournissent des secondes données numériques si le potentiel de comparaison est inférieur ou égal à la tension d'entrée, et ils fournissent des troisièmes données numériques dans tous les autres cas, et la tension de décalage qui est sélectionnée par les secondes données numériques est  $-V_{ref}$ , en désignant par  $+V_{ref}$  la tension de décalage qui est sélectionnée par les premières données numériques, tandis que la tension de décalage qui est sélectionnée par les troisièmes données numériques est égale à zéro; le potentiel de comparaison étant pratiquement égal à  $V_{ref}/4$ .

25

30

35 Grâce à l'immunité de l'algorithme de

conversion qui est incorporé dans un tel étage de conversion, vis-à-vis d'erreurs de codes manquants qui résulteraient par ailleurs de la tension de décalage des moyens comparateurs, il est possible de bénéficier 5 pleinement de l'amélioration de la précision de l'opération de conversion de tension qui est effectuée par l'étage, lorsqu'on considère la précision de conversion globale.

10 Un convertisseur analogique-numérique de ce type qui est particulièrement avantageux comprend :

une série de N étages, chacun d'eux étant un étage de conversion de tension tel que celui décrit ci-dessus, une tension analogique à numériser étant appliquée entre les premier et second noeuds d'entrée 15 du premier étage de la série, et les premier et second noeuds de chaque étage successif étant connectés respectivement aux premier et second noeuds de sortie de l'étage immédiatement précédent;

des moyens de commande capables de commander 20 les moyens de commutation de chacun des étages, en succession, pour les commuter de la configuration d'entrée à la configuration de sortie, cette commutation étant commandée de façon à avoir lieu dans chacun des étages, à l'exception du premier étage, à un 25 instant auquel les moyens de commutation de l'étage immédiatement précédent sont dans la configuration de sortie, de façon qu'avant une telle commutation l'étage qui est commuté reçoive pour sa tension d'entrée la tension de conversion analogique qui est 30 produite par cet étage immédiatement précédent, et produise ainsi sa tension de conversion analogique sous la dépendance de celle-ci, après une telle commutation; et

35 des moyens de traitement de données qui sont connectés de façon à recevoir les données numériques

fournies par les  $N$  étages, et qui sont capables d'élaborer à partir de ces données un mot de sortie numérique, comprenant  $N+1$  bits, qui est représentatif de la tension analogique appliquée.

5                   Un tel convertisseur analogique-numérique peut fonctionner très rapidement, en produisant un mot de sortie numérique complet à  $N+1$  bits par période d'horloge.

10                  Il est préférable qu'un tel convertisseur analogique-numérique travaille en alternance dans des première et seconde phases d'horloge, et que pendant la première phase d'horloge, les moyens de commande maintiennent les moyens de commutation respectifs des étages de rang impair de la série dans la configuration d'entrée, tandis qu'ils maintiennent les moyens de commutation respectifs des étages de rang pair dans la configuration de sortie, mais que pendant la seconde phase d'horloge les moyens de commande maintiennent les moyens de commutation respectifs des étages de rang pair dans la configuration d'entrée, tandis qu'ils maintiennent les moyens de commutation respectifs des étages de rang impair dans la configuration de sortie.

20                  25                  Cette structure permet au convertisseur de fonctionner à la vitesse élevée mentionnée précédemment, tout en conservant la simplicité de la commande des étages, comme il est souhaitable.

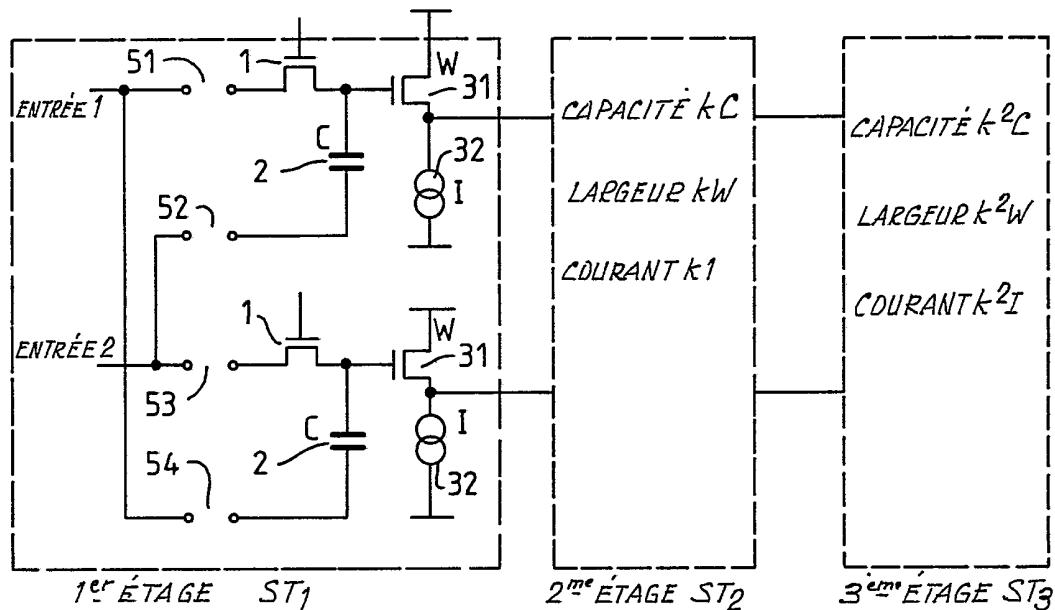

30                  Selon une caractéristique avantageuse, pour au moins une paire d'étages adjacents de la série, les condensateurs de mémorisation respectifs des premier et second circuits de mémorisation de tension dans le second étage de la paire ont une capacité inférieure à celle des condensateurs de mémorisation comparables dans le premier étage de la paire, le rapport des 35                  capacités de mémorisation des deux étages d'une paire

ou de chaque paire étant de préférence d'environ 2:1. Ceci peut contribuer à réduire la puissance consommée par le convertisseur.

5 Pour au moins une paire d'étages adjacents de la série, les dispositifs d'entrée d'éléments amplificateurs respectifs des premier et second circuits de mémorisation de tension dans le second étage de la paire ont de préférence une plus faible largeur que les dispositifs d'entrée comparables dans 10 le premier étage de la paire, le rapport des largeurs des dispositifs d'entrée des deux étages d'une paire ou de chaque paire étant avantageusement approximativement égal à 2:1, ici encore pour réduire la puissance consommée.

15 En outre, pour au moins une paire d'étages adjacents de la série, les courants respectifs dans les chemins de courant commandés des dispositifs d'entrée d'éléments amplificateurs des premier et second circuits de mémorisation de tension dans le 20 second étage de la paire peuvent être plus faibles que les courants comparables dans le premier étage de la paire, le rapport de courant des deux étages d'une paire ou de chaque paire étant de préférence approximativement égal à 2:1, ici encore pour contribuer à 25 réduire la puissance consommée.

30 Selon une caractéristique avantageuse, dans chacun des étages du convertisseur allant du second au n-ième, avec  $2 \leq n \leq N$ , chacun des condensateurs de mémorisation respectifs des premier et second circuits de mémorisation de tension de l'étage a une capacité qui est réduite, par rapport à la capacité du condensateur de mémorisation comparable de l'étage immédiatement précédent, d'un premier facteur de proportionnalité qui est constant dans l'ensemble de ces second 35 à n-ième étages. Le fait de proportionner ainsi la

capacité avec un facteur de proportionnalité constant contribue à réduire la puissance consommée par le convertisseur et à réduire l'aire de puce qui est nécessaire pour réaliser le convertisseur.

5 Le premier facteur de proportionnalité précité est de préférence égal à 2. Cette valeur de facteur de proportionnalité est optimale en ce qui concerne la réduction de la puissance consommée.

10 Selon une caractéristique avantageuse, dans chacun des étages du convertisseur allant du second au n-ième, avec  $2 \leq n \leq N$ , le dispositif d'entrée d'élément amplificateur de chaque circuit de mémorisation de tension de l'étage a une largeur de canal qui est réduite, par rapport à la largeur de canal du dispositif d'entrée d'élément d'amplificateur comparable de l'étage immédiatement précédent, d'un second facteur de proportionnalité qui est constant dans l'ensemble de ces second à n-ième étages.

20 Le fait de proportionner ainsi avec un facteur constant un certain nombre d'étages successifs peut également contribuer à réduire la puissance consommée par le convertisseur et l'aire de puce qui est occupée par ce dernier.

25 Le second facteur de proportionnalité est également de préférence égal à 2. Ceci conduit à une réduction optimale de la puissance consommée.

30 Selon une autre caractéristique avantageuse, dans chacun des étages du convertisseur allant du second au n-ième, avec  $2 \leq n \leq N$ , le courant dans chacun des chemins de courant commandés des dispositifs d'entrée d'élément amplificateur de l'étage est commandé de façon à être réduit, par rapport au courant dans le chemin de courant commandé comparable de l'étage immédiatement précédent, d'un troisième facteur de proportionnalité qui est constant dans

l'ensemble de ces second à n-ième étages.

Le fait de proportionner ainsi le courant peut contribuer encore davantage à réduire la puissance consommée par le convertisseur.

5 Le troisième facteur de proportionnalité est également de préférence égal à 2. Cette valeur est optimale en ce qui concerne la réduction de la puissance consommée.

10 Dans un autre mode de réalisation préféré, pour au moins une paire d'étages adjacents de la série, l'une au moins des valeurs possibles prédéterminées de la tension de décalage dans le second étage de la paire est réglée de manière fractionnaire en comparaison avec la valeur possible prédéterminée 15 correspondante de la tension de décalage dans le premier étage de la paire.

20 On peut utiliser un tel réglage fractionnaire pour corriger des erreurs de gain dans les éléments amplificateurs qui sont utilisés dans chaque étage, et ce réglage permet donc de maintenir un fonctionnement de haute précision du convertisseur global, malgré des imperfections dans ces éléments amplificateurs.

25 A la place, ou en plus, les moyens de traitement de données peuvent régler de manière fractionnaire les données numériques qui sont fournies par les moyens comparateurs respectifs d'étages successifs de la série, afin de faciliter la correction d'erreurs de conversion de tension dans ces étages successifs.

30 Un autre convertisseur analogique-numérique avantageux comprend :

35 des premier et second étages, chacun d'eux étant un étage de conversion de tension du type décrit ci-dessus, connectés ensemble de façon que les premier et second noeuds de sortie du premier étage soient

connectés respectivement aux premier et second noeuds d'entrée du second étage, et de façon que les premier et second noeuds de sortie du second étage soient connectés respectivement aux premier et second noeuds d'entrée du premier étage, une tension analogique à numériser étant appliquée, au début d'une opération de conversion itérative du convertisseur, entre les premier et second noeuds d'entrée du premier étage;

des moyens de commande capables de faire en sorte que les moyens de commutation des premier et second étages soient commutés en alternance, en partant du premier étage, de la configuration d'entrée vers la configuration de sortie, cette commutation étant commandée de façon à avoir lieu dans un étage à un instant auquel les moyens de commutation de l'autre étage sont dans la configuration de sortie, de façon qu'avant une telle commutation l'étage qui est commuté reçoive pour sa tension d'entrée la tension de conversion analogique qui est produite par l'autre étage, et produise ainsi sa tension de conversion analogique sous la dépendance de la tension précitée, après une telle commutation; et

des moyens de traitement de données connectés de façon à recevoir les données numériques qui sont fournies en alternance par les premier et second étages, au cours de l'opération de conversion itérative, et capables d'élaborer à partir de ces données un mot numérique de sortie représentatif de la tension analogique appliquée.

Dans un tel convertisseur analogique-numérique, deux étages seulement sont nécessaires pour effectuer une opération de conversion, ce qui conduit à une structure simple et ayant un faible encombrement, comme il est souhaitable.

Un second aspect de la présente invention

procure un convertisseur analogique-numérique, capable de fonctionner en alternance dans des première et seconde phases d'horloge, comprenant :

5 des premier et second noeuds d'entrée entre lesquels une tension d'entrée analogique à numériser peut être appliquée lorsque le convertisseur est en cours d'utilisation;

10 des premier et second circuits de mémorisation de tension, chacun d'eux comprenant des premier et second condensateurs de mémorisation respectifs et un élément amplificateur à gain égal à l'unité, ayant des bornes d'entrée et de sortie respectives, cet élément comprenant un dispositif d'entrée électronique ayant un chemin de courant commandé qui est établi

15 entre des première et seconde électrodes de chemin de courant respectives du dispositif, et ayant également une électrode de commande à laquelle un potentiel est appliqué pour commander l'intensité du courant dans le chemin de courant, cette électrode de commande étant

20 connectée à la borne d'entrée de l'élément amplificateur, et les première et seconde électrodes de chemin de courant étant connectées à des moyens suiveurs de potentiel, de façon que le potentiel de la première électrode de chemin de courant et le potentiel de la

25 seconde électrode de chemin de courant suivent le potentiel de l'électrode de commande, pendant qu'un courant circule dans le chemin de courant commandé, de façon que les potentiels respectifs des première et seconde électrodes de chemin de courant soient

30 maintenus pratiquement fixes par rapport au potentiel de la borne d'entrée;

35 des moyens d'échantillonnage d'entrée capables de fonctionner pendant l'une initiale des phases d'horloge, de façon à connecter la borne d'entrée du premier circuit de mémorisation de tension au premier

noeud d'entrée, et à connecter la borne d'entrée du second circuit de mémorisation de tension au second noeud d'entrée;

5 des premier et second noeuds de sortie qui sont respectivement connectés aux bornes de sortie d'élément amplificateur des premier et second circuits de mémorisation de tension;

10 des moyens comparateurs connectés aux premier et second noeuds de sortie, et également connectés de façon à recevoir un potentiel de comparaison, et pouvant fonctionner dans chaque phase d'horloge de façon à effectuer une comparaison entre la différence de potentiel entre les premier et second noeuds de sortie, et le potentiel de comparaison, et à 15 fournir des données numériques représentatives du résultat de la comparaison;

20 des moyens de réglage de tension comportant une paire de bornes de connexion et pouvant fonctionner dans chaque phase d'horloge de façon à appliquer entre ces bornes une tension de décalage ayant une valeur sélectionnée, par les données numériques qui sont fournies par les moyens comparateurs au cours de la phase d'horloge immédiatement précédente, parmi un ensemble de valeurs possibles prédéterminées;

25 des moyens de commutation pouvant fonctionner dans la première phase d'horloge de façon à connecter les deux premiers condensateurs de mémorisation et les bornes de connexion en série entre les bornes d'entrée respectives des éléments amplificateurs, tout en connectant les seconds condensateurs de mémorisation, mutuellement en parallèle, entre les 30 premier et second noeuds de sortie, et capables de fonctionner dans la seconde phase d'horloge de façon à connecter les seconds condensateurs de mémorisation et 35 les bornes de connexion en série entre les bornes

d'entrée respectives des éléments amplificateurs, tout en connectant les premiers condensateurs de mémorisation mutuellement en parallèle entre les premier et second noeuds de sortie; et

5 des moyens de traitement de données connectés de façon à recevoir les données numériques qui sont fournies par les moyens comparateurs, sur un nombre prédéterminé des phases d'horloge, et capables d'élaborer à partir de celles-ci un mot de sortie

10 numérique qui est représentatif de la tension d'entrée analogique appliquée.

15 Un tel convertisseur analogique-numérique n'exige qu'un seul étage pour effectuer une opération de conversion, ce qui conduit à une structure ayant une taille particulièrement réduite.

Un troisième aspect de la présente invention procure un convertisseur analogique-numérique comprenant un ensemble d'étages de conversion de tension mutuellement similaires, qui sont connectés en série de façon que la sortie d'un étage applique une information d'entrée à l'étage suivant, chaque étage comprenant un condensateur de mémorisation qui peut être connecté sélectivement à l'entrée de l'étage pour mémoriser une tension d'entrée de l'étage, et comprenant également un élément amplificateur qui peut être connecté sélectivement entre le condensateur de mémorisation et la sortie de l'étage, pour fournir une tension de sortie de l'étage qui dépend de la tension d'entrée mémorisée, dans lequel dans au moins un étage 20 de la série, autre que le premier étage, la capacité du condensateur de mémorisation est inférieure à la capacité du condensateur de mémorisation de l'étage immédiatement précédent, et/ou la largeur d'un transistor d'entrée de l'élément amplificateur est inférieure à la largeur du transistor d'entrée de

25

30

35

l'élément amplificateur de l'étage immédiatement précédent.

Un tel convertisseur analogique-numérique, employant une série d'étages de conversion de tension 5 "proportionnés", peut parvenir à un meilleur compromis global entre le bruit et la puissance consommée. Le facteur (facteur de proportionnalité) par lequel la capacité du condensateur de mémorisation et/ou la largeur du transistor d'entrée est réduite d'un étage 10 au suivant, est de préférence proche de 2. On peut arrêter la réduction proportionnelle après les quelques premiers étages; par exemple il peut y avoir une réduction proportionnelle d'un étage au suivant dans les six premiers étages, et ensuite les étages 15 restants peuvent avoir une taille constante.

D'autres caractéristiques et avantages de l'invention seront mieux compris à la lecture de la description qui va suivre de modes de réalisation, donnés à titre d'exemples non limitatifs. La suite de 20 la description se réfère aux dessins annexés dans lesquels :

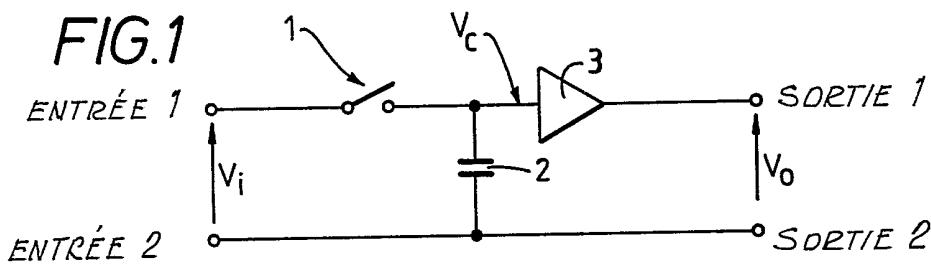

La figure 1, que l'on a envisagée précédemment, montre un schéma d'un circuit de mémorisation de tension considéré antérieurement;

25 La figure 2, qui a également été envisagée précédemment, montre de façon plus détaillée un élément amplificateur qui fait partie du circuit de la figure 1;

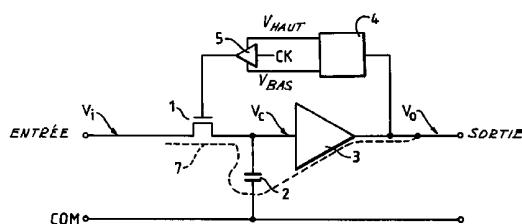

30 La figure 3 montre un schéma d'un circuit de mémorisation de tension qui met en oeuvre le premier aspect précité de l'invention;

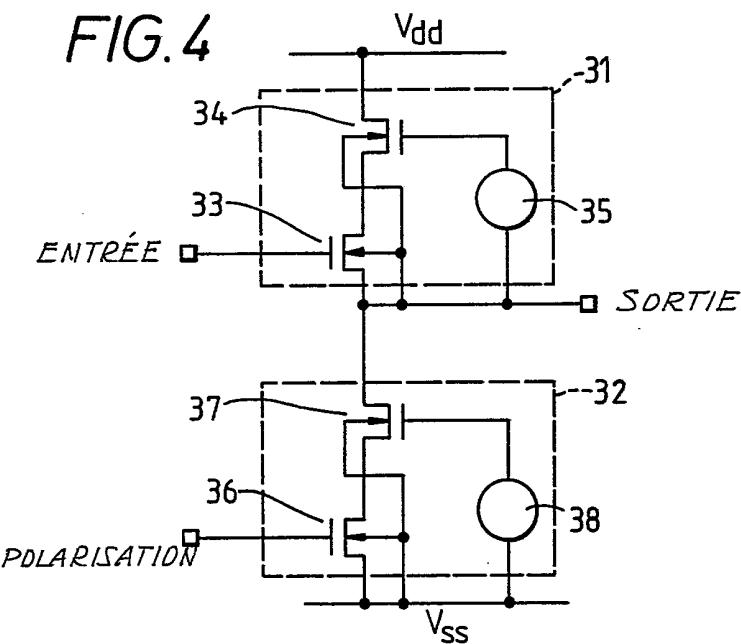

La figure 4 montre une structure d'un élément amplificateur qui fait partie du circuit de la figure 3;

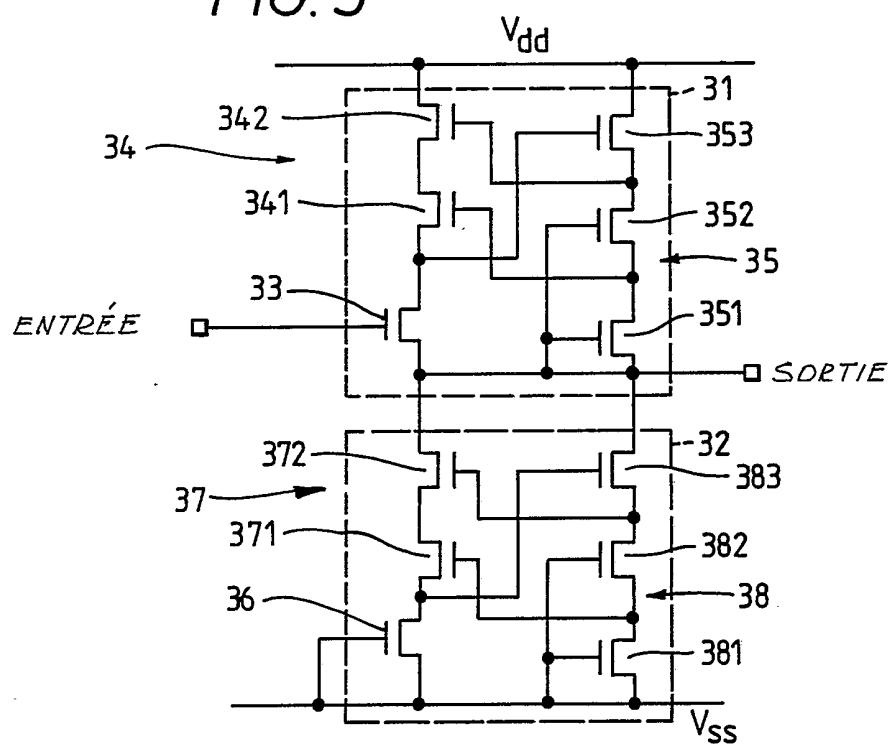

35 La figure 5 montre une autre structure

d'élément amplificateur prévu pour l'utilisation dans le circuit de la figure 3;

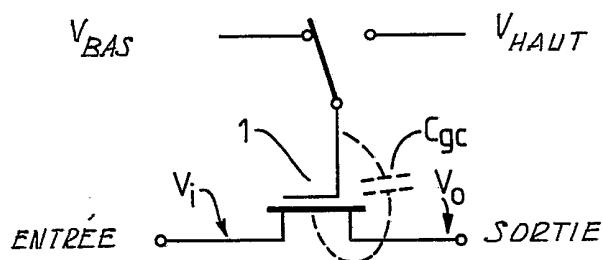

5 La figure 6 montre de façon plus détaillée un élément de commutation d'entrée qui fait partie du circuit de la figure 3;

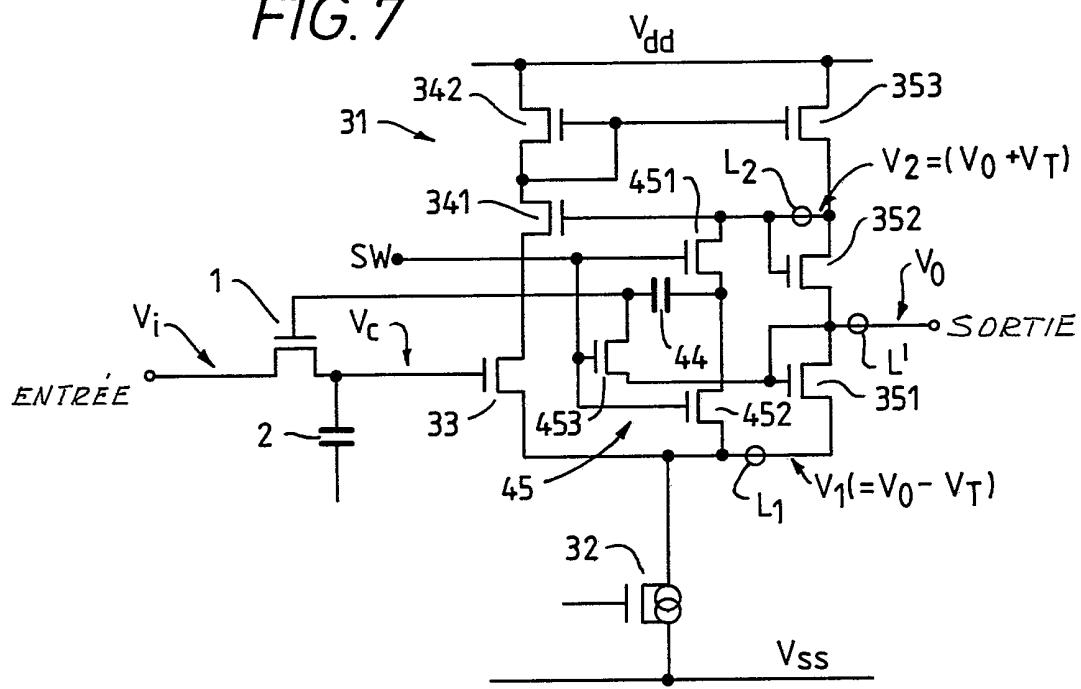

La figure 7 montre encore une autre structure d'élément amplificateur, ainsi qu'un exemple de moyens d'attaque de commutation, pour l'utilisation dans le circuit de la figure 3;

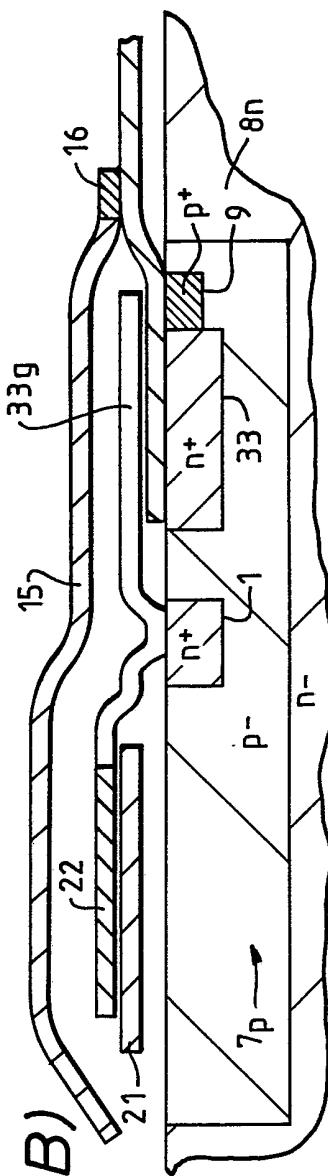

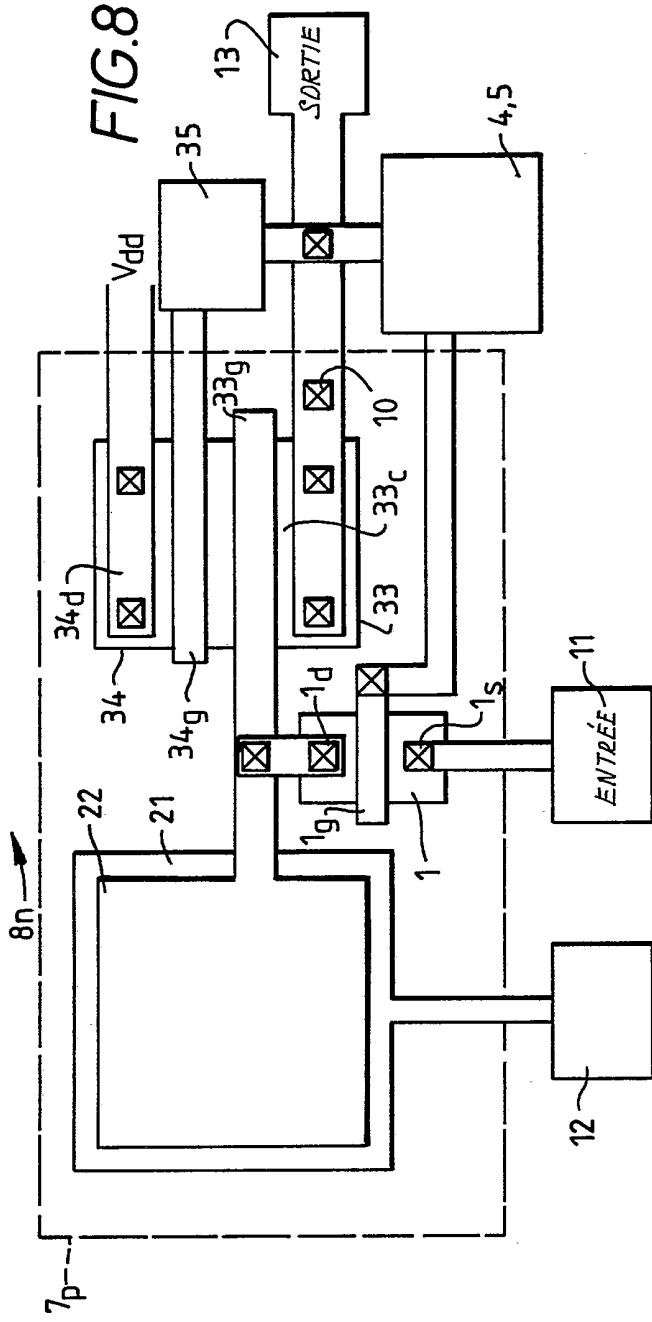

10 Les figures 8(A) et 8(B) montrent respectivement des représentations en plan et en coupe qui illustrent une implantation possible du circuit de la figure 3 sur un substrat de circuit intégré;

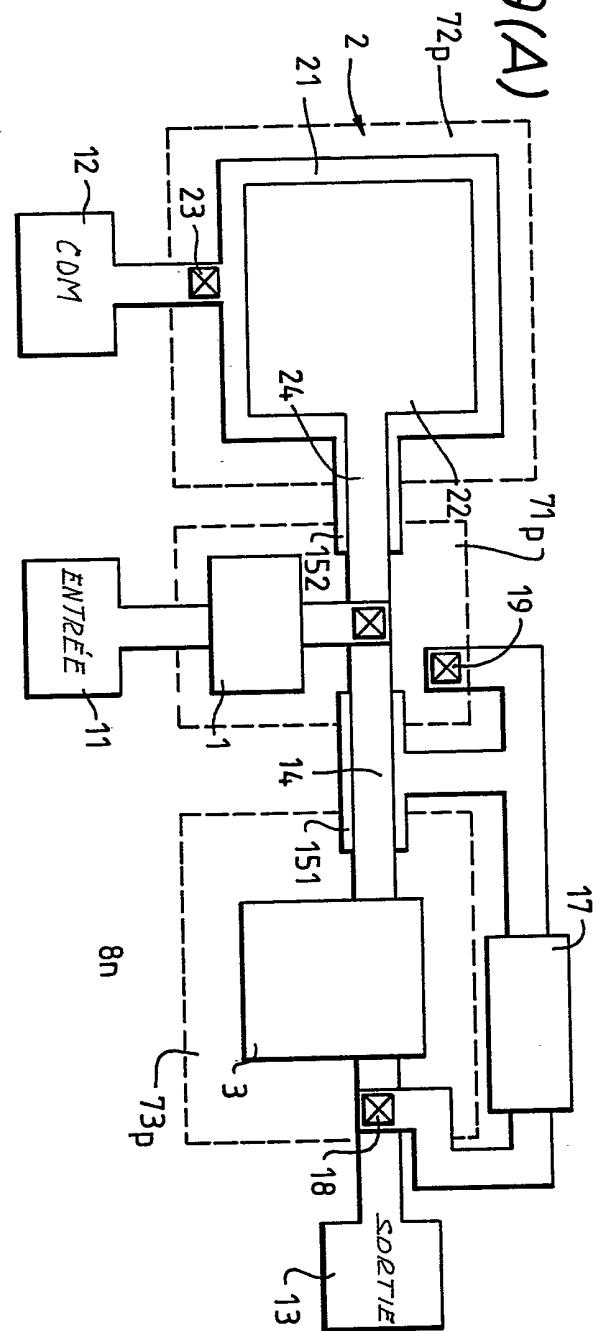

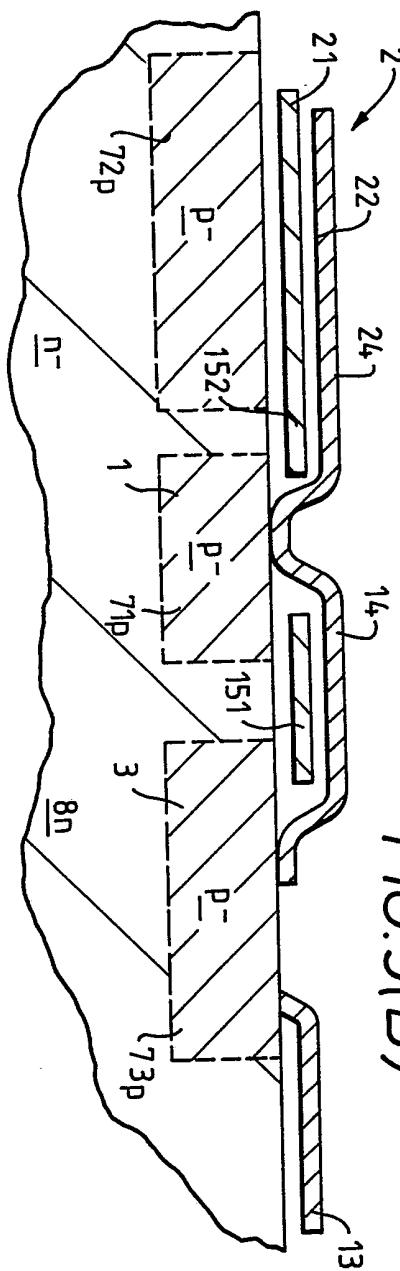

15 Les figures 9(A) et 9(B) montrent respectivement des représentations en plan et en coupe qui illustrent une autre implantation possible du circuit de la figure 3 sur un substrat de circuit intégré;

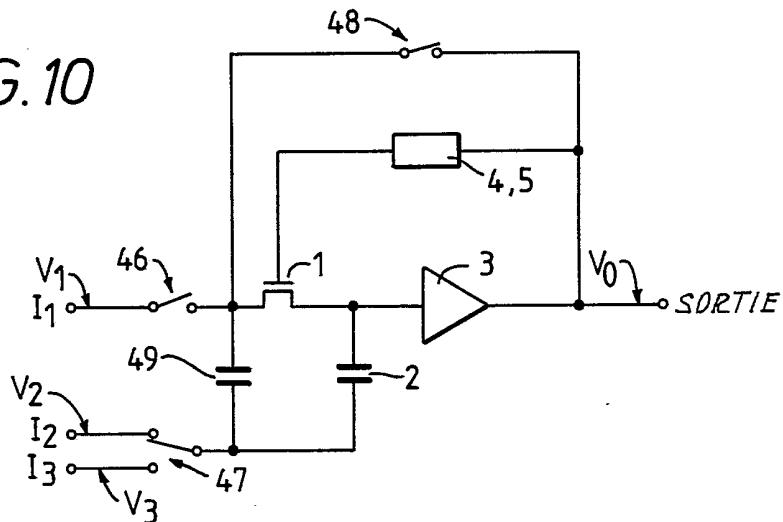

20 La figure 10 montre un schéma d'un circuit de sommation de tension qui utilise un circuit de mémorisation de tension du type représenté sur la figure 3;

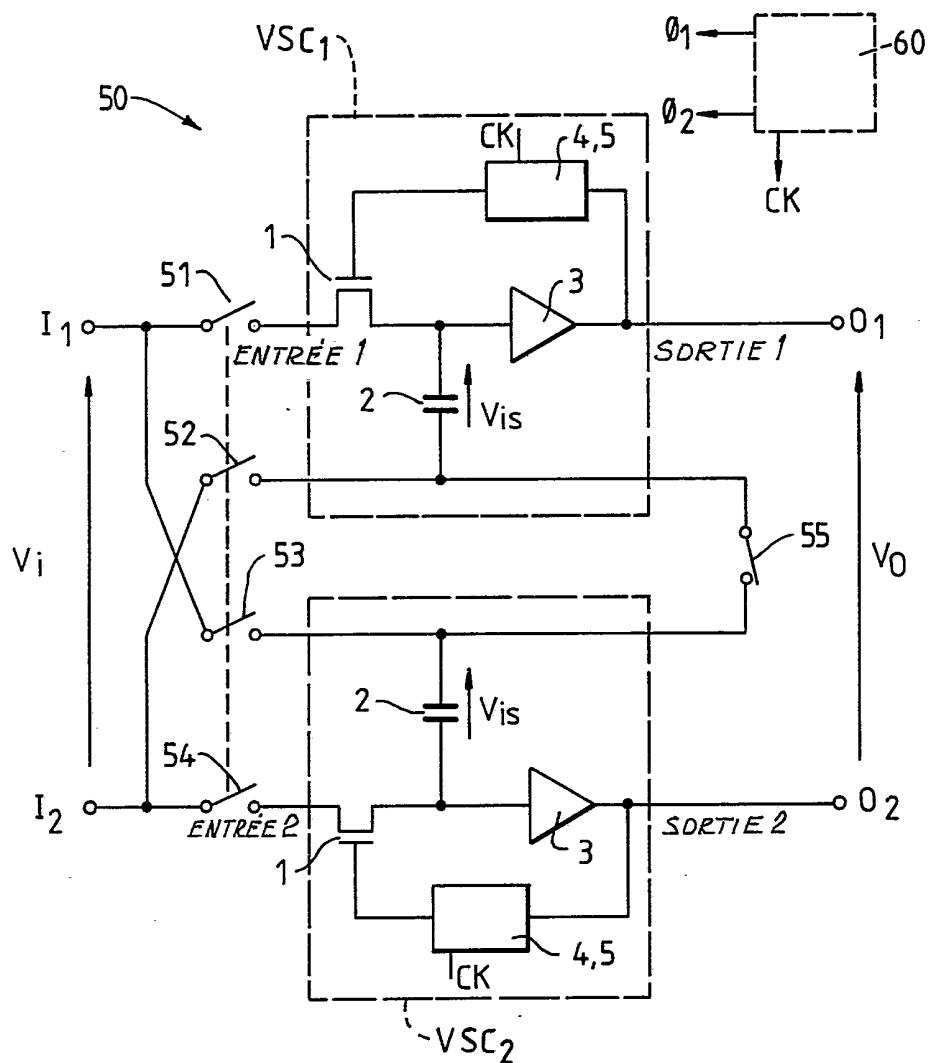

25 La figure 11 montre un schéma d'un circuit doubleur de tension qui utilise deux circuits de mémorisation de tension du type représenté sur la figure 3;

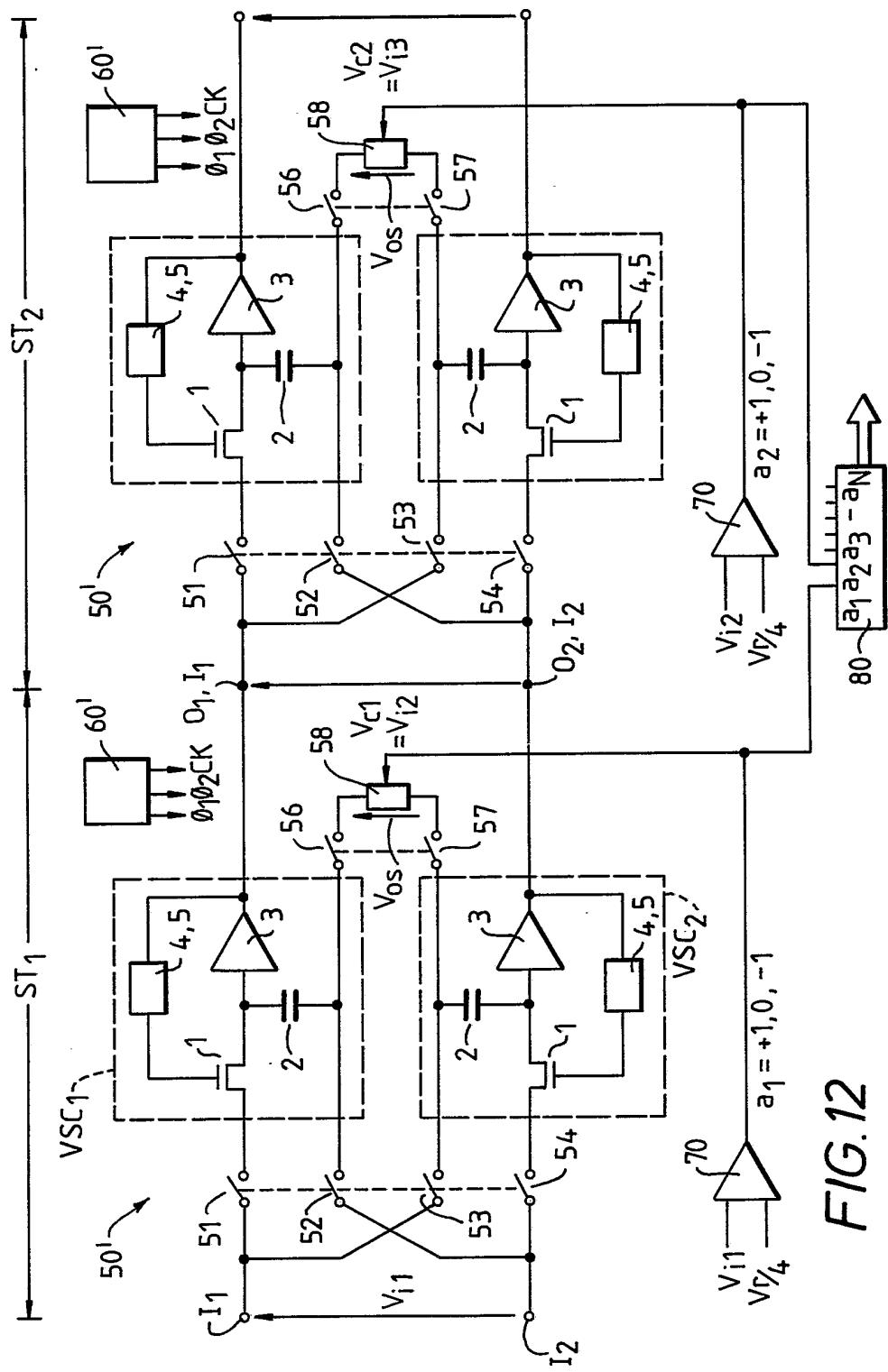

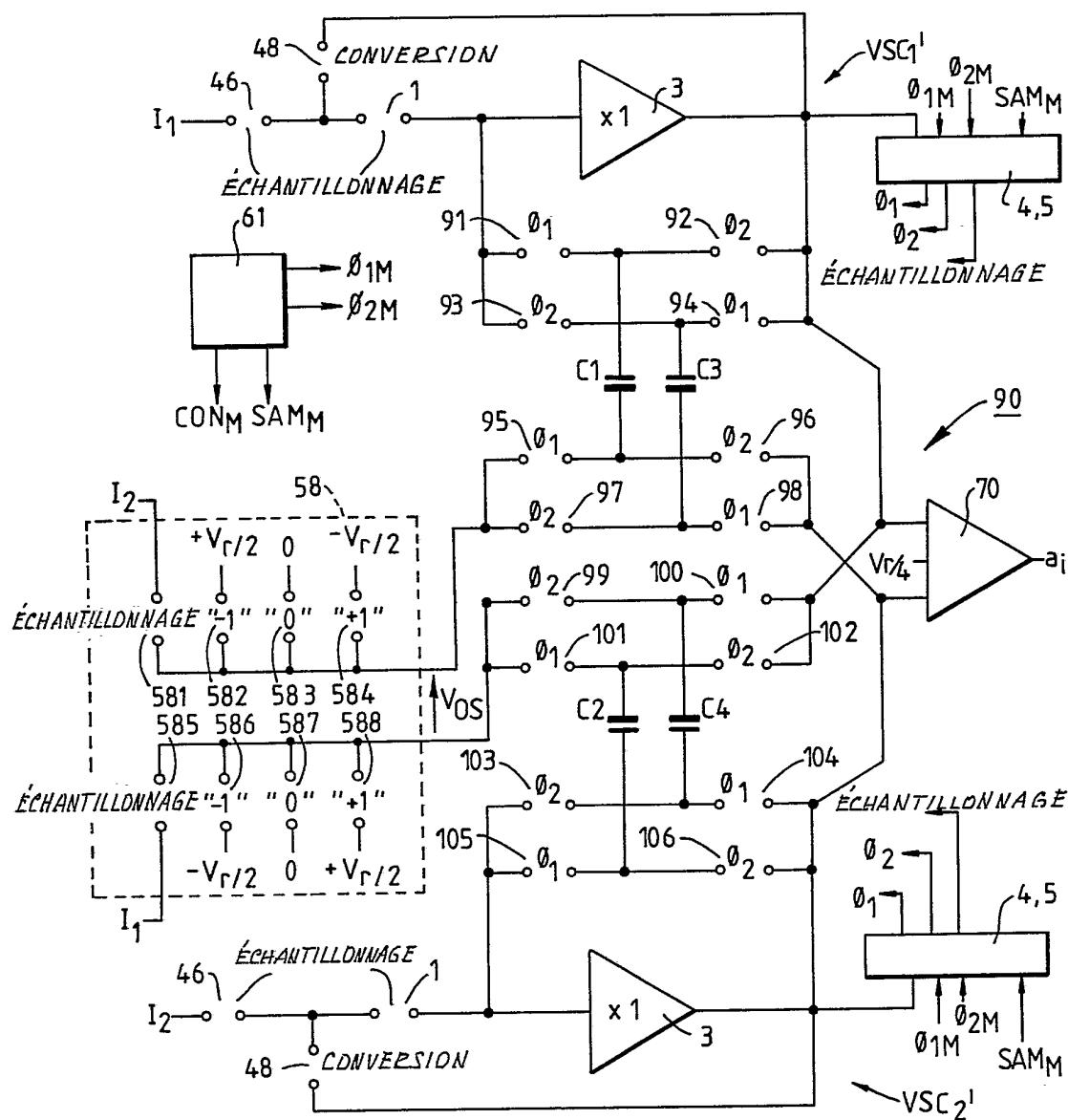

30 La figure 12 montre un schéma de circuit de certaines parties d'un convertisseur analogique-numérique comprenant un ensemble d'étages de conversion qui sont respectivement basés sur le circuit doubleur de tension de la figure 11;

35 La figure 13 montre un schéma de circuit de certaines parties d'un convertisseur analogique-numérique, ayant un seul étage de conversion, qui met en oeuvre le second aspect précité de la présente invention;

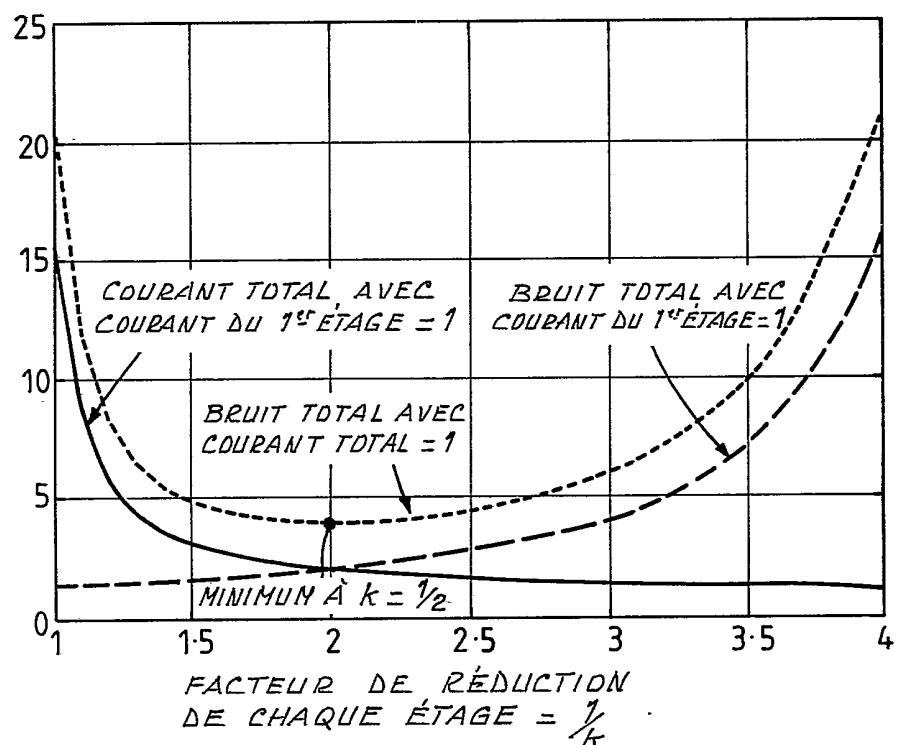

La figure 14 est un schéma de certaines parties du convertisseur de la figure 12, qui est destiné à illustrer des avantages de l'application d'un facteur de proportionnalité entre les étages successifs du convertisseur de la figure 12;

La figure 15 est une représentation graphique qui, dans le cas d'un convertisseur tel que celui représenté sur la figure 12, ayant 16 étages, illustre la relation entre le courant consommé total du convertisseur et le facteur de proportionnalité, et la relation entre le bruit total dans le convertisseur et le facteur de proportionnalité; et

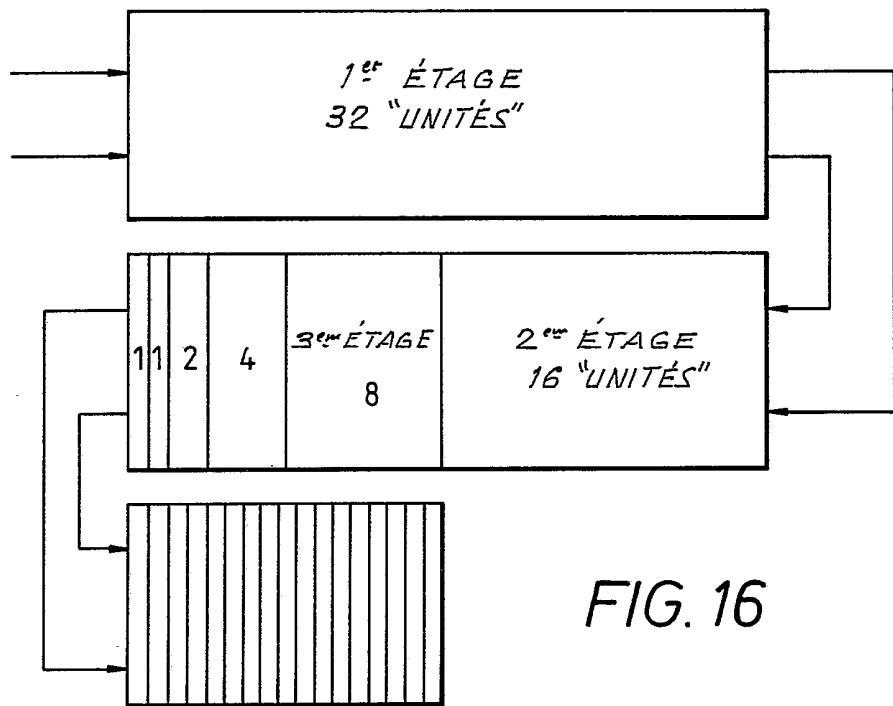

La figure 16 est un schéma qui illustre un exemple de l'implantation du convertisseur de la figure 12 sur une puce de circuit intégré.

Le circuit de mémorisation de tension de la figure 3 comprend un élément de commutation électronique 1, de préférence un transistor à effet de champ MOS, un condensateur de mémorisation 2, un amplificateur-séparateur à gain égal à l'unité, 3, et des moyens d'attaque de commutation à configuration bootstrap, 4, 5, connectés entre un circuit de borne de sortie et l'électrode de grille (électrode de commande) du transistor à effet de champ MOS 1.

La figure 4 montre un premier exemple de la structure de l'élément amplificateur 3 dans le circuit de la figure 3. L'élément 3 comprend deux parties de base, à savoir un circuit à charge de source de type cascode 31 et une source de courant 32.

Le circuit à charge de source de type cascode 31 comprend un transistor d'entrée MOS à canal n 33 dont l'électrode de grille est connectée à une armature (l'armature supérieure sur la figure 3) du condensateur de mémorisation 2. Le canal drain-source du transistor d'entrée 33 est connecté en série avec

le canal drain-source d'un transistor MOS à canal n supplémentaire, que l'on appellera ci-après un transistor de connexion en cascode 34. L'électrode de drain du transistor de connexion en cascode 34 est 5 connectée à une ligne d'alimentation positive  $V_{dd}$  du circuit, tandis que l'électrode de source du transistor d'entrée 33 est connectée à une borne de sortie SORTIE du circuit.

Egalement dans le circuit à charge de source 10 de type cascode 31, un générateur de polarisation 35 est connecté entre l'électrode de source du transistor d'entrée 33 et l'électrode de grille du transistor de connexion en cascode 34. Ce générateur de polarisation a pour fonction de maintenir une différence de potentiel pratiquement constante entre l'électrode de grille du transistor de connexion en cascode et 15 l'électrode de source du transistor d'entrée 33, indépendamment d'une variation du potentiel de l'électrode de source.

La source de courant 32 est constituée de façon pratiquement identique au circuit à charge de source de type cascode 31, et elle comprend deux 20 transistors MOS à canal n 36 et 37 (correspondant respectivement aux transistors 33 et 34 du circuit à charge de source de type cascode 31), connectés en série entre la borne de sortie SORTIE du circuit et une ligne d'alimentation négative  $V_{ss}$  du circuit, et 25 un générateur de polarisation associé 38 (correspondant au générateur de polarisation 35 dans le circuit à charge de source de type cascode 31), qui a pour fonction de maintenir une différence de potentiel pratiquement constante entre l'électrode de grille du transistor 37 et l'électrode de source du transistor 36. Dans ce cas, l'électrode de source du transistor 30 36 est directement connectée à la ligne d'alimentation 35

négative  $V_{ss}$ , de façon que le potentiel de l'électrode de grille du transistor 37 soit fixe par rapport à la ligne d'alimentation négative. La source de courant 32 comporte une borne d'entrée de polarisation, portant 5 la désignation POLARISATION qui est connectée à l'électrode de grille du transistor 36. On peut appliquer un potentiel de polarisation à l'entrée de polarisation de la source de courant 32, pour commander le fonctionnement de l'élément, comme on le décrira ci- 10 après.

Du fait que la source de courant 32 est connectée en série avec le circuit à charge de source de type cascode 31, elle établit un chemin de courant entre les lignes d'alimentation positive et négative 15  $V_{dd}$  et  $V_{ss}$ .

Dans le fonctionnement de l'élément amplificateur de la figure 4, on peut faire fonctionner la source de courant de façon qu'un courant pratiquement constant circule dans le chemin de courant mentionné 20 ci-dessus, et donc dans chacun des transistors 33 et 34 du circuit à charge de source de type cascode 31. Ceci fait en sorte que le potentiel de l'électrode de source du transistor d'entrée 33 suive le potentiel de l'électrode de grille de ce transistor, de façon que 25 le potentiel de la borne de sortie  $V_o$  suive le potentiel  $V_c$  de l'armature supérieure du condensateur de mémorisation 2.

Par conséquent, le gain en tension de l'élément est pratiquement égal à l'unité.

30 De façon similaire, le potentiel de l'électrode de source du transistor de connexion en cascode 34 suit le potentiel de l'électrode de grille de ce transistor, ce potentiel étant à son tour maintenu par le générateur de polarisation 35 pratiquement fixe par rapport au potentiel de l'électrode de source du 35

transistor d'entrée 33. Par conséquent, le potentiel de l'électrode de drain du transistor d'entrée 33 suit le potentiel de l'électrode de source de ce transistor, et il suit donc également le potentiel  $V_C$  de l'armature supérieure du condensateur de mémorisation 2.

Comme on peut le voir, indépendamment du potentiel  $V_C$  de l'armature supérieure du condensateur de mémorisation 2, les potentiels des électrodes de source et de drain du transistor d'entrée 33 sont pratiquement fixes l'un par rapport à l'autre et par rapport au potentiel de l'électrode de grille de ce transistor d'entrée. Par conséquent, les capacités parasites grille-source, grille-drain et drain-source  $C_{gs}$ ,  $C_{gd}$ ,  $C_{ds}$  ne sont pas chargées ou déchargées lorsque le potentiel  $V_C$  de l'armature supérieure du condensateur de mémorisation 2 varie, et ces capacités parasites n'ont donc pratiquement aucun effet sur la tension qui est mémorisée dans le condensateur de mémorisation 2.

Du fait que le transistor d'entrée 3 est un transistor d'entrée à effet de champ, le courant de grille est pratiquement égal à zéro, ce qui fait que la charge qui est mémorisée dans le condensateur de mémorisation ne diminue pas notablement sous l'effet du fonctionnement de l'élément amplificateur 3 après que l'élément de commutation d'entrée 1 a été ouvert.

Dans l'élément amplificateur de la figure 4, le potentiel réel sur la borne de sortie n'est pas exactement égal au potentiel de l'armature supérieure  $V_C$ , mais est légèrement réduit conformément à la tension différentielle grille-source à l'état passant du transistor 33, comme l'indique l'expression suivante :

$$V_O = V_C - (V_T + V_{DSAT})$$

dans laquelle  $V_T$  est la tension de seuil du transistor d'entrée 33 et  $V_{DSAT}$  est la tension de saturation du transistor d'entrée 33.

Comme il ressort de la figure 4, le circuit à charge de source de type cascode 31 et la source de courant 32 ont des structures qui sont pratiquement identiques l'une à l'autre. Ainsi, l'homologue du transistor d'entrée 33 du circuit à charge de source de type cascode 31, est le transistor 36 dans la source de courant 32, ce transistor 36 recevant le potentiel de polarisation précité. Du fait que le même courant circule dans les canaux drain-source respectifs des transistors 33 et 36, et du fait que ces transistors ont des dimensions identiques, on peut commander le potentiel grille-source du transistor 33 en réglant le potentiel grille-source du transistor 36 dans la source de courant 32. Ce potentiel grille-source du transistor 36 est égal à la différence entre le potentiel de polarisation et le potentiel de la ligne d'alimentation négative, ce qui fait qu'en appliquant un potentiel de polarisation constant approprié à la borne de polarisation, on peut régler à un niveau avantageusement faible et constant la différence entre le potentiel  $V_o$  de la borne de sortie et le potentiel  $V_c$  de l'armature supérieure du condensateur de mémorisation 2.

Dans l'élément amplificateur de la figure 4, les transistors 33, 34, 36 et 37 peuvent être du type à désertion ou à enrichissement.

La figure 5 montre un exemple plus perfectionné de la structure de l'élément amplificateur 3, employant des transistors MOS à canal n du type à désertion pour donner un fonctionnement rapide. Dans l'exemple de la figure 5, l'élément amplificateur comprend à nouveau un circuit à charge de source de

type cascode 31 et une source de courant 32, et le transistor d'entrée à effet de champ 33 dans le circuit à charge de source de type cascode 31 est à nouveau connecté dans la configuration à charge de source de type cascode que l'on a décrite précédemment en relation avec la figure 4, l'électrode de grille du transistor 33 étant connectée de façon à recevoir le potentiel  $V_C$  de l'armature supérieure du condensateur de mémorisation 2, l'électrode de source du transistor 33 étant connectée à la borne de sortie du circuit, portant la désignation SORTIE, et l'électrode de drain du transistor 33 étant connectée par l'intermédiaire d'un premier et d'un second transistor de connexion entre cascode, 341 et 342, à la ligne d'alimentation positive  $V_{dd}$  du circuit.

Dans ce cas, le générateur de polarisation de type cascode 35 comprend trois transistors connectés en série, 351, 352 et 353, qui sont connectés de façon à appliquer des potentiels de polarisation appropriés aux électrodes de grille respectives des premier et second transistors de connexion en cascode 341 et 342, afin que les électrodes de grille respectives des transistors de connexion en cascode 341 et 342 soient respectivement maintenues à des potentiels pratiquement fixes par rapport au potentiel de l'électrode de source du transistor d'entrée 33.

La source de courant 32 de l'élément amplificateur de la figure 5 a une structure identique à celle de son circuit à charge de source de type cascode, 31, et elle comprend trois transistors connectés en série 36, 371 et 372 (correspondant respectivement aux transistors 33, 341 et 342 du circuit à charge de source de type cascode 31), qui sont connectés entre l'électrode de source du transistor d'entrée 31 et la ligne d'alimentation négative

V<sub>ss</sub>. Dans ce cas, le potentiel de l'électrode de grille du transistor 36 (qui équivaut au potentiel de polarisation qui est appliqué à l'entrée de polarisation dans l'élément amplificateur de la figure 4), est fourni par la ligne d'alimentation négative V<sub>ss</sub>, tandis que les potentiels des électrodes de grille respectives des transistors 371 et 372 sont fournis par un générateur de polarisation 38 (ayant une structure identique à celle du générateur de polarisation 35 dans le circuit à charge de source de type cascode 31), qui comprend trois transistors connectés en série, 381 à 383. On pourra voir que les générateurs de polarisation 35 et 38 sont connectés mutuellement en série entre les lignes d'alimentation positive et négative, de façon à établir un chemin de courant supplémentaire entre elles.

Dans l'élément amplificateur de la figure 5, du fait que l'électrode de grille du transistor 36 dans la source de courant 32 est directement connectée à la ligne d'alimentation négative V<sub>ss</sub>, les potentiels de grille et de source du transistor 36 sont mutuellement égaux. Du fait que le même courant drain-source circule dans le transistor 33 et dans son transistor homologue 36 dans la source de courant 32, et du fait que le circuit à charge de source de type cascode 31 et la source de courant 32 ont une structure pratiquement identique, il en résulte que les potentiels de grille et de source du transistor d'entrée 33 dans le circuit à charge de source de type cascode 31 seront également pratiquement égaux l'un à l'autre. Ainsi, le gain en tension de l'élément amplificateur de la figure 5 est plus proche de l'unité (approximativement 0,9995) que dans le cas de l'élément amplificateur de la figure 4. En comparaison avec l'amplificateur de la figure 4, l'élément amplificateur de la figure 5 est

également capable de fonctionner plus rapidement. Cependant, le fonctionnement de l'élément de la figure 5 est par ailleurs pratiquement identique à celui de l'élément amplificateur de la figure 4.

5 En retournant maintenant à la figure 3, on note que les moyens d'attaque de commutation à configuration bootstrap comprennent un circuit de génération de potentiel 4, ayant une entrée connectée à la borne de sortie du circuit, et qui est capable de produire sur ses sorties respectives des potentiels  $V_{haut}$  et  $V_{bas}$  ( $V_{haut} > V_{bas}$ ), chacun de ces potentiels ayant un décalage constant par rapport au potentiel de la borne de sortie. Ces deux potentiels doivent être à des niveaux appropriés pour l'application à l'électrode de grille du transistor MOS 1, afin de le maintenir dans ses états passant et bloqué.

10

15

Les deux potentiels  $V_{haut}$  et  $V_{bas}$  sont appliqués sous la forme de signaux d'entrée à un élément sélecteur 5 qui reçoit également un signal de commutation CK. La sortie de l'élément sélecteur 5 est connectée à l'électrode de grille de l'élément de commutation à transistor MOS 1, pour commander son potentiel. L'élément sélecteur 5 commute le potentiel de l'électrode de grille entre les deux potentiels  $V_{haut}$  et  $V_{bas}$  sous la dépendance du signal de commutation CK. Ce signal CK peut être un signal logique qui est fourni par un circuit logique numérique qui commande le fonctionnement du circuit de mémorisation de tension.

20

25

30 Dans le but d'éviter une injection de charge imprévisible dans le condensateur de mémorisation 2, par l'élément de commutation d'entrée à transistor MOS 1, lorsque l'élément de commutation d'entrée est commuté à l'état bloqué, le potentiel de commande qui est appliqué à l'électrode de grille du transistor MOS

35

doit être pratiquement fixe par rapport au potentiel de la borne d'entrée, au moins lorsque le transistor MOS doit être commuté à l'état passant, comme on va maintenant l'expliquer en se référant à la figure 6.

5 La figure 6 montre en détail l'élément de commutation d'entrée 1, qui est dans cet exemple un transistor à effet de champ MOS du type à enrichissement et à canal n. Le transistor MOS 1 comporte une électrode de source qui constitue une borne d'entrée de l'élément de commutation, portant la désignation ENTREE, une électrode de drain qui constitue une borne de sortie de l'élément de commutation, portant la désignation SORTIE, et une électrode de grille qui est connectée de façon à être commutée alternativement 10 entre les potentiels de commande  $V_{haut}$  et  $V_{bas}$  mentionnés précédemment. Le canal drain-source du transistor est bloqué lorsque son potentiel grille-canal est égal à zéro (ou négatif), ce qui fait que lorsque le potentiel de commande appliqué est  $V_{bas}$  15 ( $\leq V_O$ ), la borne de sortie de l'élément de commutation est isolée de sa borne d'entrée, la résistance à l'état bloqué ( $R_{off}$ ) de l'élément de commutation dans cette condition étant de façon caractéristique supérieure à 10 000 MΩ. Lorsque le potentiel de grille 20 est changé pour devenir  $V_{haut}$  ( $> V_O$ ), le canal drain-source est placé dans l'état de conduction, la résistance à l'état passant ( $R_{on}$ ) de l'élément de commutation dans cette condition étant de l'ordre de quelques 25 dizaines ou centaines d'ohms.

30 Dans un convertisseur analogique-numérique qui utilise un circuit de mémorisation de tension tel que celui qui est représenté sur la figure 3, le fonctionnement de l'élément de commutation 1 doit normalement être commandé par un circuit logique numérique du convertisseur et, en partie pour cette raison, dans 35

des propositions antérieures des potentiels logiques numériques fixes (par exemple 0 et  $+V_{dd}$  volts) étaient habituellement appliquées à la grille pour commander la commutation de l'élément.

5 Il apparaît cependant un problème lorsqu'on utilise de tels potentiels logiques numériques, comme on va maintenant l'expliquer.

10 L'élément de commutation à transistor MOS 1 de la figure 6 a inévitablement une capacité parasite grille-canal  $C_{gc}$  entre son électrode de grille et son canal drain-source. Cette capacité parasite a une première composante qui est due à un chevauchement physique entre la grille et le canal du transistor à effet de champ, et une seconde composante qui est 15 associée à la charge qui est emmagasinée dans le canal lorsque le transistor à effet de champ est dans l'état passant. Il apparaît que cette seconde composante varie avec le potentiel de canal (c'est-à-dire avec le potentiel  $V_i$  du signal qui est commuté), mais d'une 20 manière imprévisible.

25 La capacité grille-canal donne lieu à une injection de charge à partir de la grille vers le canal, à l'instant de commutation  $t_{comm}$ , et cette injection produit à son tour une erreur dans la tension qui est mémorisée. L'injection de charge due à la première composante précitée de la capacité grille-canal dépend essentiellement de la variation de la tension de grille  $V_G$  à l'instant  $t_{comm}$  (par exemple  $0-V_{DD} = -V_{DD}$ ), et par conséquent elle est pratiquement 30 indépendante du potentiel de canal  $V_i$  à l'instant  $t_{comm}$ . Cependant, l'injection de charge qui est due à la seconde composante de la capacité grille-canal est influencée par le potentiel du signal d'entrée  $V_i$  par rapport au potentiel de grille à l'instant de la 35 commutation, ce qui conduit à l'erreur précitée dans

la tension mémorisée, et à une non-linéarité dans le fonctionnement du circuit de mémorisation de tension.

Il n'est pas aisé en pratique de compenser une telle injection de charge, par exemple par 5 couplage d'une version inversée du signal de grille, par l'intermédiaire d'un petit condensateur réglable, du fait que l'effet de la seconde composante précitée de la capacité grille-canal n'est pas suffisamment prévisible.

10 Dans des propositions antérieures employant des potentiels de commande fixes, tels que des potentiels logiques numériques, les effets d'injection de charge à l'instant de commutation  $t_{\text{comm}}$  sont particulièrement importants dans le cas où l'on désire 15 employer un condensateur de mémorisation ayant une faible capacité, afin de réduire le temps d'acquisition du circuit.

20 Cependant, dans les moyens d'attaque de commutation à configuration bootstrap 4, 5 de la figure 3, au moins le potentiel de commande qui est appliqué à l'élément de commutation 1 pour le maintenir dans l'état passant est fixe par rapport au potentiel de la borne d'entrée  $V_i$ , ce qui fait que la 25 quantité de charge qui est injectée par l'élément 1 lorsqu'il est commuté à l'état bloqué est pratiquement constante, indépendamment du potentiel de la borne d'entrée. Du fait que cette injection de charge est constante, elle conduit à une erreur constante dans la tension mémorisée, que l'on peut aisément compenser.

30 On notera incidemment que dans certains cas, il peut être possible que le potentiel de commande qui est appliqué à l'élément de commutation 1, lorsque ce dernier doit être maintenu dans l'état bloqué (par opposition à l'état passant), soit fixe, au lieu 35 d'être variable avec le potentiel d'entrée  $V_i$ , comme

sur la figure 3. Ceci vient du fait que la première composante précitée de la capacité parasite grille-canal  $C_{gc}$  est linéaire.