## (19) World Intellectual Property Organization International Bureau

## (43) International Publication Date 31 October 2002 (31.10.2002)

### **PCT**

# (10) International Publication Number WO 02/086966 A1

- (51) International Patent Classification<sup>7</sup>: H01L 21/8247, 27/115

- (72) Inventor: VERHAAR, Robertus, D., J.; Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL).

- (21) International Application Number: PCT/IB02/01353

- (74) Agent: DUIJVESTIJN, Adrianus, J.; Internationaal Octrooibureau B.V., Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL).

- (22) International Filing Date: 16 April 2002 (16.04.2002)

- (81) Designated States (national): JP, KR.

(25) Filing Language:

- (o-) o--g------

- (26) Publication Language:

- (84) Designated States (regional): European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR).

(30) Priority Data:

English

English

01201434.6 20 April 2001 (20.04.2001) EF

Published:with international search report

(71) Applicant: KONINKLIJKE PHILIPS ELECTRON-ICS N.V. [NL/NL]; Groenewoudseweg 1, NL-5621 BA Eindhoven (NL).

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

#### (54) Title: TWO-TRANSISTOR FLASH CELL HAVING VERTICAL ACCESS TRANSISTOR

(57) Abstract: A semiconductor device comprising a non-volatile memory cell (20; 200) for storing a bit, arranged in a semiconductor substrate (21) containing a first dopant type, said memory cell including a drain (24) in the substrate (21), a floating gate (29), a control gate (30), a thin gate isolation layer (27), and an insulating layer (32), the insulating layer (32) being above the floating gate (29), the control gate (30) being above the insulating layer (32), the floating gate (29) being above the thin gate isolation layer (27), and the cell further including an access transistor (34) for controlling access to the non-volatile memory cell (20; 200), the cell (20; 200) including a buried substrate layer (22) containing a second dopant type and a source (26), and the access transistor (34) being formed in the substrate (21), in a trench adjacent to the floating gate (29), said trench extending substantially from the source (26) to the substrate's surface.

### TWO-TRANSISTOR FLASH CELL HAVING VERTICAL ACCESS TRANSISTOR

The present invention relates to a semiconductor device comprising a non-volatile memory cell for storing at least one bit, according to the preamble of claim 1.

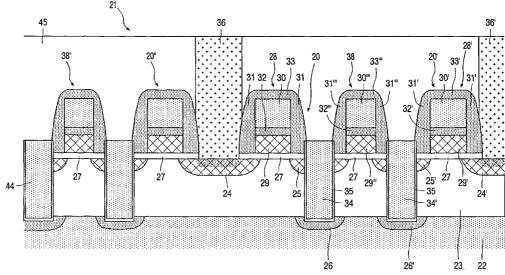

Such non-volatile memory cells are well known from the prior art in a plurality of varieties. Figure 1 shows schematically a cross-section of an exemplary prior art planar 2T non-volatile memory cell.

5

10

15

20

25

The depicted 2T non-volatile memory cell 1, also known as Flash cell, is of the planar type and comprises two distinct transistors, viz. a floating gate transistor FT and an access transistor AT. On a p-type substrate 2, an n-type drain region 3, an n-type source region 4, an n-type doped region 5 are formed. On the surface, between drain region 3 and doped region 5, a floating gate 6 is formed on a thin gate oxide 7. On top of the floating gate 6, a control gate 8 is formed. The control gate 8 is separated from the floating gate 6 by an isolating layer 14, e.g., an oxide layer or an oxide-nitride-oxide layer. Insulating side spacers 9 are formed on the sides of the stack of the floating gate 6 and the control gate 8. Adjacent to this stack, between the doped region 5 and the source region 4, an access gate 10 is formed on the thin gate oxide 7 on the surface of the substrate 2. As shown here, the access transistor may comprise a stack similar to the stack comprising the floating gate 6, the isolating layer 14 and the control gate 8, but the access gate may also comprise a structure consisting of only a single layer. Also the sidewalls of the access gate 10 are covered by an insulating spacer 11. The drain region 3 and the source region 4 are connected to a drain line and a source line, respectively, by the respective drain contact 12 and source contact 13.

In such prior art 2T non-volatile memory cell types arranged as a planar structure, as described above, the select gate is usually positioned next to the control gate which is arranged on the floating gate. This planar arrangement has the disadvantage that a non-volatile memory cell of this type occupies a relatively large area on the semiconductor surface. The advance of processing technologies enables structures having smaller feature sizes to be manufactured, so that the cell size of these planar 2T cells can be reduced. However, the size reduction is limited due to a number of structural constraints, e.g. minimal

contact sizes, minimal spacer thickness, etc. Scaling down of the structure as shown in Figure 1 is limited by its design: i.e., certain minimal sizes within the structure must be maintained. Using 0.18  $\mu$ m design rules, such a memory cell will typically have a size of  $0.6-0.8~\mu\text{m}^2$ .

2

US 5,386,132 discloses a more compact arrangement of a Flash memory cell in figures 9A and 9B. This non-volatile memory cell is arranged as a two-transistor (2T) vertical split channel EEPROM on a semiconductor substrate and comprises a source region, a drain region, a control gate, a floating gate and a select gate, the control gate being arranged as a pillar inside a trench. The floating gate is arranged as a tube surrounding this pillar-shaped control gate. The select gate is arranged as an annular structure surrounding the control gate in the top region of the control gate. The drain region is also arranged as an annular structure, which surrounds the control gate just below the select gate. The source region is located below the control gate pillar.

The non-volatile memory cell of US 5,386,132 advantageously reduces the area needed on the substrate, and allows further downsizing and/or higher densities of EEPROM and FLASH memory devices.

However, the fabrication of such a non-volatile memory cell, as disclosed in US 5,386,132, is very complex due to the application of an annular double trench structure. In particular, the separation of the respective gates by a thin oxide is difficult and may disadvantageously reduce the process yield and the reliability of the non-volatile memory cell.

Moreover, in the non-volatile memory cell of US 5,386,132, the select gate and the control gate are interconnected. During the programming steps (write and erase) and the reading steps of such a memory cell both select gate and control gate have the same potential. Separate control of the respective gate potentials is not possible.

25

30

5

10

15

20

It is an object of the present invention to provide a semiconductor device comprising a 2T non-volatile memory cell for storing at least one bit that is more compact than planar 2T non-volatile memory cells known from the prior art. The present invention relates to a semiconductor device comprising, in a semiconductor substrate containing a first dopant type, a first non-volatile memory cell for storing a bit, comprising a first drain region in the substrate, a first floating gate, a first control gate, a first thin gate isolation layer, and an insulating layer, the insulating layer being positioned on top of the first floating gate, the first control gate being positioned on top of the insulating layer, the first floating gate being

10

15

20

25

30

positioned on top of the first thin gate isolation layer, and further comprising a first access transistor for controlling access to the first non-volatile memory cell, wherein the first non-volatile memory cell comprises a buried layer in the substrate containing a second dopant type and a first source region, the first access transistor is formed in a first trench on the substrate, the first trench extending substantially from the first source region to the surface of the substrate, the first trench being adjacent to the first floating gate and directed in a first direction parallel to the surface of the substrate.

In comparison with a non-volatile memory cell of the prior art, the present invention provides a non-volatile memory cell with a smaller cell size.

Moreover, in a first embodiment the present invention relates to a semiconductor device as described above, comprising in the semiconductor substrate, a second non-volatile memory cell for storing a bit, comprising a second drain region in the substrate, a second floating gate, a second control gate, a second thin gate isolation layer, and a second insulating layer, the second insulating layer being positioned on top of the second floating gate, the second control gate being positioned on top of the second insulating layer, the second floating gate being positioned on top of the second thin gate isolation layer, the buried layer containing a second source region, and the device further comprising a second access transistor for controlling access to the second non-volatile memory cell, the second non-volatile memory cell being adjacent to the first non-volatile memory cell in a second direction, the second direction being parallel to the surface of the substrate and perpendicular to the first direction,

wherein the second access transistor is formed in a second trench on the substrate, the second trench extending substantially from the second source region to the surface of the substrate, the second trench being adjacent to the second floating gate and directed in the second direction, and

the first access transistor of the first non-volatile memory cell being separated from the second access transistor of the second non-volatile memory cell by an isolation gate, comprising a dummy floating gate, a dummy insulating layer and a dummy control gate, the dummy insulating layer being positioned on top of the dummy floating gate, the dummy control gate being positioned on top of the dummy insulating layer. This arrangement of two non-volatile memory cells results in a smaller total area than the area needed for two separate non-volatile memory cells.

Furthermore, a further size reduction for a 2T non-volatile memory cell is achieved by combining the select gates of two adjacent 2T non-volatile memory cells into a

10

15

20

25

30

4

single select gate. In a second embodiment, the present invention relates to a semiconductor device as described above, comprising in the semiconductor substrate, a second non-volatile memory cell for storing a bit, comprising a second drain region in the substrate, a second floating gate, a second control gate, the second thin gate isolation layer, and a second insulating layer, the second insulating layer being positioned on top of the second floating gate, the second control gate being positioned on top of the second insulating layer, the second floating gate being positioned on top of the second thin gate isolation layer, the buried layer containing a second source region, and the device further comprising a second access transistor for controlling access to the second non-volatile memory cell, the second non-volatile memory cell being adjacent to the first non-volatile memory cell in a second direction, the second direction being parallel to the surface of the substrate and perpendicular to the first direction,

wherein the second access transistor is formed in a second trench on the substrate, the second trench extending substantially from the second source region to the surface of the substrate, the second trench being adjacent to the second floating gate and directed in the second direction, and

the first access transistor of the first non-volatile memory cell coinciding with the second access transistor of the second non-volatile memory cell.

The present invention also relates to a non-volatile memory cell matrix comprising a plurality of non-volatile memory cells as described above, wherein the plurality of non-volatile memory cells is arranged in the first direction and the second direction.

Moreover, the present invention also relates to a semiconductor device comprising a non-volatile memory cell matrix as described above.

The present invention also relates to a method of manufacturing a semiconductor device comprising in a semiconductor substrate containing a first dopant type, a first non-volatile memory cell for storing a bit, comprising a first drain region in the substrate, a first floating gate, a first control gate, a buried layer containing a second dopant type and a first source region, a first thin gate isolation layer, and an insulating layer, the insulating layer being positioned on top of the first floating gate, the first control gate being positioned on top of the insulating layer, the first floating gate being positioned on top of the first thin gate isolation layer, said arrangement further comprising a first access transistor, and the method comprising the following steps:

formation of the buried layer in the substrate by ion implantation;

demarcation of an active area of the non-volatile memory cell by the formation of isolation lines extending in a first direction;

- formation of the first thin gate isolation layer on the surface of the substrate;

- formation of a stacked gate structure on top of the first gate isolation layer, the stacked gate structure comprising the first floating gate, the control gate, and the insulating layer;

- formation of the first access transistor comprising the following steps:

- etching of a trench in the substrate substantially from its surface to the buried layer,

- formation of a second thin oxide on the trench walls,

- deposition of doped polysilicon in the trench, said trench being adjacent to the stacked gate structure;

- passivation and metallization of the non-volatile memory cell.

Furthermore, programming and reading a 2T non-volatile memory cell as disclosed in the second embodiment requires a detection method to detect which 2T non-volatile memory cell is actually programmed. Therefore, the present invention also relates to a method of reading a bit stored in a non-volatile memory cell matrix according to the second embodiment, the method of reading a bit comprising a step of measuring a source-drain current of the first and the second non-volatile memory cell, characterized in that the step of measuring the source-drain current comprises the application of a first voltage pulse to the first control gate, and application of a second voltage pulse to the second control gate, wherein a change of the source-drain current after the application of the first and second voltage pulses determines whether the first non-volatile memory cell and the second non-volatile memory cell, respectively, are programmed or not.

25

30

5

10

15

20

Below, the invention will be explained with reference to some drawings, which are intended for illustration purposes only and do not limit the scope of protection as defined in the accompanying claims.

Fig. 1 schematically shows a cross-section of a 2T non-volatile memory cell known from the prior art;

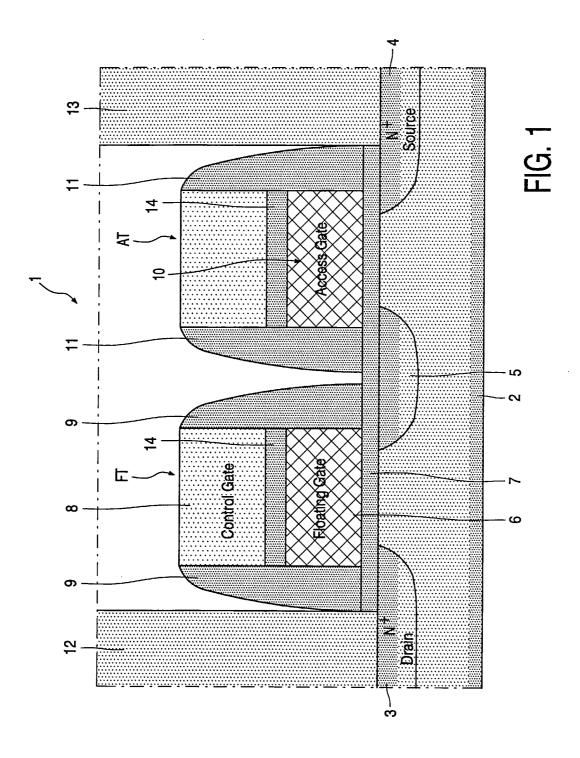

Fig. 2 schematically shows a cross-section of some 2T non-volatile memory cells according to a first embodiment of the present invention;

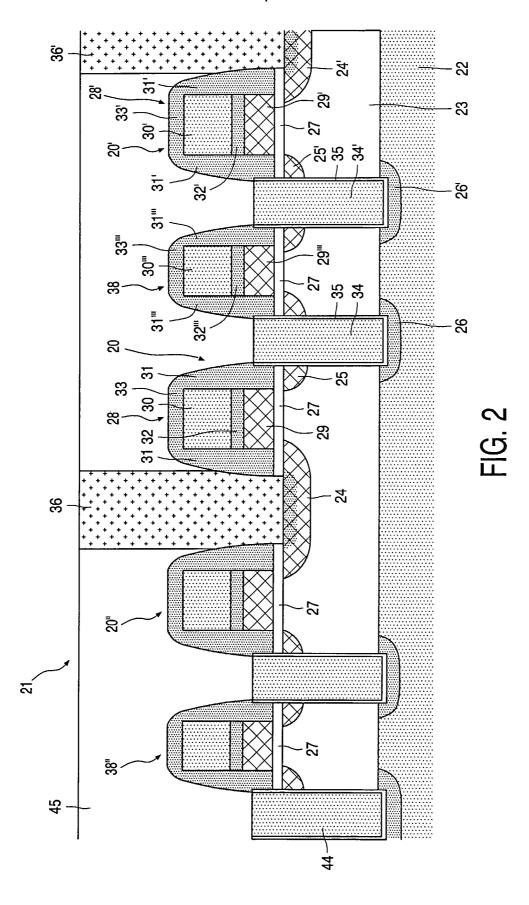

Fig. 3 schematically shows a top view of an array comprising a plurality of 2T non-volatile memory cells according to the first embodiment of the present invention;

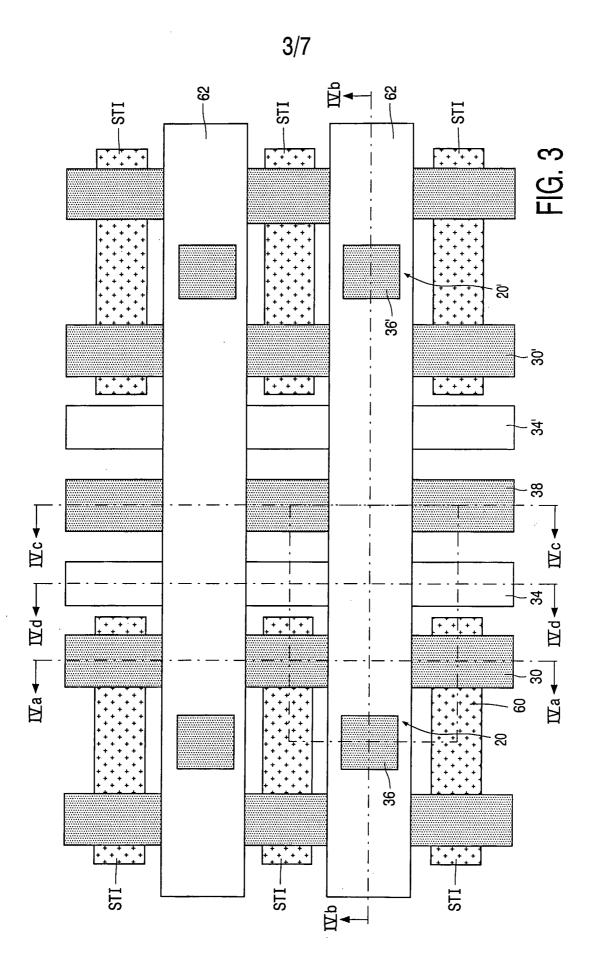

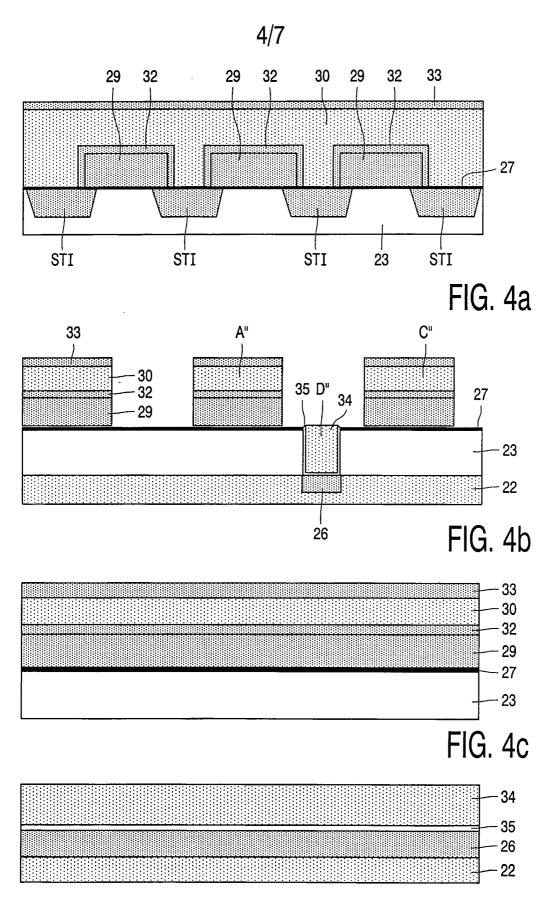

Fig. 4a shows a schematic cross-section along a control gate line according to the first embodiment of the present invention;

Fig. 4b shows a schematic cross-section of non-volatile memory cells along a line where a bit line is to be formed;

Fig. 4c shows a schematic cross-section along an isolation gate line according to the first embodiment of the present invention;

Fig. 4d shows a schematic cross-section along an access gate line according to the first embodiment of the present invention;

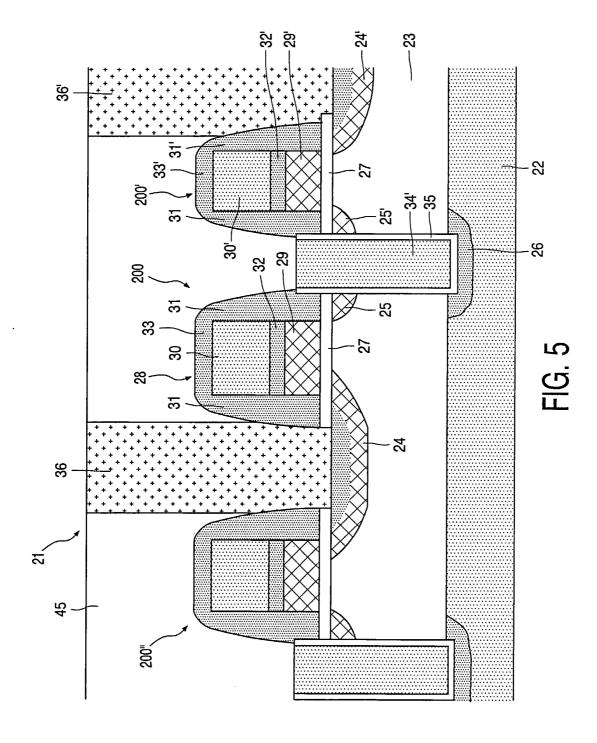

Fig. 5 schematically shows a cross-section of some 2T non-volatile memory cells according to a second embodiment of the present invention;

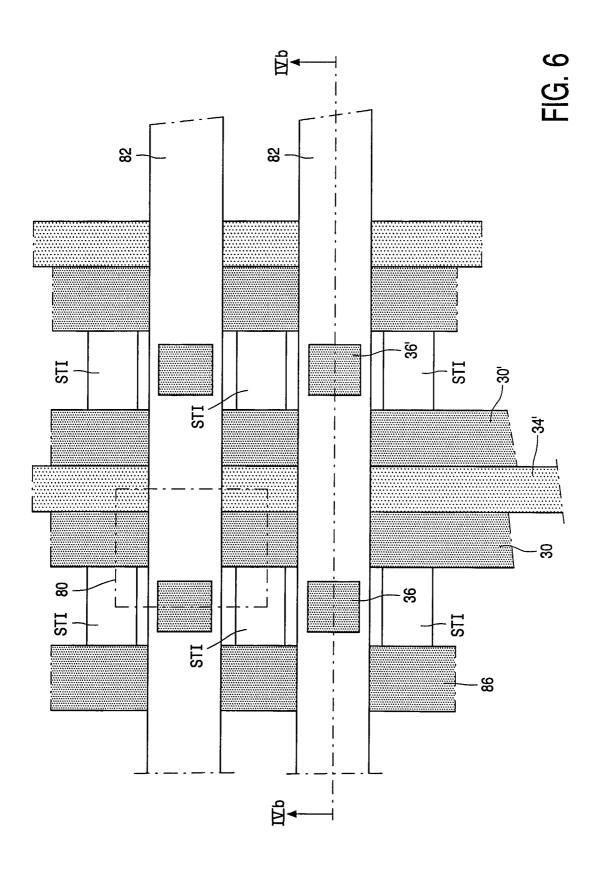

Fig. 6 schematically shows a top view of an array comprising a plurality of 2T non-volatile memory cells according to the second embodiment of the present invention;

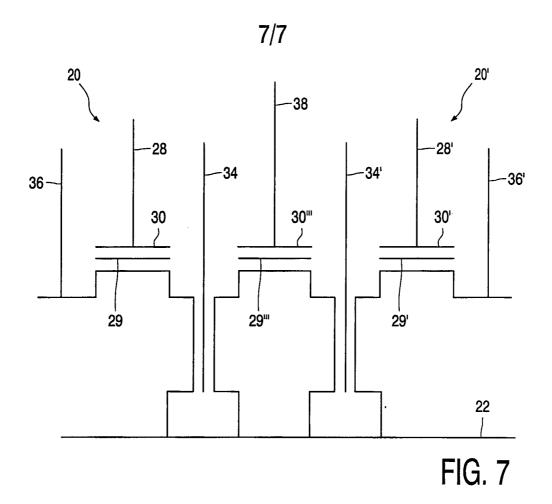

Fig. 7 shows an electrical circuit diagram of the arrangement of 2T non-volatile memory cells according to the first embodiment;

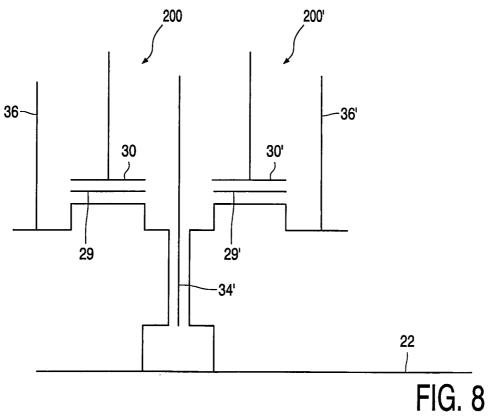

Fig. 8 shows an electrical circuit diagram of the arrangement of 2T non-volatile memory cells according to the second embodiment.

20

25

30

15

5

10

As mentioned above, in comparison with a single transistor non-volatile memory cell, a two-transistor non-volatile memory cell provides a memory cell which is highly insensitive to over-erasing and over-programming. As known to persons skilled in the art, reading of such cells is already feasible at low control gate potentials. However, the areal size of a 2T non-volatile memory cell is much larger than the size of a single transistor non-volatile memory cell.

As described above, Figure 1 schematically shows a cross-section of a planar 2T non-volatile memory cell known from the prior art.

In a first embodiment of the present invention, a further size reduction for 2T non-volatile memory cells is achieved by replacing the horizontal access gate as shown in Figure 1 with a vertical access gate.

Figure 2 schematically shows a cross-section of some 2T non-volatile memory cells 20, 20°, 20° according to a first embodiment of the present invention. A substrate 21 comprises a buried n-type doped layer 22, covered by a p-type layer 23. In the p-type layer

10

15

20

25

30

PCT/IB02/01353

23 an n-type drain region 24, 24', and an n-type doped region 25, 25' are present. In the buried n-type doped layer 22, a source region 26, 26' is defined. On the surface of the substrate 21, on top of a thin gate oxide 27, the 2T non-volatile memory cell 20 comprises a stacked structure 28 acting as floating gate transistor, consisting of a floating gate 29, a control gate 30 and side spacers 31. The control gate 30 is separated from the floating gate 29 by an insulating layer 32, preferably an ONO (oxide-nitride-oxide) layer. The top of control gate 30 is covered by an oxide layer 33. Adjacent to the stacked structure 28, there is provided an access transistor 34. The access transistor 34 extends from the substrate surface to the source region 26 in the buried n-type doped layer 22. The access transistor 34 is formed in a trench and delineated by trench walls 35 that also insulate the trench body from the source region 26. The trench walls 35, preferably, consist of a thin oxide film.

On the opposite side of the stacked structure 28, a bit line contact 36 connects with the drain region 24. In the first embodiment, a common source arrangement is used. As a separation between the non-volatile memory cell 20 and an adjacent cell 20', an isolation gate 38 is located between the access transistor 34 and the access transistor 34' of the cell 20'. The isolation gate 38 is identical to the stacked gate 28: a dummy floating gate 29''' covered by an insulating layer 32''' and, on top of the insulating layer 32''', a dummy control gate 30''', with side spacers 31''' covering the side walls of the stack 38. The top of dummy control gate 30''' is covered by an isolation layer 33'''.

The non-volatile memory cell 20' comprises an access transistor 34', a floating gate 29' on thin gate oxide 27, a control gate 30' provided on floating gate 29', a bit line contact 36', and a drain region 24'. Between the control gate 30' and the floating gate 29', an insulating layer 32' is provided. The sidewalls of non-volatile memory cell 20' are covered by side spacers 31. On top of the control gate 30' an oxide layer 33' is present.

Adjacent to the stacked structure 28', there is provided an access transistor 34'. The access transistor 34' extends from the substrate surface to the source region 26' in buried n-type doped layer 22. The access transistor 34' is formed in a trench delineated by trench walls 35 that also insulate the access gate 34' from the source region 26'. The trench walls 35, preferably, consist of a thin oxide film.

A non-volatile memory cell 20" is separated from the cell 20 by the drain region 24 and bit-line contact 36. Again, this cell 20" is separated by an isolation gate 38" from a further non-volatile memory cell of which only an access transistor 44 is shown.

An isolation layer 45 covers the stacked gate structures 28, 28', 38 to electrically insulate the 2T non-volatile memory cells 20, 20', 20".

As shown in Figure 2, an array of non-volatile memory cells can be formed by alternately linking two cells to an intermediate bit line contact, and separating the access transistors of two cells by an isolation gate.

The electrical circuit comprising two adjacent non-volatile memory cells according to the fist embodiment will be described with reference to Figure 7.

5

10

15

20

25

30

Figure 3 schematically shows a top view of an array comprising a plurality of 2T non-volatile memory cells according to the first embodiment of the present invention. In comparison with Figure 2, some space is introduced between the displayed elements for reasons of clarity.

In this array, four non-volatile memory cells according to the first embodiment of the present invention are shown. The areal size 60 of one such non-volatile memory cells is marked by dashed lines in Figure 3.

To obtain a memory array with random access features, in the arrangement according to the first embodiment, bit-lines 62, each connecting a drain region 24 through a bit line contact 36, run in a first direction perpendicular to a second direction wherein the access transistors 34, 34' are extended so as to form access transistor lines 34, 34', respectively. Control gates 30, 30' are extended so as to form control gate lines 30, 30' and run parallel to the access transistor lines 34, 34'. The isolation gates 38, 38" are extended so as to form isolation gate lines running in the same direction as the access transistor lines 34 and the control gate lines 30.

The non-volatile memory cells in the memory array are arranged with a common source in the n-type region 22.

The access transistor lines 34 are arranged as trenched lines, each located in a trench connecting with the common source in the buried n-type doped layer 22.

The control gate lines 30 run parallel to the access transistor lines 34. To define separate cells, a LOCOS isolation or STI is arranged in between the non-volatile memory cells in the p-type layer 23. Moreover, the floating gate 29, 29', consisting of amorphous or polycrystalline Si, is only defined in between two isolation lines STI. Thus, the region for storing a bit in a non-volatile memory cell according to this first embodiment is confined to the region occupied by the floating gate 29, 29'.

Cross-sections IVa along a control gate line 30, IVb along non-volatile memory cells in a nascent state, IVc along an isolation gate line 38, and IVd along an access transistor line 34, according to the arrangement shown in Figure 3, are shown in Figures 4a, 4b, 4c, and 4d, respectively, to illustrate the memory array arrangement in more detail.

10

15

20

25

30

PCT/IB02/01353

Figure 4a shows a schematic cross-section IVa along a control gate line 30, which clearly shows the separation of non-volatile memory cells by the isolation implantation STI and the separation of the respective floating gates 29 from the control gate (material) 30 by means of the insulating layer 32. The thin gate oxide 27 separates the floating gate 29 from the p-type layer 23 and the isolation lines STI.

Figure 4b shows a schematic cross-section IVb of non-volatile memory cells along the line where a bit-line is to be formed. In this cross-section Ivb, a number of pillars are shown, each consisting of a floating gate 29 encapsulated by an insulating layer 32 and covered by a control gate 30 and a capping layer 33. The pillar A" is shown in cross-section IVa of Figure 4a, which is perpendicular to the view in this cross-section. Pillar C" is shown in cross-section IVc of Figure 4c, which is perpendicular to the view in this cross-section. The access transistor line 34 formed in a trench is denoted by D", which is shown in cross-section IVd of Figure 4d (also perpendicular to the view in this cross-section). The depicted pillars are separated from the p—type layer 23 by the thin gate oxide 27. The access transistor line 34 is located in a trench in p-type layer 23. The trench walls are covered by thin oxide 35. Below the access transistor line 34, local implantation 26 is located in buried n-type layer 22.

Figure 4c shows a schematic cross-section IVc along an isolation gate line 38, cf. Figure 2. The isolation gate line comprises a stack of layers: On p-type layer 23, the stack consists of thin gate oxide 27, floating gate 29, insulating layer 32, control gate 30 and oxide layer 33.

Finally, Figure 4d shows a schematic cross-section IVd along an access transistor line 34 in a trench in p-type-layer 23, which gate line comprises, viewed from bottom to top, buried n-type layer 22, source layer 26, thin oxide 35 and access transistor material, e.g., poly-Si.

It is noted that in Figures 4a, 4b 4c, 4d, no local interconnect and no metallization level are shown. In Figure 3, the bit-line metallization runs parallel to the direction indicated by IVb.

In the following, an exemplary method of manufacturing a Flash cell of the embodiment as shown in Figures 2, 3, 4a, 4b, 4c, 4d is described.

The buried n-type doped layer 22 (buried n-well) is formed in the p-type substrate 21 by an ion-implantation process. Subsequently, in the p-type layer 23 the necessary dopant profiles are applied to define the properties of both the horizontal and vertical parts of the 2T non-volatile memory cell to be formed. The active areas of adjacent

non-volatile memory cells are separated in a first direction by oxidic (SiO<sub>2</sub>) isolation lines (not shown in Figure 2) formed by LOCOS or by STI technology.

5

10

15

20

25

30

On the thin gate oxide 27 a stacked gate structure is being formed, which confines each non-volatile memory cell in a second direction perpendicular to the first direction. The thickness of the thin gate oxide 27 is typically 5-10 nm. A first layer of poly-Si is deposited in a thickness of 10 – 200 nm. The layer is doped in-situ or by a later ion implantation step. In this first poly-Si layer, trenches are etched to form floating gates. The trenches are each parallel to the oxidic isolation lines STI. Each trench is located on top of one of the oxidic isolation lines STI. Next, an insulating layer 32 e.g., an ONO (oxide-nitride-oxide) layer, is deposited in a thickness of typically 15 nm.

Then, a second poly-Si layer is deposited in a thickness of 100-300 nm to form control gates. The layer is doped in-situ or by a later ion-implantation step. Finally, an oxide or nitride capping layer 33 is deposited.

In the next step, the stacked layers are etched to define a plurality of lines, which are directed perpendicularly to the oxide isolation lines STI. These lines will later be the control gate lines 30. In this manner, stacked gate Flash cells are formed, as is known to persons skilled in the art. Simultaneously, the isolation gate lines 38 are manufactured in the same processing steps.

Subsequently, an oxidation step and/or annealing step is carried out, followed by the formation of dopant profiles of source 26 and drain 24. The dopant profile of source 26 is optional in this embodiment. A second oxidation step and/or annealing step may be done.

In the next step, the side spacers 31 are formed. In an alternative embodiment, the formation of the side spacers 31 is omitted.

In the following step, trenches are etched in the source regions. The trenches extend as far as (or into) the buried n-well layer 22. The walls of the trenches are covered by an oxide layer 35. Successively, poly-Si is deposited in each trench and, preferably, doped insitu to form the access transistor 34, 34', 34". The excess poly-Si outside the trenches is removed.

Finally, an isolation layer 45 is deposited to cover the stacked gate structures 28, 28', 28". Subsequently, the drains 24, 24', the buried n-well layer 22 and the access transistors 34, 34', 34" are provided with contacts, followed by metallization steps to obtain connections between the FLASH cells and other structures.

10

15

20

25

30

PCT/IB02/01353

Figure 5 schematically shows a cross-section of a 2T non-volatile memory cell 200 according to a second embodiment of the present invention.

In Figure 5, entities with the same reference numbers as in Figure 2, refer to the same entities as in Figure 2.

Adjacent to the stacked gate structure 28, an access transistor 34' is provided, which extends from the substrate surface to the source region 26 in buried n-type doped layer 22.

Also in this second embodiment, a common source arrangement is used. Between the 2T non-volatile memory cell 200 and an adjacent similar 2T non-volatile memory cell 200', no isolation is provided.

Also, the cells 200 and 200' share the same bit line (not shown) located above the bit line contacts 36 and 36'. To control the read-out of each of the cells 200, 200', a reading procedure is performed which will be explained in more detail with reference to Figure 8.

A further adjacent non-volatile memory cell 200" is separated from the cell 200 by the drain region 24.

Figure 6 schematically shows a top view of an array comprising a plurality of 2T non-volatile memory cells according to the second embodiment of the present invention. In comparison with Figure 5, some space is introduced between the displayed elements for reasons of clarity.

In this memory array, four non-volatile memory cells according to the second embodiment of the present invention are shown. The areal size 80 of one such non-volatile memory cell is marked in Figure 6 by dashed lines.

To obtain a memory array with random access features, in the arrangement according to the second embodiment, the bit lines 82 for connecting the drain regions 24 through bit line contact 36, run in a first direction perpendicular to a second direction for the access transistor lines 34'. The control gate lines 30 for connecting the control gates 30 run parallel to the access transistor line 34'.

The non-volatile memory cells in the memory array are arranged with a common source in the n-type region 22.

The access transistor line 34' is arranged as a trenched line, located in a trench on top of the common source in the buried n-type doped layer 22.

The control gate lines 30 run parallel to the access transistor line 34'. To define separate cells, a LOCOS isolation or an STI isolation line STI is arranged in between

the non-volatile memory cells in the p-type layer 23. Moreover, the floating gate 29, consisting of amorphous or poly crystalline Si, is only defined in between two isolation lines STI. Thus, the region for storing a bit in a non-volatile memory cell according to this second embodiment is confined to the region occupied by the floating gate 29.

12

Figure 7 shows an electrical circuit diagram of two 2T non-volatile memory cells according to the first embodiment, in which the two 2T non-volatile memory cells 20, 20' are separated by an isolation gate 38. In Figure 7, entities with the same reference numbers as used in Figure 2 refer to the same entities as shown in Figure 2.

5

10

15

20

25

30

In the circuit of 2T non-volatile memory cell 20, an electrical potential on the control gate 30 can be controlled independently of an electrical potential on the access transistor 34. Similarly, in 2T non-volatile memory cell 20', a potential on the control gate 48 can be controlled independently of a potential on the access transistor 34'.

Programming of each 2T non-volatile memory cell 20, 20' can be done by Fowler-Nordheim tunnelling (FN) or Source Side Injection (SSI) in ways known in the art. Reading and erasure of each cell 20, 20' can also be done by mechanisms known in the art.

Figure 8 shows an electrical circuit diagram of the 2T non-volatile memory cells 200, 200' according to the second embodiment of the present invention.

In this second embodiment, the two 2T non-volatile memory cells 200, 200' are not separated by an isolation. In Figure 8, entities with the same reference numbers as used in Figure 5 refer to the same entities as shown in Figure 5.

In the circuit of 2T non-volatile memory cell 200, an electrical potential on the control gate 30 can be controlled independently of an electrical potential on the access transistor 34'. Similarly, in the 2T non-volatile memory cell 200', a potential on the control gate can be controlled independently of a potential on the access transistor 34'.

Programming of each 2T non-volatile memory cell 200, 200' can then be done by Fowler-Nordheim tunnelling (FN) or Source Side Injection (SSI) in ways known in the art.

Selective read-out of one of the two 2T non-volatile memory cells 200, 200' may not be directly obvious. By setting a potential of 1.2 V on the access transistor 34' and a potential of 0.5 V on the bit line contacts 36 and 36', the cells 200, 200' can be read. If none of the cells 200, 200' are programmed (i.e. containing a charge), no current will be present. If, however, one or two cells are programmed, a current will flow in the circuit. By substantially measuring the read-out current in response to sequentially applying a pulse (1.2 V) to the control gate of each cell, the modulation of the read-out current reveals which of the

cells is in the programmed state. If a positive pulse on the control gate of a cell affects the measured read-out current, the respective cell is in the non-programmed (erased) state. If, for example, a pulse on a first cell 200 affects the read-out current, a modulation will be found, which indicates that the first cell 200 is in a non-programmed state. If not, both the first cell 200 and the second cell 200' may be programmed. A second pulse on the second cell 200' may affect the read-out current, which indicates the state of the second cell 200'. Comparing the results for the two pulses indicates which of the cells 200 and 200' is actually in the programmed state.

5

10

15

20

25

30

It is noted that in a programmed cell, a pulse on the control gate does not substantially affect the programmed cell when the pulse comprises a relatively low potential in comparison with the programming and/or erasure voltages.

In comparison with a flash cell of the prior art as shown in Figure 1, the areal size of a 2T non-volatile memory cell can be reduced significantly. Using 0.18  $\mu$ m design rules, in a prior art 2T non-volatile memory cell as shown in Figure 1, source and drain contacts typically are 0.24  $\mu$ m wide. The stacked gate 6, 7, 8, 9, 14 and the access transistor 10, each isolated by side spacers 9 and 11, respectively, occupy a width of 0.48  $\mu$ m (gate: 0.24  $\mu$ m, spacer: 0.06  $\mu$ m). Taking into account an interstitial space of 0.14  $\mu$ m between the gate spacers of the control/floating gate and the access transistor, the total width of a cell is 1.1  $\mu$ m (taking the half width of source and drain). Using a length of each cell of 0.56  $\mu$ m, the areal size of a cell is 0,62  $\mu$ m<sup>2</sup>.

In the first embodiment of the present invention, as shown in Figure 2, the width of a cell is only 0,78  $\mu$ m (using drain contact width: 0.24  $\mu$ m, spacer: 0.06  $\mu$ m, access transistor: 0.14  $\mu$ m, and isolation gate: 0.24  $\mu$ m, and taking the half width of the drain and isolation gate). An access transistor trench width of 0.14  $\mu$ m can be obtained using the appropriate processing technology, as known in the art. At an equal cell length of 0.56  $\mu$ m, the areal size 60 of a non-volatile memory cell of the first embodiment of the present invention is 0.44  $\mu$ m<sup>2</sup>.

The cell width of a flash cell in the second embodiment is only 0.55  $\mu m$  using the same size of the control gate/floating gate stack as in the first embodiment (and the half width of the drain, the half width of the access transistor). The areal size of this non-volatile memory cell is 0.31  $\mu m^2$ .

In comparison with the 2T non-volatile memory cell of the prior art as shown in Figure 1, a size reduction of approximately 30% and 50% can be obtained by using the

14

layout of a 2T non-volatile memory cell according to the first and second embodiment, respectively.

It should be understood that the sizes mentioned above are only used to illustrate the size reduction which can be obtained using the non-volatile memory cell according to the present invention.

5

CLAIMS:

5

20

25

1. A semiconductor device comprising in a semiconductor substrate (21) containing a first dopant type, a first non-volatile memory cell (20; 200) for storing a bit, comprising a first drain region (24) in said substrate (21), a first floating gate (29), a first control gate (30), a first thin gate isolation layer (27), and an insulating layer (32), said insulating layer (32) being positioned on top of said first floating gate (29), said first control gate (30) being positioned on top of said insulating layer (32), said first floating gate (29) being positioned on top of said first thin gate isolation layer (27), and further comprising a first access transistor (34) for controlling access to said first non-volatile memory cell (20; 200),

wherein said first non-volatile memory cell (20; 200) comprises a buried layer (22) in said substrate (21) containing a second dopant type and a first source region (26), said first access transistor (34) is formed in a first trench on said substrate (21), said first trench extending substantially from said first source region (26) to said surface of said substrate, said first trench being adjacent to said first floating gate (29) and directed in a first direction parallel to said surface of said substrate (21).

2. A semiconductor device according to claim 1, comprising in said semiconductor substrate (21), a second non-volatile memory cell (20') for storing a bit, comprising a second drain region (24') in said substrate (21), a second floating gate (29'), a second control gate (30'), a second thin gate isolation layer (27), and a second insulating layer (32'), said second insulating layer (32') being positioned on top of said second floating gate (29'), said second control gate (30') being positioned on top of said second insulating layer (32'), said second floating gate (29') being positioned on top of said second thin gate isolation layer (27), said buried layer (22) containing a second source region (26'), said device further comprising a second access transistor (34') for controlling access to said second non-volatile memory cell (20'), said second non-volatile memory cell (20') being adjacent to said first non-volatile memory cell (20) in a second direction, said second direction being parallel to said surface of said substrate (21) and perpendicular to said first direction,

15

20

PCT/IB02/01353 WO 02/086966

16

wherein said second access transistor (34') is formed in a second trench on said substrate (21), said second trench extending substantially from said second source region (26') to the surface of said substrate, said second trench being adjacent to said second floating gate (29') and directed in said second direction, and

- said first access transistor (34) of said first non-volatile memory cell (20) being separated 5 from said second access transistor (34') of said second non-volatile memory cell (20') by an isolation gate (38), comprising a dummy floating gate (29""), a dummy insulating layer (32"") and a dummy control gate (30""), said dummy insulating layer (32"") being positioned on top of said dummy floating gate (29""), said dummy control gate being positioned on top of said dummy insulating layer (32"").

- A semiconductor device according to claim 1, comprising in said 3. semiconductor substrate (21), a second non-volatile memory cell (200') for storing a bit, comprising a second drain region (24') in said substrate (21), a second floating gate (29'), a second control gate (30'), said second thin gate isolation layer (27), and a second insulating layer (32'), said second insulating layer (32') being positioned on top of said second floating gate (29'), said second control gate (30') being positioned on top of said second insulating layer (32'), said second floating gate (29') being positioned on top of said second thin gate isolation layer (27), said buried layer (22) containing a second source region (26'), said device further comprising a second access transistor (34') for controlling access to said second non-volatile memory cell (200'), said second non-volatile memory cell (200') being adjacent to said first non-volatile memory cell (200) in a second direction, said second direction being parallel to said surface of said substrate (21) and perpendicular to said first direction,

- wherein said second access transistor (34') is formed in a second trench on said substrate 25 (21), said second trench extending substantially from said second source region (26') to said surface of said substrate, said second trench being adjacent to said second floating gate (29') and directed in said second direction, and said first access transistor (34) of said first non-volatile memory cell (200) coinciding with 30 said second access transistor (34') of said second non-volatile memory cell (200').

- A non-volatile memory cell matrix comprising a plurality of non-volatile 4. memory cells (20, 20'; 200, 200') according to claim 2 or 3, wherein said plurality of non-

volatile memory cells (20, 20'; 200, 200') is arranged in said first direction and said second direction.

- 5. A non-volatile memory cell matrix according to claim 2, 3, or 4, wherein said plurality of non-volatile memory cells (20, 20'; 200, 200') are arranged in a common source arrangement.

- 6. A non-volatile memory cell matrix according to claim 4 or 5, wherein a first row of non-volatile memory cells is separated from a second row of non-volatile memory cells by an isolation line (STI) extending in said first direction.

- 7. A semiconductor device comprising a non-volatile memory cell matrix according to any one of the preceding claims.

10

- 8. A method of manufacturing a semiconductor device comprising in a semiconductor substrate (21) containing a first dopant type, a first non-volatile memory cell (20; 200) for storing a bit, comprising a first drain region (24) in said substrate (21), a first floating gate (29), a first control gate (30), a buried layer (22) containing a second dopant type and a first source region (26), a first thin gate isolation layer (27), and an insulating layer (32), said insulating layer (32) being positioned on top of said first floating gate (29), said first control gate (30) being positioned on top of said insulating layer (32), said first floating gate (29) being positioned on top of said first thin gate isolation layer (27), said arrangement further comprising a first access transistor (34), and said method comprising the following steps:

- 25 formation of said buried layer (22) in said substrate (21) by ion implantation;

- demarcation of an active area of said non-volatile memory cell (20; 200) by the formation of isolation lines (STI) extending in a first direction;

- formation of said first thin gate isolation layer (27) on said surface of said substrate (21);

- formation of a stacked gate structure (29, 30, 32) on top of said first gate isolation layer (27), said stacked gate structure comprising said first floating gate (29), said control gate (30), and said insulating layer (32);

- formation of said first access transistor (34) comprising the following steps:

- etching of a trench in said substrate (21) substantially from its surface

WO 02/086966 18

to said buried layer (22),

10

15

- formation of a second thin oxide (35) on the trench walls,

- deposition of doped polysilicon in said trench, said trench being adjacent to the stacked gate structure (29, 30, 32);

PCT/IB02/01353

- 5 passivation and metallization of said non-volatile memory cell (20; 200).

- 9. A method of reading a bit stored in a non-volatile memory cell matrix according to claim 3, said method of reading a bit comprising a step of measuring a source-drain current of said first and second non-volatile memory cells (200, 200'), characterized in that said step of measuring said source-drain current comprises the application of a first voltage pulse to said first control gate (30), and the application of a second voltage pulse to said second control gate (30'), wherein a change of the source-drain current after said application of said first and second voltage pulses determines whether said first non-volatile memory cell (200) and said second non-volatile memory cell (200'), respectively, are programmed or not.

FIG. 4d

## INTERNATIONAL SEARCH REPORT

al Application No

| A. CLASSIFICATION OF SUBJECT MATTER IPC 7 H01L21/8247 H01L27/115                                                                                                                                                                                                                     |                                                                                                                                                            |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                    |                                                                                                                                                            |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| B. FIELDS SEARCHED                                                                                                                                                                                                                                                                   |                                                                                                                                                            |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| Minimum documentation searched (classification system followed by classification symbols)                                                                                                                                                                                            |                                                                                                                                                            |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| IPC 7                                                                                                                                                                                                                                                                                | H01L                                                                                                                                                       |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| Documentat                                                                                                                                                                                                                                                                           | ion searched other than minimum documentation to the extent that                                                                                           | t such documents are included in the fields se                                    | arched                                                                                                                                                                             |  |  |  |  |  |  |

| Electronic da                                                                                                                                                                                                                                                                        | ata base consulted during the international search (name of data                                                                                           | base and, where practical, search terms used)                                     | )                                                                                                                                                                                  |  |  |  |  |  |  |

| EPO-In                                                                                                                                                                                                                                                                               | ternal, WPI Data, PAJ                                                                                                                                      |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| C. DOCUME                                                                                                                                                                                                                                                                            | ENTS CONSIDERED TO BE RELEVANT                                                                                                                             |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| Category °                                                                                                                                                                                                                                                                           | Citation of document, with indication, where appropriate, of the                                                                                           | relevant passages                                                                 | Relevant to claim No.                                                                                                                                                              |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                      |                                                                                                                                                            |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| Х                                                                                                                                                                                                                                                                                    | US 5 675 161 A (THOMAS MAMMEN)                                                                                                                             |                                                                                   | 1,3-8                                                                                                                                                                              |  |  |  |  |  |  |

| А                                                                                                                                                                                                                                                                                    | 7 October 1997 (1997-10-07)<br>abstract; figure 4                                                                                                          |                                                                                   | 2,9                                                                                                                                                                                |  |  |  |  |  |  |

| х                                                                                                                                                                                                                                                                                    | US 5 049 515 A (TZENG JYH-CHERN<br>17 September 1991 (1991-09-17)                                                                                          | G J)                                                                              | 1,3-8                                                                                                                                                                              |  |  |  |  |  |  |

| А                                                                                                                                                                                                                                                                                    | the whole document                                                                                                                                         |                                                                                   | 2,9                                                                                                                                                                                |  |  |  |  |  |  |

| х                                                                                                                                                                                                                                                                                    | US 5 495 441 A (HONG GARY)<br>27 February 1996 (1996-02-27)                                                                                                |                                                                                   | 1,3-8                                                                                                                                                                              |  |  |  |  |  |  |

| Α                                                                                                                                                                                                                                                                                    | the whole document                                                                                                                                         |                                                                                   | 2,9                                                                                                                                                                                |  |  |  |  |  |  |

| A                                                                                                                                                                                                                                                                                    | US 4 905 062 A (ESQUIVEL AGERICATION 1990 (1990-02-27) column 3, line 61 -column 4, liftigure 5                                                            |                                                                                   | 6                                                                                                                                                                                  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                      |                                                                                                                                                            |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                      |                                                                                                                                                            |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| Further documents are listed in the continuation of box C.  Patent family members are listed in annex.                                                                                                                                                                               |                                                                                                                                                            |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| ° Special categories of cited documents:  "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the                                                  |                                                                                                                                                            |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| *A' document defining the general state of the arr which is not considered to be of particular relevance cited to understand the principle or theory underlying the invention  *E' earlier document but published on or after the international filling date cannot be considered to |                                                                                                                                                            |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

| *L* docume<br>which                                                                                                                                                                                                                                                                  | ent which may throw doubts on priority claim(s) or<br>i is cited to establish the publication date of another<br>in or other special reason (as specified) | involve an inventive step when the do "Y" document of particular relevance; the o | involve an inventive step when the document is taken alone  "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the |  |  |  |  |  |  |

| "O" docum<br>other                                                                                                                                                                                                                                                                   | nent referring to an oral disclosure, use, exhibition or means ent published prior to the international filling date but                                   | document is combined with one or mo                                               | document is combined with one or more other such docu-<br>ments, such combination being obvious to a person skilled                                                                |  |  |  |  |  |  |

| later t                                                                                                                                                                                                                                                                              | han the priority date claimed                                                                                                                              |                                                                                   | '&' document member of the same patent family  Date of mailing of the international search report                                                                                  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | actual completion of the international search 26 July 2002                                                                                                 | 05/08/2002                                                                        | ягон героп                                                                                                                                                                         |  |  |  |  |  |  |

| <u> </u>                                                                                                                                                                                                                                                                             | mailing address of the ISA                                                                                                                                 | Authorized officer                                                                |                                                                                                                                                                                    |  |  |  |  |  |  |

| , manno ana                                                                                                                                                                                                                                                                          | European Patent Office, P.B. 5818 Patentlaan 2<br>NL – 2280 HV Rijswijk                                                                                    |                                                                                   |                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                                       | Blackley, W                                                                       |                                                                                                                                                                                    |  |  |  |  |  |  |

## INTERNATIONAL SEARCH REPORT

ormation on patent family members

HApplication No

PCT/IB 02/01353

| Patent document cited in search report | į | Publication<br>date |                      | Patent family<br>member(s)                           | Publication date                                     |

|----------------------------------------|---|---------------------|----------------------|------------------------------------------------------|------------------------------------------------------|

| US 5675161                             | Α | 07-10-1997          | NONE                 |                                                      |                                                      |

| US 5049515                             | Α | 17-09-1991          | US<br>GB<br>JP<br>JP | 4964080 A<br>2241825 A ,B<br>3000116 B2<br>4218974 A | 16-10-1990<br>11-09-1991<br>17-01-2000<br>10-08-1992 |

| US 5495441                             | Α | 27-02-1996          | NONE                 |                                                      |                                                      |

| US 4905062                             | Α | 27-02-1990          | NONE                 |                                                      |                                                      |