(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5612117号

(P5612117)

(45) 発行日 平成26年10月22日(2014.10.22)

(24) 登録日 平成26年9月12日(2014.9.12)

(51) Int.Cl.

G06F 11/34 (2006.01)

G06F 9/46 (2006.01)

F 1

G06F 11/34 S

G06F 9/46 41 O

G06F 11/34 M

請求項の数 24 (全 25 頁)

(21) 出願番号 特願2012-540011 (P2012-540011)

(86) (22) 出願日 平成22年11月17日 (2010.11.17)

(65) 公表番号 特表2013-511776 (P2013-511776A)

(43) 公表日 平成25年4月4日 (2013.4.4)

(86) 國際出願番号 PCT/US2010/057089

(87) 國際公開番号 WO2011/063031

(87) 國際公開日 平成23年5月26日 (2011.5.26)

審査請求日 平成24年7月20日 (2012.7.20)

(31) 優先権主張番号 61/262,704

(32) 優先日 平成21年11月19日 (2009.11.19)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 12/780,588

(32) 優先日 平成22年5月14日 (2010.5.14)

(33) 優先権主張国 米国(US)

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100159651

弁理士 高倉 成男

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100109830

弁理士 福原 淑弘

最終頁に続く

(54) 【発明の名称】マルチ・スレッド・プロセッサのパフォーマンスを測定するための方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

マルチ・スレッド・プロセッサの負荷を判定する方法であって、少なくとも1つの予め定められた期間中、前記マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドにおいて、少なくとも1つのアイドル・タスクを実行することと、前記アイドル・タスクは、前記少なくとも1つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている。

前記少なくとも1つの予め定められた期間において、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定することと、

前記少なくとも1カウントであるループ実行数に基づいて、少なくとも、前記マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドの負荷を判定することと、

測定された前記負荷に基づいて、前記マルチ・スレッド・プロセッサのためのパフォーマンス・プロファイルを決定することと、

予め定められたサンプリング期間においてすべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサのマルチ・スレッド・プロセッサ・サイクル数を判定することと、

前記予め定められたサンプリング期間中に生じるマルチ・スレッド・プロセッサ・サイクルの合計数を判定することと、

前記すべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、前記判定されたマルチ・スレッド・プロセッサ・サイクル数の、前記マルチ・スレッド・プロセ

10

20

ッサ・サイクルの、前記判定された合計数に対する比に基づいて、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを導出することとを備える方法。

【請求項 2】

前記マルチ・スレッド・プロセッサのうちの 1 または複数のスレッドのおののについて、前記パフォーマンス・プロファイルを表示すること、をさらに備える請求項 1 に記載の方法。

【請求項 3】

前記少なくとも 1 つの予め定められた期間において、少なくとも 1 つのアイドル・タスクの、少なくとも 1 カウントのループ実行を判定することはさらに、10

複数の予め定められた期間において、各予め定められた期間中、1 または複数のスレッドにおいておのの実行されているアイドル・タスクに関する各カウントのためのエントリを含むアイドル・タスク・カウントのアレイを形成することを備える、請求項 1 に記載の方法。

【請求項 4】

前記マルチ・スレッド・プロセッサを、前記 1 または複数のスレッドにおいてタスクが実行されないアイドル動作に強制することと、

少なくとも 1 つのスレッドにおいて、前記少なくとも 1 つのアイドル・タスクを実行することと、

前記マルチ・スレッド・プロセッサがアイドル動作に強制されている場合、少なくとも 1 つの予め定められた期間において、前記少なくとも 1 つのスレッドにおけるアイドル・タスクの実行に関する最大カウント値を判定することと、20

をさらに備える請求項 1 に記載の方法。

【請求項 5】

前記少なくとも 1 つの予め定められた期間における、前記少なくとも 1 つのアイドル・タスクの、少なくとも 1 カウントのループ実行数の、前記最大カウント値に対する比を計算することによって、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを決定すること、をさらに備える請求項 4 に記載の方法。

【請求項 6】

前記マルチ・スレッド・プロセッサのうちの 1 または複数のスレッドのすべてについて、前記パフォーマンス・プロファイルを表示すること、をさらに備える請求項 1 に記載の方法。30

【請求項 7】

マルチ・スレッド・プロセッサの負荷を判定する装置であって、

少なくとも 1 つの予め定められた期間中、前記マルチ・スレッド・プロセッサのうちの少なくとも 1 つのスレッドにおいて、少なくとも 1 つのアイドル・タスクを実行し、前記アイドル・タスクは、前記少なくとも 1 つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている、

前記少なくとも 1 つの予め定められた期間において、少なくとも 1 つのアイドル・タスクの、少なくとも 1 カウントのループ実行を判定し、40

少なくとも 1 カウントのループ実行数に基づいて、少なくとも、前記マルチ・スレッド・プロセッサのうちの少なくとも 1 つのスレッドの負荷を判定し、

測定された前記負荷に基づいて、前記マルチ・スレッド・プロセッサのためのパフォーマンス・プロファイルを決定し、

予め定められたサンプリング期間においてすべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、マルチ・スレッド・プロセッサ・サイクル数を判定し、

前記予め定められたサンプリング期間中に生じるマルチ・スレッド・プロセッサ・サイクルの合計数を判定し、

前記すべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、前記判定されたマルチ・スレッド・プロセッサ・サイクル数の、前記マルチ・スレッド・プロセ50

ツサ・サイクルの、前記判定された合計数に対する比に基づいて、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを導出する、

ように構成された少なくとも1つのプロセッサを備える装置。

【請求項8】

前記少なくとも1つのプロセッサはさらに、前記マルチ・スレッド・プロセッサのうちの1または複数のスレッドのおののについて、前記パフォーマンス・プロファイルを表示するように構成された、請求項7に記載の装置。

【請求項9】

前記少なくとも1つのプロセッサはさらに、複数の予め定められた期間において、各予め定められた期間中、1または複数のスレッドにおいておのの実行されているアイドル・タスクに関する各カウントのためのエントリを含むアイドル・タスク・カウントのアレイを形成することによって、前記少なくとも1つの予め定められた期間において、少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定するように構成された、請求項7に記載の装置。 10

【請求項10】

前記少なくとも1つのプロセッサはさらに、

前記マルチ・スレッド・プロセッサを、前記1または複数のスレッドにおいてタスクが実行されないアイドル動作に強制し、

少なくとも1つのスレッドにおいて、前記少なくとも1つのアイドル・タスクを実行し、 20

前記マルチ・スレッド・プロセッサがアイドル動作に強制されている場合、少なくとも1つの予め定められた期間において、前記少なくとも1つのスレッドにおけるアイドル・タスクの実行に関する最大カウント値を判定する

ように構成された、請求項7に記載の装置。

【請求項11】

前記少なくとも1つのプロセッサはさらに、前記少なくとも1つの予め定められた期間における、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行数の、前記最大カウント値に対する比を計算することによって、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを決定する、ように構成された請求項10に記載の装置。 30

【請求項12】

前記少なくとも1つのプロセッサはさらに、前記マルチ・スレッド・プロセッサのうちの1または複数のスレッドのすべてについて、前記パフォーマンス・プロファイルを表示するように構成された、請求項11に記載の装置。

【請求項13】

マルチ・スレッド・プロセッサの負荷を判定する装置であって、

少なくとも1つの予め定められた期間中、マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドにおいて、少なくとも1つのアイドル・タスクを実行する手段と、前記アイドル・タスクは、前記少なくとも1つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている。 40

前記少なくとも1つの予め定められた期間において、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定する手段と、

前記少なくとも1カウントであるループ実行数に基づいて、少なくとも、前記マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドの負荷を判定する手段と、

前記少なくとも1つの予め定められた期間において、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行数の、最大カウント値に対する比を計算することによって、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを決定する手段と、

予め定められたサンプリング期間においてすべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、マルチ・スレッド・プロセッサ・サイクル数を判定する手 50

段と、

前記予め定められたサンプリング期間中に生じるマルチ・スレッド・プロセッサ・サイクルの合計数を判定する手段と、

前記すべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、前記判定されたマルチ・スレッド・プロセッサ・サイクル数の、前記マルチ・スレッド・プロセッサ・サイクルの、前記判定された合計数に対する比に基づいて、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを導出する手段と

を備える装置。

【請求項 14】

測定された前記負荷に基づいて、前記マルチ・スレッド・プロセッサのためのパフォーマンス・プロファイルを決定する手段、をさらに備える請求項 13 に記載の装置。 10

【請求項 15】

前記マルチ・スレッド・プロセッサのうちの 1 または複数のスレッドのおののについて、前記パフォーマンス・プロファイルを表示する手段、をさらに備える請求項 14 に記載の装置。

【請求項 16】

前記少なくとも 1 つの予め定められた期間において、前記少なくとも 1 つのアイドル・タスクの、少なくとも 1 カウントのループ実行を判定する手段はさらに、

複数の予め定められた期間において、各予め定められた期間中、1 または複数のスレッドにおいておののの実行されているアイドル・タスクに関する各カウントのためのエントリを含むアイドル・タスク・カウントのアレイを形成する手段をさらに備える、

請求項 13 に記載の装置。 20

【請求項 17】

前記マルチ・スレッド・プロセッサを、前記 1 または複数のスレッドにおいてタスクが実行されないアイドル動作に強制する手段と、

少なくとも 1 つのスレッドにおいて、前記少なくとも 1 つのアイドル・タスクを実行する手段と、

前記マルチ・スレッド・プロセッサがアイドル動作に強制されている場合、少なくとも 1 つの予め定められた期間において、前記少なくとも 1 つのスレッドにおけるアイドル・タスクの実行に関する最大カウント値を判定する手段と、

をさらに備える請求項 13 に記載の装置。 30

【請求項 18】

前記マルチ・スレッド・プロセッサのうちの 1 または複数のスレッドのすべてについて、前記パフォーマンス・プロファイルを表示する手段、をさらに備える請求項 13 に記載の装置。

【請求項 19】

コンピュータ読み取可能な記録媒体であって、

コンピュータに対して、マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを生成させるためのコードを記録し、前記コードは、

コンピュータに対して、少なくとも 1 つの予め定められた期間中、前記マルチ・スレッド・プロセッサのうちの少なくとも 1 つのスレッドにおいて、少なくとも 1 つのアイドル・タスクを実行させるためのコードと、前記アイドル・タスクは、前記少なくとも 1 つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている、

40

コンピュータに対して、前記少なくとも 1 つの予め定められた期間において、前記少なくとも 1 つのアイドル・タスクの、少なくとも 1 カウントのループ実行を判定させるためのコードと、

コンピュータに対して、前記少なくとも 1 カウントのループ実行数に基づいて、前記マルチ・スレッド・プロセッサのうちの少なくとも 1 つのスレッドの負荷を判定させるためのコードと、

50

コンピュータに対して、前記少なくとも1つの予め定められた期間における、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行数の、最大カウント値に対する比を計算させることによって、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを決定させるためのコードと、

コンピュータに対して、予め定められたサンプリング期間においてすべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、マルチ・スレッド・プロセッサ・サイクル数を判定させるためのコードと、

コンピュータに対して、前記予め定められたサンプリング期間中に生じるマルチ・スレッド・プロセッサ・サイクルの合計数を判定させるためのコードと、

コンピュータに対して、前記すべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、前記判定されたマルチ・スレッド・プロセッサ・サイクル数の、前記マルチ・スレッド・プロセッサ・サイクルの、前記判定された合計数に対する比に基づいて、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを導出させるためのコードと、

を備えるコンピュータ読取可能な記録媒体。

#### 【請求項20】

コンピュータに対して、測定された前記負荷に基づいて、前記マルチ・スレッド・プロセッサのためのパフォーマンス・プロファイルを決定させるためのコードをさらに記録した、請求項19に記載のコンピュータ読取可能な記録媒体。

#### 【請求項21】

コンピュータに対して、前記マルチ・スレッド・プロセッサのうちの1または複数のスレッドのおののについて、前記パフォーマンス・プロファイルを表示させるためのコードをさらに記録した、請求項20に記載のコンピュータ読取可能な記録媒体。

#### 【請求項22】

前記コンピュータに対して、少なくとも1つの予め定められた期間において、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定させるためのコードはさらに、

コンピュータに対して、複数の予め定められた期間において、各予め定められた期間中、1または複数のスレッドにおいておのの実行されているアイドル・タスクに関する各カウントのためのエントリを含むアイドル・タスク・カウントのアレイを形成させるためのコードを記録した、請求項19に記載のコンピュータ読取可能な記録媒体。

#### 【請求項23】

コンピュータに対して、前記マルチ・スレッド・プロセッサを、前記1または複数のスレッドにおいてタスクが実行されないアイドル動作に強制させるためのコードと、

コンピュータに対して、少なくとも1つのスレッドにおいて、前記少なくとも1つのアイドル・タスクを実行させるためのコードと、

前記マルチ・スレッド・プロセッサがアイドル動作に強制されている場合、コンピュータに対して、少なくとも1つの予め定められた期間において、前記少なくとも1つのスレッドにおけるアイドル・タスクの実行に関する最大カウント値を判定させるためのコードと、

をさらに記憶した、請求項19に記載のコンピュータ読取可能な記録媒体。

#### 【請求項24】

コンピュータに対して、前記マルチ・スレッド・プロセッサのうちの1または複数のスレッドのすべてについて、前記パフォーマンス・プロファイルを表示させるためのコードをさらに記憶した、請求項19に記載のコンピュータ読取可能な記録媒体。

#### 【発明の詳細な説明】

#### 【優先権の主張】

#### 【0001】

本特許出願は、本明細書において参照によって明確に組み込まれ、本願の譲受人に譲渡された2009年11月19日出願の「マルチ・スレッド・プロセッサのパフォーマンス

10

20

30

40

50

・プロファイルのための方法および装置」(METHODS AND APPARATUS FOR PERFORMANCE PROFILING OF A MULTI-THREAD PROCESSOR)と題された仮出願番号61/262,704の優先権を主張する。

【技術分野】

【0002】

本開示は、一般に、マルチ・スレッド・プロセッサのパフォーマンスを測定するための方法および装置に関し、さらに詳しくは、例えば、スレッド毎ベースで、かつ、さまざまな用途およびデータ・レートについて、無線デバイスのようなデバイスにおけるマルチ・スレッド・プロセッサの負荷測定およびパフォーマンス・プロファイリングのための方法および装置に関する。

10

【背景技術】

【0003】

例えば無線デバイスのようなデバイスでは、無線通信が実行されているプロセッサのパフォーマンスのプロファイリングが重要である。プロセッサ・パフォーマンスのプロファイリングおよび測定は、設計最適化のための見識を提供するのみならず、設計デバックのための便利なツールをも提供する。このようなプロファイリングの結果は、一例において、例えば無線デバイスのように、プロセッサを利用するデバイスにおけるリソース管理のために使用されうる。プロファイリングがリアル・タイム方式で実行される場合、このようなリソース管理は動的かつ柔軟でありうる。一例は、パフォーマンス・プロファイリングに基づいて測定される、通信フロー制御ベースのプロセッサ負荷である。

20

【0004】

無線技術が発展すると、多くの洗練されたモバイル機能や高いデータ・レートが、無線デバイスまたはハンドヘルド・デバイスで実現されることが望まれる。これにしたがって、無線デバイスのプロセッサ技術も発展する。例えばGSM(登録商標)/GPRSのような2Gセルラ技術の場合、一般的なプロセッサは、単一スレッド・アーキテクチャに基づく一方、例えばHSPA+/LTE/EV-DOのような3G/4Gセルラ技術の場合、プロセッサは、マルチ・スレッド・ベースになるように発展してきた。

【0005】

しかしながら、当該技術分野において利用可能などのスキームまたは装置も、さまざまな用途ケースおよびデータ・レートの下で、マルチ・スレッド・プロセッサCPUの負荷を測定しない。さらに、例えば無線デバイスのようなデバイスにおいて、パケット・データ・セッションが進行中である場合、マルチ・スレッド・プロセッサCPUの使用量を、各スレッド毎に調べるために利用可能な既知のツールも計器も存在しない。さらに、無線デバイスにおいて、パケット・データ・セッションが進行中である場合、マルチ・スレッド・プロセッサ“all-wait”(すなわち、すべてのプロセッサ・スレッドがアイドルである)状態をプローブするために利用可能な既知のツールも計器も存在しない。したがって、マルチ・スレッド・プロセッサの負荷を判定し、判定された負荷を用いて、プロセッサのパフォーマンスをプロファイルするためのニーズがある。

30

【発明の概要】

【0006】

態様では、マルチ・スレッド・プロセッサの負荷を判定する方法が開示される。この方法は、少なくとも1つの予め定められた期間中、マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドにおいて、少なくとも1つのアイドル・タスクを実行することを含む。このアイドル・タスクは、少なくとも1つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている。少なくとも1つの予め定められた期間において、少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行が判定される。最後に、この方法は、少なくとも1カウントであるループ実行数に基づいて、少なくとも、マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドの負荷を判定することを含む。

40

【0007】

50

別の態様では、マルチ・スレッド・プロセッサの負荷を判定する装置が開示される。この装置は、少なくとも1つの予め定められた期間中、マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドにおいて、少なくとも1つのアイドル・タスクを実行するように構成された少なくとも1つのプロセッサを含む。ここでは、このアイドル・タスクは、少なくとも1つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている。このプロセッサはまた、少なくとも1つの予め定められた期間において、少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定するように構成される。最後に、このプロセッサは、少なくとも1カウントのループ実行数に基づいて、少なくとも、マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドの負荷を判定するように構成される。

10

#### 【0008】

さらに別の態様によれば、マルチ・スレッド・プロセッサの負荷を判定する装置が開示される。この装置は、少なくとも1つの予め定められた期間中、マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドにおいて、少なくとも1つのアイドル・タスクを実行する手段を含む。ここで、このアイドル・タスクは、少なくとも1つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている。少なくとも1つの予め定められた期間において、少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定する手段がさらに含まれる。さらに、この装置は、少なくとも1つのカウントからなるループ実行数に基づいて、少なくとも、マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドの負荷を判定する手段をも含む。

20

#### 【0009】

さらにもう1つの態様によれば、コンピュータ読取可能な媒体を備えるコンピュータ・プログラム製品が開示される。この媒体は、コンピュータに対して、マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを生成させるためのコードを備える。ここで、このコードは、コンピュータに対して、少なくとも1つの予め定められた期間中、マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドにおいて、少なくとも1つのアイドル・タスクを実行させるためのコードを含む。このアイドル・タスクは、少なくとも1つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている。さらに、コンピュータに対して、少なくとも1つの予め定められた期間において、少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定させるためのコードと、コンピュータに対して、少なくとも1カウントのループ実行数に基づいて、マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドの負荷を判定させるためのコードとが含まれる。

30

#### 【図面の簡単な説明】

#### 【0010】

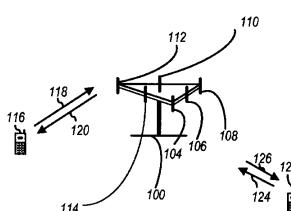

【図1】図1は、多元接続無線通信システムの例を例示する。

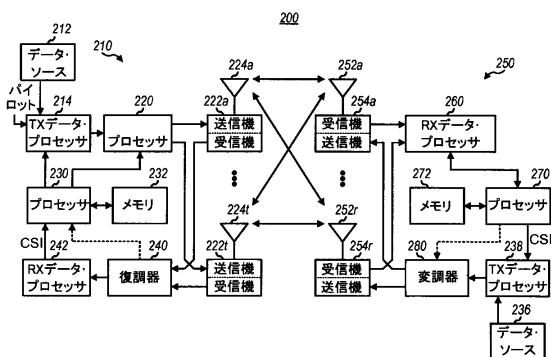

【図2】図2は、ここで開示された方法および装置を適用または利用しうる典型的な通信システムのブロック図である。

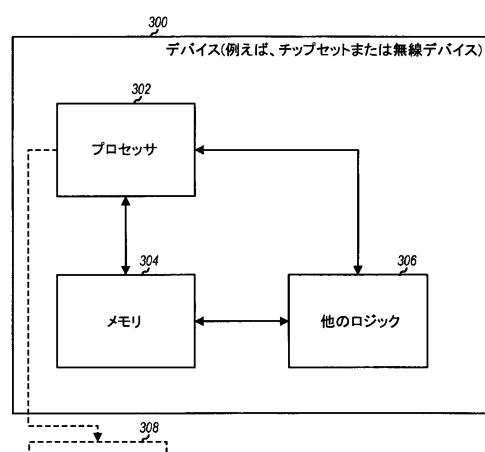

【図3】図3は、マルチ・スレッド・プロセッサ・プロファイリング構成のブロック図を例示する。

40

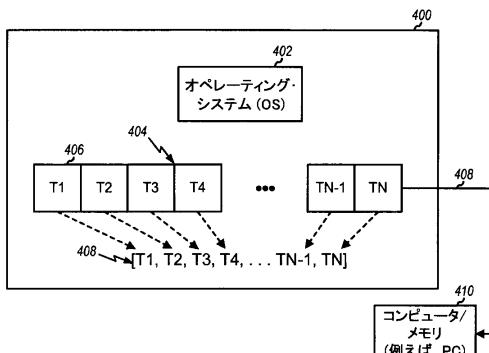

【図4】図4は、マルチ・スレッド・プロセッサの負荷を判定するための装置動作を例示するブロック図である。

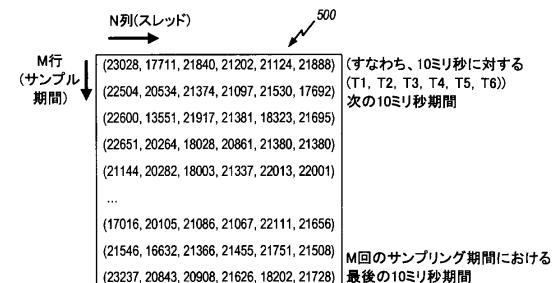

【図5】図5は、マルチ・スレッド・プロセッサの複数のスレッド上で動作するアイドル・タスクのカウントを累積するためのスリープ・ベクトルのアレイを例示する。

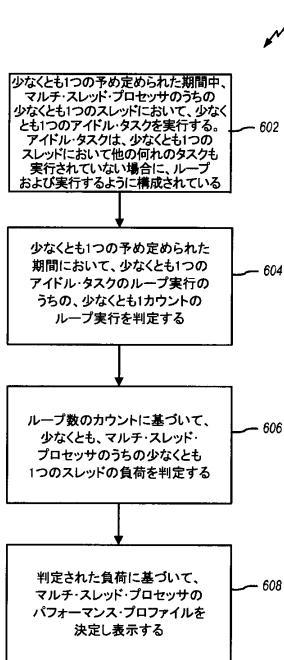

【図6】図6は、本開示の態様にしたがって、マルチ・スレッド・プロセッサ・プロファイリングを有効にする方法である。

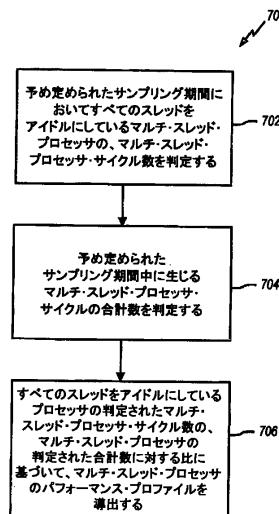

【図7】図7は、本開示の態様にしたがって、別のマルチ・スレッド・プロセッサ・プロファイリングを有効にする別の方法である。

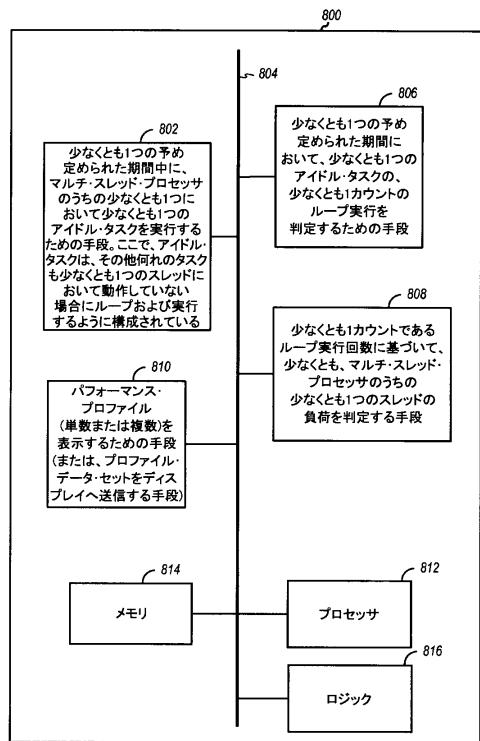

【図8】図8は、マルチ・スレッド・プロセッサのプロファイルを決定するための別の典

50

型的な装置のブロック図を例示する。

【発明を実施するための形態】

【0011】

本開示は、例えば高速パケット・アクセス（HSPA）技術、イボルブドHSPA（HSAPA+）技術、ロング・ターム・イボリューション（LTE）技術、およびEV-DO技術のような、3G / 4G技術のためのデバイスで使用されるような、マルチ・スレッド・プロセッサCPUのパフォーマンスの測定および／またはプロファイリングをする方法および装置に注目する。さらに、ここで開示される方法および装置は、マルチ・スレッドCPU使用量または動作の設計または最適化において使用するためにリアル・タイムで表示されうるリアル・タイム・プロファイリングおよび／または測定を行う。

10

【0012】

本明細書に記載された装置および方法は、マルチ・スレッド・プロセッサを利用するさまざまなデバイスに適用可能である。特定の態様では、本装置および方法は、無線デバイスにおけるプロセッサ動作の最適化を支援するために、マルチ・スレッド・プロセッサを利用する無線デバイスに適用されうる。このようなデバイスが実施しうる典型的な無線通信技術は、符号分割多元接続（CDMA）、時分割多元接続（TDMA）ネットワーク、周波数分割多元接続（FDMA）、直交FDMA（OFDMA）、シングル・キャリアFDMA（SC-FDMA）、高速パケット接続（HSPAおよびHSPA+）技術、ロング・ターム・イボリューション（LTE）、EV-DO技術等を含みうる。CDMAネットワークは、例えば、ユニバーサル地上ラジオ・アクセス（UTRA）、cdma2000等のようなラジオ技術を実現しうる。UTRAは、広帯域CDMA（W-CDMA）および低チップ・レート（LCR）を含む。cdma2000は、IS-2000規格、IS-95規格、およびIS-856規格をカバーする。TDMAネットワークは、例えばグローバル移動体通信システム（GSM（登録商標））のようなラジオ技術を実現しうる。OFDMAネットワークは、例えば、ウルトラ・モバイル帯域幅（UMB）、イボルブドUTRA（E-UTRA）、IEEE 802.11、IEEE 802.16（WiMax）、IEEE 802.20、フラッシュ-OFDM等のようなラジオ技術を実現することができる。UTRA、E-UTRA、およびGSMは、ユニバーサル・モバイル・テレコミュニケーション・システム（UMTS）の一部である。ロング・ターム・イボリューション（LTE）は、E-UTRAを使用するUMTSの最新のリリースである。UTRA、E-UTRA、GSM、UMTS、およびLTEは、「第3世代パートナシップ計画」（3GPP）と命名された組織からの文書に記載されている。cdma2000は、「第3世代パートナシップ計画2」（3GPP2）と命名された組織からの文書に記載されている。これらさまざまなラジオ技術および規格は、当該技術分野において知られている。

20

【0013】

さらに、本明細書で使用される用語「プロセッサ」は、限定される訳ではないが、CPU、ASIC、デジタル信号プロセッサ（DSP）、または、命令群を実行することが可能なその他任意のタイプのプロセッサを含みうる。さらに、本開示は主にマルチ・スレッド・プロセッサに関連しているが、本装置および方法は、処理を並列につまり同時に実行している任意のプロセッサに、あるいは、潜在的にマルチ・タスクにさえも適合しうることが当業者に明らかとなるであろう。さらに、本開示は、無線システムで使用されるプロセッサのコンテキストで説明されているが、当業者であれば、本方法および装置は、アプリケーションまたは用途に関わらず、任意のマルチ・スレッド・プロセッサに適用されうることを認識するであろう。

30

【0014】

図1に示すように、本方法および装置が適用される多元接続無線通信システムの例が示される。アクセス・ポイント100（AP）は、1つは104および106を含み、別の1つは108および110を含み、さらに別の1つは112および114を含む複数のアンテナ・グループを含む。図1では、おのののアンテナ・グループについて2本のアン

40

50

テナしか示されていない。しかしながら、おのののアンテナ・グループについて、それより多いまたはそれより少ないアンテナが利用されうる。アクセス端末116(AT)(またはモバイル・デバイスまたはユーザ機器(UE))は、アンテナ112、114と通信しており、アンテナ112、114は、ダウンリンク(DL)すなわち順方向リンク120でアクセス端末116へ情報を送信し、アップリンク(UL)すなわち逆方向リンク118でアクセス端末116から情報を受信する。アクセス端末122は、アンテナ106、108と通信しており、アンテナ106、108は、順方向リンク126でアクセス端末122へ情報を送信し、逆方向リンク124でアクセス端末122から情報を受信する。FDDシステムでは、通信リンク118、120、124、126は、通信のために異なる周波数を使用することができる。例えば、DL120は、UE118によって使用されるものとは異なる周波数を使用しうる。TDDシステムでは、UL信号とDL信号とが時間多重化されて、単一の周波数が、UL118とDL120との両方のために使用される。10

#### 【0015】

通信するように設計された領域および/またはアンテナのおのののグループは、しばしば、アクセス・ポイントのセクタと称される。態様では、アンテナ・グループは各々、アクセス・ポイント100によってカバーされた領域のセクタ内のアクセス端末に通信するように設計される。

#### 【0016】

アクセス・ポイントは、端末と通信するために使用される固定局であり、アクセス・ポイント、ノードB、あるいはその他幾つかの専門用語でも称されうる。アクセス端末はまた、アクセス端末、ユーザ機器(UE)、無線通信デバイス、端末、アクセス端末、あるいはその他いくつかの専門用語で称されうる。20

#### 【0017】

図2は、空間ダイバーシティ多重化を提供するMIMOシステム200における(アクセス・ポイントとしても知られている)送信機システム210および(アクセス端末としても知られている)受信機システム250の例を示すプロック図である。送信機システム210では、多くのデータ・ストリーム用のトラフィック・データが、データ・ソース212から送信(TX)データ・プロセッサ214に提供される。

#### 【0018】

態様では、データ・ストリームはおののの、それぞれの送信アンテナを介して送信される。TXデータ・プロセッサ214は、おのののデータ・ストリームのトラフィック・データをフォーマットし、このデータ・ストリームのために選択された特定の符号化スキームに基づいて符号化し、インタリープして、符号化されたデータを提供する。30

#### 【0019】

おのののデータ・ストリームの符号化されたデータは、OFDM技術を用いてパイルット・データと多重化されうる。パイルット・データは一般に、既知の手法で処理される既知のデータ・パターンであり、チャネル応答を推定するために受信機システムにおいて使用されうる。おのののデータ・ストリームについて多重化されたパイルットおよび符号化されたデータは、データ・ストリームのために選択された特定の変調スキーム(例えば、BPSK、QPSK、M-PSK、あるいはM-QAM等)に基づいて変調(例えば、シンボル・マップ)され、変調シンボルが提供される。おのののデータ・ストリームのデータ・レート、符号化、および変調は、プロセッサ230によって実行される命令群によって決定されうる。40

#### 【0020】

すべてのデータ・ストリームの変調シンボルは、(例えば、OFDMのために)変調シンボルをさらに処理するTX MIMOプロセッサ220に提供される。TX MIMOプロセッサ220はその後、NT個の変調シンボル・ストリームを、NT個の送信機(TMTR)222a乃至222tへ提供する。ある態様では、TX MIMOプロセッサ220は、データ・ストリームのシンボル、および、このシンボルが送信されるアンテナへ

、ビームフォーミング重みを適用する。

#### 【0021】

おののの送信機222は、1または複数のアナログ信号を提供するために、それぞれのシンボル・ストリームを受信して処理し、さらには、MIMOチャネルを介した送信に適切な変調信号を提供するために、このアナログ信号を調整（例えば、増幅、フィルタ、およびアップコンバート）する。送信機222a乃至222tからのNT個の変調信号は、その後、NT個のアンテナ224a乃至224tからそれぞれ送信される。

#### 【0022】

受信機システム250では、送信された変調信号がNR個のアンテナ252a乃至252rによって受信され、おのののアンテナ252からの受信信号が、それぞれの受信機（RCVR）254a乃至254rへ提供される。おののの受信機254は、受信したそれぞれの信号を調整（例えば、フィルタ、増幅、およびダウンコンバート）し、この調整された信号をデジタル化してサンプルを提供し、さらにこのサンプルを処理して、対応する「受信された」シンボル・ストリームを提供する。

10

#### 【0023】

RXデータ・プロセッサ260は、NR個の受信機254からNR個のシンボル・ストリームを受信し、受信されたこれらシンボル・ストリームを、特定の受信機処理技術に基づいて処理して、NT個の「検出された」シンボル・ストリームを提供する。RXデータ・プロセッサ260は、その後、検出されたおのののシンボル・ストリームを復調し、デインタリープし、復号して、このデータ・ストリームのためのトラフィック・データを復元する。RXデータ・プロセッサ260による処理は、送信機システム210におけるTX MIMOプロセッサ220およびTXデータ・プロセッサ214によって実行されるものと相補的である。

20

#### 【0024】

逆方向リンク・メッセージすなわちULメッセージは、通信リンクおよび/または受信されたデータ・ストリームに関するさまざまなタイプの情報を備えうる。逆方向リンク・メッセージは、多くのデータ・ストリームのトラフィック・データをデータ・ソース236から受け取るTXデータ・プロセッサ238によって処理され、変調器280によって変調され、送信機254a乃至254rによって調整され、基地局210へ送り戻される。

30

#### 【0025】

送信機システム210では、受信機システム250からの変調された信号が、アンテナ224によって受信され、受信機222によって調整され、復調器240によって復調され、RXデータ・プロセッサ242によって処理されることにより、受信機システム250によって送信された逆方向リンク・メッセージすなわちULメッセージが抽出される。さらに、プロセッサ230は、ビームフォーミング重みを決定するためにどのプリコードイング行列を使用するかを決定し、この抽出されたメッセージを処理する。

#### 【0026】

本開示は、例えば、無線デバイス210、250におけるプロセッサ230、270のようなプロセッサをプロファイリングする装置および方法を提供するが、これは、無線デバイスであろうとなかろうと、任意の数のさまざまな装置における何れのマルチ・スレッド・プロセッサにも適用されうることが注目される。

40

#### 【0027】

実装の一例として、図3は、マルチ・スレッド・プロセッサ・プロファイリング構成のブロック図を例示する。例示されたように、統合されて、または、チップセット（例えば、移動局モデム（登録商標））として構成されうるか、または、一体デバイスとしてより広く考慮されうるデバイス300は、マルチ・スレッド・プロセッサであるプロセッサ302を含みうる。プロセッサ302とともにメモリ304が存在する。メモリ304は、プロセッサ302のパッケージングに統合されうるか、または、分離されうる（あるいは、デバイス300からさえも分離されうる）。さらに、デバイス300の内部（または、

50

外部)には、例えば、後に詳しく述べるような、プロセッサ302のすべてのスレッドがアイドルであるCPUサイクルを判定すること、のような追加のプロファイルまたはパフォーマンス・データを提供するための、他のロジック306が含まれうる。あるいは、ロジック306によって実行される機能は、プロセッサ302によって実行されうる。さらに、リアル・タイム・プロファイリング・データを表示するディスプレイ・インターフェース308が含まれうる。

#### 【0028】

図4は、マルチ・スレッド・プロセッサの負荷を判定するための装置動作を例示するブロック図である。この例示はシステム400を示す。これは、単なる一例であるが、例えば無線デバイスのようなデバイスにおいて動作可能なマルチ・スレッド処理システムを示す。このシステム400は、根底にあるオペレーティング・システム(OS)402に基づいて、マルチ・スレッドを含む動作を実行する。オペレーティング・システムおよび付随するソフトウェアは、マルチ・スレッド処理システムにおけるスレッドのうちの1または複数においてアイドル・タスクを実行するように構成されうる。アイドル・タスクは、他の何れのタスクもスレッド内で実行されていない場合に実行されるように構成され、無限ループまたはその他いくつかの反復動作でありうる。態様では、アイドル・タスクは、単に、反復がカウントされうるループ動作をのみを実行するループである。

#### 【0029】

態様では、システム400は、スレッドのうちの1または複数のそれぞれにおいて動作するアイドル・タスクのループのカウントを格納するために使用される、レジスタ404または等価のデバイス(または、ソフトウェアまたはファームウェアの場合における機能)を含みうる。レジスタ404は、レジスタ404内のカウント・ストレージのうちの1つを示す参照番号406によって例示されるように、おのののスレッドのため、個別のカウント・ストレージを含む。レジスタ404は、予め定められた期間(例えば、Tミリ秒(ms))において、N個のスレッド(T1乃至TN)のうちのおのので動作する各アイドル・タスクのカウントを格納する。態様では、レジスタ404は、N個の独立したスレッドのおのののために実行されたアイドル・タスクのループ・カウントを含む。おののがアイドル・タスク実行のループ・カウントを有するN個の要素を備え、ベクトル408によって数字的に示されているベクトルが、予め定められた期間(Tミリ秒)の各持続時間について形成される。ユーザへ表示するためにカウント・データを照合し処理するために、通信カップリング410を介して、例えばコンピュータおよびメモリ412のような処理デバイスへベクトルが出力される。

#### 【0030】

N個のスレッド・ベクトルのおののための、N個のアイドル・タスク・カウントである[T1, T2, T3, ..., TN]からなるベクトル408は、Tミリ秒のサンプリング期間の数からなるベクトル・アレイが形成されるように、Tミリ秒毎に出力される。したがって、Tミリ秒の予め定められた期間毎に、ベクトルの数が1ずつ増える。スリーピング・ベクトルの最大数は、予め定められた数Mである。M\*Tミリ秒後、すべてのアイドル・タスク・カウント・ベクトルが、M\*Nのサイズを持つアレイを形成する。このアレイは、M\*Tミリ秒後に更新される。

#### 【0031】

図5は、マルチ・スレッド・プロセッサのうちの複数のスレッドで動作するアイドル・タスクのためのカウントを蓄積するためのアイドル・タスク・カウント・ベクトルの典型的なアレイ500を例示する。例えば、スレッドの数N=6であり、予め定められたサンプリング期間T=10ミリ秒であり、サンプリング期間の合計数M=1024である場合、図示するように、スリーピング・アレイは、1024\*6(すなわち、M\*N)のアレイ500のように見える。図5の例は単なる例示であり、M、N、およびTの値は、所望の任意の数に設定されうることが注目される。

#### 【0032】

図6は、マルチ・スレッド・プロセッサ(例えば、プロセッサ302)のパフォーマン

10

20

30

40

50

スをプロファイルするために利用されるマルチ・スレッド・プロセッサ・プロファイリングのための方法 600 を例示する。方法 600 はまず、ブロック 602 に示すように、少なくとも 1 つの予め定められた期間中、マルチ・スレッド・プロセッサのうちの少なくとも 1 つのスレッドにおいて、少なくとも 1 つのアイドル・タスクを実行することを含む。このアイドル・タスクは、少なくとも 1 つのスレッドにおいて他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている。特定の態様では、ブロック 602 の処理は、マルチ・スレッド・プロセッサ（例えば、302）のうちの独立した各スレッドにおいて、それぞれのスレッドがアイドルである（すなわち、他のどの機能またはタスクもこのスレッドで実行されない）場合には常に、アイドル・タスクをループすることを実施することを含みうる。

10

#### 【0033】

方法 600 はさらに、ブロック 604 に示すように、少なくとも 1 つの予め定められた期間において、少なくとも 1 つのアイドル・タスクのループ実行のうちの、少なくとも 1 カウントのループ実行を判定することを含む。前述したように、カウントすることは、レジスタ 404 または類似のユニットまたは機能によって有効とされうる。さらなる態様では、ブロック 602 においてアイドル・タスクを実行すること、および、カウントすることを実行することの処理は、前述したように、M \* N ベクトル・アレイを形成するために、M 回の予め定められた期間、実行される。したがって、ブロック 602、604 は、M \* N アレイを取得するために、M 回の予め定められた期間における M 個のスレッドについて、複数の N 個のベクトルのためのループ実行のアイドル・タスク実行およびカウントすることを含む。

20

#### 【0034】

当業者によって、ブロック 602、604 の処理は、図 6 において時間的にシーケンシャルに例示されており、これら処理は、各アイドル・タスク・ループの実行後、予め定められた期間が終了するまで、レジスタがカウントを進める場合に同時に、または、反復して実行されうることもまた認識されるであろう。この期間が終了した後、レジスタは、M 回の期間のカウント・アレイが導出されるまで、予め定められた次の期間等におけるアイドル・タスクのループをカウントするために、ゼロにリセットされる。

#### 【0035】

例えば、少なくとも 1 つの予め定められた期間後のように、ブロック 604 の処理が完了した後、ブロック 606 によって例示されるように、カウントに基づいて、マルチ・スレッド・プロセッサのうちの 1 または複数の独立したスレッドの負荷を判定するために、ループ・カウント（単数または複数）が使用されうる。例において、アイドル・タスク・ループのカウントは、特定のスレッドがどれくらいの頻度でアイドルになるかのタイミングを与える。なぜなら、アイドル・タスクは、スレッド内で他の何れのタスクも実行されていない場合にのみ動作するように構成されているからである。したがって、所与のスレッドについて、所与の予め定められた期間における最大のスリープ・カウントが知られている場合、この期間の負荷は、通常のプロセッサ動作中のアイドル・タスク・ループの、ベースライン最大スリープ・カウントに対する比に基づいて決定されうる。複数の予め定められた期間（例えば、前述したように M 回の期間）におけるこの負荷は、マルチ・スレッド・プロセッサ内の 1 または複数のスレッドにどれくらい負荷がかかっているのかを知るために、パフォーマンス・プロファイルのうちの少なくとも 1 つの態様を導出するために使用されうる。

30

#### 【0036】

（図 6 には明示的に例示されていないが）ブロック 606 における負荷をどのようにして判定するかの 1 つの特定の例では、マルチ・スレッド・プロセッサのうちの 1 または複数のスレッドが、アイドル動作にあることが強制されうる。アイドル・タスクは、その後、少なくとも予め定められた期間、カウントされたアイドル・タスクのループ実行回数、マルチ・スレッド・プロセッサのおおののスレッドで動作しうる。別の特定の例では、アイドル・タスクは、前述した M \* N アレイを満たすための十分なカウントを得るために

40

50

、合計してM回の予め定められた期間の間動作する。プロセッサ（または、マルチ・スレッド・プロセッサとは別のプロセッサ）は、その後、アイドル・タスクのみが動作するM回の期間中、 $M * N$ アレイにログされた最大アイドル・タスク・カウント（本明細書では、最大スリープ・スカラ値または“MAX\_SLEEP\_SCALER”と称される）を発見しうる。実際、この値は、所与の任意のスレッドの100%CPUアイドル状態またはスリープを表す。

#### 【0037】

その後、N個のベクトルのにおける各スレッドのカウント値が、MAX\_SLEEP\_SCALER値によって除され、アイドル・タスクまたはスリープ・プロファイルが導出される。これは、特定のスレッドの負荷を表す、最大アイドル・タスク状態に対するアイドル・タスクのパーセンテージである。あるいは、 $M * N$ アレイが決定された場合、M回の期間における特定のスレッドの合計カウントが総和され、MAX\_SLEEP\_SCALERによって除される。これは、特定のスレッドの負荷を取得するために、Mが乗じられる。何れの場合であれ、判定された負荷は、その後、ブロック608における処理によって示されるように、パーセンテージの単位で、または、その他任意の適切な数（例えば、単にMAX\_SLEEP\_SCALERによって除されたスリープ・カウントまたはアイドル・タスクのフラクション）で表示されうる。マルチ・スレッド・プロセッサでは、各アイドル・タスクまたはスリープ・プロファイルが、スレッド毎に表示されうる。

#### 【0038】

方法600におけるすべての処理を実行した後、方法600は、時間におけるプロファイリング・データの生成を続けるために連続的に反復するであろうことが注目される。一例において、予め定められた期間は、M回からなる合計の期間数が25に等しい場合、10ミリ秒でありうる。したがって、スリープ・プロファイルを決定するために使用されるデータの累積は、250ミリ秒毎に実行され（すなわち、ブロック602乃至606）、表示され（ブロック608）、その後も、250ミリ秒毎に反復され表示される。

#### 【0039】

図7は、マルチ・スレッド・プロセッサのための別のパフォーマンス・プロファイルを決定する別の典型的な方法700を例示する。図示するように、方法700は、ブロック702に示すように、予め定められたサンプリング期間（例えば、Yミリ秒）においてすべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、マルチ・スレッド・プロセッサ・サイクル数を判定することを含む。プロセッサ・サイクルという用語は、処理ユニットのCPUサイクルを示すことが注目される。さらに、どのサイクルがすべてのスレッドをアイドルにしているのかの判定は、図3に示すように、例えば、すべてのスレッドがアイドルである場合にインジケーションが出力されるロジック306のようなロジックによって実施されうる。態様では、この判定は、スレッドがタスクを実行していない場合に、スレッド・クロックがアイドルであるマルチ・スレッド・プロセッサの特性に依存しうることが注目される。したがって、このロジックは、すべてのスレッド・クロックがアイドルである場合、すべてのスレッドがアイドルであることを示すロジック状態を出力するように構成されうる。一例では、ブロック702の処理は、本明細書で“A11\_Wait\_Cycle”として称される、「すべてのスレッドが待機している（アイドルである）」マルチ・スレッド・プロセッサ・サイクルの回数を取得することを含む。

#### 【0040】

さらに、方法700は、ブロック704に示すように、予め定められたサンプリング期間（例えば、Yミリ秒）中に生じるマルチ・スレッド・プロセッサ・サイクルの合計数を判定することを含む。態様では、サンプリング期間中に生じるサイクルの合計数は、“Total\_Cycle”と称されうる。

#### 【0041】

さらに、方法700は、ブロック706に示されるように、すべてのスレッドをアイドルにしているプロセッサの、判定されたマルチ・スレッド・プロセッサ・サイクル数の、

10

20

30

40

50

マルチ・スレッド・プロセッサの、判定された合計数に対する比に基づいて、マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを導出することを含む。本明細書で“all-wait ratio”または“all-wait percentage”と称されるこの比は、商All\_Wait\_Cycle / Total\_Cycleで導出される。

#### 【0042】

方法600と同様に、方法700もまた、all-wait percentage情報を表示させるさらなる処理を含む。態様では、各スレッドがどれくらい利用されているかを示す負荷プロファイルを判定することによってのみならず、すべてのスレッドがどれだけの頻度でアイドルであるか待機しているかに関するプロファイルを判定することによって、マルチ・スレッド・プロセッサのより完全なパフォーマンス・プロファイル・レコード・データ・セットを取得するために、方法600、700がともに有用であることが注目される。さらに、開示された装置および方法は、Yミリ秒毎にプロファイリング・レコード・データ・セットを生成して、(例えば、プロセッサ(302)によって実施される機能である)ディスプレイ機能へ発行し、ディスプレイ・インターフェース(例えば、308)によってプロファイル情報を表示する。プロファイリング・レコード・データ・セットは、(例えば図4に示すような)アイドル・カウント・アレイと、上述したMAX\_SLEEP\_SCALERとから構成されうる。プロファイリング・レコード・データ・セットはまた、サンプリング期間Yミリ秒の間、all-wait percentageを含む。態様では、予め定められたサンプリング期間Yミリ秒は、カウント・アレイ内のM個の予め定められた期間の合計に等しくなりうることが注目される。生成されうるプロファイリング・レコード・データ・セットの例として、以下に示すテーブル1は、Y=250ミリ秒、予め定められた各期間が10ミリ秒に等しいN=6(6スレッド)、およびM=25(すなわち、 $25 \times 10$ ミリ秒=250ミリ秒からなる合計アレイ時間)を有する少なくとも3つのアイテムを持つ特定の例を与える。

【表1】

| レコード・アイテム                           | タイプ              | 説明                                                                       |

|-------------------------------------|------------------|--------------------------------------------------------------------------|

| MAX_250ms_SLEEP_SCALER              | ユニット32           | 250ミリ秒期間の最大アイドル・スリープ・カウントデフォルト=20500最大カウント*25                            |

| 250ミリ秒スリープ・プロファイリング生データ             | ユニット32<br>アレイ[6] | 250ミリ秒について6スリープ・プロファイリング生データ(6スレッド)                                      |

| 250ミリ秒中の<br>All-Waits percentage(%) | ユニット16           | この値は、250ミリ秒の期間中、6つすべてのスレッドが待機状態(すなわち、“All-Waits”)にある(0%乃至100%)パーセンテージである |

テーブル1:プロファイリング・レコード・データ・セット

#### 【0043】

図示されるように、含まれている3つのアイテムは、M=25の予め定められた期間のサンプリングを合計した205ミリ秒のMAX\_SLEEP\_SCALERと、10ミリ秒長さの予め定められた期間が乗じられたM=25のM\*Nアレイの生のカウント・データ(すなわち、250ミリ秒の合計期間)と、250ミリ秒からなる同じ期間中のAll-waitsパーセンテージとである。この例では、上述した表示機能は、パーセンテージの単位(%)でアイドル・カウントを導出しうる。すなわち、個々のスリープ・カウントを、MAX\_SLEEP\_SCALERを用いて除し、スレッド毎のスリープ・プロファイリングを表示する。それにも関わらず、代案では、このパーセンテージ計算は、監視

10

20

30

40

50

中のマルチ・スレッド・プロセッサによって実行され、データ・セット内の別のフィールドとして送信されうる。

#### 【0044】

図8は、マルチ・スレッド・プロセッサのプロファイルを決定するための別の典型的な装置800のブロック図を例示する。装置800は、マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを導出するように動作する方法600、700に関連して上述した機能のようなさまざまな機能を有効にするためのさまざまなモジュールまたは手段を含む。この装置800の手段またはモジュールは、ハードウェア、ソフトウェア、ファームウェア、またはこれらの任意の組み合わせを用いて実現されうる。さらに、監視中のマルチ・スレッド・プロセッサ、別のプロセッサ、パーソナル・コンピュータ、専用デバイス、またはこれら任意の組み合わせは、この装置800のさまざまなモジュールまたは手段を実現しうる。さらに、1つの態様では、装置800は、無線通信デバイス内に少なくとも部分的に実現されうる。

#### 【0045】

装置800は、少なくとも1つの予め定められた期間中に、マルチ・スレッド・プロセッサ（例えば、プロセッサ302）のうちの少なくとも1つにおいて少なくとも1つのアイドル・タスクを実行するための手段802を含む。ここで、アイドル・タスクは、その他何れのタスクも少なくとも1つのスレッドにおいて動作していない場合にループおよび実行するように構成されている。1つの例では、手段802は、プロセッサ302、および、特に、プロセッサのOS動作（例えばOS402）によって実現されうる。装置800はさらに、通信手段、または図8において、単に手段間の通信またはさまざまな機能間の情報の引き渡しを示すカップリング804として示される通信カップリング・デバイスを含む。

#### 【0046】

装置はさらに、少なくとも1つの予め定められた期間において、少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定するための手段806を含む。一例では、手段806はまた、例えばレジスタ（例えば、前述したレジスタ404）のようなアイドル・タスクのループのカウントをインクリメントして格納する手段と連携したマルチ・スレッド・プロセッサ（例えば、302）によって有効とされうる。手段806によって累積されたカウント情報は、少なくとも1カウントであるループ実行回数に基づいて、少なくとも、マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドの負荷を判定する手段808に通知されうる。手段808は、マルチ・スレッド・プロセッサ、別のプロセッサ、パーソナル・コンピュータ、または、マルチ・スレッド・プロセッサを含むデバイスの外側にある他のコンピュータ内に実装されうることが注目される。例えば、手段806からの生のカウント・データは、テーブル1におけるデータ・セットのようなデータ・セットの一部となりうる。このデータ・セットは、負荷を判定するために外部デバイスへ送られる。

#### 【0047】

さらに、装置800は、パフォーマンス・プロファイル（単数または複数）を表示するための手段810を含みうる。あるいは、装置810は、パフォーマンス・プロファイル・データ・セットを、装置800の外部のディスプレイ（図示せず）に送信するための手段として構成されうる。さらに、装置800は、代替案として、とりわけ、プロセッサ（例えば、マルチ・スレッド・プロセッサまたはプロセッサ812）によって実行可能なコードを格納するとともに、パフォーマンス・プロファイル・データを格納するメモリ814およびプロセッサ812を含みうる。最後に、装置800は、前述したA11\_Wait\_Cycleである、マルチ・スレッド・プロセッサがアイドルまたは待機中であるCPUサイクル数のようなデータを判定するように構成された追加のハードウェアまたはロジック816を含みうる。

#### 【0048】

当業者であれば、上記開示された装置および方法は、追加の機器またはソフトウェアを

10

20

30

40

50

必要とすることなく、プロセッサ・パフォーマンス・プロファーリングの動的かつリアル・タイムによる方式を与えることを認識するであろう。さらに、ここで開示されたプロファイリングは、パフォーマンス低下を引き起こさない。なぜなら、このプロファイリングは、一部、「アイドル」タスクで実行されるからである。本装置および方法は、デバッグや、電力最適化を含むシステム最適化のために役立つ。さらに、この方法および装置は、テスト・ツールとしてCPUを用いて、システムの設計および開発のために利用される。あるいは、CPUおよび/または付随するシステムの進行中の「オン・ザ・フライ」最適化を可能にするプロファイリングを実行するために、例えば、無線デバイスにおいて使用されるCPUを用いて実現されうる。

#### 【0049】

10

特定の態様では、本開示された方法および装置は、このようなデバイスにのみ限定されていないが、無線デバイスのためのプロセッサ・パフォーマンスを測定およびプロファイ尔するために、動的かつリアル・タイムでの方式で提供する。開示された方法および装置は、「アイドル」なタスクの設計および実装、“`all-wait percentage`”の設計、最大スリープまたはアイドル・カウント・スケーラを導出すること、プロファイリング・レコード・データ・セットを収集および発行すること、さらには、リアル・タイム方式での任意またはすべてのプロファイリング情報を表示することを含みうる。要約すると、ここで開示された装置および方法は、例えば無線デバイスで進行中であるパケット・データ・セッションのような特定のタスクが実行されている場合、さまざまな用途ケースおよびデータ・レートの下におけるマルチ・スレッド・プロセッサCPU負荷を測定するため、各スレッド毎のマルチ・スレッド・プロセッサCPU使用量を調べるために、そして、マルチ・スレッド・プロセッサ“`all-wait`”（すなわち、すべてのプロセッサ・スレッドがアイドルである）状態を調べるための、革新的な方式を提供する。提供されたこれらすべての機能は、無線標準化ツールまたは追加のいかなるツールも必要としないことが注目される。

#### 【0050】

20

本明細書において「典型的な」という用語は、「例、事例あるいは例示として役立つ」ことを意味するために使用されることが注目される。本明細書で“典型的である”と記載されたあらゆる実施形態は、他の実施形態によりも好適であるとか有利であるとか解釈される必要は必ずしもない。

#### 【0051】

30

開示された処理におけるステップの具体的な順序または階層は、単なる典型的なアプローチの例であることが理解される。設計選択に基づいて、これら処理におけるステップの具体的な順序または階層は、本開示のスコープ内であることを保ちながら、再構成されうることが理解される。方法請求項は、さまざまなステップの要素を、サンプル順で示しており、示された具体的な順序または階層に限定されないことが意味される。

#### 【0052】

当業者であれば、情報および信号は、さまざまな異なる技術および技法のうちの何れかを用いて表されることを理解するだろう。例えば、上記説明を通じて参照されうるデータ、命令群、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場または磁性粒子、光学場または光学粒子、あるいはこれらの任意の組み合わせによって表現されうる。

#### 【0053】

40

当業者であればさらに、本明細書で開示された実施形態に関連して記載された例示的なさまざまな論理ブロック、モジュール、回路、およびアルゴリズム・ステップは、電子的なハードウェア、コンピュータ・ソフトウェア、あるいはこれら両方の組み合わせとして実現されることを認識するであろう。ハードウェアとソフトウェアとの相互置換性を明確に説明するために、さまざまな例示的な構成要素、ブロック、モジュール、回路、およびステップが、これらの機能の観点から一般的に記載された。これら機能がハードウェアとしてまたはソフトウェアとして実現されるかは、特定のアプリケーションおよびシステム

50

全体に課せられている設計制約に依存する。当業者であれば、各特定のアプリケーションに応じて変化する方法で上述した機能を実現することができる。しかしながら、この適用判断は、本開示の範囲からの逸脱をもたらすものと解釈されるべきではない。

#### 【0054】

本明細書で開示された実施形態に関連して記述されたさまざまな例示的な論理ブロック、モジュール、および回路は、汎用プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(AVIC)、フィールド・プログラマブル・ゲート・アレイ(FPGA)あるいはその他のプログラマブル論理デバイス、ディスクリート・ゲートあるいはトランジスタ・ロジック、ディスクリート・ハードウェア構成要素、または上述された機能を実現するために設計された上記何れかの組み合わせを用いて実現または実施されうる。汎用プロセッサは、マイクロ・プロセッサでありうるが、代わりに、従来技術によるプロセッサ、コントローラ、マイクロコントローラ、あるいは順序回路を用いることも可能である。プロセッサは、例えばDSPとマイクロ・プロセッサとの組み合わせ、複数のマイクロ・プロセッサ、DSPコアと連携する1または複数のマイクロ・プロセッサ、またはその他任意のこのような構成であるコンピューティング・デバイスの組み合わせとして実現されうる。10

#### 【0055】

本明細書で開示された実施形態について記述された方法またはアルゴリズムのステップは、ハードウェアにおいて直接的に、プロセッサによって実行されるソフトウェア・モジュールによって、あるいはこれら2つの組み合わせによって具体化されうる。ソフトウェア・モジュールは、RAMメモリ、フラッシュ・メモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハード・ディスク、リムーバブル・ディスク、CD-ROM、あるいは当該技術分野で知られているその他の型式の記憶媒体に収納されうる。典型的な記憶媒体は、この記憶媒体から情報を読み取ったり、この記憶媒体に情報を書き込むことができるプロセッサのようなプロセッサに接続される。あるいは、この記憶媒体は、プロセッサに統合されうる。このプロセッサと記憶媒体とは、AVIC内に存在しうる。AVICは、ユーザ端末内に存在しうる。あるいは、プロセッサおよび記憶媒体は、ユーザ端末内のディスクリート部品として存在しうる。20

#### 【0056】

開示された実施形態の前述した記載は、いかなる当業者であっても、本発明を製造または使用できるように提供される。これら実施形態に対するさまざまな変形例もまた、当業者には明らかであって、本明細書で定義された一般的な原理は、本発明の主旨または範囲から逸脱することなく他の例にも適用されうる。このように、本発明は、本明細書で示された実施形態に限定されることは意図されておらず、本明細書に記載された原理および新規な特徴に一致した最も広い範囲に相当するものとされる。30

#### [C1]

マルチ・スレッド・プロセッサの負荷を判定する方法であって、

少なくとも1つの予め定められた期間中、前記マルチ・スレッド・プロセッサのうちの

少なくとも1つのスレッドにおいて、少なくとも1つのアイドル・タスクを実行すること

と、前記アイドル・タスクは、前記少なくとも1つのスレッドにおいて、他の何れのタス

クも実行されていない場合に、ループおよび実行するように構成されている、

前記少なくとも1つの予め定められた期間において、前記少なくとも1つのアイドル・

タスクの、少なくとも1カウントのループ実行を判定すること、

前記少なくとも1カウントであるループ実行数に基づいて、少なくとも、前記マルチ・

スレッド・プロセッサのうちの少なくとも1つのスレッドの負荷を判定することと、

を備える方法。

#### [C2]

測定された前記負荷に基づいて、前記マルチ・スレッド・プロセッサのためのパフォーマンス・プロファイルを決定すること、をさらに備えるC1に記載の方法。

#### [C3]

10

20

40

50

前記マルチ・スレッド・プロセッサのうちの 1 または複数のスレッドのおののについて、前記パフォーマンス・プロファイルを表示すること、をさらに備える C 2 に記載の方法。

[ C 4 ]

前記少なくとも 1 つの予め定められた期間において、少なくとも 1 つのアイドル・タスクの、少なくとも 1 カウントのループ実行を判定することはさらに、

複数の予め定められた期間において、各予め定められた期間中、1 または複数のスレッドにおいておののの実行されているアイドル・タスクに関する各カウントのためのエントリを含むアイドル・タスク・カウントのアレイを形成することを備える、C 1 に記載の方法。

10

[ C 5 ]

前記マルチ・スレッド・プロセッサを、前記 1 または複数のスレッドにおいてタスクが実行されないアイドル動作に強制することと、

少なくとも 1 つのスレッドにおいて、前記少なくとも 1 つのアイドル・タスクを実行することと、

前記マルチ・スレッド・プロセッサがアイドル動作に強制されている場合、少なくとも 1 つの予め定められた期間において、前記少なくとも 1 つのスレッドにおけるアイドル・タスクの実行に関する最大カウント値を判定することと、

をさらに備える C 1 に記載の方法。

[ C 6 ]

20

前記少なくとも 1 つの予め定められた期間における、前記少なくとも 1 つのアイドル・タスクの、少なくとも 1 カウントのループ実行数の、前記最大カウント値に対する比を計算することによって、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを決定すること、をさらに備える C 5 に記載の方法。

[ C 7 ]

予め定められたサンプリング期間においてすべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、マルチ・スレッド・プロセッサ・サイクル数を判定することと、

前記予め定められたサンプリング期間中に生じるマルチ・スレッド・プロセッサ・サイクルの合計数を判定することと、

30

前記すべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、予め定められたマルチ・スレッド・プロセッサ・サイクル数の、前記マルチ・スレッド・プロセッサ・サイクルの、予め定められた合計数に対する比に基づいて、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを導出することと、

をさらに備える C 1 に記載の方法。

[ C 8 ]

前記マルチ・スレッド・プロセッサのうちの 1 または複数のスレッドのすべてについて、前記パフォーマンス・プロファイルを表示すること、をさらに備える C 7 に記載の方法。

。

[ C 9 ]

40

マルチ・スレッド・プロセッサの負荷を判定する装置であって、

少なくとも 1 つの予め定められた期間中、前記マルチ・スレッド・プロセッサのうちの少なくとも 1 つのスレッドにおいて、少なくとも 1 つのアイドルなタスクを実行し、前記アイドル・タスクは、前記少なくとも 1 つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている、

前記少なくとも 1 つの予め定められた期間において、少なくとも 1 つのアイドル・タスクの、少なくとも 1 カウントのループ実行を判定し、

少なくとも 1 カウントのループ実行数に基づいて、少なくとも、前記マルチ・スレッド・プロセッサのうちの少なくとも 1 つのスレッドの負荷を判定する、

ように構成された少なくとも 1 つのプロセッサを備える、装置。

50

## [ C 1 0 ]

前記少なくとも 1 つのプロセッサはさらに、測定された前記負荷に基づいて、前記マルチ・スレッド・プロセッサのためのパフォーマンス・プロファイルを決定するように構成された、C 9 に記載の装置。

## [ C 1 1 ]

前記少なくとも 1 つのプロセッサはさらに、前記マルチ・スレッド・プロセッサのうちの 1 または複数のスレッドのおのののについて、前記パフォーマンス・プロファイルを表示するように構成された、C 1 0 に記載の装置。

## [ C 1 2 ]

前記少なくとも 1 つのプロセッサはさらに、複数の予め定められた期間において、各予め定められた期間中、1 または複数のスレッドにおいておののの実行されているアイドル・タスクに関する各カウントのためのエントリを含むアイドル・タスク・カウントのアレイを形成することによって、前記少なくとも 1 つの予め定められた期間において、少なくとも 1 つのアイドル・タスクの、少なくとも 1 カウントのループ実行を判定するように構成された、C 9 に記載の装置。

10

## [ C 1 3 ]

前記少なくとも 1 つのプロセッサはさらに、

前記マルチ・スレッド・プロセッサを、前記 1 または複数のスレッドにおいてタスクが実行されないアイドル動作に強制し、

少なくとも 1 つのスレッドにおいて、前記少なくとも 1 つのアイドル・タスクを実行し

20

前記マルチ・スレッド・プロセッサがアイドル動作に強制されている場合、少なくとも 1 つの予め定められた期間において、前記少なくとも 1 つのスレッドにおけるアイドル・タスクの実行に関する最大カウント値を判定する

ように構成された、C 9 に記載の装置。

## [ C 1 4 ]

前記少なくとも 1 つのプロセッサはさらに、前記少なくとも 1 つの予め定められた期間における、前記少なくとも 1 つのアイドル・タスクの、少なくとも 1 カウントのループ実行数の、前記最大カウント値に対する比を計算することによって、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを決定する、ように構成された C 1 3 に記載の装置。

30

## [ C 1 5 ]

前記少なくとも 1 つのプロセッサはさらに、

予め定められたサンプリング期間においてすべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、マルチ・スレッド・プロセッサ・サイクル数を判定し、

前記予め定められたサンプリング期間中に生じるマルチ・スレッド・プロセッサ・サイクルの合計数を判定し、

前記すべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、予め定められたマルチ・スレッド・プロセッサ・サイクル数の、前記マルチ・スレッド・プロセッサ・サイクルの、予め定められた合計数に対する比に基づいて、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを導出する

40

ように構成された、C 9 に記載の装置。

## [ C 1 6 ]

前記少なくとも 1 つのプロセッサはさらに、前記マルチ・スレッド・プロセッサのうちの 1 または複数のスレッドのすべてについて、前記パフォーマンス・プロファイルを表示するように構成された、C 1 5 に記載の装置。

## [ C 1 7 ]

マルチ・スレッド・プロセッサの負荷を判定する装置であって、

少なくとも 1 つの予め定められた期間中、マルチ・スレッド・プロセッサのうちの少なくとも 1 つのスレッドにおいて、少なくとも 1 つのアイドル・タスクを実行する手段と、

50

前記アイドル・タスクは、前記少なくとも1つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するよう構成されている、

前記少なくとも1つの予め定められた期間において、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定する手段と、

前記少なくとも1カウントであるループ実行数に基づいて、少なくとも、前記マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドの負荷を判定する手段と、を備える装置。

[ C 1 8 ]

測定された前記負荷に基づいて、前記マルチ・スレッド・プロセッサのためのパフォーマンス・プロファイルを決定する手段、をさらに備えるC 1 7に記載の装置。

10

[ C 1 9 ]

前記マルチ・スレッド・プロセッサのうちの1または複数のスレッドのおののについて、前記パフォーマンス・プロファイルを表示する手段、をさらに備えるC 1 8に記載の装置。

[ C 2 0 ]

前記少なくとも1つの予め定められた期間において、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定する手段はさらに、

複数の予め定められた期間において、各予め定められた期間中、1または複数のスレッドにおいておのの実行されているアイドル・タスクに関する各カウントのためのエントリを含むアイドル・タスク・カウントのアレイを形成する手段を備える、

20

C 1 7に記載の装置。

[ C 2 1 ]

前記マルチ・スレッド・プロセッサを、前記1または複数のスレッドにおいてタスクが実行されないアイドル動作に強制する手段と、

少なくとも1つのスレッドにおいて、前記少なくとも1つのアイドル・タスクを実行する手段と、

前記マルチ・スレッド・プロセッサがアイドル動作に強制されている場合、少なくとも1つの予め定められた期間において、前記少なくとも1つのスレッドにおけるアイドル・タスクの実行に関する最大カウント値を判定する手段と、

をさらに備えるC 1 7に記載の装置。

30

[ C 2 2 ]

前記少なくとも1つの予め定められた期間において、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行数の、前記最大カウント値に対する比を計算することによって、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを決定する手段、をさらに備えるC 2 1に記載の装置。

[ C 2 3 ]

予め定められたサンプリング期間においてすべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、マルチ・スレッド・プロセッサ・サイクル数を判定する手段と、

前記予め定められたサンプリング期間中に生じるマルチ・スレッド・プロセッサ・サイクルの合計数を判定する手段と、

40

前記すべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、予め定められたマルチ・スレッド・プロセッサ・サイクル数の、前記マルチ・スレッド・プロセッサ・サイクルの、予め定められた合計数に対する比に基づいて、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを導出する手段と、

をさらに備えるC 1 7に記載の装置。

[ C 2 4 ]

前記マルチ・スレッド・プロセッサのうちの1または複数のスレッドのすべてについて、前記パフォーマンス・プロファイルを表示する手段、をさらに備えるC 2 3に記載の装置。

50

## [ C 25 ]

コンピュータ・プログラム製品であって、

コンピュータに対して、マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを生成させるためのコードを備えるコンピュータ読取可能な媒体を備え、前記コードは

、

コンピュータに対して、少なくとも1つの予め定められた期間中、前記マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドにおいて、少なくとも1つのアイドル・タスクを実行させるためのコードと、前記アイドル・タスクは、前記少なくとも1つのスレッドにおいて、他の何れのタスクも実行されていない場合に、ループおよび実行するように構成されている、

10

コンピュータに対して、前記少なくとも1つの予め定められた期間において、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定させるためのコードと、

コンピュータに対して、前記少なくとも1カウントのループ実行数に基づいて、前記マルチ・スレッド・プロセッサのうちの少なくとも1つのスレッドの負荷を判定させるためのコードと、

を備えるコンピュータ・プログラム製品。

## [ C 26 ]

コンピュータに対して、測定された前記負荷に基づいて、前記マルチ・スレッド・プロセッサのためのパフォーマンス・プロファイルを決定させるためのコードをさらに備える、

C 25 に記載のコンピュータ・プログラム製品。

20

## [ C 27 ]

コンピュータに対して、前記マルチ・スレッド・プロセッサのうちの1または複数のスレッドのおののについて、前記パフォーマンス・プロファイルを表示させるためのコードをさらに備える、

C 26 に記載のコンピュータ・プログラム製品。

## [ C 28 ]

前記コンピュータに対して、少なくとも1つの予め定められた期間において、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行を判定させるためのコードはさらに、

コンピュータに対して、複数の予め定められた期間において、各予め定められた期間中、1または複数のスレッドにおいておのの実行されているアイドル・タスクに関する各カウントのためのエントリを含むアイドル・タスク・カウントのアレイを形成させるためのコードを備える、

C 25 に記載のコンピュータ・プログラム製品。

30

## [ C 29 ]

コンピュータに対して、前記マルチ・スレッド・プロセッサを、前記1または複数のスレッドにおいてタスクが実行されないアイドル動作に強制させるためのコードと、

コンピュータに対して、少なくとも1つのスレッドにおいて、前記少なくとも1つのアイドル・タスクを実行させるためのコードと、

前記マルチ・スレッド・プロセッサがアイドル動作に強制されている場合、コンピュータに対して、少なくとも1つの予め定められた期間において、前記少なくとも1つのスレッドにおけるアイドル・タスクの実行に関する最大カウント値を判定させるためのコードと、

40

をさらに備える、

C 25 に記載のコンピュータ・プログラム製品。

## [ C 30 ]

コンピュータに対して、前記少なくとも1つの予め定められた期間における、前記少なくとも1つのアイドル・タスクの、少なくとも1カウントのループ実行数の、前記最大カウント値に対する比を計算させることによって、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを決定させるためのコードをさらに備える、

C 29 に記載のコンピュータ・プログラム製品。

## [ C 31 ]

50

コンピュータに対して、予め定められたサンプリング期間においてすべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、マルチ・スレッド・プロセッサ・サイクル数を判定させるためのコードと、

コンピュータに対して、前記予め定められたサンプリング期間中に生じるマルチ・スレッド・プロセッサ・サイクルの合計数を判定させるためのコードと、

コンピュータに対して、前記すべてのスレッドをアイドルにしているマルチ・スレッド・プロセッサの、予め定められたマルチ・スレッド・プロセッサ・サイクル数の、前記マルチ・スレッド・プロセッサ・サイクルの、予め定められた合計数に対する比に基づいて、前記マルチ・スレッド・プロセッサのパフォーマンス・プロファイルを導出させるためのコードと、

をさらに備えるC 2 5に記載のコンピュータ・プログラム製品。

[ C 3 2 ]

コンピュータに対して、前記マルチ・スレッド・プロセッサのうちの1または複数のスレッドのすべてについて、前記パフォーマンス・プロファイルを表示させるためのコードをさらに備える、C 3 1に記載のコンピュータ・プログラム製品。

10

【図1】

図1

Fig. 1

【図3】

図3

Fig. 3

【図2】

図2

Fig. 2

【図4】

図4

Fig. 4

【図5】

図5

Fig. 5

【図6】

図6

Fig. 6

【図7】

図7

Fig. 7

【図8】

図8

Fig. 8

---

フロントページの続き

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(72)発明者 シュ、リヤンチ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドラ

イブ 5775

(72)発明者 カダガラ、ビジャイ・クマー

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドラ

イブ 5775

審査官 大塚 俊範

(56)参考文献 特開平04-062644(JP,A)

特開平07-006062(JP,A)

特開平11-327927(JP,A)

米国特許出願公開第2007/0288728(US,A1)

特開2003-241978(JP,A)

特表2006-524380(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 11/28 - 11/34

G 06 F 9/46