(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2018-516518

(P2018-516518A)

(43) 公表日 平成30年6月21日(2018.6.21)

(51) Int.Cl.

HO3M 1/66 (2006.01)

F 1

HO3M 1/66

テーマコード(参考)

C 5J022

審査請求 未請求 予備審査請求 未請求 (全 21 頁)

(21) 出願番号 特願2018-513922 (P2018-513922)

(86) (22) 出願日 平成28年5月26日 (2016.5.26)

(85) 翻訳文提出日 平成30年1月29日 (2018.1.29)

(86) 國際出願番号 PCT/GB2016/051534

(87) 國際公開番号 WO2016/193677

(87) 國際公開日 平成28年12月8日 (2016.12.8)

(31) 優先権主張番号 1509325.5

(32) 優先日 平成27年5月29日 (2015.5.29)

(33) 優先権主張國 英国(GB)

(71) 出願人 517416123

エムキューエー リミテッド

イギリス国 ケンブリッジシャー, ハンテ

インドン, ラッサム ロード 11

(71) 出願人 516369620

ライネ ソシエテ アー レスポンサビリ

テ リミテ

ルクセンブルク国 ルクセンブルク, ブー

ルバール プリンス ヘンリ 35

(74) 代理人 110001427

特許業務法人前田特許事務所

(72) 発明者 スチュアート ジョン ロバート

イギリス国 ケンブリッジシャー, ケンブ

リッジ, ストアイーズ ウェイ 21

F ターム(参考) 5J022 AB01 BA04 CA09 CD07 CE04

最終頁に続く

(54) 【発明の名称】デジタル・アナログ変換

## (57) 【要約】

デジタル・アナログ変換(DAC)装置及び方法が提供され、偶数個のデジタル・アナログコンバータのアナログ信号が合成される。個々のコンバータは、同じデータに対して動作するが、1つ以上のコンバータによって受信される入力デジタル信号とコンバータのうちの他のものによって受信される入力デジタル信号との間には、相対的な時間遅延が存在し、遅延はデータサンプリング周期の一部である。更に、コンバータのうちの半分に供給されるデジタル信号は、コンバータのうちの他方の半分に供給されるデジタル信号に対して反転した関係にあり、それらのアナログ出力は減算される。ディザ及びフィルタリング技術も採用され得る。

【選択図】図5

Fig. 5

## 【特許請求の範囲】

## 【請求項 1】

デジタル・アナログコンバータ（D A C）装置であって、データサンプリングレート  $F_s$  及びサンプリング周期  $1 / F_s$  を有するデジタル信号を受信する入力部と、

前記デジタル信号を受信する前記入力部に結合された  $N$  個（ $N$  は偶数の整数であり、 $N = 2$ ）のデジタル・アナログコンバータ（D A C）と、

前記入力部及び前記  $N$  個の D A C のうちの半分に結合されたインバータであって、それによって、前記  $N$  個の D A C のうちの前記半分によって受信される入力デジタル信号が前記  $N$  個の D A C のうちの他方の半分によって受信される前記入力デジタル信号に対して反転される、インバータと、

前記入力部に結合され、前記  $N$  個の D A C のうちの 1 つ以上によって受信される前記入力デジタル信号と前記  $N$  個の D A C のうちの他のものによって受信される前記入力デジタル信号との間に相対的な時間遅延を導入する、前記相対的な時間遅延が前記デジタル信号のサンプリング周期  $1 / F_s$  の部分である、遅延ユニットと、

前記  $N$  個の D A C に結合され、前記  $N$  個の D A C のうちの前記半分のアナログ出力を、前記  $N$  個の D A C のうちの前記他方の半分のアナログ出力と減算されるように合成して、出力アナログ信号を提供する合成器と、

を備える D A C 装置。

## 【請求項 2】

前記  $N$  個の D A C のうちの前記半分によって受信される前記入力デジタル信号と前記  $N$  個の D A C のうちの前記他方の半分によって受信される前記入力デジタル信号との間の相対的な時間遅延は、 $1 / (2 \times F_s)$  である、

請求項 1 の D A C 装置。

## 【請求項 3】

前記  $N$  個の D A C のうちの前記半分のそれぞれによって受信される前記入力デジタル信号間の前記相対的な時間遅延は、異なっており、前記  $N$  個の D A C のうちの前記他方の半分における対応する D A C によって受信される前記入力デジタル信号に対して  $1 / (2 \times F_s)$  遅れている、

請求項 1 の D A C 装置。

## 【請求項 4】

前記  $N$  個の D A C のうちの前記半分によって受信される前記入力デジタル信号と前記  $N$  個の D A C のうちの前記他方の半分によって受信される前記入力デジタル信号との間の前記相対的な時間遅延は、 $1 / (N \times F_s)$  である、

請求項 1 の D A C 装置。

## 【請求項 5】

前記  $N$  個の D A C のうちの前記半分のそれぞれによって受信される前記入力デジタル信号間の前記相対的な時間遅延は、異なっており、前記  $N$  個の D A C のうちの前記他方の半分における対応する D A C によって受信される前記入力デジタル信号に対して  $1 / (N \times F_s)$  遅れている、

請求項 1 の D A C 装置。

## 【請求項 6】

少なくとも 1 つの D A C には、前記入力デジタル信号からの同じ時間遅延を有する他の D A C が存在しない、

請求項 1 の D A C 装置。

## 【請求項 7】

前記入力部及び前記  $N$  個の D A C に結合されたディザユニットを更に備え、

前記ディザユニットは、前記  $N$  個の D A C のそれぞれによって受信される前記入力デジタル信号に加えるためのランダムなディザ信号を生成する、

請求項 1 ~ 6 のいずれか 1 項の D A C 装置。

10

20

30

40

50

**【請求項 8】**

前記ディザ信号は、整形されたディザ信号である、

請求項 7 の D A C 装置。

**【請求項 9】**

前記ディザ信号は、2 個以上の最下位ビット ( L S B ) を有する、

請求項 7 又は 8 の D A C 装置。

**【請求項 10】**

前記ディザ信号は、前記入力デジタル信号のサンプリングレートより高いレートで生成

される、

請求項 7 ~ 9 のいずれか 1 項の D A C 装置。

10

**【請求項 11】**

前記ディザ信号は、より低いレートのディザシーケンスをアップサンプリングすること

によって生成される、

請求項 10 の D A C 装置。

**【請求項 12】**

前記ディザ信号は、前記出力アナログ信号の復元レートで生成され、各 D A C の組に連

続して供給される、

請求項 10 又は 11 の D A C 装置。

20

**【請求項 13】**

前記ディザ信号は、前記 N 個の D A C の時間遅延毎に異なるフィルタでフィルタリング

される、

請求項 7 ~ 9 のいずれか 1 項の D A C 装置。

**【請求項 14】**

前記入力デジタル信号は、より高い周波数においてより少ないエネルギーを含むように

、ノイズ整形されている、

請求項 7 ~ 9 のいずれか 1 項の D A C 装置。

30

**【請求項 15】**

前記合成器は、前記 N 個の D A C のそれぞれのアナログ出力を、適用される重み付けを

して合成する、

請求項 1 ~ 14 のいずれか 1 項の D A C 装置。

40

**【請求項 16】**

前記適用される重み付けは、各アナログ出力について同じである、

請求項 15 の D A C 装置。

**【請求項 17】**

前記適用される重み付けは、前記 N 個の D A C のうちの少なくとも 2 個について異なる

、

請求項 15 の D A C 装置。

**【請求項 18】**

前記適用される重み付けは、各 D A C によって受信される前記入力デジタル信号の相対

的な時間遅延に依存する、

請求項 15 の D A C 装置。

**【請求項 19】**

前記デジタル信号は、デジタルオーディオ信号を含む、

請求項 1 ~ 18 のいずれか 1 項の D A C 装置。

**【請求項 20】**

前記デジタルオーディオ信号は、パルス符号変調 ( P C M ) 信号である、

請求項 19 の D A C 装置。

**【請求項 21】**

デジタル信号をアナログ信号に変換する方法であって、

データサンプリングレート  $F_s$  及びサンプリング周期  $1 / F_s$  を有するデジタル信号を

50

受信するステップと、

前記デジタル信号をN個（Nは偶数の整数であり、N≥2）のデジタル・アナログコンバータ（D A C）に、前記N個のD A Cのうちの半分によって受信される入力デジタル信号が前記N個のD A Cのうちの他方の半分によって受信される前記入力デジタル信号に対して反転されるように、かつ、前記N個のD A Cのうちの1つ以上によって受信される前記入力デジタル信号と前記N個のD A Cのうちの他のものによって受信される前記入力デジタル信号との間に相対的な時間遅延が存在するように、供給する、前記相対的な時間遅延が前記デジタル信号のサンプリング周期1/Fsの部分である、ステップと、

前記N個のD A Cのうちの前記半分のアナログ出力を、前記N個のD A Cのうちの前記他方の半分のアナログ出力と減算されるように合成して、出力アナログ信号を提供するステップと、

を備える、デジタル信号をアナログ信号に変換する方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、デジタル・アナログコンバータにおける改良に関し、特にそれらの高品質オーディオへの応用に関する。

【背景技術】

【0002】

デジタル・アナログコンバータ（D A C）は、電子機器において幅広く応用されており、デジタルデータをアナログ信号に変換する作用をする。これは、アナログ・デジタルコンバータ（A D C）の逆の作用をする。典型的にはより複雑な装置を必要とするが、デジタルデータは、アナログ信号と比べて、最小限の劣化で記憶、送信、及び処理が行われ得る。よって、この利益を得るために、アナログ信号をデジタルデータに変換することは、普通のことである。しかし、多くの応用において、最終的な用途のためにデジタルデータは最後には変換されてアナログ信号に戻らなければならない。

【0003】

詳細な例がオーディオ信号の送信及び処理にある。元の発生源からの音波がマイクロホン装置によって取得され、アナログ電気信号に変換され得る。A D Cを用いて、次にこれはデジタルストリームに変換され得て、それは記憶、送信、又は処理され得る。しかし、次にD A Cは、実際の音（空気の圧力波）を発生させるために、デジタル信号をイヤホン又はスピーカーアンプを駆動するアナログ電気信号に変換する必要がある。

【0004】

特定の応用によるデジタルデータの記憶及び送信のために、さまざまなフォーマットが存在する。例えば、映像及びオーディオデータを記憶するために使用される一般的なフォーマットはM P E G - 4であり、これはインターネット上でストリーミングを可能にするデジタルマルチメディアフォーマットである。

【0005】

高品質オーディオ用の他の一般的なフォーマットは、パルス符号変調（P C M）であり、それは、サンプリングされたアナログオーディオ信号をデジタル的に表現する方法に関する。このフォーマットでは、アナログ信号は均一な間隔でサンプリングされ、各サンプルはデジタルステップの範囲内で最も近い値に量子化される。

【0006】

結果として生じるP C Mストリームは、サンプリングレート及びビット深度によって特徴付けられ、サンプリングレートは元のオーディオ信号がサンプリングされる1秒あたりの回数であり、ビット深さは各サンプルを表現するのに使用可能なデジタル値の数を決定する。

【0007】

デジタル・アナログコンバータ（D A C）は、多くのやり方で実現可能である。リニアP C M（L P C M）には、2つのアーキテクチャが一般に使用されて来た。すなわち、a

) サンプリングレートでデジタルワードがアナログ出力に直接変換されるフラッシュ変換、及び b ) オーバーサンプリングコンバータであり、それはオーディオ用の集積されたコンバータにおいて最も一般的になっている。

【発明の概要】

【発明が解決しようとする課題】

【0008】

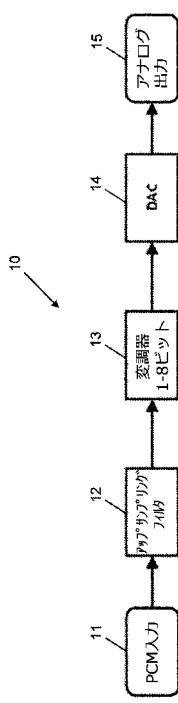

図1は、典型的なオーバーサンプリング集積回路デジタル・アナログコンバータ(DAC)10の内部ブロック図を示す。入力PCMストリーム11は、最初にアップサンプリングフィルタ12によってアップサンプリングされる。次に、変換が高速デルタ・シグマ変調器13で行われ、DAC14に供給して出力アナログ信号15を提供する。

10

【0009】

変調器は、ナローワードの(3~8ビット)アップサンプリングされたPCMストリームに対して、多くの場合3~13MHzの間のレートで動作する。一般に、変調器13は入力データレートの整数倍のレートで動作する。この変調器のアーキテクチャは、シリコン上に実装するのが効率的であるので選択されている。実際の装置では、変調器のアナログ出力は、シングルエンド又は平衡型の電流源又は電圧源であり得る。オーディオ用の入力リニアPCMデータは、32~384kHzの範囲のサンプリングレートを16~32ビットの範囲の精度で一般に使用し得る。

【0010】

図1において、入力PCM信号11のレートを変調器13のレートに適合させる補間アップサンプリングフィルタ構造12が存在することがわかる。実装の効率のために、補間構造は、一連のステップにおいてアップサンプリング処理を行うフィルタの多段式カスケードの形式をとることが多い。この構造においてそのように補間されたサンプリングレートは、整数関係を有してもよいし、有しなくてもよい。

20

【0011】

非常に高い性能を意図する設計にとっては、カスケードされた補間フィルタは制約を呈する。例えば、これらは以下の1つ以上を含み得る。すなわち、カスケードされたフィルタの畳込みインパルス応答の形状、ステップ応答のリップル、エイリアシング誤差、並びに、フィルタ又は変調器段階の不十分なディザリングによる量子化ノイズ及び量子化歪み。これらの理由で、ナイキスト周波数に対して相対的に高周波の成分が存在しない場合でさえ、96, 192, 又は384kHzのようなより高いオーディオサンプリングレートによって、それは補間の段階の数を減少させるのであるが、質のよい音が結果として得られ得る。

30

【0012】

高性能を意図するいくつかのコンバータは、変調器への直接の入力を可能にし、これらの場合は、既に適切にアップサンプリングされ、ディザされ、量子化された信号に依拠するが、これはかなり大きな計算リソースを必要とする。一般的に、経済上の考慮によって、大部分の応用が集積フィルタを使用する結果となる。

【0013】

より高い音質を引き出したい製品設計者は、アップサンプリングフィルタ及び変調器のいくつかの特性を向上させる比較的簡単なステップを取り得る。そのような応用の改良は、過渡現象において前及び/又は後リングを防ぐために、サブナイキスト周波数伝達を零にするようにしたいわゆる「アポディゼーション」フィルタ(apodising filter)をコンバータの前に置くことを含む。このタイプのフィルタは、Craven, P.G., 「高サンプリングレートにおけるアンチエイリアスフィルタ及びシステム過渡応答(Antialias Filters and System Transient Response at High Sample Rates)」, J. Audio Eng. Soc., Vol. 52, No. 3, PP. 216-242 (2004年3月)に記載されている。

40

【0014】

再生回路の性能は、DAC、そのアナログ及びデジタルフィルタを、アップサンプリング段階のいくつか又は全てが三角又はBスプラインカーネルに基づいて単純な段階のカス

50

ケードにおいて行われ得る階層的な機構に組み入れることによっても、改善され得る。このアプローチは、Stuart, J.R., Craven, P.G., 「アーカイブ及び分配への階層的アプローチ (A Hierarchical Approach to Archiving and Distribution)」, 137th AES Convention, Los Angeles (2014年10月) に記載されている。例えば、そのようなカスケードは、Pohl, V., Yang, F., Boche, H., 「整合性のある信号復元のための原因復元カーネル」, EUSIPCO, Bucharest, pp. 174-1178 (2012年) に記載されているように、信号を 192 kHz から 384 kHz へアップサンプリングするフィルタのために単純な三角カーネルを使用し得る。

#### 【0015】

Bスプライン及び/又は三角カーネルの階層に基づいてシステムを実現することの1つの制約は、利用可能な集積デバイスが 96 又は 192 kHz のような入力データレートに限定され得るので、Stuart, J.R. and Craven, P.G. によって「アーカイブ及び分配への階層的アプローチ (A Hierarchical Approach to Archiving and Distribution)」, 137th AES Convention, Los Angeles (2014年10月) において述べられているように、それによって回路の長さが限定されるということである。

#### 【0016】

高品質の音を得ようとする応用は、集積コンバータにおける量子化誤差の主観的効果を隠すために、最下位ビット (LSB) よりいくらか高いレベルで、ディザを使用する、又は入力信号に低レベルの相関性のないノイズを加えることもし得る。そのようなノイズ信号は、その可聴性を最小限にするためにスペクトルが整形され得る。

#### 【0017】

ノイズ整形 (noise shaping) 及びディザの使用のいくつかの例が、Widrow, B., Kollar, I., 「量子化ノイズ：デジタル計算、信号処理、制御及び通信における丸め誤差 (Quantization Noise: Roundoff Error in Digital Computation, Signal Processing, Control, and Communications)」, CUP, Cambridge, UK, ISBN: 0521886716 (2008年)、及びGerzon, M.A., Craven, P.G., Stuart, J.R., and Wilson, R.J., 「CD 及び他の線形デジタルメディアにおける心理音響学的なノイズ整形がされた改善 (Psychoacoustic Noise Shaped Improvements in CD and Other Linear Digital Media)」, AES 94th Convention, Berlin, preprint 3501 (1993年3月)、最後にStuart, J.R., and Wilson, R.J., 「44.1、48、及び 96 kHz でのノイズ整形されたディザを使用したダイナミックレンジ向上 (Dynamic Range Enhancement using Noise-Shaped Dither at 44.1, 48 and 96 kHz)」, AES 100th Convention, Copenhagen (1996年) に記載されている。

#### 【0018】

集積回路 DAC における他の性能制約には、アナログ段階で生じる熱雑音及び非線形性が含まれる。信号雑音比は、出力がアナログ領域で合計される 2 個の同様に駆動される DAC を使用することによって (いわゆる「モノラルモード」)、3 dB まで改善され得る。更に洗練すると、反対の関係になる 2 個のコンバータへの入力信号、及び減算が行われるアナログ信号を用意することによって、偶数次の非線形歪みが部分的な相殺によって低減され得る。

#### 【0019】

しかし、上述の進展にもかかわらず、改良されたデジタル・アナログコンバータ装置への要求が残り、それはより普通の DAC 装置において一般化している問題を扱う。これは、高品質の音を必要とする応用に特に当てはまる。

#### 【課題を解決するための手段】

#### 【0020】

本発明の第 1 の局面によると、

データサンプリングレート  $F_s$  及びサンプリング周期  $1/F_s$  を有するデジタル信号を受信する入力部と、

前記デジタル信号を受信する前記入力部に結合された  $N$  個 ( $N$  は偶数の整数であり、 $N \geq 2$ ) のデジタル・アナログコンバータ (DAC) と、

10

20

30

40

50

前記入力部及び前記 N 個の D A C のうちの半分に結合されたインバータであって、それによって、前記 N 個の D A C のうちの前記半分によって受信される入力デジタル信号が前記 N 個の D A C のうちの他方の半分によって受信される前記入力デジタル信号に対して反転される、インバータと、

前記入力部に結合され、前記 N 個の D A C のうちの 1 つ以上によって受信される前記入力デジタル信号と前記 N 個の D A C のうちの他のものによって受信される前記入力デジタル信号との間に相対的な時間遅延を導入する、前記相対的な時間遅延が前記デジタル信号のサンプリング周期  $1 / F_s$  の部分である、遅延ユニットと、

前記 N 個の D A C に結合され、前記 N 個の D A C のうちの前記半分のアナログ出力を、前記 N 個の D A C のうちの前記他方の半分のアナログ出力と減算されるように合成して、出力アナログ信号を提供する合成器と、

10

を備える D A C 装置が提供される。

#### 【0021】

このように、装置全体の性能が、多数の D A C 装置のアナログ出力を合成することによって向上され得る。個々のコンバータは、同じデータに対して動作するが、他のコンバータの少なくともいくつかに対して、データサンプリング周期の部分であって零ではない特定の時間オフセットを有する。N 個の D A C への同じデジタル信号の相対的に遅延した入力は、それらからアナログ信号が復元される復元点の数を効果的に増加させるという点で有益である。更に、コンバータの半分に供給されるデータ信号は、コンバータの他方の半分に供給されるデータ信号とは反転した関係にあり、それらのアナログ信号は減算され、それによってアナログ非線形歪みが相殺によって低減され得る。

20

#### 【0022】

本装置は、ディスクリートの D A C を採用してもよいし、そうでなければ单一の集積回路装置であってもよい。同様に、本装置は、応用に従って、フラッシュ又はオーバーサンプリング D A C を使用して実現されてもよい。

#### 【0023】

好ましくは、N 個の D A C は実質的に互いに同じであり、それによって D A C から整合した応答を提供し、それらの出力を所望のやり方で合成することをより容易にする。

#### 【0024】

いくつかの実施形態において、それぞれの D A C によって受信される入力デジタル信号間の相対的な時間遅延は、装置に所定のインパルス応答を提供するように選ばれ得る。このように、D A C 装置は特定の所望のインパルス応答を提供するように構成され得る。

30

#### 【0025】

いくつかの好ましい実施形態において、前記 N 個の D A C のうちの前記半分によって受信される前記入力デジタル信号と前記 N 個の D A C のうちの前記他方の半分によって受信される前記入力デジタル信号との間の相対的な時間遅延は、 $1 / (2 \times F_s)$  である。このように、D A C のうちの半分は、D A C のうちの他方の半分に対して、入力信号のサンプリング周期の半分、遅延しており、それによって復元点の数を効果的に 2 倍にする。

#### 【0026】

他の好ましい実施形態において、前記 N 個の D A C のうちの前記半分のそれぞれによって受信される前記入力デジタル信号間の前記相対的な時間遅延は、異なっており、前記 N 個の D A C のうちの前記他方の半分における対応する D A C によって受信される前記入力デジタル信号に対して  $1 / (2 \times F_s)$  遅れている。

40

#### 【0027】

他の好ましい実施形態において、前記 N 個の D A C のうちの前記半分によって受信される前記入力デジタル信号と前記 N 個の D A C のうちの前記他方の半分によって受信される前記入力デジタル信号との間の前記相対的な時間遅延は、 $1 / (N \times F_s)$  である。このように、D A C のうちの半分は、D A C のうちの他方の半分に対して、入力信号のサンプリング周期の  $1 / N$ 、遅延する。

#### 【0028】

10

20

30

40

50

他の好ましい実施形態において、前記N個のD A Cのうちの前記半分のそれぞれによって受信される前記入力デジタル信号間の前記相対的な時間遅延は、異なっており、前記N個のD A Cのうちの前記他方の半分における対応するD A Cによって受信される前記入力デジタル信号に対して $1/(N \times F_s)$ 遅れている。

【0029】

いくつかの実施形態において、少なくとも1つのD A Cには、前記入力デジタル信号からの同じ時間遅延を有する他のD A Cが存在しない。

【0030】

更に、遅延したD A Cは、同じ信号位相で動作する必要はない。D A Cの早い方の対と遅い方の対とが差動的に動作して高周波ノイズをより相殺することは、有利なことであり得るからである。

10

【0031】

いくつかの更に好ましい実施形態において、D A C装置は前記入力部及び前記N個のD A Cに結合されたディザユニットを更に備え、前記ディザユニットは、前記N個のD A Cのそれぞれによって受信される前記入力デジタル信号にコモンモードで加えるためのランダムなディザ信号を生成する。この振幅ディザ信号はアナログ領域において相殺しがちであるが、それが各D A Cに存在することは、線形性を向上させ、全体的な結果に導入される変調ノイズ誤差を低減させる。

【0032】

いくつかの実施形態において、前記ディザ信号は、整形されたディザ信号である。典型的には前記ディザ信号は2個以上の最下位ビット(L S B)を含む。

20

【0033】

いくつかの実施形態において、前記ディザ信号は、前記入力デジタル信号のサンプリングレートより高いレートで生成される。前記ディザ信号は、より低いレートのディザシーケンスをアップサンプリングすることによって生成され得る。これは、より高いレートで直接生成するより計算的には効率がよい。更に、前記ディザ信号は、前記出力アナログ信号の復元レートで生成され得て、ディザノイズのアナログ相殺が相対的な時間オフセットによって減少させられないように、各D A Cの組に連続して供給される。

【0034】

他の実施形態において、前記入力デジタル信号は、より高い周波数においてより少ないエネルギーを含むように、ノイズ整形されており、それは遅延した差分の計算に起因する高周波相殺の損失を改善し得る。

30

【0035】

よって、本発明は、出力ノイズフロアを過度に不利にすることなく、線形性が最適化されるように、ディザが使用されることを可能にする。本発明は、これらのディザ信号が高レートストリームから導き出されること、又は高周波においてアナログ相殺を最大化する遅延方法を使用することも、可能にする。

【0036】

D A C装置のいくつかの実施形態において、前記合成器は、前記N個のD A Cのそれぞれのアナログ出力を、適用される重み付けをして合成し、それは、各アナログ出力について同じであり得る。代替として、前記適用される重み付けは、前記N個のD A Cのうちの少なくとも2個について異なり得る。いくつかの好ましい実施形態において、前記適用される重み付けは、各D A Cによって受信される前記入力デジタル信号の相対的な時間遅延に依存し、前記装置の周波数応答を修正する。

40

【0037】

本発明のD A C装置はさまざまなデータを伝達する広い範囲のデジタル信号とともに使用され得るが、デジタルオーディオ信号を含むデジタル信号に特に適用でき、それはパルス符号変調(P C M)信号であり得る。前記装置は、高品質オーディオを含む応用によく適している。デジタル・アナログ変換に関連することが多いノイズ又は信号歪みが非常に軽減されるからである。

50

## 【0038】

本発明の第2の局面によると、デジタル信号をアナログ信号に変換する方法が提供される。この方法は、

データサンプリングレート  $F_s$  及びサンプリング周期  $1/F_s$  を有するデジタル信号を受信するステップと、

前記デジタル信号を  $N$  個 ( $N$  は偶数の整数であり、 $N \geq 2$ ) のデジタル・アナログコンバータ (DAC) に、前記  $N$  個の DAC のうちの半分によって受信される入力デジタル信号が前記  $N$  個の DAC のうちの他方の半分によって受信される前記入力デジタル信号に対して反転されるように、かつ、前記  $N$  個の DAC のうちの 1 つ以上によって受信される前記入力デジタル信号と前記  $N$  個の DAC のうちの他のものによって受信される前記入力デジタル信号との間に相対的な時間遅延が存在するように、供給する、 $N$  が整数かつ  $N \geq 2$  であり、前記相対的な時間遅延が前記デジタル信号のサンプリング周期  $1/F_s$  の部分である、ステップと、

前記  $N$  個の DAC のうちの前記半分のアナログ出力を、前記  $N$  個の DAC のうちの前記他方の半分のアナログ出力と減算されるように合成して、前記出力アナログ信号を提供するステップと、

を有する。

## 【0039】

種々の実施形態において、第2の局面の方法は、追加された方法ステップの観点からいえば、本発明の第1の局面の装置の実施形態の多くを反映し得る。

## 【0040】

当業者によって理解されるように、本発明は新しいタイプのデジタル・アナログ変換装置を提供し、その厳密な実現は個々の設計及び応用に従って改変され得る。更なる変形及び修飾が、当業者にはこの開示に鑑みて明らかとなろう。

## 【図面の簡単な説明】

## 【0041】

本発明の例が、添付の図面を参照してここに詳細に説明される。

【図1】図1は、典型的なオーバーサンプリング集積回路DACにおける内部機能のブロック図を示す。

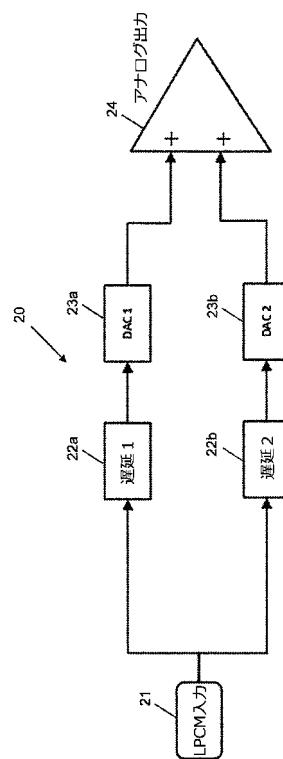

【図2】図2は、共通の入力に対して動作している2個のDACが相対的に遅延しており、それらの出力が加算されるように合成される、装置のブロック図を示す。

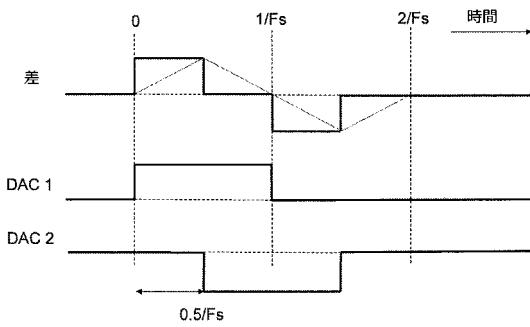

【図3】図3は、図2に示された構成のインパルス応答を示す。

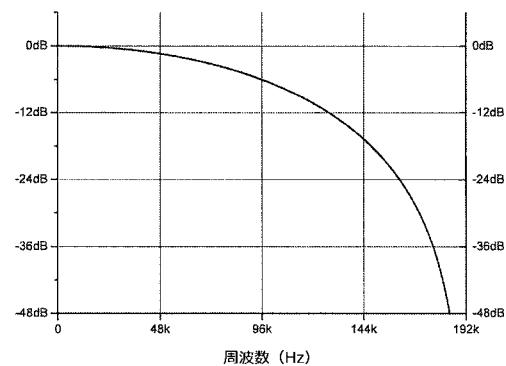

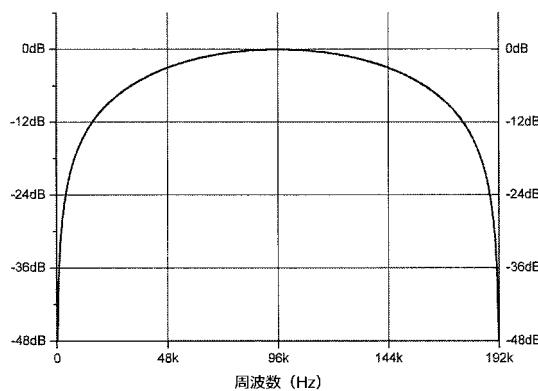

【図4】図4は、入力サンプリングレートが192kHzであるときの、図3に示されたアナログ出力の畳込み周波数応答を示す。

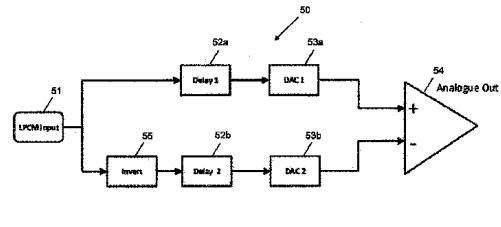

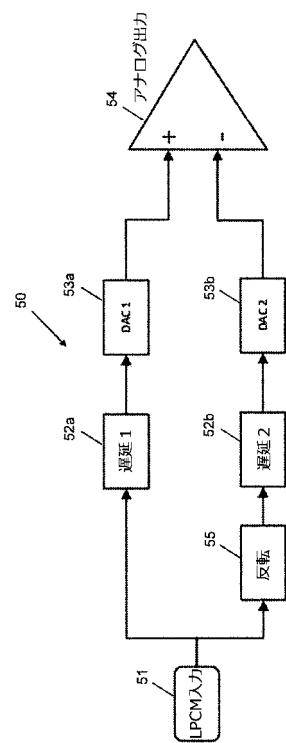

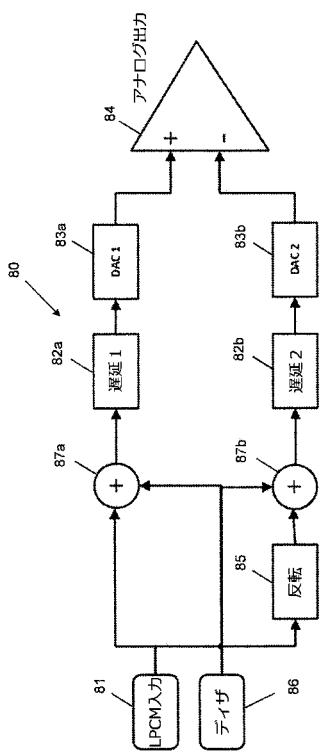

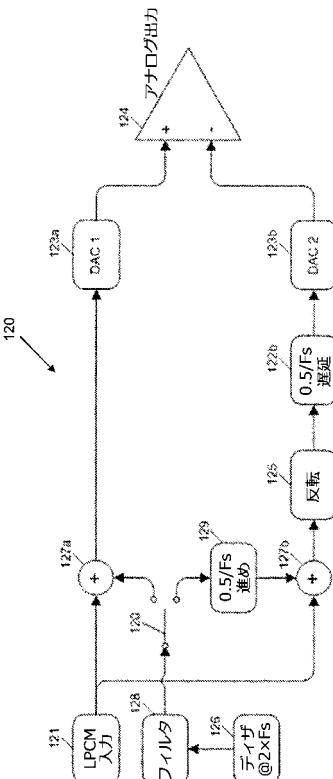

【図5】図5は、2個のDACが、共通の入力に対して動作し、相対的に遅延し、それらの出力が減算されるように合成される、本発明の実施形態を示す。

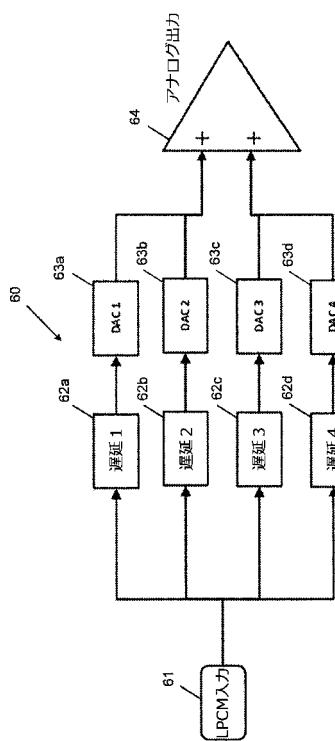

【図6】図6は、共通の入力に対して動作する4個のDACが相対的に遅延させられ、それらの出力が加算されるように合成される装置のブロック図を示す。

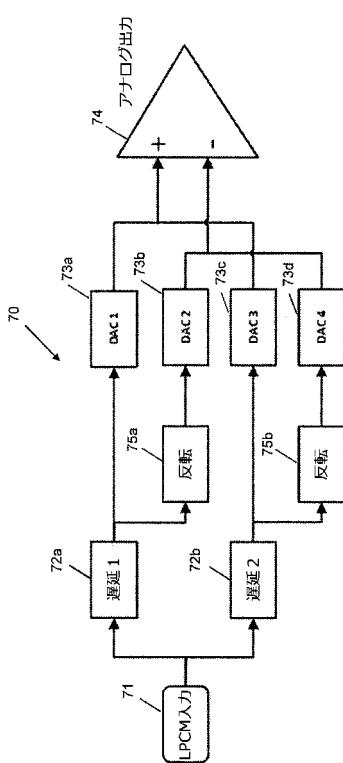

【図7】図7は、DACの2個の対が、対の間で異なる時間遅延を有して差動的に組み合わされる装置を示す。

【図8】図8は、図5の実施形態に類似する本発明の実施形態を示すが、これにおいてはコモンモードディザ信号が各DAC用のデータ信号に遅延の前に加えられる。

【図9】図9は、図8に示されたタイプの構成におけるディザ信号の観点から、インパルス応答を示す。

【図10】図10は、入力サンプルレートが192kHzであるときの図8に示された構成におけるディザ信号について、アナログ周波数応答を示す。

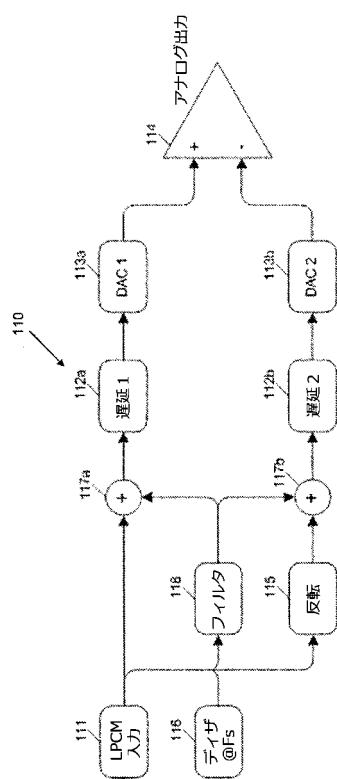

【図11】図11は、図8の実施形態に類似する本発明の他の実施形態を示すが、これにおいてはディザ信号がフィルタによって整形される。

【図12】図12は、ディザを使用する本発明の他の実施形態を示し、それにおいて、濾波された高レートディザストリームが各DACで交互に使用され、所与の出力ノイズスペ

クトラムによりよい D A C 線形化が行われる。

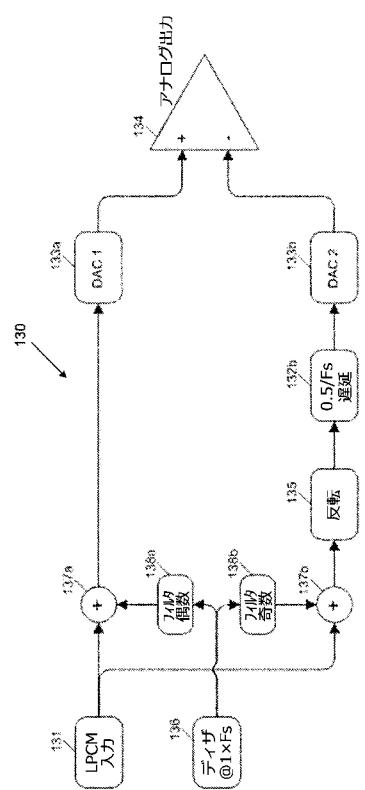

【図 1 3】図 1 3 は、高レートディザを使用する本発明の他の実施形態を示し、それにおいて、入力 P C M サンプリングレートでサンプルされた単一のディザ源が D A C の各相に異なるフィルタを通して供給される。

【発明を実施するための形態】

【0 0 4 2】

説明されるように、本発明は、新規な複合デジタル・アナログコンバータ ( D A C ) 装置を提供し、それにおいては、2 個以上の D A C が、変換されるデジタル信号のサンプリング周期の部分であって零ではない相対的な時間遅延を有するさまざまな構成で組み合わせられる。遅延は、単一の遅延ユニット又は複数の遅延ユニットによって実現され得る。典型的には、データストリーム及びクレームが、所与の D A C について共に遅延させられる。

【0 0 4 3】

D A C 装置は、フラッシュ D A C 又は図 1 に示されているタイプのオーバーサンプリング集積回路 D A C を含む、さまざまなアーキテクチャで実現され得る。複数のそのような D A C が、適切な時間遅延を有するアレイで、又はそのような集積回路 D A C において、組み合わせられ得る。

【0 0 4 4】

図 2 は、2 個の類似する D A C 2 3 a 及び 2 3 b が、それらのアナログ出力が加算されるように合成 2 4 されて最終的なアナログ出力信号を発生させるように、単一の変換システムにおいて組み合わされる。両方の D A C が、単一の入力データストリーム 2 1 に対して F s レートで、時間 1 / F s 間隔のサンプルを用いて動作する。しかし、各 D A C への信号は、異なる量だけ遅延している。示されているように、入力データストリームは、リニアパルス符号変調 ( L P C M ) 信号であり得る。

【0 0 4 5】

いくつかの実装において、遅延 1 2 2 a は、零であり得るのに対して、遅延 2 2 2 b は 1 / ( 2 × F s ) であり得る。この場合、( 遅延 2 - 遅延 1 ) = 1 / ( 2 × F s ) に等しい相対的な遅延、すなわち遅延の差が存在し、1 つの D A C 用のデータ及びクロックは、他方の D A C に対してサンプリング周期の半分、遅延しており、それによって復元点 ( reconstruction point ) の数を効果的に 2 倍にする。

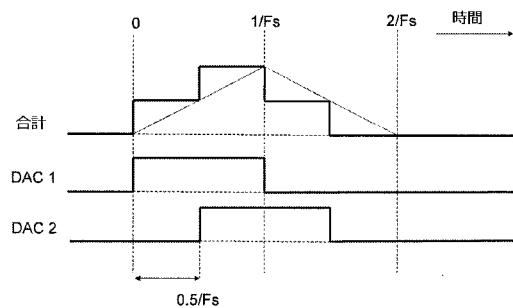

【0 0 4 6】

図 3 に示されているように、2 個の D A C はレート F s で単位インパルス入力信号である入力信号に対して動作する。D A C 1 2 3 a がサンプル点において変換するのに対して、D A C 2 2 3 b はサンプリング周期の半分、遅れる。もし各コンバータが等しく重み付けされていれば、それらの固有応答 ( natural response ) は時間間隔 1 / ( 2 × F s ) を有するダブルインパルスで畳み込まれ、その結果、復元レート ( reconstruction rate ) が効果的に 2 倍になる。合計された出力が図 3 の上方の曲線に示されている。この出力がアナログローパスフィルタに供給されると、図 3 の上方の曲線に点線で示されているように、三角の出力が結果として生じる。

【0 0 4 7】

よって、この組合せの効果は、中間の復元補間点を提供することであり、結果として生じるアナログ応答は、図 3 に示されているように、F s における 2 サンプルの幅の三角形の形状の関数に類似するインパルス応答を有するシステムに類似する。そうでなければ、この補間された応答は、F s レートの 2 倍で動作する単一の D A C 、及びデジタル領域において三角形の形状の関数で畳み込まれたデータストリームによって獲得され得るのみである。

【0 0 4 8】

結果として、2 個の D A C の組合せに例えれば 1 9 2 k H z でデータが供給されると、結果として得られるアナログ応答は、図 4 に示されているが、2 0 k H z における小さな 0 . 1 2 d B の応答低下がアナログポストフィルタにおいて簡単に補正され得る一方、有利

10

20

30

40

50

なことに零点を 192 kHz に有する。

【0049】

図5は、2個の類似するD A C 53a及び53bが、それらのアナログ出力が減算されるように合成54されて最終的なアナログ出力信号を発生させるように、単一の変換システム50に組み合わされる、本発明の実施形態を示す。両方のD A Cは、F s レートで单一の入力データストリームに対して動作する。しかし、D A C 2 53bへの信号はインバータ55によって反転され、各D A Cは異なる量だけ遅延している。いくつかの実装において、遅延2 52bは $1 / (2 \times F s)$ であり得るのに対して、遅延1 52aは零であり得る。この場合、1つのD A C用のデータ及びクロックは、他方のD A Cに対してサンプリング周期の半分、遅延している。

10

【0050】

この実施形態の時間及び周波数応答は、図2の示されている装置と同じであるが、差分モードの結果としての相殺によって、アナログ非線形歪みが低減され得る。

【0051】

図2に示されている装置の代替としての装置においては、いかなる数のD A Cも、それらのアナログ出力が適切に合成されるように、単一の変換システムに組み合わされ得る。D A CはF s レートで单一の入力データストリームに対して動作するが、D A C用のデータ及びクロックは、入力サンプリング周期の異なる部分だけ遅延しており、それによって、復元点の数にD A Cの数を効果的に乗算する。よって、N個のD A Cは、それぞれが $1 / (N \times F s)$ だけ時間が離れたサンプリング時点において動作するように、組み合わせられ得る。これらの場合において、アナログ合成は、D A Cのそれぞれについて、それらの相対的な遅延に従って異なる重み付けを使用し得る。例えば、D A Cのいくつかは、周波数応答を鋭くするために出力信号を低減し得る。

20

【0052】

図6は、コンバータ装置60全体において4個のD A C 63a～63dが組み合わされているような、装置を示す。4個のD A Cは、単一の入力データストリーム61に対してそれぞれの遅延62a～62dに従って動作する。4個の63a～63dのアナログ出力は、加算されるように合成されて最終的なアナログ出力を発生させる。

【0053】

よって、本発明のいくつかの実施形態においては、D A Cの複数の対が用いられる。具体的には、もしN個のD A CがN/2個の対に組み合わされると、N/2個のD A Cには反転した信号が供給され、それらのアナログ出力は、反転していない信号が供給されている他のN/2個のD A Cの出力と、減算されるように合成される。この実施形態において、D A Cのうちの半分は、他のものに対して入力サンプリングレートの周期の半分、遅延もされ得るが、それによって復元点の数を効果的に2倍にする。遅延したD A Cは、同じ信号位相で動作する必要はないということが、更に注目される。例として、4個のD A Cが使用され、2個のD A Cが他の2個からサンプルの半分遅れて動作する。早い対と遅い対とが差動的に動作して高周波ノイズをより多く相殺することは、有利なことであり得る。

30

【0054】

図7は、コンバータ装置70全体において4個のD A C 73a～73dが組み合わされている装置を示す。4個のD A Cは、単一の入力データストリーム71に対してF s レートで動作する。しかし、D A C 1 73a及びD A C 2 73bへの信号は、D A C 3 73c及びD A C 4 73dへの信号が遅延させられる遅延量72bとは異なる遅延量72aだけ遅延させられている。更に、D A C 2 73b及びD A C 4 73dへの遅延した信号は、インバータ75a及び75bによって反転されている。D A C 1 73a及びD A C 3 73cからのアナログ出力は、D A C 2 73b及びD A C 4 73dからのアナログ出力と、減算するように合成74され、最終的なアナログ出力信号を発生させる。

40

【0055】

本発明の他の実施形態においては、D A Cの2以上の対が差動的に組み合わされ、2個

50

以上の最下位ビット (LSB) のコモンモードの整形された又は整形されていないランダムなディザ信号が、各減算対に供給されるデータに加えられ得る。この信号がアナログ領域において相殺することが期待されるが、各DACにそれが存在することは、線形性を向上させ、全体的な結果に導入される変調ノイズ誤差を低減させ得る。

【0056】

図8は、2個の類似するDAC83a及び83bが、それらのアナログ出力が減算されるように合成84されて最終的なアナログ出力信号を発生させるように、コンバータ装置80全体において結合されているような、実施形態を示す。両方のDACは、Fsレートで単一の入力データストリーム81に対して動作する。しかし、DAC2 83bへの信号は、インバータ85によって反転され、時間遅延82bによって遅延させられており、時間遅延82bは、DAC1 83aへの信号に適用される時間遅延82aとは異なる。いくつかの実施形態において、遅延2 82bは $1/(2 \times Fs)$ であり得るのに対して、遅延1 82aは零であり得る。この場合、1つのDAC用のデータ及びクロックは、他方のDACに対してサンプリング周期の半分、遅延している。更に、振幅ディザ信号86が、87a及び87bにおいて、遅延の前に各データ信号に加えられる。

10

【0057】

図8は、DACが差動的に組み合わされるときに、ディザ信号が、出力へのその影響が低周波におけるアナログ減算によって低減されるようにして、示されているように加えられ得る、ということを示している。この構成の有利な点は、遅延ユニットに供給される信号が時間的に同等である(co-temporal)ということである。

20

【0058】

図9は、図8に示されている構成におけるディザ信号の観点からのインパルス応答を示しており、遅延差(遅延2 - 遅延1) =  $1/(2 \times Fs)$ 、すなわち、サンプリング周期の半分である。差信号が、点線で示されている結果として得られるアナログ信号とともに、上方の曲線で示されている。

【0059】

図10は、図8に示されている構成におけるディザ信号について、入力サンプリングレートが192kHzである場合の、アナログ周波数応答を示す。周波数領域における相殺の程度が明らかである。

30

【0060】

この実施形態の改良において、含まれる高周波エネルギーがより小さくなり、よって遅延した差の導出に起因する高周波における相殺の損失が改善されるように、Fsレートのストリームが整形され得る。図11は、そのような装置110を示す。再び、2個の類似するDAC113a及び113bが、それらのアナログ出力が減算するように合成114されて最終的なアナログ出力信号を発生させるように、組み合わせられる。両方のDACが、Fsレートで単一の入力データストリーム111に対して動作し、DAC2 113bへの信号はインバータ115によって反転され、次に時間遅延112bによって遅延させられ、時間遅延112bはDAC1 113aへの信号に適用される時間遅延112aとは異なる。しかし、この実施形態においては、Fsでのディザ116は、フィルタ118によって整形される。

40

【0061】

図12は、 $2 \times Fs$ での高レートディザ126がフィルタ128によって整形される、この実施形態の代替としての改良120を示す。濾波されたディザは $2 \times Fs$ で生成されており、スイッチ120は、偶数番目のサンプルをDAC1 123aに向けて、奇数番目のサンプルをDAC2 123bに向けて送る。進め動作129は、奇数番目のサンプル値を偶数番目のサンプルの時点に適用して、LPCM入力121のサンプルの時点に一致させることに対応する。半サンプル遅延動作122bは、DAC1 123aに対して反対のクロック位相で制御されているDAC2 123bに対応する。DAC2 123bへの入力は、インバータ125によって反転され、2個のDACのアナログ出力は減算されるように合成されて最終的なアナログ出力信号を発生させる。

50

## 【0062】

一般的に、この実施形態は、入力デジタル信号（高レートディザ）のサンプルレートより高いレートで、典型的には出力アナログ信号の復元レートで生成されたディザストリームを特徴とし、ディザストリームからのサンプルは、各相において交互に、D A Cに順次分配される。フィルタ128（その設計については以下で述べられる）は、各D A C位相に供給されるサブストリーム間の関係であって、アナログ出力の残留ノイズを許容限度に適合させながら、サブストリームにD A Cの線形性を向上させるために多くのノイズを含ませる関係を確立する。

## 【0063】

濾波されたディザの奇数番目のサンプルを考えると、時間進みと遅延動作とは相殺し、反転125とアナログ平衡不平衡変換124の反転入力とも、相殺する。よって、もし両方のD A Cが同じであれば、偶数番目のサンプルと奇数番目のサンプルとの両方に同じ処理が起こり、濾波されたディザがアナログ出力においてD A Cインパルス応答によって畳み込まれて現れ、それにもかかわらず、それはどちらのD A Cもが受け入れ可能なものより高いサンプルレートを有する。0.5 F sより下では、D A Cの周波数応答は重要ではなく、フィルタの設計の主な制約は、アナログ出力における許容可能なノイズのレベルである。

10

## 【0064】

0.5 F sより上では、オーバーサンプリングD A Cは阻止帯域を有する。ノイズはD A Cの線形化に有益な影響を及ぼすが、アナログ出力の前にD A Cの阻止帯域によって減衰するので、好ましくは、フィルタはこの領域において余分なノイズを有することができるように設計される。フラッシュD A Cは、F sにおいて単一の零に向かってよりゆるやかな低下を有し、それは、小さいがこの領域において余分な有益なノイズを有する有用な能力を与える。

20

## 【0065】

好ましくは、D A C不整合の可能性についても考慮する。不整合のD A Cの影響は、ノイズスペクトラムを約0.5 F s反転させることである。よって、フィルタの設計は、周波数F s - fにおけるノイズレベルを、周波数fにおけるものと比べて好ましくは制限すべきである。例えば、1%まで整合した192 kHz D A Cでは、フィルタ設計は、182 kHzにおけるノイズレベルが10 kHzにおけるノイズレベルを40 dBより多く越えないことを確実にするべきである。

30

## 【0066】

この実施形態において高レートディザを使用する利点は、アナログ出力における許容可能なノイズのあるレベルについて、より多くのノイズを各D A Cに与えることができ、それぞれがその不都合な点のよりよい線形化を達成するということである。

## 【0067】

図13は、この実施形態の更なる発展130を示し、それにおいては、ディザ136が最初に $1 \times F_s$ で生成される。これは次に、フィルタ138aを通ってD A C1 133aに適用するために渡され、フィルタ138bを通ってD A C2 133bに適用するために渡される。D A C2 133bへの入力は、インバータ135によって反転され、時間遅延132bによって遅延させられる。2個のD A Cのアナログ出力は、減算するようになし合せられ、最終的なアナログ出力信号を発生させる。

40

## 【0068】

この動作は実際には図12における動作に等しく、 $2 \times F_s$ ディザジェネレータ126は、 $1 \times$ ディザジェネレータ136をアップサンプリングし、サンプル値間に零を挿入することによって動作する。フィルタ138aはフィルタ128のインパルス応答の偶数番目のタップを含み、フィルタ138bは奇数番目のタップを含む。根源的な密接な関係にもかかわらず、装置が全く異なっているように見えるので、それは別個の図として示されている。それにもかかわらず、それは上述の高レートディザの説明に適合する。

## 【0069】

50

よってフィルタ 138a 及び 138b の設計は、概要が上述された、フィルタ 128 を設計する方法によって行われることができ、結果として得られたフィルタを偶数及び奇数係数に分割する。

【0070】

このアーキテクチャは、フィルタ 138a 及び 138b を、同じ周波数応答を有するが周波数範囲にわたって群遅延が  $0.5 / F_s$  異なるように設計するような、代替の設計方法を提案する。これは、フィルタ 128 をその範囲にわたって零応答を有するように設計することと同等である。

【0071】

要約すると、本発明は、特定の応用に従って多くのさまざまな構成で実施され得る新しいタイプのデジタル・アナログコンバータ装置を提供する。一般性を失うことなく、上述の実施形態の教示は任意の複雑なシステムに組み合わされ得る。更に、当業者によって理解されるように、本発明のさまざまな変更が、上述の教示に基づいて可能である。

10

【図 1】

【図 2】

【図3】

【図5】

【図4】

【図7】

【図6】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/GB2016/051534

A. CLASSIFICATION OF SUBJECT MATTER

INV. H03M1/66

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H03M

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data, COMPENDEX, INSPEC, IBM-TDB

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                    | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2012/194373 A1 (STEINBACH GUNTER [US])<br>2 August 2012 (2012-08-02)<br>paragraphs [0004], [0026], [0029];<br>figures 5,6<br>----- | 1-21                  |

| X         | JP H03 62733 A (KENWOOD CORP)<br>18 March 1991 (1991-03-18)<br>abstract<br>figures 5,6<br>-----                                       | 1-21                  |

| A         | US 2005/225464 A1 (LIN HENG-CHIH [US] ET AL)<br>13 October 2005 (2005-10-13)<br>figures 3b,3c<br>-----                                | 1-6                   |

| A         | US 9 007 250 B1 (JERAJ JANEZ [US] ET AL)<br>14 April 2015 (2015-04-14)<br>figures 4b,5<br>-----                                       | 1-6                   |

|           |                                                                                                                                       | -/-                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier application or patent but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

\*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

\*&\* document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

11 August 2016

22/08/2016

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Galardi, Leonardo

## INTERNATIONAL SEARCH REPORT

|                              |

|------------------------------|

| International application No |

| PCT/GB2016/051534            |

| C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                    |                       |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------|

| Category*                                            | Citation of document, with indication, where appropriate, of the relevant passages                 | Relevant to claim No. |

| A                                                    | US 4 864 305 A (TOYAMA AKIRA [JP])<br>5 September 1989 (1989-09-05)<br>abstract; figure 4<br>----- | 7-14                  |

| A                                                    | EP 0 369 630 A2 (SONY CORP [JP])<br>23 May 1990 (1990-05-23)<br>abstract; figure 4<br>-----        | 7-14                  |

| A                                                    | GB 2 250 148 A (SONY CORP [JP])<br>27 May 1992 (1992-05-27)<br>abstract; figure 2<br>-----         | 7-18                  |

| A                                                    | US 2010/097253 A1 (MU FENGHAO [SE])<br>22 April 2010 (2010-04-22)<br>abstract; figure 9<br>-----   | 15-18                 |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/GB2016/051534

| Patent document cited in search report |    | Publication date | Patent family member(s) |            | Publication date |

|----------------------------------------|----|------------------|-------------------------|------------|------------------|

| US 2012194373                          | A1 | 02-08-2012       | NONE                    |            |                  |

| JP H0362733                            | A  | 18-03-1991       | JP 2602331 B2           | 23-04-1997 |                  |

|                                        |    |                  | JP H0362733 A           | 18-03-1991 |                  |

| US 2005225464                          | A1 | 13-10-2005       | NONE                    |            |                  |

| US 9007250                             | B1 | 14-04-2015       | NONE                    |            |                  |

| US 4864305                             | A  | 05-09-1989       | JP S63224521 A          | 19-09-1988 |                  |

|                                        |    |                  | US 4864305 A            | 05-09-1989 |                  |

| EP 0369630                             | A2 | 23-05-1990       | DE 68920005 D1          | 26-01-1995 |                  |

|                                        |    |                  | DE 68920005 T2          | 27-04-1995 |                  |

|                                        |    |                  | EP 0369630 A2           | 23-05-1990 |                  |

|                                        |    |                  | JP H02134010 A          | 23-05-1990 |                  |

|                                        |    |                  | US 5073778 A            | 17-12-1991 |                  |

| GB 2250148                             | A  | 27-05-1992       | GB 2250148 A            | 27-05-1992 |                  |

|                                        |    |                  | JP H04261222 A          | 17-09-1992 |                  |

|                                        |    |                  | US 5148163 A            | 15-09-1992 |                  |

| US 2010097253                          | A1 | 22-04-2010       | EP 2342827 A1           | 13-07-2011 |                  |

|                                        |    |                  | ES 2391810 T3           | 30-11-2012 |                  |

|                                        |    |                  | US 2010097253 A1        | 22-04-2010 |                  |

|                                        |    |                  | WO 2010046228 A1        | 29-04-2010 |                  |

---

## フロントページの続き

(81)指定国 AP(BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), EA(AM, AZ, BY, KG, KZ, RU, T

J, TM), EP(AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, R

O, RS, SE, SI, SK, SM, TR), OA(BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG), AE, AG, AL, AM, AO, AT, AU, AZ,

BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, H

N, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG

, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ,

UA, UG, US