UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA NUMERO     | 101997900601913 |  |

|--------------------|-----------------|--|

| Data Deposito      | 05/06/1997      |  |

| Data Pubblicazione | 05/12/1998      |  |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| Н       | 04     | N           |        |             |

## Titolo

PERFEZIONAMENTI AI CIRCUITI PER LA STIMA DEL MOVIMENTO IN CODIFICATORI DI SEQUENZE VIDEO NUMERIZZATE.

Descrizione dell'invenzione avente per titolo:

"PERFEZIONAMENTI AI CIRCUITI PER LA STIMA DEL MOVIMENTO IN CODIFICATORI DI SEQUENZE VIDEO NUMERIZZATE"

a nome di CSELT - Centro Studi e Laboratori Telecomunicazioni S.p.A., Via G. Reiss Romoli 274, 10148 Torino (Italia), di nazionalità italiana, e di Ecole Polytechnique Fédérale de Lausanne, ELB-Ecublens, CH-1015 Losanna (Svizzera), di nazionalità elvetica.

Inventori: Fabio BELLIFEMINE, Gianmario BOLLANO, Stephanie DOGIMONT, Marco

GANDINI, Pierangelo GARINO, Martin GUMM, Marco MATTAVELLI,

Frederich MOMBERS, Didier NICOULAZ, Alessandro TORIELLI

Domanda N. T. O 97 A UUU486 Depositata il \$5 GIU. 1997

La presente invenzione si riferisce all'elaborazione di segnali video numerizzati, ed in particolare riguarda un circuito per la stima del movimento nella codifica o compressione di sequenze video numerizzate. Nel seguito si farà riferimento a titolo di esempio non limitativo a sequenze organizzate secondo la normativa internazionale ISO/IEC 13818-2 (nota anche come ISO/MPEG2), ma l'invenzione può applicarsi a qualunque codificatore che utilizza tecniche di predizione temporale con stima del movimento (a livello di blocco di elementi d'immagine) per la riduzione della ridondanza temporale.

La stima del movimento consiste nella ricerca, in una o più immagini di riferimento, del macrobiocco di luminanza (16x16 pixel) corrispondente ad un macrobiocco nell'immagine corrente in corso di codifica e nella generazione di uno o più vettori che rappresentano lo spostamento del macrobiocco nell'immagine corrente rispetto alla posizione dello stesso nell'immagine (nelle immagini) di riferimento,

insieme con una funzione di "costo" che fornisce una indicazione dell'errore di stima. I vettori possono anche indicare uno spostamento nullo. Le informazioni così otteriute possono inoltre essere utilizzate come parametro per valutare una funzione di costo di codifica, per consentire di applicare la strategia di predizione (compresa la rinuncia alla predizione, cioè l'effettuazione di una codifica intra-immagine) che rappresenta il migliore compromesso tra la qualità della codifica e la quantità di informazioni da trasmettere.

Tenendo conto di ciò, specialmente nel caso di codificatori per applicazioni professionali (ad es. per trasmissioni TV numeriche) è stato proposto che la stima del movimento venga svolta in tre passi successivi: il primo passo è l'applicazione di un algoritmo di ricerca più o meno preciso per determinare il vettore candidato (i vettori candidati) per ciascun tipo di predizione possibile per una data struttura di macroblocco; il secondo passo è un raffinamento dei vettori calcolati nel passo precedente e il terzo passo è la selezione della modalità di predizione e fornisce l'effettivo vettore (gli effettivi vettori) di movimento da inserire nella sequenza codificata.

La nostra parallela domanda di brevetto Italiana N. TO 97A000209 illustra un circuito integrato progettato per effettuare la determinazione dell'insieme di vettori candidati oppure il raffinamento dei vettori, possibilmente in unione alla selezione della predizione. Il circuito comprende unità di elaborazione programmabili per eseguire l'algoritmo di ricerca con cui calcolare o raffinare i vettori di movimento candidati e/o eseguire le operazioni necessarie per selezionare la strategia di predizione.

La presente invenzione mira a fornire un'unità di elaborazione (unità operativa) altamente flessibile, basata su un approccio misto hardware-software, in grado di svolgere in maniera efficace le funzioni di cui sopra.

Le caratteristiche dell'invenzione sono meglio definite nelle rivendicazioni che

seguono.

L'invenzione verrà ora illustrata in dettaglio con riferimento ai disegni allegati, in cui:

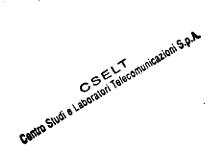

- la fig. 1 è uno schema a blocchi di un circuito di stima del movimento che utilizza un'unità operativa secondo l'invenzione;

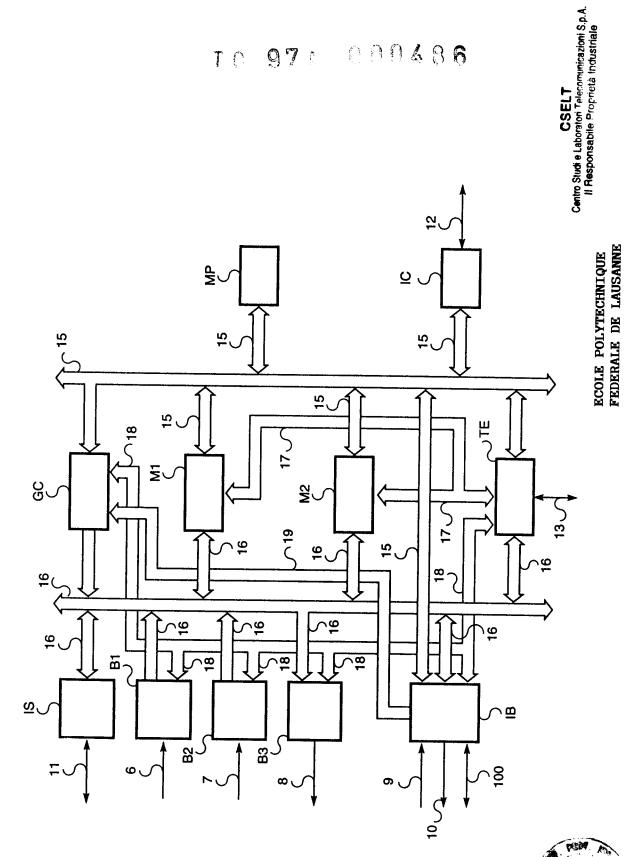

- la fig. 2 è uno schema a blocchi di un'unità operativa;

- le figure 3, 4 sono schemi a blocchi di alcuni circuiti delle unità operative;

- la fig. 5 è uno schema a blocchi dell'unità di controllo per il circuito di fig. 1; e

- le figure da 6 a 8 sono diagrammi del funzionamento dell'unità di controllo.

Facendo riferimento alla fig. 1, viene mostrata l'architettura di un circuito integrato come quello illustrato nel brevetto menzionato in precedenza.

Al circuito sono associate due connessioni di ingresso o bus 6, 7 ed una connessione di uscita o bus 8 per i dati video (il bus 6 convoglia i dati dell'immagine corrente e il bus 7 i dati dell'immagine di riferimento nel caso di raffinamento dei vettori), una connessione di ingresso o bus 9 e una connessione di uscita o bus 10 per le informazioni necessarie per l'elaborazione (d'ora in poi chiamate parametri di elaborazione) e i risultati dell'elaborazione (vettori e costi od errori associati, i termini "costo " ed "errore" essendo utilizzati con lo stesso significato nel corso di tutta la descrizione), una connessione bidirezionale o bus 11 per la connessione ad una memoria esterna (non rappresentata), che memorizza i dati dell'immagine o delle immagini di riferimento e i risultati dell'elaborazione, e una connessione bidirezionale o bus 12 che porta segnali di informazione e di controllo provenienti da un controllore esterno (non rappresentato) o diretti ad esso. I bus 6 - 8 per i dati video e i bus 9, 10 per i parametri di elaborazione e i risultati dell'elaborazione verranno nel seguito chiamati rispettivamente bus delle immagini e bus delle informazioni.

Centro Studi e Laboratori Telecomunicazioni S.p.A.

Ţ

I componenti fondamentali del circuito sono le unità operative (moduli) M1, M2, che, a seconda del caso, eseguono l'algoritmo di ricerca per calcolare i vettori di movimento candidati o raffinare i vettori candidati calcolati da un circuito analogo e/o eseguono le operazioni necessarie per la selezione della strategia di predizione. Nella realizzazione illustrata, vengono utilizzati due moduli M1, M2, ciò che rappresenta un compromesso ragionevole tra le prestazioni da una parte e l'area del circuito e il costo di produzione dall'altra. I moduli M1 e M2 sono basati su di un approccio misto hardware-software, in cui si utilizza un hardware dedicato per il calcolo dei costi dei vettori a partire dalle informazioni dei pixel, ed un processore RISC (reduced instruction set computer = calcolatore con insieme di istruzioni ridotto), che controlla l'hardware dedicato, è programmato per calcolare i vettori di movimento candidati. I moduli contengono memorie interne per memorizzare la finestra di ricerca (che può anche essere posizionata asimmetricamente rispetto al macroblocco corrente) e il macroblocco corrente. I due moduli sono utilizzati per elaborare in modo concorrente e indipendente due macroblocchi diversi, cosicché il circuito di stima del movimento costituisce una struttura MIMD (Multiple Instruction, Multiple Data = istruzioni multiple, dati multipli), nel senso che ogni modulo può comportarsi in maniera diversa (Istruzioni multiple) su pixel differenti (dati multipli).

Nella realizzazione preferita dell'invenzione, per quanto concerne la stima del movimento vera e propria, i moduli eseguono un particolare algoritmo genetico, i principali passi del quale sono riassunti qui di seguito:

Inizializzazione: viene generato un primo insieme di N vettori o cromosomi (popolazione iniziale); l'insieme comprende: un gruppo di vettori (p. es. 9) che sono i vettori associati ad altrettanti macroblocchi circostanti il macroblocco corrente nell'immagine precedentemente ricevuta e rappresentano la correlazione temporale;

il vettore di movimento del macroblocco precedente (considerato in senso spaziale, cioè il macroblocco che è stato codificato appena prima di quello corrente, se i due macroblocchi appartengono alla stessa riga, o il primo macroblocco della riga precedente, all'inizio di una nuova riga), che rappresenta la correlazione spaziale; un gruppo di vettori ulteriori ottenuti aggiungendo vettori casuali ad ognuno dei vettori menzionati precedentemente. La popolazione iniziale può anche comprendere un ulteriore vettore (vettore guida), rappresentativo anch'esso delle correlazioni esistenti nell'immagine o tra immagini, che serve a facilitare il reperimento del macroblocco migliore;

۹

- Valutazione: ciascun vettore viene valutato utilizzando lo scarto medio assoluto come funzione di costo;

- Selezione: i vettori sono ordinati e un sottoinsieme (p. es. i migliori 9 vettori) è memorizzato nel modulo per essere utilizzato per calcolare ulteriori generazioni di vettori (iterazione);

- Iterazione: è svolta ad esempio in tre passi; ad ogni passo, i vettori del sottoinsieme ottenuti alla fine del passo precedente sono combinati p. es. calcolandone la semisomma vettoriale e si ottiene un gruppo di vettori figli (p. es. dieci); la popolazione nella generazione corrente è completata con un altro gruppo di vettori ottenuto aggiungendo un vettore casuale ad ogni vettore figlio; i vettori vengano valutati come prima;

- Conclusione: i migliori vettori per ogni tipo di predizione ed i costi associati vengono memorizzati nella memoria esterna, insieme con il miglior vettore candidato per la predizione riguardante l'intero macroblocco (da utilizzare nell'elaborazione del macroblocco successivo).

Per il raffinamento dei vettori, i moduli M1, M2 possono svolgere una ricerca

OSELT Centro Studi e Laboratsii Telecomunicazioni S.p.A

esaustiva del macroblocco migliore all'interno di un'area di ricerca leggermente più grande di un macroblocco (p. es. 20x20 pixel) estratta da una cosiddetta "zona" (che è un insieme di pixel normalmente più piccolo della finestra di ricerca usata nella stima del movimento), pesando ogni vettore candidato con un peso associato alla quantità di bit richiesti per la trasmissione del vettore stesso.

La struttura dei moduli M1, M2 verrà illustrata con dettagli maggiori con riferimento alla fig. 2.

I moduli M1 e M2 sono connessi a due bus interni 15, 16.

Il bus 15 serve per lo scambio di informazioni con un controllore esterno (non rappresentato) tramite il bus 12 e per lo scambio di informazioni tra i moduli stessi e le altre unità nel circuito. Lo scambio di informazioni con il controllore esterno è gestito da un'interfaccia convenzionale IC che permette al controllore di accedere al circuito per inizializzare i registri di configurazione e caricare i programmi necessari nella fase di avvio, per scrivere i parametri di elaborazione richiesti durante la normale attività, nonché per scopi di monitoraggio.

bus di memoria 11 e convoglia i dati letti dalla memoria esterna o che devono essere scritti nella memoria esterna. Il bus 16 è interfacciato con i bus delle informazioni e delle immagini attraverso un gestore dei bus delle informazioni IB e alle memorie tampone B1 - B3 per la memorizzazione temporanea dei dati video provenienti dai bus delle immagini o che devono essere inoltrati agli stessi e per la conversione del parallelismo dei dati tra il formato utilizzato sui bus delle immagini (per esempio, 8 bit) e sul bus 16 (per esempio, 16 bit). Per chiarezza di descrizione, si supporrà che il trasferimento dei dati sul bus 16 venga controllato da un segnale di orologio a 54 MHz. Nel caso in cui il circuito appartenga ad una configurazione multi-componente in cui il

trasferimento dei risultati intermedi dell'elaborazione da un componente al successivo avviene attraverso una linea dedicata 100, il gestore dei bus delle informazioni IB è anch'esso connesso a detta linea. Una descrizione dettagliata della struttura e delle funzioni del gestore del bus delle informazioni IB è inclusa nella domanda di brevetto TO 97A000209 menzionata in precedenza.

Il trasferimento dei dati sul bus 16 è controllato da un'unità di controllo microprogrammata GC (controllore globale o interno), in cooperazione con un'interfaccia di memoria IS. L'unità di controllo GC, che è anche sensibile a parametri che arrivano al circuito tramite il bus delle informazioni 9 e sono inoltrati a GC tramite la connessione o bus 19, deve sostanzialmente:

- controllare il flusso globale delle operazioni nel circuito;

- generare e distribuire la sincronizzazione generale ai blocchi del circuito;

- sincronizzare l'attività interna del circuito con la sincronizzazione esterna;

- avviare tutti i trasferimenti di dati (nel seguito chiamati transazioni) sui bus 16;

- avviare le operazioni dei moduli.

La struttura di GC sarà illustrata con maggiori dettagli con riferimento alla fig. 5.

L'interfaccia IS controlla attraverso una struttura hardware l'effettivo accesso alla memoria esterna, una volta che il controllore ha identificato l'unità interessata al trasferimento, generando tutti i segnali di controllo e di indirizzamento necessari. Per esempio, IS può sostanzialmente operare come descritto nella domanda di brevetto Italiana TO 96A000123 depositata il 26 Febbraio 1996.

Il circuito comprende inoltre una memoria interna MP e un'unità di prova TE.

La memoria MP, a cui i moduli M1, M2 accedono attraverso il bus 15, è una normale memoria ad accesso casuale che memorizza una matrice di pesi utilizzata nel raffinamento dei vettori o che potrebbe anche essere utilizzata come memoria ausiliaria

da un'unità di elaborazione nei moduli M1, M2.

B

ے

L'unità di prova TE è una cosiddetta interfaccia JTAG (Joint Test Action Group = gruppo di azione di prova congiunto) conforme allo standard IEEE1149.1. L'unità di prova TE è connessa attraverso il bus 13 ad un normale controllore delle prove (non rappresentato) da cui riceve le informazioni necessarie per controllare tutte le prestazioni di prova automatica incorporate nel circuito e a cui invia i risultati della prove. Per effettuare le prove, TE ha accesso attraverso i bus 15, 16 a tutte le risorse connesse a detti bus e ha accesso diretto ai moduli M1, M2 attraverso un bus 17 e, attraverso un bus 18, alle memorie tampone B1...B3, alla memoria MP e alle memorie delle unità IB, GC per il controllo delle funzioni di prova automatica di tali memorie e la ricezione delle informazioni di stato e dei risultati delle prove. Una descrizione dettagliata della struttura e delle funzioni dell'unità di prova TE non è necessaria per la comprensione della presente invenzione.

Facendo ora riferimento alla fig. 2, il modulo Mi (i = 1, 2) comprende essenzialmente:

- un'unità di generazione dei vettori GV, che deve calcolare i vettori di movimento in base alla funzione del circuito e all'algoritmo scelto e controllare le altre unità del modulo;

- una prima e una seconda memoria MM, MF, che memorizzano rispettivamente il macroblocco corrente e la finestra di ricerca estratta dall'immagine di riferimento; sia l'immagine di riferimento che il macroblocco corrente vengono letti dalla memoria esterna; a questo proposito, vogliamo ricordare che l'immagine di riferimento, nel caso di un'immagine di tipo quadro, sarà l'immagine I o P precedente (I = immagine sottoposta a codifica intra-immagine, P = immagine codificata con predizione), mentre nel caso di un'immagine di tipo semiquadro ciascun semiquadro utilizza,

CSELT Centro Studi e Laboratori Telecomunicazioni S.p.A,

come immagine di riferimento, i due precedenti semiquadri I o P;

- un'unità di generazione degli indirizzi GIN, che deve generare gli indirizzi di lettura e di scrittura per MF e MM sfruttando i vettori forniti da GV e segnali di controllo forniti tramite il bus 16;

- un elaboratore di pixel o macchina di confronto CE, che deve svolgere le operazioni aritmetiche sui pixel necessarie per determinare i costi associati ai vettori o alle varie modalità di predizione, in base alla funzione che il circuito deve svolgere. CE è associato ad un controllore CCE che riceve da GV le informazioni circa il tipo di operazione che CE deve svolgere in una certa fase dell'operazione e i vettori di movimento i quali, secondo la normativa MPEG2, comprendono anche informazioni operative;

- un'unità di ordinamento e classificazione SU la quale, durante l'elaborazione relativa ad un macroblocco, riceve i vettori e gli errori corrispondenti da CE, e deve disporre i vettori in ordine di costo e mantenere a disposizione i vettori migliori (cioè quelli associati agli errori minori, per esempio i nove vettori migliori) indipendentemente dal tipo di errore, e classificare le coppie vettore/errore in base al tipo di predizione e memorizzare il vettore migliore per ciascun tipo di predizione, da utilizzare come vettore candidato per quel tipo di predizione; SU deve inoltre rendere disponibili le coppie memorizzate vettore/errore alla memoria esterna o ad altre unità del circuito per l'impiego nell'elaborazione del macroblocco successivo nel caso di stima del movimento (le nove coppie vettore/errore migliori), oppure per il raffinamento (i vettori candidati per ciascun tipo di predizione) e ricevere dalla memoria esterna o da altre unità del circuito le coppie vettore/errore calcolate precedentemente per renderle disponibili a GV; la struttura di SU sarà meglio illustrata con riferimento alla fig. 4

- un generatore GVC dei vettori casuali richiesti dall'algoritmo genetico;

8

- un banco di registri locali RL per la memorizzazione di informazioni di controllo, fornite dal controllore GC (fig. 1) p. es. attraverso il bus 15, necessarie per avviare e sincronizzare le operazioni del modulo, e di informazioni che devono essere rese disponibili all'esterno, come lo stato del modulo;

- un'unità UTM di prova delle memorie, che serve a provare le memorie MF, MM e una memoria interna in GV, in cooperazione con l'unità di prova TE (fig. 1).

Il modulo comprende un bus interno 20 a cui sono direttamente connesse le unità CE, CCE, SU, GVC, RL, UTM e che, attraverso un'interfaccia IBU, permette la connessione di dette unità o al bus 15 o all'unità di generazione dei vettori GV, la quale è connessa a IBU attraverso un bus 30. IBU permette inoltre la connessione dell'unità di generazione dei vettori GV al bus 15 attraverso la stessa interfaccia. Perciò IBU comprenderà, oltre alle unità appropriate che svolgono le necessarie conversioni di formato, una rete di commutazione che stabilisce la connessione richiesta dalla particolare fase dell'operazione. L'instaurazione della connessione opportuna sarà affidata a GV, nel caso di operazioni controllate da GV (generalmente, scrittura/lettura di registri all'interno del modulo) oppure all'interfaccia del controllore esterno IC (fig. 1) quando un'unità del modulo deve avere accesso al bus 15.

La memoria MM serve ovviamente a memorizzare i 16x16 pixel del macroblocco corrente. Essa comprende due unità operanti a ping-pong, aventi ciascuna una capacità di memoria di 128 parole da 16 bit (cioè 128 coppie di pixel). Ogni operazione di scrittura interessa due pixel alla volta e ogni operazione di lettura interessa 8 pixel alla volta. I pixel letti da MM vengono presentati su un bus 21. Per permettere un funzionamento corretto con la geometria della matrice implicata da una tale organizzazione, la memoria MM viene preferibilmente realizzata come un banco di

registri. I segnali di controllo e di indirizzamento per MM vengono forniti da GIN attraverso un bus 22.

3

Ē

La memoria MF è atta a memorizzare, per la stima del movimento vera e propria, una finestra di ricerca che, nella realizzazione dell'invenzione qui descritta a titolo di esempio non limitativo, ha la dimensione di 96x64 pixel (6x4 macroblocchi), mentre per il raffinamento dei vettori memorizza una zona che ha dimensioni corrispondenti per esempio a 4 macroblocchi. La memoria MF è composta da sei unità di memoria, ciascuna avente una capacità di memoria di 16x64 pixel organizzati p. es. in 128 parole di 64 bit ciascuna (cioè ciascuna parola comprende i dati di 8 pixel). Ciascuna unità vantaggiosamente comprende due elementi, ciascuno destinato a memorizzare 128 parole di 32 bit dato che, come noto all'esperto del ramo, l'area complessiva di tali due elementi è minore di quella occupata da un singolo elemento con la capacità di memoria complessiva richiesta dall'unità stessa. I segnali di indirizzamento e di controllo per MF vengono forniti da GIN attraverso la connessione 27.

Le sei unità in MF sono organizzate in maniera differente a seconda che appartengano ad un circuito che svolge l'effettiva stima del movimento oppure ad un circuito che opera il raffinamento dei vettori. Nella stima del movimento, è richiesta l'intera capacità della memoria MF per memorizzare la finestra di ricerca e si accede individualmente alle sei unità sia in scrittura che in lettura. Per quanto riguarda la scrittura, viene sfruttato il fatto che le finestre di ricerca per macroblocchi adiacenti differiscono di una striscia verticale di 4 macroblocchi della larghezza di 1 macroblocco, cosicché ad ogni ciclo di macroblocco soltanto questa striscia deve essere scritta in MF. Per quanto riguarda la lettura, l'algoritmo genetico utilizzato nella realizzazione preferita richiede il confronto del macroblocco corrente con macroblocchi di riferimento che vengono scelti sostanzialmente a caso e perciò deve essere possibile accedere a

punti casuali all'interno della finestra di ricerca. Nel raffinamento dei vettori, dove deve essere memorizzata soltanto la zona, le sei unità formano due banchi di memoria che operano a ping-pong. In questo caso, tuttavia, le zone da utilizzare nell'elaborazione di macroblocchi adiacenti possono avere una qualunque posizione relativa e quindi ad ogni nuovo ciclo di macroblocco tutti i dati della zona devono essere caricati in MF. Ciascuna zona è in realtà composta da due parti, ognuna associata ad uno diei due semiquadri dell'immagine di riferimento (per l'immagine di tipo quadro) oppure a uno dei semiquadri di riferimento. Date le dimensioni della zona, anche nel raffinamento dei vettori ciascuna operazione di scrittura in MF aggiorna una delle unità. La fettura avverrà secondo le modalità richieste da una ricerca esaustiva nell'area di ricerca interessata.

Le singole unità in MF ricevono i dati attraverso un bus di ingresso 23 (p. es. da 32 bit) il quale è connesso al bus 16 attraverso un convertitore CPD del parallelismo dei dati da 16 a 32 bit. I dati letti da MF vengono presentati su un bus di uscita 24 da 192 bit (cioè vengono letti 24 pixel alla volta). Questo assicura che ad ogni ciclo di orologio vengano effettivamente letti 17 pixel adiacenti (un'intera riga di un macroblocco più un ulteriore pixel necessario per l'interpolazione a semi-pixel e la predizione "dual prime"). I 17 pixel letti simultaneamente verranno chiamati "gruppo". Il bus di uscita 24 di MF porta ad un cosiddetto "barrel shifter" BS il quale sceglie, in base a opportuni segnali di controllo forniti dall'unità di controllo CCE attraverso la connessione 25, i 17 pixel adiacenti di interesse all'interno della stringa di 24 pixel letta da MF e presenta i pixel scelti su un bus 26 che porta a CE. Il blocco CCE ottiene i segnali di controllo utilizzando i bit meno significativi dei vettori di movimento forniti da GV e informazioni di configurazione provenienti dal controllore globale GC (fig. 1). Circuiti che svolgono i compiti di BS sono ben noti nel settore.

L'unità di generazione degli indirizzi GIN, in fase di scrittura, indirizza le unità MM, MF cooperando con l'interfaccia della memoria esterna IS, come indicato dalla connessione di GIN al bus 16. La scrittura in MF durante l'effettiva stima del movimento deve tenere conto dei fatto che i sei elementi vengono aggiornati ciclicamente, come detto in precedenza, cosicché avviene uno spostamento ciclico dell'origine della finestra di ricerca. In fase di lettura, GIN calcola gli indirizzi per MF partendo dai valori delle componenti x e y di un vettore fornito da GV. GIN può comandare la lettura simultanea di entrambe le memorie, oppure la lettura di una sola di esse, in base alla particolare operazione svolta. Si suppone che le informazioni che riguardano la modalità di operazione siano fornite da CCE, attraverso la connessione 25.

3

څ

L'unità di generazione dei vettori GV si basa su un'architettura elaborativa RISC in pipeline in grado di eseguire un'istruzione ad ogni ciclo di orologio. In base al programma memorizzato, GV può implementare qualunque algoritmo desiderato di determinazione dei vettori, di raffinamento dei vettori, di selezione della predizione o di prova. Per quanto riguarda la determinazione e il raffinamento dei vettori e la selezione della predizione, l'unità GV deve essere in grado di elaborare due tipi di dati: vettori (che richiedono un'elaborazione separata delle due componenti a ciascuna istruzione) e errori (che richiedono l'elaborazione dell'intero dato). A questo scopo essa comprende un banco di registri (p. es. 16), ciascuno dei quali è dedicato ad un errore e ad un vettore; l'organizzazione dei registri è tale che un singolo indirizzo logico viene associato ad un vettore e ad un errore, anche se il registro fisicamente contiene due sezioni che memorizzano rispettivamente gli errori e i vettori. La selezione di un errore o di un vettore per l'elaborazione è ottenuta tramite un'opportuna codifica delle istruzioni.

GV utilizza cinque gruppi di istruzioni:

- 35. 3

- istruzioni aritmetiche e logiche;

- istruzioni di prova;

- istruzioni di diramazione e di salto;

- istruzioni di accesso esterno;

- istruzioni di sincronizzazione.

L'insieme di istruzioni verrà caricato in GV in fase di inizializzazione, attraverso il bus 15 e l'interfaccia IBU. Attraverso i registri locali RL l'unità di generazione dei vettori GV riceve appropriati segnali di controllo dal controllore globale GC; a questo proposito si deve notare che il controllore globale potrebbe causare l'esecuzione di parti differenti del programma in momenti differenti del ciclo operativo. Le istruzioni aritmetiche permettono di effettuare operazioni di addizione, sottrazione, combinazione logica, confronto e spostamento; queste ultime servono per eseguire divisioni e moltiplicazioni. Nel caso delle operazioni sugli errori, è anche possibile determinare valori massimi e minimi. Le moltiplicazioni necessarie per la selezione della predizione sono svolte senza la necessità di avere in GV un effettivo moltiplicatore. Riguardo alle istruzioni di sincronizzazione, esse comprendono un'istruzione di "attesa" per la sincronizzazione di GV con le altre unità nel modulo.

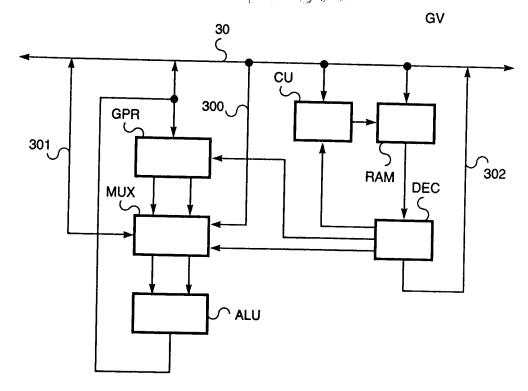

L'architettura di GV è sostanzialmente quella standard di tali unità e non richiede una descrizione dettagliata. Tuttavia, per una migliore comprensione, essa è stata schematicamente illustrata in fig. 3, dove:

- RAM indica la memoria di istruzioni convenzionale, scritta attraverso i bus 15 e 30 dal controllore esterno, e dotata di funzioni di prova automatica incorporate;

- CU indica il complesso delle unità di controllo (contatore di programma, controllore di RAM, unità di diramazione...), indirizzate attraverso il bus 30;

- DEC comprende il decodificatore di istruzioni e il controllore della pipeline, che

generano i segnali di controllo e di indirizzamento per i vari blocchi in GV e gli indirizzi esterni (su una connessione 302 che confluisce nel bus 30);

£

- GPR è il banco di registri, organizzato come descritto in precedenza e avente un ingresso dati connesso al bus 30 o all'uscita di un'unità aritmetico-logica ALU, e due uscite dati; le due uscite dati sono separate, dal punto di vista operativo, solo riguardo ai vettori;

- MUX comprende i multiplexer che selezionano i differenti tipi di ingressi per ALU come pure le unità di pipeline e di avanzamento; MUX può ricevere i dati dal decodificatore (dati immediati), dai registri locali (connessione 300) e dalle unità esterne (connessione 301 che si dirama dal bus 30), e inoltrare i dati alle unità esterne (sempre attraverso la connessione 301);

- l'unità aritmetico-logica ALU, che svolge due operazioni indipendenti sulle due componenti del vettore, oppure una singola operazione su un errore.

L'elaboratore di pixel CE è atto calcolare l'errore (scarto) medio assoluto tra un macroblocco corrente e un macroblocco di riferimento, confrontando pixel omologhi in gruppi di pixel elaborati contemporaneamente e forniti da BS e MM attraverso le connessioni 26, 21. Nel caso in cui il circuito svolga la selezione della predizione, CE deve calcolare anche il costo associato alla codifica intra-immagine. Il calcolo dell'errore viene effettuato su un intero macroblocco (errore a 16 linee) e sulle sue due metà (errore a 8 linee), cosicché vengono generati tre errori per ciascun macroblocco. I tre errori permettono di valutare i costi per tutti i tipi di predizione ammessi dallo standard MPEG2 ("quadro", "semiquadro", "dual prime" per immagini di tipo quadro, "semiquadro", "16x8", "dual prime" per immagini di tipo semiquadro), come risulta chiaro agli esperti del ramo. Gli errori vengono forniti all'unità di classificazione SU attraverso la connessione 28, insieme con il rispettivo vettore fornito da CCE. Il calcolo

base dell'errore richiede un ciclo di orologio (a 54 MHz) per ciascuna riga di pixel nel macroblocco. Il circuito è in grado di calcolare gli errori per pixel interi, o con una precisione a semi-pixel, effettuando l'interpolazione tra pixel adiacenti in una riga (interpolazione orizzontale) e/o in righe consecutive (interpolazione verticale o diagonale) e a questo scopo è necessario un ulteriore ciclo di orologio. L'errore può essere calcolato con o senza rimozione della componente continua dai pixel elaborati. Anche il valore della componente continua è calcolato da CE. La rimozione della componente continua è richiesta per ottenere una buona prestazione della trasformata bidimensionale richiesta dallo standard. Il tipo di operazione che deve essere effettuata in CE è indicato dai segnali di controllo forniti attraverso la connessione 25 da CCE.

CE perciò deve calcolare:

<u>ت</u>

્ટ

a) tre valori di errore che hanno l'espressione generale

$$MAE = \frac{\sum_{j=1}^{N} \sum_{i=1}^{16} \left| (P_{SW}(i,j) - DC_{SW}) - (P_{MC}(i,j) - DC_{MC}) \right|}{N \times 16}$$

(1)

dove P<sub>SW</sub>(i,j) è l'i-esimo pixel (eventualmente sottoposto ad interpolazione) nella j-esima riga nel macroblocco (o parte di macroblocco) di riferimento considerato nella finestra di ricerca; P<sub>MC</sub>(i,j) è l'i-esimo pixel nella j-esima riga del macroblocco corrente; N vale 16 o 8 a seconda che l'errore riguardi un intero macroblocco o la metà di un macroblocco; DC<sub>SW</sub>, DC<sub>MC</sub> sono le componenti continue del macroblocco di riferimento e rispettivamente del macroblocco corrente (relative all'intero macroblocco o a metà di esso), date dall'espressione generale:

$$DC = \frac{\sum_{j=1}^{N} \sum_{i=1}^{16} |P(i,j)|}{N \times 16}$$

(2)

dove P è il pixel del macroblocco corrente o di riferimento, secondo i casi.

b) durante la selezione della predizione, il costo intra-immagine dato da:

Cantro Studi e Laboratori Telecomunicazioni S.p.A.

$$IPC = \frac{\sum_{i,j=1}^{16} |P_{MC}(i,j) - DC_{MC}|}{256}$$

(3)

Ovviamente DC è diverso da 0 solo se è necessaria la rimozione della componente continua.

ŝ

÷

CE consiste essenzialmente di un'unità aritmetica in pipeline, dove gli stadi della pipeline possono essere abilitati in maniera differente in base al particolare calcolo che CE deve effettuare in un certo istante; sulla base della fase dell'operazione, della modalità dell'operazione e della funzione del circuito, CE effettua le seguenti operazioni:

1) interpolazione (se richiesta) sui pixel di un gruppo o di gruppi consecutivi dell' macroblocco di riferimento, operando pixel per pixel; più in dettaglio, indicando con A(k) il k-esimo pixel (k = 0...15) nel gruppo corrente e con B(k) il pixel corrispondente nel gruppo precedente, viene calcolato uno dei seguenti pixel:

$$\begin{array}{ll} Q_1(k) \equiv A(k) & \text{pixel intero} \\ Q_2(k) \equiv \frac{A(k) + B(k) + 1}{2} & \text{intero dual prime o interpolazione verticale} \\ Q_3(k) \equiv \frac{A(k) + A(k+1) + 1}{2} & \text{interpolazione orizzontale} \\ Q_4(k) \equiv \frac{Q_2(k) + Q_2(k+1)}{2} & \text{interpolazione diagonale} \\ Q_5(k) \equiv \frac{Q_2(k) + Q_2(k+1)}{2} & \text{interpolazione dual prime e verticale} \\ Q_6(k) \equiv \frac{Q_5(k) + Q_5(k+1)}{2} & \text{interpolazione dual prime e diagonale} \end{array}$$

L'addendo "+1" nelle espressioni di  $Q_2$  e  $Q_3$  rappresenta un arrotondamento del valore del pixel, richiesto dalla normativa; il termine  $Q_2$ '(k) nell'espressione di  $Q_5$  è il pixel  $Q_2$ (k) relativo alla precedente riga interessata dall'interpolazione.

2a) nel caso di calcolo dell'errore con rimozione della componente continua: calcolo della componente continua per una riga del macroblocco corrente e di quello di riferimento, pixel per pixel; accumulo delle componenti relative a 16 o 8 righe e

calcolo della media dei valori accumulati;

3

9

2b) calcolo dell'errore per una riga, accumulo su 16 o 8 righe e calcolo della media dei risultati accumulati.

Inoltre, nel caso della selezione della predizione, vengono effettuate le seguenti operazioni:

- 3) costo intra-immagine per una riga del macrobiocco corrente con rimozione della componente continua; accumulo dei costi delle 16 righe e calcolo della media dei risultati accumulati;

- 4) valutazione del costo per una codifica con trasformata coseno-discreta a quadro o semiquadro, nel caso che un'immagine debba essere sottoposta a codifica intraimmagine.

Date le relazioni matematiche di cui sopra, l'esperto del ramo non ha alcun problema nel progettare un'unità aritmetica in grado di svolgere le operazioni descritte.

Il generatore di vettori casuali GVC si basa sull'utilizzo di registri a scorrimento con retroazione lineare ed è organizzato in modo da formire una distribuzione pseudo-Gaussiana di numeri casuali per ciascuna delle componenti di un vettore. La distribuzione desiderata è ottenuta effettuando l'inversione e la moltiplicazione su di un insieme di base di numeri casuali. La varianza in entrambe le direzioni della distribuzione può essere regolata dall'unità di generazione dei vettori GV o dal controllore esterno. GVC fornisce a GV un vettore quando riceve una richiesta da parte di GV; la richiesta dà inizio alla generazione di un nuovo vettore. Il progetto di un generatore di questo tipo non è un problema per gli esperti del ramo, una volta data la particolare distribuzione richiesta.

L'unità di prova delle memorie UTM è un'unità destinata a cooperare con le funzioni di prova automatica incorporate nelle memorie del modulo; UTM è connessa

da una parte al bus 17 per ricevere segnali di controllo delle prove da TE (fig. 1) e per inviare risultati delle prove e informazioni di stato a TE, e dall'altra parte è connessa a MF, MM attraverso una connessione o bus 31 tramite il quale indirizza un particolare elemento di memoria interessato dalla prova, invia dati di prova all'elemento e ne riceve i risultati delle prove, e al bus 20 per l'accesso a RAM (fig. 3) in GV.

æ .-

્દ

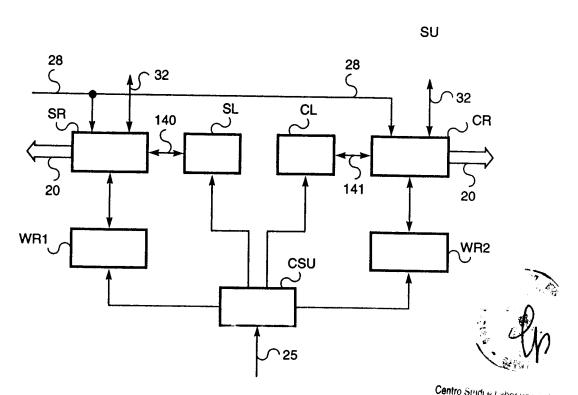

La fig. 4 mostra uno schema funzionale dell'unità di ordinamento e classificazione SU. A SU devono avere accesso, in fasi di operazione diverse: la memoria esterna. che deve caricare in SU le coppie vettore/errore per l'inizializzazione di GV e ricevere da SU le migliori coppie vettore/errore al termine dell'elaborazione di un macroblocco; l'unità di generazione dei vettori GV, che deve leggere le coppie vettore/errore fornite dalla memoria esterna; l'elaboratore di pixel CE, che deve scrivere le coppie vettore/errore da ordinare e classificare. SU è suddivisa dal punto di vista funzionale in due parti, la prima destinata a svolgere l'ordinamento dei vettori in base al valore dell'errore (tenendo conto a questo scopo di un solo errore specifico, p. es. l'errore a 16 linee) durante la stima del movimento e la seconda destinata a effettuare l'associazione delle coppie vettore/errore con il tipo di errore (e quindi di predizione) per il raffinamento del vettore e la selezione della predizione e per memorizzare la miglior coppia vettore/errore per ciascun tipo di predizione.

La prima parte comprende un banco di registri SR (p. es. nove nella realizzazione dell'algoritmo genetico eseguito nel modulo data come esempio) e una logica di ordinamento SL che effettua i confronti necessari per l'ordinamento. Il registro SR può essere scritto da CE (connessione 28), letto da GV (attraverso il bus 20) e scritto/letto dalla memoria esterna (connessione 32 verso IB16). Durante l'elaborazione, una nuova coppia vettore/errore ricevuta viene memorizzata nell'opportuno registro del banco ogni volta il costo è inferiore a quello del peggior vettore memorizzato fino a quel momento.

Questo richiede un trasferimento delle coppie vettore/errore da SR a SL e viceversa, come schematizzato dalla connessione 140. Il blocco WR1 schematizza un'unità convenzionale che controlla la scrittura o la lettura nell'opportuno registro da parte della memoria esterna o di GV, CE e SL, a seconda del caso. Il blocco WR1 è controllato da una logica di controllo CSU, la quale riceve le necessarie informazioni sulle modalità operative p. es. da CCE (connessione 25) e controlla inoltre le operazioni della logica di ordinamento SL.

څ

Ξ.

La seconda parte di SU comprende anch'essa un banco di registri CR, ciascuno dei quali è associato ad un tipo di errore e memorizza il miglior vettore per tale tipo, e una logica di classificazione CL che effettua i confronti necessari per individuare il miglior vettore e per indirizzare l'opportuno registro. Per esempio, sono necessari due registri per la predizione di tipo semiquadro di un'immagine semiquadro basata sul semiquadro di riferimento della stessa parità o rispettivamente di parità opposta; altri quattro registri sono associati invece alle predizioni su otto linee, dove può essere considerata la metà superiore o inferiore del macroblocco. Analogamente a SR, CR riceve le coppie di errore/vettore attraverso la connessione 28, può essere scritto/letto dalla memoria esterna attraverso la connessione 32 e può essere letto da GV attraverso il bus 20; inoltre esso scambia, attraverso la connessione 141, le coppie vettore/errore con la logica di classificazione CL. Il blocco WR2 ha gli stessi compiti di WR1 ed è controllato in maniera analoga da CSU, che a sua volta controlla anche CL.

Verrà ora riassunto il funzionamento del modulo.

Considerando la stima del movimento per un dato macroblocco a regime (cioè quando un'immagine di riferimento è già disponibile), il macroblocco corrente e la relativa finestra di riferimento (più in particolare, la parte che differisce dalla finestra memorizzata per il macroblocco precedente) vengono letti dalla memoria esterna e

caricati nelle memorie MM e MF. Inoltre, le coppie vettore/errore richieste per l'inizializzazione della popolazione di vettori vengono lette dalla memoria esterna e trasferite a GV attraverso i registri SR (fig. 4) dell'unità SU. GV inizia quindi a generare la popolazione di vettori utilizzando anche i vettori casuali forniti da GVC, come illustrato in precedenza. Durante ciascun passo di iterazione dell'algoritmo genetico i vettori vengono forniti in sequenza al controllore CCE della macchina di confronto CE per impostarla correttamente, e al generatore di indirizzi GIN per la lettura da MF dei macroblocchi identificati da detti vettori. CE esegue i calcoli degli errori e, al termine di ciascun passo di iterazione, i migliori vettori (per esempio 9, cioè quanti sono quelli memorizzati nei registri di ordinamento SR) vengono conservati nell'unità di generazione dei vettori per essere utilizzati nella costruzione della generazione successiva secondo l'algoritmo genetico. Il calcolo dell'errore viene ripetuto per i vettori di ogni nuova generazione. Quando tutte le generazioni sono state prese in considerazione, i nove vettori che presentano i migliori errori a 16 linee vengono memorizzati nei registri SR dell'unità SU, mentre il miglior vettore per ciascun tipo di errore viene memorizzato nei registri CR. Il miglior vettore in SR viene pure trasferito alla memoria esterna per essere utilizzato nella fase di inizializzazione relativa all'immagine successiva ed è mantenuto disponibile per essere utilizzato da GV per il macroblocco successivo. Anche i vettori in CR vengono trasferiti alla memoria esterna, da dove verranno letti nell'ordine richiesto per l'uscita sul bus 10 (fig. 1). In effetti, i due moduli elaborano contemporaneamente due macroblocchi appartenenti ad una stessa colonna nell'immagine, mentre i vettori devono essere inviati in uscita sul bus 10 in maniera sequenziale, riga per riga. Si noti inoltre che, nel caso di un circuito appartenente ad una struttura multi-componente come quella illustrata nella nostra domanda di brevetto parallela No. TO 97A000209, il trasferimento del vettore da SU

څ •

្ទ

alla memoria esterna riguarda soltanto l'ultimo componente della catena, mentre il vettori calcolati nei componenti intermedi vengono trasferiti alle unità di confronto appropriate.

3

Quando il circuito è utilizzato per il raffinamento dei vettori, viene caricata in MF una zona, invece di una più ampia finestra di ricerca come richiesto per la stima del movimento. L'unità di generazione dei vettori GV e l'unità di correzione degli errori CE utilizzano i vettori candidati (identificati e classificati da CR e CL) che vengono recuperati dalla memoria esterna. Il raffinamento dei vettori richiede la pesatura dei vettori candidati con i pesi memorizzati nella memoria MP (fig. 1,) che pervengono a GV attraverso il bus 15 e l'interfaccia IBU. GV genererà i vettori come richiesto da una ricerca esaustiva all'interno della finestra di ricerca nella zona e, per ciascun nuovo vettore, CE calcolerà gli errori a 16 e a 8 linee come prima, aggiornando CR quando necessario. Al termine dell'elaborazione, le coppie vettore/errore possono essere direttamente trasferite sul bus 10, attraverso IB16, il bus 16 e IB (fig. 1)

Infine, per la selezione della predizione, il modulo utilizza l'insieme di vettori candidati conservati al termine del raffinamento dei vettori e i relativi errori, per svolgere le operazioni richieste dal particolare programma memorizzato in GV e per individuare se la migliore modalità di predizione per l'immagine è una predizione in avanti, all'indietro o bidirezionale; inoltre, calcola il costo IPC della codifica intra-immagine, come discusso in precedenza, e lo confronta con l'errore MAE associato alla migliore modalità di predizione identificata. La codifica intra-immagine verrà generalmente scelta allorché MAE supera IPC di un valore superiore ad un dato valore di soglia. Un ulteriore passo nella selezione della predizione è la scelta della maniera in cui deve venire calcolata la trasformata bidimensionale. A questo riguardo, si deve ricordare che la trasformata può essere calcolata a quadro o a semiquadro: la decisione assume una

certa rilevanza nel caso della codifica intra-immagine, mentre nel caso della predizione la scelta è legata al tipo di predizione scelto.

ŝ

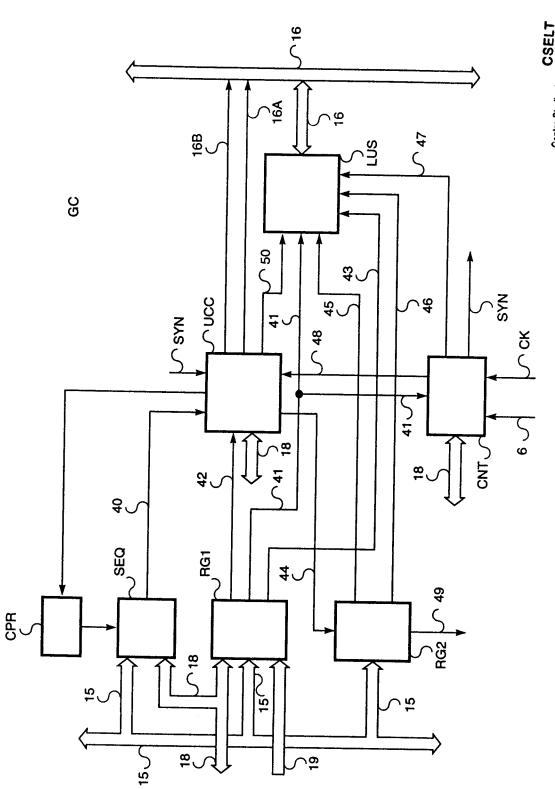

Facendo ora riferimento alla fig. 5, il controllore globale GC comprende essenzialmente: un sequenziatore di microistruzioni SEQ controllato da un contatore di programma CPR, il quale controlla in maniera sequenziale l'esecuzione delle microistruzioni; due insiemi di registri RG1, RG2; un gruppo di contatori CNT; una rete logica di uscita LUS ed un'unità di controllo UCC.

Il sequenziatore di microistruzioni SEQ memorizza un insieme di istruzioni fornito durante una fase di inizializzazione del circuito dal controllore esterno attraverso il bus 15. Le istruzioni riguardano essenzialmente il trasferimento di pixel o di vettori sul bus 16 oppure il trasferimento di parametri operativi in e tra registri interni del controllore globale. Le istruzioni contengono un codice di operazione che definisce l'operazione che GC deve avviare, così come informazioni di sincronizzazione che definiscono il tempo assegnato all'esecuzione dell'istruzione stessa. Le istruzioni vengono inviate attraverso una connessione 40 alla logica di controllo UCC la quale le decodificherà e attiverà quindi l'operazione opportuna. Le informazioni di sincronizzazione vengono utilizzate dalla logica di controllo UCC per fare in modo che il contatore di programma CPR faccia avanzare il sequenziatore SEQ alla fine dell'istruzione. Le istruzioni che riguardano il trasferimento di parametri in o tra registri interni contengono inoltre informazioni da cui la logica di controllo UCC può estrarre gli indirizzi di scrittura e di lettura per i registri.

Il primo insieme di registri RG1 comprende registri di configurazione, i quali sono assegnati a parametri validi in permanenza e sono inizializzati dal controllore esterno attraverso il bus 15, oltre a registri che memorizzano informazioni che variano a cadenza di macroblocco e a registri che memorizzano informazioni che variano a

cadenza d'immagine; le informazioni per gli ultimi due gruppi di registri possono pervenire da IB (fig. 1), attraverso la connessione 19, oppure dal controllore esterno o dall'unità di generazione dei vettori GV (fig. 2) attraverso il bus 15. Dato che la memoria esterna memorizza generalmente più immagini, i registri per le informazioni che variano a cadenza d'immagine contengono più elementi, ciascuno associato ad una delle immagini. Il contenuto dei registri di configurazione e di quelli assegnati alle informazioni che variano a cadenza d'immagine può essere utilizzato tra l'altro per impostare i contatori in CNT e per influenzare le operazioni della logica d'uscita LUS, e viene trasferito a CNT e LUS attraverso una connessione 41. Uno dei registri di configurazione è inoltre atto a ricevere dal controllore esterno una segnalazione che indica che l'inizializzazione è terminata (e quindi il controllore è pronto ad operare) e a trasferirla all'unità di controllo UCC come segnale di attivazione (connessione 42). Un altro registro può ricevere da TE (fig. 1), attraverso il bus 18, una segnalazione di prova che imposta il controllore in modalità di prova. I parametri che variano a cadenza di macroblocco vengono tipicamente utilizzati da LUS per costruire parametri di uscita e vengono inviati a LUS attraverso una connessione 43.

ŝ

Il secondo insieme di registri RG2 comprende i registri interni del controllore che possono essere interessati dal trasferimento di parametri menzionato in precedenza. Questi registri vengono indirizzati da UCC attraverso la connessione 44, a partire da informazioni contenute nelle istruzioni provenienti da SEQ. Ad alcuni dei registri possono anche avere accesso altre unità del circuito attraverso il bus 15. Tra le informazioni fornite da queste altre unità o destinate ad esse, menzioniamo informazioni di stato relative all'attivazione dell'unità di generazione dei vettori GV (fig. 2), che vengono fornite ai registri locali RL attraverso la connessione 49, e parametri che devono essere inviati alla rete logica di uscita LUS in modo da influire sul suo

funzionamento o che devono essere utilizzati da LUS per costruire i parametri di uscita. Le linee 45, 46 schematizzano le connessioni che trasportano detti parametri a LUS.

ć

I contatori CNT devono: controllare, in modo programmabile dai registri di configurazione in RG1, l'attivazione delle operazioni di elaborazione e di emissione dei dati; generare i segnali di sincronismo d'immagine, di macroblocco e di pixel (indicati nel complesso dall'uscita SYN) per sincronizzare l'attività delle varie unità del circuito; attivare le varie unità nel circuito negli istanti opportuni, di nuovo in modo programmabile dai registri di configurazione in RG1. Per svolgere i loro compiti, i contatori CNT si agganciano a segnali di sincronismo d'immagine associati ai dati in arrivo sul bus delle immagini 6 (fig. 1) (oppure ai parametri in arrivo sul bus delle informazioni 9) e ricevono gli appropriati segnali di orologio CK (p. es. a 18 o 54 MHz, nella realizzazione preferita dell'invenzione). Uno dei contatori deve calcolare il tempo dedicato all'esecuzione delle singole microistruzioni e emettere i segnali di tempo scaduto verso UCC (connessione 48) in modo che essa possa far avanzare il contatore di programma CPR.

La rete logica di uscita LUS comprende sostanzialmente un banco di multiplexer che servono a costruire, a partire da valori forniti dal contatore e/o da informazioni memorizzate nei registri in RG1, RG2, alcuni parametri che regolano il corretto accesso alla memoria esterna per il trasferimento di pixel sul bus 16. I parametri vengono quindi inviati all'interfaccia della memoria esterna IS (fig. 2) attraverso il bus 16. I parametri più importanti indicano: l'immagine memorizzata nella memoria esterna ed interessata dall'operazione di trasferimento; la posizione dei macroblocco corrente in quella immagine; la posizione della regione, che è rappresentata da un vettore indicante la posizione di una parte d'immagine (p. es. la finestra di ricerca o una zona) interessata da una operazione di trasferimento di dati; la dimensione della regione. Chiaramente, la

posizione della regione e la posizione del macroblocco coincidono nel caso in cui il trasferimento dei dati riguarda un macroblocco. Detti parametri vengono emessi qualunque sia l'operazione di trasferimento di pixel che deve essere effettuata (p. es. lettura o scrittura di un macroblocco nella memoria esterna, lettura di una finestra di ricerca o di una zona), ma possono essere costruiti in modo differente in base al tipo di operazione e/o a particolare esigenze di elaborazione. In particolare, LUS può costruire i parametri a partire da dati prestabiliti (che possono essere i valori presenti sulle uscite 47 dei contatori, nel caso della posizione del macroblocco, i valori fomiti dai registri RG1 attraverso la connessione 43 per la posizione della regione e valori fissi per la dimensione della regione, valori fomiti dai registri per l'immagine) oppure utilizzando valori fomiti dai registri RG2 attraverso la connessione 46. La scelta delle sorgenti di dati appropriate è comandata da informazioni riguardanti il tipo di operazione (OPCODE) fornite dalla logica di controllo UCC attraverso i fili 50 e da segnali forniti dai registri in RG1, RG2 attraverso le connessioni 41, 45. Questi causeranno in generale fa selezione da parte di LUS dei valori particolari memorizzati nei registri RG2.

3

\_ **₫**. ≎

La logica di controllo UCC comprende essenzialmente una rete logica di decodifica, la quale decodifica le istruzioni generate da SEQ, e una logica sequenziale (macchina a stati) che deve avviare l'attività generale del controllore GC, al ricevimento della segnalazione di avvio menzionata in precedenza e a controllare l'evoluzione del microprogramma memorizzato nel sequenziatore. UCC riceve inoltre gli appropriati segnali di sincronismo SYN dai contatori e, durante l'esecuzione di un'istruzione, emette sui fili 16B del bus 16 un segnale (ADRVAL) che indica alle unità connesse al bus 16 che deve essere svolta un'operazione identificata dall'informazione OPCODE presentata sui fili 16A. Si noti che l'informazione OPCODE deve essere inviata a LUS tramite i fili 50 in anticipo rispetto a quella presentata sul bus 16, e questo è il motivo

per cui si sono indicate due connessioni separate. OPCODE può essere o il codice operativo contenuto nell'istruzione, oppure un codice indicante che non deve essere eseguita alcuna operazione o ancora un codice che indica che si deve "rigenerare" la memoria esterna. Questi ultimi codici sono generati dalla logica sequenziale in UCC. Il codice "nessuna operazione" è generato da UCC quando non è abilitata una particolare operazione indicata nell'istruzione: l'abilitazione delle singole transazioni è gestita internamente da UCC tenendo conto della situazione generale del circuito (disponibile nella logica sequenziale) e dei valori forniti dai contatori CNT. Il codice "rigenerazione della memoria esterna" verrà normalmente generato in situazioni in cui non può essere abilitato alcun trasferimento di dati, indipendentemente dal contenuto dell'istruzione: per esempio, la rigenerazione può avvenire in corrispondenza di un'istruzione che richiede l'emissione della cosiddetta "cancellazione di striscia".

I contatori CNT, il sequenziatore SEQ e la logica di controllo UCC sono inoltre connessi al bus 18 attraverso il quale TE (fig. 1) controlla le funzioni di prova automatica e riceve informazioni sullo stato delle prove e risultati delle prove.

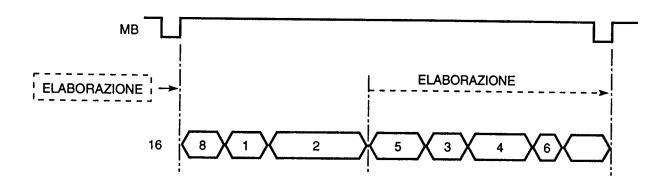

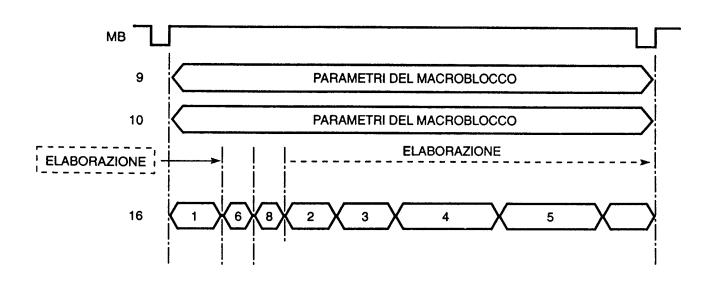

Per una migliore comprensione del funzionamento generale del controllore, si può fare riferimento alle fig. 6, 7 e 8 le quali illustrano l'evoluzione dell'elaborazione e la sequenza delle transazioni durante un periodo d'immagine (fig. 6) e durante un periodo di macroblocco, rispettivamente per la stima del movimento e per il raffinamento dei vettori (figure 7 e 8). Queste figure sono una versione semplificata delle figure 7-9 della domanda di brevetto TO 97A000209 menzionata in precedenza, e in esse, tra le varie operazioni che non richiedono l'intervento dei moduli, viene mostrato solamente il caricamento delle immagini di ingresso, mentre non sono mostrate le transazioni relative ad una struttura multi-componente. Le figure 7, 8 si riferiscono ad un macroblocco elaborato ad un istante come l'istante τ in fig. 6. Le linee

indicate con 6, 9, 10, 16 si riferiscono alle operazioni relative ai bus omonimi. SD indica la memoria esterna. Ciascuna operazione è attivata dai segnali ADRVAL e OPCODE, in presenza dei rispettivi segnali di abilitazione generati in UCC.

La fig. 6 mostra che, durante i periodi attivi del segnale di sincronismo di immagine, un'immagine di ingresso in arrivo tramite il bus 6 viene caricata nella memoria esterna e che, dopo un tempo di latenza Ld, che generalmente è di 2 strisca di macroblocchi per la stima del movimento e di 1 tempo di macroblocco per il raffinamento dei vettori, inizia l'elaborazione dei dati e vengono trasferiti alle memorie MF, MM (fig. 2) dei moduli la finestra di ricerca e il macroblocco corrente. Contemporaneamente all'inizio dell'elaborazione dei pixel, i moduli M1, M2 (fig. 1) cominciano a leggere dalla memoria esterna i vettori di inizializzazione, per eseguire l'algoritmo genetico e inviare le migliori coppie vettore/errore alla memoria esterna. Al termine dell'elaborazione, i vettori memorizzati nella memoria esterna vengono trasferiti al bus di uscita delle informazioni in sincronismo con i pixel e con i parametri di elaborazione.

Nelle figure 7 e 8 si vede che l'elaborazione può non cominciare immediatamente all'inizio del periodo di macroblocco, per permettere l'acquisizione dei risultati dell'elaborazione ottenuti nel periodo di macroblocco precedente. Quindi, una volta iniziata, l'elaborazione occupa la restante parte del periodo di macroblocco e l'intero periodo di macroblocco successivo nel caso della stima del movimento, mentre, nel caso del raffinamento dei vettori, occupa l'intero periodo di macroblocco successivo e una frazione iniziale di ancora un altro periodo di macroblocco, anche se in totale l'elaborazione è leggermente più breve di due periodi di macroblocco.

Per la stima del movimento, la sequenza delle transazioni è la seguente:

- trasferimento del miglior vettore calcolato durante il periodo di macroblocco precedente da uno dei moduli M1, M2 (fig. 1) alla memoria esterna (transazione 8);

2

- trasferimento dei vettori di inizializzazione dalla memoria esterna al modulo (transazione 1)

- trasferimento di quattro macroblocchi verticali della finestra di ricerca dalla memoria

esterna alla memoria MF (fig. 2) del modulo (transazione 2);

- trasferimento dei pixel di luminanza e crominanza di un macrobiocco dalla memoria esterna alla memoria tampone di uscita B3 (fig. 3) (transazione 5); l'elaborazione effettiva comincia all'inizio di questa transazione;

- trasferimento del macrobiocco corrente (solo pixel di luminanza) dalla memoria

esterna alla memoria MM del modulo (transazione 3);

- trasferimento di un macroblocco (pixel di luminanza e crominanza) dalla memoria tampone di ingresso B1 (fig. 1) alla memoria esterna (transazione 4);

- trasferimento delle coppie vettore/errore dalla memoria esterna al gestore del bus

delle informazioni (transazione 6); la fine di questa operazione coincide con la fine

del periodo dedicato al trasferimento dei vettori dal bus di ingresso delle

informazioni al circuito e dal circuito al bus di uscita delle informazioni.

Naturalmente, durante periodi come il tempo di latenza, vengono eseguite solo alcune delle operazioni viste sopra e quindi non vengono generati i rispettivi segnali di abilitazione; in queste condizioni GC emetterà il codice "nessuna operazione".

Per il raffinamento dei vettori (fig. 8), il trasferimento dei parametri di elaborazione dal bus di ingresso delle informazioni al circuito o dal circuito al bus di uscita delle informazioni potrebbe richiedere sostanzialmente l'intero tempo di macroblocco. La sequenza delle operazioni è la seguente:

trasferimento dei pixel di luminanza e di crominanza dal bus di ingresso delle immagini 6 alla memoria esterna e trasferimento del macroblocco corrente (solo pixel di luminanza) dalla memoria esterna alla memoria MM del modulo (transazione 1); durante questa operazione, termina l'elaborazione di un macroblocco iniziata due periodi di macroblocco prima;

Ŧ

- trasferimento di un gruppo di vettori candidati dal gestore del bus delle informazioni al modulo (transazione 8);

- trasferimento dei pixel di luminanza dell'immagine di riferimento dal bus di ingresso delle immagini 7 alla memoria esterna (transazione 2); contemporaneamente all'inizio dell'operazione, comincia l'elaborazione;

- trasferimento dei pixel di luminanza e di crominanza del macroblocco dalla memoria esterna al bus di uscita delle immagini 8 (transazione 3);

- trasferimento di un primo semiquadro della zona dalla memoria esterna alla memoria MF del modulo (transazione 4);

- trasferimento di un secondo semiquadro della zona dalla memoria esterna alla memoria MF del modulo (transazione 5).

Ogni trasferimento di parametri in o tra registri interni del controllore globale necessario ad una transazione è compreso nella rispettiva transazione.

E' evidente che la descrizione che precede è data solo a titolo di esempio non limitativo e che sono possibili varianti e modifiche senza uscire dal campo di protezione della presente invenzione.

## RIVENDICAZIONI

٦

- 1. Circuito per la stima del movimento per codificatori di sequenze video numerizzate, il quale riceve blocchi di pixel di un'immagine corrente e genera, per ognuno di detti blocchi di pixel (nel seguito chiamato "blocco corrente"), uno o più vettori che rappresentano lo spostamento di detto blocco rispetto ad un blocco di pixel corrispondente (nel seguito chiamato "blocco di riferimento") in una finestra di ricerca appartenente a un'immagine di riferimento, il circuito comprendendo:

- almeno una coppia di unità operative (M1, M2) che sono programmabili indipendentemente e sono atte a elaborare in modo concorrente dati differenti nell'immagine corrente e nella finestra di ricerca secondo una tecnica di elaborazione a istruzioni multiple e a dati multipli, per eseguire una delle seguenti funzioni:

- determinazione di un insieme di vettori di movimento candidati per ciascun blocco

corrente, ogni vettore nell'insieme identificando un blocco di riferimento che

meglio riproduce il blocco corrente secondo una data modalità di predizione, e di

un errore di stima associato ad ogni vettore candidato;

- raffinamento dei vettori, per migliorare la concordanza tra detto macroblocco di riferimento e detto macroblocco corrente;

- eventualmente in aggiunta ad una selezione di una modalità di predizione tra una molteplicità di possibili modalità di predizione, per determinazione se nella codifica dell'immagine corrente si deve utilizzare una modalità di predizione, e quale;

- un primo bus interno (15), al quale sono connesse dette unità operative (M1. M2) e che è destinato a trasferire al circuito informazioni di programmazione e inizializzazione oppure parametri di elaborazione provenienti da un controllore esterno, a portare informazioni di monitoraggio a detto controllore esterno e a

4

permettere lo scambio di informazioni tra unità diverse nel circuito;

- un secondo bus interno (16), al quale sono connesse dette unità operative (M1, M2)

e che è destinato a trasportare dati video e parametri di elaborazione, inclusi risultati della stima, che devono essere scritti in una memoria esterna oppure che sono letti da detta memoria esterna;

- un controllore interno (GC), connesso a detti primo e secondo bus interno (15, 16), che deve: identificare e abilitare le unità del circuito interessate da un trasferimento di dati su detto secondo bus (16); assegnare a unità diverse parti diverse di un ciclo di elaborazione; generare e distribuire la sincronizzazione generale alle unità del circuito; controllare il flusso globale delle operazioni nel circuito; sincronizzare l'attività interna del circuito con una sincronizzazione esterna; e avviare le operazioni delle unità operative (M1,M2);

caratterizzato dal fatto che ciascuna unità operativa (M1, M2) comprende:

- un'unità di generazione dei vettori (GV) che deve generare i vettori di movimento che rappresentano lo spostamento di un biocco corrente di pixel rispetto a una molteplicità di blocchi di riferimento che sono provati nella finestra di ricerca, eseguendo istruzioni caricate nell'unità (GV) durante una fase di inizializzazione e relative ad un algoritmo prestabilito per la determinazione o il raffinamento dei vettori candidati od ancora per la selezione della predizione;

- una prima e una seconda unità di memoria interna (MM, MF) connesse a detto secondo bus (16) e destinate a memorizzare rispettivamente detto blocco corrente di pixel e i pixel della rispettiva finestra di ricerca, forniti da detta memoria esterna;

- un'unità di generazione degli indirizzi (GIN), che deve generare gli indirizzi di lettura

e di scrittura per dette prima e seconda unità di memoria interna (MM, MF) a partire

da vettori forniti dall'unità di generazione dei vettori (GV);

- un elaboratore di pixel (CE, CCE) che riceve da dette unità di memoria (MM, MF) i pixel del blocco corrente e di un blocco di riferimento e da detta unità di generazione dei vettori (GV) i vettori e informazioni riguardanti il tipo di operazione che l'elaboratore di pixel (CE) deve svolgere, l'elaboratore di pixel eseguendo su detti pixel operazioni aritmetiche richieste per determinare detto errore di stima, confrontando gruppi di pixel nel blocco corrente con gruppi omologhi di pixel in un certo numero di blocchi di riferimento identificati nella finestra di ricerca da vettori generati da detta unità di generazione dei vettori (GV), oppure per selezionare la modalità di predizione appropriata, l'elaboratore di pixel calcolando detto errore di stima rispetto ad un intero blocco oppure rispetto a parti differenti dei blocchi;

- un'unità di ordinamento (SU), che è connessa a detto elaboratore di pixel (CE; CCE) da cui riceve i vettori di movimento e i relativi errori, insieme ad informazioni sulle modalità operative, e comprende mezzi (CR, CL) per dividere i vettori in base alla modalità di predizione, per individuare il vettore associato al più basso errore per ciascuna modalità di predizione e per memorizzare tale vettore come vettore candidato per quella modalità di predizione insieme con il rispettivo errore, detti mezzi di divisione, individuazione e memorizzazione (CR) essendo accessibili da detta memoria esterna e da altre unità del circuito per la scrittura di coppie vettore/errore calcolate durante l'elaborazione di blocchi correnti precedenti e per la lettura delle coppie vettore/errore conservate alla fine dell'elaborazione relativa al blocco corrente, e da detta unità di generazione dei vettori per la lettura di coppie vettore/errore scritte dalla memoria esterna;

- un terzo bus interno (20) a cui sono connessi detta unità di generazione degli indirizzi (GIN), detto elaboratore di pixel (CE, CCE) e detta unità di ordinamento (SU), detto terzo bus (20) essendo associato a mezzi (IBU) per stabilire una

connessione tra detto terzo bus (20) e detto primo bus interno (15), oppure tra detto terzo bus (20) e detta unità di generazione dei vettori (GV), oppure tra detto primo bus interno (15) e detta unità di generazione dei vettori (GV).

3

- 2. Circuito secondo la rivendicazione 1, caratterizzato dal fatto che ogni unità operativa (M1, M2) comprende inoltre un generatore (GVC) di vettori casuali, connesso a detto terzo bus interno (20) per fornire all'unità di generazione dei vettori (GV) vettori casuali da utilizzarsi nella costruzione di una popolazione di vettori necessaria per l'esecuzione di un algoritmo genetico per la determinazione dei vettori candidati.

- 3. Circuito secondo la rivendicazione 1 o 2, caratterizzato dal fatto che detto generatore di vettori casuali (GVC) è un generatore di numeri casuali con una distribuzione pseudo-Gaussiana, ed è atto a generare una distribuzione configurabile sia per una componente orizzontale sia per una verticale di ciascun vettore.

- 4. Circuito secondo una qualsiasi delle rivendicazioni da 1 a 3, caratterizzato dal fatto che detta unità di ordinamento (SU) comprende anche mezzi (SR, SL) per ordinare i vettori forniti dall'elaboratore di pixel (CE, CCE) anche sulla base del valore di uno degli errori di stima calcolati da detto elaboratore e per memorizzare, alla fine dell'elaborazione riguardante un blocco di pixel, un certo numero di vettori che presentano gli errori più bassi insieme ai rispettivi errori, detti mezzi di ordinamento e di memorizzazione (SR) essendo accessibili da detta memoria esterna e da altre unità del circuito per la scrittura di coppie vettore/errore calcolate durante l'elaborazione dei blocchi precedenti e per la lettura di coppie vettore/errore conservate alla fine dell'elaborazione relativa al blocco corrente, e da detta unità di generazione dei vettori (GV) per la lettura delle coppie vettore/errore scritte dalla memoria esterna in una fase di inizializzazione della costruzione della popolazione di vettori.

- 5. Circuito secondo una qualsiasi delle rivendicazioni da 1 a 4, caratterizzato dal

fatto che detta unità di generazione dei vettori (GV) è basata su di un elaboratore con insieme di istruzioni ridotto (RISC) a pipeline, che include un primo banco di registri (GPR) comprendente due insiemi di registri di cui uno ("registri dei vettori") è atto a memorizzare vettori e l'altro ("registri degli errori") è atto a memorizzare errori, ogni registro dei vettori essendo a sua volta diviso in due parti che memorizzano rispettivamente una componente orizzontale e una componente verticale del rispettivo vettore; uno stesso indirizzo logico essendo assegnato ad un registro dei vettori e ad un registro degli errori così da instaurare e mantenere l'associazione tra ciascun vettore e il relativo errore, la selezione dei dati da elaborare da un registro dei vettori o da un registro degli errori associati ad uno stesso indirizzo essendo effettuata per mezzo di un codice di operazione contenuto in istruzioni memorizzate nell'unità.

3

- 6. Circuito secondo una qualsiasi delle rivendicazioni da 1 a 5, caratterizzato dal fatto che detto elaboratore di pixel (CE, CCE) è un'unità aritmetica in pipeline atta a ricevere da dette prima e seconda unità di memoria (MM, MF), per detto calcolo dell'errore, gruppi corrispondenti di pixel appartenenti al blocco corrente e ad un blocco di riferimento, e a svolgere su detti pixel le seguenti operazioni:

- a1) far passare inalterati i pixel di un gruppo appartenente ad un blocco di riferimento; oppure

- a2) effettuare una interpolazione tra pixel adiacenti di un gruppo o tra pixel di gruppi successivi, l'esecuzione delle operazioni a1) e a2) o di interpolazioni differenti nell'operazione a2) essendo mutuamente esclusiva ed essendo determinata da segnali di controllo forniti da un'unità di controllo (CCE) dell'elaboratore;

- b) confrontare pixel omologhi in detti gruppi corrispondenti e calcolare un errore relativo ad un gruppo;

- c) accumulare gli errori relativi a tutti i gruppi in un blocco o in una parte di blocco per

ottenere un errore accumulato;

- d) calcolare la media dell'errore accumulato.

- 7. Circuito secondo la rivendicazione 6, caratterizzato dal fatto che detto elaboratore di pixel è atto a calcolare, prima dell'operazione di calcolo dell'errore nel passo b), un valore medio del blocco o parte di blocco di pixel, e sottrarre detto valore medio all'errore calcolato.

- 8. Circuito secondo la rivendicazione 6 o 7, caratterizzato dal fatto che detto elaboratore di pixel è atto a calcolare, in un circuito che effettua la selezione della predizione, un costo associato ad una codifica intra-immagine, detto calcolo del costo richiedendo il confronto tra pixel di un blocco corrente con un valore medio degli stessi, l'accumulo dei risultati del confronto e il calcolo della media del valore accumulato.

- 9. Circuito secondo una qualsiasi delle rivendicazioni da 1 a 8, caratterizzato dal fatto che ogni unità operativa (M1, M2) comprende inoltre registri (RL), connessi anch'essi a detto terzo bus interno (20), per la memorizzazione temporanea di informazioni che sono fornite da detto controllore interno (GC) e devono essere lette da detta unità di generazione dei vettori (GV).

- 10. Circuito secondo una qualsiasi delle rivendicazioni da 1 a 9, caratterizzato dal fatto che detta seconda unità di memoria (MF) è costituita da un gruppo di elementi di memoria accessibili in maniera indipendente, che forniscono nell'insieme la capacità di memoria richiesta per la memorizzazione dei pixel di una finestra di ricerca comprendente, almeno per la generazione dei vettori candidati, un numero significativo di detti blocchi di riferimento; e dal fatto che i mezzi di indirizzamento (GIN) per detta seconda memoria (MF) sono atti a indirizzare detti elementi in maniera tale che ogni operazione di scrittura riguardi singoli elementi di memoria e causi l'aggiornamento di almeno un intero elemento, e la lettura riguardi una molteplicità di elementi di memoria

e blocchi di pixel scelti in modo casuale, e causi il trasferimento contemporaneo di tutti i pixel in un gruppo a detto elaboratore di pixel (CE).

11. Circuito secondo una qualsiasi delle rivendicazioni da 1 a 10, caratterizzato dal fatto che dette unità operative (M1, M2) comprendono inoltre un'unità di prova delle memorie (UTM), connessa da un lato ad una interfaccia di prova (TE) nel circuito per ricevere informazioni di controllo e inviare risultati di prove e informazioni di stato sulle prove, e dall'altro a singoli elementi in dette prima e seconda unità di memoria (MM, MF) per l'indirizzamento di uno specifico elemento di memoria interessato dalla prova, l'invio di dati di prova all'elemento e la ricezione di risultati della prova dallo stesso.

12. Circuito secondo la rivendicazione 11, caratterizzato dal fatto che detta unità di prova delle memorie (UTM) è connessa a detto terzo bus (20) per l'accesso a una memoria di istruzioni di detta unità di generazione dei vettori.(GV) e per la prova di tale memoria.

13. Circuito secondo una qualsiasi delle rivendicazioni da 1 a 12, caratterizzato dal fatto che detto controllore interno (GC) comprende:

- un sequenziatore di istruzioni (SEQ), che memorizza un gruppo di istruzioni, caricate in detto sequenziatore (SEQ) durante una fase di inizializzazione del circuito e riguardanti il trasferimento di pixel e/o vettori su detto secondo bus interno (16) o ancora il trasferimento di parametri operativi in o tra registri del controllore interno stesso;

- un contatore di programma (CPR) che controlla l'esecuzione in sequenza di dette istruzioni;

- una logica di controllo (UCC), attivata alla ricezione di un segnale di attivazione indicante che il controllore è pronto ad operare, e comprendente mezzi di decodifica, i quali decodificano le istruzioni generate dal sequenziatore (SEQ), e una logica

sequenziale la quale, per ogni istruzione, deve abilitare altre unità nel circuito a svolgere un'operazione specificata in detta istruzione e deve pilotare detto contatore di programma (CPR), alla fine di un periodo assegnato all'esecuzione di detta istruzione, in modo che esso faccia procedere la sequenza delle istruzioni, l'evoluzione della logica sequenziale essendo controllata da segnali di sincronismo (SYN) generati nel controllore interno (GC);

۹

- un secondo banco di registri (RG1), comprendente registri di configurazione, destinati a memorizzare informazioni permanenti fornite da detto controllore esterno, e registri destinati a memorizzare informazioni variabili specifiche per un blocco o un'immagine, un registro nel banco fornendo alla logica di controllo (UCC) detto segnale di attivazione;

- un gruppo di contatori (CNT), che deve: controllare, in modo programmabile dai registri di configurazione nel secondo banco di registri (RG1), l'attivazione delle operazioni di elaborazione e di emissione dei dati; generare detti segnali di sincronismo (SYN); e attivare unità differenti del circuito ad istanti che sono anch'essi programmabili da detti registri di configurazione, detti contatori (CNT) ricevendo, per l'esecuzione di tali compiti, segnali di sincronizzazione associati ai dati in arrivo e segnali di orologio esterni (CK);

- un terzo banco di registri (RG2), che memorizzano detti parametri operativi interessati dalle istruzioni di trasferimento di parametri generate da detto sequenziatore (SEQ), almeno alcuni dei registri del terzo banco essendo accessibili da altre unità nel circuito per la lettura di parametri operativi di interesse per dette altre unità o per la scrittura di parametri operativi da utilizzarsi nella costruzione di informazioni di uscita che regolano il trasferimento di pixel su detto secondo bus interno (16);

una rete logica di uscita (LUS) che comprende un'unità di multiplazione atta a

costruire dette informazioni di uscita a partire da valori forniti da detti contatori (CNT)

e da informazioni memorizzate almeno in detto secondo banco di registri (RG1).

14. Circuito secondo la rivendicazione 13, caratterizzato dal fatto che detta rete logica di uscita (LUS) comprende inoltre mezzi di selezione sensibili a informazioni relative al tipo di operazione fornite da detta logica di controllo (UCC) e da detti secondo e terzo banco di registri (RG1, RG2) per controllare la costruzione di dette informazioni di uscita o a partire da valori prestabiliti forniti da detti contatori (CNT) e da detto secondo banco di registri (RG1), oppure a partire da valori programmabili, forniti da detto terzo banco di registri (RG2).

15 Circuito secondo la rivendicazione 13 o 14, caratterizzato dal fatto che dette informazioni di uscita comprendono: la posizione di un'immagine nella memoria esterna; la posizione del blocco corrente all'interno di un'immagine in corso di elaborazione; la posizione di una regione d'immagine interessata da una operazione di trasferimento di pixel; e la dimensione della regione.

ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE

CSELT

Centro Studi e Laboratori Telecomunicazioni S.p.A.

B Responsabile Proprietà Industriale

(Brung MURACA)

Fig. 1

(Bruno/MURACA)

(Brunh MURACA)

Fig. 2

Fig. 3

Centro Studi e Laboration indecomunicazioni o p.A.

ECOLE POLYTECHNIQUE Responsabile Proprietà Industriale

FEDERALE DE LAUSANNE

Fig. 4

(Brugo MURACA)

CSELT

Centro Studi e Laboratori Telecomunicazioni S.p.A.

Il Responsabile Proprietà Industriale

(Bruno/MURACA)

ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE

Fig. 5

TO 97 A

CARICAMENTO FINESTRA E MB CORRENTE IN MF, MM VETTORI MIGLIORI-VETTORE / ERRORE CORRENTE MEMORIZZAZIONE IMMAGINE ENTRANTE IN SD VETTORI INIZIALIZZAZIONE ۲٩ ELABORAZ. SU → SD SD → SU 7

ဖ

ECOLE POLYTECHNIQUE<sub>Centro</sub> Shudi e Laboratori Telecomunicazioni S.p.A. C. I. Responsabile Proprietà industriale

LAUSANNE

(Bruno MURACA)

Fig. 6

Fig. 7

ECOLE POLYTECNIQUE FEDERALE DE LAUSANNE

Fig. 8

CSELT

Centro Studi e Laboratori Telecomunicazioni S.p.A.

Il Responsabile Proprietà Industriale

(Bruno MURACA)