(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-33032

(P2006-33032A)

(43) 公開日 平成18年2月2日(2006.2.2)

|                            |             |             |

|----------------------------|-------------|-------------|

| (51) Int.CI.               | F 1         | テーマコード (参考) |

| <b>H04L 7/00</b> (2006.01) | H 04 L 7/00 | H 5K047     |

| <b>H04L 7/02</b> (2006.01) | H 04 L 7/02 | Z           |

審査請求 未請求 請求項の数 9 O L (全 22 頁)

|           |                              |          |                                               |

|-----------|------------------------------|----------|-----------------------------------------------|

| (21) 出願番号 | 特願2004-204412 (P2004-204412) | (71) 出願人 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (22) 出願日  | 平成16年7月12日 (2004.7.12)       | (74) 代理人 | 100090479<br>弁理士 井上 一                         |

|           |                              | (74) 代理人 | 100090387<br>弁理士 布施 行夫                        |

|           |                              | (74) 代理人 | 100090398<br>弁理士 大渕 美千栄                       |

|           |                              | (72) 発明者 | 森垣 利彦<br>長野県諏訪市大和3丁目3番5号 セイコ<br>ーエプソン株式会社内    |

|           |                              |          | F ターム (参考) 5K047 AA05 GG07 GG24               |

(54) 【発明の名称】クロック切り替え回路

## (57) 【要約】

【課題】 ハザードを生じることなく早いタイミングでのクロック切り替えが可能なクロック切り替え回路を提供すること。

【解決手段】 第1のクロックCLK1と、第2のクロックCLK2と、クロックCLK1とクロックCLK2を切り替えるためのクロック切り替え実行信号CESとを受け、クロックCLK2が第1のレベルである期間に信号CESがアクティブになった場合に、クロックCLK1の立ち上がりエッジまたは立ち下がりエッジを含む前後の所与の期間、クロックCLK2のレベルを第2のレベルに固定してクロック切り替え用合成クロックCMPとして出力する合成クロック生成回路300と、クロックCMPと、信号CESとを受け、クロックの切り替え指示信号CDSを出力する切り替え指示信号生成回路200と、信号CDSがアクティブになった場合に、第1のクロック選択信号CSS1のレベルを変化させるクロック選択信号生成回路100と、信号CSS1のレベルに応じて、クロックCLK1またはクロックCMPのいずれかを選択して出力する第1のセレクタ400を含

**【特許請求の範囲】****【請求項 1】**

第1のクロックと、前記第1のクロックとは周波数が異なる第2のクロックと、前記第1のクロックと前記第2のクロックを切り替えるためのクロック切り替え実行信号とを受け、前記第2のクロックが第1のレベルである期間にクロック切り替え実行信号がアクティブになった場合に、前記第1のクロックの立ち上がりエッジまたは立ち下がりエッジを含む前後の所与の期間、前記第2のクロックのレベルを第2のレベルに固定してクロック切り替え用合成クロックとして出力する合成クロック生成回路と、

前記クロック切り替え用合成クロックと、前記クロック切り替え実行信号とを受け、クロックの切り替え指示信号を出力する切り替え指示信号生成回路と、

前記切り替え指示信号がアクティブになった場合に、第1のクロック選択信号のレベルを変化させるクロック選択信号生成回路と、

前記クロック選択信号生成回路からの前記第1のクロック選択信号のレベルに応じて、前記第1のクロックまたは前記クロック切り替え用合成クロックのいずれかを選択して出力する第1のセレクタを含むことを特徴とするクロック切り替え回路。

**【請求項 2】**

請求項1において、

前記第1のクロックの立ち上がりエッジまたは立ち下がりエッジを含む前後の所与の期間は、前記第1のクロックの立ち上がりエッジまたは立ち下がりエッジの前の1クロック期間と、前記第1のクロックの立ち上がりエッジまたは立ち下がりエッジの後ろの1クロック期間で構成されることを特徴とするクロック切り替え回路。

**【請求項 3】**

請求項1または2において、

前記合成クロック生成回路は、

前記切り替え実行信号と前記第2のクロックが入力される第1のOR回路と、

前記第1のOR回路の出力を前記第1のクロックに基づいて保持し、保持された信号を出力することで、前記クロック切り替え用合成クロックを前記切り替え指示信号生成回路及び前記第1のセレクタに出力する合成クロック用フリップフロップと、

を含み、

前記第1のレベルはローレベルであり、前記第2のレベルはハイレベルであり、

前記第1のOR回路は、前記第2のクロックがローレベルである期間であっても、前記クロック切り替え実行信号がアクティブに設定された場合はハイレベルの信号を前記合成クロック用フリップフロップに出力することを特徴とするクロック切り替え回路。

**【請求項 4】**

請求項1乃至3のいずれかにおいて、

前記切り替え指示信号生成回路は、前記切り替え実行信号と前記合成クロック生成回路の出力が入力される第1のAND回路を含み、

前記第1のAND回路は、前記切り替え実行信号がアクティブであり、且つ、前記合成クロック生成回路の前記合成クロックがハイレベルである場合に、前記切り替え指示信号をアクティブに設定することを特徴とするクロック切り替え回路。

**【請求項 5】**

請求項1または2において、

前記合成クロック生成回路は、

前記切り替え実行信号と前記第2のクロックが入力される第2のAND回路と、

前記第2のAND回路の出力を前記第1のクロックに基づいて保持し、保持された信号を出力することで、前記クロック切り替え用合成クロックを前記切り替え指示信号生成回路及び前記第1のセレクタに出力する合成クロック用フリップフロップと、

を含み、

前記第1のレベルはハイレベルであり、前記第2のレベルはローレベルであり、

前記第2のAND回路は、前記第2のクロックがハイレベルである期間であっても、前

10

20

30

40

50

記クロック切り替え実行信号がアクティブに設定された場合はローレベルの信号を前記合成クロック用フリップフロップに出力することを特徴とするクロック切り替え回路。

【請求項 6】

請求項 1 または 2 または 5 のいずれかにおいて、

前記切り替え指示信号生成回路は、前記切り替え実行信号と前記合成クロック生成回路の出力が入力される第 2 の OR 回路を含み、

前記第 2 の OR 回路は、前記切り替え実行信号がアクティブであり、且つ、前記合成クロック生成回路の前記合成クロックがローレベルである場合に、前記切り替え指示信号をアクティブに設定することを特徴とするクロック切り替え回路。

【請求項 7】

10

請求項 1 乃至 6 のいずれかにおいて、

前記クロック選択信号生成回路は、

選択信号用セレクタと、

前記選択信号用セレクタの出力信号を前記第 1 のクロックに基づいて保持し、保持された信号を前記選択信号用セレクタ及び前記第 1 のセレクタに前記第 1 のクロック選択信号として出力する選択信号用フリップフロップとを含み、

前記選択信号用セレクタは、前記選択信号用フリップフロップからの前記第 1 のクロック選択信号と、クロック切り替え時に前記第 1 のセレクタに選択されるクロックを決定するための第 2 のクロック選択信号とを受け、前記切り替え指示信号生成回路からの前記切り替え指示信号に基づいて、前記第 1 のクロック選択信号または前記第 2 のクロック選択信号のいずれかを前記選択信号用フリップフロップに出力することを特徴とするクロック切り替え回路。

20

【請求項 8】

請求項 7 において、

前記選択信号用セレクタは、前記切り替え指示信号生成回路の前記切り替え指示信号がアクティブに設定されると、前記第 2 のクロック選択信号を前記選択信号用フリップフロップに出力することを特徴とするクロック切り替え回路。

【請求項 9】

請求項 1 乃至 8 のいずれかにおいて、

複数のクロックを受け、前記複数のクロックのうちの任意のクロックを選択して、前記第 2 のクロックとして前記合成クロック生成回路に出力する第 2 のセレクタをさらに含むことを特徴とするクロック切り替え回路。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、クロック切り替え回路に関する。

【背景技術】

【0002】

例えば複数のクロックを受け、切り替え信号に基づいて複数のクロックのうちの 1 つを出力するセレクタでは、一方のクロックから他方のクロックに切り替える際にハザードと称されるパルス幅の狭いクロックパルスが生じる場合がある。このハザードは、例えば一方のクロックのレベルがハイレベルであって、他方のクロックのレベルがローレベルである時に、切り替え信号がアクティブに設定されクロック切り替えが行われた場合に生じる可能性がある。これは、セレクタ内での切り替え信号の遅延に起因する。このハザードは他の回路の誤動作等を引き起こす可能性があるため、ハザードを生じさせないために一方のクロック及び他方のクロックの双方がハイレベルまたはローレベルである期間でクロック切り替えを行う必要があり、従来のクロック切り替え回路は短い時間でクロック切り替えを行うことができなかった。

40

【0003】

また、他の手法によってハザードの発生を防止するクロック切り替え回路が考案されて

50

いる（特許文献1）。特許文献1に記載されているクロック切り替え回路は、クロック切り替え時にまず一方のクロック出力を停止し、所定の時間が経過した後に他方のクロックを出力するような構成である。

#### 【0004】

特許文献1を含む従来のクロック切り替え回路は、ハザードの発生を防止することができるが、クロック切り替えに要する時間が長くなってしまうという課題を有する。

#### 【特許文献1】特開平8-107406号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

本発明は、以上のような技術的課題に鑑みてなされたものであり、その目的とするところは、ハザードを生じることなく早いタイミングでのクロック切り替えが可能なクロック切り替え回路を提供することにある。

#### 【課題を解決するための手段】

#### 【0006】

本発明は、第1のクロックと、前記第1のクロックとは周波数が異なる第2のクロックと、前記第1のクロックと前記第2のクロックを切り替えるためのクロック切り替え実行信号とを受け、前記第2のクロックが第1のレベルである期間にクロック切り替え実行信号がアクティブになった場合に、前記第1のクロックの立ち上がりエッジまたは立ち下がりエッジを含む前後の所与の期間、前記第2のクロックのレベルを第2のレベルに固定してクロック切り替え用合成クロックとして出力する合成クロック生成回路と、前記クロック切り替え用合成クロックと、前記クロック切り替え実行信号とを受け、クロックの切り替え指示信号を出力する切り替え指示信号生成回路と、前記切り替え指示信号がアクティブになった場合に、第1のクロック選択信号のレベルを変化させるクロック選択信号生成回路と、前記クロック選択信号生成回路からの前記第1のクロック選択信号のレベルに応じて、前記第1のクロックまたは前記クロック切り替え用合成クロックのいずれかを選択して出力する第1のセレクタを含むクロック切り替え回路に関する。 20

#### 【0007】

本発明によれば、クロック切り替えを行う際、前記第1のクロックの立ち上がりエッジまたは立ち下がりエッジを含む前後の所与の期間、前記第2のクロックのレベルを第2のレベルに固定することができるので、ハザードを生じさせることなく短い期間でクロック切り替えを完了することができる。 30

#### 【0008】

また、本発明では、前記第1のクロックの立ち上がりエッジまたは立ち下がりエッジを含む前後の所与の期間は、前記第1のクロックの立ち上がりエッジまたは立ち下がりエッジの前の1クロック期間と、前記第1のクロックの立ち上がりエッジまたは立ち下がりエッジの後ろの1クロック期間で構成されてもよい。

#### 【0009】

本発明によれば、第1のクロックの少なくとも2クロックの期間でハザードを生じさせることなくクロック切り替えを完了することができる。 40

#### 【0010】

また、本発明では、前記合成クロック生成回路は、前記切り替え実行信号と前記第2のクロックが入力される第1のOR回路と、前記第1のOR回路の出力を前記第1のクロックに基づいて保持し、保持された信号を出力することで、前記クロック切り替え用合成クロックを前記切り替え指示信号生成回路及び前記第1のセレクタに出力する合成クロック用フリップフロップと、を含み、前記第1のレベルはローレベルであり、前記第2のレベルはハイレベルであり、前記第1のOR回路は、前記第2のクロックがローレベルである期間であっても、前記クロック切り替え実行信号がアクティブに設定された場合はハイレベルの信号を前記合成クロック用フリップフロップに出力するようにしてよい。

#### 【0011】

本発明によれば、切り替え実行信号がアクティブに設定されると、合成クロック生成回路は、合成クロック生成回路の出力を前記所定の期間、ハイレベルに固定することができる、第2のクロックがローレベルである期間であってもクロック切り替えを行うことができる。即ち、第2のクロックがローレベルである期間であっても、第2のクロックのレベルがハイレベルになるまで待機する必要なしに、短い期間でクロック切り替えを完了することができる。

【0012】

また、本発明では、前記切り替え指示信号生成回路は、前記切り替え実行信号と前記合成クロック生成回路の出力が入力される第1のAND回路を含み、前記第1のAND回路は、前記切り替え実行信号がアクティブであり、且つ、前記合成クロック生成回路の前記合成クロックがハイレベルである場合に、前記切り替え指示信号をアクティブに設定するようにしてもよい。10

【0013】

本発明によれば、クロック切り替え用合成クロックのレベルがハイレベルである期間にクロック切り替え指示信号をアクティブに設定することができるので、クロック切り替えの際にハザードの発生を防止できる。

【0014】

また、本発明では、前記合成クロック生成回路は、前記切り替え実行信号と前記第2のクロックが入力される第2のAND回路と、前記第2のAND回路の出力を前記第1のクロックに基づいて保持し、保持された信号を出力することで、前記クロック切り替え用合成クロックを前記切り替え指示信号生成回路及び前記第1のセレクタに出力する合成クロック用フリップフロップと、を含み、前記第1のレベルはハイレベルであり、前記第2のレベルはローレベルであり、前記第2のAND回路は、前記第2のクロックがハイレベルである期間であっても、前記クロック切り替え実行信号がアクティブに設定された場合はローレベルの信号を前記合成クロック用フリップフロップに出力するようにしてもよい。20

【0015】

本発明によれば、切り替え実行信号がアクティブに設定されると、合成クロック生成回路は、合成クロック生成回路の出力を前記所定の期間、ローレベルに固定することができる、第2のクロックがハイレベルである期間であってもクロック切り替えを行うことができる。即ち、第2のクロックがハイレベルである期間であっても、第2のクロックのレベルがローレベルになるまで待機する必要なしに、短い期間でクロック切り替えを完了することができる。30

【0016】

また、本発明では、前記切り替え指示信号生成回路は、前記切り替え実行信号と前記合成クロック生成回路の出力が入力される第2のOR回路を含み、前記第2のOR回路は、前記切り替え実行信号がアクティブであり、且つ、前記合成クロック生成回路の前記合成クロックがローレベルである場合に、前記切り替え指示信号をアクティブに設定するようにしてもよい。

【0017】

本発明によれば、クロック切り替え用合成クロックのレベルがローレベルである期間にクロック切り替え指示信号をアクティブに設定することができるので、クロック切り替えの際にハザードの発生を防止できる。40

【0018】

また、本発明では、前記クロック選択信号生成回路は、選択信号用セレクタと、前記選択信号用セレクタの出力信号を前記第1のクロックに基づいて保持し、保持された信号を前記選択信号用セレクタ及び前記第1のセレクタに前記第1のクロック選択信号として出力する選択信号用フリップフロップとを含み、前記選択信号用セレクタは、前記選択信号用フリップフロップからの前記第1のクロック選択信号と、クロック切り替え時に前記第1のセレクタに選択されるクロックを決定するための第2のクロック選択信号とを受け、前記切り替え指示信号生成回路からの前記切り替え指示信号に基づいて、前記第1のクロ50

ック選択信号または前記第2のクロック選択信号のいずれかを前記選択信号用フリップフロップに出力するようにしてもよい。

#### 【0019】

本発明によれば、第1のクロック及びクロック切り替え用合成クロックのレベルが双方ともロー・レベルまたはハイ・レベルである間にクロック切り替えを行うことができるので、ハザードの発生を確実に防止でき、短い期間でクロック切り替えを完了することができる。

#### 【0020】

また、本発明では、前記選択信号用セレクタは、前記切り替え指示信号生成回路の前記切り替え指示信号がアクティブに設定されると、前記第2のクロック選択信号を前記選択信号用フリップフロップに出力するようにしてもよい。 10

#### 【0021】

また、本発明では、複数のクロックを受け、前記複数のクロックのうちの任意のクロックを選択して、前記第2のクロックとして前記合成クロック生成回路に出力する第2のセレクタをさらに含むようにしてもよい。

#### 【発明を実施するための最良の形態】

#### 【0022】

以下、本発明の一実施形態について、図面を参照して説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成のすべてが本発明の必須構成要件であるとは限らない。 20

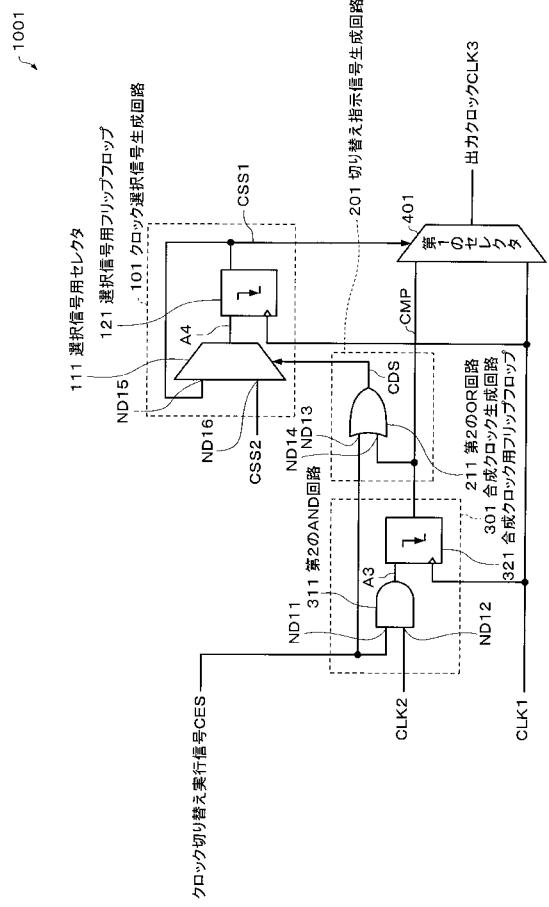

#### 【0023】

##### 1. 第1実施形態に係るクロック切り替え回路

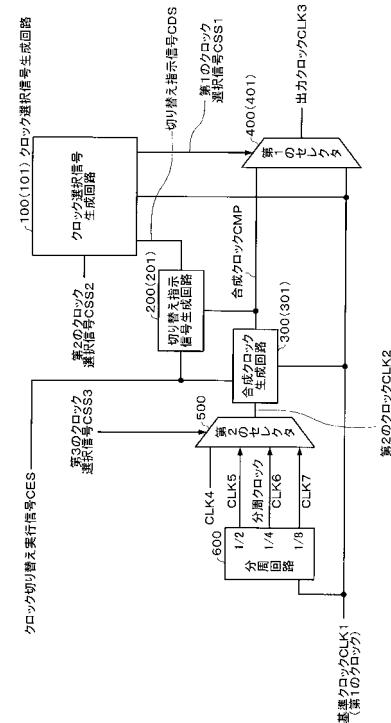

図1は、第1実施形態に係るクロック切り替え回路1000を示すブロック図である。クロック切り替え回路1000は、第1のクロック選択信号CSS1を出力するクロック選択信号生成回路100と、クロック切り替え実行信号CES及び合成クロックCMPに基づいて切り替え指示信号CDSを出力する切り替え指示信号生成回路200とを含む。また、クロック切り替え回路1000は、第1のクロック（基準クロックとも言う）CLK1、第2のクロックCLK2及びクロック切り替え実行信号CESに基づいて合成クロックCMP（広義にはクロック切り替え用合成クロック）を出力する合成クロック生成回路300を含む。 30

#### 【0024】

また、クロック切り替え回路1000は、出力クロックCLK3を出力する第1のセレクタ400と、第3のクロック選択信号CSS3に基づいて第2のクロックCLK2を出力する第2のセレクタ500とを含む。また、クロック切り替え回路1000は、第1のクロックCLK1に基づいて複数の分周クロックを出力する分周回路600を含む。

#### 【0025】

クロック切り替え回路1000は上記の構成に限定されず、クロック切り替え回路1000は、例えば第2のセレクタ500や分周回路600を含まない構成でもよい。

#### 【0026】

クロック選択信号生成回路100は、切り替え指示信号生成回路200から出力される切り替え指示信号CDS、第1のクロックCLK1（広義には第1のクロック）及び第2のクロック選択信号CSS2に基づいて、第1のセレクタ400に第1のクロック選択信号CSS1を出力する。なお、第2のクロック選択信号CSS2は、クロック切り替え時に第1のセレクタ400から出力クロックCLK3として出力されるクロックを、合成クロックCMPまたは第1のクロックCLK1のいずれかに決定するための信号である。例えば、第2のクロック選択信号CSS2がハイ・レベルに設定されている場合には、クロック選択信号生成回路100は、第1のセレクタ400が合成クロックCMPを出力クロックCLK3として出力するように、第1のクロック選択信号CSS1のレベルを例えばハイ・レベルに設定する。即ち、図1のクロック切り替え回路1000では、第2のクロック選択信号CSS2がハイ・レベルに設定されると、第1のクロック選択信号CSS1がハイ 40

レベルに設定され、結果として合成クロック C M P が第 1 のセレクタ 4 0 0 から出力される。但し、上記の構成は一例であって、クロック切り替え回路 1 0 0 0 は、第 2 のクロック選択信号 C S S 2 がハイレベルに設定された場合に第 1 のセレクタ 4 0 0 から第 1 のクロック C L K 1 が出力されるような構成でもよい。また、クロック切り替え回路 1 0 0 0 は、第 1 のクロック選択信号 C S S 1 がハイレベルに設定された場合、第 1 のセレクタ 4 0 0 から第 1 のクロック C L K 1 が出力されるような構成でもよい。

#### 【 0 0 2 7 】

合成クロック生成回路 3 0 0 は、第 2 のクロック C L K 2 を受け、クロック切り替え実行信号 C E S がアクティブに設定されると、例えば第 1 のクロック C L K 1 の立ち上がりエッジに応じて合成クロック C M P を例えばハイレベルに設定する。合成クロック生成回路 3 0 0 は、クロック切り替え実行信号 C E S がアクティブに設定されている期間に基づいて、合成クロック C M P のレベルの例えばハイレベルである期間を設定する。10

#### 【 0 0 2 8 】

クロック切り替え実行信号 C E S がノンアクティブに設定されている場合には、合成クロック生成回路 3 0 0 は、第 2 のクロック C L K 2 に基づいて合成クロック C M P を出力する。この場合、合成クロック生成回路 3 0 0 は、例えば第 2 のクロック C L K 2 を遅延させて合成クロック C M P として出力するが、例えば第 2 のクロック C L K 2 をそのまま合成クロック C M P として出力してもよい。20

#### 【 0 0 2 9 】

第 2 のセレクタ 5 0 0 は、分周回路 6 0 0 から出力される複数のクロックを受け、第 3 のクロック選択信号 C S S 3 に基づいて複数のクロックのいずれかを選択して、第 2 のクロック C L K 2 として合成クロック生成回路 3 0 0 に出力する。20

#### 【 0 0 3 0 】

分周回路 6 0 0 は、第 1 のクロック C L K 1 を分周することで、複数のクロックを生成し第 2 のセレクタ 5 0 0 に出力する。例えば、分周回路 6 0 0 は、3 つの分周クロック C L K 5 ~ C L K 7 を生成し、第 2 のセレクタ 5 0 0 に出力するがこれに限定されない。例えば分周回路 6 0 0 は、1 つの分周クロック、2 つの分周クロック、4 つの分周クロック等、n ( n は自然数 ) 個の分周クロックを生成し出力するようにしてもよい。なお、クロック C L K 4 は、常時一定レベル、例えばハイレベルに設定される。これは、第 2 のセレクタ 5 0 0 は例えば4 つの入力が設けられているのに対して、分周回路 6 0 0 は3 つの分周クロック C L K 5 ~ C L K 7 を第 2 のセレクタ 5 0 0 に出力するためである。以下の図において同符号のものは同様の意味を表す。30

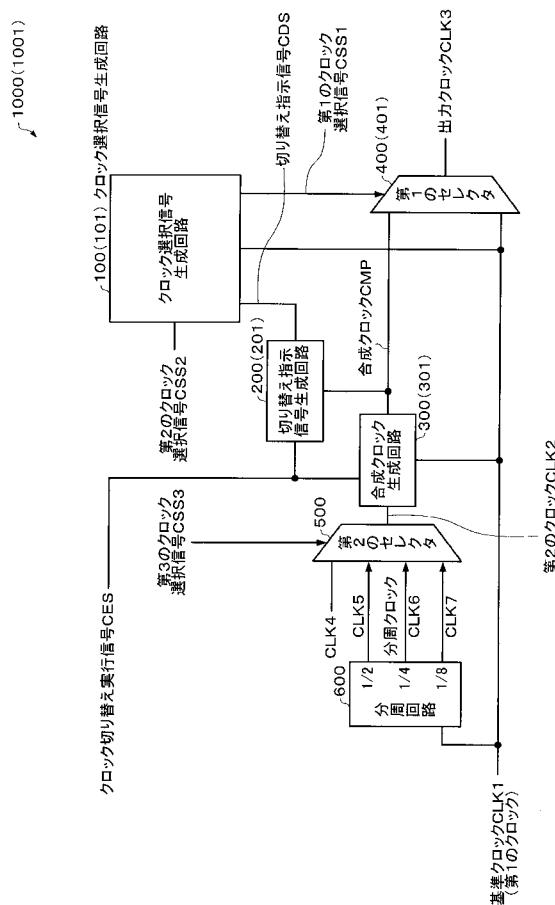

#### 【 0 0 3 1 】

図 2 は、クロック切り替え回路 1 0 0 0 の一部を示す回路図である。クロック選択信号生成回路 1 0 0 は、選択信号用セレクタ 1 1 0 と、選択信号用フリップフロップ 1 2 0 を含むがこれに限定されない。例えば、クロック選択信号生成回路 1 0 0 は選択信号用セレクタ 1 1 0 を含まない構成でもよい。

#### 【 0 0 3 2 】

切り替え指示信号生成回路 2 0 0 は、第 1 の A N D 回路 2 1 0 を含む。合成クロック生成回路 3 0 0 は、第 1 の O R 回路 3 1 0 と、合成クロック用フリップフロップ 3 2 0 を含むが、これに限定されない。例えば、合成クロック生成回路 3 0 0 は、第 1 の O R 回路 3 1 0 を含まない構成でもよい。40

#### 【 0 0 3 3 】

例えば合成クロック C M P が第 1 のセレクタ 4 0 0 から出力クロック C L K 3 として出力されている状態から、第 1 のセレクタ 4 0 0 の出力クロック C L K 3 を第 1 のクロック C L K 1 に切り替えたい場合を説明する。この場合、クロック切り替えを行う際にクロック切り替え実行信号 C E S がアクティブに設定され、第 2 のクロック選択信号 C S S 2 は例えばローレベルに設定される。

#### 【 0 0 3 4 】

例えば第 1 の O R 回路 3 1 0 の入力ノード N D 1 及び第 1 の A N D 回路 2 1 0 の入力ノ50

ード N D 3 にはアクティブな信号、例えばハイレベルの信号が入力される。これにより、第 1 の O R 回路 3 1 0 はハイレベルの信号を合成クロック用フリップフロップ 3 2 0 に出力する。

#### 【 0 0 3 5 】

合成クロック用フリップフロップ 3 2 0 は、例えば第 1 のクロック C L K 1 の立ち上がりエッジに応じて第 1 の O R 回路 3 1 0 から入力されたハイレベルの信号を保持し、例えば第 1 のクロック C L K 1 の次の立ち上がりエッジが合成クロック用フリップフロップ 3 2 0 に入力されるまで、ハイレベルの信号を例えば第 1 の A N D 回路 2 1 0 の入力ノード N D 4 及び第 1 のセレクタ 4 0 0 に出力する。

#### 【 0 0 3 6 】

この場合、第 1 の A N D 回路 2 1 0 の入力ノード N D 3 及び N D 4 にはハイレベルの信号が入力されるので、第 1 の A N D 回路 2 1 0 は例えばハイレベルの信号を選択信号用セレクタ 1 1 0 に出力する。選択信号用セレクタ 1 1 0 は、第 1 の A N D 回路 2 1 0 の出力信号のレベルに応じて、選択信号用セレクタ 1 1 0 の入力ノード N D 5 、 N D 6 のそれぞれに入力される信号のいずれかを選択して選択信号用フリップフロップ 1 2 0 に出力する。例えば、選択信号用セレクタ 1 1 0 は、第 1 の A N D 回路 2 1 0 からハイレベルの信号を受けると、入力ノード N D 6 に入力される第 2 のクロック選択信号 C S S 2 を選択し選択信号用フリップフロップ 1 2 0 に出力する。

#### 【 0 0 3 7 】

このとき第 1 のクロック選択信号 C S S 2 は、ローレベルに設定されているので、例えば選択信号用フリップフロップ 1 2 0 は第 1 のクロック C L K 1 の立ち上がりエッジに応じて選択信号用セレクタ 1 1 0 の出力信号であるローレベルの信号を保持し、次の第 1 のクロック C L K 1 の例えば立ち上がりエッジが入力されるまで、ローレベルの信号を選択信号用セレクタ 1 1 0 の入力ノード N D 5 及び第 1 のセレクタ 4 0 0 に出力する。

#### 【 0 0 3 8 】

第 1 のセレクタ 4 0 0 は、クロック選択信号生成回路 1 0 0 の選択信号用フリップフロップ 1 2 0 からローレベルの信号（広義には第 1 のクロック選択信号 C S S 1 ）を受け、合成クロック C M P から第 1 のクロック C L K 1 に切り替えて、第 1 のクロック C L K 1 を出力クロック C L K 3 として出力する。

#### 【 0 0 3 9 】

上述のように出力クロック C L K 3 が設定されるクロック切り替え回路 1 0 0 0 では、クロック切り替えを行う場合には、クロック切り替え実行信号 C E S がアクティブ（例えばハイレベルの信号）に設定される。さらに、クロック切り替え回路 1 0 0 0 の出力クロック C L K 3 を第 1 のクロック C L K 1 に設定したい場合は、第 2 のクロック選択信号 C S S 2 は例えばローレベルの信号に設定される。また、クロック切り替え回路 1 0 0 0 の出力クロック C L K 3 を合成クロック C M P （広義には第 2 のクロック）に設定したい場合は、第 2 のクロック選択信号 C S S 2 は例えばハイレベルの信号に設定される。

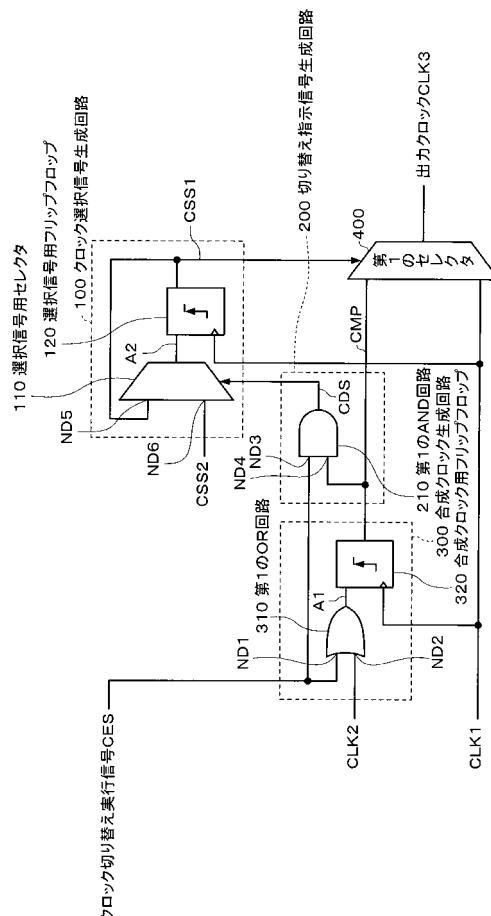

#### 【 0 0 4 0 】

図 3 は、第 1 のセレクタ 4 0 0 の構成を示す回路図である。第 1 のセレクタ 4 0 0 は、O R 回路 O R 1 、 O R 2 、 A N D 回路 A N D 1 を含む。O R 回路 O R 1 の入力ノード N D 7 には、合成クロック C M P が入力され、入力ノード N D 8 には、第 1 のクロック選択信号 C S S 1 の反転信号が入力される。また、O R 回路 O R 2 の入力ノード N D 9 には、第 1 のクロック選択信号 C S S 1 が入力され、入力ノード N D 1 0 には、第 1 のクロック C L K 1 が入力される。A N D 回路 A N D 1 は、O R 回路 O R 1 、 O R 2 の出力を受けて、出力クロック C L K 3 を出力する。

#### 【 0 0 4 1 】

例えば、第 1 のクロック選択信号 C S S 1 がハイレベルに設定された場合、O R 回路 O R 1 の入力ノード N D 8 には、反転された信号であるローレベルの信号が入力され、O R 回路 O R 2 の入力ノード N D 9 には、ハイレベルの信号が入力される。このとき、O R 回路 O R 1 の出力信号のレベルは、合成クロック C M P のレベルに応じて変化し、O R 回路

OR2の出力信号のレベルは、ノードND9にハイレベルの信号が入力されている間は、常にハイレベルとなる。これにより、AND回路AND1の出力レベルは合成クロックCMPの信号レベルに応じて変化する。即ち、出力クロックCLK3は、合成クロックCMPに基づいたクロック信号となる。

#### 【0042】

反対に、第1のクロック選択信号CSS1がローレベルに設定された場合、OR回路OR1の入力ノードND8には、反転された信号であるハイレベルの信号が入力され、OR回路OR2の入力ノードND9には、ローレベルの信号が入力される。このとき、OR回路OR1の出力信号のレベルは、ノードND8にハイレベルの信号が入力されている間は、常にハイレベルとなり、OR回路OR2の出力信号のレベルは、第1のクロックCLK1のレベルに応じて変化する。これにより、AND回路AND1の出力レベルは第1のクロックCLK1の信号レベルに応じて変化する。即ち、出力クロックCLK3は、第1のクロックCLK1に基づいたクロック信号となる。

#### 【0043】

上述のように、第1のセレクタ400は、第1のクロック選択信号CSS1に基づいて合成クロックCMP及び第1のクロックCLK1を切り替えて、出力クロックCLK3として出力する。

#### 【0044】

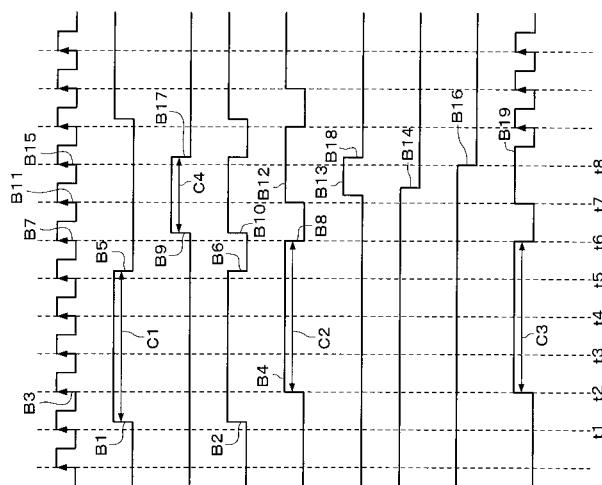

次に図2と図4を参照しながらクロック切り替え回路1000の動作を説明する。図4は、第2のクロックCLK2から第1のクロック（基準クロック）CLK1に切り替える際のクロック切り替え実行信号CESや切り替え指示信号CDS等を示すタイミングチャートである。なお、図4では第2のクロックCLK2として例えば1/8分周クロックが入力されているが、これに限定されない。第2のクロックCLK2は、第1のクロックCLK1に基づいて分周された分周クロックであればよく、例えば1/2分周クロックでもよいし、1/16分周クロックでもよい。また、図4の符号t1～t8は、時間を示す。

#### 【0045】

例えば図1の第2のセレクタ500から出力された第2のクロックCLK2が、図2の第1のOR回路310の入力ノードND2に入力される。ノードND2に入力されている信号が図4のB1で示されるように立ち上がると、図2の第1のOR回路310の出力信号A1は図4のB2に示されるように立ち上がる。そして、出力信号A1を受ける合成クロック用フリップフロップ320は、B3に示される第1のクロックCLK1の立ち上がりエッジに応じて、B4に示されるハイレベルの信号を第1のAND回路210及び第1のセレクタ400に出力する。なお、時間t1における第1のOR回路310の出力信号A1はローレベルの信号であるため、時間t1からt2の期間では、合成クロック用フリップフロップ320の出力信号はローレベルである。

#### 【0046】

その後、ノードND2に入力されている信号がB5に示されるように立ち下がると、図2の第1のOR回路310の出力信号A1は図4のB6に示されるように立ち下がる。そして、出力信号A1を受ける合成クロック用フリップフロップ320は、第1のAND回路210及び第1のセレクタ400に出力する信号を、B7に示される第1のクロックCLK1の立ち上がりエッジに応じて、B8に示されるように立ち下げる。なお、時間t2、t3、t4、t5における第1のOR回路310の出力信号A1はハイレベルの信号であるため、時間t2からt6の期間では、合成クロック用フリップフロップ320の出力信号はハイレベルである。

#### 【0047】

時間t1からt8までの期間では、第1のクロック選択信号CSS1はハイレベルに設定されているため、この期間での第1のセレクタ400から出力される出力クロックCLK3は、合成クロック用フリップフロップ320の出力、即ち合成クロックCMPである。ここで、時間t1からt7までの期間において、第2のクロックCLK2のパルス幅C1、合成クロックCMPのパルス幅C2及び出力クロックCLK3のパルス幅C3を比較

すると、すべて同じことが図4からわかる。つまり、このときの合成クロックCMPは、第2のクロックCLK2が合成クロック生成回路300によって遅延されて出力されたクロックであり、この合成クロックCMPが第1のセレクタ400から出力クロックCLK3として出力される。

#### 【0048】

ここで、例えば、B9に示されるようにクロック切り替え実行信号CESが立ち上がり、アクティブに設定されると、第1のOR回路310の入力ノードND1及び第1のAND回路210の入力ノードND3にはハイレベルの信号が入力される。これによって、B10に示されるように第1のOR回路310の出力信号A1は立ち上がり、ハイレベルの信号に設定される。第1のOR回路310の出力信号A1を受ける合成クロック用フリップフロップ320は、第1のクロックCLK1のB11に示される立ち上がりエッジに応じて、B12に示されるハイレベルの信号を第1のAND回路210の入力ノードND4及び第1のセレクタ400に出力する。10

#### 【0049】

切り替え実行信号CESがアクティブに設定されることで、時間t7からt8において第1のAND回路210の入力ノードND3、ND4にハイレベルの信号が入力され、切り替え指示信号CDSはB13のようにアクティブ（ハイレベル）に設定される。選択信号用セレクタ110はアクティブな切り替え指示信号CDSを受け、選択信号用セレクタ110のノードND6に入力される第2のクロック選択信号CSS2を選択信号用セレクタ110の出力信号A2として選択信号用フリップフロップ120に出力する。第2のクロックCLK2から第1のクロックCLK1に切り替える際には第2のクロック選択信号CSS2は例えばローレベルに設定される。即ち、選択信号用セレクタ110は、アクティブな切り替え指示信号CDSを受け、ローレベルに設定されている第2のクロック選択信号CSS2に基づいて、図4のB14に示されるように出力信号A2を立ち下げる。20

#### 【0050】

ローレベルに設定された出力信号A2を受ける選択信号用フリップフロップ120は、第1のクロックCLK1のB15に示される立ち上がりエッジに応じて、B16に示されるように第1のクロック選択信号CSS1を立ち下げ、ローレベルに設定された第1のクロック選択信号CSS1を選択信号用セレクタ110の入力ノードND5及び第1のセレクタ400に出力する。なお、B17にしめされるようにクロック切り替え実行信号CESが立ち下げられることで、切り替え指示信号CDSもB18に示されるように立ち下げる。これにより、クロック切り替え実行信号CESがローレベルに設定されている間は、選択信号用セレクタ110は入力ノードND5に入力される第1のクロック選択信号CSS1を選択信号用フリップフロップ120に出力するため、再度クロック切り替え実行信号CESがアクティブに設定されるまでは、第1のクロック選択信号CSS1はローレベルに維持される。30

#### 【0051】

第1のセレクタ400は、ローレベルに設定された第1のクロック選択信号CSS1を受け、出力クロックCLK3をB19に示されるように第1のクロックCLK1に切り替える。図4によると、時間t8以降、出力クロックCLK3は第1のクロックCLK1に切り替えられていることがわかる。切り替えを行う際のクロック切り替え実行信号CESは、B9に示されるようにアクティブに設定されている。つまり、B9に示されるように立ち上げられてから、B19に示されるようにクロック切り替えが行われるまでに要した期間はC4に示される期間であり、第1のクロックCLK1のおよそ2クロックである。40

#### 【0052】

さらに、図5を用いて、第2のクロックCLK2から第1のクロックCLK1に切り替える際の動作を説明する。図5は、図4とほぼ同様のタイミングチャートであるが、クロック切り替え実行信号CESをアクティブに設定するタイミングが図4とは異なる場合のタイミングチャートである。図4のタイミングチャートと同様に、B20に示される第2のクロックCLK2が図2の第1のOR回路310のノードND2に入力されるので、B50

21で示されるハイレベルの出力信号A1が合成クロック用フリップフロップ320に出力される。時間t2での第1のクロックCLK1の例えれば立ち上がりエッジに応じて、合成クロック用フリップフロップ320からB22に示されるハイレベルの信号が合成クロックCMPとして出力される。

#### 【0053】

例えれば切り替え実行信号CESがB23で示されるように立ち上げられ、B24で示されるように立ち下げられると、C5で示される期間において図2の第1のAND回路210の入力ノードND3、ND4のレベルが双方ともハイレベルに設定されるので、切り替え指示信号CDSはB25で示されるように立ち上がり、B26で示されるように立ち下がる。

10

#### 【0054】

この切り替え指示信号CDSを受ける選択信号用セレクタ110は、例えばローレベルに設定された第2のクロック選択信号CSS2に基づいてローレベルの信号を選択信号用フリップフロップ120に出力するので、選択信号用セレクタ110の出力信号A2は、B27に示されるように立ち下げられ、ローレベルの信号に設定される。時間t5での第1のクロックCLK1の例えれば立ち上がりエッジに応じて、選択信号用フリップフロップ120はローレベルの出力信号A2に基づいてローレベルの信号を第1のクロック選択信号CSS1として第1のセレクタ400に出力する。これにより、第1のクロック選択信号CSS1はB28に示されるように立ち下げられ、ローレベルの信号に設定される。

#### 【0055】

ローレベルの第1のクロック選択信号CSS1を受け、第1のセレクタ400はB29に示されるように出力クロックCLK3を第2のクロックCLK2から第1のクロックCLK1に切り替えて出力する。ここで、クロック切り替え実行信号CESは、B23でアクティブに設定されている。つまり、B23に示されるように立ち上げられてから、B29に示されるようにクロック切り替えが行われるまでに要した期間はC5に示される期間、第1のクロックCLK1のおよそ1クロックである。

20

#### 【0056】

つまり、第2のクロックCLK2がハイレベルである間にクロック切り替え実行信号CESがアクティブに設定されると、第1のクロックCLK1のおよそ1クロックの期間でクロック切り替えが完了する。また、第2のクロックCLK2がローレベルである間にクロック切り替え実行信号CESがアクティブに設定されても、第1のクロックCLK1のおよそ2クロックの期間でクロック切り替えが完了する。なお、いずれの場合も第1のクロック選択信号CSS1のレベルが変更される時は、第1のクロックCLK1及び合成クロックCMPがハイレベルであるので、クロック切り替え回路1000は第1のセレクタ400からパルス幅の短いハザードが出力されることを防止できる。

30

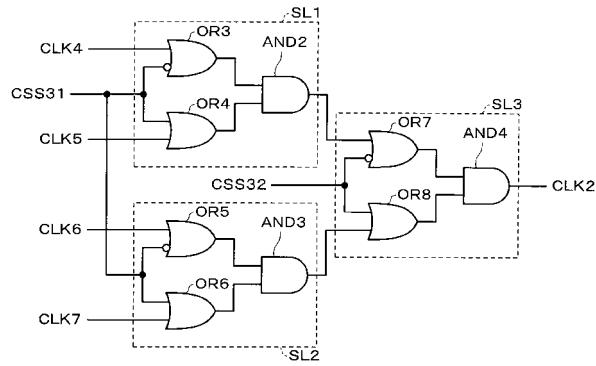

#### 【0057】

図6は、図1の第2のセレクタ500を示す回路図である。第2のセレクタ500はセレクタSL1～SL3で構成され、各セレクタSL1～SL3は例えば2つのOR回路及び1つのAND回路を含む。セレクタSL1、SL2の各出力はセレクタSL3に出力される。第1実施形態では、クロックCLK4のレベルはハイレベルに固定される。図1の第3のクロック選択信号CSS3は、例えばクロック選択信号CSS31、CSS32で構成される。

40

#### 【0058】

例えれば、クロック選択信号CSS31及びCSS32がハイレベルに設定されると、セレクタSL1ではOR回路OR3、OR4の出力はハイレベルとなりAND回路AND2の出力はハイレベルとなるので、セレクタSL1の出力はハイレベルとなる。このとき、セレクタSL2では、OR回路OR5の出力はクロックCLK6に基づく出力となり、OR回路OR6はハイレベルとなるので、AND回路AND3の出力はクロックCLK6となる。これにより、セレクタSL3のOR回路OR7にはハイレベルの信号が入力され、OR回路OR8にはクロックCLK6が入力されるので、セレクタSL3の出力はクロック

50

ク CLK 6 となる。

【 0 0 5 9 】

このように、クロック選択信号 CSS31、CSS32 のレベルの設定の組み合わせにより、第 2 のセレクタ 500 の出力クロック CLK2 が切り替えられる。

【 0 0 6 0 】

第 1 実施形態では、第 2 のセレクタ 500 は、一例として 3 つの分周クロック CLK5 ~ CLK7 を切り替えるが、これに限定されない。より複数の場合のクロックを切り替える場合は、セレクタ SL1、SL2 の各入力に例えばセレクタ SL1 と同様のセレクタを設ければよい。

【 0 0 6 1 】

また、各セレクタ SL1 ~ SL3 は、図 8 で示されるような例えば 2 つの AND 回路及び 1 つの OR 回路で構成されたセレクタでもよい。

【 0 0 6 2 】

2 . 第 2 実施形態に係るクロック切り替え回路

第 2 実施形態に係るクロック切り替え回路 1001 は、図 1 の第 1 実施形態のクロック選択信号生成回路 100、切り替え指示信号生成回路 200、合成クロック生成回路 300 及び第 1 のセレクタ 400 の構成が異なる。その他の構成は第 1 実施形態と同様である。クロック切り替え回路 1001 は、クロック選択信号生成回路 101、切り替え指示信号生成回路 201、合成クロック生成回路 301 及び第 1 のセレクタ 401 を含むがこれに限定されない。クロック切り替え回路 1001 は、例えばクロック選択信号生成回路 101 を省略する構成でもよい。

【 0 0 6 3 】

図 7 は、クロック切り替え回路 1001 の一部を示す回路図である。クロック選択信号生成回路 101 は、選択信号用セレクタ 111 と、選択信号用フリップフロップ 121 を含むがこれに限定されない。例えば、クロック選択信号生成回路 101 は選択信号用セレクタ 111 を含まない構成でもよい。

【 0 0 6 4 】

切り替え指示信号生成回路 201 は、第 2 の OR 回路 211 を含む。合成クロック生成回路 301 は、第 2 の AND 回路 311 と、合成クロック用フリップフロップ 321 を含むが、これに限定されない。例えば、合成クロック生成回路 301 は、第 2 の AND 回路 311 を含まない構成でもよい。

【 0 0 6 5 】

例えば合成クロック CMP が第 1 のセレクタ 401 から出力クロック CLK3 として出力されている状態から、第 1 のセレクタ 401 の出力クロック CLK3 を第 1 のクロック CLK1 に切り替えたい場合を説明する。この場合、クロック切り替えを行う際にクロック切り替え実行信号 CES がアクティブに設定され、第 2 のクロック選択信号 CSS2 は例えばハイレベルに設定される。

【 0 0 6 6 】

例えば第 2 の AND 回路 311 の入力ノード ND11 及び第 2 の OR 回路 211 の入力ノード ND13 にはアクティブな信号、例えばローレベルの信号が入力される。これにより、第 2 の AND 回路 311 はローレベルの信号を合成クロック用フリップフロップ 321 に出力する。

【 0 0 6 7 】

合成クロック用フリップフロップ 321 は、例えば第 1 のクロック CLK1 の立ち下がりエッジに応じて第 2 の AND 回路 311 から入力されたローレベルの信号を保持し、例えば第 1 のクロック CLK1 の次の立ち下がりエッジが合成クロック用フリップフロップ 321 に入力されるまで、ローレベルの信号を例えば第 2 の OR 回路 211 の入力ノード ND14 及び第 1 のセレクタ 401 に出力する。

【 0 0 6 8 】

この場合、第 2 の OR 回路 211 の入力ノード ND13 及び ND14 にはローレベルの

10

20

30

40

50

信号が入力されるので、第2のOR回路211は例えばローレベルの信号を選択信号用セレクタ111に出力する。選択信号用セレクタ111は、第2のOR回路211の出力信号のレベルに応じて、選択信号用セレクタ111の入力ノードND15、ND16のそれぞれに入力される信号のいずれかを選択して選択信号用フリップフロップ121に出力する。例えば、選択信号用セレクタ111は、第2のOR回路211からローレベルの信号を受けると、入力ノードND16に入力される第2のクロック選択信号CSS2を選択し選択信号用フリップフロップ121に出力する。

#### 【0069】

このとき第1のクロック選択信号CSS2は、ハイレベルに設定されているので、例えば選択信号用フリップフロップ121は第1のクロックCLK1の立ち下がりエッジに応じて選択信号用セレクタ111の出力信号であるハイレベルの信号を保持し、次の第1のクロックCLK1の例えば立ち下がりエッジが入力されるまで、ハイレベルの信号を選択信号用セレクタ111の入力ノードND15及び第1のセレクタ401に出力する。10

#### 【0070】

第1のセレクタ401は、クロック選択信号生成回路101の選択信号用フリップフロップ121からハイレベルの信号（広義には第1のクロック選択信号CSS1）を受け、合成クロックCMPから第1のクロックCLK1に切り替えて、第1のクロックCLK1を出力クロックCLK3として出力する。

#### 【0071】

上述のように出力クロックCLK3が設定されるクロック切り替え回路1001では、クロック切り替えを行う場合には、クロック切り替え実行信号CESがアクティブ（例えばローレベルの信号）に設定される。さらに、クロック切り替え回路1001の出力クロックCLK3を第1のクロックCLK1に設定したい場合は、第2のクロック選択信号CSS2は例えばハイレベルの信号に設定される。また、クロック切り替え回路1001の出力クロックCLK3を合成クロックCMP（広義には第2のクロック）に設定したい場合は、第2のクロック選択信号CSS2は例えばローレベルの信号に設定される。20

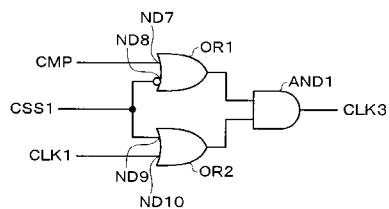

#### 【0072】

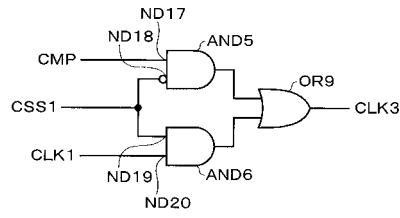

図8は、第1のセレクタ401の構成を示す回路図である。第1のセレクタ401は、OR回路OR9、AND回路AND5、AND6を含む。AND回路AND5の入力ノードND17には、合成クロックCMPが入力され、入力ノードND18には、第1のクロック選択信号CSS1の反転信号が入力される。また、AND回路AND6の入力ノードND19には、第1のクロック選択信号CSS1が入力され、入力ノードND20には、第1のクロックCLK1が入力される。OR回路OR9は、AND回路AND5、AND6の出力を受けて、出力クロックCLK3を出力する。30

#### 【0073】

例えば、第1のクロック選択信号CSS1がローレベルに設定された場合、AND回路AND5の入力ノードND18には、反転された信号であるハイレベルの信号が入力され、AND回路AND6の入力ノードND19には、ローレベルの信号が入力される。このとき、AND回路AND5の出力信号のレベルは、合成クロックCMPのレベルに応じて変化し、AND回路AND6の出力信号のレベルは、ノードND19にローレベルの信号が入力されている間は、常にローレベルとなる。これにより、OR回路OR9の出力レベルは合成クロックCMPの信号レベルに応じて変化する。即ち、出力クロックCLK3は、合成クロックCMPに基づいたクロック信号となる。40

#### 【0074】

反対に、第1のクロック選択信号CSS1がハイレベルに設定された場合、AND回路AND5の入力ノードND18には、反転された信号であるローレベルの信号が入力され、AND回路AND6の入力ノードND19には、ハイレベルの信号が入力される。このとき、AND回路AND5の出力信号のレベルは、ノードND18にローレベルの信号が入力されている間は、常にローレベルとなり、AND回路AND6の出力信号のレベルは、第1のクロックCLK1のレベルに応じて変化する。これにより、OR回路OR9の出50

カレルは第1のクロックCLK1の信号レベルに応じて変化する。即ち、出力クロックCLK3は、第1のクロックCLK1に基づいたクロック信号となる。

#### 【0075】

上述のように、第1のセレクタ401は、第1のクロック選択信号CSS1に基づいて合成クロックCMP及び第1のクロックCLK1を切り替えて、出力クロックCLK3として出力する。

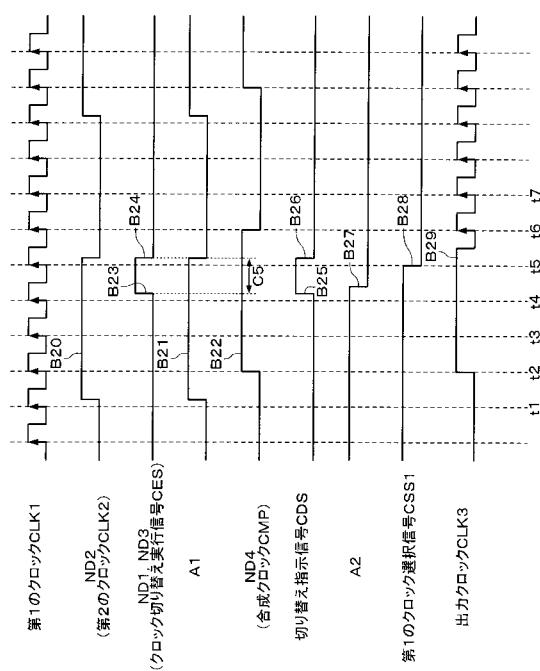

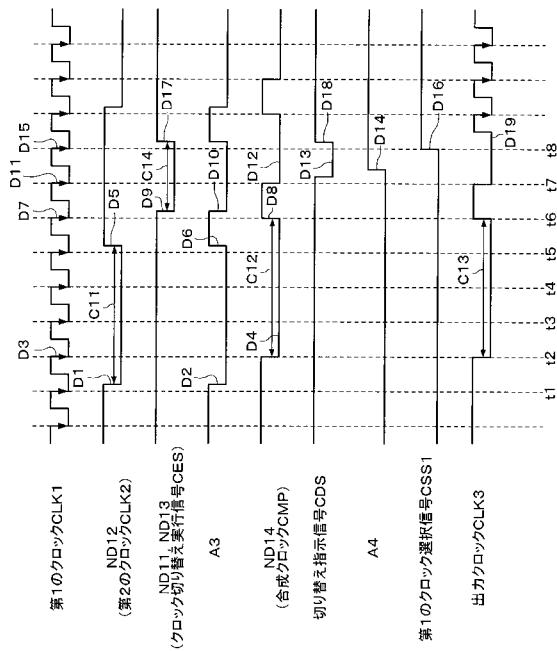

#### 【0076】

次に図7と図9を参照しながらクロック切り替え回路1001の動作を説明する。図9は、第2のクロックCLK2から第1のクロック（基準クロック）CLK1に切り替える際のクロック切り替え実行信号CESや切り替え指示信号CDS等を示すタイミングチャートである。なお、図9では第2のクロックCLK2として例えば1/8分周クロックが入力されているが、これに限定されない。第2のクロックCLK2は、第1のクロックCLK1に基づいて分周された分周クロックであればよく、例えば1/2分周クロックでもよいし、1/16分周クロックでもよい。

10

#### 【0077】

例えば図1の第2のセレクタ500から出力された第2のクロックCLK2が、図7の第2のAND回路311の入力ノードND12に入力される。ノードND12に入力されている信号が図9のD1で示されるように立ち上がると、図7の第2のAND回路311の出力信号A3は図9のD2に示されるように立ち上がる。そして、出力信号A3を受ける合成クロック用フリップフロップ321は、D3に示される第1のクロックCLK1の立ち下がりエッジに応じて、D4に示されるローレベルの信号を第2のOR回路211及び第1のセレクタ401に出力する。なお、時間t1における第2のAND回路311の出力信号A3はハイレベルの信号であるため、時間t1からt2の期間では、合成クロック用フリップフロップ321の出力信号はハイレベルである。

20

#### 【0078】

その後、ノードND12に入力されている信号がD5に示されるように立ち上がると、図7の第2のAND回路311のノードND11にはハイレベルに設定されたクロック切り替え実行信号CESが入力されているので出力信号A3は図9のD6に示されるように立ち上がる。そして、出力信号A3を受ける合成クロック用フリップフロップ321は、第2のOR回路211及び第1のセレクタ401に出力する信号を、D7に示される第1のクロックCLK1の立ち下がりエッジに応じて、D8に示されるように立ち上げる。なお、時間t2、t3、t4、t5における第2のAND回路311の出力信号A3はローレベルの信号であるため、時間t2からt6の期間では、合成クロック用フリップフロップ321の出力信号はローレベルである。

30

#### 【0079】

時間t1からt8までの期間では、第1のクロック選択信号CSS1はローレベルに設定されているため、この期間での第1のセレクタ401から出力される出力クロックCLK3は、合成クロック用フリップフロップ321の出力、即ち合成クロックCMPである。ここで、時間t1からt7までの期間において、第2のクロックCLK2のパルス幅C11、合成クロックCMPのパルス幅C12及び出力クロックCLK3のパルス幅C13を比較すると、すべて同じことが図9からわかる。つまり、このときの合成クロックCMPは、第2のクロックCLK2が合成クロック生成回路301によって遅延されて出力されたクロックであり、この合成クロックCMPが第1のセレクタ401から出力クロックCLK3として出力される。

40

#### 【0080】

ここで、例えば、D9に示されるようにクロック切り替え実行信号CESが立ち下がり、アクティブに設定されると、第2のAND回路311の入力ノードND11及び第2のOR回路211の入力ノードND13にはローレベルの信号が入力される。これによって、D10に示されるように第2のAND回路311の出力信号A3は立ち下がり、ローレベルの信号に設定される。第2のAND回路311の出力信号A3を受ける合成クロック

50

用フリップフロップ321は、第1のクロックCLK1のD11に示される立ち下がりエッジに応じて、D12に示されるローレベルの信号を第2のOR回路211の入力ノードND14及び第1のセレクタ401に出力する。

#### 【0081】

切り替え実行信号CESがアクティブに設定されることで、時間t7からt8において第2のOR回路211の入力ノードND13、ND4にローレベルの信号が入力され、切り替え指示信号CDSはD13のようにアクティブ（ローレベル）に設定される。選択信号用セレクタ111はアクティブな切り替え指示信号CDSを受け、選択信号用セレクタ111のノードND16に入力される第2のクロック選択信号CSS2を選択信号用セレクタ111の出力信号A4として選択信号用フリップフロップ121に出力する。第2のクロックCLK2から第1のクロックCLK1に切り替える際には第2のクロック選択信号CSS2は例えればハイレベルに設定される。即ち、選択信号用セレクタ111は、アクティブな切り替え指示信号CDSを受け、ハイレベルに設定されている第2のクロック選択信号CSS2に基づいて、図9のD14に示されるように出力信号A4を立ち上げる。

#### 【0082】

ハイレベルに設定された出力信号A4を受ける選択信号用フリップフロップ121は、第1のクロックCLK1のD15に示される立ち下がりエッジに応じて、D16に示されるように第1のクロック選択信号CSS1を立ち上げ、ハイレベルに設定された第1のクロック選択信号CSS1を選択信号用セレクタ111の入力ノードND15及び第1のセレクタ401に出力する。なお、D17にしめされるようにクロック切り替え実行信号CESが立ち上げられることで、切り替え指示信号CDSもD18に示されるように立ち上げられる。これにより、クロック切り替え実行信号CESがハイレベルに設定されている間は、選択信号用セレクタ111は入力ノードND15に入力される第1のクロック選択信号CSS1を選択信号用フリップフロップ121に出力するため、再度クロック切り替え実行信号CESがアクティブに設定されるまでは、第1のクロック選択信号CSS1はハイレベルに維持される。

#### 【0083】

第1のセレクタ401は、ハイレベルに設定された第1のクロック選択信号CSS1を受け、出力クロックCLK3をD19に示されるように第1のクロックCLK1に切り替える。図9によると、時間t8以降、出力クロックCLK3は第1のクロックCLK1に切り替えられていることがわかる。切り替えを行う際のクロック切り替え実行信号CESは、D9に示されるようにアクティブに設定されている。つまり、D9に示されるように立ち下げられてから、D19に示されるようにクロック切り替えが行われるまでに要した期間はC14に示される期間であり、第1のクロックCLK1のおよそ2クロックである。

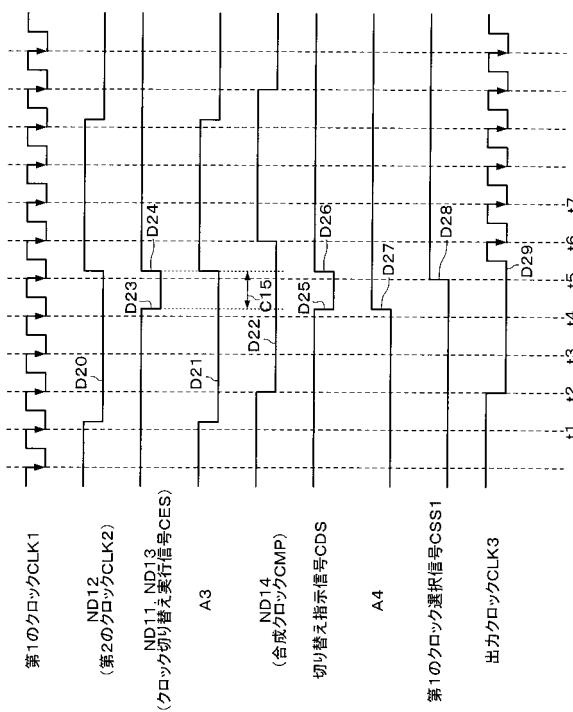

#### 【0084】

さらに、図10を用いて、第2のクロックCLK2から第1のクロックCLK1に切り替える際の動作を説明する。図10は、図9とほぼ同様のタイミングチャートであるが、クロック切り替え実行信号CESをアクティブに設定するタイミングが図9とは異なる場合のタイミングチャートである。図9のタイミングチャートと同様に、D20に示される第2のクロックCLK2が図7の第2のAND回路311のノードND12に入力されるので、D21で示されるローレベルの出力信号A3が合成クロック用フリップフロップ321に出力される。時間t2での第1のクロックCLK1の例えは立ち下がりエッジに応じて、合成クロック用フリップフロップ321からD22に示されるローレベルの信号が合成クロックCMPとして出力される。

#### 【0085】

例えは切り替え実行信号CESがD23で示されるように立ち下げられ、D24で示されるように立ち上げられると、C15で示される期間において図7の第2のOR回路211の入力ノードND13、ND4のレベルが双方ともローレベルに設定されるので、切り替え指示信号CDSはD25で示されるように立ち下がり、D26で示されるように立ち

上がる。

【0086】

この切り替え指示信号 CDS を受ける選択信号用セレクタ 111 は、例えばハイレベルに設定された第 2 のクロック選択信号 CSS2 に基づいて、ハイレベルの信号を選択信号用フリップフロップ 121 に出力するので、選択信号用セレクタ 111 の出力信号 A4 は、D27 に示されるように立ち上げられ、ハイレベルの信号に設定される。時間 t5 での第 1 のクロック CLK1 の例えれば立ち下がりエッジに応じて、選択信号用フリップフロップ 121 はハイレベルの出力信号 A4 に基づいてハイレベルの信号を第 1 のクロック選択信号 CSS1 として第 1 のセレクタ 401 に出力する。これにより、第 1 のクロック選択信号 CSS1 は D28 に示されるように立ち上げられ、ハイレベルの信号に設定される。

10

【0087】

ハイレベルの第 1 のクロック選択信号 CSS1 を受け、第 1 のセレクタ 401 は D29 に示されるように出力クロック CLK3 を第 2 のクロック CLK2 から第 1 のクロック CLK1 に切り替えて出力する。ここで、クロック切り替え実行信号 CES は、D23 でアクティブに設定されている。つまり、D23 に示されるように立ち上げられてから、D29 に示されるようにクロック切り替えが行われるまでに要した期間は C15 に示される期間、第 1 のクロック CLK1 のおよそ 1 クロックである。

【0088】

つまり、第 2 のクロック CLK2 がローレベルである間にクロック切り替え実行信号 CES がアクティブに設定されると、第 1 のクロック CLK1 のおよそ 1 クロックの期間でクロック切り替えが完了する。また、第 2 のクロック CLK2 がハイレベルである間にクロック切り替え実行信号 CES がアクティブに設定されても、第 1 のクロック CLK1 のおよそ 2 クロックの期間でクロック切り替えが完了する。なお、いずれの場合も第 1 のクロック選択信号 CSS1 のレベルが変更される時は、第 1 のクロック CLK1 及び合成クロック CMP がローレベルであるので、クロック切り替え回路 1001 は第 1 のセレクタ 401 からパルス幅の短いハザードが出力されることを防止できる。

20

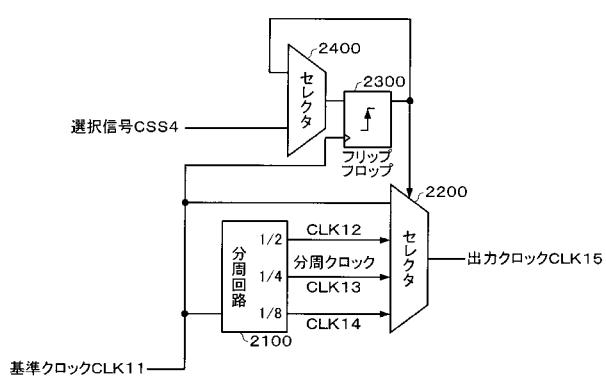

【0089】

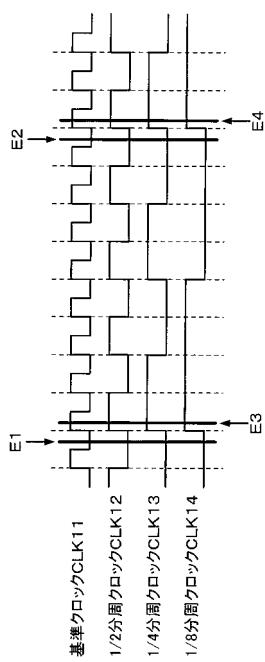

### 3. 第 1 実施形態及び第 2 実施形態と、比較例との対比

図 11 は、第 1 実施形態及び第 2 実施形態のクロック切り替え回路 1000、1001 に対する比較例であるクロック切り替え回路 2000 を示す回路図である。クロック切り替え回路 2000 は、基準クロック CLK11 に基づいて複数の分周クロックを出力する分周回路 2100、セレクタ 2200、フリップフロップ 2300 及びセレクタ 2400 を含むが、これに限定されない。クロック切り替え回路 2000 は、例えはフリップフロップ 2300 またはセレクタ 2400 を省略する構成でもよい。分周回路 2100 は、基準クロック CLK11 に基づいて、例えは 1/2 分周クロック CLK12、1/4 分周クロック CLK13、1/8 分周クロック CLK14 をセレクタ 2200 に出力する。

30

【0090】

図 12 は、図 11 のクロック切り替え回路 2000 において、クロック切り替えを行うタイミングを示すためのタイミングチャートである。クロック切り替え回路 2000 のセレクタ 2200 が、例えは図 8 で示されているようなセレクタを含む構成である場合、クロック切り替えは、各クロック CLK11 ~ CLK14 がすべてローレベルである期間内（例えは E1、E2 で示されるタイミング）に行われる必要がある。この場合、その他の期間でクロック切り替えを行ってしまうと、例えはセレクタ内のインバータ等によって信号遅延が生じ、出力クロック CLK15 にはパルス幅の狭いハザードが含まれてしまう。

40

【0091】

また、クロック切り替え回路 2000 のセレクタ 2200 が、例えは図 3 で示されているようなセレクタを含む構成である場合、クロック切り替えは、各クロック CLK11 ~ CLK14 がすべてハイレベルである期間内（例えは E3、E4 で示されるタイミング）に行われる必要がある。この場合、その他の期間でクロック切り替えを行ってしまうと、例えはセレクタ内のインバータ等によって信号遅延が生じ、出力クロック CLK15 にはパルス幅の狭いハザードが含まれてしまう。

50

にはパルス幅の狭いハザードが含まれてしまう。

#### 【0092】

図12から明らかなように、例えばセレクタ2200が図8のセレクタを含む場合、E1のタイミングでクロック切り替えを行えなかった場合は、E2のタイミングまでクロック切り替えを行えない。同様に、セレクタ2200が図3のセレクタを含む場合のクロック切り替えが可能なタイミングは、E3のタイミングの次はE4のタイミングである。いずれの場合も、クロック切り替え可能なタイミングは、基準クロックCLK11の8クロック分の間隔があり、クロック切り替えを素早く行うことができない。また、セレクタ2200に入力されるクロックの数が、図12では4つであるが、この入力されるクロックの数が増加すると、前述のクロック切り替えタイミングの間隔はさらに長くなってしまう。また、分周クロックの周期がより長い場合も、前述のクロック切り替えタイミングの間隔をさらに長くしてしまう。10

#### 【0093】

一方、第1実施形態及び第2実施形態のクロック切り替え回路1000、1001は、いずれもクロック切り替え実行信号がアクティブに設定されてから、第1のクロックCLK1の1クロックまたは2クロックで示される期間でクロック切り替えを完了できる。これは、比較例のクロック切り替え回路2000に比べて、短い期間でクロック切り替えを完了することができる意味する。例えば、第2のクロックCLK2が第1のクロックCLK1が分周された1/8分周クロックである場合であっても、クロック切り替え回路1000、1001は、第1のクロックCLK1のおよそ1クロックまたは2クロックでクロック切り替えを完了することができる。さらに、クロック切り替え回路1000、1001では、クロック切り替えされるクロックの数によらず、第1のクロックCLK1の1クロックまたは2クロックで示される期間でクロック切り替えを完了できる。また、クロック切り替え回路1000、1001では、入力される分周クロックの周期の長さにもよらず、第1のクロックCLK1の1クロックまたは2クロックで示される期間でクロック切り替えを完了できる。20

#### 【0094】

上述のように、第1実施形態及び第2実施形態のクロック切り替え回路1000、1001は、複数のクロックに対して、ハザードの発生を防止しながら短い期間でクロック切り替えを完了することができる。30

#### 【0095】

なお、本発明は、上記実施形態で説明されたものに限らず、種々の変形実施が可能である。例えば、明細書又は図面中の記載において広義や同義な用語（第1のクロックCLK1、第2のクロックCLK2等）として引用された用語は、明細書又は図面中の他の記載においても広義や同義な用語（基準クロックCLK1、分周クロック等）に置き換えることができる。

#### 【図面の簡単な説明】

#### 【0096】

【図1】第1実施形態または第2実施形態に係るクロック切り替え回路を示すブロック図。40

【図2】第1実施形態に係るクロック切り替え回路の一部を示す回路図。

【図3】第1実施形態に係る第1のセレクタを示す回路図。

【図4】第1実施形態に係るクロック切り替え回路の動作を示すタイミングチャート。

【図5】第1実施形態に係るクロック切り替え回路の他の動作を示すタイミングチャート。45

【図6】第1実施形態または第2実施形態に係るクロック切り替え回路の第2のセレクタを示す回路図。

【図7】第2実施形態に係るクロック切り替え回路の一部を示すブロック図。

【図8】第2実施形態に係る第1のセレクタを示す回路図。

【図9】第2実施形態に係るクロック切り替え回路の動作を示すタイミングチャート。50

【図10】第2実施形態に係るクロック切り替え回路の他の動作を示すタイミングチャート。

【図11】第1実施形態及び第2実施形態に係る比較例のクロック切り替え回路を示すブロック図。

【図12】比較例の動作を示すタイミングチャート。

【符号の説明】

【0097】

100、101 クロック選択信号生成回路、110、111 選択信号用セレクタ、

120、121 選択信号用フリップフロップ、

200、201 切り替え指示信号生成回路、210 第1のAND回路、

211 第2のOR回路、300、301 合成クロック生成回路、

310 第1のOR回路、311 第2のAND回路、

320、321 合成クロック用フリップフロップ、400 第1のセレクタ、

401 第1のセレクタ、500 第2のセレクタ、

1000、1001 クロック切り替え回路、CDS 切り替え指示信号、

CES クロック切り替え実行信号、CLK1 第1のクロック、

CLK2 第2のクロック、CMP クロック切り替え用合成クロック、

CSS1 第1のクロック選択信号、CSS2 第2のクロック選択信号

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

フロントページの続き

【要約の続き】

む。

【選択図】 図 1