(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5535494号

(P5535494)

(45) 発行日 平成26年7月2日(2014.7.2)

(24) 登録日 平成26年5月9日(2014.5.9)

(51) Int.Cl.

H01L 25/10 (2006.01)

F 1

H01L 25/14

Z

H01L 25/11 (2006.01)

H01L 25/18 (2006.01)

請求項の数 5 (全 27 頁)

(21) 出願番号 特願2009-39213 (P2009-39213)

(22) 出願日 平成21年2月23日(2009.2.23)

(65) 公開番号 特開2010-199129 (P2010-199129A)

(43) 公開日 平成22年9月9日(2010.9.9)

審査請求日 平成24年1月13日(2012.1.13)

前置審査

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 内山 健太

長野県長野市小島田町80番地 新光電気

工業株式会社内

審査官 石野 忠志

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

電極パッドが設けられた電極パッド形成面、及び該電極パッド形成面の反対側に位置する背面を有する電子部品と、

前記電極パッド形成面を露出する第1の面、及び前記背面を露出する第2の面を有し、前記電子部品の側面を封止する絶縁部材と、

前記第1の面上及び前記電極パッド形成面上に積層された複数の絶縁層と配線パターンとを有する多層配線構造体と、

前記絶縁部材を前記第1の面から前記第2の面にかけて貫通する貫通電極と、を有し、

複数の前記絶縁層は、前記第1の面及び前記電極パッド形成面を直接被覆する第1絶縁層を含み、

複数の前記配線パターンは、前記第1絶縁層の前記電子部品と反対側の面上に設けられた配線と、前記第1絶縁層内に設けられたビアとが一体に形成された第1配線パターンを含み、

前記第1配線パターンの前記ビアが、前記電極パッド及び前記貫通電極と直接接続され、

前記貫通電極が前記絶縁部材の前記第1の面から突出し、前記貫通電極の前記第1の面側の端面と前記電極パッドの接続面とが面一であり、

前記電子部品の前記電極パッド形成面と前記絶縁部材の前記第1の面とが面一である半導体装置。

10

20

**【請求項 2】**

前記多層配線構造体の最上層に、前記第1配線パターンと電気的に接続された外部接続用パッドが設けられている請求項1記載の半導体装置。

**【請求項 3】**

前記絶縁部材の前記第2の面に露出する前記貫通電極の端面が、外部接続用の面である請求項1又は2記載の半導体装置。

**【請求項 4】**

前記第1絶縁層には、前記貫通電極の端面と前記電子部品の電極パッドを露出する開口部が設けられており、

前記ピアは、前記開口部内に設けられている請求項1乃至3の何れか一項記載の半導体装置。 10

**【請求項 5】**

前記絶縁部材の前記第2の面側の前記貫通電極の端面が、前記絶縁部材の前記第2の面及び前記電子部品の背面に対して面一となるように形成されている請求項1乃至4の何れか一項記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置に関する。

**【背景技術】****【0002】**

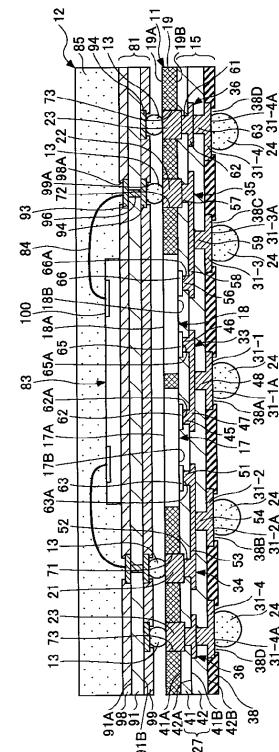

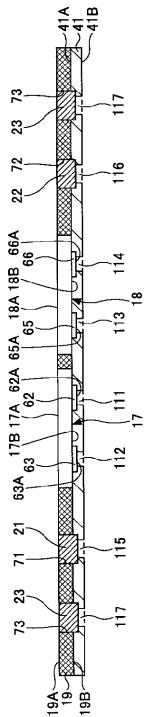

図1は、従来の電子装置の断面図である。

**【0003】**

図1を参照するに、従来の電子装置200は、半導体装置201, 202と、内部接続端子203とを有する。半導体装置201は、配線基板211と、電子部品212と、アンダーフィル樹脂213と、外部接続端子214とを有する。

**【0004】**

配線基板211は、板状とされた多層配線構造体である。配線基板211は、積層された絶縁層216, 217と、配線パターン219, 228, 229と、パッド221と、ソルダーレジスト層222, 226と、外部接続用パッド223, 224とを有する。絶縁層216は、絶縁層217の上面217Aに設けられている。 30

**【0005】**

配線パターン219及びパッド221は、絶縁層216の上面216Aに設けられている。配線パターン219は、ソルダーレジスト層222から露出されたパッド部232, 233を有する。パッド221は、ソルダーレジスト層222から露出されている。

**【0006】**

ソルダーレジスト層222は、絶縁層216の上面216Aに設けられている。外部接続用パッド223, 224は、絶縁層217の下面217Bに設けられている。外部接続用パッド223, 224の下面是、ソルダーレジスト層226から露出されている。

**【0007】**

ソルダーレジスト層226は、絶縁層217の下面217Bに設けられている。配線パターン228, 229は、積層された絶縁層216, 217に内設されている。配線パターン228は、パッド部233及び外部接続用パッド223と接続されている。配線パターン229は、パッド221及び外部接続用パッド224と接続されている。

**【0008】**

電子部品212は、半導体装置201と半導体装置202との間に配置されている。電子部品212は、電極パッド236を有する。電極パッド236は、バンプ237(例えば、はんだバンプ)を介して、パッド部232と電気的に接続されている。

**【0009】**

アンダーフィル樹脂213は、電子部品212と配線基板211との隙間を充填するよ 50

うに設けられている。外部接続端子 214 は、外部接続用パッド 223, 224 の下面に設けられている。

#### 【0010】

半導体装置 202 は、半導体装置 201 の上方に配置されている。半導体装置 202 は、配線基板 241 と、電子部品 243 と、モールド樹脂 246 を有する。配線基板 241 は、板状とされており、パッド 251, 252, 254 を有する。パッド 251 は、パッド部 233 と対向すると共に、内部接続端子 203 を介して、パッド部 233 と電気的に接続されている。パッド 252 は、パッド 221 と対向すると共に、内部接続端子 203 を介して、パッド 221 と電気的に接続されている。パッド 254 は、パッド 251 又はパッド 252 と電気的に接続されている。

10

#### 【0011】

電子部品 243 は、配線基板 241 上に接着されると共に、金属ワイヤ 244 を介して、パッド 254 と電気的に接続されている。モールド樹脂 246 は、配線基板 241 上に設けられている。モールド樹脂 246 は、金属ワイヤ 244 及び電子部品 243 を封止している。

#### 【0012】

内部接続端子 203 は、電子部品 212 と半導体装置 202 とが接触しないような大きさ（高さ）とされている。内部接続端子 203 の高さは、例えば、 $200 \mu\text{m}$  とすることができます（例えば、特許文献 1 参照。）。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0013】

【特許文献 1】特開平 6 - 13541 号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0014】

しかしながら、従来の半導体装置 201 では、バンプ 237 を介して、配線基板 211 の上面側に配置された電子部品 212 と配線基板 211（多層配線構造体）とを電気的に接続させていたため、半導体装置 201 の高さ方向のサイズが大型化してしまうという問題があった。

30

#### 【0015】

また、バンプ 237 を介して、電子部品 212 と配線基板 211 とを電気的に接続させる場合、隣り合うバンプ 237 が接触しないようにバンプ 237 を配置する必要があるため、バンプ 237 の配設ピッチを小さくすることが困難であり、バンプ 237 と接続される配線パターン 219 を微細かつ高密度に配置することができないという問題があった。

#### 【0016】

さらに、従来の電子装置 200 では、半導体装置 201 と半導体装置 202 とを電気的に接続する内部接続端子 203 の高さを、電子部品 212 の高さとバンプ 237 の高さとを加算した値よりも大きくする必要があるため、電子装置 200 の厚さ方向のサイズが大型化してしまうという問題があった。

40

#### 【0017】

なお、半導体装置 201 及び電子装置 200 の厚さ方向のサイズが大型化してしまうという問題は、電子部品 212 と配線基板 211 とをワイヤボンディング接続した場合にも発生する。

#### 【0018】

そこで本発明は、上述した問題点に鑑みなされたものであり、電子部品の電極パッドと接続される配線パターンを微細かつ高密度に配置することができると共に、厚さ方向のサイズの小型化を図ることのできる半導体装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0019】

50

本発明の一観点によれば、電極パッドが設けられた電極パッド形成面、及び該電極パッド形成面の反対側に位置する背面を有する電子部品と、前記電極パッド形成面を露出する第1の面、及び前記背面を露出する第2の面を有し、前記電子部品の側面を封止する絶縁部材と、前記第1の面上及び前記電極パッド形成面上に積層された複数の絶縁層と配線パターンとを有する多層配線構造体と、前記絶縁部材を前記第1の面から前記第2の面にかけて貫通する貫通電極と、を有し、複数の前記絶縁層は、前記第1の面及び前記電極パッド形成面を直接被覆する第1絶縁層を含み、複数の前記配線パターンは、前記第1絶縁層の前記電子部品と反対側の面上に設けられた配線と、前記第1絶縁層内に設けられたピアとが一体に形成された第1配線パターンを含み、前記第1配線パターンの前記ピアが、前記電極パッド及び前記貫通電極と直接接続され、前記貫通電極が前記絶縁部材の前記第1の面から突出し、前記貫通電極の前記第1の面側の端面と前記電極パッドの接続面とが面一であり、前記電子部品の前記電極パッド形成面と前記絶縁部材の前記第1の面とが面一である半導体装置が提供される。

【発明の効果】

【0031】

本発明によれば、電子部品の電極パッドと接続される配線パターンを微細かつ高密度に配置できると共に、半導体装置の厚さ方向のサイズの小型化を図ることができる。

【図面の簡単な説明】

【0032】

【図1】従来の電子装置の断面図である。

【図2】本発明の第1の実施の形態に係る電子装置の断面図である。

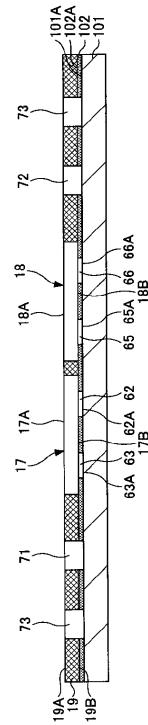

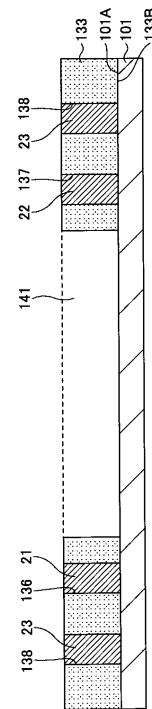

【図3】本発明の第1の実施の形態に係る半導体装置の製造工程（その1）を示す図である。

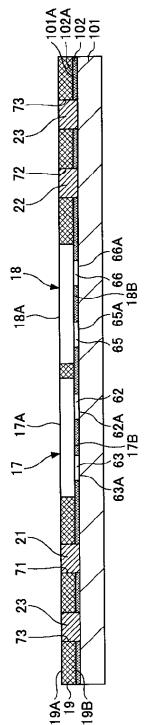

【図4】本発明の第1の実施の形態に係る半導体装置の製造工程（その2）を示す図である。

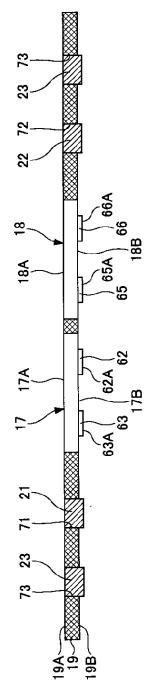

【図5】本発明の第1の実施の形態に係る半導体装置の製造工程（その3）を示す図である。

【図6】本発明の第1の実施の形態に係る半導体装置の製造工程（その4）を示す図である。

【図7】本発明の第1の実施の形態に係る半導体装置の製造工程（その5）を示す図である。

【図8】本発明の第1の実施の形態に係る半導体装置の製造工程（その6）を示す図である。

【図9】本発明の第1の実施の形態に係る半導体装置の製造工程（その7）を示す図である。

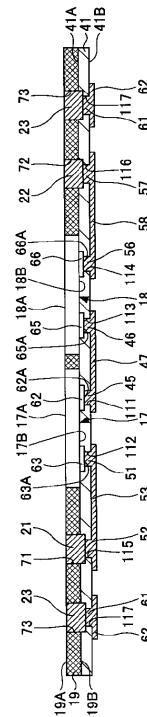

【図10】本発明の第1の実施の形態に係る半導体装置の製造工程（その8）を示す図である。

【図11】本発明の第1の実施の形態に係る半導体装置の製造工程（その9）を示す図である。

【図12】本発明の第1の実施の形態に係る半導体装置の製造工程（その10）を示す図である。

【図13】本発明の第1の実施の形態に係る半導体装置の製造工程（その11）を示す図である。

【図14】本発明の第1の実施の形態に係る半導体装置の製造工程（その12）を示す図である。

【図15】本発明の第2の実施の形態に係る電子装置の断面図である。

【図16】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図（その1）である。

【図17】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図（その2）で

10

20

30

40

50

ある。

【図18】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図（その3）である。

【図19】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図（その4）である。

【図20】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図（その5）である。

【図21】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図（その6）である。

【図22】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図（その7）である。 10

【図23】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図（その8）である。

#### 【発明を実施するための形態】

##### 【0033】

以下、図面に基づいて本発明の実施の形態について説明する。

##### 【0034】

（第1の実施の形態）

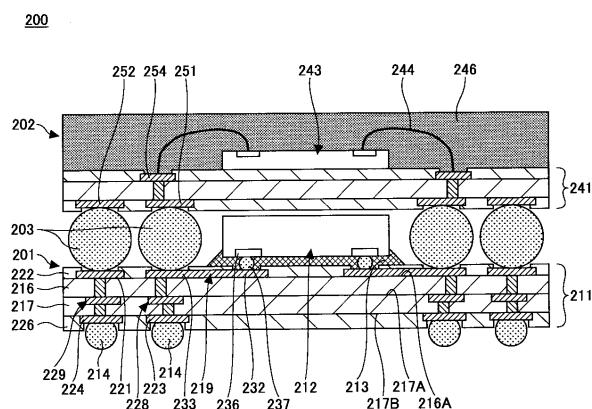

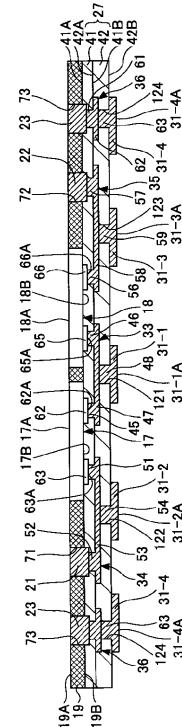

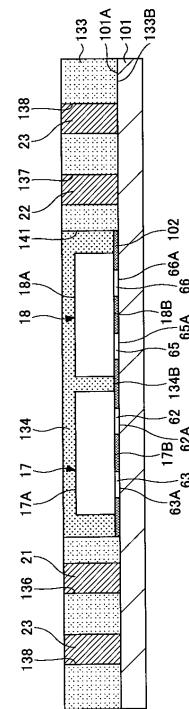

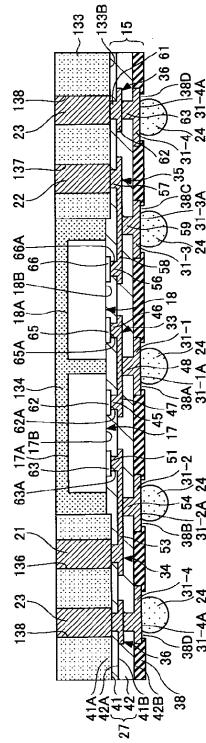

図2は、本発明の第1の実施の形態に係る電子装置の断面図である。

##### 【0035】

図2を参照するに、第1の実施の形態の電子装置10は、半導体装置11と、他の半導体装置である半導体装置12と、内部接続端子13とを有する。 20

##### 【0036】

半導体装置11は、多層配線構造体15と、電子部品17，18と、絶縁部材19と、貫通電極21～23と、外部接続端子24を有する。

##### 【0037】

多層配線構造体15は、絶縁部材19の下面19B（第1の面）、電子部品17，18の後述する電極パッド形成面17B，18B、薄板化された電子部品17，18に設けられた後述する電極パッド62，63，65，66を覆うように設けられている。

##### 【0038】

多層配線構造体15は、積層体27と、外部接続用パッド31-1，31-2，31-3，31-4と、配線パターン33～36と、ソルダーレジスト層38とを有する。 30

##### 【0039】

積層体27は、複数の絶縁層41，42が積層された構成とされている。絶縁層41は、電子部品17，18に設けられた電極パッド62，63，65，66と、電子部品17の電極パッド形成面17B（電極パッド62，63が設けられた側の面）、電子部品18の電極パッド形成面18B（電極パッド65，66が設けられた側の面）、及び絶縁部材19の下面19Bに設けられている。絶縁層41としては、例えば、絶縁樹脂層（例えば、エポキシ樹脂層）を用いることができる。絶縁層41の厚さは、例えば、5～30μmとすることができます。 40

##### 【0040】

絶縁層42は、絶縁層41の下面41Bに設けられている。絶縁層42としては、例えば、絶縁樹脂層（例えば、エポキシ樹脂層）を用いることができる。絶縁層42の厚さは、例えば、5～30μmとすることができます。

##### 【0041】

外部接続用パッド31-1，31-2，31-3，31-4は、絶縁層42の下面42Bに設けられている。外部接続用パッド31-1は、外部接続端子24が配設される接続面31-1Aを有する。外部接続用パッド31-1は、配線パターン33と接続されている。外部接続用パッド31-1は、配線パターン33を介して、電子部品17，18と電気的に接続されている。 50

**【0042】**

外部接続用パッド31-2は、外部接続端子24が配設される接続面31-2Aを有する。外部接続用パッド31-2は、配線パターン34と接続されている。外部接続用パッド31-2は、配線パターン34を介して、半導体装置12及び電子部品17と電気的に接続されている。

**【0043】**

外部接続用パッド31-3は、外部接続端子24が配設される接続面31-3Aを有する。外部接続用パッド31-3は、配線パターン35と接続されている。外部接続用パッド31-3は、配線パターン35を介して、半導体装置12及び電子部品18と電気的に接続されている。

10

**【0044】**

外部接続用パッド31-4は、外部接続端子24が配設される接続面31-4Aを有する。外部接続用パッド31-4は、配線パターン36と接続されている。外部接続用パッド31-4は、配線パターン36を介して、半導体装置12と電気的に接続されている。

**【0045】**

上記構成とされた外部接続用パッド31-1, 31-2, 31-3, 31-4の材料としては、例えば、Cuを用いることができる。

**【0046】**

配線パターン33～36は、積層体27を貫通するように、積層体27に内設されている。配線パターン33は、第1の接続部であるビア45, 46と、ビア48と、配線47とを有する。ビア45は、電子部品17に設けられた電極パッド62と対向する部分の絶縁層41を貫通するように設けられている。つまり、ビア45は、電子部品17の配設領域に対応する部分の絶縁層41から露出されている。ビア45の上端は、電極パッド62と直接接続されている。これにより、ビア45は、電子部品17と電気的に接続されている。

20

**【0047】**

ビア46は、電子部品18の電極パッド65と対向する部分の絶縁層41を貫通するように設けられている。つまり、ビア46は、電子部品18の配設領域に対応する部分の絶縁層41から露出されている。ビア46の上端は、電極パッド65と直接接続されている。これにより、ビア46は、電子部品18と電気的に接続されている。

30

**【0048】**

配線47は、絶縁層41の下面41B及びビア45, 46の下端面に設けられている。配線47は、ビア45, 46の下端と接続されている。配線47は、ビア45, 46を介して、電子部品17, 18と電気的に接続されている。

**【0049】**

ビア48は、配線47と外部接続用パッド31-1との間に位置する部分の絶縁層42を貫通するように設けられている。ビア48の上端は、配線47と接続されている。ビア48の下端は、外部接続用パッド31-1と接続されている。これにより、ビア48は、配線47と外部接続用パッド31-1とを電気的に接続している。上記構成とされた配線パターン33の材料としては、例えば、Cuを用いることができる。

40

**【0050】**

配線パターン34は、第1の接続部であるビア51と、第2の接続部であるビア52と、ビア54と、配線53とを有する。ビア51は、電子部品17の電極パッド63と対向する部分の絶縁層41を貫通するように設けられている。つまり、ビア51は、電子部品17の配設領域に対応する部分の絶縁層41から露出されている。ビア51の上端は、電極パッド63と直接接続されている。これにより、ビア51は、電子部品17と電気的に接続されている。

**【0051】**

ビア52は、貫通電極21の下方に位置する部分の絶縁層41を貫通するように設けられている。つまり、ビア52は、電子部品17の配設領域の外側に位置する部分の絶縁層

50

4 1 から露出されている。ビア 5 2 の上端は、貫通電極 2 1 の下端と直接接続されている。これにより、ビア 5 2 は、貫通電極 2 1 と電気的に接続されている。

#### 【 0 0 5 2 】

配線 5 3 は、絶縁層 4 1 の下面 4 1 B 及びビア 5 1 , 5 2 の下端面に設けられている。配線 5 3 は、ビア 5 1 , 5 2 の下端と接続されている。これにより、配線 5 3 は、ビア 5 1 , 5 2 を介して、電子部品 1 7 及び半導体装置 1 2 と電気的に接続されている。

#### 【 0 0 5 3 】

ビア 5 4 は、配線 5 3 と外部接続用パッド 3 1 - 2 との間に位置する部分の絶縁層 4 2 を貫通するように設けられている。ビア 5 4 の上端は、配線 5 3 と接続されており、ビア 5 4 の下端は、外部接続用パッド 3 1 - 2 と接続されている。これにより、ビア 5 4 は、配線 5 3 と外部接続用パッド 3 1 - 2 とを電気的に接続している。上記構成とされた配線パターン 3 4 の材料としては、例えば、Cu を用いることができる。10

#### 【 0 0 5 4 】

配線パターン 3 5 は、第 1 の接続部であるビア 5 6 と、第 2 の接続部であるビア 5 7 と、配線 5 8 と、ビア 5 9 とを有する。ビア 5 6 は、電子部品 1 8 の電極パッド 6 6 と対向する部分の絶縁層 4 1 を貫通するように設けられている。つまり、ビア 5 6 は、電子部品 1 8 の配設領域に対応する部分の絶縁層 4 1 から露出されている。ビア 5 6 の上端は、電極パッド 6 6 と直接接続されている。これにより、ビア 5 6 は、電子部品 1 8 と電気的に接続されている。

#### 【 0 0 5 5 】

ビア 5 7 は、貫通電極 2 2 の下方に位置する部分の絶縁層 4 1 を貫通するように設けられている。ビア 5 7 の上端は、貫通電極 2 2 の下端と直接接続されている。これにより、ビア 5 7 は、貫通電極 2 2 と電気的に接続されている。20

#### 【 0 0 5 6 】

配線 5 8 は、絶縁層 4 1 の下面 4 1 B 及びビア 5 6 , 5 7 の下端面に設けられている。配線 5 8 は、ビア 5 6 , 5 7 の下端と接続されている。これにより、配線 5 8 は、ビア 5 6 , 5 7 を介して、電子部品 1 8 及び半導体装置 1 2 と電気的に接続されている。

#### 【 0 0 5 7 】

ビア 5 9 は、配線 5 8 と外部接続用パッド 3 1 - 3 との間に位置する部分の絶縁層 4 2 を貫通するように設けられている。ビア 5 9 の上端は、配線 5 8 と接続されており、ビア 5 9 の下端は、外部接続用パッド 3 1 - 3 と接続されている。これにより、ビア 5 9 は、配線 5 8 と外部接続用パッド 3 1 - 3 とを電気的に接続している。上記構成とされた配線パターン 3 5 の材料としては、例えば、Cu を用いることができる。30

#### 【 0 0 5 8 】

配線パターン 3 6 は、第 2 の接続部であるビア 6 1 と、ビア 6 3 と、配線 6 2 とを有する。ビア 6 1 は、貫通電極 2 3 と対向する部分の絶縁層 4 1 を貫通するように設けられている。つまり、ビア 6 1 は、電子部品 1 8 の配設領域の外側に位置する部分の絶縁層 4 1 から露出されている。ビア 6 1 の上端は、貫通電極 2 3 の下端と直接接続されている。これにより、ビア 6 1 は、貫通電極 2 3 と電気的に接続されている。

#### 【 0 0 5 9 】

配線 6 2 は、絶縁層 4 1 の下面 4 1 B 及びビア 6 1 の下端面に設けられている。配線 6 2 は、ビア 6 1 の下端と接続されている。これにより、配線 6 2 は、ビア 6 1 を介して、貫通電極 2 3 と電気的に接続されている。40

#### 【 0 0 6 0 】

ビア 6 3 は、配線 6 2 と外部接続用パッド 3 1 - 4 との間に位置する部分の絶縁層 4 2 を貫通するように設けられている。ビア 6 3 の上端は、配線 6 2 と接続されており、ビア 6 3 の下端は、外部接続用パッド 3 1 - 4 と接続されている。これにより、ビア 6 3 は、配線 6 2 と外部接続用パッド 3 1 - 4 とを電気的に接続している。上記構成とされた配線パターン 3 6 の材料としては、例えば、Cu を用いることができる。

#### 【 0 0 6 1 】

10

20

30

40

50

ソルダーレジスト層38は、絶縁層42の下面42Bに設けられている。ソルダーレジスト層38は、接続面31-1Aを露出する開口部38Aと、接続面31-2Aを露出する開口部38Bと、接続面31-3Aを露出する開口部38Cと、接続面31-4Aを露出する開口部38Dとを有する。

#### 【0062】

上記構成とされた多層配線構造体15は、図2や後述する図13及び図14において、薄板化された電子部品17, 18の厚さや絶縁部材19の厚さよりも薄くなるように図示されている。しかし、実際には、多層配線構造体15の厚さは、薄板化された電子部品17, 18の厚さ（例えば、200～300μm）や絶縁部材19の厚さ（例えば、200～300μm）よりも薄い。多層配線構造体15の厚さは、例えば、20～80μmとすることができる。多層配線構造体15は、電子部品17, 18の電極パッド形成面17B, 18Bや絶縁部材19の下面19Bに、膜状又は層状に形成されている。10

#### 【0063】

電子部品17は、薄板化された電子部品であり、背面17Aと、背面17Aの反対側に位置する電極パッド形成面17Bと、複数の電極パッド62, 63を有する。電子部品17は、電子部品17の電極パッド形成面17Bと絶縁層41の上面41A（積層体27の上面）とが接触するように、絶縁層41の上面41Aに配設されている。電極パッド62, 63は、電子部品17の電極パッド形成面17Bに設けられている。電極パッド62, 63は、電子部品17の電極パッド形成面17Bから突出している。電極パッド62, 63は、絶縁層41により覆われている。20

#### 【0064】

電極パッド62は、接続面62Aを有する。接続面62Aは、配線パターン33の構成要素のうちの1つであるピア45の上端と直接接続されている。電極パッド63は、接続面63Aを有する。接続面63Aは、配線パターン34の構成要素のうちの1つであるピア51の上端と直接接続されている。つまり、電極パッド62, 63と配線パターン33, 34とが直接接続されることで、電子部品17と多層配線構造体15とが電気的に接続されている。絶縁層41上に配置された部分の電子部品17の厚さは、例えば、200～300μmとすることができる。

#### 【0065】

電子部品18は、薄板化された電子部品であり、背面18Aと、背面18Aの反対側に位置する電極パッド形成面18Bと、複数の電極パッド65, 66を有する。電子部品18は、電子部品18の電極パッド形成面18Bと絶縁層41の上面41Aとが接触するように、絶縁層41上に配設されている。電極パッド65, 66は、電子部品18の電極パッド形成面18Bに設けられている。電極パッド65, 66は、電子部品18の電極パッド形成面18Bから突出している。電極パッド65, 66は、絶縁層41により覆われている。30

#### 【0066】

電極パッド65は、接続面65Aを有する。接続面65Aは、配線パターン33の構成要素のうちの1つであるピア46の上端と直接接続されている。電極パッド66は、接続面66Aを有する。接続面66Aは、配線パターン35の構成要素のうちの1つであるピア56の上端と直接接続されている。つまり、電極パッド65, 66と配線パターン33, 35とが直接接続されることで、電子部品18と多層配線構造体15とが電気的に接続される。40

#### 【0067】

絶縁層41の上面41Aに配置された部分の電子部品18の厚さは、絶縁層41の上面41Aに配置された部分の電子部品17の厚さと略等しい。絶縁層41の上面41Aに配置された部分の電子部品18の厚さは、例えば、200～300μmとすることができる。

#### 【0068】

このように、絶縁層41の上面41Aと電子部品17, 18の電極パッド形成面17B50

, 18Bとが接触するように、絶縁層41の上面41Aに電子部品17, 18を配置し、電子部品17に設けられた電極パッド62, 63と配線パターン33, 34を構成するビア45, 51とを直接接続させると共に、電子部品18に設けられた電極パッド65, 66と配線パターン33, 35を構成するビア46, 56とを直接接続させることにより、バンプ或いは金属ワイヤを介して、電子部品と配線パターンとを電気的に接続させた従来の半導体装置と比較して、半導体装置11の厚さ方向のサイズの小型化を図ることができる。

#### 【0069】

また、電子部品17, 18に設けられた電極パッド62, 63, 65, 66と配線パターン33～35とを直接接続することにより、電子部品17, 18と配線パターン33～35とを接続するバンプ(例えば、はんだバンプ)が不要となるため、配線パターン33～35(具体的には、ビア45, 46, 51, 56及び配線47, 53, 58)を微細かつ高密度に配置することができる。

#### 【0070】

上記説明した電子部品17, 18としては、例えば、半導体チップを用いることができる。具体的には、電子部品17, 18としてCPU(Central Processing Unit)用の半導体チップを用いる場合や、電子部品17, 18のどちらか一方にCPU(Central Processing Unit)用の半導体チップを用い、他方にメモリ用の半導体チップを用いる場合や、電子部品17, 18のどちらか一方にCPU(Central Processing Unit)用の半導体チップを用い、他方にGPU(Graphics Processing Unit)用の半導体チップを用いる場合がある。

#### 【0071】

絶縁部材19は、電子部品17, 18の側面を覆うように、絶縁層41の上面41Aに設けられている。これにより、絶縁部材19は、電子部品17, 18の周囲(側面部分)を封止している。絶縁部材19は、絶縁層41の上面41Aに配置された部分の電子部品17, 18と略等しい厚さとされている。絶縁部材19の厚さは、例えば、200～300μmとすることができる。

#### 【0072】

絶縁部材19の上面19Aは、電子部品17, 18の背面17A, 18Aと略面一となるように構成されている。これにより、絶縁部材19の上面19Aと電子部品17, 18の背面17A, 18Aとは、同一平面上に配置されている。

#### 【0073】

このように、絶縁層41の上面41Aに、電子部品17, 18の側面を封止すると共に、電子部品17, 18の背面17A, 18Aと略面一とされた上面19Aを有する絶縁部材19を設けることにより、半導体装置11の厚さ方向のサイズを大型化させることなく、電子部品17, 18を封止することができる。

#### 【0074】

絶縁部材19は、貫通孔71～73を有する。貫通孔71は、ビア52の上端面を露出するように形成されている。貫通孔72は、ビア57の上端面を露出するように形成されている。貫通孔73は、ビア61の上端面を露出するように形成されている。

#### 【0075】

上記構成とされた絶縁部材19としては、例えば、モールド樹脂を用いることができる。モールド樹脂の材料としては、例えば、エポキシ樹脂を用いることができる。

#### 【0076】

貫通電極21は、貫通孔71に設けられている。貫通電極21の上端面は、平坦な面とされており、絶縁部材19の上面19Aと同一平面上に配置されている。貫通電極21の上端は、内部接続端子13と接続されている。貫通電極21は、内部接続端子13を介して、半導体装置12と電気的に接続されている。貫通電極21の下端面は、平坦な面とされており、絶縁部材19の下面19Bと略同一平面上に配置されている。なお、貫通電極21は、製造時の接着剤102の厚さ分だけ、絶縁部材19の下面19Bから突出する。

10

20

30

40

50

このため、実際には、貫通電極 2 1 の下端面と絶縁部材 1 9 の下面 1 9 B とは、完全な同一平面上に配置されない。

#### 【 0 0 7 7 】

貫通電極 2 1 の下端は、ビア 5 2 と直接接続されている。これにより、貫通電極 2 1 は、配線パターン 3 4 を介して、外部接続用パッド 3 1 - 2 と電気的に接続されている。貫通電極 2 1 の材料としては、例えば、Cu を用いることができる。

#### 【 0 0 7 8 】

貫通電極 2 2 は、貫通孔 7 2 に設けられている。貫通電極 2 2 の上端面は、平坦な面とされており、絶縁部材 1 9 の上面 1 9 A と同一平面上に配置されている。貫通電極 2 2 の上端は、内部接続端子 1 3 と接続されている。貫通電極 2 2 は、内部接続端子 1 3 を介して、半導体装置 1 2 と電気的に接続されている。貫通電極 2 2 の下端面は、平坦な面とされており、絶縁部材 1 9 の下面 1 9 B と略同一平面上に配置されている。なお、貫通電極 2 2 は、製造時の接着剤 1 0 2 の厚さ分だけ、絶縁部材 1 9 の下面 1 9 B から突出する。このため、実際には、貫通電極 2 2 の下端面と絶縁部材 1 9 の下面 1 9 B とは、完全な同一平面上に配置されない。

#### 【 0 0 7 9 】

貫通電極 2 2 の下端は、ビア 5 7 と直接接続されている。これにより、貫通電極 2 2 は、配線パターン 3 5 を介して、外部接続用パッド 3 1 - 3 と電気的に接続されている。貫通電極 2 2 の材料としては、例えば、Cu を用いることができる。

#### 【 0 0 8 0 】

貫通電極 2 3 は、貫通孔 7 3 に設けられている。貫通電極 2 3 の上端面は、平坦な面とされており、絶縁部材 1 9 の上面 1 9 A と同一平面上に配置されている。貫通電極 2 3 の上端は、内部接続端子 1 3 と接続されている。貫通電極 2 3 は、内部接続端子 1 3 を介して、半導体装置 1 2 と電気的に接続されている。貫通電極 2 3 の下端面は、平坦な面とされており、絶縁部材 1 9 の下面 1 9 B と略同一平面上に配置されている。なお、貫通電極 2 3 は、製造時の接着剤 1 0 2 の厚さ分だけ、絶縁部材 1 9 の下面 1 9 B から突出する。このため、実際には、貫通電極 2 3 の下端面と絶縁部材 1 9 の下面 1 9 B とは、完全な同一平面上に配置されない。

#### 【 0 0 8 1 】

貫通電極 2 3 の下端は、ビア 6 1 と接続されている。これにより、貫通電極 2 3 は、配線パターン 3 6 を介して、外部接続用パッド 3 1 - 4 と電気的に接続されている。貫通電極 2 3 の材料としては、例えば、Cu を用いることができる。

#### 【 0 0 8 2 】

上記説明したように、貫通電極 2 1 ~ 2 3 の上端面は、電子部品 1 7 , 1 8 の背面 1 7 A , 1 8 A 及び絶縁部材 1 9 の上面 1 9 A と同一平面上に配置されている。

#### 【 0 0 8 3 】

このように、絶縁部材 1 9 を貫通するように内部接続端子 1 3 と接続される貫通電極 2 1 ~ 2 3 を設けると共に、貫通電極 2 1 ~ 2 3 の上端面、電子部品 1 7 , 1 8 の背面 1 7 A , 1 8 A 、及び絶縁部材 1 9 の上面 1 9 A を同一平面上に配置することにより、半導体装置 1 2 と対向する半導体装置 1 1 の上面が平坦な面となるため、半導体装置 1 1 と半導体装置 1 2 とを電気的に接続する内部接続端子 1 3 の高さ方向のサイズを小さくすることができる。電子装置 1 0 の厚さ方向のサイズの小型化を図ることができる。

#### 【 0 0 8 4 】

また、内部接続端子 1 3 の高さ方向のサイズを小さくすることにより、貫通電極 2 1 ~ 2 3 を狭ピッチで配置することが可能となるので、半導体装置 1 1 と半導体装置 1 2 との間における電気的接続箇所を増加させることができ（言い換えれば、半導体装置 1 1 , 1 2 間に配置される内部接続端子 1 3 の数を増加させることができる。）。

#### 【 0 0 8 5 】

さらに、はんだボール等の内部接続端子 1 3 を小径化が可能となることにより、貫通電極 2 1 ~ 2 3 を狭ピッチ化できる。

10

20

30

40

50

**【0086】**

なお、内部接続端子13が接続される側の貫通電極21～23の端面に、保護層（例えば、貫通電極21～23の端面に、Niめっき層と、Auめっき層とを順次積層させたNi/Au積層膜）を設けてよい。

**【0087】**

外部接続端子24は、接続面31-1A, 31-2A, 31-3A, 31-4Aにそれぞれ設けられている。外部接続端子24は、電子装置10をマザーボード等の実装基板（図示せず）に接続する際、実装基板に設けられたパッドと接続される端子である。外部接続端子24としては、例えば、はんだボールを用いることができる。図2では、外部接続端子24としてははんだボールを用いた場合を例に挙げて図示したが、はんだボールの代わりにピン端子を外部接続端子24として用いてもよい。10

**【0088】**

本実施の形態の半導体装置によれば、絶縁層41の上面41Aと電子部品17, 18の電極パッド形成面17B, 18Bとが接触するように、絶縁層41の上面41Aに電子部品17, 18を配置し、電子部品17に設けられた電極パッド62, 63と配線パターン33, 34を構成するビア45, 51とを直接接続させると共に、電子部品18に設けられた電極パッド65, 66と配線パターン33, 35を構成するビア46, 56とを直接接続することにより、バンプ或いは金属ワイヤを介して、電子部品と配線パターンとを電気的に接続させた従来の半導体装置と比較して、半導体装置11の厚さ方向のサイズの小型化を図ることができる。20

**【0089】**

また、電子部品17, 18に設けられた電極パッド62, 63, 65, 66と配線パターン33～35とを直接接続することにより、電子部品17, 18と配線パターン33～35とを接続するバンプ（例えば、はんだバンプ）が不要となるため、配線パターン33～35（具体的には、ビア45, 46, 51, 56及び配線47, 53, 58）を微細かつ高密度に配置することができる。

**【0090】**

半導体装置12は、半導体装置11の上方に配置されており、配線基板81と、電子部品83と、モールド樹脂85とを有する。配線基板81は、基板本体91と、パッド93, 94と、配線パターン96と、ソルダーレジスト層98, 99とを有する。基板本体91は、板状とされている。基板本体91としては、例えば、複数の絶縁樹脂層が積層された積層体を用いることができる。30

**【0091】**

パッド93は、基板本体91の上面91Aに設けられている。パッド93は、金属ワイヤ84（例えば、Auワイヤ）の一方の端部及び配線パターン96の上端と接続されている。パッド93は、金属ワイヤ84を介して、電子部品83と電気的に接続されている。パッド93の材料としては、例えば、Cuを用いることができる。

**【0092】**

パッド94は、基板本体91の下面91Bに設けられている。パッド94は、配線パターン96の下端及び内部接続端子13と接続されている。パッド94は、配線パターン96を介して、パッド93と電気的に接続されると共に、内部接続端子13を介して、半導体装置11と電気的に接続されている。パッド94の材料としては、例えば、Cuを用いることができる。40

**【0093】**

配線パターン96は、基板本体91を貫通するように、基板本体91に内設されている。配線パターン96は、例えば、複数の配線及びビア（図示せず）により構成することができる。配線パターン96の上端は、パッド93と接続されており、配線パターン96の下端は、パッド94と接続されている。

**【0094】**

ソルダーレジスト層98は、基板本体91の上面91Aに設けられている。ソルダーレ50

ジスト層 9 8 は、パッド 9 3 の上面を露出する開口部 9 8 A を有する。

**【 0 0 9 5 】**

ソルダーレジスト層 9 9 は、基板本体 9 1 の下面 9 1 B に設けられている。ソルダーレジスト層 9 9 は、パッド 9 4 の下面を露出する開口部 9 9 A を有する。

**【 0 0 9 6 】**

電子部品 8 3 は、複数の電極パッド 1 0 0 を有する。電子部品 8 3 は、電極パッド 1 0 0 が形成されていない側の電子部品 8 3 の面とソルダーレジスト層 9 8 の上面とが接触するように、ソルダーレジスト層 9 8 上に接着されている。電極パッド 1 0 0 は、金属ワイヤ 8 4 の他方の端部と接続されている。これにより、電子部品 8 3 は、金属ワイヤ 8 4 を介して、配線基板 8 1 と電気的に接続されている。電子部品 8 3 としては、例えば、メモリ用の半導体チップを用いることができる。10

**【 0 0 9 7 】**

モールド樹脂 8 5 は、電子部品 8 3 及び金属ワイヤ 8 4 を覆うように、パッド 9 3 の上面及びソルダーレジスト 9 8 の上面に設けられている。モールド樹脂 8 5 は、電子部品 8 3 及び金属ワイヤ 8 4 を封止するための樹脂である。モールド樹脂 8 5 の材料としては、例えば、エポキシ樹脂を用いることができる。

**【 0 0 9 8 】**

内部接続端子 1 3 は、半導体装置 1 1 と半導体装置 1 2 との間に配置されると共に、貫通電極 2 1 ~ 2 3 のうちのいずれか 1 つの電極の上端及びパッド 9 4 と接続されている。20 これにより、内部接続端子 1 3 は、半導体装置 1 1 と半導体装置 1 2 とを電気的に接続している。先に説明したように、半導体装置 1 2 と対向する半導体装置 1 1 の上面は、平坦な面とされているため、内部接続端子 1 3 の高さ方向のサイズを小さくすることが可能である。内部接続端子 1 3 の高さ方向のサイズは、例えば、 $30 \mu m$  とすることができる。内部接続端子 1 3 としては、例えば、はんだボールを用いることができる。

**【 0 0 9 9 】**

本実施の形態の電子装置によれば、同一平面上に配置された電子部品 1 7 , 1 8 の背面 1 7 A , 1 8 A 、絶縁部材 1 9 の上面 1 9 A 、及び貫通電極 2 1 ~ 2 3 の上端面を有し、半導体装置 1 2 と対向する面が平坦な面とされた半導体装置 1 1 と、半導体装置 1 1 の上方に配置された半導体装置 1 2 と、内部接続端子 1 3 を介して電気的に接続することにより、内部接続端子 1 3 の高さ方向のサイズを小さくすることが可能となるため、電子装置 1 0 の高さ方向のサイズの小型化を図ることができる。30

**【 0 1 0 0 】**

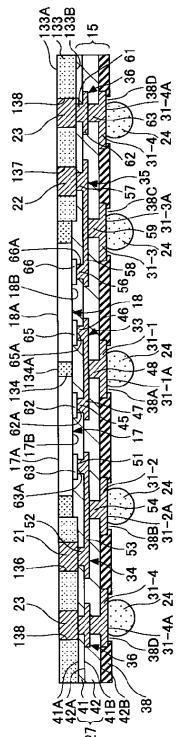

図 3 ~ 図 1 4 は、本発明の第 1 の実施の形態に係る半導体装置の製造工程を示す図である。図 3 ~ 図 1 4 において、第 1 の実施の形態の半導体装置 1 1 と同一構成部分には同一符号を付す。

**【 0 1 0 1 】**

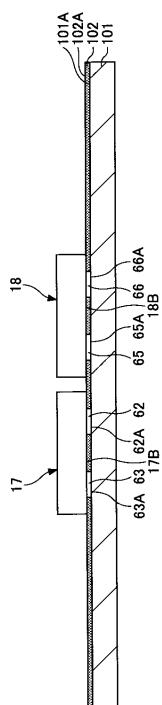

図 3 ~ 図 1 4 を参照して、第 1 の実施の形態の半導体装置 1 1 の製造方法について説明する。始めに、図 3 に示す工程では、支持体 1 0 1 の上面 1 0 1 A に接着剤 1 0 2 を形成した後、接着剤 1 0 2 により、電子部品 1 7 , 1 8 と支持体 1 0 1 とを接着させる（電子部品接着工程）。40

**【 0 1 0 2 】**

このとき、支持体 1 0 1 の上面 1 0 1 A と電極パッド 6 2 , 6 3 , 6 5 , 6 6 の接続面 6 2 A , 6 3 A , 6 5 A , 6 6 A とが接触するように、電子部品 1 7 , 1 8 と支持体 1 0 1 とを接着させる。なお、押圧により電子部品 1 7 , 1 8 が接着剤 1 0 2 に埋め込まれるようにし、電極パッド 6 2 , 6 3 , 6 5 , 6 6 の接続面 6 2 A , 6 3 A , 6 5 A , 6 6 A が支持体 1 0 1 の上面 1 0 1 A と接触するようにするとよい。

**【 0 1 0 3 】**

この段階での電子部品 1 7 , 1 8 は、薄板化されていない。このような薄板化されていない電子部品 1 7 , 1 8 は、薄板化された電子部品 1 7 , 1 8 よりもハンドリングしやすいため、支持体 1 0 1 の所定の位置に電子部品 1 7 , 1 8 を精度良く接着することができ50

る。薄板化前の電子部品 17, 18 の厚さは、例えば、 $700 \mu\text{m}$  とすることができます。

#### 【0104】

電子部品 17, 18 としては、例えば、半導体チップを用いることができる。具体的には、電子部品 17, 18 として C P U (Central Processing Unit) 用の半導体チップを用いる場合や、電子部品 17, 18 のどちらか一方に C P U (Central Processing Unit) 用の半導体チップを用い、他方にメモリ用の半導体チップを用いる場合や、電子部品 17, 18 のどちらか一方に C P U (Central Processing Unit) 用の半導体チップを用い、他方に G P U (Graphics Processing Unit) 用の半導体チップを用いる場合がある。

#### 【0105】

支持体 101 としては、例えば、ガラス基板、シリコン基板、金属板（例えば、Cu 板）等を用いることができる。支持体 101 の厚さは、例えば、 $300 \sim 600 \mu\text{m}$  とすることができます。接着剤 102 としては、例えば、接着性を有したポリイミド樹脂テープ（例えば、厚さ  $1 \sim 20 \mu\text{m}$ ）を用いることができる。

#### 【0106】

次いで、図 4 に示す工程では、接着剤 102 の上面 102A に、電子部品 17, 18 の側面の一部を封止する絶縁部材 19 を形成する（絶縁部材形成工程）。絶縁部材 19 としては、例えば、モールド樹脂（例えば、エポキシ樹脂よりなるモールド樹脂）を用いることができる。絶縁部材 19 は、例えば、トランスマルチモード法により形成することができる。絶縁部材 19 は、薄板化後の電子部品 17, 18 の背面 17A, 18A よりも上方に絶縁部材 19 の上面が位置するように形成する。この段階での絶縁部材 19 の厚さは、例えば、 $300 \mu\text{m}$  とすることができます。

#### 【0107】

次いで、図 5 に示す工程では、図 4 に示す構造体の上面側（電子部品 17, 18 の背面 17A, 18A 側）から、電子部品 17, 18 及び絶縁部材 19 を研削（例えば、バックサイドグラインダによる研削）することで、電子部品 17, 18 を薄板化すると共に、薄板化された電子部品 17, 18 の背面 17A, 18A と研削された絶縁部材 19 の上面 19A とを同一平面上に配置させる（研削工程。）。

#### 【0108】

これにより、図 5 に示す構造体の上面は、平坦な面となる。薄板化された電子部品 17, 18 の厚さ（接着剤 102 上に配置された部分の電子部品 17, 18 の厚さ）は、例えば、 $200 \mu\text{m}$  とすることができます。この場合、研削後の絶縁部材 19 の厚さは、例えば、 $200 \mu\text{m}$  とすることができます。

#### 【0109】

次いで、図 6 に示す工程では、絶縁部材 19 の上面 19A 側から、絶縁部材 19 及び接着剤 102 を貫通する貫通孔 71 ~ 73 を形成する（貫通孔形成工程）。

#### 【0110】

貫通孔 71 ~ 73 は、例えば、貫通孔 71 ~ 73 の形成領域に対応する部分の絶縁部材 19 及び接着剤 102 にレーザを照射することで形成できる。貫通孔 71 ~ 73 は、支持体 101 の上面 101A を露出している。貫通孔 71 ~ 73 の直径は、例えば、 $200 \mu\text{m}$  とすることができます。

#### 【0111】

次いで、図 7 に示す工程では、貫通孔 71 を充填する貫通電極 21、貫通孔 72 を充填する貫通電極 22、及び貫通孔 73 を充填する貫通電極 23 を同時に形成する（貫通電極形成工程）。

#### 【0112】

このとき、貫通電極 21 ~ 23 は、貫通電極 21 ~ 23 の上端面、電子部品 17, 18 の背面 17A, 18A、及び絶縁部材 19 の上面 19A が同一平面上に配置されるように形成する。貫通電極 21 ~ 23 は、例えば、めっき法や印刷法等により形成することができます。

#### 【0113】

10

20

30

40

50

めっき法を用いて貫通電極 21～23 を形成する場合、支持体 101（例えば、シリコン基板、ガラス基板等）の上面 101A に、スパッタ法により Cu 層（シリコン基板、ガラス基板の場合には給電層となる）を形成し、その後、先に説明した図 3～図 6 に示す工程と同様な処理を行った後、Cu 層に給電して、貫通孔 71～73 を充填するようにめっき膜を析出成長させることで、貫通電極 21～23 を形成する。貫通電極 21～23 の材料としては、例えば、Cu を用いることができる。

#### 【0114】

なお、支持体 101 として金属板（例えば、Cu 板）を用いる場合、支持体 101 が給電層として機能するため上記 Cu 層の形成は不要となる。

#### 【0115】

また、貫通電極 21～23 を形成後、内部接続端子 13 が接続される側の貫通電極 21～23 の端面に、保護層（例えば、貫通電極 21～23 の端面に、Ni めっき層と、Au めっき層とを順次積層させた Ni / Au 積層膜）を設けてもよい。

#### 【0116】

次いで、図 8 に示す工程では、図 7 に示す電子部品 17, 18 及び貫通電極 21～23 が形成された絶縁部材 19 から接着剤 102 及び支持体 101 を除去する（支持体除去工程）。

#### 【0117】

具体的には、例えば、図 7 に示す電子部品 17, 18 及び貫通電極 21～23 が形成された絶縁部材 19 から、支持体 101 を機械的に剥がすことで、支持体 101 と共に、接着剤 102 を除去する。これにより、貫通電極 21～23 及び電極パッド 62, 63, 65, 66 は、接着剤 102 の厚さ分だけ、絶縁部材 19 の下面 19B から突出するが、多少突出していたとしても製造工程上問題は無い。また、貫通電極 21～23 の下端面及び電極パッド 62, 63, 65, 66 の接続面 62A, 63A, 65A, 66A と絶縁部材 19 の下面 19B とは、完全な同一平面には配置されない。

#### 【0118】

次いで、図 9 に示す工程では、絶縁部材 19 の下面 19B、電極パッド 62, 63, 65, 66、電子部品 17, 18 の電極パッド形成面 17B, 18B、及び貫通電極 21～23 の下端面に、開口部 111～117 を有した絶縁層 41 を形成する。

#### 【0119】

具体的には、絶縁層 41 は、例えば、図 8 に示す構造体の下面に絶縁層 41 の母材となる絶縁樹脂フィルム（例えば、エポキシ樹脂フィルム）を貼り付けた後、開口部 111～117 に対応する部分の絶縁樹脂フィルムをレーザ加工することで形成する。

#### 【0120】

開口部 111 は、接続面 62A を露出するように形成し、開口部 112 は、接続面 63A を露出するように形成する。また、開口部 113 は、接続面 65A を露出するように形成し、開口部 114 は、接続面 66A を露出するように形成する。また、開口部 115 は、貫通電極 21 の下端面を露出するように形成し、開口部 116 は、貫通電極 22 の下端面を露出するように形成する。さらに、開口部 117 は、貫通電極 23 の下端面を露出するように形成する。

#### 【0121】

次いで、図 10 に示す工程では、開口部 111～117 及び絶縁層 41 の下面 41B に、ピア 45, 46, 51, 52, 56, 57, 61 及び配線 47, 53, 58, 62 を同時に形成する。これにより、電子部品 17 に設けられた電極パッド 62, 63 とピア 45, 51 とが直接接続されると共に、電子部品 18 に設けられた電極パッド 65, 66 とピア 46, 56 とが直接接続される。

#### 【0122】

このように、電子部品 17, 18 の電極パッド 62, 63, 65, 66 とピア 45, 46, 51, 56 とを直接接続することにより、バンプ或いは金属ワイヤを介して、電子部品と配線パターンとを電気的に接続させた従来の半導体装置と比較して、半導体装置 11

10

20

30

40

50

の厚さ方向のサイズの小型化を図ることができる。

**【0123】**

ビア52は、貫通電極21の下端と直接接続され、ビア57は、貫通電極22の下端と直接接続される。また、ビア61は、貫通電極23の下端と直接接続される。

**【0124】**

ビア45, 46, 51, 52, 56, 57, 61及び配線47, 53, 58, 62は、例えば、セミアディティブ法により形成することができる。ビア45, 46, 51, 52, 56, 57, 61及び配線47, 53, 58, 62の材料としては、例えば、Cuを用いることができる。

**【0125】**

次いで、図11に示す工程では、先に説明した図9に示す工程と同様な処理を行うことにより、絶縁層41の下面41Bに、開口部121～124を有した絶縁層42を形成する。これにより、複数の絶縁層41, 42が積層された積層体27が形成される。開口部121は、配線47の一部を露出するように形成し、開口部122は、配線53の一部を露出するように形成する。開口部123は、配線58の一部を露出するように形成し、開口部124は、配線62の一部を露出するように形成する。上記絶縁層42としては、例えば、エポキシ樹脂フィルムを用いることができる。

10

**【0126】**

次いで、図12に示す工程では、先に説明した図10に示す工程と同様な処理を行うことにより、開口部121～124及び絶縁層42の下面42Bに、ビア48, 54, 59, 63と、接続面31-1A, 31-2A, 31-3A, 31-4Aを有した外部接続用パッド31-1, 31-2, 31-3, 31-4とを同時に形成する。

20

**【0127】**

これにより、電子部品17, 18と外部接続用パッド31-1とを電気的に接続する配線パターン33と、電子部品17及び貫通電極21と外部接続用パッド31-2とを電気的に接続する配線パターン34と、電子部品18及び貫通電極22と外部接続用パッド31-3とを電気的に接続する配線パターン35と、貫通電極23と外部接続用パッド31-4とを電気的に接続する配線パターン36とが形成される。

**【0128】**

ビア48, 54, 59, 63及び外部接続用パッド31-1, 31-2, 31-3, 31-4の材料としては、例えば、Cuを用いることができる。

30

**【0129】**

次いで、図13に示す工程では、絶縁層42の下面42Bに、開口部38A, 38B, 38C, 38Dを有したソルダーレジスト層38を形成する。開口部38Aは、接続面31-1Aを露出するように形成し、開口部38Bは、接続面31-2Aを露出するように形成する。開口部38Cは、接続面31-3Aを露出するように形成し、開口部38Dは、接続面31-4Aを露出するように形成する。なお、接続面31-1A, 31-2A, 31-3A, 31-4Aに、Niめっき層と、Auめっき層とを順次積層させ、Ni/Au積層膜よりなる保護層を設けてもよい。図9～図13に示す工程が、「多層配線構造体形成工程」に相当する工程である。

40

**【0130】**

次いで、図14に示す工程では、接続面31-1A, 31-2A, 31-3A, 31-4Aに、それぞれ1つの外部接続端子24を形成する。外部接続端子24としては、例えば、はんだボールを用いることができる。なお、図14では、外部接続端子24としてははんだボールを用いた場合を例に挙げて図示したが、はんだボールの代わりにピン端子を外部接続端子24として用いてもよい。なお、外部接続端子24として、はんだボール等を設ける代わりに、接続面31-1A, 31-2A, 31-3A, 31-4A自体を外部接続端子として用いてもよい。

**【0131】**

本実施の形態の半導体装置の製造方法によれば、支持体101の上面101Aと電子部

50

品 17, 18 に設けられた電極パッド 62, 63, 65, 66 とが接触するように、接着剤 102 により、支持体 101 と電子部品 17, 18 を接着し、次いで、接着剤 102 の上面 102A に電子部品 17, 18 の周囲（側面）の一部を封止する絶縁部材 19 を形成し、次いで、電子部品 17, 18 及び絶縁部材 19 を研削することにより、電子部品 17, 18 を薄板化すると共に、薄板化された電子部品 17, 18 の背面 17A, 18A と絶縁部材 19 の上面 19A とを同一平面上に配置し、次いで、絶縁部材 19 を貫通する貫通電極 21～23 を形成し、次いで、接着剤 102 及び支持体 101 を除去し、その後、絶縁部材 19 の下面 19B、電極パッド 62, 63, 65, 66、電子部品 17, 18 の電極パッド形成面 17B, 18B、及び貫通電極 21～23 の下端面に、電極パッド 62, 63, 65, 66 及び貫通電極 21～23 の下端面と直接接続される配線パターン 33～36 を形成することにより、バンプ或いは金属ワイヤを介して、電子部品と配線パターンとを電気的に接続させた従来の半導体装置と比較して、半導体装置 11 の厚さ方向のサイズの小型化を図ることができる。

10

#### 【0132】

また、電子部品 17, 18 に設けられた電極パッド 62, 63, 65, 66 と配線パターン 33～35 を直接接続することにより、電子部品 17, 18 と配線パターン 33～35 を接続するバンプ（例えば、はんだバンプ）が不要となるため、配線パターン 33～35（具体的には、ピア 45, 46, 51, 56 及び配線 47, 53, 58）を微細かつ高密度に形成することができる。

#### 【0133】

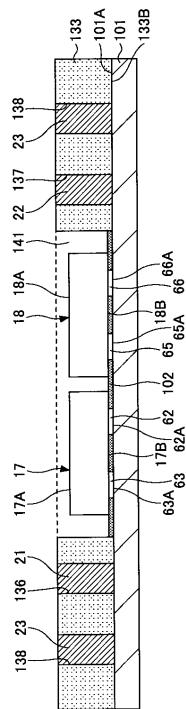

（第 2 の実施の形態）

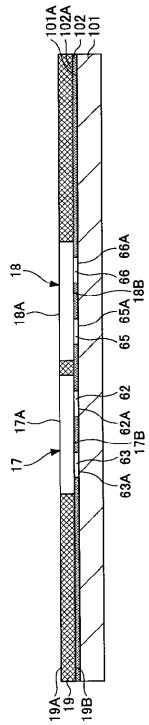

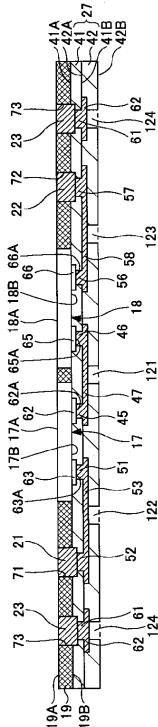

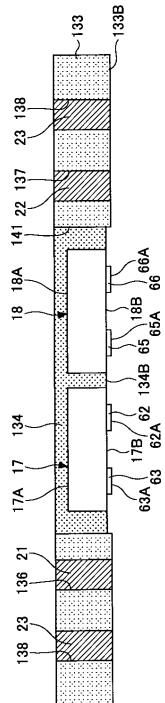

図 15 は、本発明の第 2 の実施の形態に係る電子装置の断面図である。図 15 において、第 1 の実施の形態の電子装置 10 と同一構成部分には同一符号を付す。

20

#### 【0134】

図 15 を参照するに、第 2 の実施の形態の電子装置 130 は、第 1 の実施の形態の電子装置 10 に設けられた半導体装置 11 の代わりに半導体装置 131 を設けた以外は、電子装置 10 と同様に構成される。

#### 【0135】

半導体装置 131 は、第 1 の実施の形態で説明した半導体装置 11 に設けられた絶縁部材 19 の代わりに絶縁部材 133 及び封止樹脂 134 を設けた以外は、半導体装置 11 と同様に構成される。

30

#### 【0136】

絶縁部材 133 は、絶縁層 41 の上面 41A に設けられている。絶縁部材 133 は、貫通孔 136～138 と、貫通部 141 とを有する。貫通孔 136 は、ピア 52 の上面を露出するように形成されている。貫通孔 137 は、ピア 57 の上面を露出するように形成されている。貫通孔 138 は、ピア 61 の上面を露出するように形成されている。貫通部 141 は、絶縁部材 133 を貫通するように形成されている。貫通部 141 は、多層配線構造体 15（具体的には、配線パターン 33～35）と電気的に接続された電子部品 17, 18 を収容するための空間である。

#### 【0137】

絶縁部材 133 は、絶縁層 41 の上面 41A に配置された部分の電子部品 17, 18 の厚さと略等しくなるように構成されている。絶縁層 41 の上面 41A に配置された部分の電子部品 17, 18 の厚さが 200 μm の場合、絶縁部材 133 の厚さは、例えば、200 μm とすることができます。絶縁部材 133 の上面 133A は、平坦な面とされている。絶縁部材 133 の上面 133A は、電子部品 17, 18 の背面 17A, 18A と略面一となるように構成されている。これにより、絶縁部材 133 の上面 133A 及び電子部品 17, 18 の背面 17A, 18A は、同一平面上に配置されている。上記構成とされた絶縁部材 133 としては、例えば、エポキシ樹脂層を用いることができる。

40

#### 【0138】

封止樹脂 134 は、電子部品 17, 18 が収容された貫通部 141 を充填するように配

50

置されている。封止樹脂 134 は、電子部品 17, 18 の背面 17A, 18A を露出している。封止樹脂 134 は、電子部品 17, 18 の側面を覆っている。これにより、封止樹脂 134 は、電子部品 17, 18 の側面部を封止している。封止樹脂 134 の上面 134A は、平坦な面とされている。封止樹脂 134 の上面 134A は、電子部品 17, 18 の背面 17A, 18A 及び絶縁部材 133 の上面 133A と略面一になるように構成されている。封止樹脂 134 の厚さは、絶縁層 41 の上面 41A に配置された部分の電子部品 17, 18 の厚さ及び絶縁部材 133 の厚さと略等しい。封止樹脂 134 の厚さは、例えば、 $200\mu m$  とすることができます。封止樹脂 134 の材料としては、例えば、エポキシ樹脂を用いることができる。

## 【0139】

10

上記構成とされた第 2 の実施の形態の半導体装置 131 は、第 1 の実施の形態の半導体装置 11 と同様な効果を得ることができます。

## 【0140】

本実施の形態の電子装置によれば、電子部品 17, 18 の背面 17A, 18A、絶縁部材 133 の上面 133A、及び封止樹脂 134 の上面 134A を同一平面上に配置することにより、半導体装置 12 と対向する半導体装置 131 の上面が平坦な面となるため、半導体装置 131 と半導体装置 12 との間に配置される内部接続端子 13 の高さ方向のサイズを小さくすることができるため、電子装置 130 の厚さ方向のサイズの小型化を図ることができます。

## 【0141】

20

また、内部接続端子 13 の高さ方向のサイズを小さくすることにより、貫通電極 21～23 を狭ピッチで配置することができるため、半導体装置 131 と半導体装置 12 の間ににおける電気的接続箇所を増加させることができ（言い換えれば、半導体装置 131 と半導体装置 12 の間に配置される内部接続端子 13 の数を増加させることができる。）。

## 【0142】

さらに、はんだボール等の内部接続端子 13 を小径化が可能となることにより、貫通電極 21～23 を狭ピッチ化できる。

## 【0143】

30

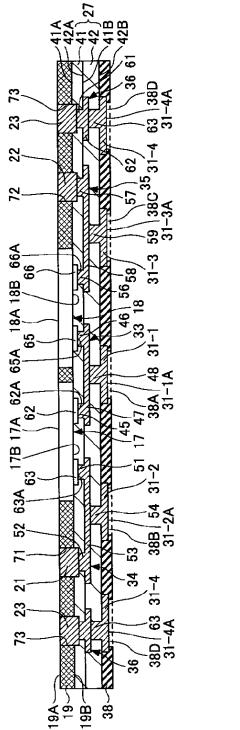

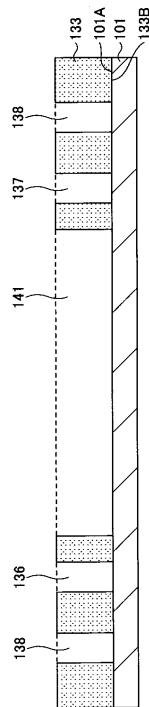

図 16～図 23 は、本発明の第 2 の実施の形態に係る半導体装置の製造工程を示す図である。図 16～図 23 において、第 2 の実施の形態の半導体装置 131 と同一構成部分には同一符号を付す。

## 【0144】

図 16～図 23 を参照して、第 2 の実施の形態の半導体装置 131 の製造方法について説明する。始めに、図 16 に示す工程では、支持体 101 の上面 101A に絶縁部材 133 を形成する。

## 【0145】

具体的には、絶縁部材 133 は、例えば、支持体 101 の上面 101A に、樹脂（例えば、エポキシ樹脂）を塗布することで形成する。なお、図 16 に示す絶縁部材 133 は、先に説明した図 15 に示す絶縁部材 133 よりも厚さが厚くなるように形成する。この段階での絶縁部材 133 の厚さは、例えば、 $300\mu m$  にすることができる。

40

## 【0146】

次いで、図 17 に示す工程では、絶縁部材 133 を貫通する貫通部 141 及び貫通孔 136～138 を形成する。貫通部 141 及び貫通孔 136～138 は、例えば、貫通部 141 及び貫通孔 136～138 の形成領域に対応する部分の絶縁部材 133 にレーザを照射することで形成できる。なお、図 17 に示す貫通部 141 及び貫通孔 136～138 の深さは、先に説明した図 15 に示す貫通部 141 及び貫通孔 136～138 の深さ（例えば、 $200\mu m$ ）よりも深い。電子部品 17, 18 の大きさが  $5mm \times 9mm$  の場合、貫通部 141 の大きさは、例えば、 $15mm \times 14mm$  とすることができる。また、貫通電極 136～138 の直径は、例えば、 $200\mu m$  とすることができます。

50

**【0147】**

次いで、図18に示す工程では、貫通孔136を充填する貫通電極21と、貫通孔137を充填する貫通電極22と、貫通孔138を充填する貫通電極23とを同時に形成する。貫通電極21～23は、例えば、第1の実施の形態で説明した図7に示す工程と同様なめっき処理を行うことで形成できる。なお、この際、貫通部141にめっき膜が形成されないように、めっき処理の前に、貫通部141をめっき用レジストで被覆する。貫通電極21～23の材料としては、例えば、Cuを用いることができる。

**【0148】**

次いで、図19に示す工程では、貫通部141の形成領域に対応する部分の支持体101の上面101Aと接続面62A、63A、65A、66Aとが接触するように、接着剤102により、電子部品17、18と支持体101とを接着する。図19に示す電子部品17、18は、薄板化される前の電子部品17、18であり、先に説明した図15に示す電子部品17、18の厚さよりも厚くなるように構成されている。このような薄板化されていない電子部品17、18は、薄板化された電子部品17、18よりもハンドリングしやすいため、支持体101の所定の位置に電子部品17、18を精度良く接着することができる。薄板化されていない電子部品17、18の厚さは、例えば、700μmとすることができる。

10

**【0149】**

電子部品17、18としては、例えば、半導体チップを用いることができる。具体的には、電子部品17、18としてCPU(Central Processing Unit)用の半導体チップを用いる場合や、電子部品17、18のどちらか一方にCPU(Central Processing Unit)用の半導体チップを用い、他方にメモリ用の半導体チップを用いる場合や、電子部品17、18のどちらか一方にCPU(Central Processing Unit)用の半導体チップを用い、他方にGPU(Graphics Processing Unit)用の半導体チップを用いる場合がある。

20

**【0150】**

次いで、図20に示す工程では、貫通部141を充填する封止樹脂134を形成する。これにより、電子部品17、18は、封止樹脂134により封止される。封止樹脂134は、例えば、トランスファーモールド法、圧縮形成法、ポッティング法等の手法により形成することができる。封止樹脂134の材料としては、例えば、エポキシ樹脂を用いることができる。

30

**【0151】**

次いで、図21に示す工程では、図20に示す構造体から支持体101及び接着剤102を除去する。具体的には、例えば、支持体101を機械的に剥がすことで、支持体101と共に、接着剤102を除去する。これにより、電子部品17、18の電極パッド形成面17B、18B、電極パッド62、63、65、66、貫通電極21～23の下端面、絶縁部材133の下面133B、及び封止樹脂134の下面134Bが露出される。

**【0152】**

なお、支持体101及び接着剤102を除去すると、封止樹脂134の下面134Bと電子部品17、18の電極パッド形成面17B、18Bが、絶縁部材133の下面133Bから、接着剤102の厚さ分だけ凹んだ構造となるが、製造工程上問題とならない。

40

**【0153】**

次いで、図22に示す工程では、第1の実施の形態で説明した図9～図14に示す工程と同様な処理を行うことで、電子部品17、18の電極パッド形成面17B、18B、電極パッド62、63、65、66、貫通電極21～23の下端面、絶縁部材133の下面133B、及び封止樹脂134の下面134Bに、電子部品17、18及び貫通電極21～23と電気的に接続された多層配線構造体15を形成する。

**【0154】**

このとき、配線パターン33は、電極パッド62、65と直接接続されるように形成する。また、配線パターン34は、貫通電極21の下端及び電極パッド63と直接接続されるように形成する。また、配線パターン35は、貫通電極22の下端及び電極パッド66

50

と直接接続されるように形成する。さらに、配線パターン36は、貫通電極23の下端と直接接続されるように形成する。

#### 【0155】

このように、電極パッド62, 63, 65, 66と配線パターン33～35とを直接接続することにより、バンプ或いは金属ワイヤを介して、電子部品と配線パターンとを電気的に接続させた従来の半導体装置と比較して、半導体装置131の厚さ方向のサイズの小型化を図ることができる。

#### 【0156】

次いで、図23に示す工程では、図22に示す構造体の上面側から、電子部品17, 18、貫通電極21～23、絶縁部材133、及び封止樹脂134を研削（例えば、バックサイドグラインダを用いた研削）することにより、電子部品17, 18の薄板化を行う。これにより、第2の実施の形態の半導体装置131が製造される。

#### 【0157】

また、上記研削により、図22に示す貫通電極21～23と比較して貫通電極21～23の深さが浅くなると共に、貫通電極21～23の上端面、電子部品17, 18の背面17A, 18A、絶縁部材133の上面133A、及び封止樹脂134の上面134Aが同一平面上に配置される。

#### 【0158】

絶縁層41の上面41Aに配置された部分の薄板化後の電子部品17, 18の厚さは、例えば、200μmにすることができる。この場合、貫通電極21～23の深さは、例えば、200μmとすることができます。また、絶縁部材133及び封止樹脂134の厚さは、例えば、200μmとすることができます。

#### 【0159】

なお、電子部品17, 18の薄板化した後、内部接続端子13が接続される側の貫通電極21～23の端面に、保護層（例えば、貫通電極21～23の端面に、Niめっき層と、Auめっき層とを順次積層させたNi/Au積層膜）を設けてもよい。

#### 【0160】

本実施の形態の半導体装置の製造方法によれば、支持体101の上面101Aに貫通孔136～138及び貫通部141を有した絶縁部材133を形成し、次いで、貫通部141から露出された部分の支持体101の上面101Aに、接着剤102により、接続面62A, 63A, 65A, 66Aと支持体101の上面101Aとが接触するように、電子部品17, 18を接着し、次いで、貫通部141に電子部品17, 18を封止する封止樹脂134を形成し、次いで、接着剤102及び支持体101を除去し、次いで、電子部品17, 18の電極パッド62, 63, 65, 66と配線パターン33～35とが直接接続されるように多層配線構造体15を形成することにより、バンプ或いは金属ワイヤを介して、電子部品と配線パターンとを電気的に接続させた従来の半導体装置と比較して、半導体装置131の厚さ方向のサイズの小型化を図ることができる。

#### 【0161】

また、電子部品17, 18に設けられた電極パッド62, 63, 65, 66と配線パターン33～35とを直接接続することにより、電子部品17, 18と配線パターン33～35とを接続するバンプ（例えば、はんだバンプ）が不要となるため、配線パターン33～35（具体的には、ビア45, 46, 51, 56及び配線47, 53, 58）を微細かつ高密度に形成することができる。

#### 【0162】

なお、本実施の形態では、多層配線構造体15を形成後に、電子部品17, 18の薄板化を行った場合を例に挙げて説明したが、図20に示す工程の後に、研磨により電子部品17, 18の薄板化を行い、次いで、支持体101を除去し、その後、多層配線構造体15を形成してもよい。

#### 【0163】

また、外部接続端子39は、電子部品17, 18の薄板化後に形成してもよい。

10

20

30

40

50

## 【0164】

以上、本発明の好ましい実施の形態について詳述したが、本発明はかかる特定の実施の形態に限定されるものではなく、特許請求の範囲内に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

## 【0165】

例えば、第1及び第2の実施の形態の半導体装置11, 131では、2つの電子部品(電子部品17, 18)を設けた場合を例に挙げて説明したが、多層配線構造体15上に配置される電子部品の数はこれに限定されない。つまり、多層配線構造体15上に配置される電子部品の数は、1つでもよいし、3つ以上でもよい。

## 【符号の説明】

10

## 【0166】

10, 130 電子装置

11, 12, 131 半導体装置

13 内部接続端子

16, 81 多層配線構造体

17, 18, 83 電子部品

17A, 18A 背面

17B, 18B 電極パッド形成面

19 絶縁部材

19A, 41A, 42A, 91A, 101A, 102A, 133A, 134A 上面

20

19B, 41B, 42B, 91B, 133B, 134B 下面

21~23 貫通電極

24 外部接続端子

27 積層体

31-1, 31-2, 31-3, 31-4 外部接続用パッド

31-1A, 31-2A, 31-3A, 31-4A 接続面

33~36, 96 配線パターン

38, 98, 99 ソルダーレジスト層

38A, 38B, 38C, 38D, 98A, 99A, 111~117, 121~124

開口部

30

41, 42 絶縁層

45, 46, 48, 51, 52, 54, 56, 57, 59, 61, 63 ピア

47, 53, 58, 62 配線

62, 63, 65, 66, 100 電極パッド

62A, 63A, 65A, 66A 接続面

71~73, 136~138 貫通孔

84 金属ワイヤ

85 モールド樹脂

91 基板本体

93, 94 パッド

40

101 支持体

102 接着剤

141 貫通部

【図1】

【図2】

### 従来の電子装置の断面図

### 本発明の第1の実施の形態に係る電子装置の断面図

【 図 3 】

【図4】

本発明の第1の実施の形態に係る半導体装置の製造工程(その1)を示す図

【図5】

本発明の第1の実施の形態に係る半導体装置の製造工程(その3)を示す図

【図6】

本発明の第1の実施の形態に係る半導体装置の製造工程(その4)を示す図

【図7】

本発明の第1の実施の形態に係る半導体装置の製造工程(その5)を示す図

【図8】

本発明の第1の実施の形態に係る半導体装置の製造工程(その6)を示す図

【図9】

本発明の第1の実施の形態に係る半導体装置の製造工程(その7)を示す図

【 図 1 0 】

本発明の第1の実施の形態に係る半導体装置の製造工程(その8)を示す図

【図11】

本発明の第1の実施の形態に係る半導体装置の製造工程(その9)を示す図

【図12】

本発明の第1の実施の形態に係る半導体装置の製造工程(その10)を示す図

【図13】

本発明の第1の実施の形態に係る半導体装置の製造工程(その11)を示す図 本発明の第1の実施の形態に係る半導体装置の製造工程(その12)を示す図

【図17】

本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その2) 本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その3)

【図19】

【図20】

本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その4) 本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その5)

【図21】

【図22】

本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その7)

【図23】

本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その8)

---

フロントページの続き

(56)参考文献 特開2004-095836(JP,A)

特開2003-318323(JP,A)

特開2004-221418(JP,A)

特開2007-287803(JP,A)

特開2004-342862(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/065

H01L 25/07

H01L 25/10

H01L 25/11

H01L 25/18

H01L 23/12